要約

MAX2742を内蔵したCMOS RFフロントエンドGPSレシーバを使用して、最小限の外付け部品で完全なGPSのソリューションを実現することができます。

はじめに

MAX2742は、シングルチップのCMOS GPSフロントエンドダウンコンバータです。この最先端デバイスは、消費電力が極めて少なく(2.4Vで32mW)、高価なIFSAWフィルタや、かさばるディスクリートのIFバンドパスフィルタを必要としません。MAX2742は、低ノイズアンプ(LNA)、ミキサ、BPF、自動利得制御(AGC)アンプ、局部発振器シンセサイザ、クロックバッファ、および内部ディジタルサンプラを内蔵しています。

このデバイスは、市販の多くのGPSベースバンドICとの接続が可能です。MAX2742は、車載ナビゲーション、テレマティクス、自動セキュリティ、資産管理、位置情報サービス(LBS)、および家庭用電化製品など、多くのアプリケーションに適しています。GPS RFのソリューションのために、デバイスの周りに必要な外付け部品は最小限ですみます。以下の項に、システムのブロック図を掲載いたします。

MAX2742は、18.414MHz*の水晶またはTXCOで動作し、1.023MHzにて差動またはシングルエンド**のIF出力を提供します。信号変換利得の合計は120dBで、ノイズ指数は4.5dBです。IF信号は、18.414MHzのリファレンスクロックレートでサンプリングされます。

詳細については、MAX2742のデータシートを参照してください。

* 注:18.414MHzは、1.023MHz(GPSの基本周波数である10.23MHzの10分の1)の18倍になります。

** 注:3つのIF出力ピンがあります。すなわち1対の差動出力と1つのシングルエンド出力です。ピン10によってこの選択を制御します。

GPS RFフロントエンド部の全体のソリューション

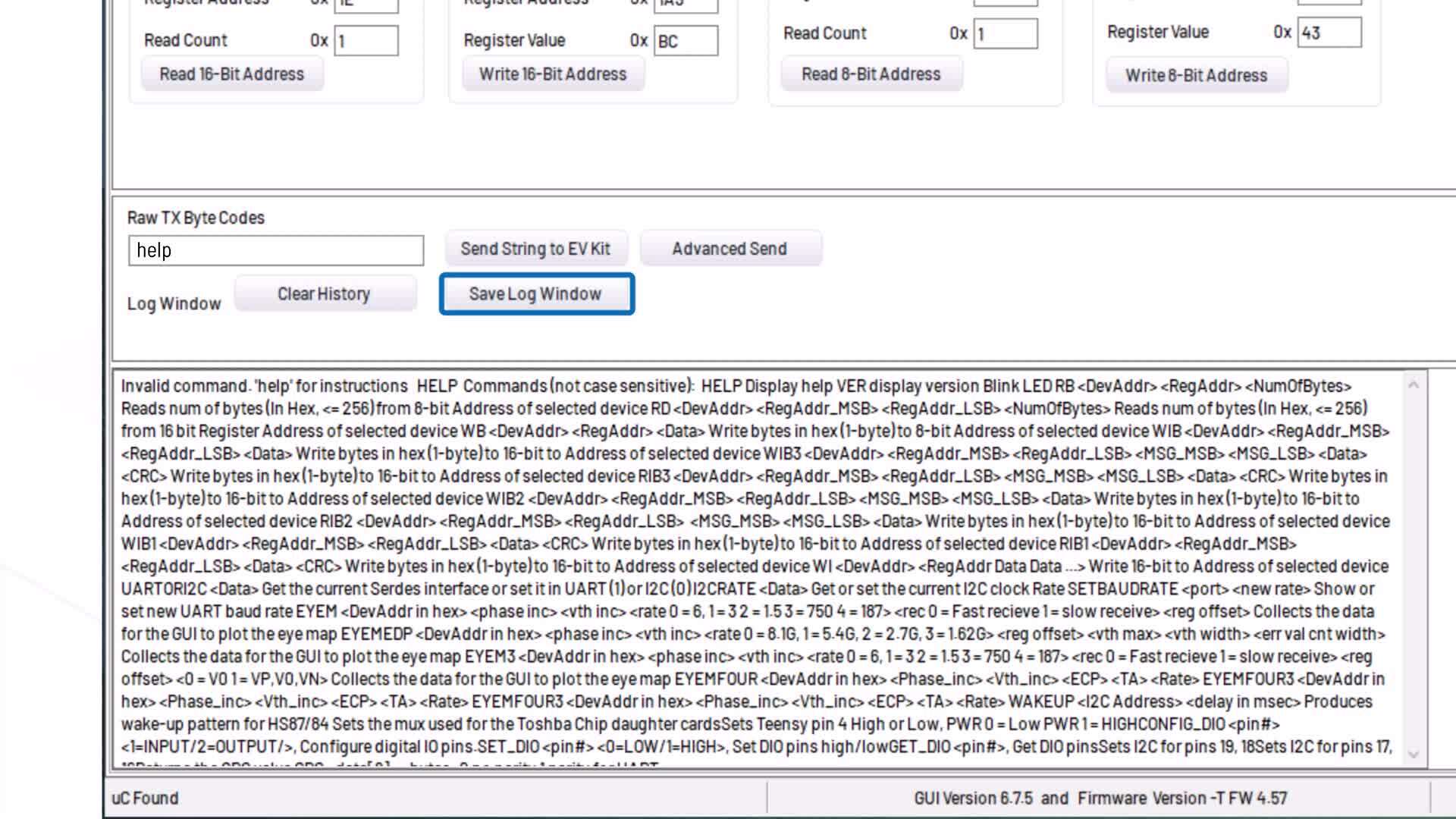

図1は、マキシムのGPS RFソリューション全体の、重要な構成要素と機能を示しています。構成要素の詳細については表1を、カスケード接続したときの性能については表2をご覧ください。図2は、MAX2742を使用したGPSレシーバのRF部分のアプリケーション回路を示しています。

図1. GPS RFフロントエンドのブロックダイアグラム

| Block | Description | Note |

| GPS antenna | Active GPS antenna, commonly has ~1.5dB NF and ~20dB gain | |

| LNA | MAX2641/MAX2654/MAX2655 LNA | External LNA is required when active GPS antenna may not be present. |

| RF SAW | RF bandpass filter centered at 1575.42MHz | RF BPF is required for jammer immunity |

| Power management | MAX8510 low-noise LDO | |

| RF downconverter | MAX2742 | |

| Reference clock | 18.414MHz crystal/TCXO | |

| DSP | Baseband processor |

| Specification | Cascaded Performance | Note |

| Gain | 131dB | Without active antenna, assuming 15dB external LNA gain, 3dB BPF loss, and 1dB matching network loss |

| Noise Figure | 1.9dB | Without active antenna, assuming 1.5dB external LNA NF. |

| Power Consumption | 20mA | MAX2744+MAX2654 as an example |

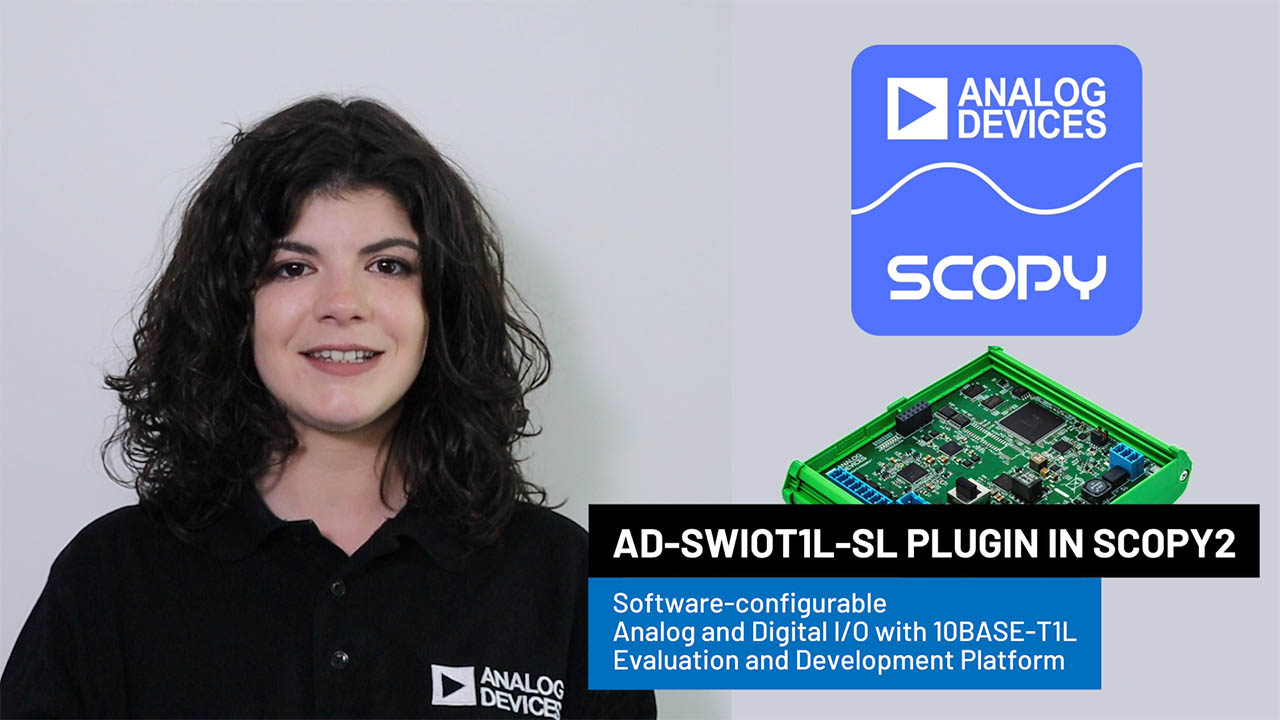

図2. MAX2742用のGPS RF部分の回路図

スタンドアロンGPSレシーバの全体ソリューション

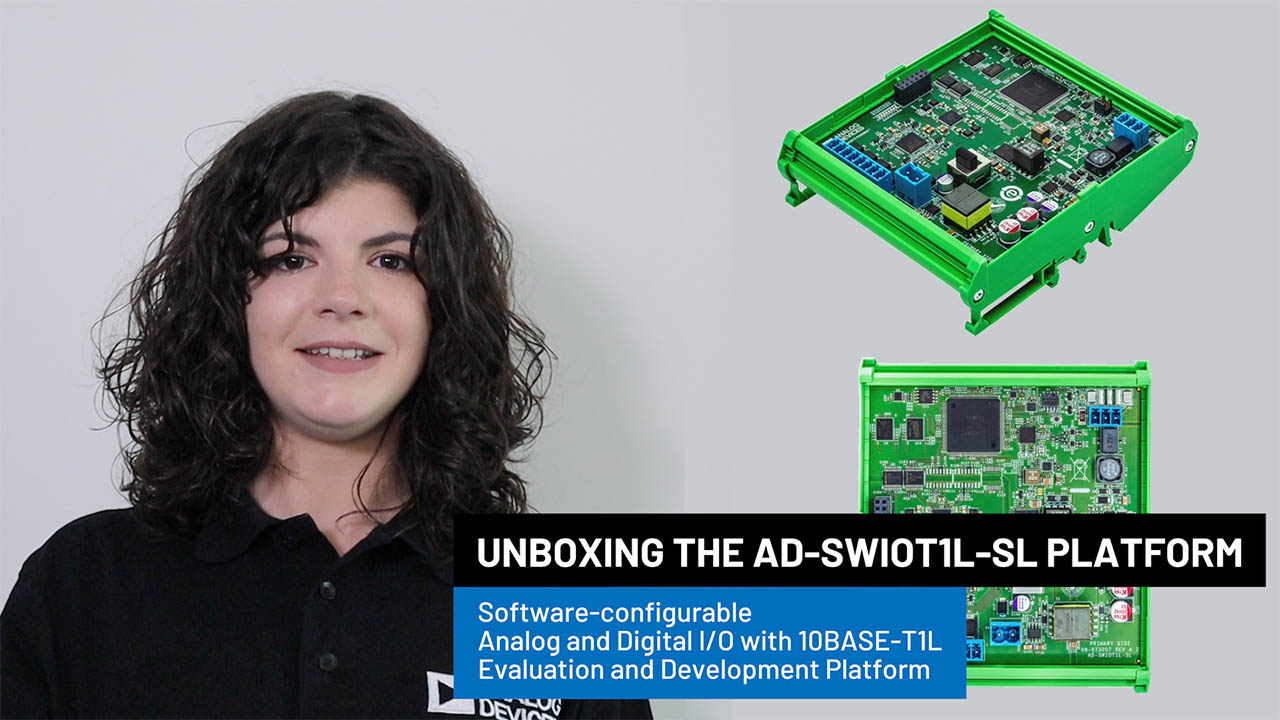

GPSレシーバの全体を構築するには、RFとベースバンドICだけでなく、さらなる構成要素が必要です。図3に示すように、アンテナ供給制御ブロック、RESET回路、および遅延回路が必要となります。構成要素の詳細については表3を、カスケード接続したときの性能については表4>をご覧ください。

図3. GPSレシーバの全体ソリューションのブロックダイアグラム

| Block | Description | Note |

| GPS Antenna | GPS Antenna | Refer to the RF portion for details. |

| LNA | MAX2654 LNA | Refer to the RF portion for details. |

| RF SAW | RF bandpass | Refer to the RF portion for details. |

| Power management | MAX8510 low-noise LDO | |

| RF downconverter | MAX2742 | |

| Reference clock | 18.414MHz TCXO | The TCXO also supplies the baseband clock. In this reference design, GPS clock output from the MAX2742 is not used. |

| GPS baseband | Sony CXD2932 | The CXD2932 also controls active antenna supply, RESET function. See details below. |

| Antenna control block | Antenna supply control with p-MOSFET and current-sense resistor | The sense resistor feeds the antenna supply information back to CXD2932. There are three possible conditions: normal, short, and open. |

| RESET/delay circuitry | Different levels of RESET, and delay circuit required by CXD2932 | To ensure successful startup, CXD2932 requires two RESET signals 100ms apart. |

| Baseband interface | TX: external control command | |

| RX: GPS data out | Data-rate programmable | |

| 1PPS: one pulse-per-second signal | This signal is aligned with GPS atomic clock. |

図4は、リファレンスデザインの実際のPCBレイアウトを示しています。ソリューション全体で、プリント基板スペースの25mm x 25mmを占有するだけです。

図4. GPSレシーバのPCBレイアウト

| Block | Description | Note | Block | Description | Note | Description | Note |

| 1 | Power supply | VCC | (Note 1) | 2.7 ~ 3.6 | T.C. | V | |

| 2 | Current consumption | ICC | VCC = 3.0V | 91 | 88 | mA | |

| 3.1 | Sensitivity | Sens | Acquisition | Tracking | -145 | -145 | dBm |

| 3.2 | -138 | -138 | |||||

| 4 | TTFF | TFC | Cold start | 58 (typ) | 60 (max) | s | |

| 5 | TFW | Warm start | 45 | 30 (max) | s | ||

| 6 | TFH | Hot start | 17 | 6 (max) | s | ||

| 7 | Position drift range | PR | 95% possibility | 100 | 90 | ft | |

| 8 | 1PPS output accuracy | 1PPS | 1 | N.M. | ns | ||

| Note 1: T.C. = test condition, N.M. = not measured. | |||||||

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}