### 概述

MAX16952为电流模式、同步PWM降压控制器,工作在 3.5V至36V输入电压,空载时静态电流仅50µA。开关频率 可通过外部电阻在1MHz至2.2MHz范围内调节,并且可同 步至高达2.4MHz的外部时钟。MAX16952输出电压可通 过引脚选择为固定5V或1V至10V可调。宽输入电压范围, 以及欠压瞬态期间工作在压差模式的能力使器件可理想用 于汽车和工业应用。

MAX16952工作在固定频率PWM模式和低静态电流跳脉 冲模式。器件具有使能逻辑输入,支持高达42V电压,可 禁止器件并将关断电流降低至10µA。保护特性包括限流、 过压,欠压以及带自动恢复功能的热关断保护。器件还具 有电源就绪监测器,方便电源排序。

MAX16952采用热增强、16引脚、TSSOP封装,带裸焊盘,工作在-40°C至+125°C汽车级温度范围。

|     |  | 应用 |

|-----|--|----|

| 汽车  |  |    |

| 工业  |  |    |

| 军品  |  |    |

| 负载点 |  |    |

定购信息

| 器件             | 温度范围         | 引脚-封装        |

|----------------|--------------|--------------|

| MAX16952AUE+   | -40°C至+125°C | 16 TSSOP-EP* |

| MAX16952AUE/V+ | -40°C至+125°C | 16 TSSOP-EP* |

注: 所有器件均可工作在-40℃至+125℃温度范围。 +表示无铅(Pb)/符合RoHS标准的封装。

T = 卷 带 包 装。

特性

- ◆ 3.5V至36V宽输入电压范围

- ◆ 可承受42V输入瞬态电压

- ◆ 瞬间欠压时提供高占空比

- ◆ 1MHz至2.2MHz可调节开关频率

- ◆ 可调节(1V至10V)输出电压, ±2%精度

- ◆ 2.2V至3.6V供电电压

- ◆ 三种工作模式 50µA超低静态电流跳脉冲模式 强制固定频率模式 外部时钟同步

- ◆ 低BOM数量, 电流模式控制架构

- ♦ 电源就绪输出

- ◆ 使能输入支持3.3V逻辑电平至42V电压

- ◆ 限流、热关断和过压保护

- ◆ -40°C至+125°C汽车级温度范围

- ♦ 符合汽车级应用要求

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。如需进一步确认,请在您的设计中参考英文资料。 有关价格、供货及订购信息,请联络Maxim亚洲销售中心: 10800 852 1249 (北中国区),10800 152 1249 (南中国区), 或访问Maxim的中文网站: china.maximintegrated.com。

### **ABSOLUTE MAXIMUM RATINGS**

| SUP and EN to SGND             |                                    |

|--------------------------------|------------------------------------|

| BST to LX                      |                                    |

| BIAS, FB, PGOOD, FSYNC to SGND | -0.3V to +6V                       |

| DH to LX                       | -0.3V to +6V                       |

| DL to PGND                     | 0.3V to (V <sub>BIAS</sub> + 0.3V) |

| FOSC to SGND                   | 0.3V to (VBIAS + 0.3V)             |

| CS and OUT to SGND             | 0.3V to +11V                       |

| PGND to SGND                                          | 0.3V to +0.3V  |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| TSSOP (derate 26.1mW/°C above +70°C)                  | 2088.8mW       |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

TSSOP

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to china.maximintegrated.com/thermal-tutorial.

### **ELECTRICAL CHARACTERISTICS**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu F, C_{OUT} = 94\mu F, C_{BIAS} = 2.2\mu F, C_{BST} = 0.1\mu F, R_{FOSC} = 14.3k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL              | CONDITIONS                                                                                           | MIN   | ТҮР  | MAX   | UNITS |

|------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| SUP Input Voltage Range                  | V <sub>SUP</sub>    | (Note 3)                                                                                             | 3.5   |      | 36    | V     |

| SUP Operating Supply Current             | I <sub>SUP</sub>    | Fixed 5V output, fixed-frequency, PWM mode, $V_{FB} = V_{BIAS}$ , no external FETs connected         |       | 1    |       | mA    |

| Skip Mode Supply Current                 | ISKIP               | No load, fixed 5V output                                                                             |       | 50   | 90    | μA    |

| SUP Shutdown Supply Current              | ISHDN,SUP           | $V_{EN} = 0V$                                                                                        |       | 10   | 20    | μΑ    |

|                                          | Value               | $V_{SUP} = 3.5V, I_{BIAS} = 45mA$                                                                    |       | 3.0  |       | V     |

| BIAS Voltage                             | VBIAS               | $6V < V_{SUP} < 36V$                                                                                 | 4.7   | 5.0  | 5.3   | V     |

| BIAS Undervoltage Lockout                | VUVBIAS             | V <sub>BIAS</sub> rising                                                                             |       | 3.1  | 3.4   | V     |

| BIAS Undervoltage Lockout<br>Hysteresis  |                     | V <sub>BIAS</sub> falling                                                                            |       | 200  |       | mV    |

| BIAS Minimum Load                        | IBIAS(MIN)          | V <sub>SUP</sub> - V <sub>BIAS</sub> > 200mV                                                         |       | 45   |       | mA    |

| OUTPUT VOLTAGE (OUT)                     |                     | •                                                                                                    |       |      |       |       |

| Output Voltage Adjustable<br>Range       |                     |                                                                                                      | 1.0   |      | 10    | V     |

| OUT Pulldown Resistance                  | R <sub>PULL_D</sub> | V <sub>EN</sub> = 0V or fault condition active                                                       |       | 30   |       | Ω     |

| Output Voltage (5V Fixed Mode)           | Vout                | V <sub>SUP</sub> = 6V to 36V, V <sub>FB</sub> = V <sub>BIAS</sub> ,<br>fixed-frequency mode (Note 4) | 4.925 | 5.0  | 5.075 | V     |

| FB Feedback Voltage<br>(Adjustable Mode) | V <sub>FB</sub>     | $V_{SUP} = 6V \text{ to } 36V, 0V < (V_{CS} - V_{OUT}) < 80 \text{mV},$ fixed-frequency mode         | 0.99  | 1.0  | 1.01  | V     |

| FB Current                               | I <sub>FB</sub>     | $V_{FB} = 1.0V$                                                                                      |       | 0.02 |       | μA    |

| FB Line Regulation                       |                     | $V_{EN} = V_{SUP}, 6V < V_{SUP} < 36V$ (Note 4)                                                      |       | 0.02 |       | %N    |

# 36V、2.2MHz降压控制器, 低工作电流

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 14.3$ k $\Omega$ ,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                              | SYMBOL              | CONDITIONS                                                                                | MIN  | ТҮР      | MAX  | UNITS            |

|----------------------------------------|---------------------|-------------------------------------------------------------------------------------------|------|----------|------|------------------|

| Transconductance (from FB to COMP)     | gm,EA               |                                                                                           |      | 1200     |      | μS               |

| Error-Amplifier Output<br>Impedance    | R <sub>OUT,EA</sub> |                                                                                           |      | 30       |      | MΩ               |

| Operating Frequency                    | fsw                 | $R_{FOSC} = 30.1 k\Omega$                                                                 |      | 1000     |      | kHz              |

| Operating Frequency                    | ISW                 | $R_{FOSC} = 14.3 k\Omega$                                                                 | 1800 | 2000     | 2200 |                  |

| Minimum On-Time                        | ton(MIN)            |                                                                                           |      | 80       |      | ns               |

| Maximum FSYNC Frequency                | ffsync(max)         |                                                                                           |      | 2400     |      | kHz              |

| Minimum FSYNC Frequency                | ffsync(MIN)         | $f_{FSYNC} > 110\%$ of internal frequency (20% duty cycle), $f_{SW} = 1000$ kHz           |      | 1100     |      | kHz              |

| FSYNC Logic-High Threshold             | VFSYNC,HI           |                                                                                           | 1.4  |          |      | V                |

| FSYNC Logic-Low Threshold              | VFSYNC,LO           |                                                                                           |      |          | 0.4  | V                |

| FSYNC Internal Pulldown<br>Resistance  |                     |                                                                                           |      | 1        |      | MΩ               |

| CURRENT LIMIT                          | ·                   |                                                                                           |      |          |      |                  |

| CS Input Current                       | ICS                 | V <sub>CS</sub> = V <sub>OUT</sub> = 0V or V <sub>BIAS</sub> (Note 5)                     | -1   |          | +1   | μA               |

| OUT Input Current                      | IOUT                | During normal operation<br>VFB = VBIAS                                                    |      | 22<br>32 |      | μA               |

| CS Current-Limit Voltage<br>Threshold  | VLIMIT              | $V_{CS} - V_{OUT}, V_{BIAS} = 5V, V_{OUT} \ge 2.5V$                                       | 68   | 80       | 92   | mV               |

| FAULT DETECTION                        | •                   |                                                                                           |      |          |      | •                |

| Output Overvoltage Trip<br>Threshold   | V <sub>FB,OV</sub>  | V <sub>OUT</sub> = V <sub>FB</sub> , rising edge                                          | 108  | 113      | 118  | %V <sub>FB</sub> |

| Output Overvoltage Trip<br>Hysteresis  |                     |                                                                                           |      | 2.5      |      | %                |

| Output Overvoltage Fault               |                     | Rising edge                                                                               |      | 25       |      |                  |

| Propagation Delay                      | tovp                | Falling edge                                                                              |      | 25       |      | μs               |

| Output Undervoltage Trip<br>Threshold  | VFB,UV              | V <sub>OUT</sub> = V <sub>FB</sub> ; with respect to slewed FB<br>threshold, falling edge | 83   | 88       | 93   | %V <sub>FB</sub> |

| Output Undervoltage Trip<br>Hysteresis |                     |                                                                                           |      | 2.5      |      | %                |

| Output Undervoltage                    |                     | Falling edge                                                                              |      | 25       |      |                  |

| Propagation Delay                      |                     | Rising edge (excluding startup)                                                           |      | 25       |      | μs               |

| PGOOD Output Low Voltage               | Vpgood,l            | Isink = 3mA                                                                               |      |          | 0.4  | V                |

| PGOOD Leakage Current                  | IPGOOD              |                                                                                           |      | 1        |      | μA               |

| Thermal Shutdown Threshold             | T <sub>SHDN</sub>   | (Note 5)                                                                                  |      | +175     |      | °C               |

| Thermal Shutdown Hysteresis            |                     | (Note 5)                                                                                  |      | 15       |      | °C               |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 14.3$ k $\Omega$ ,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                          | SYMBOL             | CONDITIONS                                                                 | MIN | ТҮР | MAX | UNITS |  |

|------------------------------------|--------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|--|

| GATE DRIVE                         |                    |                                                                            | ·   |     |     | •     |  |

| DH Gate-Driver On-Resistance       | Dett               | (V <sub>BST</sub> - V <sub>LX</sub> ) forced to 5V                         |     | 10  |     | Ω     |  |

|                                    | RDH                | (V <sub>BST</sub> - V <sub>LX</sub> ) forced to 0V                         |     | 2   |     | 52    |  |

| DL Gate-Driver On-Resistance       | Pol                | DL = high state                                                            |     | 3.5 |     | Ω     |  |

|                                    | R <sub>DL</sub>    | DL = low state                                                             |     | 2   |     | 52    |  |

| DH/DL Dood Time (Note 5)           | topup              | DL rising                                                                  |     | 30  |     |       |  |

| DH/DL Dead Time (Note 5)           | <sup>t</sup> DEAD  | DH rising                                                                  |     | 30  |     | ns    |  |

| BST Input Current                  | I <sub>BST</sub>   | $V_{LX} = 0V, V_{BST} = 5V,$<br>$V_{DH} - V_{LX} = V_{DL} - V_{PGND} = 0V$ |     | 1   |     | μA    |  |

| BST On-Resistance                  |                    | (Note 5)                                                                   |     | 5   | 15  | Ω     |  |

| ENABLE INPUT                       | •                  |                                                                            |     |     |     |       |  |

| EN Input Threshold Low             | V <sub>EN,LO</sub> |                                                                            |     |     | 1.2 | V     |  |

| EN Input Threshold High            | V <sub>EN,HI</sub> |                                                                            | 2.2 |     |     | V     |  |

| EN Threshold Voltage<br>Hysteresis |                    |                                                                            |     | 0.2 |     | V     |  |

| EN Input Current                   | I <sub>EN</sub>    |                                                                            |     | 0.5 |     | μA    |  |

| SOFT-START                         |                    |                                                                            | ·   |     |     |       |  |

| Soft-Start Ramp Time               | tss                |                                                                            |     | 5   |     | ms    |  |

**Note 2:** Devices tested at  $T_A = +25^{\circ}C$ . Limits over temperature are guaranteed by design.

Note 3: For 3.5V operation, the n-channel MOSFET's threshold voltage should be compatible to (lower than) this input voltage.

Note 4: Device not in dropout condition.

Note 5: Guaranteed by design; not production tested.

###

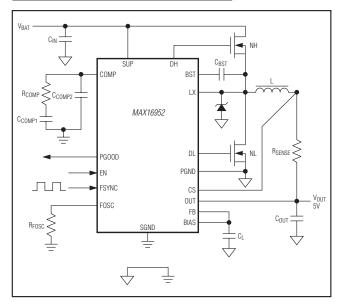

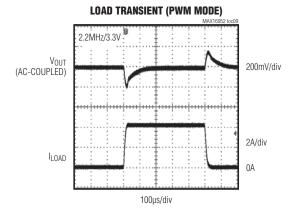

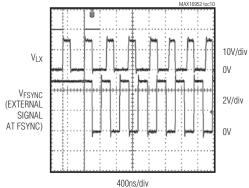

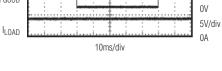

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 47\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 13k\Omega$ ,  $V_{FB} = V_{BIAS}$ ,  $R_{BST} = 75\Omega$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

### 典型工作特性(续)

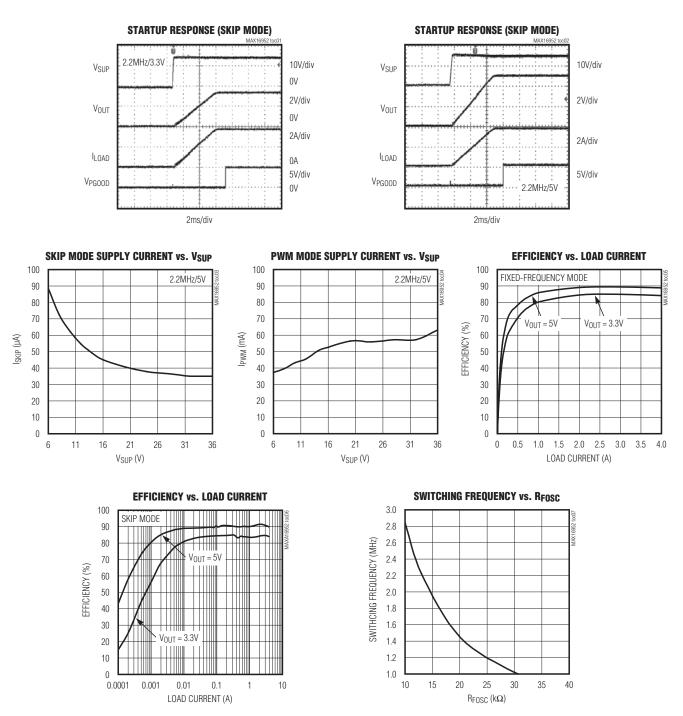

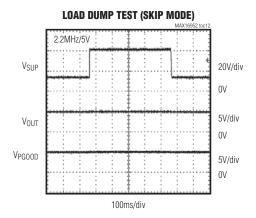

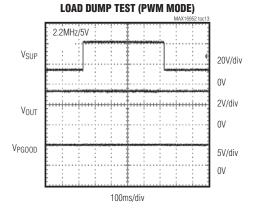

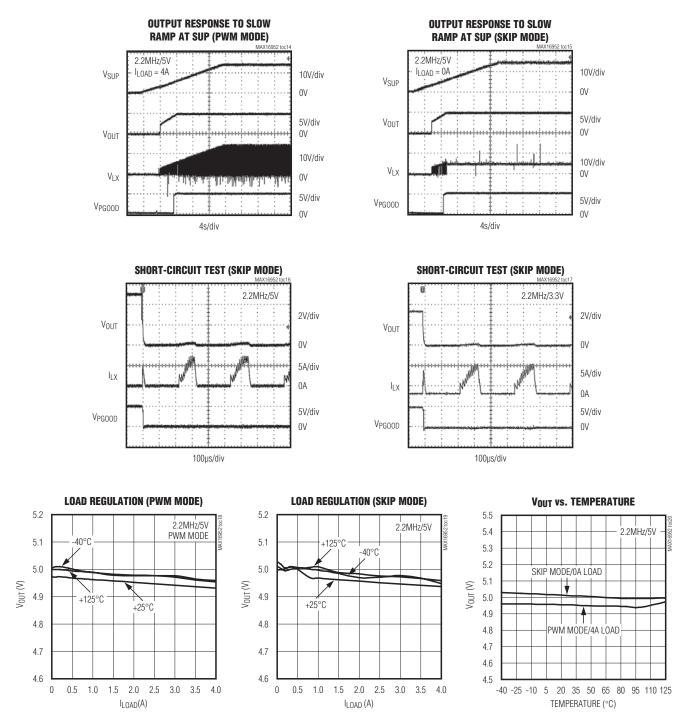

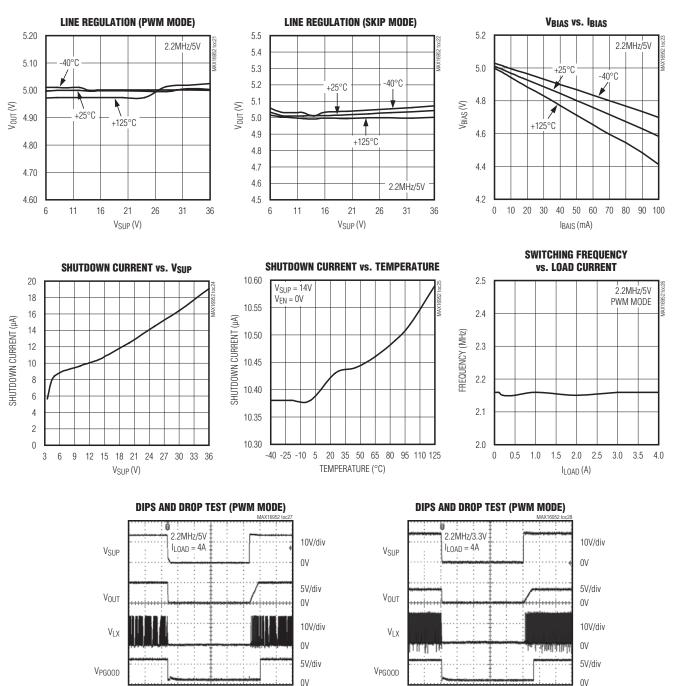

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 47\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 13k\Omega$ ,  $V_{FB} = V_{BIAS}$ ,  $R_{BST} = 75\Omega$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

SYNCHRONIZATION WITH External signal at Fsync

**COLD CRANK TEST (PWM MODE)**

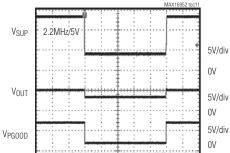

### 典型工作特性(续)

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 47\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 13k\Omega$ ,  $V_{FB} = V_{BIAS}$ ,  $R_{BST} = 75\Omega$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

### 典型工作特性(续)

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 47\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 13k\Omega$ ,  $V_{FB} = V_{BIAS}$ ,  $R_{BST} = 75\Omega$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

10ms/div

10ms/div

# 36V、2.2MHz降压控制器, 低工作电流

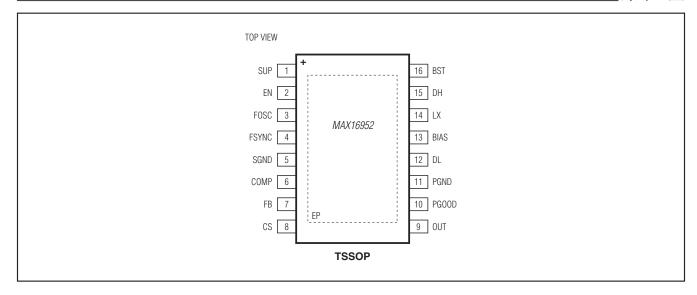

引脚配置

### 引脚说明

| 引脚       | 名称    | 功能                                                                                                                |

|----------|-------|-------------------------------------------------------------------------------------------------------------------|

| 1        | SUP   | 输入电源电压。SUP为内部线性稳压器的输入电压,利用最小1µF陶瓷电容将SUP旁路至PGND。                                                                   |

| 2, 5, 10 | EN    | 高电平有效使能输入。EN支持5V和3.3V逻辑电平。将EN驱动为逻辑高电平时使能输出,将EN驱动为逻<br>辑低电平时,将控制器置于低功耗关断模式。将EN连接至SUP时始终保持就绪状态,不要将EN浮空。             |

| 3        | FOSC  | 振荡器定时电阻输入。在FOSC和SGND之间连接电阻,在1MHz至2.2MHz范围内设置振荡器频率。参见设置开关频率部分。                                                     |

| 4        | FSYNC | 同步和模式选择输入。将FSYNC连接至BIAS时,选择固定频率PWM模式,禁止跳脉冲模式;将FSYNC<br>连接至SGND时,选择跳脉冲模式;将FSYNC连接至外部时钟时为同步。FSYNC通过1MΩ电阻内部下拉<br>至地。 |

| 5        | SGND  | 信号地。将SGND直接连接至本地接地区域。通过单点将SGND连接至PGND。                                                                            |

| 6        | COMP  | 误差放大器输出。将COMP连接至补偿反馈网络。参见补偿设计部分。                                                                                  |

| 7        | FB    | 反馈调节点。将FB连接至BIAS时为固定5V输出电压;可调节模式下,连接至输出(V <sub>OUT</sub> )和SGND之间的<br>电阻分压器的中间抽头以设置输出电压。FB电压稳压至1V(典型值)。           |

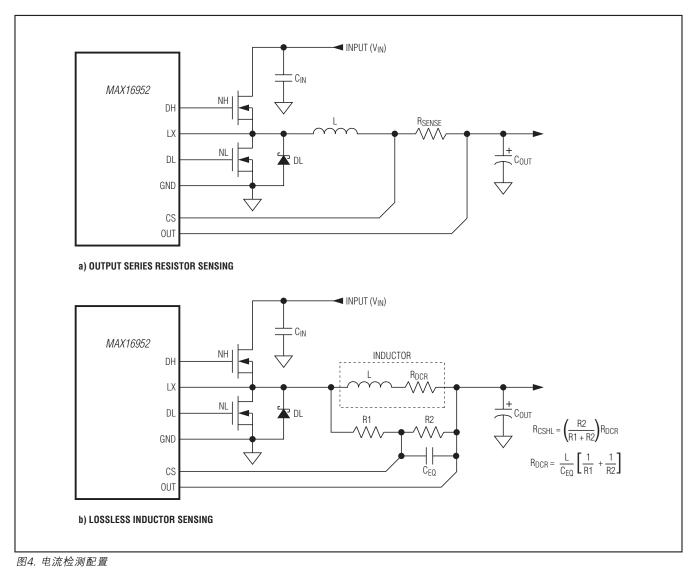

| 8        | CS    | 电流检测输入正端。将CS连接至电流检测元件的正端。图4所示为两种不同的电流检测选项:1)利用检测电阻进行精确检测;或2)无损耗电感DCR检测。                                           |

### \_引脚说明(续)

| 引脚 | 名称    | 功能                                                                                     |

|----|-------|----------------------------------------------------------------------------------------|

| 9  | OUT   | 输出检测和负的电流检测输入。使用内部预设5V反馈分压器(FB = BIAS)时,控制器利用OUT检测输出电压。将OUT连接至电流检测元件的负端。               |

| 10 | PGOOD | 电源就绪开漏输出。PGOOD为逻辑高电压时,表示输出电压在调节范围之内;输出电压超出调节范围时,<br>PGOOD拉低。在PGOOD和数字接口电压之间连接10kΩ上拉电阻。 |

| 11 | PGND  | 电源地。将输入和输出滤波电容的负端连接至PGND。在外部通过单点将PGND连接至SGND。                                          |

| 12 | DL    | 低边栅极驱动器输出。DL从VBIAS至PGND摆动。如果DL和MOSFET的栅极之间需要电阻,请向工厂咨<br>询最佳电阻值。                        |

| 13 | BIAS  | 内部5V线性稳压器输出。BIAS为偏置和驱动供电。在BIAS和PGND之间连接2.2µF至10µF的陶瓷电容。                                |

| 14 | LX    | 外部电感连接。将LX连接至电感的开关侧。LX作为DH高边栅极驱动器的低电源轨。                                                |

| 15 | DH    | 高边栅极驱动输出。DH从LX至BST摆动。如果DH和MOSFET的栅极之间需要电阻,请向工厂咨询最佳<br>电阻值。                             |

| 16 | BST   | 升压飞电容连接。在BST和LX之间连接陶瓷电容。详细信息请参见升压飞电容选择部分。                                              |

| _  | EP    | 裸焊盘,内部连接至地。将EP连接至电势为SGND的连续大覆铜区域以提高散热性能。请勿将其用作主<br>接地连接。                               |

# 36V、2.2MHz降压控制器, 低工作电流

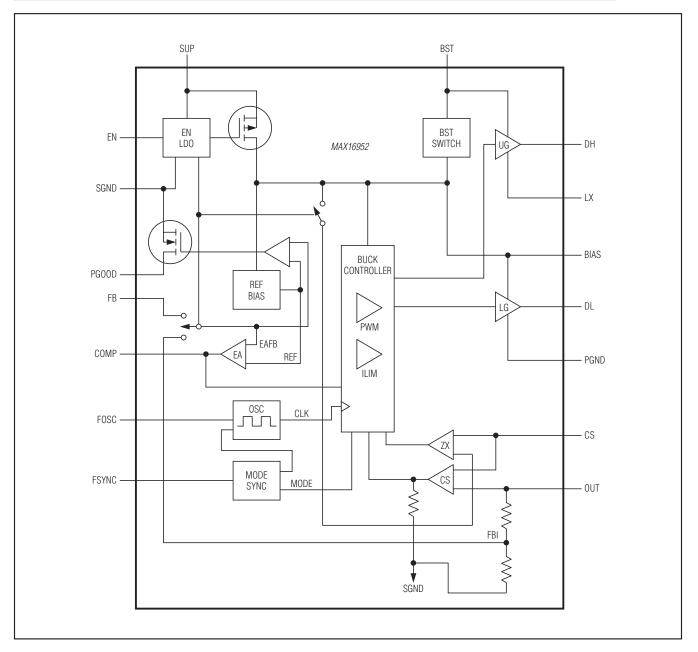

功能框图

### 详细说明

MAX16952为电流模式、同步PWM降压控制器,设计用 于驱动逻辑电平MOSFET。器件支持3.5V至42V输入电压 范围,产生1V至10V可调电压或固定5V输出电压。器件可 工作在压差模式,理想用于具有瞬间电压跌落的汽车和工 业应用。

开关频率可通过外部电阻在1MHz至2.2MHz范围内调节, 并且可同步至外部时钟。高开关频率降低输出纹波,允许 使用小外部元件。器件工作在固定频率PWM模式和低静 态电流跳脉冲模式。工作在跳脉冲模式时,工作电流低至 50μA。

器件具有使能逻辑输入,可禁止器件并将关断电流降低至 10µA。保护特性包括逐周期限流、过压检测和热关断保护。 器件也集成了软启动和电源就绪监测器,有助于电源排序。

### 供电范围(SUP)

MAX16952的供电范围(V<sub>SUP</sub>)兼容3.5V至36V的典型汽车 电池电压范围,支持高达42V瞬态电压。

#### 输入电压低速缓升

如果输入电压(V<sub>SUP</sub>)爬升很慢,器件将工作在压差模式, 直至V<sub>SUP</sub>高于稳压输出电压。通过监测高边FET导通8个 时钟周期,检测压差模式。检测到压差模式后,控制器在 开关时钟的上升沿发送一个强制低边脉冲,刷新BST电容。 这样可维持正确的BST电压,以在器件处于压差模式时导 通高边MOSFET。

### 系统使能(EN)和软启动

使能控制输入(EN)将MAX16952从其低功耗关断模式中激活。EN支持低至3.5V的汽车电池电平输入。高压兼容性允许EN连接至SUP、KEY/KL30或CAN收发器的抑制引脚(INH)。

EN逻辑高电平将开启内部稳压器。当V<sub>BIAS</sub>高于内部锁定 电平V<sub>UVL</sub> = 3.1V (典型值)时,控制器以5ms固定软启动 时间进行启动。达到稳压电压时,PGOOD变为高阻。 EN逻辑低电平将关断器件。关断期间,内部线性稳压器 和栅极驱动器关闭。关断为最低功耗状态,将静态电流降 低至10μA (典型值)。

关断期间,为保护低边MOSFET,在输出电压下降至1.25V 以下之前不使能降压型调节器。内部30Ω下拉开关帮助对 输出进行放电。如果EN引脚变为低电平后又变为高电平, 开关稳压器关断,并在输出电压下降至1.25V之前保持关 断。此时,MAX16952采用软启动顺序打开。

### 固定5V线性稳压器(BIAS)

MAX16952内置5V线性稳压器,利用SUP上的高压输入电 源产生5V偏置电压。该偏压为外部n沟道MOSFET的栅极 驱动器供电,提供模拟控制器、基准和逻辑电路所需的电 源。该偏置电压轨需要用BIAS上2.2μF或更大的电容进行 稳压,可提供高达45mA (典型值)总电流。

线性稳压器的过流门限约为100mA。发生过流事件时, 将电流限制至100mA,BIAS电压开始下降。V<sub>BIAS</sub>下降至 2.9V (典型值)时,降压转换器关断,功率MOSFET关闭。

### 振荡器频率和外同步

MAX16952提供从1MHz至2.2MHz可调节的内部振荡器。 在FOSC和SGND之间连接电阻,可设置开关频率。参见 *设置开关频率*部分。

将外部时钟信号连接至FSYNC时,MAX16952也可同步至 外部时钟。为保证频率同步,FSYNC的输入频率必须至少 比设置的内部振荡器频率高10%。FSYNC上的时钟上升 沿作为同步输入。如果FSYNC信号丢失,内部振荡器负责 控制开关速率,恢复为FOSC上电阻设置的开关频率。这 样即使FSYNC信号发生间歇性中断时也可保证输出在稳 压范围内。最大可同步频率为2.4MHz。

将FSYNC连接至SGND时,器件工作在跳脉冲模式;将 FSYNC连接至BIAS或由外部时钟驱动时,MAX16952在 软启动期间工作在跳脉冲模式,在软启动结束后变为固定 频率PWM模式。

## 36V、2.2MHz降压控制器, 低工作电流

检错和故障操作

有多种检错机制防止损坏MAX16952和应用电路:

- 过流保护

- 输出过压保护

- BIAS上欠压锁定

- 输出电压电源就续检测

- IC过热保护

#### 过流保护

MAX16952在FB电压大于0.7V(即稳压输出电压的70%) 时提供逐周期限流。如果输出电压由于过流事件下降至稳 压点的70%以下,16个连续限流事件将触发重启。如果 重启后仍然发生过流,MAX16952则关断,然后再次重启。 器件将持续自动重启过程,直到过流条件消除。如果重启 期间过流条件消失,器件则进入正常软启动程序。

如果输出通过长导线短路,输出电压会在达到过流门限之前下降到地电平以下,这种条件下,MAX16952在输出下降稳压值的20%时,则立即断开开关并进行重启。

#### 输出过压保护

MAX16952内置输出过压保护功能。如果V<sub>OUT</sub>升高到比 稳压值高出13% (典型值)时,高边MOSFET关断,低边 MOSFET导通。低边MOSFET在V<sub>OUT</sub>恢复到稳压范围之 前保持导通。V<sub>OUT</sub>处于规定范围之内时,保持正常开关 操作。

欠压锁定(UVLO) 如果5V偏置电源(BIAS)低于3.1V(典型值)UVLO门限,BIAS 输入欠压锁定(UVLO)电路断开开关。如果BIAS电压下降至 UVLO门限以下,控制器断开开关并关断高边、低边栅极驱 动器,直至BIAS电压恢复。

#### 电源就绪检测(PGOOD)

MAX16952包括带有滞回的电源就绪比较器,以监测降 压控制器的输出电压以及检测电压就绪门限。PGOOD为 开漏输出,应利用外部电阻上拉到其驱动逻辑输入电源, 该电压不应超过6V。10kΩ上拉电阻适用于大多数应用。 PGOOD为低电平时可吸入高达3mA电流。 PGOOD在以下条件时变为有效:

- 待机模式

- 欠压, VOUT低于设置值的88% (典型值)

- 过压, VOUT高于设置值的113% (典型值)

如果使用反馈分压器,在FB测量电源就绪电平。如果 MAX16952工作在5V模式,FB连接至BIAS,则利用OUT 作为电压调节和电源就绪检测的反馈通路。

#### 过热保护

热过载保护限制MAX16952内的总功耗。结温超过+175°C (典型值)时,内部温度传感器关断降压控制器,允许IC冷却。 结温冷却15°C以及输出电压下降至1.25V (典型值)以下后, 温度传感器再次打开IC。

连续过热条件会导致器件重复开/关操作。

### 固定频率、电流模式PWM控制器

MAX16952的降压控制器采用PWM、电流模式控制机制。 内部跨导放大器产生积分误差电压。PWM控制器的核心 是一个开关比较器,该比较器将积分电压反馈信号与放大 的电流检测信号加斜率补偿进行比较;在主PWM比较器 中加斜率补偿的目的是保证内环路稳定性以及消除电感阶 梯效应。在每个内部时钟下降沿,高边MOSFET导通,直 至PWM比较器触发、达到最大占空比或达到峰值电流限 值。在此导通期间,电流通过电感缓升,在其磁场中储存 能量并源出电流至输出。电流模式反馈系统调节峰值电感 电流,电流是输出电压误差信号的函数。该电路作为开关 模式跨导放大器,消除输出LC滤波器双极点的影响。

在开关周期的后半部分,高边MOSFET关断,低边MOSFET 导通。电流缓降时,电感释放储存的能量,为输出提供电 流。输出电容在电感电流超过所需的负载电流时储存电荷, 电感电流较低时放电,稳定负载上的电压。轻过载条件下, 当峰值电感电流超过所选电流限值时,高边MOSFET立即 关断;低边MOSFET导通,使电感电流缓降,直至下一个 时钟周期。

#### 强制固定频率PWM模式

低噪声强制固定频率PWM模式(FSYNC连接至BIAS或外部时钟),禁止控制低边开关导通时间的过零比较器。这样强制低边栅极驱动器波形总是与高边栅极驱动器的波形反相。轻载时,电感电流反向,DH的占空比维持为V<sub>OUT</sub>/V<sub>SUP</sub>。

强制固定频率PWM模式的好处是保证开关频率恒定。然而,强制固定频率PWM工作具有缺点: 空载5V供电电流 会高达45mA,取决于外部MOSFET和开关频率。强制固 定频率PWM模式最有利于避免音频噪声以及提高负载瞬 态响应。

#### 轻载低静态电流工作模式(跳脉冲)

MAX16952具有一个轻载工作模式控制输入(FSYNC = SGND),用于使能或禁止过零比较器。使能过零比较器时,稳压器在电流检测输入检测到电感电流为零时强制DL为低电平。这样防止电感对输出电容放电,并强制稳压器在轻载条件下产生跳脉冲,避免输出过充。

跳脉冲模式下工作电流最低。MAX16952工作在无外部负载电流的跳脉冲模式时,总耗流可低至50µA。跳脉冲模式的缺点是工作频率不固定。

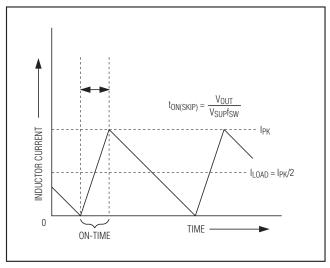

### 跳脉冲模式电流检测门限

使能跳脉冲模式时,当输出电压超过反馈门限时以及电流 检测电压超过空闲模式电流检测门限(V<sub>CS,IDLE</sub>)时,降压控 制器的导通周期结束。请参见图1。轻载条件下,导通周 期的持续时间只与跳脉冲模式电流检测门限有关,检测门 限为25mV (典型值)。这强制控制器在每周期源出最小的 功率。为避免输出过充,在输出电压下降至反馈门限时, 才开始另一个导通周期。由于过零比较器防止开关稳压器 吸入电流,所以控制器必须跳脉冲。因此,在轻载条件下, 控制器调节输出纹波的谷值。

#### 跳脉冲模式自动切换

跳脉冲模式下,轻载时会自动切换至脉冲频率调制(PFM) 模式。这种切换受控于比较器,该比较器在电感电流过零 时终止低边开关导通时间。过零比较器检测CS至OUT的 电感电流,一旦(V<sub>CS</sub> - V<sub>OUT</sub>)下降至6mV过零电流检测门 限以下,比较器强制拉低DL。这种机制使跳脉冲PFM和 非跳脉冲PWM工作模式之间的门限与连续和非连续电感 电流工作模式之间的分界点(也称为临界传导点)相一致。 PFM/PWM转折点的负载电流I<sub>LOAD(SKIP</sub>)计算如下:

$$LOAD(SKIP)[A] = \frac{(V_{SUP} - V_{OUT})V_{OUT}}{2 \times V_{SUP} \times f_{SW}[MHz] \times L[\mu H]}$$

轻载导致跳脉冲工作模式时,开关波形中可能出现噪声和 异步,但这是获得高轻载效率的正常工作条件。通过改变 电感值,可在PFM噪声和轻载效率之间取得平衡。通常来 讲,电感值较低时,效率-负载曲线上高效率的平坦区域 更为宽阔;而较高的电感值会得到更高的满载效率(假定 线圈电阻保持不变)和更小的输出电压纹波。使用较高电 感值会增大物理尺寸,降低负载瞬态响应(在低输入电压 时更为显著)。

#### MOSFET栅极驱动器(DH和DL)

DH和DL驱动器针对驱动逻辑电平n沟道功率MOSFET进 行了优化。DH高边n沟道MOSFET驱动器由BST上的电荷 泵供电,DL同步整流器驱动器由5V线性稳压器(BIAS)直 接供电。自适应死区时间电路监测DH和DL输出,防止另 一侧的MOSFET在另一个MOSFET完全关断前导通。所 以,该电路允许高边驱动器只在DL栅极驱动器关闭时导 通,同样防止低边(DL)在DH栅极驱动器关闭之前导通。

## 36V、2.2MHz降压控制器, 低工作电流

图1. 跳脉冲/非连续转折点

自适应驱动器死区时间允许利用各种MOSFET进行无贯通 工作,延迟最小并保证效率。DL和DH驱动器至MOSFET 栅极必须具有低电阻、低电感通路,使自适应死区电路 正常工作。否则,由于栅极放电通路中的杂散阻抗,当 MOSFET的V<sub>GS</sub>仍然为高电平时,检测电路会将MOSFET 栅极电压理解为关闭。为将杂散阻抗降至最低,使用非常 短而宽的走线(如果MOSFET距离控制器1 in,使用50 mil 至100 mil宽)。

同步整流通过利用低电阻MOSFET开关代替常规的低边 肖特基环流二极管,减小传导损耗。驱动DL为低电平的 内部下拉晶体管很可靠,导通电阻为2 $\Omega$ (典型值),可防 止在LX节点的快速上升沿时由于低边同步整流MOSFET 的漏极-栅极容性耦合导致DL被上拉。应用中,如果输 入电压较高,驱动器具有较长感性走线,可能需要额外 的栅极-源极电容,以确保LX的快速上升沿不会上拉低边 MOSFET的栅极而导致贯通电流。由MOSFET的栅极-漏 极电容(C<sub>GD</sub> = C<sub>RSS</sub>)、栅极-源极电容(C<sub>GS</sub> = C<sub>ISS</sub> - C<sub>GD</sub>) 以及电路板附加寄生电容引起的LX和DL之间的容性耦合 不能超过以下的最小门限:

$$V_{GS(TH)} > V_{SUP} \left( \frac{C_{RSS}}{C_{ISS}} \right)$$

### 高边栅极驱动电源(BST)

通过闭合BST和DH之间的内部开关,导通高边MOSFET, 这提供了导通高边MOSFET所必需的栅极-源极电压,将 栅极驱动信号提高至V<sub>SUP</sub>以上。高边MOSFET导通周期 内,BST和LX之间连接的升压电容保持栅极驱动器上的电 压。

高边MOSFET关断以及LX节点下降至地时,升压电容被 充电以补充驱动栅极而释放的电荷。LX节点为低电平时, BIAS和BST之间连接的内部高压开关将升压电容重新充电 至BIAS电压。关于选择正确大小升压电容的信息,请参 见升压飞电容选择部分。

#### 发生瞬间欠压时的工作状态

在低压工作期间,控制器每八个时钟周期产生一个低边脉冲,以刷新BST电容。这保证MAX16952在冷启动等瞬间 欠压时能够工作在低压差模式,更多详细信息请参见升压 飞电容选择部分。

### 限流和电流检测输入(CS和OUT)

限流电路利用差分电流检测输入(CS和OUT)限制峰值电感 电流。如果电流检测信号的幅值超过限流门限,PWM控 制器则关断高边MOSFET。实际最大负载电流比峰值限流 门限小电感纹波电流的一半。因此,最大负载电流是电流 检测电阻、电感值、开关频率和占空比(Vour/VsuP)的函数。 请参见电流检测部分。

### 设计步骤

### 有效输入电压范围

尽管MAX16952控制器可工作在从输入电源至高达42V的 范围内以及稳压低至1V,最小电压转换比(V<sub>OUT</sub>/V<sub>SUP</sub>)可 能受限于最小可控导通周期。为了正确工作在固定频率 PWM模式,电压转换比应遵循以下条件:

$$\frac{V_{OUT}}{V_{SUP}} > t_{ON(MIN)} \times f_{SW}$$

式中,t<sub>ON(MIN)</sub>为80ns;f<sub>SW</sub>为开关频率,单位为Hz。如 果希望的电压转换率不满足以上条件,会发生跳脉冲,以 降低有效占空比。为避免这种情况,降低开关频率或减小 输入电压(V<sub>SUP</sub>)。

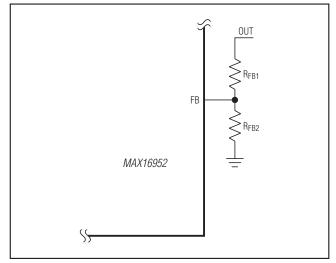

### 设置输出电压

将FB连接至BIAS时,使能固定降压控制器输出电压(5V), 电压由输出(OUT)和SGND之间连接的预设内部电阻分压 器设置。

为达到1V至10V之间的其它电压,在OUT至FB、SGND之间连接电阻分压器(图2)。选择R<sub>FB2</sub> (FB至SGND之间的电阻)小于或等于100kΩ。利用下式计算R<sub>FB1</sub> (OUT至FB之间的电阻):

$$R_{FB1} = R_{FB2} \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$$

式中,V<sub>FB</sub> = 1V (典型值)(见*Electrical Characteristics表*), V<sub>OUT</sub>可为1V至10V。

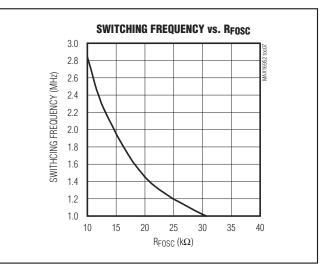

选择开关频率

开关频率f<sub>SW</sub>由FOSC与SGND之间的电阻(R<sub>FOSC</sub>)设置。 参见图3根据预期开关频率选择正确的R<sub>FOSC</sub>值。

例如, R<sub>FOSC</sub> = 14.3kΩ时,设置的开关频率为2MHz。较 高的频率允许设计时使用较小的电感值和较小的输出电 容。所以,开关频率较高时,峰值电流和I<sup>2</sup>R损耗较低, 但磁芯损耗、栅极充电电流和开关损耗增大。

电感选择

为配合MAX16952正常工作,必须限定电感的三个关键 参数:电感值(L)、电感饱和电流(ISAT)和直流电阻(RDCR)。 为选择电感值,必须首先选择电感的峰-峰交流电流与直 流平均电流(LIR)之比。尺寸和损耗之间的良好平衡使峰-峰纹波电流与平均电流比为30% (LIR = 0.3)。开关频率、 输入电压、输出电压及所选的LIR决定电感值,关系如下:

$$L = \frac{V_{OUT} \left( V_{SUP(MIN)} - V_{OUT} \right)}{V_{SUP(MIN)} \times f_{SW} \times I_{OUT(MAX)} \times LIR}$$

式中,V<sub>SUP(MIN)</sub>为最小供电电压,V<sub>OUT</sub>为典型输出电压, I<sub>OUT(MAX)</sub>为最大负载电流。开关频率由R<sub>FOSC</sub>设置(见*设置 开关频率*部分)。MAX16952使用与内部频率无关的斜率 补偿,以确保占空比高于50%时稳定工作。利用下式选择 电感值:

$\frac{V_{OUT}[V]}{L[\mu H] \times f_{SW}[MHz]} = 1 \pm 25\%$

图2. 可调输出电压

图3. 开关频率与RFOSC的关系

## 36V、2.2MHz降压控制器, 低工作电流

然而,如果需要,可选择较高的电感值。

准确的电感值不是特别关键,可根据大小、成本、效率及 瞬态响应要求进行调整。表1所示为大电感和小电感之间 的比较。

### 表1. 电感比较

| INDUCTOR SIZE        |                                           |  |  |  |  |

|----------------------|-------------------------------------------|--|--|--|--|

| SMALLER              | LARGER                                    |  |  |  |  |

| Lower price          | Smaller ripple                            |  |  |  |  |

| Smaller form factor  | Higher efficiency                         |  |  |  |  |

| Faster load response | Larger fixed-frequency range in skip mode |  |  |  |  |

实用的最小电感值应使电路工作在临界导通状态(最大负载时,电感电流在每个周期恰好归零)的电感值。电感值低于该最小值将无益于进一步减小尺寸。最佳工作点通常位于25%至45%纹波电流之间。跳脉冲模式下(FSYNC为低电平,轻载),电感值也决定PFM/PWM切换时的负载电流值。

选定电感值时,电感纹波电流的实际峰-峰值( $\Delta I_{INDUCTOR}$ ) 由下式决定:

$$\Delta I_{\text{INDUCTOR}} = \frac{V_{\text{OUT}} \left( V_{\text{SUP}} - V_{\text{OUT}} \right)}{V_{\text{SUP}} \times f_{\text{SW}} \times L}$$

式中, Al<sub>INDUCTOR</sub>的单位为mA, L的单位为µH, f<sub>SW</sub>的单位为kHz。

磁芯必须足够大,以确保在电感电流峰值(IPEAK)时不饱和:

$$l_{\text{PEAK}} = l_{\text{LOAD}(\text{MAX})} + \frac{\Delta l_{\text{INDUCTOR}}}{2}$$

瞬态响应

电感纹波电流对瞬态响应性能也有影响,尤其是V<sub>SUP</sub>-V<sub>OUT</sub>差值较小时。低电感值允许电感电流更快地摆动, 以补充负载突变时从输出滤波电容上释放的电荷。输出电 压的总下跌量包括两部分,一部分是电感电流上升期间的 下跌,另一部分是下一脉冲之前的下跌:

$$V_{SAG} = \frac{L(\Delta I_{LOAD(MAX)})^{2}}{2C_{OUT}((V_{SUP} \times D_{MAX}) - V_{OUT})} + \frac{\Delta I_{LOAD(MAX)}(t - \Delta t)}{C_{OUT}}$$

式中,DMAX是最大占空比(见*Electrical Characteristics* 表);L是电感值(单位为 $\mu$ H);C<sub>OUT</sub>是输出电容值(单位为  $\mu$ F);t是开关周期(1/f<sub>SW</sub>,单位为 $\mu$ s); $\Delta$ t在固定频率PWM 模式下等于(V<sub>OUT</sub>/V<sub>SUP</sub>)×t,在跳脉冲模式下等于L×0.2 ×I<sub>MAX</sub>/(V<sub>SUP</sub> - V<sub>OUT</sub>)。在满载向空载瞬变期间,由于电感 值储能引起的过冲电压(V<sub>SOAR</sub>)可由下式计算:

$$V_{\text{SOAR}} \approx \frac{\left(\Delta I_{\text{LOAD}(\text{MAX})}\right)^2 L}{2C_{\text{OUT}} V_{\text{OUT}}}$$

电流检测

为获得最高精度的电流检测,在电感和输出电容之间使用 电流检测电阻(R<sub>SENSE</sub>)。将CS连接至R<sub>SENSE</sub>的电感侧,将 OUT连接至电容侧。选择R<sub>SENSE</sub>的大小,使其最大电流 (I<sub>OC</sub>)在R<sub>SENSE</sub>上产生的电压为V<sub>LIMIT</sub> (最小68mV)。

如果R<sub>SENSE</sub>上必须具有较高的电压降,利用CS和OUT之间的分压器对检测电阻上的电压进行分压,使其达到 V<sub>LIMIT</sub> (最小68mV)。

电流检测方法(图4)及幅值决定可达到的电流限值精度和功 率损耗。一般而言,较高的电流检测限值具有较高的精度, 但是功率损耗也更大。为获得最佳电流检测精度和过流保 护,在电感和输出之间使用具有低寄生电感、±1%容限 的电流检测电阻,如图4a所示。

对于限流保护精度要求不高的应用,也可通过与电感并联 (图4b)具有等效时间常数的RC电路,降低总体功耗:

$$R_{CSHL} = \left(\frac{R_2}{R1+R2}\right) R_{DCR}$$

及:

$$R_{\text{DCR}} = \frac{L}{C_{\text{EQ}}} \left( \frac{1}{\text{R1}} + \frac{1}{\text{R2}} \right)$$

式中,R<sub>CSHL</sub>为所需的电流检测电阻,R<sub>DCR</sub>为电感的直流 串联电阻。使用电感制造商提供的典型电感和R<sub>DCR</sub>值。 严格遵守PCB布局指导,确保噪声和直流误差不会影响CS和OUT上的差分电流检测信号。利用短而直的走线将检测 电阻布置在靠近IC的位置,利用开尔文检流方式连接到检流电阻。

## 36V、2.2MHz降压控制器, 低工作电流

输入电容

输入滤波电容降低来自于电源的尖峰电流,减小电流开关 引起的输入噪声和电压纹波。

输入电容的RMS电流要求(I<sub>RMS</sub>)由下式定义:

$$I_{\rm RMS} = I_{\rm LOAD(MAX)} \frac{\sqrt{V_{\rm OUT} (V_{\rm SUP} - V_{\rm OUT})}}{V_{\rm SUP}}$$

输入电压等于输出电压的2倍时(V<sub>SUP</sub> = 2V<sub>OUT</sub>), I<sub>RMS</sub>的 值最大,所以I<sub>RMS(MAX)</sub> = I<sub>LOAD(MAX)/2</sub>。

所选电容在RMS输入电流时的自热温升低于+10℃,以实现最优的长期稳定性。

输入电压纹波由ΔV<sub>Q</sub>(由电容放电引起)和ΔV<sub>ESR</sub> (由电容的 ESR引起)组成。在输入上使用低ESR、高纹波电流的陶瓷 电容。假设ESR和电容放电引起的纹波为50%。利用下式 计算规定输入电压纹波时的输入电容和ESR要求:

$$\text{ESR}_{\text{IN}} = \frac{\Delta V_{\text{ESR}}}{I_{\text{OUT}} + \frac{\Delta I_{\text{L}}}{2}}$$

式中:

$$\Delta I_{L} = \frac{\left(V_{SUP} - V_{OUT}\right) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

及:

$$C_{IN} = \frac{I_{OUT} \times D(1-D)}{\Delta V_Q \times f_{SW}}$$

式中:

$$D = \frac{V_{OUT}}{V_{SUP}}$$

#### 输出电容

输出滤波电容的ESR一方面应足够低,以满足输出纹波以 及负载瞬态要求,另一方面也不能太低,以满足稳定性要 求。输出电容值必须足够大,当发生从满载到空载的瞬变 时应当能够吸收电感能量,而不会触发过压故障保护。使 用大容量、低ESR的电容时,滤波电容的ESR对于输出电 压纹波起决定作用。因此输出电容的大小取决于满足输出 电压纹波(V<sub>RIPPLE(P-P)</sub>)要求所需的最大ESR:

#### $V_{RIPPLE(P-P)} = ESR \times I_{LOAD(MAX)} \times LIR$

跳脉冲模式下,电感电流不连续,其峰值电流取决于跳脉 冲模式下的电流检测门限(V<sub>SKIP</sub> = 32mV,典型值)。跳脉 冲模式下,空载输出纹波的计算公式如下:

$$V_{\text{RIPPLE}(P-P)} = \frac{V_{\text{SKIP}} \times \text{ESF}}{R_{\text{SENSE}}}$$

实际所需电容值与满足低ESR要求所需的物理尺寸有关, 还与电容器的工艺有关。因此,选择电容器时通常首先考 虑其ESR和额定电压,然后再选择电容值。

当使用容值较小的滤波电容时,例如陶瓷电容,其尺寸通 常应以保证在负载瞬变期间V<sub>SAG</sub>和V<sub>SOAR</sub>不超标为准。通 常来讲,只要电容值大到足以满足过冲要求,上升负载 沿引起的下冲也不会有问题(见*瞬态响应*部分中的V<sub>SAG</sub>和 V<sub>SOAR</sub>公式)。然而,低容量滤波电容的ESR零点通常较高, 可能会影响总体稳定性。

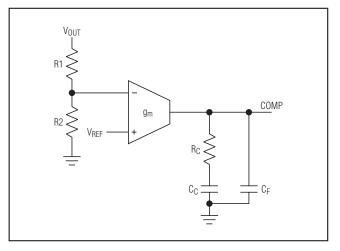

补偿设计

MAX16952采用内部跨导误差放大器,其反相输入及其输 出可供用户进行外部频率补偿。输出电容和补偿网络决定 环路稳定性。综合考虑性能、尺寸和成本来选择电感和输 出电容。此外,补偿网络优化控制环路稳定性。

控制器采用电流模式控制机制,通过限制流经外部电感的 电流调节输出电压。MAX16952利用电感的直流电阻或串 联的检流电阻上的电压降测量电感电流。电流模式控制消 除了反馈环路中由电感和输出电容产生的双极点,相移更 小;与电压模式控制方案相比,对误差放大器的要求较低。 只需简单的电阻(R<sub>C</sub>)和电容(C<sub>C</sub>)串联,即可在使用陶瓷电 容作为输出滤波的应用中实现稳定的高带宽环路(图5)。对 于其它类型的电容,由于电容量和ESR较大,电容和ESR 产生的零点频率低于预期的闭环交越频率。为稳定非陶瓷 输出电容环路,在COMP至SGND之间另外增加一个补偿 电容(C<sub>F</sub>),以补偿该ESR零点。

基本的稳压环路可以等效为功率调制器、输出反馈分压器 和误差放大器。功率调制器的直流增益由gmc × RLOAD设 置,极点和零点对由RLOAD、输出电容(COUT)及其ESR设置。 下式决定功率调制器的近似增益值(GAINMOD(dc)),不计斜 率补偿的影响。当占空比高于50%时,必须进行斜率补偿, 在MAX16952内部自动完成:

$$GAIN_{MOD(dc)} \cong g_{mc} \times \frac{R_{LOAD} \times f_{SW} \times L}{R_{LOAD} + (f_{SW} \times L)}$$

式中,R<sub>LOAD</sub> = V<sub>OUT</sub>/I<sub>OUT(MAX</sub>)的单位为 $\Omega$ ,f<sub>SW</sub>为开关频 率(MHz),L为输出电感( $\mu$ H),g<sub>mc</sub> = 1/(A<sub>V\_CS</sub> × R<sub>DC</sub>)(S)。 A<sub>V\_CS</sub>为电流检测放大器的电压增益,典型值为11V/V。 R<sub>DC</sub>为电感的直流电阻或电流检测电阻,单位为 $\Omega$ 。

在电流模式降压转换器中,输出电容及其ESR和负载电阻 产生的极点频率如下:

$$f_{pMOD} = \frac{I}{2\pi \times C_{OUT} \times \left(\frac{R_{LOAD} \times f_{SW} \times L}{R_{LOAD} + (f_{SW} \times L)} + ESR\right)}$$

输出电容及其ESR也产生以下频率的零点:

$$f_{zMOD} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

当 $C_{OUT}$ 包含n个相同的并联电容时, $C_{OUT} = n \times C_{OUT(EACH)}$ ,而ESR = ESR<sub>(EACH)</sub>/n。请注意,相同的电容并联时,电容零点与单个电容一致。

反馈分压器的增益为GAIN<sub>FB</sub> = V<sub>FB</sub>/V<sub>OUT</sub>,其中V<sub>FB</sub>为1V (典型值)。

跨导误差放大器的直流增益为GAIN<sub>EA(dc)</sub> = g<sub>m,EA</sub> × R<sub>OUT,EA</sub>, 其中g<sub>m,EA</sub>为误差放大器的跨导,R<sub>OUT,EA</sub>为误差放大器 的输出电阻。采用gm,EA为2500µS (最大值)及R<sub>OUT,EA</sub>为 30MΩ (典型值)的补偿设计时,相位裕量最大。 主极点(f<sub>dpEA</sub>)由补偿电容(C<sub>C</sub>)、补偿电阻(R<sub>C</sub>)和放大器输出 电阻(R<sub>OUT,EA</sub>)决定;零点(f<sub>zEA</sub>)由补偿电阻(R<sub>C</sub>)和补偿电容 (C<sub>C</sub>)决定。还有一个由C<sub>F</sub>和R<sub>C</sub>决定的可选极点(f<sub>pEA</sub>),若 其位置接近交越频率(f<sub>C</sub>,此时环路增益等于1 (0dB)),则 可抵消输出电容ESR零点。

因此:

$$f_{dpEA} = \frac{1}{2\pi \times C_C \times (R_{OUT,EA} + R_C)}$$

$$f_{zEA} = \frac{1}{2\pi \times C_C \times R_C}$$

$$f_{pEA} = \frac{1}{2\pi \times C_C \times R_C}$$

环路增益交越频率(f<sub>C</sub>)应远小于开关频率的1/5,并且远高于功率调制器极点(f<sub>pMOD</sub>):

$2\pi \times C_F \times R_C$

$$f_{pMOD} \ll f_C \le \frac{f_{SW}}{5}$$

总环路增益为调制器增益、反馈分压器增益和误差放大器 增益的乘积,在fc时应等于1。所以:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times GAIN_{EA(fC)} = 1$$

### 对于f<sub>zMOD</sub>大于f<sub>C</sub>的情况:

$$\begin{aligned} \text{GAIN}_{\text{EA}(\text{fC})} &= \text{g}_{\text{m,EA}} \times \text{R}_{\text{C}} \\ \text{GAIN}_{\text{MOD}(\text{fC})} &= \text{GAIN}_{\text{MOD}(\text{dc})} \times \frac{\text{f}_{\text{pMOD}}}{\text{f}_{\text{C}}} \end{aligned}$$

## 36V、2.2MHz降压控制器, 低工作电流

所以:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times g_{m,EA} \times R_{C} = 1$$

解出Rc:

$$R_{C} = \frac{V_{OUT}}{g_{m,EA} \times V_{FB} \times GAIN_{MOD(fC)}}$$

将 $R_C$ 和 $C_C$ 形成的误差放大器补偿零点(f\_{zEA})设置为f\_{pMOD}。 按照下式计算 $C_C$ :

$$C_{\rm C} = \frac{1}{2\pi \times f_{\rm pMOD} \times R_{\rm C}}$$

如果 $f_{zMOD}$ 小于5 x f<sub>C</sub>,在COMP与SGND之间增加第二 个电容C<sub>F</sub>,将R<sub>C</sub>和C<sub>F</sub>形成的补偿极点(f<sub>pEA</sub>)设置为f<sub>zMOD</sub>。 按下式计算C<sub>F</sub>:

$$C_{F} = \frac{1}{2\pi \times f_{zMOD} \times R_{C}}$$

负载电流减小时,调制器极点也降低;然而,调制器增益 相应增大,因此交越频率保持不变。

### 对于fzMOD小于fc的情况:

功率调制器在fc频点的增益为:

$$GAIN_{MOD(fC)} = GAIN_{MOD(dc)} \times \frac{f_{pMOD}}{f_{zMOD}}$$

误差放大器在fc频点的增益为:

$$GAIN_{EA(fC)} = g_{m,EA} \times R_C \times \frac{f_{zMOD}}{f_C}$$

所以:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times g_{m,EA} \times R_C \times \frac{f_{zMOD}}{f_C} = 1$$

解出R<sub>C</sub>:

$$R_{C} = \frac{V_{OUT} \times f_{C}}{g_{m,EA} \times V_{FB} \times GAIN_{MOD}(f_{C})} \times f_{ZMOD}$$

将R<sub>C</sub>和C<sub>C</sub>形成的误差放大器补偿零点设置为f<sub>pMOD</sub> (f<sub>zEA</sub> = f<sub>pMOD</sub>):

$$C_{C} = \frac{1}{2\pi \times f_{2MOD} \times R_{C}}$$

如果 $f_{zMOD}$ 小于5 × f<sub>C</sub>,在COMP与SGND之间增加第二个 电容C<sub>F</sub>。设置 $f_{pEA} = f_{zMOD}$ ,利用下式计算C<sub>F</sub>:

$$C_{\rm F} = \frac{1}{2\pi \times R_{\rm C} \times f_{\rm ZMOD}}$$

MOSFET选择

MAX16952的控制器驱动外部两个作为电路开关元件的逻辑电平n沟道MOSFET。选择MOSFET时考虑的关键参数包括:

- 导通电阻(R<sub>DS(ON)</sub>)

- 最大漏极-源极电压(VDS(MAX))

- 最小门限电压(V<sub>TH(MIN)</sub>)

- 总栅极电荷(QG)

- 反向传输电容(CRSS)

- 功率耗散

图5. 补偿网络

两个n沟道MOSFET必须为逻辑电平型,在V<sub>GS</sub> = 4.5V时 保证导通电阻不超标。确保最小输入电压时的传导损耗不 超过MOSFET的封装热保护限值,或不超过总体热预算。 也要保证传导损耗加上最小输入电压时的开关损耗不超过 封装额定值,或不超过总体热预算。MAX16952的DL栅 极驱动器必须驱动低边MOSFET (NL)。特别要检查确认高 边MOSFET (NH)导通引起的dV/dt不会通过其漏极-栅极 电容拉高NL栅极。这是交叉导通故障的最常见原因。

栅电荷损耗由驱动器耗散,不会使MOSFET温度升高。因此,如果驱动电流来自于内部LDO稳压器,必须检查由于驱动损耗引起的功率耗散。两个MOSFET的总栅电荷必须足够低,BIAS可为两个驱动器供电,而不会使IC过热:

PDRIVE = (VSUP - VBIAS) × QG\_TOTAL × fSW 式中,QG\_TOTAL为两个MOSFET的栅电荷之和。

升压飞电容选择

自举电容储存内部开关的栅极电压。其大小受限于高边 MOSFET的开关频率和栅电荷。理想情况下,自举电容应 至少为栅极电容的9倍。

$$C_{BST(TYP)} = 9 \times \frac{Q_G}{V_{BIAS}}$$

这就造成在驱动栅极时产生10%的压降。然而,如果该值 太大,不能在最小关断周期内重新充电,则必须选择较小 的电容。

重新充电期间,内部自举开关作为电阻,形成具有相关时 间常数的RC电路。两个τ(时间常数)内必须能够从90%充 电至99%。因此,最大允许电容为:

$$C_{BST(MAX)} = \frac{t_{OFF(MIN)}}{2 \times R_{BST(MAX)}}$$

MAX16952的最小允许关断时间为100ns (典型值)。如果 检测到连续8个100ns脉冲,则强制LSFET导通最小半个时 钟周期,这确保完全补充升压电容的电荷。

最坏工作情况是输出空载时MAX16952接近压差模式但未 完全处于压差模式,这意味着连续最小关断周期脉冲的数 量小于8。这种情况下,确保在100ns内补充每周期释放 的电荷数量。 有些应用中,增加外部升压电阻,以降低HSFET的导通时 间,这样每周期在BST电容上产生一个额外压降,可能需 要并联自举二极管。

设:

Q<sub>G</sub> = HSFET的栅极总电荷

Q<sub>BST</sub> = BST每周期释放的电荷

VL = BIAS电压 = 5V (典型值)

VBST = BST电压(BST - LX)

R<sub>BST\_EXT</sub> = 使用的外部升压电阻(连接在BST电容和 BST引脚之间)

R<sub>BST</sub> = 内部升压开关电阻 = 5Ω (典型值)

对于以上一组参数,确保:

Q<sub>BST</sub> > QG,每个100ns最小关断时间内

$Q_{BST} = (V_L - V_{BST})/(R_{BST_EXT} + R_{BST}) \times 100$ ns

所用外部HSFET的门限电压(V<sub>TH</sub>)决定V<sub>L</sub> - V<sub>BST</sub>,如果外 部HSFET的门限电压为3V,则V<sub>L</sub> - V<sub>BST</sub> = 2V。

此时,如果不满足Q<sub>BST</sub> > Q<sub>G</sub>,则需要外部并联自举肖特 基二极管。

### 应用信息

#### PCB布局指南

控制器接地连接:利用任意PCB层在IC附近布置一个小模拟接地区域。将该区域连接至SGND,并将该区域作为 SUP旁路电容、补偿元件、反馈驱动器及FOSC电阻的接 地连接。

如果可能,将所有功率元件布置在电路板的顶层,仅在顶 层上使用走线或覆铜布置电源级电流,尤其是大的高频元 件;不要增加过孔。

在顶层为输出布置一个大的PGND覆铜区域,将高频输入 电容、输出电容以及低边MOSFET的源极端连接至该区域。

## 36V、2.2MHz降压控制器, 低工作电流

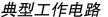

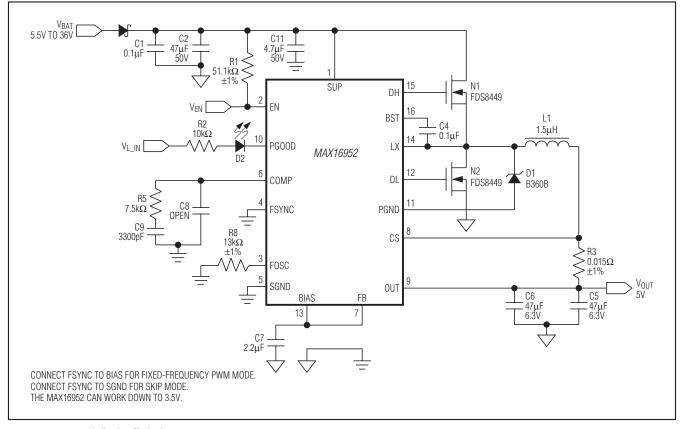

图6. VOUT = 5V的典型工作电路

然后,利用源极附近很少的过孔通过星型连接将SGND区 域连接至顶层覆铜PGND区域。不用通过其它任何位置连 接PGND和SGND。布局指南请参见MAX16952评估板的 数据资料。

使电源走线和负载连接尽量短,尤其在接地端。这对于高效率、无抖动工作至关重要。采用厚铜PCB (2oz VS 1oz) 以提高效率。

使控制器IC邻近同步整流器MOSFET (NL),并使LX、 PGND、DH和DL的走线短而宽。利用多个小过孔将这些 信号从顶层连接至底层。栅极电流的走线必须短而宽,如 果低边MOSFET距离控制器1 in,使用50 mil至100 mil 宽的走线。将来自于IC的PGND走线连接至靠近低边 MOSFET的源极端。

使高速开关节点(BST、LX、DH和DL)远离敏感的模拟区域(FOSC、COMP和FB)。将全部以SGND为基准的元件和

反馈元件分组靠近IC。使FB和补偿网络尽量小,以防拾取 噪声。

### 芯片信息

PROCESS: BiCMOS

### 封装信息

如需最近的封装外形信息和焊盘布局(占位面积),请查询china. maximintegrated.com/packages。请注意,封装编码中的"+"、 "#"或"-"仅表示RoHS状态。封装图中可能包含不同的尾缀字符, 但封装图只与封装有关,与RoHS状态无关。

| 封装类型        | 封装编码   | 外形编号           | 焊盘布局编号         |

|-------------|--------|----------------|----------------|

| 16 TSSOP-EP | U16E+3 | <u>21-0108</u> | <u>90-0120</u> |

### 修订历史

| 修订号 | 修订日期  | 说明                    | 修改页          |

|-----|-------|-----------------------|--------------|

| 0   | 3/11  | 最初版本。                 |              |

| 1   | 10/12 | 将VOUT限值修改为10V。        | 1, 2, 12, 16 |

| 2   | 1/13  | 定购信息中增加了MAX16952AUE+。 | 1            |

Maxim北京办事处 北京8328信箱 邮政编码100083 免费电话: 800 810 0310 电话: 010-6211 5199 传真: 010-6211 5299

Maxim不对Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。电气 特性表中列出的参数值(最小值和最大值)均经过设计验证,数据资料其它章节引用的参数值供设计人员参考。