### MAX3421F

### SPI接口的USB外设/主机控制器

#### 概述

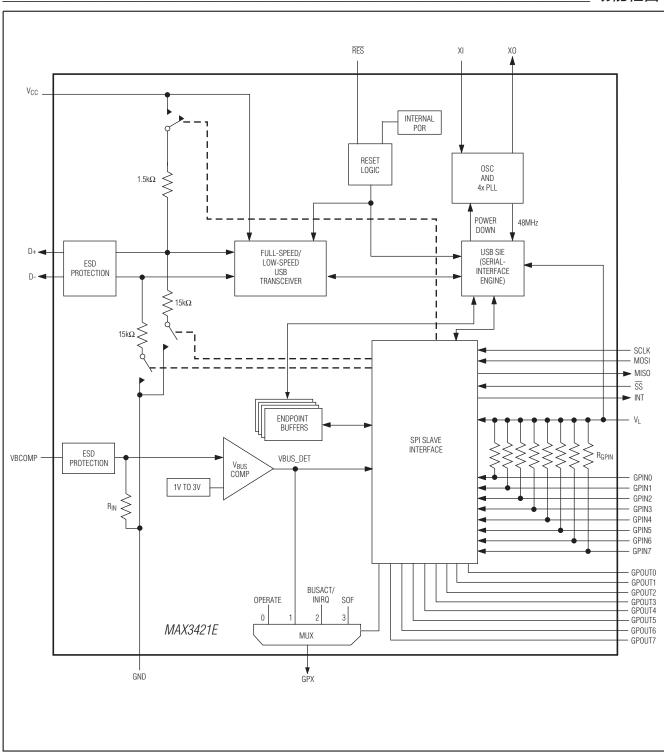

MAX3421E USB外设/主机控制器包含了所有必要的数字逻辑和模拟电路,可用来实现符合USB 2.0规范的全速USB外设或全速/低速主机。内置的收发器具有±15kV的ESD保护,并提供可编程的USB连接和断开功能。内部串行接口引擎(SIE)处理底层USB协议的细节,例如差错检验和总线重试。MAX3421E利用一组寄存器展开工作,通过一个最高工作速率达26MHz的SPI™接口可以访问这些寄存器。利用简单的3线或4线SPI接口,该器件可以给任何SPI主控制器(微处理器、ASIC、DSP等)增加USB外设或主机功能。

当作为USB主机工作时,MAX3421E使大量的USB外设能够为任何微处理器、ASIC或DSP所用。以点到点方案为例,可以为嵌入式系统增加USB键盘或鼠标接口,操作MAX3421E的固件可以非常简单,因为只需支持单个目标设备。

由于内部集成了电平转换器,SPI接口可工作于1.4V至3.6V的系统电压。USB定时操作在MAX3421E内部完成,完成后提供中断,这样无需占用SPI主控制器的定时器来满足USB定时要求。MAX3421E还提供八路通用输入和输出,因此,当微处理器采用I/O引脚实现SPI接口时,总的I/O口线不减反增。

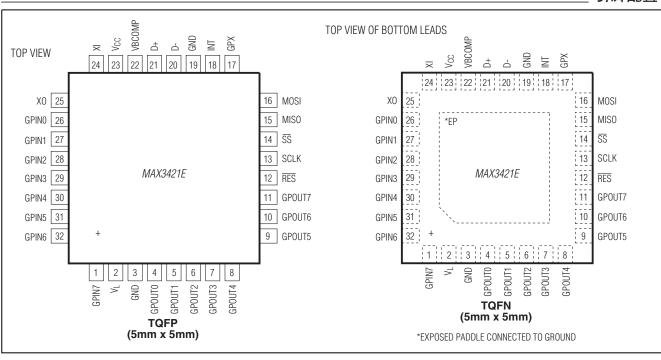

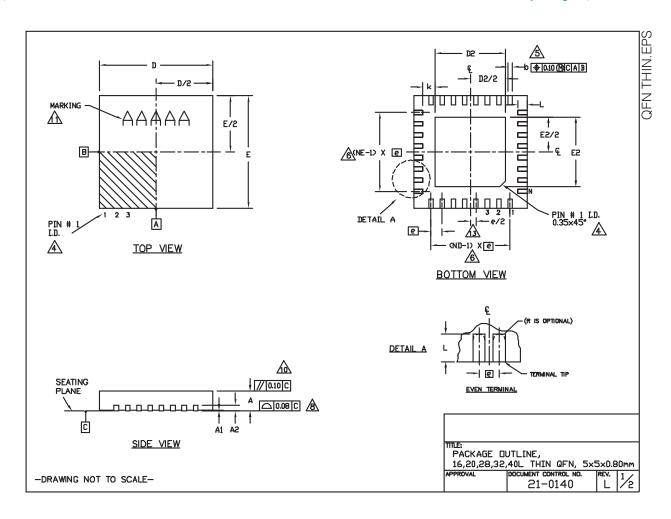

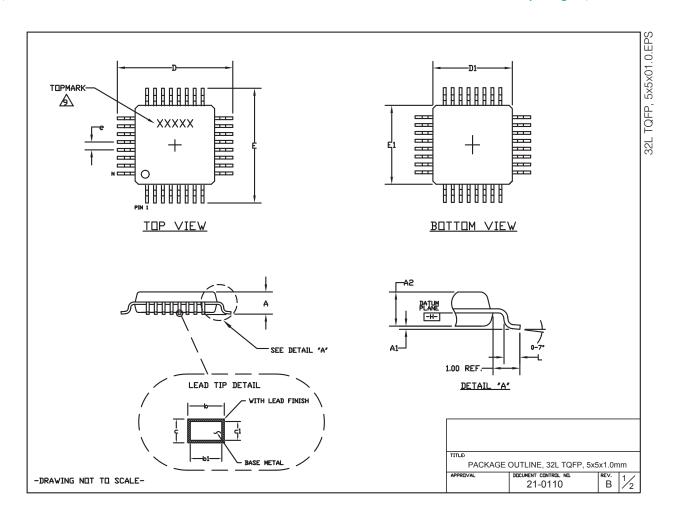

MAX3421E工作于-40°C至+85°C扩展级温度范围,备有32 引脚TQFP封装(5mm x 5mm)和32引脚TQFN封装(5mm x 5mm)。 特性

- ◆ 独立于微处理器的USB方案

- ♦ 软件兼容干SPI接口的USB外设控制器MAX3420E

- ◆ 符合USB 2.0规范(全速12Mbps外设, 全/低速12Mbps/1.5Mbps主机)

- ◆ 集成USB收发器

- ◆ 固件/硬件控制内部D+上拉电阻(外设模式)和 D+/D-下拉电阻(主机模式)

- ◆ 可编程3线或4线26MHz SPI接口

- ◆ 电平转换器和V<sub>1</sub> 输入允许使用独立的系统接口电压

- ◆ 在自供电外设应用中由内部比较器检测V<sub>BUS</sub>

- ♦ D+、D-和VBCOMP上提供ESD保护

- ◆ 中断输出引脚(电平或可编程边沿触发模式)实现查询或中断驱动的SPI接口

- ◆ 八个通用输入, 八个通用输出

- ◆ 用于通用输入引脚的中断信号, 可编程边沿极性

- ◆ 智能USB SIE

- ◆ 自动处理USB流量控制和双缓存

- ◆ 处理底层USB信号细节

- ◆ 自带定时器满足USB定时要求,无需SPI主控制器参与定时事件

- ◆ 节省空间的无铅TQFP和TQFN封装(5mm x 5mm)

#### 应用

嵌入式系统

台式路由器

医疗设备

PLC

微处理器和DSP 机顶盒 用户USB设备 PDA

相机 MP3播放器

仪表

#### 定购信息

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG CODE |  |

|--------------|----------------|-----------------|----------|--|

| MAX3421EEHJ+ | -40°C to +85°C | 32 TQFP         | H32-1    |  |

| MAX3421EETJ+ | -40°C to +85°C | 32 TQFN-EP*     | T3255-4  |  |

<sup>\*</sup>EP = 裸焊盘,连接至地。

SPI是Motorola, Inc.的商标。

<sup>+</sup>表示无铅封装。

### MAX3421F

### SPI接口的USB外设/主机控制器

主机工作特性

外设工作特性

- ◆ 在原来的MAX3420E寄存器组中增加十一个寄存器 (R21-R31)来控制主机工作模式

- ◆ 主控制器工作于全速或低速模式

- ♦ FIFO

SNDFIFO: 发送FIFO, 双缓冲、64字节 RCVFIFO: 接收FIFO, 双缓冲、64字节

- ◆ 处理DATA0/DATA1触发的产生和检测

- ♦ 处理全部传送过程的错误校验

- ◆ 以1ms间隔自动产生SOF (全速)/EOP (低速)

- ◆ 利用帧起始包(SOF/EOP)自动同步主机传送

- ◆ 可报告主机请求的结果

- ♦ 支持USB集线器

- ◆ 支持ISOCHRONOUS (同步)传送

- ♦ 简单编程

SIE自动产生周期性SOF (全速)或EOP (低速)帧标记 SPI主控制器装载数据,设置功能单元地址、端点和 传送类型,并启动传送

MAX3421E以中断和代码报告外设的响应

可在任意时间加载传送请求

SIE与帧标记保持同步

对于多包传送,SIE自动维护并检查数据触发

#### ◆ 内部端点FIFO

EP0: 控制(CONTROL) (64字节)

EP1: 输出(OUT), BULK或INTERRUPT,

2 x 64字节(双缓冲)

EP2: 输入(IN), BULK或INTERRUPT,

2 x 64字节(双缓冲)

EP3: 输入(IN), BULK或INTERRUPT (64字节)

- ◆ 双缓冲数据端点允许SPI主控制器的数据传送与USB 传送同时进行,提高了吞吐能力

- ♦ 设置(SETUP)数据有自己的8字节FIFO,简化了固件

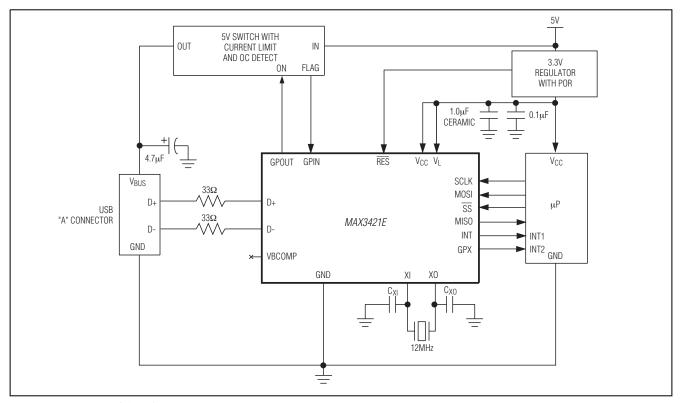

#### 典型应用电路

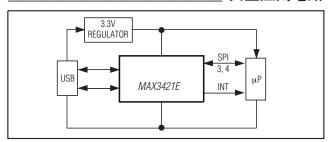

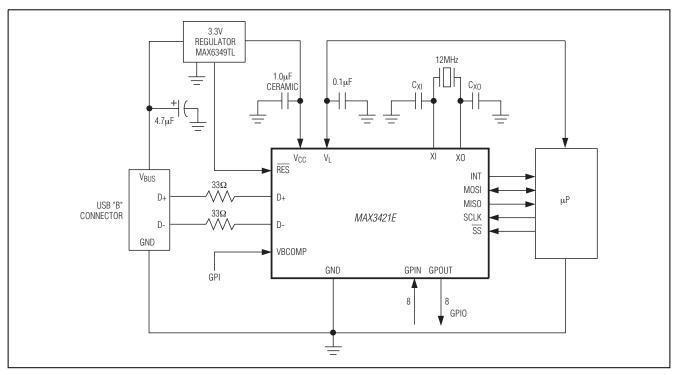

图1. MAX3421E通过3或4个接口引脚连至任何微处理器

MAX3421E通过3或4个接口引脚连接至任何微处理器(µP)(图1)。对于不含硬件SPI接口的简单微处理器,可通过通用I/O引脚逐位操作的方式进行通信。MAX3421E上的八个GPIN (通用输入)引脚和八个GPOUT (通用输出)引脚替代µP被通信接口占用的口线后仍有富余。虽然MAX3421E的SPI接口具有独立的数据输入(MOSI,主出从人)和数据输出(MISO,主人从出)引脚,由于SPI接口的MOSI也可配置为双向数据线,可以省下一个接口引脚。即所谓的半双工模式。

### SPI接口的USB外设/主机控制器

#### 典型应用电路(续)

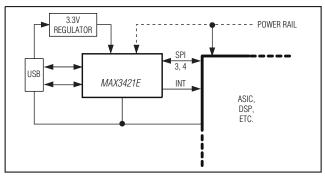

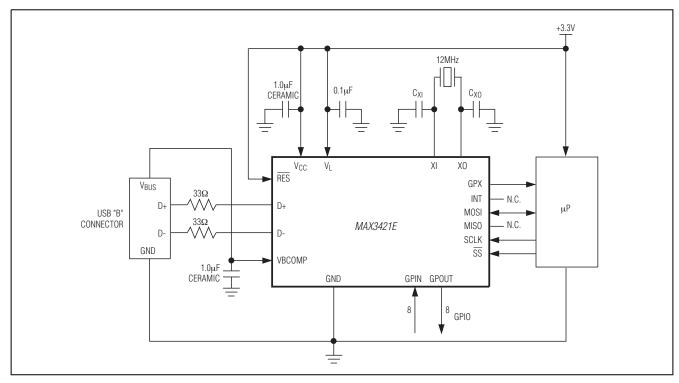

图2. MAX3421E连至大型芯片

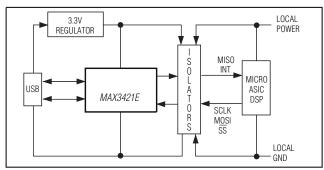

图3. 利用MAX3421E实现USB的光电隔离

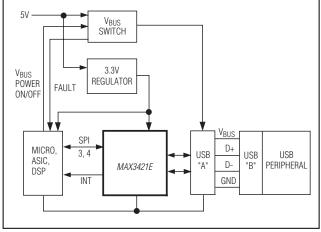

图4. MAX3421E用于嵌入式主机应用

MAX3421E的两个特性使其非常易于和ASIC和DSP这样的大规模、高速芯片接口(见图2)。首先,SPI接口的速度高达26MHz;其次,单独的V<sub>L</sub>引脚和内部电平转换器使其系统接口能够工作在比3.3V的V<sub>CC</sub>更低的电压。

MAX3421E为USB接口的电气隔离提供了理想方案(图3)。 USB具有流量控制特性,在微处理器完成SPI端口的数据 传送操作前,MAX3421E会自动以NAK握手包应答主机 请求。这就意味着SPI接口可工作在最高至26MHz的任何 频率下。因此,设计者可自由选择接口的工作频率,并 根据成本和性能要求选择最优的光电耦合器。

图4给出了MAX3421E工作在USB主机模式下的系统框图。USB主机供应5V电源给USB "A"型连接器的V<sub>BUS</sub>引脚,为USB外设供电。为外设供电的系统须在供电引脚上采用保护电路,以免外设过流给系统造成损害。V<sub>BUS</sub>开关(例如MAX4789)可提供功率控制和另外两项功能:限制输送给外设的电流(例如200mA),并向SPI主控制器报告故障(过流)。Maxim提供多种不同限制电流和功能的V<sub>BUS</sub>开关。详情请访问Maxim网站。

3.3V调节器(例如MAX6349TL)为MAX3421E或者系统控制器提供电源。如果系统控制器工作在更低电压下,MAX3421E的SPI和I/O接口也可工作在更低电压下,只需将系统电压(例如2.5V或1.8V)连接至MAX3421E的V<sub>I</sub>引脚。

# SPI接口的USB外设/主机控制器

### 功能框图

# SPI接口的USB外设/主机控制器

### 引脚说明

| 引脚    | 名称     | 输入/<br>输出        | 功能                                                                                                                                                                                              |

|-------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GPIN7  | 输入               | 通用输人。GPIN7-GPIN0通过内部上拉电阻连接至V <sub>L</sub> 。GPIN7-GPIN0的逻辑电平参照于V <sub>L</sub> 电压。                                                                                                                |

| 2     | VL     | 输入               | 电平转换器电压输入。连接 $V_L$ 到1.4 $V$ 至3.6 $V$ 的系统逻辑电源。用一只0.1 $\mu$ F电容,尽可能靠近 $V_L$ 引脚旁路 $V_L$ 到地。                                                                                                        |

| 3, 19 | GND    | 输入               | 地。                                                                                                                                                                                              |

| 4     | GPOUT0 |                  |                                                                                                                                                                                                 |

| 5     | GPOUT1 |                  |                                                                                                                                                                                                 |

| 6     | GPOUT2 |                  |                                                                                                                                                                                                 |

| 7     | GPOUT3 | 输出               | │<br>│ 通用推挽式输出。GPOUT7-GPOUT0的逻辑电平参照于V <sub>L</sub> 电压。                                                                                                                                          |

| 8     | GPOUT4 | 湘山               | 应用准况共福田。OFOOT/-GFOOTO的这种电十多然 1 VL电压。                                                                                                                                                            |

| 9     | GPOUT5 |                  |                                                                                                                                                                                                 |

| 10    | GPOUT6 |                  |                                                                                                                                                                                                 |

| 11    | GPOUT7 |                  |                                                                                                                                                                                                 |

| 12    | RES    | 输入               | 器件复位。驱动 $\overline{\text{RES}}$ 为低可清除PINCTL (R17)、USBCTL (R15)和SPI逻辑之外的所有内部寄存器。逻辑电平参照于 $V_L$ 电压。(关于MAX3421E的复位特性详见 <i>器件复位</i> 部分。) <b>注</b> :在没有 $V_{CC}$ 或 $V_L$ 时,MAX3421E由内部复位,此时不能访问寄存器文件。 |

| 13    | SCLK   | 输入               | SPI串行时钟输入。外部SPI主控制器提供SCLK,频率最高 $26$ MHz。逻辑电平参照于 $V_L$ 。数据在SCLK的上升沿输入SPI从器件接口。在SCLK的下降沿,SPI从器件接口输出数据。                                                                                            |

| 14    | SS     | 输入               | $SPI$ 从器件选择输入。 $\overline{SS}$ 逻辑电平参照于 $V_L$ 。当 $\overline{SS}$ 被驱动为高时, $SPI$ 从器件接口为非选定状态, $MISO$ 引脚为高阻态, $SCLK$ 跳变沿没有作用。一次 $SPI$ 传送始于由高到低的 $\overline{SS}$ 跳变,终止于由低到高的 $\overline{SS}$ 跳变。     |

| 15    | MISO   | 输出               | SPI串行数据输出(主人从出)。MISO为推挽式输出。MISO在半双工模式或 $\overline{SS}$ = 1时为三态。MISO逻辑电平参照于 $V_L$ 。                                                                                                              |

| 16    | MOSI   | 输人或<br>输入/<br>输出 | SPI串行数据输入(主出从人)。MOSI逻辑电平参照于V <sub>L</sub> 。MOSI也可配置为双向MOSI/MISO输入和输出。(参见图15。)                                                                                                                   |

| 17    | GPX    | 输出               | 通用推挽式复用输出。通过写寄存器PINCTL (R17)中的GPXB和GPXA控制位以及寄存器MODE (R27)中的SEPIRQ位,可选择出现在GPX引脚上的MAX3421E内部信号。GPX可用来输出五种信号之一(参见 $GPX$ 部分)。                                                                       |

| 18    | INT    | 输出               | 中断输出。边沿模式下INT逻辑电平参照于V <sub>L</sub> ,为极性可编程的推挽式输出。电平模式下,INT为低有效开漏输出。置位寄存器CPUCTL (R16)中的IE位可使能INT。                                                                                                |

| 20    | D-     | 输入/<br>输出        | USB之D-信号。通过一只33Ω ±1%串联电阻连接D-至USB连接器。器件内部接有可切换的15kΩ D-下拉电阻。                                                                                                                                      |

# SPI接口的USB外设/主机控制器

引脚说明(续)

| 引脚 | 名称       | 输入/<br>输出 | 功能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | D+       | 输入/<br>输出 | USB之D+信号。通过一只33 $\Omega$ ±1%串联电阻连接D+至USB连接器。器件内部接有可切换的1.5k $\Omega$ D+上拉电阻和15k $\Omega$ D+下拉电阻。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22 | VBCOMP   | 输人        | V <sub>BUS</sub> 比较器输入。VBCOMP连接至一个内部电压比较器,以便于SPI主控制器检查(通过中断或寄存器位) V <sub>BUS</sub> 的加电或掉电状态。用一只1.0μF陶瓷电容旁路VBCOMP到地。VBCOMP被R <sub>IN</sub> 下拉至地(参见 <i>Electrical Characteristics</i> )。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23 | Vcc      | 输入        | USB收发器和内核逻辑电源输入。连接 $V_{CC}$ 至 $3.3V$ 正电源。用一只 $1.0\mu$ F陶瓷电容尽量靠近 $V_{CC}$ 引脚旁路 $V_{CC}$ 到地。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24 | XI       | 输入        | 晶振输人。连接XI到并联谐振频率为 $12 MHz \pm 0.25\%$ 的晶体的一端和一只连接至GND的负载电容。也可用一个参照于 $V_{CC}$ 的外部时钟驱动XI。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25 | ХО       | 输出        | 晶振输出。连接XO到并联谐振频率为12MHz ±0.25%的晶体的另一端和一只连接至GND的负载电容。当XI由外部源驱动时浮空XO。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 26 | GPIN0    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27 | GPIN1    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28 | GPIN2    |           | VZ ITEM 1 CODY CODY OF THE COD |

| 29 | GPIN3    | 输入        | 通用输入。GPIN7-GPIN0通过内部上拉电阻连接至V <sub>L</sub> 。GPIN7-GPIN0的逻辑电平参照于V <sub>L</sub><br>电压。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30 | GPIN4    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 31 | 31 GPIN5 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32 | GPIN6    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EP | GND      | 输入        | 裸焊盘,连接至地。连接EP到GND或浮空。EP位于TQFN封装的底部。TQFP封装没有裸焊盘。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### SPI接口的USB外设/主机控制器

#### 寄存器说明

SPI主控制器通过读写MAX3421E内部的26个寄存器(外设模式,见表1)或23个寄存器(主机模式,见表2)控制其工作。置位MODE寄存器(R27)中的HOST位可配置MAX3421E为主机工作模式。当作为USB外设使用时,MAX3421E的寄存器兼容于MAX3420E,附加功能列于表1下面的注释1b中。关于这些寄存器内容的完整说明,参见Maxim网站上的应用笔记3785: MAX3421E编程指南。

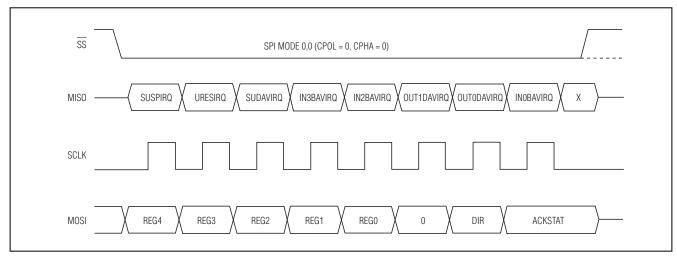

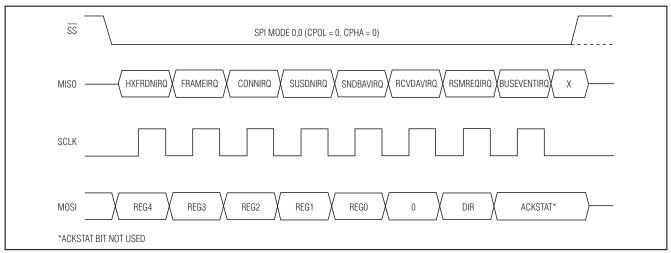

一次寄存器访问包含两个阶段,首先是SPI主控制器写SPI 命令字节,紧接着就是对所寻址寄存器的读或写操作。所 有SPI传送都是MSB (最高有效位)在先。命令字节包括寄存 器地址、一个方向位(读 = 0, 写 = 1)和ACKSTAT位(图 5)。 SPI主控制器在命令字节的Reg4至Reg0位写入寄存器编号 对应的二进制码,即可寻址对应的MAX3421E内部寄存器。 例如,要访问IOPINS1寄存器(R20),Reg4到Reg0可设置如 Arr: Reg4 = 1, Reg3 = 0, Reg2 = 1, Reg1 = 0, Reg0 = 0. DIR (方向)位决定数据传送的方向。DIR=1意味着数据将 被写入寄存器, DIR=0意味着数据将被读出寄存器。 ACKSTAT位设定EPSTALLS寄存器(R9)中ACKSTAT位的 状态(仅用于外设模式)。SPI主控制器将该位置位表明它 已完成一次CONTROL传送。由于该位会被频繁用到,将 其放在SPI命令字节中可提高固件效率。主机模式下 ACKSTAT位被忽略。在全双工SPI模式中, 伴随着命令字 节的送人, MAX3421E同时送出八个USB状态位(图6、7)。 在半双工模式中,可按照访问一般寄存器位的方式访问 这些状态位。

前五个寄存器(R0-R4)用来访问外设和主机模式下的FIFO。 重复访问这些寄存器时内部寄存器地址被冻结,这样, 可以在同一个SPI访问周期中(SS保持为低)通过FIFO写人 或读出多个字节。访问寄存器R5-R19时,在一次SPI访问 周期中随着每个字节的传送,内部寄存器地址可自动递 增。访问R20时,地址冻结于该寄存器,而对于R21-R31 的访问也会使内部地址递增,重复访问R31时地址冻结于 R31。

表1和表2中的寄存器映像给出了外设和主机模式下适用的寄存器位。不适用于某种模式的寄存器位显示为零。 这些寄存器位读出时为零,不应将它们写为逻辑1。

#### 外设模式寄存器映像

当工作于USB外设模式时(MAX3421E的HOST位被置0 (默认)), MAX3421E保持与MAX3420E寄存器的兼容性。为MAX3420E写的固件无需调整就可运行于MAX3421E。为了支持MAX3421E的新特性,寄存器组中包含了一些新的位,在表1底部的注释1b中有所描述。

#### 主机模式寄存器映像

正如表2所示,在主机模式下(HOST = 1),有些MAX3420E 寄存器被重新命名(例如R1变为RCVFIFO),有些没有使用(显示为零),而有些仍然适用于主机模式。此外,另有11个寄存器(R21-R31)增加了USB主机功能。

| b7   | b6   | b5   | b4   | b3   | b2 | b1  | b0       |

|------|------|------|------|------|----|-----|----------|

| Reg4 | Reg3 | Reg2 | Reg1 | Reg0 | 0  | DIR | ACKSTAT* |

<sup>\*</sup>ACKSTAT位在主机模式下被忽略。 图5. SPI命令字节

| STATUS BITS (PERIPHERAL MODE) |         |          |           |           |            |            |           |  |

|-------------------------------|---------|----------|-----------|-----------|------------|------------|-----------|--|

| b7 b6 b5 b4 b3 b2 b1 b6       |         |          |           |           |            | b0         |           |  |

| SUSPIRQ                       | URESIRQ | SUDAVIRQ | IN3BAVIRQ | IN2BAVIRQ | OUT1DAVIRQ | OUTODAVIRQ | IN0BAVIRQ |  |

图6. 外设模式下, USB状态位随着每次传送的首个字节送出(全双工模式)

| STATUS BITS (HOST MODE) |                         |         |          |           |           |           |             |  |

|-------------------------|-------------------------|---------|----------|-----------|-----------|-----------|-------------|--|

| b7                      | b7 b6 b5 b4 b3 b2 b1 b0 |         |          |           |           |           |             |  |

| HXFRDNIRQ               | FRAMEIRQ                | CONNIRQ | SUSDNIRQ | SNDBAVIRQ | RCVDAVIRQ | RSMREQIRQ | BUSEVENTIRQ |  |

图7. 主机模式下, USB状态位随着每次传送的首个字节送出(全双工模式)

# SPI接口的USB外设/主机控制器

### 表1. 外设模式下(HOST = 0)的MAX3421E寄存器映像(注1a、1b)

| REG | NAME       | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | acc |

|-----|------------|-----------|-----------|-----------|-----------|-----------|------------|------------|-----------|-----|

| R0  | EP0FIFO    | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R1  | EP10UTFIF0 | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R2  | EP2INFIFO  | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R3  | EP3INFIFO  | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R4  | SUDFIFO    | b7        | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R5  | EP0BC      | 0         | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R6  | EP10UTBC   | 0         | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R7  | EP2INBC    | 0         | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R8  | EP3INBC    | 0         | b6        | b5        | b4        | b3        | b2         | b1         | b0        | RSC |

| R9  | EPSTALLS   | 0         | ACKSTAT   | STLSTAT   | STLEP3IN  | STLEP2IN  | STLEP1OUT  | STLEP0OUT  | STLEP0IN  | RSC |

| R10 | CLRTOGS    | EP3DISAB  | EP2DISAB  | EP1DISAB  | CTGEP3IN  | CTGEP2IN  | CTGEP1OUT  | 0          | 0         | RSC |

| R11 | EPIRQ      | 0         | 0         | SUDAVIRQ  | IN3BAVIRQ | IN2BAVIRQ | OUT1DAVIRQ | OUT0DAVIRQ | IN0BAVIRQ | RC  |

| R12 | EPIEN      | 0         | 0         | SUDAVIE   | IN3BAVIE  | IN2BAVIE  | OUT1DAVIE  | OUT0DAVIE  | INOBAVIE  | RSC |

| R13 | USBIRQ     | URESDNIRQ | VBUSIRQ   | NOVBUSIRQ | SUSPIRQ   | URESIRQ   | BUSACTIRQ  | RWUDNIRQ   | OSCOKIRQ  | RC  |

| R14 | USBIEN     | URESDNIE  | VBUSIE    | NOVBUSIE  | SUSPIE    | URESIE    | BUSACTIE   | RWUDNIE    | OSCOKIE   | RSC |

| R15 | USBCTL     | HOSCSTEN  | VBGATE    | CHIPRES   | PWRDOWN   | CONNECT   | SIGRWU     | 0          | 0         | RSC |

| R16 | CPUCTL     | PULSEWID1 | PULSEWID0 | 0         | 0         | 0         | 0          | 0          | ΙE        | RSC |

| R17 | PINCTL     | EP3INAK   | EP2INAK   | EPOINAK   | FDUPSPI   | INTLEVEL  | POSINT     | GPXB       | GPXA      | RSC |

| R18 | REVISION   | 0         | 0         | 0         | 1         | 0         | 0          | 1          | 0         | R   |

| R19 | FNADDR     | 0         | b6        | b5        | b4        | b3        | b2         | b1         | b0        | R   |

| R20 | IOPINS1    | GPIN3     | GPIN2     | GPIN1     | GPIN0     | GPOUT3    | GPOUT2     | GPOUT1     | GPOUT0    | RSC |

| R21 | IOPINS2    | GPIN7     | GPIN6     | GPIN5     | GPIN4     | GPOUT7    | GPOUT6     | GPOUT5     | GPOUT4    | RSC |

| R22 | GPINIRQ    | GPINIRQ7  | GPINIRQ6  | GPINIRQ5  | GPINIRQ4  | GPINIRQ3  | GPINIRQ2   | GPINIRQ1   | GPINIRQ0  | RSC |

| R23 | GPINIEN    | GPINIEN7  | GPINIEN6  | GPINIEN5  | GPINIEN4  | GPINIEN3  | GPINIEN2   | GPINIEN1   | GPINIEN0  | RSC |

| R24 | GPINPOL    | GPINPOL7  | GPINPOL6  | GPINPOL5  | GPINPOL4  | GPINPOL3  | GPINPOL2   | GPINPOL1   | GPINPOL0  | RSC |

| R25 | _          | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         | _   |

| R26 | _          | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         | _   |

| R27 | MODE       | 0         | 0         | 0         | SEPIRQ    | 0         | 0          | 0          | HOST = 0  | RSC |

| R28 |            | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         |     |

| R29 | _          | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         |     |

| R30 |            | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         |     |

| R31 | _          | 0         | 0         | 0         | 0         | 0         | 0          | 0          | 0         | _   |

注1a: acc (访问)列表示SPI主控制器访问寄存器的方式。

R = 读; RC = 读或清除; RSC = 读、置位或清除。

对R(只读)寄存器写不会有任何作用。 对RC位(读或清除)写1将清除该位。 对RC位写零不会有任何作用。

# SPI接口的USB外设/主机控制器

### 表1. 外设模式下(HOST = 0)的MAX3421E寄存器映像(注1a、1b) (续)

注1b: 外设模式下, MAX3421E除了下列增强功能外, 执行与MAX3420E相同的功能:

- 1) R16新增PULSEWID0和PULSEWID1位来控制边沿中断模式下的INT脉冲宽度(见图12)。MAX3420E中这些位默认设置为10.6ps。

- 2) R21新增四个GPIO位。

- 3) R22和R23添加通用输入引脚至中断系统。R24控制边沿极性。

- 4) R27控制外设/主机模式和SEPIRQ位。

- 5) 当位[GPXB:GPXA] = [1:0]且位SEPIRQ = 1 (R27第4位)时,GPX输出的BUSACT信号被替换为第二个IRQ信号,专用于GPIN引脚产生中断。

#### 表2. 主机模式下(HOST = 1)的MAX3421E寄存器映像(注2)

| REG | NAME     | b7        | b6        | b5        | b4       | b3        | b2        | b1        | b0          | acc |

|-----|----------|-----------|-----------|-----------|----------|-----------|-----------|-----------|-------------|-----|

| R0  | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R1  | RCVFIFO  | b7        | b6        | b5        | b4       | b3        | b2        | b1        | b0          | RSC |

| R2  | SNDFIFO  | b7        | b6        | b5        | b4       | b3        | b2        | b1        | b0          | RSC |

| R3  | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R4  | SUDFIFO  | b7        | b6        | b5        | b4       | b3        | b2        | b1        | b0          | RSC |

| R5  | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R6  | RCVBC    | 0         | BC6       | BC5       | BC4      | BC3       | BC2       | BC1       | BC0         | RSC |

| R7  | SNDBC    | 0         | BC6       | BC5       | BC4      | BC3       | BC2       | BC1       | BC0         | RSC |

| R8  | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           |     |

| R9  | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R10 | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R11 | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R12 | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R13 | USBIRQ   | 0         | VBUSIRQ   | NOVBUSIRQ | 0        | 0         | 0         | 0         | OSCOKIRQ    | RC  |

| R14 | USBIEN   | 0         | VBUSIE    | NOVBUSIE  | 0        | 0         | 0         | 0         | OSCOKIE     | RSC |

| R15 | USBCTL   | 0         | 0         | CHIPRES   | PWRDOWN  | 0         | 0         | 0         | 0           | RSC |

| R16 | CPUCTL   | PULSEWID1 | PULSEWID0 | 0         | 0        | 0         | 0         | 0         | ΙE          | RSC |

| R17 | PINCTL   | EP3INAK   | EP2INAK   | EP0INAK   | FDUPSPI  | INTLEVEL  | POSINT    | GPXB      | GPXA        | RSC |

| R18 | REVISION | 0         | 0         | 0         | 1        | 0         | 0         | 1         | 0           | R   |

| R19 | _        | 0         | 0         | 0         | 0        | 0         | 0         | 0         | 0           | _   |

| R20 | IOPINS1  | GPIN3     | GPIN2     | GPIN1     | GPIN0    | GPOUT3    | GPOUT2    | GPOUT1    | GPOUT0      | RSC |

| R21 | IOPINS2  | GPIN7     | GPIN6     | GPIN5     | GPIN4    | GPOUT7    | GPOUT6    | GPOUT5    | GPOUT4      | RSC |

| R22 | GPINIRQ  | GPINIRQ7  | GPINIRQ6  | GPINIRQ5  | GPINIRQ4 | GPINIRQ3  | GPINIRQ2  | GPINIRQ1  | GPINIRQ0    | RC  |

| R23 | GPINIEN  | GPINIEN7  | GPINIEN6  | GPINIEN5  | GPINIEN4 | GPINIEN3  | GPINIEN2  | GPINIEN1  | GPINIEN0    | RSC |

| R24 | GPINPOL  | GPINPOL7  | GPINPOL6  | GPINPOL5  | GPINPOL4 | GPINPOL3  | GPINPOL2  | GPINPOL1  | GPINPOL0    | RSC |

| R25 | HIRQ     | HXFRDNIRQ | FRAMEIRQ  | CONNIRQ   | SUSDNIRQ | SNDBAVIRQ | RCVDAVIRQ | RSMREQIRQ | BUSEVENTIRQ | RC  |

| R26 | HIEN     | HXFRDNIE  | FRAMEIE   | CONNIE    | SUSDNIE  | SNDBAVIE  | RCVDAVIE  | RSMREQIE  | BUSEVENTIE  | RSC |

| R27 | MODE     | DPPULLDN  | DMPULLDN  | DELAYISO  | SEPIRQ   | SOFKAENAB | HUBPRE    | SPEED     | HOST = 1    | RSC |

| R28 | PERADDR  | 0         | b6        | b5        | b4       | b3        | b2        | b1        | b0          | RSC |

| R29 | HCTL     | SNDTOG1   | SNDTOG0   | RCVTOG1   | RCVTOG0  | SIGRSM    | BUSSAMPLE | FRMRST    | BUSRST      | LS  |

| R30 | HXFR     | HS        | ISO       | OUTNIN    | SETUP    | EP3       | EP2       | EP1       | EP0         | LS  |

| R31 | HRSL     | JSTATUS   | KSTATUS   | SNDTOGRD  | RCVTOGRD | HRSLT3    | HRSLT2    | HRSLT1    | HRSLT0      | R   |

## SPI接口的USB外设/主机控制器

#### 表2. 主机模式下(HOST = 1)的MAX3421E寄存器映像(注2) (续)

注2: acc (访问)列表示SPI主控制器访问寄存器的方式。

R = 读; RC = 读或清除; RSC = 读、置位或清除; LS = 加载检测。

对R(只读)寄存器写不会有任何作用。

对RC位(读或清除)写1将清除该位。

对RC位写零不会有任何作用。

写LS寄存器将基于寄存器内容启动一次主机操作。

#### 引脚配置

# SPI接口的USB外设/主机控制器

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.) VCC0.3V to +4V | Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>32-Pin TQFN (derate 21.3mW/°C above +70°C)1702mW |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| V <sub>L</sub> 0.3V to +4V                                               | 32-Pin TQFP (derate 13.1mW/°C above +70°C)1047mW                                                          |

| VBCOMP0.3V to +6V                                                        | Operating Temperature Range40°C to +85°C                                                                  |

| D+, D-, XI, XO0.3V to (V <sub>CC</sub> + 0.3V)                           | Junction Temperature+150°C                                                                                |

| SCLK, MOSI, MISO, SS, RES, GPOUT7-GPOUT0,                                | Storage Temperature Range65°C to +150°C                                                                   |

| GPIN7–GPIN0, GPX, INT0.3V to $(V_L + 0.3V)$                              | Lead Temperature (soldering, 10s)+300°C                                                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3V \text{ to } +3.6V, V_L = +1.4V \text{ to } +3.6V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V, V_L = +2.5V, T_A = +25^{\circ}C.) \text{ (Note 3)}$

| PARAMETER                                            | SYMBOL            | CONDITIONS                                                                                               | MIN                   | TYP  | MAX | UNITS |  |

|------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------|-----------------------|------|-----|-------|--|

| DC CHARACTERISTICS                                   |                   |                                                                                                          | •                     |      |     |       |  |

| Supply Voltage V <sub>CC</sub>                       | Vcc               |                                                                                                          | 3.0                   | 3.3  | 3.6 | V     |  |

| Logic-Interface Voltage V <sub>L</sub>               | VL                |                                                                                                          | 1.4                   |      | 3.6 | V     |  |

| V <sub>CC</sub> Supply Current                       | lcc               | Continuously transmitting on D+ and D- at 12Mbps, C <sub>L</sub> = 50pF on D+ and D- to GND, CONNECT = 0 |                       |      | 45  | mA    |  |

| V <sub>L</sub> Supply Current                        | ΙL                | SCLK toggling at 20MHz, $\overline{SS}$ = low, GPIN7–GPIN0 = 0                                           |                       | 2.35 | 10  | mA    |  |

| V <sub>CC</sub> Supply Current During Idle           | ICCID             | D+ = high, D- = low                                                                                      |                       | 8.7  | 15  | mA    |  |

| V <sub>CC</sub> Suspend Supply Current               | Iccsus            | CONNECT = 0, PWRDOWN = 1                                                                                 |                       | 30   | 60  | μΑ    |  |

| V <sub>L</sub> Suspend Supply Current                | I <sub>LSUS</sub> | CONNECT = 0, PWRDOWN = 1                                                                                 |                       | 20   | 50  | μΑ    |  |

| LOGIC-SIDE I/O                                       |                   |                                                                                                          |                       |      |     |       |  |

| MISO, GPOUT7-GPOUT0, GPX,<br>INT Output High Voltage |                   | $I_{LOAD} = +1mA$                                                                                        | V <sub>L</sub> - 0.4  |      |     |       |  |

|                                                      | VoH               | $I_{LOAD} = +5mA$ , $V_L < 2.5V$ (Note 4)                                                                | V <sub>L</sub> - 0.45 |      |     | V     |  |

| The Output High Voltage                              |                   | $I_{LOAD} = +10$ mA, $V_{L} \ge 2.5$ V (Note 4)                                                          | V <sub>L</sub> - 0.4  |      |     |       |  |

| MICO ODOLITZ ODOLITO ODV                             |                   | $I_{LOAD} = -1mA$                                                                                        |                       |      | 0.4 |       |  |

| MISO, GPOUT7-GPOUT0, GPX, INT Output Low Voltage     | V <sub>OL</sub>   | I <sub>LOAD</sub> = -20mA, V <sub>L</sub> < 2.5V (Note 4)                                                |                       |      | 0.6 | V     |  |

| The Odiput Low Voltage                               |                   | $I_{LOAD} = -20$ mA, $V_{L} \ge 2.5$ V (Note 4)                                                          |                       |      | 0.4 |       |  |

| SCLK, MOSI, GPIN7-GPIN0, SS, RES Input High Voltage  | VIH               |                                                                                                          | 2/3 x V <sub>L</sub>  |      |     | V     |  |

| SCLK, MOSI, GPIN7-GPIN0, SS, RES Input Low Voltage   | VIL               |                                                                                                          |                       |      | 0.4 | V     |  |

| SCLK, MOSI, SS, RES Input<br>Leakage Current         | lıL               |                                                                                                          | -1                    |      | +1  | μΑ    |  |

| GPIN7-GPIN0 Pullup Resistor to V <sub>L</sub>        | RGPIN             |                                                                                                          | 10                    | 20   | 30  | kΩ    |  |

| TRANSCEIVER SPECIFICATIONS                           | 6                 |                                                                                                          |                       |      |     |       |  |

| Differential-Receiver Input<br>Sensitivity           |                   | IV <sub>D+</sub> - V <sub>D-</sub> I                                                                     | 0.2                   |      |     | V     |  |

# SPI接口的USB外设/主机控制器

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}$  = +3V to +3.6V,  $V_L$  = +1.4V to +3.6V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{CC}$  = +3.3V,  $V_L$  = +2.5V,  $T_A$  = +25°C.) (Note 3)

| PARAMETER                                              | SYMBOL            | CONDITIONS                                                    | MIN                   | TYP  | MAX   | UNITS |

|--------------------------------------------------------|-------------------|---------------------------------------------------------------|-----------------------|------|-------|-------|

| Differential-Receiver Common-<br>Mode Voltage          |                   |                                                               | 0.8                   |      | 2.5   | V     |

| Single-Ended Receiver Input Low Voltage                | VIL               |                                                               |                       |      | 0.8   | V     |

| Single-Ended Receiver Input<br>High Voltage            | VIH               |                                                               | 2.0                   |      |       | V     |

| Single-Ended Receiver<br>Hysteresis Voltage            |                   |                                                               |                       | 0.2  |       | V     |

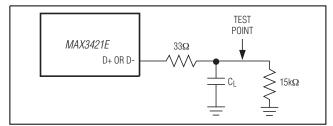

| D+, D- Output Low Voltage                              | V <sub>OL</sub>   | $R_L = 1.5k\Omega$ from D+ to 3.6V                            |                       |      | 0.3   | V     |

| D+, D- Output High Voltage                             | VoH               | $R_L = 15k\Omega$ from D+ and D- to GND                       | 2.8                   |      | 3.6   | V     |

| Driver Output Impedance<br>Excluding External Resistor |                   | (Note 4)                                                      | 2                     | 7    | 11    | Ω     |

| D+ Pullup Resistor                                     |                   | $R_{EXT} = 33\Omega$                                          | 1.425                 | 1.5  | 1.575 | kΩ    |

| D+, D- Pulldown Resistor                               |                   | $R_{EXT} = 33\Omega$                                          | 14.25                 | 15   | 15.75 | kΩ    |

| D+, D- Input Impedance                                 |                   |                                                               | 300                   |      |       | kΩ    |

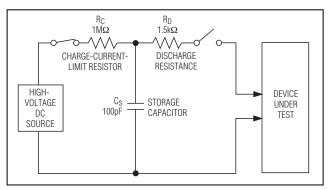

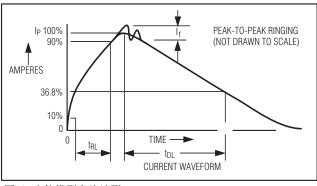

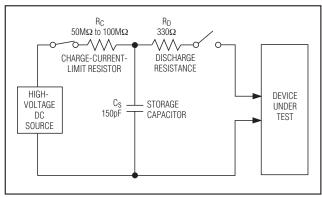

| ESD PROTECTION (D+, D-, VBCC                           | MP)               |                                                               |                       |      |       |       |

| Human Body Model                                       |                   | 1μF ceramic capacitors from VBCOMP and VCC to GND             |                       | ±15  |       | kV    |

| IEC 61000-4-2 Air-Gap Discharge                        |                   | 1μF ceramic capacitors from VBCOMP and V <sub>CC</sub> to GND |                       | ±12  |       | kV    |

| IEC 61000-4-2 Contact Discharge                        |                   | 1μF ceramic capacitors from VBCOMP and VCC to GND             |                       | ±8   |       | kV    |

| THERMAL SHUTDOWN                                       | •                 |                                                               | •                     |      |       | •     |

| Thermal-Shutdown Low-to-High                           |                   |                                                               |                       | +160 |       | °C    |

| Thermal-Shutdown High-to-Low                           |                   |                                                               |                       | +140 |       | °C    |

| CRYSTAL OSCILLATOR SPECIF                              | CATIONS (X        | I, XO)                                                        | •                     |      |       |       |

| XI Input High Voltage                                  |                   |                                                               | 2/3 x V <sub>CC</sub> |      | Vcc   | V     |

| XI Input Low Voltage                                   |                   |                                                               |                       |      | 0.4   | V     |

| XI Input Current                                       |                   |                                                               |                       |      | 10    | μΑ    |

| XI, XO Input Capacitance                               |                   |                                                               |                       | 3    |       | рF    |

| VBCOMP COMPARATOR SPECIF                               | ICATIONS          |                                                               |                       |      |       |       |

| VBCOMP Comparator Threshold                            | V <sub>TH</sub>   |                                                               | 1.0                   | 2.0  | 3.0   | V     |

| VBCOMP Comparator Hysteresis                           | V <sub>H</sub> YS |                                                               |                       | 375  |       | mV    |

| VBCOMP Comparator Input<br>Impedance                   | R <sub>IN</sub>   |                                                               | 100                   |      |       | kΩ    |

# SPI接口的USB外设/主机控制器

#### **TIMING CHARACTERISTICS**

$(V_{CC} = +3V \text{ to } +3.6V, V_L = +1.4V \text{ to } +3.6V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V, V_L = +2.5V, T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER                                  | SYMBOL                    | CONDITIONS                                      | MIN  | TYP | MAX | UNITS |

|--------------------------------------------|---------------------------|-------------------------------------------------|------|-----|-----|-------|

| USB TRANSMITTER TIMING CHA                 | RACTERIST                 | ICS (FULL-SPEED MODE)                           | •    |     |     | •     |

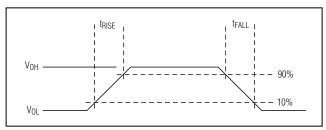

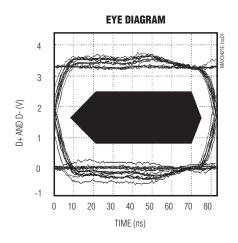

| D+, D- Rise Time                           | trise                     | C <sub>L</sub> = 50pF, Figures 8 and 9          | 4    |     | 20  | ns    |

| D+, D- Fall Time                           | tfall                     | C <sub>L</sub> = 50pF, Figures 8 and 9          | 4    |     | 20  | ns    |

| Rise-/Fall-Time Matching                   |                           | C <sub>L</sub> = 50pF, Figures 8 and 9 (Note 4) | 90   |     | 110 | %     |

| Output-Signal Crossover Voltage            |                           | C <sub>L</sub> = 50pF, Figures 8 and 9 (Note 4) | 1.3  |     | 2.0 | V     |

| USB TRANSMITTER TIMING CHA                 | ARACTERIST                | TICS (HOST LOW-SPEED MODE)                      |      |     |     |       |

| D+, D- Rise Time                           | trise                     | 200pF ≤ C <sub>L</sub> ≤ 600pF, Figures 8 and 9 | 75   |     | 300 | ns    |

| D+, D- Fall Time                           | tfall                     | 200pF ≤ C <sub>L</sub> ≤ 600pF, Figures 8 and 9 | 75   |     | 300 | ns    |

| Rise-/Fall-Time Matching                   |                           | 200pF ≤ C <sub>L</sub> ≤ 600pF, Figures 8 and 9 | 80   |     | 120 | %     |

| Output-Signal Crossover Voltage            |                           | 200pF ≤ C <sub>L</sub> ≤ 600pF, Figures 8 and 9 | 1.3  |     | 2.0 | V     |

| SPI BUS TIMING CHARACTERIS                 | TICS (V <sub>L</sub> = 2. | 5V) (Figures 10 and 11) (Note 5)                |      |     |     |       |

| Carial Clask (CCL K) Dariad (Nata C)       |                           | V <sub>L</sub> > 2.5V                           | 38.4 |     |     |       |

| Serial Clock (SCLK) Period (Note 6)        | t <sub>CP</sub>           | V <sub>L</sub> = 1.4V                           | 77.7 |     |     | ns    |

| SCLK Pulse-Width High                      | tch                       |                                                 | 17   |     |     | ns    |

| SCLK Pulse-Width Low                       | tcL                       |                                                 | 17   |     |     | ns    |

| SS Fall to MISO Valid                      | tcss                      |                                                 | 20   |     |     | ns    |

| SS Leading Time Before the First SCLK Edge | t∟                        |                                                 | 30   |     |     | ns    |

| SS Trailing Time After the Last SCLK Edge  | t <sub>T</sub>            |                                                 | 30   |     |     | ns    |

| Data-In Setup Time                         | t <sub>DS</sub>           |                                                 | 5    |     |     | ns    |

| Data-In Hold Time                          | tDH                       |                                                 | 10   |     |     | ns    |

| SS Pulse High                              | tcsw                      |                                                 | 200  |     |     | ns    |

| SCLK Fall to MISO Propagation<br>Delay     | t <sub>DO</sub>           |                                                 | 14.2 |     |     | ns    |

| SCLK Fall to MOSI Propagation Delay        | tDI                       |                                                 | 14.2 |     |     | ns    |

| SCLK Fall to MOSI Drive                    | ton                       |                                                 | 3.5  |     |     | ns    |

| SS High to MOSI High Impedance             | toff                      |                                                 |      |     | 20  | ns    |

| SUSPEND TIMING CHARACTERI                  | STICS                     |                                                 |      |     |     |       |

| Time-to-Enter Suspend                      |                           | PWRDOWN = 1 to oscillator stop                  |      |     | 5   | μs    |

| Time-to-Exit Suspend                       |                           | PWRDOWN = 1 to 0 to OSCOKIRQ (Note 7)           |      | 3   |     | ms    |

**Note 3:** Parameters are 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

Note 4: Guaranteed by bench testing. Limits are not production tested.

**Note 5:** At  $V_L = 1.4V$  to 2.5V, derate all the SPI timing characteristics by 50%. Not production tested.

Note 6: The minimum period is derived from SPI timing parameters.

Note 7: Time-to-exit suspend is dependent on the crystal used.

# SPI接口的USB外设/主机控制器

#### 测试电路和时序图

图8. 上升和下降时间

图9. D+/D-交流测量时的负载情况

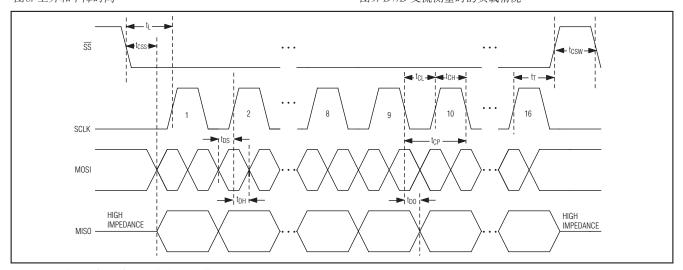

图10. SPI总线时序图(全双工模式, SPI模式(0,0))

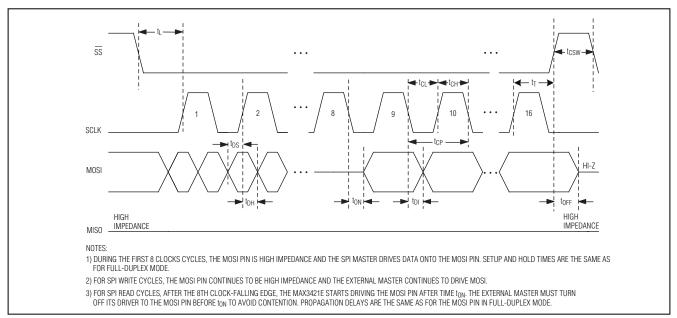

图11. SPI总线时序图(半双工模式, SPI模式(0,0))

### SPI接口的USB外设/主机控制器

典型工作特性

$(V_{CC} = +3.3V, V_L = +3.3V, T_A = +25^{\circ}C.)$

#### 详细说明

MAX3421E包含了用来实现USB 2.0标准全速USB外设或全/低速主机所需的所有数字逻辑和模拟电路。通过写MODE寄存器(R27)中的HOST位,可以选择MAX3421E工作在主机或外设方式。MAX3421E内置有USB收发器,并在D+、D-和VBCOMP引脚上集成了±15kV的ESD保护。D+线上集成了可切换的1.5kΩ上拉电阻,D+和D-线上集成了可切换的15kΩ下拉电阻。任何SPI主控制器都可通过SPI从器件接口与MAX3421E通信(工作于SPI模式(0,0)或(1,1))。SPI主控制器通过读写MAX3421E内部的寄存器对其进行访问。要完成一次典型的数据传送,首先需要写一个字节来设定寄存器地址和传送方向,然后就是要读出或写人目标寄存器或内部FIFO的数据字节。

在外设模式下,MAX3421E包含384字节的端点缓冲存储器,用于以下端点:

- EPO: 64字节的双向CONTROL端点

- EP1: 2 x 64字节的双缓存BULK/INT OUT端点

- EP2: 2 x 64字节的双缓存BULK/INT IN端点

- EP3: 64字节BULK/INT IN端点

选择EP1、EP2、EP3作为BULK还是INTERRUPT端点,完全取决于枚举过程中SPI主控制器返回给USB主机的端点描述符。

在主机模式下,MAX3421E包含256字节的发送和接收FIFO存储器:

- SNDFIFO: 发送FIFO——双缓冲64字节FIFO

- RCVFIFO: 接收FIFO——双缓冲64字节FIFO

主机FIFO能够以全速或低速向外设发送SETUP、BULK、INTERRUPT和ISOCHRONOUS请求。MAX3421E能够接纳直接接人或通过USB集线器接入的低速设备。由于大部分内部管理任务由MAX3421E完成,其编程非常容易。SPI主控制器作为一个典型主机的操作就简化为:设置设备地址和端点,发送一个包并等待表明完成的中断。然后检查传送结果标志位以确定外设的响应。它自动生成帧标识(全速SOF包或低速保持脉冲),并在相对于这些标志恰当的时刻分发包。

MAX3421E的寄存器组和SPI接口按照降低SPI通信量的目标进行了优化。当需要SPI主控制器提供USB服务时,中断输出INT向其发出信号,例如当有包到达、有包发出或主机挂起或恢复总线活动时。双缓冲FIFO允许USB和SPI接口同时传送数据,有助于保证带宽。

## SPI接口的USB外设/主机控制器

#### $V_{CC}$

施加3.3V电源于 $V_{CC}$ ,以驱动USB收发器和数字逻辑工作。尽量靠近 $V_{CC}$ 引脚,用一只 $1.0\mu$ F的陶瓷电容旁路 $V_{CC}$ 到GND。

#### $V_I$

$V_L$ 是SPI接口和所有其它数字输入及输出的参考电平。可将 $V_L$ 连接到系统的逻辑电源。由于内部电平转换器和 $V_L$ 引脚的存在,SPI接口和所有通用输入及输出能够工作在 1.4V至 3.6V的系统电压下。

#### **VBCOMP**

MAX3421E内部集成了一个USB  $V_{BUS}$ 检测器,VBCOMP是该检测器的输入。VBCOMP引脚可承受高达6V的输入电压。用一只 $1.0\mu$ F陶瓷电容旁路 VBCOMP到GND。VBCOMP在芯片内部被连接至一个电压比较器,以便SPI主控制器检测(通过中断或查询寄存器位)  $V_{BUS}$ 的加电情况。VBCOMP不作为任何MAX3421E内部电路的电源。VBCOMP通过 $R_{IN}$ 下拉至地(见Electrical Characteristics)。

#### 外设模式下的VBCOMP

VBCOMP在芯片内部被连接至一个电压比较器,以便SPI 主控制器检测VBUS的加电情况。根据USB 2.0规范,自供电的USB设备在USB主机关闭VBUS电源后,必须切断D+上的 $1.5k\Omega$ 上拉电阻。利用USBCTL寄存器(R15)中的VBGATE位,MAX3421E内部逻辑可以选择自动切断D+上的 $1.5k\Omega$ 上拉电阻。USBCTL寄存器(R15)中的VBGATE和CONNECT位,再加上VBCOMP比较器的输出(VBUS\_DET),三者共同控制着这个 $V_{CC}$ 和D+间的上拉电阻,如表3和功能框图所示。注意,如果VBGATE=1且VBUS\_DET=0,那么无论CONNECT位的设置如何,上拉电阻都会被断开。如果MAX3421E所在的设备是由总线供电的(通过连接至 $V_{CC}$ 的+3.3V稳压器),MAX3421E的VBCOMP输入可作为通用输入使用。有关这种用法的详情请见应用信息部分。

#### 表3. 外设模式下内部上拉电阻的控制

| CONNECT | VBGATE | VBUS_DET | PULLUP        |

|---------|--------|----------|---------------|

| 0       | Χ      | X        | Not Connected |

| 1       | 0      | X        | Connected     |

| 1       | 1      | 0        | Not Connected |

| 1       | 1      | 1        | Connected     |

#### 主机模式下的VBCOMP

MAX3421E用在主机模式时无需检测V<sub>BUS</sub>状态。在此情况下,VBCOMP输入可作为通用输入使用。

#### D+和D-

内部USB全/低速收发器通过双向数据引脚D+和D-引出。 这些引脚上集成了±15kV ESD保护。D+和D-应通过33Ω ±1%串联电阻连接到"B"型USB连接器。

#### 外设模式下的D+和D-

外设模式下D+和D-通过串联电阻连接到"B"型USB连接器。可切换的1.5kΩ上拉电阻在芯片内部连接至D+。

#### 主机模式下的D+和D-

主机模式下D+和D-通过串联电阻连接到 "A"型USB连接器。可切换的15kΩ下拉电阻在芯片内部连接至D+和D-。MODE寄存器(R27)中的DPPULLDN和DMPULLDN位控制着D+和D-到GND之间的连接。作为主机使用时,将这些位设为1,接通下拉电阻。当有外设被接人或拆除时,主机中断位CONNIRQ可向SPI主控制器发出告警。

#### XI和XO

XI和XO引脚用来将一个外部的12MHz晶体连接至内部振荡电路。XI是晶体振荡器的输入,XO是输出。将12MHz±0.25%的并联谐振晶体的一端连接至XI,另一端接至XO。在XI和XO上对地连接负载电容(最大20pF)。也可用一个外部的12MHz±0.25%时钟驱动XI。如果用外部时钟驱动XI,则浮空XO。外部时钟必须满足Electrical Characteristics表中所描述的电压特性。内部逻辑是单沿触发的。外部时钟应该具有标称50%的占空比。

### SPI接口的USB外设/主机控制器

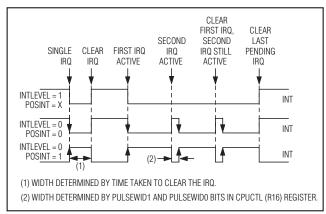

图12. 不同INTLEVEL和POSINT位设置时INT引脚的表现

#### RES

驱动 $\overline{\text{RES}}$ 为低可触发MAX3421E的芯片复位。芯片复位将除PINCTL (R17)、USBCTL (R15)和SPI逻辑之外的所有寄存器置为各自的默认状态。芯片复位期间所有FIFO的内容未知。驱动 $\overline{\text{RES}}$ 为高电平可使MAX3421E脱离芯片复位。 $\overline{\text{RES}}$ 脉冲最短可至200ns。关于MAX3421E的复位特性参见器件复位部分。

#### INT

当有USB事件发生,需要SPI主控制器注意时,MAX342IE 通过INT输出引脚发出中断信号。还可以将INT配置为当有任何通用输入(GPIN0-GPIN7)被触发时(详情请见 GPIN7-GPIN0部分)发出中断。SPI主控制器必须将 CPUCTL寄存器(R16)中的IE位置位方可激活INT功能。若 IE位被清零,INT不工作(电平模式下为开路,负沿模式为高,正沿模式为低)。INT在上电伊始或芯片复位后也处于不工作状态(IE = 0)。

INT引脚可以设置为推挽式或漏极开路输出。置位PINCTL 寄存器(R17)中的INTLEVEL位可将INT编程为低电平有效的漏极开路输出。这种配置需要外部到V<sub>L</sub>的上拉电阻。在电平模式下,若有任何中断标志被置位,MAX3421E就会驱动INT为低。如果有多个中断未处理,则INT只有在SPI主控制器清除了最后一个有效的中断请求后才会变为无效(图12)。在电平模式下,PINCTL寄存器(R17)中的POSINT位对于INT没有作用。

表4. 由PULSEWID1和PULSEWID0配置的INT输出脉宽

| PULSEWID1 | PULSEWID0 | INT PULSE WIDTH (μs) |

|-----------|-----------|----------------------|

| 0         | 0         | 10.6                 |

| 0         | 1         | 5.3                  |

| 1         | 0         | 2.6                  |

| 1         | 1         | 1.3                  |

清零INTLEVEL位则将INT编程为边沿模式的推挽式输出。通过PINCTL寄存器(R17)中的POSINT位可编程设定有效沿。在边沿模式中,若有中断请求发生,或者某个中断请求已被清除,但仍存在其他未处理的中断请求,MAX3421E就会产生一个参照于 $V_L$ 的跳变沿(图12)。在PINCTL寄存器(R17)中置位POSINT位则选择INT为上升沿有效,清零POSINT位则选择下降沿有效INT。CPUCTL寄存器(R16)中的PULSEWID1和PULSEWID0位可控制边沿模式下INT脉冲的宽度,如表4所示。

#### GPIN7-GPIN0

SPI主控制器通过读取寄存器IOPINS1 (R20)的第7位到第4位采样GPIN3-GPIN0的状态。GPIN7-GPIN4的状态通过读取寄存器IOPINS2 (R21)的第7位到第4位进行采样。向这些位写数据不会有任何作用。

无论外设和主机模式,都由三个寄存器控制来自于GPIN7-GPIN0的八个中断请求。寄存器GPINIRQ (R22)含有八个GPIN输入的中断请求标志。寄存器GPINIEN (R23)含有八个GPIN中断各自独立的中断使能位。寄存器GPINPOL (R24)控制着八个GPIN中断的边沿极性。八个GPIN中断被加入MAX3421E中断系统中,当有使能中断被触发时,即可从INT输出引脚发出中断信号。还可以将GPIN中断分离出来,单独通过GPX引脚输出,只需设置SEPIRQ = 1即可。这样可以减小中断服务的延迟,因为GPX输出的中断源是已知的,只需查询GPINIRQ寄存器便可确定中断源。注意GPINPOL中的位控制使内部"未处理中断"触发器置位的GPIN跳变沿,而非INT输出。INT引脚的输出特性受控于INTLEVEL和POSINT寄存器位,正如MAX3420E一样。当GPX引脚被配置成GPIN INT时,其输出特性和INT引脚一样。

### MAX3421F

### SPI接口的USB外设/主机控制器

#### GPOUT7-GPOUT0

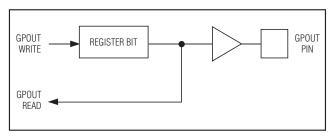

SPI主控制器通过写寄存器IOPINS1 (R20)的第3位到第0位控制GPOUT3-GPOUT0的状态。GPOUT7-GPOUT4的状态可通过写寄存器IOPINS2 (R21)的第3位到第0位进行控制。GPOUT7-GPOUT0的逻辑电平以 $V_L$ 电压为参考。如图13所示,在读取GPOUT7-GPOUT0所对应的位时,返回的是内部寄存器位的状态,并非实际引脚的状态。在对某输出引脚执行"读-修改-写"操作时(例如LED的闪烁)该特点很有用,因为输出引脚上的负载不会影响寄存器的逻辑状态。

#### **GPX**

GPX是推挽输出,内部由一个四通道多路复用器选择其输出信号。GPX的逻辑电平以 $V_L$ 为参考。SPI主控制器通过PINCTL寄存器(R17)中的GPXA和GPXB位选择五种内部信号之一,通过GPX引脚输出,如表5所示。

#### 表5. GPX输出状态和GPXB、GPXA位的关系

| GPXB | GPXA | GPX PIN OUTPUT          |

|------|------|-------------------------|

| 0    | 0    | OPERATE (Default State) |

| 0    | 1    | VBUS_DET                |

| 1    | 0    | BUSACT/INIRQ*           |

| 1    | 1    | SOF                     |

- \*如果SEPIRO = 1。

- OPERATE: 当MAX3421E在上电后或RES复位后进人工作状态时该信号变高。OPERATE在RES输入为高且内部上电复位(POR)信号处于非触发状态时有效。OPERATE是GPX的默认输出。

- VBUS\_DET: VBUS\_DET是VBCOMP比较器的输出。 通过该信号用户可以直接监视V<sub>RUS</sub>的状态。

- BUSACT: USB总线活动状态指示信号(高有效)。当 USB总线上有通信时该信号有效。只要监测到SYNC域, BUSACT信号即被置位。BUSACT在总线复位期间,或 者经历了32位长的J状态后变低。

图13. GPOUT3-GPOUT0上的读写操作

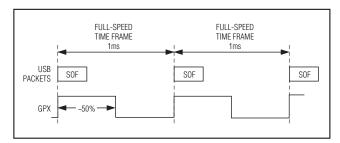

图14. SOF模式下的GPX输出

图15. MAX3421E SPI数据引脚在全双工(上图)和半双工(下图) 模式下的工作情况

### SPI接口的USB外设/主机控制器

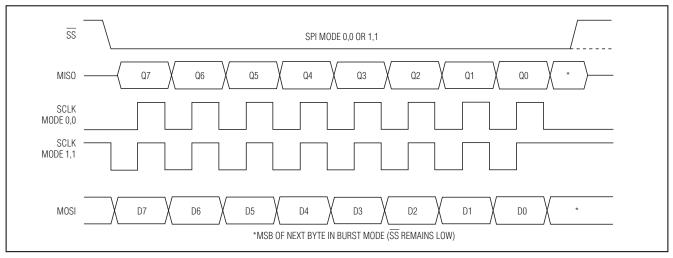

图16. SPI时钟模式

- INIRQ: 当MODE寄存器(R27)中的SEPIRQ位被置位时, BUSACT信号被从INT输出中去掉,如果GPX[B:A]=10, GPX被作为专用于GPIN中断的IRQ输出引脚。在此模 式下,GPIN中断仅出现在GPX引脚,而不再出现于 INT输出引脚。

- SOF: 方波信号, 正沿指示USB帧的起始点(图14)。

#### MOSI (主出从入)和MISO (主入从出)

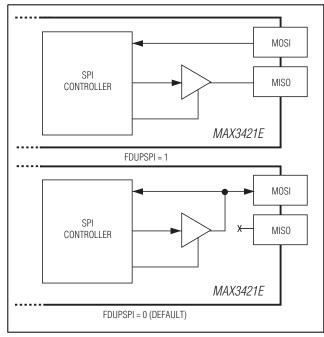

SPI数据引脚MOSI和MISO的工作状态受控于寄存器位FDUPSPI (全双工SPI)的设置。图15显示了两种FDUPSPI 位设置所对应的配置。

全双工模式下(FDUPSPI = 1),MOSI和MISO是独立的,MISO引脚仅当 $\overline{SS}$ 为低时才有驱动。在此模式下,开始的八个SCLK沿( $\overline{SS}$  = 0之后)将命令字节通过MOSI移人MAX3421E,同时,八个USB状态位通过MISO被移出MAX3421E。如果是SPI写周期,紧随命令字节之后的所有字节都通过MOSI被移入MAX3421E,同时,从MISO移出零。如果是SPI读周期,发完命令之后,数据字节通过MISO移出MAX3421E,而MOSI上的数据被忽略。SPI周期结束后( $\overline{SS}$  = 1),MISO输出变为三态。

在半双工模式下,MOSI是双向引脚,MISO引脚为三态。这可以为SPI接口省下一个引脚。由于共用数据引脚的关系,该模式不能随着命令字节送人MAX3421E的同时提供八个USB状态位(图6和7)。半双工模式下MISO引脚可以浮空。

#### SCLK (串行时钟)

SPI主控制器为MAX3421E提供SCLK信号来驱动SPI接口。对SCLK没有低频限制,最高频率可至26MHz。MAX3421E在SCLK的下降沿改变其输出数据(MISO),在SCLK的上升沿采样输入数据(MOSI)。当 $\overline{SS}$ 为高时MAX3421E忽略SCLK跳变沿。空闲时的SCLK电平可以为高或低,取决于SPI工作模式(图16)。

#### SS (从选择)

仅当SS为低时,MAX3421E的SPI接口才进入有效状态。当SS为高时,MAX3421E置SPI输出引脚为三态,并复位内部SPI逻辑。如果SS在一个完整字节被移入之前就变高,那么这个不完整的字节将被丢掉。SPI主控制器可以在发完第一个8位数据(命令字节)之后就终止SPI周期。该特性可以在全双工系统中用来取回USB状态位(图6和图7),而无需发送或接收SPI数据。

#### 应用信息

#### SPI接口

MAX3421E工作在SPI从模式。要访问其内部寄存器,SPI 主控制器需首先写一个SPI命令字节,随后就可对所寻址的寄存器进行读或写操作(详见*寄存器说明*)。所有SPI传送都是MSB在前。时钟由外部SPI主控制器提供,输入MAX3421E的SCLK引脚。时钟频率可介于直流至26MHz间。位传送发生在SCLK的正沿。MAX3421E计算输入的位数并将其划分成字节。如果在SS变高时输入的位数不足8位,MAX3421E会丢掉这个不完整字节。

### SPI接口的USB外设/主机控制器

MAX3421E的SPI接口可以无需任何调整工作在两种SPI模式下(CPOL=0、CPHA=0)或(CPOL=1、CPHA=1)。无须通过模式位在这两种模式间进行选择,因为两种模式的时钟有效沿都是上升沿。这两种时钟模式示于图16。注意,两种模式下SCLK的空闲状态电平是不同的。图16所示为全双工模式,数据被同时移入和移出MAX3421E。

#### 半双工和全双工SPI工作模式

MAX3421E可被编程为半双工(一条双向数据线)或全双工(一条数据输入,一条数据输出)工作模式。SPI主控制器设置一个被称为FDUPSPI(全双工SPI)的寄存器位为1选择全双工,为0则选半双工。上电时的默认状态为半双工。

#### 全双工

若SPI主控制器设置FDUPSPI=1, SPI接口使用单独的数据引脚(MOSI和MISO)来发送和接收数据。由于采用了分离的数据引脚,数据位可以同时被移入和移出MAX3421E。MAX3421E利用该特性,在移入命令字节的同时移出8个USB状态位。图17显示了外设模式下移出的状态位,图18显示了主机模式下移出的状态位。

#### 由SPI从接口读取数据(MISO)

SPI主控制器按照以下步骤通过MAX3421E从器件接口读取数据:

- 1) SS为高时未选定MAX3421E, MISO输出为高阻。

- 2) 驱动SCLK至空闲态后,SPI主控制器驱动SS为低,选择MAX3421E。MAX3421E打开其MISO输出缓冲器,并将首个数据位(Q7)放到MISO输出上(图16)。

- 3) SPI主控制器向MAX3421E的MOSI引脚移入命令字节,同时从MAX3421E的MISO引脚移出USB状态位,所有数据移位发生在SCLK时钟的上升沿。MAX3421E在SCLK的下降沿改变其MISO输出数据。

- 4) 八个时钟周期后,主控制器可以驱动 SS 为高,取消对MAX3421E的选择,使其置MISO输出为三态。时钟的下降沿将后续数据字节的MSB放到MISO输出上(图16)。

- 5) 如果保持<del>SS</del>为低,并持续送SCLK脉冲给MAX3421E, 主控制器就可读出寄存器中的数据字节(突发模式)。 主控制器驱动<del>SS</del>为高可终止传输过程。主控制器必

须在下一次访问开始时(驱动 $\overline{SS}$ 为低)确保SCLK处于空闲态。全双工模式下,MAX3421E在从MISO移出数据时忽略MOSI上的数据。

#### 写SPI从接口(MOSI)

SPI主控制器按照以下步骤向MAX3421E从器件接口写数据:

- 1) SPI主控制器设置时钟为空闲态。由于SS为高,主控制器可以驱动MOSI输入。

- 2) SPI主控制器驱动 SS 为低,选定MAX3421E,然后将 首个数据位放到MOSI口线上。

- 3) 在SCLK时钟(由SPI主控制器提供)的上升沿,SPI主控制器将命令字节送人MAX3421E,同时,USB状态位也通过MAX3421E的MISO引脚输出。SPI主控制器在SCLK的下降沿改变其MOSI数据。

- 4) 八个时钟周期后,主控制器可驱动SS为高,以撤销对于MAX3421E的选定。

- 5) 若持续保持 SS 为低,通过连续发送 SCLK 脉冲,主控制器可以连续将多个数据字节写人 MAX3421E (突发模式)。主控制器驱动 SS 为高则终止传输过程。在下一次访问开始时(驱动 SS 为低),主控制器必需保证 SCLK处于空闲态。全双工模式下,MAX3421E在首个8位(命令字节)传输期间向MISO输出 USB 状态位,而接下来在 SPI 主控制器向 MOSI 送人数据字节时,MISO输出全为零。

#### 半双工

在上电初始,或者SPI主控制器清除FDUPSPI位时,MAX3421E工作于半双工模式。半双工模式下,MAX3421E 将其MISO引脚置为三态,而使MOSI引脚双向工作,这样就节省了SPI接口的一个引脚。半双工模式下可以使MISO引脚浮空。

由于半双工模式只有一个数据引脚,全双工模式中随着 SPI主控制器发送命令字节而出现的USB状态位不再出现。 半双工模式中,这些状态位只能作为一般的寄存器位进 行访问。

SPI主控制器必需双向操作MOSI引脚。按以下方式访问 MAX3421E内部寄存器:

## SPI接口的USB外设/主机控制器

图17. 全双工模式的SPI端口(外设模式)

图18. 全双工模式的SPI端口(主机模式)

- 1) SPI主控制器设置时钟为空闲态。由于SS为高,主控制器可以驱动MOSI引脚为任意状态。

- 2) SPI主控制器驱动 SS 为低,选择MAX3421E,然后将 首个数据位(MSB)放到MOSI口线上。

- 3) SPI主控制器打开其输出驱动器,在SCLK时钟的上升 沿将命令字节移人MAX3421E。SPI主控制器在SCLK 的下降沿改变其MOSI数据。

- 4) 八个时钟周期后,主控制器即可驱动SS为高,撤销对于MAX3421E的选择。