### Click here to ask an associate for production status of specific part numbers. Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

### **General Description**

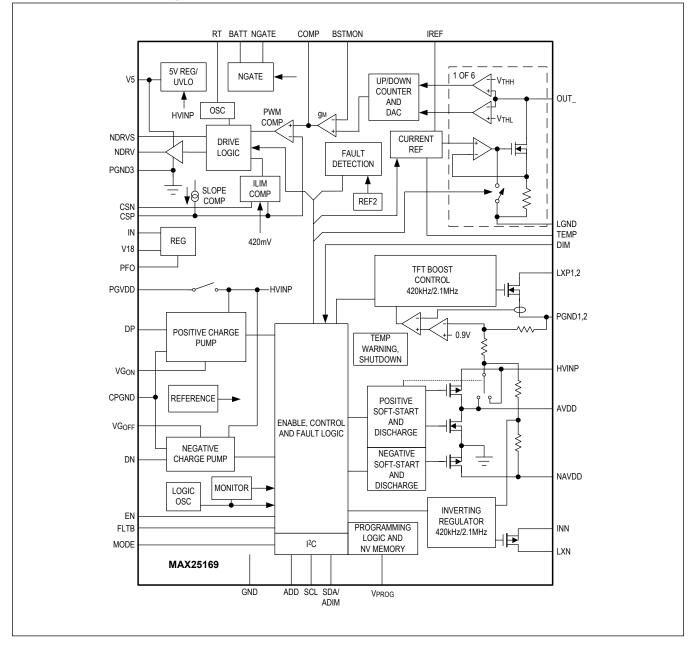

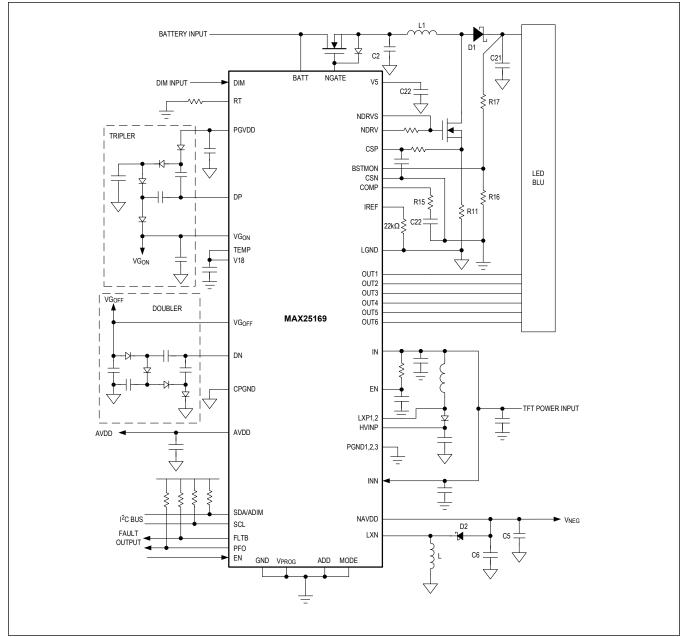

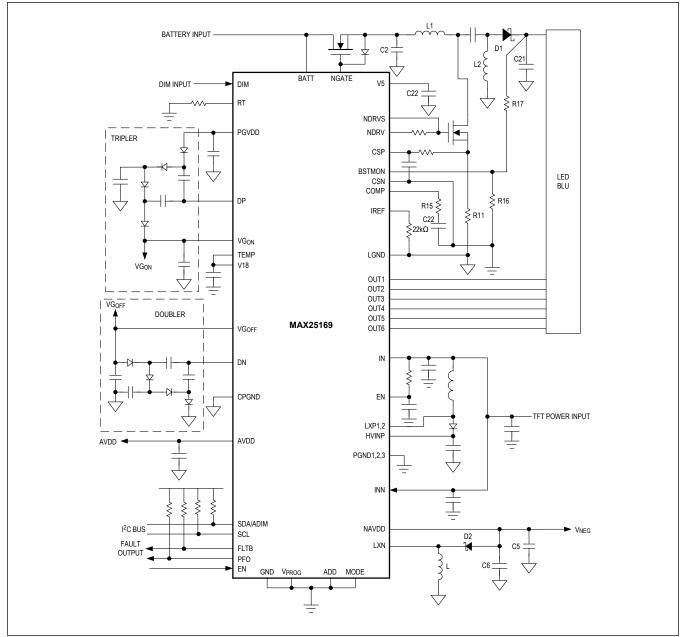

The MAX25169 is a highly integrated TFT power supply and LED backlight driver IC for automotive TFT-LCD applications. This IC integrates one boost converter, one inverting buck-boost converter, two gate-driver supplies, and a boost/SEPIC controller that can power 1 to 6 strings of LEDs in the display backlight.

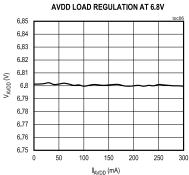

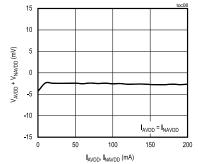

The source-driver power supplies consist of a boost converter which can provide up to +18V in unipolar mode and an inverting buck-boost converter that can generate a voltage down to -10.5V. The AVDD output can deliver up to 300mA at 13.5V, while NAVDD can provide up to 200mA. The positive source-driver supply-regulation voltage (V<sub>AVDD</sub>) is set using internal NV memory or through I<sup>2</sup>C. The negative source-driver supply voltage (V<sub>NAVDD</sub>) is always tightly regulated to -V<sub>AVDD</sub>. The source-driver supplies operate from an input voltage between 2.65V and 5.5V.

The gate-driver power supplies consist of regulated charge pumps that generate up to +31.5V and down to -18V and can deliver up to 15mA each.

The IC features a 6-string LED driver with input switch control (NGATE) that can power up to 6 strings of LEDs with 150mA (max) of current per string.

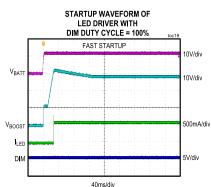

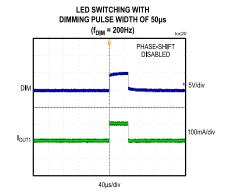

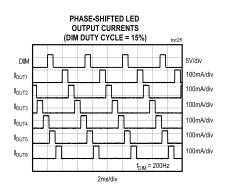

Logic-controlled and I<sup>2</sup>C-controlled pulse-width modulation (PWM) dimming are included, with minimum pulse widths as low as 300ns and the option of phase shifting the LED strings with respect to one another. When phase shifting is enabled, each string is turned on at a different time, reducing the input and output ripple, as well as audible noise. With phase shifting disabled, the current sinks turn on simultaneously and parallel connection of current sinks is possible.

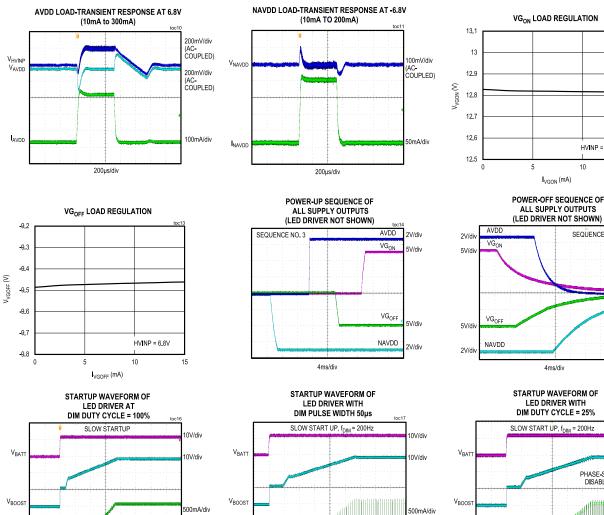

The startup and shutdown sequences for all power domains are controlled using one of the eight preset modes, which are selectable using internal nonvolatile memory or through the  $I^2C$  interface.

The MAX25169 is available in a 7mm x 7mm, 48-pin TQFN package with an exposed pad, and operates over the -40 $^{\circ}$ C to +125 $^{\circ}$ C ambient temperature range.

### **Applications**

- Automotive Dashboards

- Automotive Central Information Displays

- Automotive Head-Up Displays

- Automotive Navigation Systems

### **Benefits and Features**

- 4-Output TFT-LCD Bias Power

- 2.65V to 5.5V Input for the TFT-LCD Section

- Integrated 420kHz or 2.1MHz Boost and Buck-Boost Converters

- Positive and Negative 15mA Gate Voltage Regulators with Adjustable Output Voltage (Tripler/ Inverting Doubler)

- Flexible Sequencing

- · Undervoltage Detection on All Outputs

- Low-Quiescent-Current Standby Mode

- 6-Channel, 36V LED Backlight Driver

- NGATE Control for External NMOSFET Series

Switch

- Programmable nMOSFET Current Limit

- Up to 150mA Current per Channel

- 4.5V to 36V Input Voltage Range, 3V Operation after Startup

- Integrated Boost/SEPIC Controller (400kHz to 2.2MHz with Synchronization)

- Dimming Ratio 16,667:1 at 200Hz

- Adaptive Voltage Optimization to Reduce Power Dissipation in LED Current Sinks

- Open-String, Shorted-LED, and Short-to-GND Diagnostics

- Low EMI

- Phase-Shift Dimming of LED Strings

- Spread Spectrum on LED Driver and TFT Outputs

- Selectable Switching Frequency

- I<sup>2</sup>C Interface for Control and Diagnostics

- Fault Indication through the FLTB Pin and I<sup>2</sup>C

Nonvolatile Configuration Memory

- Overload and Thermal Protection

- ASIL B Compliant

- -40°C to +125°C Ambient Temperature Operation

- 7mm x 7mm, 48-Pin TQFN Package with Exposed Pad

- AEC-Q100 Grade 1

Ordering Information appears at end of data sheet.

19-101585; Rev 1; 6/23

© 2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

### **Simplified Block Diagram**

Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **TABLE OF CONTENTS**

| General Description                                  |

|------------------------------------------------------|

| Applications                                         |

| Benefits and Features                                |

| Simplified Block Diagram                             |

| Absolute Maximum Ratings                             |

| Package Information                                  |

| 48 TQFN                                              |

| Electrical Characteristics                           |

| Typical Operating Characteristics                    |

| Pin Configuration                                    |

| Pin Description                                      |

| Detailed Description                                 |

| Supply Voltages                                      |

| PFO Output                                           |

| TFT Power Section                                    |

| Source-Driver Power Supplies                         |

| AVDD Switch                                          |

| Gate-Driver Power Supplies                           |

| Sequencing                                           |

| Description of the LED Driver                        |

| Undervoltage Lockout                                 |

| Low-Voltage Operation                                |

| Oscillator Frequency/External Synchronization        |

| Spread-Spectrum Modulation                           |

| LED Forward Voltage                                  |

| LED Current Control                                  |

| Current-Mode DC-DC Controller                        |

| 9-Bit Digital-to-Analog Converter (DAC)              |

| Startup Sequence                                     |

| Stage 1                                              |

| Stage 2                                              |

| Stage 3                                              |

| Backlight Boost Startup                              |

| Open-LED Management and Overvoltage Protection (OVP) |

| Short-LED Detection                                  |

| Dimming                                              |

| Low-Dimming Mode                                     |

| Phase-Shift Dimming                                  |

| Automatic Fade-In/Fade-Out During Dimming            |

Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **TABLE OF CONTENTS (CONTINUED)**

| Disabling Individual Strings                                       | . 33 |

|--------------------------------------------------------------------|------|

| Hybrid Dimming                                                     | . 33 |

| Temperature Foldback                                               | . 34 |

| Fault Protection                                                   | . 36 |

| ASIL B Features                                                    | . 37 |

| Analog-to-Digital Converter (ADC)                                  | . 37 |

| Serial Interface                                                   | . 37 |

| Parity Checking                                                    | . 38 |

| Nonvolatile (NV) Memory                                            | . 38 |

| Autorefresh Function                                               | . 39 |

| BURN, REBOOT, and RESTART Commands                                 | . 39 |

| Register Map                                                       | . 40 |

| MAX25169                                                           | . 40 |

| Register Details                                                   | . 42 |

| Applications Information                                           | . 68 |

| TFT Power Section.                                                 | . 68 |

| AVDD Boost Converter                                               | . 68 |

| Boost Converter Inductor Selection                                 | . 68 |

| Boost Output-Filter Capacitor Selection                            | . 68 |

| Boost Converter External Diode Selection                           | . 68 |

| Setting the AVDD Voltage                                           | . 68 |

| NAVDD Inverting Regulator                                          | . 68 |

| NAVDD Regulator Inductor Selection                                 | . 68 |

| NAVDD External Diode Selection                                     | . 68 |

| NAVDD Output Capacitor Selection                                   | . 68 |

| Setting the VG <sub>ON</sub> and VG <sub>OFF</sub> Output Voltages | . 69 |

| LED Driver Section                                                 | . 69 |

| DC-DC Converter for LED Driver                                     | . 69 |

| Power-Circuit Design.                                              | . 69 |

| Boost Configuration                                                | . 69 |

| SEPIC Configuration                                                | . 70 |

| Current-Sense Resistor and Slope Compensation                      | . 71 |

| Output Capacitor Selection                                         | . 71 |

| External Switching-MOSFET Selection                                | . 72 |

| Rectifier Diode Selection                                          | . 72 |

| Feedback Compensation                                              | . 72 |

| Using NV Memory                                                    | . 73 |

| Typical Application Circuit                                        | . 75 |

| Basic Application Circuit                                          | . 75 |

|                                                                    |      |

Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **TABLE OF CONTENTS (CONTINUED)**

| SEPIC Application Circuit | 76 |

|---------------------------|----|

| Ordering Information      | 77 |

| Revision History          | 78 |

Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## LIST OF FIGURES

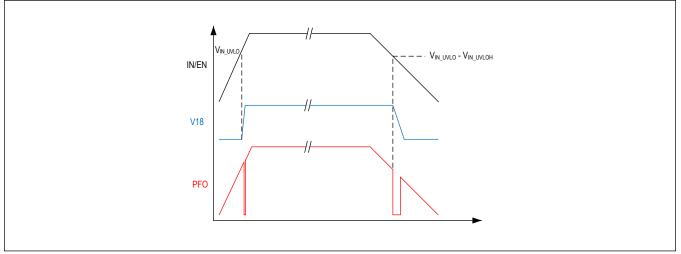

| Figure 1. PFO Waveform                                           | 25 |

|------------------------------------------------------------------|----|

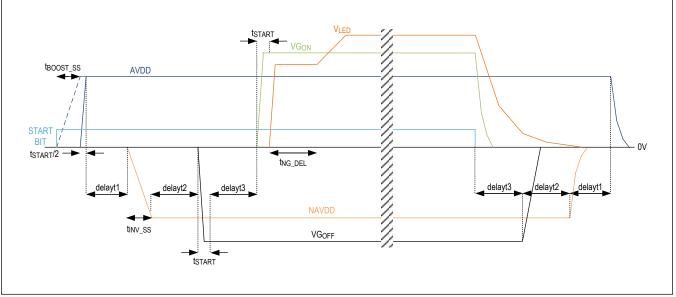

| Figure 2. Output Sequencing                                      | 27 |

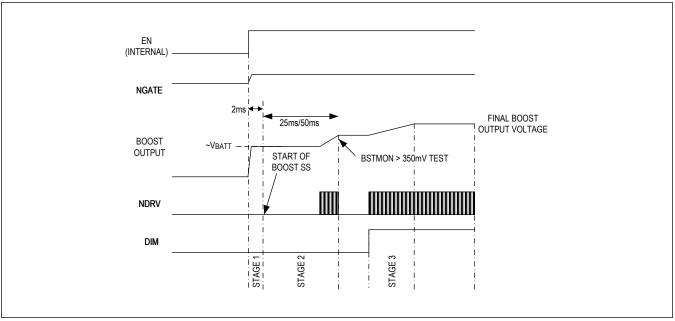

| Figure 3. Backlight Boost Startup                                | 30 |

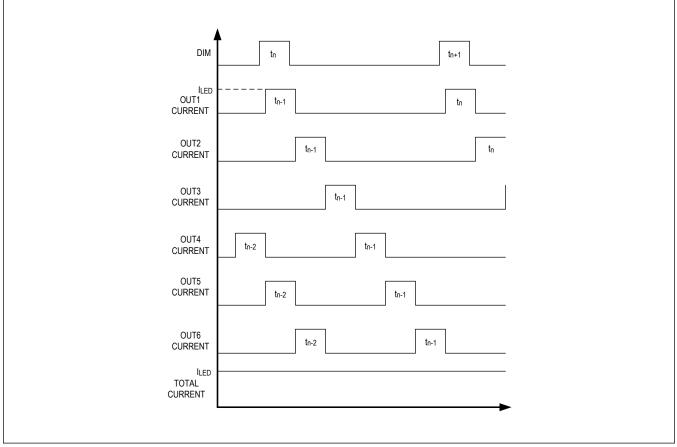

| Figure 4. Phase-Shifted Outputs                                  | 32 |

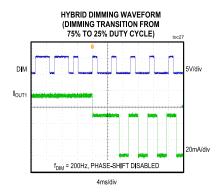

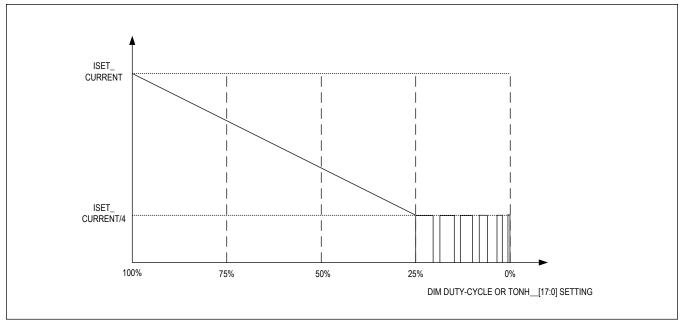

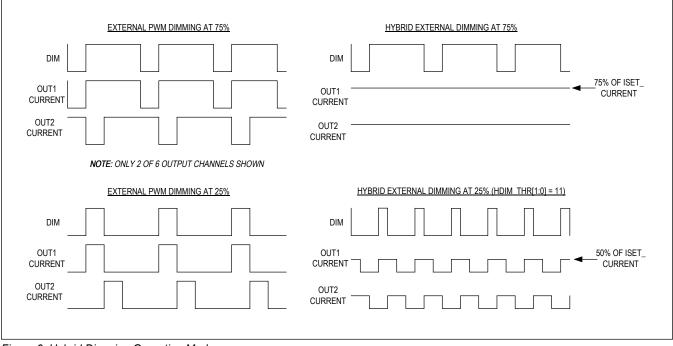

| Figure 5. Hybrid Dimming Operation with hdim_thr[1:0] = 10 (25%) | 34 |

| Figure 6. Hybrid Dimming Operation Modes                         | 34 |

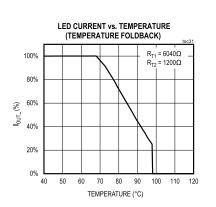

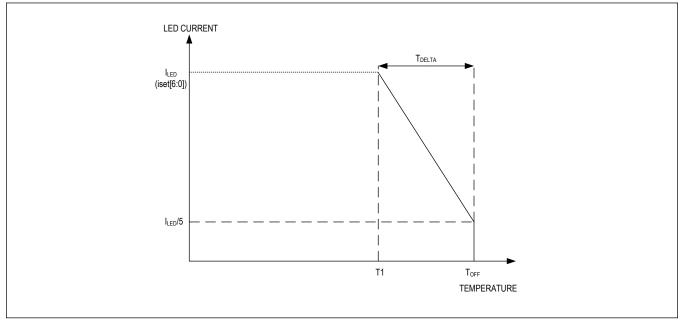

| Figure 7. Temperature Foldback Curve                             | 35 |

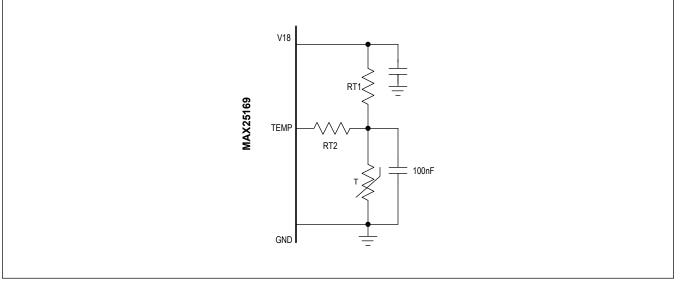

| Figure 8. TEMP External Circuitry                                | 36 |

Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## LIST OF TABLES

| Table 1. PFO Thresholds                | . 25 |

|----------------------------------------|------|

| Table 2. Sequencing                    | . 26 |

| Table 3. Temperature Foldback Examples | . 35 |

| Table 4. Add/Mode Pins                 | . 38 |

| Table 5. I <sup>2</sup> C Address      | . 38 |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

### **Absolute Maximum Ratings**

| BATT, OUT1-6, BSTMON to GND0.3V to +42V                 |

|---------------------------------------------------------|

| NGATE to BATT+6V                                        |

| NGATE to GND0.3V to +42V                                |

| IN, INN, FLTB, PFO, DIM, EN, SDA, SCL to GND0.3V to +6V |

| NDRV, NDRVS to GND0.3V to V5 + 0.3V                     |

| TEMP, MODE, CSP, COMP, IREF, RT, ADD to GND0.3V to      |

| V18 + 0.3V                                              |

| HVINP to GND0.3V to +22V                                |

| LXP to GND0.3V to +30V                                  |

| LXP1/2, PGND1/2 RMS Total Current Rating                |

| V5 to GND0.3V to MIN (6, HVINP + 0.3)V                  |

| V18 to GND0.3V to MIN (2.2, IN + 0.3)V                  |

| PGVDD, AVDD, DP, DN to GND0.3V to HVINP + 0.3V          |

| LXN to INN22V to +0.3V                                  |

| LXN, INN RMS Current Rating 1.6A                        |

| VG <sub>ON</sub> to GND0.3V to +40V                     |

| V <sub>PROG</sub> to GND0.3V to +12V<br>NAVDD to GNDV <sub>V18</sub> - 16V to V <sub>V18</sub> + 0.3V<br>VG <sub>OFF</sub> to GNDV <sub>V18</sub> - 22V to V <sub>V18</sub> + 0.3V<br>GND to PGND1, PGND2, PGND30.3V to +0.3V<br>GND to LGND0.3V to +0.3V |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND to CPGND                                                                                                                                                                                                                                              |  |

| GND to CSN0.3V to +0.3V<br>Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                                                                                                                          |  |

| 48-Pin TQFN-EP (derate 43mW/°C above +70°C), (multilayer board)                                                                                                                                                                                           |  |

| Operating Temperature Range40°C to +125°C<br>Junction Temperature+150°C                                                                                                                                                                                   |  |

| Storage Temperature Range65°C to +150°C<br>Lead Temperature (soldering, 10s)+300°C                                                                                                                                                                        |  |

| Soldering Temperature (reflow)+260°C                                                                                                                                                                                                                      |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **48 TQFN**

| Package Code                          | T4877+9C       |

|---------------------------------------|----------------|

| Outline Number                        | <u>21-0144</u> |

| Land Pattern Number                   | <u>90-0464</u> |

| Thermal Resistance, Four-Layer Board: |                |

| Junction to Ambient $(\theta_{JA})$   | 23.3°C/W       |

| Junction to Case ( $\theta_{JC}$ )    | 1°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## **Electrical Characteristics**

| PARAMETER                                                   | SYMBOL                | CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------------------|-----------------------|------------------------------------------------|------|-----|------|-------|

| INPUT SUPPLY                                                |                       |                                                |      |     |      |       |

| IN, INN Voltage Range                                       | V <sub>IN_RNG</sub>   |                                                | 2.65 |     | 5.5  | V     |

| IN UVLO Threshold,<br>Rising                                | V <sub>IN_UVLOR</sub> | IN voltage rising                              | 2.4  | 2.5 | 2.57 | V     |

| IN UVLO Threshold,<br>Falling                               | VIN_UVLOF             |                                                | 2.3  |     | 2.5  | V     |

| PFO Threshold                                               | V <sub>PFO</sub>      | IN falling, pfo_th = 0, PFO output goes<br>low | 2.4  | 2.5 | 2.6  | V     |

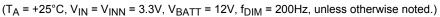

| Total Input Shutdown<br>Current (IN + INN +<br>HVINP + LXP) | IN_SHDN               | EN = GND, T <sub>A</sub> = +25°C               |      | 3.5 | 15   | μA    |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

| PARAMETER                                                    | SYMBOL                          | CON                                                                                                                          | DITIONS                              | MIN   | TYP  | MAX  | UNITS |

|--------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|------|------|-------|

| IN + INN Quiescent<br>Current                                | I <sub>IN_Q</sub>               | V <sub>EN</sub> = 3.3V, no swi                                                                                               | tching                               |       | 2    | 4    | mA    |

| V18 REGULATOR                                                | •                               |                                                                                                                              |                                      |       |      |      |       |

| V18 Output Voltage                                           | V <sub>V18_ACC</sub>            | No load on V18                                                                                                               |                                      | 1.72  | 1.8  | 1.88 | V     |

| V18 Current Limit                                            | I <sub>LIM_V18</sub>            | V <sub>V18</sub> = 1V                                                                                                        |                                      | 50    |      |      | mA    |

| V18 Undervoltage<br>Lockout                                  | V <sub>V18</sub> _UVLO          | V18 voltage rising                                                                                                           |                                      | 1.6   | 1.65 | 1.7  | V     |

| V18 Undervoltage<br>Hysteresis                               | V <sub>V18_UVLO_H</sub><br>YS   |                                                                                                                              |                                      |       | 150  |      | mV    |

| V18OOR Diagnostic<br>Levels                                  |                                 |                                                                                                                              |                                      |       | ±8   |      | %     |

| TFT POWER SECTION /                                          | OSCILLATOR                      |                                                                                                                              |                                      |       |      |      |       |

| Operating Frequency                                          | <b>f</b> BOOSTH                 | f <sub>SW</sub> bit = 0, dither d                                                                                            | isabled                              | 1950  | 2100 | 2250 | - kHz |

|                                                              | <b>f</b> BOOSTL                 | f <sub>SW</sub> bit = 1, dither d                                                                                            | isabled                              | 380   | 420  | 460  |       |

| Frequency Dither                                             | <b>f</b> BOOSTD                 |                                                                                                                              |                                      |       | ±6   |      | %     |

| TFT POWER SECTION /                                          | BOOST REGUL                     | ATOR                                                                                                                         |                                      |       |      |      | _     |

| HVINP Output Voltage                                         | V <sub>HVINP</sub>              | dis_navdd = 0                                                                                                                |                                      | 4.9   |      | 10.5 | - v   |

| Range                                                        | * HVINP                         | dis_navdd = 1                                                                                                                |                                      | 11.7  |      | 18   | v     |

| AVDD Adjustment Step<br>Size                                 | V <sub>STEP</sub>               |                                                                                                                              |                                      |       | 0.1  |      | V     |

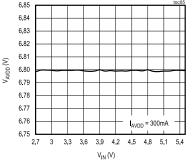

| AVDD Output<br>Regulation                                    | V <sub>AVDD_ACC</sub>           | avdd[5:0] = 0x1A, dis_navdd = 0                                                                                              |                                      | 6.66  | 6.8  | 6.94 | V     |

| LXP Maximum Duty                                             |                                 | 420kHz switching fr                                                                                                          | requency                             | 91.75 | 95   |      | - %   |

| Cycle                                                        | D <sub>LXP_MAX</sub>            | 2.1MHz switching fi                                                                                                          | requency                             | 91.75 | 95   |      | 70    |

| Low-Side Switch On-<br>Resistance                            | R <sub>ON_LS_LXP</sub>          | I <sub>LXP</sub> = 0.1A                                                                                                      |                                      |       | 0.1  | 0.2  | Ω     |

| LXP Leakage Current                                          | ILEAK_LXP                       | $V_{EN}$ = 0V, $V_{LXP}$ = 7                                                                                                 | 15V                                  |       |      | 6    | μA    |

|                                                              | ILIMPHB                         | dis_navdd = 0                                                                                                                | Duty cycle = 80%,<br>Lxp_Lim_Low = 0 | 1.5   | 1.8  | 2.1  |       |

| LXP Current Limit                                            | ILIMPLB                         |                                                                                                                              | Duty cycle = 80%,<br>Lxp_Lim_Low = 1 |       | 1    |      | - A   |

|                                                              | ILIMPHU                         | dis_navdd = 1                                                                                                                | Duty cycle = 80%,<br>Lxp_Lim_Low = 0 | 2.3   | 2.7  | 3.2  |       |

|                                                              | ILIMPLU                         |                                                                                                                              | Duty cycle = 80%,<br>Lxp_Lim_Low = 1 |       | 1.35 |      |       |

| Soft-Start Period                                            | tBOOST_SS                       | Current-limit ramp                                                                                                           |                                      |       | 5    |      | ms    |

| TFT POWER SECTION /                                          | INVERTING REC                   | GULATOR                                                                                                                      |                                      |       |      |      |       |

| LXN Maximum Duty<br>Cycle                                    | D <sub>LXN_MAX</sub>            | f <sub>SW</sub> = 420kHz or 2.                                                                                               | 1MHz                                 | 91.75 | 95   |      | %     |

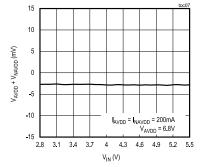

| V <sub>AVDD</sub> + V <sub>NAVDD</sub><br>Regulation Voltage | V <sub>NAVDD_AVD</sub><br>D_REG | $V_{INN}$ = 2.65V to 5.5V, $V_{AVDD}$ = 6.8V,<br>1mA < I <sub>NAVDD</sub> < 200mA, I <sub>AVDD</sub> = same<br>load as NAVDD |                                      | -34   | 0    | 34   | mV    |

| LXN On-Resistance                                            | R <sub>ON LXN</sub>             | LXN = 0.1A                                                                                                                   |                                      |       | 0.25 | 0.5  | Ω     |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

### **Electrical Characteristics (continued)**

| PARAMETER                                                | SYMBOL                       | CONDITIONS                                                        | MIN  | TYP  | MAX                | UNITS |

|----------------------------------------------------------|------------------------------|-------------------------------------------------------------------|------|------|--------------------|-------|

| LXN Leakage Current                                      | ILXN_LEAK                    | $V_{LXN} = V_{NAVDD} = -6.8V, T_A = +25^{\circ}C$                 |      |      | 20                 | μA    |

| LXN Current Limit                                        | ILIMNL                       | Duty cycle = 80%, Lxp_Lim_low = 1                                 | 0.6  | 0.8  |                    | А     |

|                                                          | ILIMNH                       | Duty cycle = 80%, Lxp_Lim_low = 0                                 | 1.55 | 1.9  | 2.25               | ~     |

| Soft-Start Period                                        | t <sub>INV_</sub> SS         | Current-limit ramp                                                |      | 5    |                    | ms    |

| TFT POWER SECTION /                                      | CHARGE-PUMP                  | REGULATORS                                                        |      |      |                    |       |

| PGVDD Operating<br>Voltage Range                         | V <sub>PGVDD</sub>           |                                                                   | 4.9  |      | V <sub>HVINP</sub> | V     |

| HVINP-PGVDD<br>Threshold for VG <sub>ON</sub><br>Startup | V <sub>HVINP-</sub><br>PGVDD | V <sub>HVINP</sub> = 5V                                           | 360  | 520  | 680                | mV    |

| High-Side DP/DN<br>Current Limit                         | I <sub>DR_HS</sub>           | V <sub>HVINP</sub> = 6.8V, V <sub>DP</sub> = V <sub>DN</sub> = 3V | 95   |      |                    | mA    |

| Low-Side DP/DN<br>Current Limit                          | I <sub>DR_LS</sub>           | $V_{DP} = V_{DN} = 3V$                                            | 95   |      |                    | mA    |

| High-Side DP/DN On-<br>Resistance                        | R <sub>DR_HS</sub>           | $I_{DP} = I_{DN} = -20$ mA,<br>$V_{PGVDD} = V_{HVINP} = 6.8$ V    |      | 5    | 8                  | Ω     |

| Low-Side DP/DN On-<br>Resistance                         | R <sub>DR_LS</sub>           | I <sub>DP</sub> = I <sub>DN</sub> = 20mA                          |      | 3    | 6                  | Ω     |

| VG <sub>ON</sub> Unipolar Voltage<br>Range               | VG <sub>ON_RNG</sub>         | dis_navdd = 1                                                     | 12.6 |      | 31.5               | V     |

| VG <sub>ON</sub> Bipolar Voltage<br>Range                | VGON <sub>RNGB</sub>         | dis_navdd = 0                                                     | 8.4  |      | 21                 | V     |

| VG <sub>ON</sub> Unipolar<br>Adjustment Step Size        | LSB <sub>VGON</sub>          | dis_navdd = 1                                                     |      | 0.3  |                    | V     |

| VG <sub>ON</sub> Bipolar<br>Adjustment Step Size         | LSB <sub>VGONB</sub>         | dis_navdd = 0                                                     |      | 0.2  |                    | V     |

| VG <sub>ON</sub> Internal<br>Feedback Resistor<br>Value  | R <sub>VGON</sub>            |                                                                   | 700  |      | 1250               | kΩ    |

| VG <sub>ON</sub> Output Voltage<br>Accuracy              | ACC <sub>VGON</sub>          | 0x16h setting                                                     | -2   |      | 2                  | %     |

| VG <sub>OFF</sub> Voltage Range                          | VG <sub>OFF_RNG</sub>        |                                                                   | -18  |      | -4                 | V     |

| VG <sub>OFF</sub> Adjustment Step<br>Size                | LSB <sub>VGOFF</sub>         |                                                                   |      | 0.25 |                    | V     |

| VG <sub>OFF</sub> Output-Voltage<br>Accuracy             | ACC <sub>VGOFF</sub>         | 0x16h setting                                                     | -3   |      | +3                 | %     |

| TFT POWER SECTION /                                      | SEQUENCE SW                  | ITCHES                                                            |      |      |                    |       |

| AVDD Switch On-<br>Resistance                            | R <sub>ON_AVDD</sub>         | V <sub>HVINP</sub> = 6.8V, I <sub>AVDD</sub> = -100mA             |      | 0.9  | 1.6                | Ω     |

| AVDD Switch Current<br>Limit                             | I <sub>LIM_AVDD</sub>        |                                                                   | 400  | 500  | 650                | mA    |

| AVDD Discharge<br>Resistance                             | R <sub>AVDD_</sub> DIS       | AVDD disabled, V <sub>V18</sub> > V <sub>V18</sub> _UVLO          |      | 1.2  |                    | kΩ    |

| PGVDD On-Resistance                                      | R <sub>ON_PGVDD</sub>        | (HVINP - PGVDD), I <sub>PGVDD</sub> = 10mA                        |      | 2.5  | 5                  | Ω     |

|                                                          |                              |                                                                   |      |      |                    |       |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

| PARAMETER                                         | SYMBOL                  | CONDITIONS                                         | MIN  | TYP | MAX  | UNITS |

|---------------------------------------------------|-------------------------|----------------------------------------------------|------|-----|------|-------|

| PGVDD Current Limit                               | ILIM_PGVDD              | V <sub>PGVDD</sub> = 3V, V <sub>HVINP</sub> = 6.8V | 70   | 100 |      | mA    |

| VG <sub>ON</sub> Discharge<br>Resistance          | R <sub>DIS_VGON</sub>   |                                                    | 2    | 3   | 4    | kΩ    |

| VG <sub>OFF</sub> Discharge<br>Current            | IDIS_VGOFF              |                                                    |      | 1.5 |      | mA    |

| NAVDD Discharge<br>Resistance                     | R <sub>NAVDD_</sub> DIS | NAVDD disabled, $V_{V18} > V_{V18}_{UVLO}$         |      | 1   |      | kΩ    |

| TFT POWER SECTION /                               | TFT FAULT PR            | OTECTION                                           |      |     |      |       |

| Fault Timeout                                     | <sup>t</sup> FAULT      | tfault[1:0] = 10                                   |      | 60  |      | ms    |

| Fault Retry Time                                  | <sup>t</sup> аuto       | tretry[1:0] = 10 or 11                             |      | 1.9 |      | s     |

| FLTB Output Frequency                             |                         | Stand-alone mode only                              | 0.88 | 1   | 1.12 | kHz   |

| HVINP/AVDD<br>Undervoltage Fault<br>Threshold     | THR <sub>UV</sub>       | Relative measurement between HVINP and AVDD        | 81   | 85  | 89   | %     |

| HVINP/AVDD<br>Overvoltage Fault<br>Threshold      | THR <sub>OV</sub>       | Percentage of set value, voltage rising            | 111  | 115 | 119  | %     |

| HVINP/AVDD Short-<br>Circuit Fault Threshold      | THR <sub>SHRT</sub>     |                                                    | 36   | 40  | 44   | %     |

| NAVDD Undervoltage<br>Fault Threshold             | THR <sub>UV</sub>       | Of AVDD regulation voltage, NAVDD rising           | 81   | 85  | 89   | %     |

| NAVDD Overvoltage<br>Fault Threshold              | THR <sub>OV</sub>       | Of AVDD regulation voltage, NAVDD voltage falling  | 111  | 115 | 119  | %     |

| NAVDD Short-Circuit<br>Fault Threshold            | THR <sub>SHRT</sub>     | Of AVDD regulation voltage, NAVDD voltage rising   | 36   | 40  | 44   | %     |

| VG <sub>ON</sub> Undervoltage<br>Fault Threshold  | THR <sub>UV</sub>       | Of set value, VG <sub>ON</sub> voltage falling     | 81   | 85  | 89   | %     |

| VG <sub>ON</sub> Overvoltage Fault<br>Threshold   | THR <sub>OV</sub>       | Of set value, $VG_{ON}$ voltage rising             | 111  | 115 | 119  | %     |

| VG <sub>OFF</sub> Undervoltage<br>Fault Threshold | THR <sub>UV</sub>       | Of set value, VG <sub>OFF</sub> voltage rising     | 78   |     | 88   | %     |

| VG <sub>OFF</sub> Overvoltage<br>Fault Threshold  | THR <sub>OV</sub>       | Of set value, VG <sub>OFF</sub> voltage falling    | 105  |     | 120  | %     |

| Short-Circuit Fault Delay                         |                         | After completion of soft-start                     |      | 10  |      | μs    |

| Bandgap Out-of-Range<br>Diagnostic Threshold      |                         |                                                    |      | ±11 |      | %     |

| LED BACKLIGHT DRIVE                               | R                       |                                                    |      |     |      |       |

| BATT Operating Voltage<br>Range                   | V <sub>BATT</sub>       |                                                    | 4.5  |     | 36   | V     |

| BATT Operating Voltage<br>Range after Startup     | V <sub>BATT</sub>       | Maximum duration 100ms                             | 3    |     | 36   | V     |

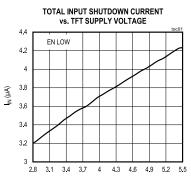

| BATT Quiescent Supply<br>Current                  | IQ_BATT                 |                                                    |      | 5   | 10   | μA    |

|                                                   |                         | -                                                  |      |     |      |       |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

| PARAMETER                                                | SYMBOL                | CONDITIONS                                                                                                  | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|-------|

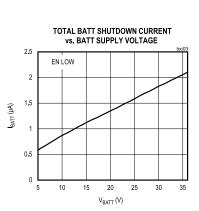

| BATT Shutdown Supply<br>Current                          | IBATT_SHDN            | $V_{EN}$ = 0V, $T_A$ = +25°C, typical application circuit                                                   |      | 1    | 3    | μA    |

| BATT Undervoltage<br>Lockout, Rising                     | V <sub>BATT_UVR</sub> | BATT voltage rising                                                                                         | 4.15 | 4.29 | 4.4  | V     |

| BATT Undervoltage<br>Lockout, Falling                    | V <sub>BATT_UVF</sub> | BATT voltage falling                                                                                        | 2.77 | 2.9  | 2.95 | V     |

| BATT Threshold for                                       | V <sub>BATT_LVF</sub> | BATT voltage falling                                                                                        | 5.35 | 5.5  | 5.65 |       |

| Low-Voltage Operation<br>Mode                            | V <sub>BATT_LVR</sub> | BATT voltage rising                                                                                         | 5.55 | 5.72 | 5.85 | V     |

| LED BACKLIGHT DRIVE                                      | R / V5 REGULA         | TOR                                                                                                         |      |      |      | 1     |

| V5 Output Voltage                                        | V <sub>V5</sub>       | 5.75V < V <sub>HVINP</sub> < 18V,<br>I <sub>V5</sub> = 1mA to 10mA                                          | 4.8  | 5    | 5.2  | V     |

| V5 Dropout Voltage                                       | V <sub>V5_DRP</sub>   | V <sub>HVINP</sub> = 4.9V, I <sub>V5</sub> = 5mA                                                            |      | 0.05 | 0.12 | V     |

| V5 Undervoltage                                          | $V_{V5}UVLOR$         | V5 voltage rising                                                                                           | 3.8  | 3.9  | 4.1  | v     |

| Lockout                                                  | V <sub>V5_UVLOF</sub> | V5 voltage falling                                                                                          | 3.6  | 3.7  | 3.8  | v     |

| V5 Short-Circuit Current<br>Limit                        | I <sub>V5_SC</sub>    | V5 shorted to GND                                                                                           | 50   |      |      | mA    |

| V5 Overvoltage<br>Threshold                              |                       |                                                                                                             | 5.6  | 5.75 | 5.9  | V     |

| LED BACKLIGHT DRIVE                                      | R / NGATE OUT         | PUT                                                                                                         |      |      |      |       |

| NGATE Output Voltage                                     | V <sub>NGATE</sub>    | Above V <sub>BATT</sub> , 3.3V < V <sub>BATT</sub> < 33V,<br>I <sub>NGATE</sub> = 1μA                       | 4.3  | 5.25 | 6    | V     |

| NGATE Source Current                                     | I <sub>NG_SO</sub>    | V <sub>NGATE</sub> = V <sub>BATT</sub>                                                                      | 30   | 50   |      | μA    |

| NGATE Sink Current                                       | I <sub>NG_SINK</sub>  |                                                                                                             | 0.4  | 0.7  |      | mA    |

| NGATE Output Voltage<br>at High Input Voltage            | V <sub>NGATE_HV</sub> | Above V <sub>BATT</sub> , V <sub>BATT</sub> > 35.5V,<br>I <sub>NGATE</sub> = 1μA                            | -0.3 |      | 0    | V     |

| BATT HV Comparator<br>Threshold                          | V <sub>LD_THR</sub>   | BATT voltage rising                                                                                         | 33   |      | 35.5 | V     |

| BATT HV Comparator<br>Hysteresis                         | V <sub>LD_HYS</sub>   |                                                                                                             |      | 0.7  |      | V     |

| NGATE Start Delay                                        | t <sub>NG_DEL</sub>   | Delay between NGATE charge-pump turning on and BSTMON rising                                                |      | 2    | 2.2  | ms    |

| LED BACKLIGHT DRIVE                                      | R / RT OSCILLA        | TOR                                                                                                         |      |      |      |       |

| Switching Frequency<br>Range                             | fsw_rt                | Frequency dithering disabled                                                                                | 400  |      | 2200 | kHz   |

| Oscillator Frequency<br>Accuracy                         |                       | I <sub>RT</sub> = 13.85μA (f <sub>SW</sub> = 400kHz),<br>I <sub>RT</sub> = 75μA (f <sub>SW</sub> = 2200kHz) | -10  |      | 10   | %     |

| Boost Converter<br>Maximum Duty Cycle,<br>High Frequency |                       | 1.3MHz to 2.2MHz                                                                                            | 89   | 91   | 94   | %     |

| Boost Converter<br>Maximum Duty Cycle,<br>Low Frequency  |                       | f <sub>SW</sub> = 400kHz to 1.3MHz                                                                          | 94   |      | 98   | %     |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

| PARAMETER                                             | SYMBOL                | CONDITIONS                                          | MIN      | TYP  | MAX   | UNITS |

|-------------------------------------------------------|-----------------------|-----------------------------------------------------|----------|------|-------|-------|

| Boost Minimum On-<br>Time                             |                       |                                                     |          | 60   |       | ns    |

| Frequency Dither, High Setting                        | SSHI                  | bl_ssl = 0                                          |          | ±6   |       | %     |

| Frequency Dither, Low Setting                         | SSLO                  | bl_ssl = 1                                          |          | ±4   |       | %     |

| RT Output Voltage                                     | V <sub>RT</sub>       | $R_{RT} = 65k\Omega \text{ or } R_{RT} = 10k\Omega$ | 0.875    | 0.9  | 0.925 | V     |

| Sync Threshold                                        | V <sub>RT_SYNC</sub>  | V <sub>RT</sub> rising                              | 0.77     |      | 0.84  | V     |

| Sync Frequency Duty-<br>Cycle                         | D <sub>SYNC</sub>     |                                                     |          | 50   |       | %     |

| Sync Frequency Range                                  |                       |                                                     | 400      |      | 2200  | kHz   |

| LED BACKLIGHT DRIVE                                   | R / SLOPE COM         | IPENSATION                                          |          |      |       |       |

| Peak Slope-<br>Compensation Current<br>Ramp per Cycle | ISLOPE                | Current ramp added to CS                            | 42       | 50   | 60    | μA    |

| LED BACKLIGHT DRIVE                                   | R / CURRENT-L         | IMIT COMPARATOR                                     | <b>I</b> |      |       |       |

| CSP Threshold Voltage                                 | V <sub>CSP-CSNL</sub> | bl_ilim = 1                                         | 275      | 300  | 325   | mV    |

| VCSP-CSN                                              |                       | bl_ilim = 0                                         | 380      | 410  | 440   |       |

| CSP Threshold Voltage<br>During Low Voltage           | V <sub>CSP_LV</sub>   | $V_{BATT} < V_{BATT_LVF}, V_{BATT}$ falling         | 560      | 600  | 640   | mV    |

| CSP Input Current                                     | I <sub>CSP</sub>      | V <sub>EN</sub> = 0V, V <sub>CSP</sub> = 0.4V       |          |      | +1    | μA    |

| LED BACKLIGHT DRIVE                                   | R / ERROR AM          | PLIFIER                                             |          |      |       |       |

| OUT_ Regulation High<br>Threshold                     | V <sub>THH</sub>      | V <sub>OUT</sub> _rising                            | 0.825    | 0.85 | 0.875 | V     |

| OUT_ Regulation Low<br>Threshold                      | V <sub>THL</sub>      | V <sub>OUT_</sub> falling                           | 0.55     | 0.58 | 0.61  | V     |

| Transconductance                                      | Ям                    |                                                     | 410      | 630  | 890   | μS    |

| COMP Sink Current                                     | ICOMP_SINK            | V <sub>COMP</sub> = 1V                              | 270      | 380  | 500   | μA    |

| COMP Source Current                                   | ICOMP_SRC             | V <sub>COMP</sub> = 1V                              | 270      | 380  | 500   | μA    |

| LED BACKLIGHT DRIVE                                   | R / MOSFET DR         | IVER                                                |          |      |       |       |

| NDRV On-Resistance                                    | R <sub>NDRV_LS</sub>  | V <sub>V5</sub> = 5V, I <sub>NDRV</sub> = 100mA     |          | 1.2  | 2     | Ω     |

|                                                       | R <sub>NDRV_HS</sub>  | V <sub>V5</sub> = 5V, I <sub>NDRV</sub> = -100mA    |          | 1.5  | 3     |       |

| NDRV Rise Time                                        | <sup>t</sup> NDRV_R   | C <sub>NDRV</sub> = 1nF, ( <u>Note 2</u> )          |          | 8    |       | ns    |

| NDRV Fall Time                                        | t <sub>NDRV_F</sub>   | C <sub>NDRV</sub> = 1nF, ( <u>Note 2</u> )          |          | 8    |       | ns    |

| NDRVS Input Logic-Low                                 | V <sub>IL_NDRVS</sub> | V <sub>NDRVS</sub> falling                          |          | 2    | 2.4   | V     |

| NDRVS Input Logic-<br>High                            | V <sub>IH_NDRVS</sub> | V <sub>NDRVS</sub> rising                           | 2.55     | 3.3  |       | V     |

| NDRVS Input Current                                   | INDRVS                | V <sub>NDRVS</sub> = 5V                             |          | 60   |       | μA    |

| LED BACKLIGHT DRIVE                                   | R / LED CURRE         |                                                     |          |      |       |       |

|                                                       |                       |                                                     |          |      |       |       |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

### **Electrical Characteristics (continued)**

| PARAMETER                                | SYMBOL                 | CONDITIONS                                                                                                            | MIN  | TYP  | MAX   | UNITS |

|------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|

|                                          | IOUT_                  | iset[6:0] = 0x7F, 150mA setting                                                                                       | 145  | 150  | 154   |       |

| Full-Scale OUT_ Output                   | I <sub>OUT100</sub>    | iset[6:0] = 0x4D, 100mA setting                                                                                       | 97   | 100  | 103   |       |

| Current                                  | I <sub>OUT50</sub>     | iset[6:0] = 0x1B, 50mA setting                                                                                        | 48   | 50   | 52    | mA    |

|                                          | I <sub>OUT23</sub>     | iset[6:0] = 0x00, 23mA setting                                                                                        | 21.5 | 23   | 25.2  |       |

| Current Regulation<br>Between Strings    | IOUT_MATCH1<br>50      | I <sub>OUT</sub> = 150mA, design target                                                                               | -2   |      | +2    | %     |

| Current-Setting<br>Resolution            | IOUT_LSB               |                                                                                                                       |      | 1    |       | mA    |

| OUT_ Leakage Current                     | 1                      | $V_{OUT}$ = 36V, DIM = 0, all OUT_pins<br>shorted together, T <sub>A</sub> = +25°C                                    |      | 0.1  | 5     | μA    |

| OUT_Leakage Current                      | IOUT_LEAK              | V <sub>OUT</sub> = 36V, DIM = 0, all OUT_pins<br>shorted together                                                     |      | 0.1  | 15    | μA    |

| OUT_ Minimum Pulse<br>Width              |                        |                                                                                                                       |      | 300  |       | ns    |

| OUT_ Minimum<br>Negative Pulse Width     |                        |                                                                                                                       |      | 90   |       | ns    |

| I <sub>OUT</sub> _Rise Time              | IOUT_TR                | I <sub>OUT</sub> _ = 150mA, 10% to 90% I <sub>OUT</sub> _                                                             |      | 150  |       | ns    |

| I <sub>OUT</sub> _ Fall Time             | IOUT_TF                | I <sub>OUT</sub> = 150mA, 90% to 10% I <sub>OUT</sub>                                                                 |      | 20   |       | ns    |

| LED BACKLIGHT DRIVE                      | R / DIM, ADIM IN       | NPUTS                                                                                                                 |      |      |       |       |

| DIM Frequency Range                      |                        |                                                                                                                       | 90   |      | 50000 | Hz    |

| DIM Sampling<br>Frequency                |                        |                                                                                                                       |      | 20   |       | MHz   |

| ADIM Input Frequency<br>Range            |                        |                                                                                                                       | 10   |      | 100   | kHz   |

| LED BACKLIGHT DRIVE                      | R / LED FAULT          | DETECTION                                                                                                             |      |      |       |       |

| LED Short-Detection                      | VTHSHRT                | I <sup>2</sup> C mode, bit configuration = 11 (00:<br>short detection disabled), default value in<br>stand-alone mode | 7.7  | 8    | 8.3   | v     |

| Threshold                                | - montri               | I <sup>2</sup> C mode, led_short_th[1:0 ] = 10                                                                        | 5.75 | 6    | 6.25  |       |

|                                          |                        | I <sup>2</sup> C mode, led_short_th[1:0] = 01                                                                         | 2.8  | 3    | 3.2   |       |

| OUT_ Check-LED-<br>Source Current        | IOUT_CKLED             | V <sub>OUT</sub> _= 0.5V                                                                                              | 50   | 60   | 70    | μA    |

| OUT_ Short-to-GND<br>Detection Threshold | VOUT_GND               | V <sub>OUT</sub> _falling                                                                                             | 230  | 250  | 270   | mV    |

| OUT_ Unused-Detection<br>High Threshold  | Vout_un                |                                                                                                                       | 0.8  | 0.85 | 0.9   | V     |

| OUT_ Open-LED-<br>Detection Threshold    | V <sub>OUT_OPEN</sub>  |                                                                                                                       | 230  | 250  | 270   | mV    |

| Shorted-LED-Detection<br>Flag Delay      | <sup>t</sup> SHRT      |                                                                                                                       |      | 6.8  |       | μs    |

| LED BACKLIGHT DRIVE                      | R / OVERVOLTA          | AGE AND UNDERVOLTAGE PROTECTION                                                                                       |      |      |       |       |

| BSTMON Overvoltage<br>Threshold          | V <sub>BSTMON_OV</sub> | V <sub>BSTMON</sub> rising                                                                                            | 0.92 | 0.95 | 0.98  | V     |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

| PARAMETER                                           | SYMBOL                        | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|

| BSTMON Overvoltage<br>Hysteresis                    | V <sub>BSTMON_OV</sub><br>HYS |                                                                                      |       | 50    |       | mV    |

| BSTMON Input Bias<br>Current                        | IBSTMON                       | 0 < V <sub>BSTMON</sub> < 1V                                                         | -1    |       | +1    | μA    |

| BSTMON Undervoltage-<br>Trip Threshold              | V <sub>OVPUVLO</sub>          | V <sub>BSTMON</sub> rising                                                           | 0.384 | 0.4   | 0.416 | V     |

| Boost Undervoltage-<br>Detection Delay              | OVPUVLO_B<br>LK               |                                                                                      |       | 10    |       | μs    |

| Boost Undervoltage-                                 |                               | After soft-start, fast_ss = 1                                                        | 26.28 | 28.46 | 30.74 | me    |

| Blanking Time                                       |                               | After soft-startup, fast_ss = 0                                                      | 49    | 53.25 | 57.5  | ms    |

| TEMP PIN                                            |                               |                                                                                      |       |       |       |       |

| TEMP Pin Voltage                                    | V <sub>TEMP</sub>             | I <sub>TEMP</sub> = -10μA                                                            | 380   | 400   | 420   | mV    |

| TEMP to IOUT_ Gain                                  |                               |                                                                                      |       | 0.667 |       | %/µA  |

| TEMP Pin Disable<br>Threshold                       |                               |                                                                                      |       | 0.5   |       | V     |

| TEMP Pin Leakage<br>Current                         |                               | +25°C                                                                                |       | 0.05  | 1     | μA    |

| TEMP Current for LED<br>Current Disable             | ITEMPD                        |                                                                                      | 80    | 120   | 160   | μA    |

| PROGRAMMING VOLTA                                   | GE                            |                                                                                      |       |       |       |       |

| V <sub>PROG</sub> Voltage                           |                               |                                                                                      | 8.2   | 8.5   | 8.8   | V     |

| V <sub>PROG</sub> Voltage<br>Undervoltage Threshold |                               | V <sub>PROG</sub> rising                                                             |       | 8     | 8.2   | V     |

| V <sub>PROG</sub> Voltage<br>Overvoltage Threshold  |                               | V <sub>PROG</sub> falling                                                            | 8.8   | 9     |       | V     |

| VPROG Input Current                                 |                               | During NV programming, $T_A = +25^{\circ}C$                                          |       | 9     | 25    | mA    |

| NV Programming Time                                 |                               |                                                                                      |       | 16    | 20    | ms    |

| LOGIC INPUTS AND OUT                                | TPUTS (EN, SCI                | ., SDA, DIM, ADD, MODE, PFO)                                                         |       |       |       |       |

| Digital Inputs Logic-High                           | V <sub>IH</sub>               |                                                                                      | 1.25  |       |       | V     |

| Digital Inputs Logic-Low                            | V <sub>IL</sub>               |                                                                                      |       |       | 0.5   | V     |

| Digital Inputs Hysteresis                           | V <sub>HYS</sub>              |                                                                                      |       | 300   |       | mV    |

| EN Input Pull-down<br>Resistor                      |                               |                                                                                      | 100   | 165   |       | kΩ    |

| EN Blanking Time                                    | <sup>t</sup> EN_BLK           |                                                                                      |       | 10    |       | μs    |

| DIM Pull-up Current                                 | I <sub>DIM</sub>              | V <sub>DIM</sub> = 0V                                                                |       | 5     |       | μA    |

| ADD and MODE Pull-up<br>Current                     | IADD_MODE                     | V <sub>ADD</sub> = V <sub>MODE</sub> = 0V                                            |       | 2     |       | μA    |

| SCL Input Current                                   | I <sub>SCL</sub>              | V <sub>SCL</sub> = +5V                                                               |       |       | +1    | μA    |

| PFO, FLTB, SDA Output<br>Low Voltage                | V <sub>OL_OUT</sub>           | I <sub>FLTB</sub> = I <sub>SDA</sub> = I <sub>PFO</sub> = 5mA                        |       |       | 0.4   | V     |

| PFO, FLTB, SDA Output<br>Leakage Current            | IOUT_LEAK                     | V <sub>EN</sub> = 0V, V <sub>FLTB</sub> = V <sub>SDA</sub> = V <sub>PFO</sub> = 5.5V |       |       | +1    | μΑ    |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{BATT} = 12V, typical operating circuit, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = +25°C. (*Note 1*))

| PARAMETER                                           | SYMBOL                 | CONDITIONS                 | MIN  | TYP    | MAX | UNITS |

|-----------------------------------------------------|------------------------|----------------------------|------|--------|-----|-------|

| THERMAL WARNING/S                                   | HUTDOWN                |                            |      |        |     | 1     |

| Thermal-Warning<br>Threshold, TFT Section           | T <sub>WARN_TFT</sub>  | Temperature rising         |      | 125    |     |       |

| Thermal-Warning<br>Threshold, Backlight<br>Section  | T <sub>WARN_BL</sub>   |                            |      | 125    |     | °C    |

| Thermal-Shutdown<br>Threshold, TFT Section          | T <sub>SHDN_TFT</sub>  | Temperature rising         |      | 165    |     | °C    |

| Thermal-Shutdown<br>Threshold, Backlight<br>Section | T <sub>SHDN_BL</sub>   | Temperature rising         |      | 160    |     | °C    |

| Thermal-Shutdown<br>Hysteresis                      | T <sub>SHDN_HYS</sub>  |                            |      | 17     |     | °C    |

| ANALOG-TO-DIGITAL C                                 | ONVERTER               |                            |      |        |     |       |

| ADC Measurement<br>Resolution                       | ADC <sub>BIT</sub>     | ( <u>Note 2</u> )          |      | 8      |     | bits  |

| Total Measurement<br>Error, Current                 | E_ADC <sub>OUT</sub>   | 150mA setting              | -8   |        | +8  | mA    |

| Total Measurement<br>Error, BSTMON                  | E_ADC <sub>BSTMO</sub> | V <sub>BSTMON</sub> = 0.9V | -70  |        | 70  | mV    |

| ADC Gain Error                                      | ADC <sub>GAIN</sub>    | 150mA setting              | -4   |        | +4  | %     |

| ADC Offset Error                                    | ADC <sub>OFF</sub>     | 150mA setting              | -4   |        | +4  | LSB   |

| Measurement<br>Resolution, Current                  | LSB <sub>OUT</sub>     |                            |      | 0.64   |     | mA    |

| Measurement<br>Resolution, BSTMON                   | LSB <sub>BSTMON</sub>  |                            |      | 3.9216 |     | mV    |

| I <sup>2</sup> C INTERFACE                          |                        |                            |      |        |     |       |

| Clock Frequency                                     | f <sub>SCL</sub>       |                            |      |        | 0.4 | MHz   |

| Hold Time (Repeated)<br>START                       | <sup>t</sup> HD:STA    |                            | 600  |        |     | ns    |

| SCL Low Time                                        | tLOW                   |                            | 1300 |        |     | ns    |

| SCL High Time                                       | thigh                  |                            | 600  |        |     | ns    |

| Setup Time (Repeated)<br>START                      | t <sub>SU:STA</sub>    |                            | 600  |        |     | ns    |

| Data Hold Time                                      | t <sub>HD:DAT</sub>    |                            | 0    |        |     | ns    |

| Data Setup Time                                     | t <sub>SU:DAT</sub>    |                            | 100  |        |     | ns    |

| Setup Time for STOP<br>Condition                    | t <sub>SU:STO</sub>    |                            | 600  |        |     | ns    |

| Spike Suppression                                   |                        |                            |      | 50     |     | ns    |

Note 1: Limits are 100% tested at  $T_A = +25^{\circ}$ C,  $T_A = +125^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Guaranteed by design. Not production tested.

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Typical Operating Characteristics**

I<sub>BATT</sub> (µA)

AVDD + NAVDD LINE REGULATION

TOTAL IN QUIESCENT CURRENT vs. TFT SUPPLY VOLTAGE 2.9 2.88 2.86 <sub>IN\_Q</sub> (mA) 2.84 2.82 V<sub>EN</sub> 3.3V NO SWITCHING 2.8 2.8 3.1 3.4 3.7 4 4.3 4.6 4.9 5.2 5.5  $V_{IN}\left(V\right)$

AVDD LINE REGULATION AT 6.8V

toc05

AVDD + NAVDD LOAD REGULATION

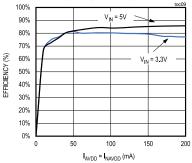

EFFICIENCY WITH DIFFERENTIAL LOAD FROM AVDD TO NAVDD

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with **ASIL B Features**

## **Typical Operating Characteristics (continued)**

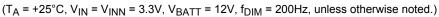

$(T_A = +25^{\circ}C, V_{IN} = V_{INN} = 3.3V, V_{BATT} = 12V, f_{DIM} = 200Hz$ , unless otherwise noted.)

100ms/div

V/div

LED

DIM

40ms/div

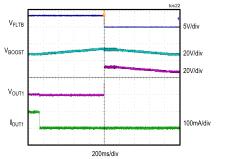

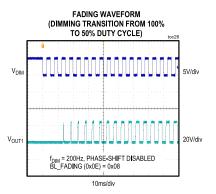

STARTUP WAVEFORM OF LED DRIVER WITH DIM DUTY CYCLE = 25% SLOW START UP, f<sub>DIM</sub> = 200Hz 10V/div 10V/div PHASE-SHIFT DISABLED 500mA/div

40ms/div

LEI

DI

5V/div

HVINP = 6.8V

SEQUENCE NO. 3

15

10

LE

DIN

5V/div

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Typical Operating Characteristics (continued)**

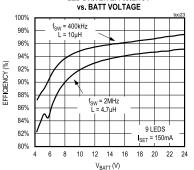

LED DRIVER EFFICIENCY

LED OPEN FAULT ON OUT1

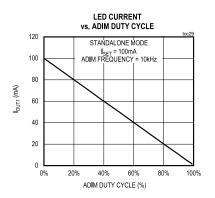

LED DRIVER EFFICIENCY vs. I<sub>SET</sub> CURRENT 100% f<sub>SW</sub> = 400kHz L = 10µH 98% 96% 94% EFFICIENCY (%) 92% 90% 88% 86% f<sub>SW</sub> = 2Μπ2 L = 4.7μH = 2MHz 84% 9 LEDS 82% V<sub>BATT</sub> = 12V 80% 20 40 60 80 100 120 140 160 ISET CURRENT (mA)

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

## **Typical Operating Characteristics (continued)**

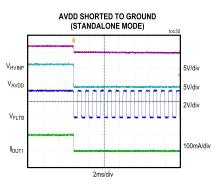

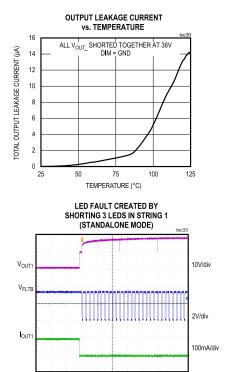

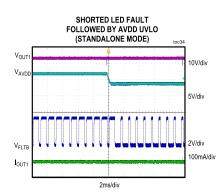

(T<sub>A</sub> = +25°C, V<sub>IN</sub> = V<sub>INN</sub> = 3.3V, V<sub>BATT</sub> = 12V,  $f_{DIM}$  = 200Hz, unless otherwise noted.)

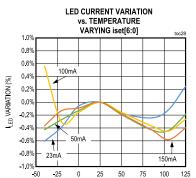

TEMPERATURE (°C)

4ms/div

www.analog.com

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

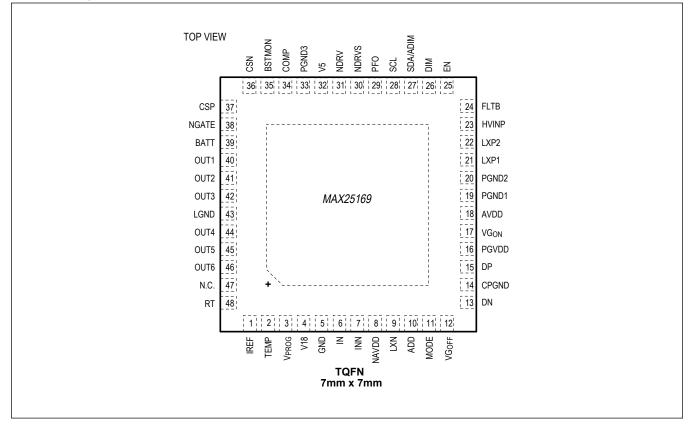

## **Pin Configuration**

## **Pin Description**

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                               |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IREF              | Reference Current Set Pin. Connect a 1% resistor of value 22kΩ from IREF to GND.                                                                                                                                                       |

| 2   | TEMP              | Temperature Sensor Input. To implement LED current reduction at high temperatures, connect an NTC temperature sensor (e.g., the NTCLE100E3103G) to GND with resistors from the NTC to TEMP and to V18. If unused, connect TEMP to V18. |

| 3   | V <sub>PROG</sub> | Programming Voltage. Apply a voltage of 8.5V to this pin during the programming of nonvolatile registers. Connect to GND through a resistor during normal operation.                                                                   |

| 4   | V18               | Output of Internal 1.8V Regulator. Connect 1µF and 22nF capacitors in parallel from V18 to GND with an additional 100nF capacitor close to the V18 and GND pins.                                                                       |

| 5   | GND               | Ground Connection                                                                                                                                                                                                                      |

| 6   | IN                | Supply Input. Connect at least one 10µF ceramic capacitor from IN to GND for proper operation.                                                                                                                                         |

| 7   | INN               | Buck-Boost Converter Input. Connect a 10µF ceramic capacitor from INN to GND for proper operation.                                                                                                                                     |

| 8   | NAVDD             | Negative Source-Driver Output Voltage                                                                                                                                                                                                  |

| 9   | LXN               | DC-DC Inverting Converter Inductor/Diode Connection                                                                                                                                                                                    |

| 10  | ADD               | Device Address Select Pin. Connect to GND or V18 to select the device I <sup>2</sup> C address. See <u>Table 5</u> . ADD has an internal pull-up to V18.                                                                               |

| 11  | MODE              | Mode Selector Pin. Together with ADD, this pin determines the mode of operation of the I <sup>2</sup> C interface and whether it is used. See <u>Table 3</u> . MODE has an internal pull-up to V18.                                    |

# Automotive, I<sup>2</sup>C-Controlled, 6-Channel, 150mA Backlight Driver and 4-Output TFT-LCD Bias with ASIL B Features

# **Pin Description (continued)**

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 12  | VG <sub>OFF</sub> | Output of Negative Charge-Pump Block. Connects directly to the negative charge-pump output to facilitate $VG_{OFF}$ discharge through an internal switch connected between $VG_{OFF}$ and GND. $VG_{OFF}$ is also the regulator feedback pin.                                                            |  |  |  |  |  |

| 13  | DN                | Regulated Charge-Pump Driver for the Negative Charge Pump. Connect to an external flying capacitor.                                                                                                                                                                                                      |  |  |  |  |  |

| 14  | CPGND             | Charge Pump Ground                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 15  | DP                | Regulated Charge-Pump Driver for Positive Charge Pump. Connect to an external flying capacitor                                                                                                                                                                                                           |  |  |  |  |  |

| 16  | PGVDD             | Switched Version of HVINP Voltage for the Positive Charge Pump. Provides soft-start control of the VG <sub>ON</sub> output. Bypass PGVDD with a $1\mu$ F ceramic capacitor to GND.                                                                                                                       |  |  |  |  |  |

| 17  | VG <sub>ON</sub>  | Output of Positive Charge-Pump Block. $VG_{ON}$ connects directly to the positive charge-pump output to facilitate $VG_{ON}$ discharge through an internal switch connected between $VG_{ON}$ and GND. $VG_{ON}$ is also the regulator feedback pin.                                                     |  |  |  |  |  |

| 18  | AVDD              | Positive Source-Driver Output Voltage. Bypass AVDD with a capacitor to GND.                                                                                                                                                                                                                              |  |  |  |  |  |

| 19  | PGND1             | Power-Ground Connection                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 20  | PGND2             | Power-Ground Connection                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 21  | LXP1              | Boost HVINP Converter Switching-Node Connection. Connect LXP1 to the external inductor and rectifier diode.                                                                                                                                                                                              |  |  |  |  |  |

| 22  | LXP2              | Boost HVINP Converter Switching-Node Connection. Connect LXP2 to the external inductor and rectifier diode.                                                                                                                                                                                              |  |  |  |  |  |

| 23  | HVINP             | Boost Output and Input for the AVDD, PGVDD, and Charge Pumps                                                                                                                                                                                                                                             |  |  |  |  |  |