PolyPhase Surface Mount Power Supply Meets AMD Athlon Processor Requirements with No Heat Sink – Design Note 216 Craig Varga

## Introduction

With the introduction of the AMD Athlon processor, the supply current requirement for a desktop PC's processor has, for the first time, surpassed the 40A mark. This, combined with low operating voltage (1.6V nominal) and very tight transient-response requirements, pushes conventional power supply design approaches to their limits. The LTC®1929 PolyPhase® current mode controller makes a slight break with convention. Instead of trying to deliver 40A with a single regulator, the load is split in half by paralleling two regulators. The magic, however, is in the phase relationship of the two regulators' clocks.

## **PolyPhase Architecture**

The two synchronous buck regulators are connected in parallel and their clocks are synchronized 180° out of phase. This seemingly simple trick results in tremendous performance advantages as well as cost savings. A current mode architecture was chosen to reduce possible problems related to circulating currents that can appear in paralleled voltage mode regulators. Competing

T, LT, LTC, LTM, Linear Technology, the Linear logo and PolyPhase are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

L C23

C/I

\_\_ C5

L 022

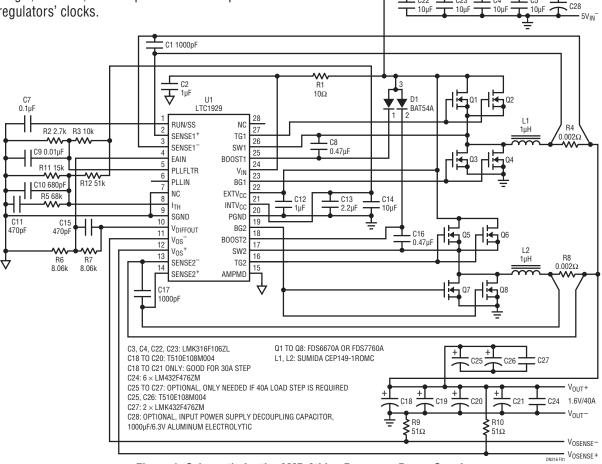

Figure 1. Schematic for the AMD Athlon Processor Power Supply

solutions use nonsynchronous regulators (using a diode for the low side switch) to eliminate this problem, but suffer a significant efficiency loss as a result.

The high side switch current waveform of a buck regulator is trapezoidal and varies between zero and approximately I<sub>OUT</sub>. Since the input current is DC, the input capacitors must supply the difference between the instantaneous switch current and the average input current. This places a large ripple current burden on the input capacitor. By interleaving the two regulators, the peak current is halved as one stage tries to "fill the holes" left by the other. The net effect is a dramatic reduction in input capacitor ripple current.

The output ripple is reduced in a similar fashion. While one inductor's current is increasing, the other's is decreasing. There is also a significant reduction in the required inductor energy storage (approximately 75%). The inductor's volume, and therefore cost, are reduced as well. See Linear Technology's Application Note 77 for complete details.

In addition to a significant reduction in output ripple current, the power supply's maximum available current slew rate is dramatically increased. During a load step, the two inductors behave as if they were connected in parallel, while during steady-state operation, they appear to operate in series. The result is very low ripple and blazingly fast dynamic performance. The reduced ripple also takes a smaller bite out of the total error budget, leaving that much more margin for transient response. The bottom line is a significant reduction in the required output capacitance.

Figure 1 is the schematic of the AMD Athlon-optimized circuit. The design is quite straightforward: there are essentially two identical synchronous buck regulators connected in parallel. The controller drives them 180° out of phase. The LTC1929 has large gate drivers (approximately  $1.5\Omega$ ) so it can drive large MOSFETs efficiently. There is also an accurate differential amplifier in the feedback path for easy remote sensing of both the output voltage and ground. The two PWM stages share a common error amplifier, which ensures that both channels provide the same amount of current to the load. Load sharing is therefore "open loop," eliminating oscillations in the share circuit that can occur with other approaches.

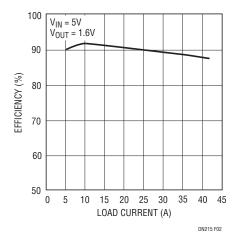

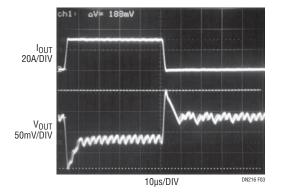

Figure 2 illustrates the efficiency for the circuit in Figure 1. The basic design will also operate with 12V as the main input source. The efficiency will be several points lower in this instance, but there may be advantages at the system-design level that need to be considered. Figure 3 shows the response of the regulator to a transient load step of 3A to 30A. To minimize PCB space, the design uses four  $1000\mu F$  surface mount tantalum output capacitors. If lowest cost is an overriding objective, twelve  $3900\mu F$  aluminum electrolytic capacitors can be substituted. If VID control is desired, the LTC1709 offers the same performance as the LTC1929 and includes a 5-bit VID DAC to program the output voltage from 1.3V to 3.5V.

Figure 2. Measured Efficiency

Figure 3. Load Transient Response with Active Voltage Positioning

Data Sheet Download

www.linear.com

For applications help, call (408) 432-1900