Keywords: direct-sampling DAC, RF DAC

# APPLICATION NOTE 5446 DIRECT-SAMPLING DACS IN THEORY AND APPLICATION

By: Stephanie Overhoff, Field Applications Engineer

Abstract: High-speed digital-to-analog converters (DACs) with high resolution in the 12- to 14-bit range enable new types of transmitter designs that employ a direct modulation scheme. In such designs, the modulated transmission signal is generated directly on the base frequency. This application note explains how direct-sampling RF DACs enable new communications systems such as cable infrastructure and explains how to synchronize multiple DACs that have multiplexed inputs (MUXDACs).

A similar version of this article appeared in German in the July 2012 issue of *Elektronik Informationen* magazine.

Modern high-speed digital-to-analog converters (DACs) that feature high resolution in the 12- to 14-bit range provide a basis for new types of transmitter designs that employ a direct modulation scheme. In such designs, the modulated transmission signal is generated directly on the base frequency. Until now, this approach has only been used for generating transmissions for quadrature-amplitude modulated (QAM) multicarrier signals in cable TV systems, or intermediate frequency signals for microwave systems employed by radar equipment and military communications systems. Now further development has made it possible to use these radio frequency (RF) DACs for other types of communications systems.

Today, CMOS RF DACs that have a resolution of 12 to 14 bits feature an update rate of more than 4Gsps. Together with signal processing components that employ CMOS technology, they make it possible to digitally generate transmission signals of up to 2GHz.

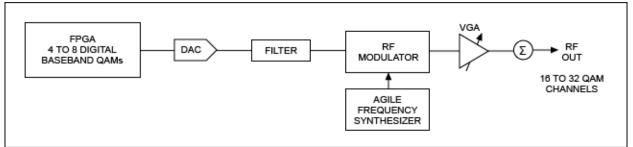

**Figure 1** shows a typical block diagram for an analog multicarrier QAM transmit path. To generate several QAM transmission channels, it is necessary to bring together several individual transmit chains with an adder. In addition, each RF modulator is supplied via its own synthesizer. Since each functional block has its own component tolerances, temperature drift, conversion losses etc., these must all be taken into account during system configuration by performing a tolerance calculation.

Figure 1. Block diagram of an analog multicarrier QAM transmitter.

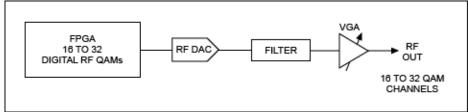

**Figure 2** shows the block diagram for a digital multicarrier QAM transmit path. Generating 32 QAM channels, for example, does not require combining multiple transmit paths—a single transmit path can handle this. In this case, the transmission path consists of an RF DAC with a downstream filter and a VGA. This also eliminates the need for an RF modulator or synthesizer in each transmit branch.

Figure 2. Block diagram for a digital multicarrier QAM transmitter with an RF DAC.

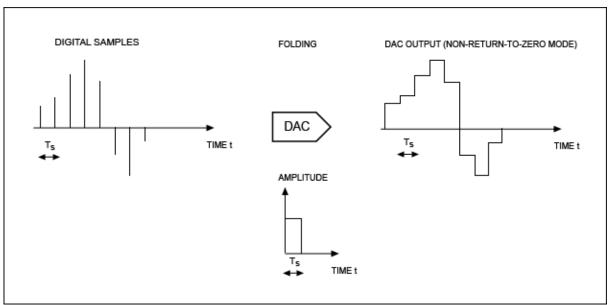

Sampling theory makes it possible to describe a DAC's output signal in the time and frequency domains. **Figure 3** shows the output signal for a DAC. Here, this is a sequence of rectangle pulses, the amplitude of which matches the corresponding digital value. Since the duration of these rectangle pulses is finite,  $T_s > 0$ , this results in an output spectrum. In the frequency domain, this output spectrum is described with the sinx/x function. The sinx/x function, which is also known as a sinc function, has zeros at the frequency  $f_s = 1/T_s$ .

Figure 3. DAC output signal as a sequence of rectangle pulses.  $T_s$  = sample time.

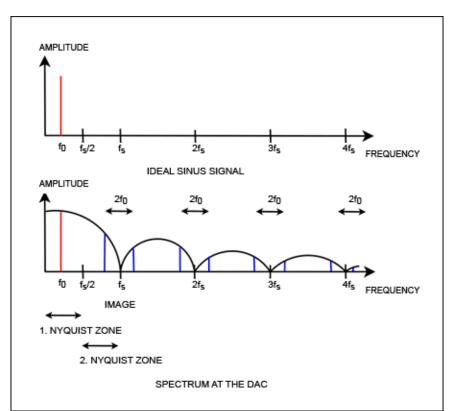

In the frequency domain, an ideal sinus signal with the frequency  $f_0$  has a spectral line at  $f_0$ . If the sinus signal is now generated with a DAC, besides the spectral line at  $f_0$ , additional frequency conversion products arise at higher frequencies (see **Figure 4**).

Figure 4. The sinus signal, described in the frequency range, and the output spectrum of a signal generated with a DAC.

These frequency conversion products can be described using Equation 1:

$$|K \times f_s \pm f_0|$$

$K = 1, 2, 3, ...$  (Eq. 1)

Equation 2 defines what is known as the "Nyquist zone" for the order N.

$$[(N - 1) \times f_{s}/2, N \times f_{s}/2] \quad K = 1, 2, 3, ...$$

(Eq. 2)

As Figure 4 shows, the DAC output signal does not consist of a single spectral line at  $f_0$ ; instead, it also has further spectral components at higher frequencies. This means that the DAC's output signal must be filtered. Besides these spurious emissions, additional frequency-conversion products arise. These are caused, for example, by the DAC's nonlinear output characteristics.

The fact that additional spectral components arise in higher Nyquist zones is exploited in order to use "sub-Nyquist DACs" to generate signals at high output frequencies. To do this, the signal's first harmonic wave is, for example, filtered out with a bandpass filter. The advantages here lie in the lower data rate in the baseband and in the reduced dissipation loss, compared with a DAC that generates the output signal directly on the fundamental frequency.

The MAX5879 RF DAC features 14-bit resolution and a sample rate of 2.3Gsps, ideal for base stations.

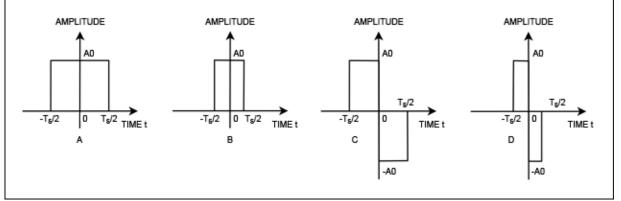

Additionally, the MAX5879's output's impulse responses can be programmed in four different operational modes, which we will examine more closely (**Figure 5**).

Figure 5. The MAX5879 RF DAC's impulse response for a) NRZ mode; b) RZ mode; c) RF mode; and d) RFZ mode.

The default impulse response is the non-return-to-zero (NRZ) impulse response (Figure 5a). The sample period is identical with the time  $T_s$ . The sinc function has its zeros at multiples of the update clock rate  $f_{CLK} = 1/T_s$ . When this impulse response is used, the following function arises for the DAC's frequency response:

$$A_{NRZ} = A_0[\sin(\pi f_{OUT} T_s)/(\pi f_{OUT} T_s)]$$

(Eq. 3)

$f_{OUT}$  is the DAC output frequency,  $T_s = 1/f_{CLK}$  is the DAC update clock rate, and A0 is the amplitude factor.

In return-to-zero (RZ) mode, the DAC output amplitude is zero for 50% of the time (Figure 5b). This results in the following frequency response:

$$A_{RZ} = A_0 / 2[sin(\pi f_{OUT} T_s / 2) / (\pi f_{OUT} T_s / 2)]$$

(Eq. 4)

The third programmable impulse response is the radio frequency (RF) mode. As Figure 5c shows, the DAC output signal is inverted during each clock cycle halfway through the clock period. The DAC's frequency response is described below:

$$A_{\text{RF}} = A_0[\sin(\pi f_{\text{OUT}} T_s/2)/(\pi f_{\text{OUT}} T_s/2) \times \sin(\pi f_{\text{OUT}} T_s/2)]$$

(Eq. 5)

The fourth new operating mode is the RFZ mode, which stands for "radio frequency return-to-zero mode." Its impulse response is as follows:

$$A_{RFZ} = A_0 / 2[\sin(\pi f_{OUT} T_s / 4) / (\pi f_{OUT} T_s / 4) \times \sin(\pi f_{OUT} T_s / 4)]$$

(Eq. 6)

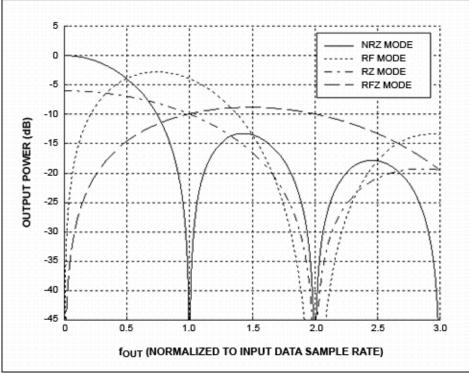

**Figure 6** shows the MAX5879's frequency response with the four possible operational modes. The figure's x axis shows the output frequency normalized to the input data sample rate. The range from 0 to 0.5 delineates the first Nyquist zone. The NRZ mode delivers the largest output signal in the first Nyquist zone. The RZ mode, comparatively, features the flattest frequency response in the first and third Nyquist zones. The RF mode is characterized by a maximum output power in the second and third Nyquist zones. Furthermore, the

frequency response in the second Nyquist zone is marked by a flatter rise than the other two operational modes exhibit. Of all the operational modes, the RFZ mode has the flattest impulse response across all of the Nyquist zones.

Figure 6. The MAX5879 RF DAC's normalized frequency response for the four possible operational modes.

The MAX5882 direct-sampling DAC has an update rate of 4.6Gsps at the output. This makes it possible to use direct modulation to generate transmission signals in the frequency range from 47MHz to 1003MHz. The MAX5882 was developed specifically for cable TV applications and complies with the Data-Over-Cable Service Interface Specification (DOCSIS<sup>®</sup>), Version 3.

## Simplifying DAC Control with a Digital Upconverter (DUC)

Until now, making the high data rate available for high-speed DACs required the use of field-programmable gate arrays (FPGAs) with a high power rating. Digital upconversion of the data is accomplished in the FPGA. The disadvantages of such a solution include high dissipation loss and higher system costs. Furthermore, upgrading the system for higher modulation schemes can only be done with great difficulty. If the distribution of the transmit system's capabilities is changed so that the digital upconversion function is realized with a dedicated chip, it is possible to use an FPGA with a lower power rating. That, in turn, reduces system costs and dissipation losses. As a side effect, this simplifies the interface between the RF DAC and the FPGA, because the DUC is adapted ideally to the RF DAC.

The MAX5880 QAM modulator and DUC is specially developed for applications in cable systems. In addition, it has capabilities for digital predistortion of the transmit signal. Its interface has been optimized to meet the requirements of the MAX5879 and MAX5882 high-speed DACs.

Maxim has since integrated the functionality of the MAX5880 and MAX5882 into a single package and now offers the MAX5862/MAX5860 High-Density QAM Modulators (Integrated DUCs and RF DACs) which support up to a maximum of 32/128 QAM channels respectively.

### Clock Synchronization in Applications that Use Multiple DACs

Modern communications systems frequently combine multiple transmit paths. This results in special requirements for synchronizing the clocks of the individual RF DACs. These special requirements must also be taken into consideration when using DACs with multiplexed inputs (MUXDACs).

Synchronizing multiple DACs requires consideration of the following problems:

- 1. The relative phase angle of the rising clock edge must be detected.

- 2. The relative phase angle between the individual DACs must be shifted until the DACs are synchronous with each other in the right phase relationship.

The MAX19692 RF DAC has four multiplex inputs. Here, four input signals are combined to form one output signal. As a result, the input data rate is 1/4 of the data rate for the DAC update. Thus, an update data rate of 2.3Gsps results in a maximum input data rate of 575Msps. The DAC takes on the data, which is optionally programmable, with the data clock's rising edge or with its rising and falling edges. With the aid of a digital divider, the DAC generates a clock signal from the applied input clock. When the DAC is turned on, the N-divider can be in any state when the digital clock divider starts up. When several of these DACs are then combined on a single transmit path, it is possible for each of these DACs to start up with the N-divider in a different divider state. Since the individual DACs accept their input data with different data edges, the output data from each DAC is then offset by one or several clock cycles from that of the others. Resetting the clock divider is only a partial solution to this problem; it is also necessary to detect any erroneous divider states that arise during operation. This is accomplished by measuring and correcting the various phase relationships.

In the simplest case, the phase error between the individual data clock outputs can be accomplished using an XOR gate. The most complicated solution is to employ a phase-frequency detector, such as those known from the use of phase-locked loops (PLLs).

In such cases, a separate PLL is used for each DAC. A comparison is made between the data output's phase angle and a reference frequency with a PLL. The PLLs from the various DACs are supplied with a common reference frequency. This process makes it possible to achieve a phase-locked or phase-synchronous constellation. Nevertheless, two disadvantages arise out of this configuration: The additional modules result in higher costs, and PLL-generated phase noise can limit system performance.

The MAX2870/MAX2871 frequency synthesizer maintains superior phase noise performance and covers the 23.5MHz to 6000MHz frequency range. This is made possible by an integrated voltage-controlled oscillator (VCO) that covers the frequency range from 3000MHz to 6000MHz and by internal dividers, with a division factor from 1 to 128, which divide the output to the desired frequency. To achieve such a broad range, several VCOs have been incorporated into this module, and they can either be selected automatically or manually by the developer. This device can be operated in both the integer-N mode and fractional-N mode Due to these features the MAX2870/MAX2871 can be used as a synthesizer for RF DACs.

#### Conclusion

RF DACs make it possible to generate broadband transmission signals from 50MHz to 1GHz with a single DAC. Due to this achievement, new types of transmitter designs with direct modulation schemes are possible. In the past, this approach has only been used for generating transmissions for quadrature-amplitude modulated (QAM) multicarrier signals in cable TV systems, or intermediate frequency signals for microwave systems employed by radar equipment and military communications systems. This new generation of DACs can also be used for other communication systems. When signals are generated digitally, the component tolerances, temperature drift, conversion losses and distortions that are caused by analog interference only play a minor role. In addition, in the case of digitally generated QAM signals, it is also possible to essentially eliminate quadrature errors and crosstalk from the local oscillator (LO feedthrough). Special attention must be paid to accounting for the spurious emissions and noise products that the digital system can produce. Further advantages include the smaller component footprint and reduced power consumption, which leads to greater integration density.

#### References

- Kuckreja Ajay, Ostrem Geir, "High-Speed DACs ease transmitter designs," Microwave & RF, August 2010

- 2. Application note 3901, "Synchronizing Multiple High-Speed Multiplexed DACs for Transmit Applications."

- 3. Stanley Chen, Jan Rabea, "Direct Waveform Synthesis," BWRC Summer Retreat 2008.

| Related Parts |                                                                               |              |

|---------------|-------------------------------------------------------------------------------|--------------|

| MAX19692      | 12-Bit, 2.3Gsps Multi-Nyquist DAC                                             |              |

| MAX19693      | 12-Bit, 4.0Gsps High-Dynamic Performance Wideband DAC                         |              |

| MAX2870       | 23.5MHz to 6000MHz Fractional/Integer-N Synthesizer/VCO                       | Free Samples |

| MAX2871       | 23.5MHz to 6000MHz Fractional/Integer-N Synthesizer/VCO                       | Free Samples |

| MAX5860       | Scalable High-Density Downstream Cable QAM Modulator                          |              |

| MAX5862       | High-Density Downstream Cable QAM Modulator                                   |              |

| MAX5868       | 16-Bit, 5Gsps Interpolating and Modulating RF DAC                             |              |

| MAX5869       | 16-Bit, 5.9Gsps Interpolating and Modulating RF DAC with JESD204B Interface   | Free Samples |

| MAX5879       | 14-Bit, 2.3Gsps Direct RF Synthesis DAC with Selectable<br>Frequency Response |              |

| MAX5882       | 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC                      | Free Samples |

|               |                                                                               |              |

DOCSIS is a registered trademark and registered service mark of Cable Television Laboratories, Inc.

#### **More Information**

For Technical Support: https://www.maximintegrated.com/en/support For Samples: https://www.maximintegrated.com/en/samples Other Questions and Comments: https://www.maximintegrated.com/en/contact

Application Note 5446: https://www.maximintegrated.com/en/an5446 APPLICATION NOTE 5446, AN5446, AN 5446, APP5446, Appnote5446, Appnote 5446 © 2018 Maxim Integrated Products, Inc.

The content on this webpage is protected by copyright laws of the United States and of foreign countries. For requests to copy this content, **contact us**.

Additional Legal Notices: https://www.maximintegrated.com/en/legal