# MAX32690 User Guide

UG7618; Rev 1; 1/2023

**Abstract:** This user guide provides application developers information on how to use the memory and peripherals of the MAX32690 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing all the peripherals, clocks, power, and startup for the device family.

# MAX32690 User Guide

## Table of Contents

| MAX32690 L | Jser Guide                                            | 2  |

|------------|-------------------------------------------------------|----|

| 1. Introd  | uction                                                | 32 |

| 1.1 Rel    | lated Documentation                                   | 32 |

| 1.2 Doc    | cument Conventions                                    | 32 |

| 1.2.1      | Number Notations                                      |    |

| 1.2.2      | Register and Field Access Definitions                 |    |

| 1.2.3      | Register Lists                                        |    |

| 1.2.4      | Register Detail Tables                                | 33 |

| 2. Overvi  | iew                                                   |    |

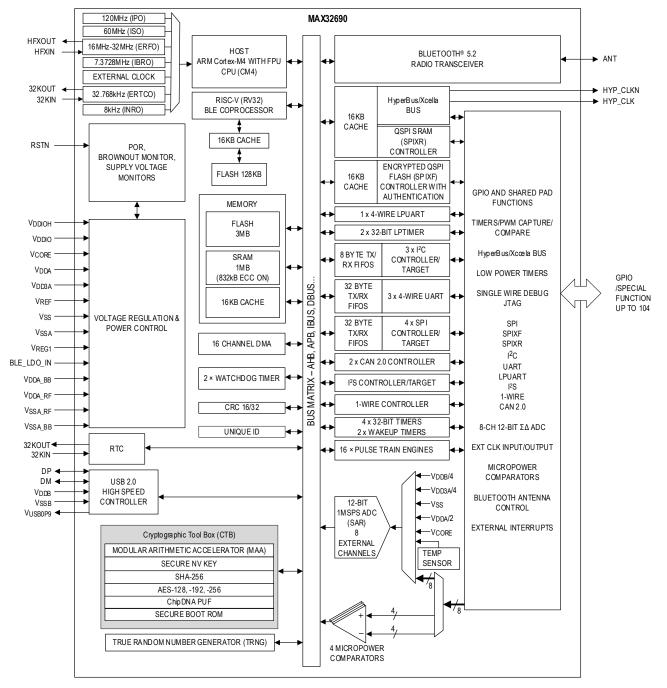

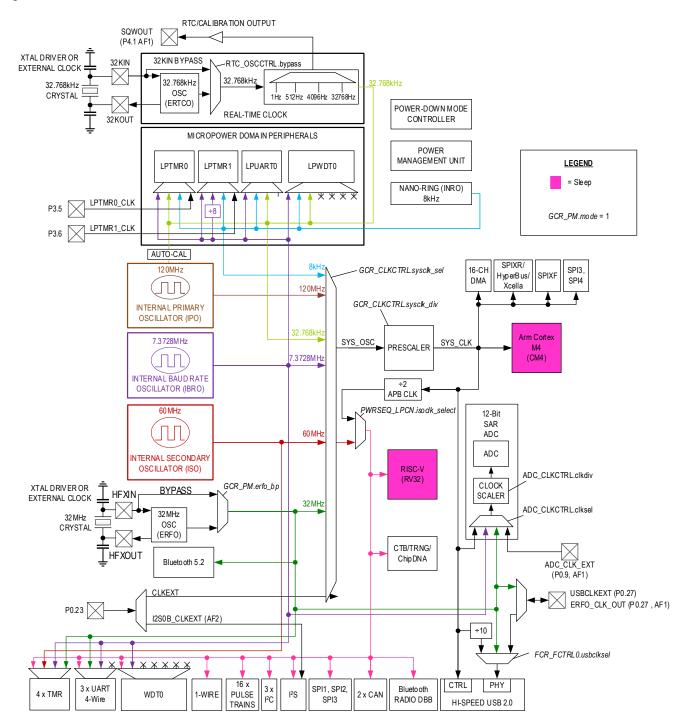

| 2.1 Blo    | nck Diagram                                           | 35 |

| 3. Memo    | pry, Register Mapping, and Access                     | 36 |

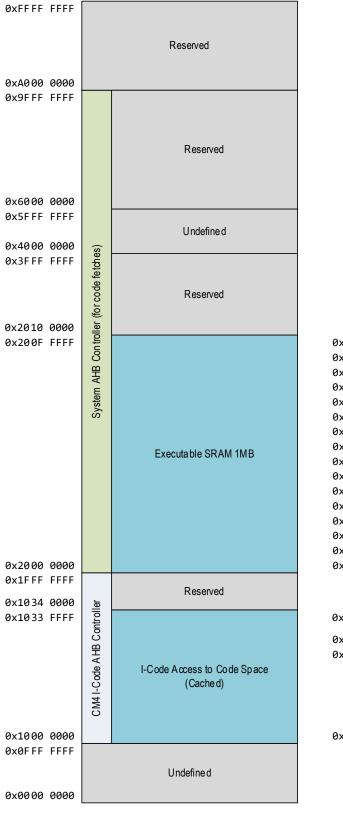

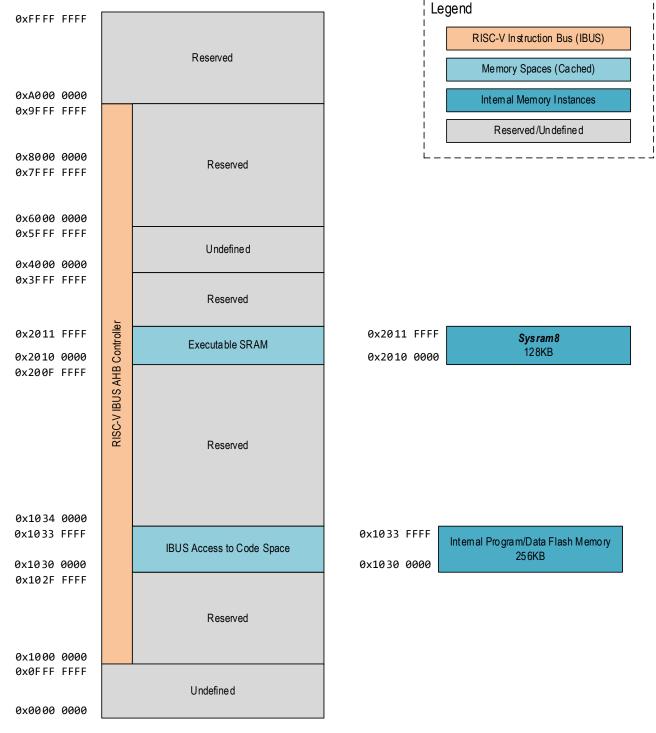

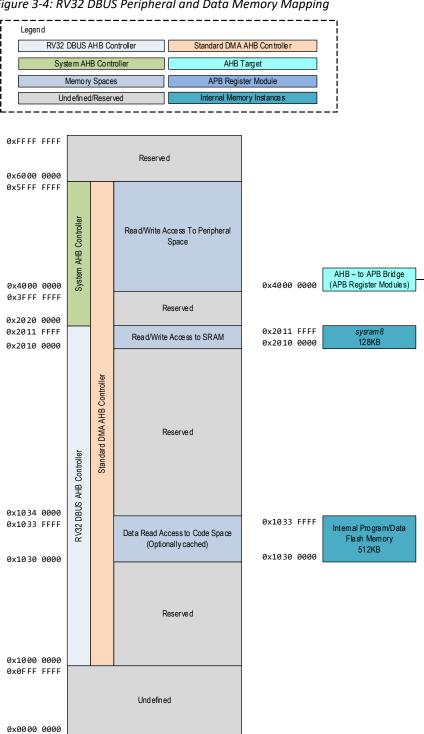

|            | emory, Register Mapping, and Access Overview          |    |

|            | Indard Memory Regions                                 |    |

| 3.2.1      | Code Space                                            |    |

| 3.2.2      | Instruction Cache Memory                              |    |

| 3.2.3      | Information Block Flash Memory                        | 41 |

| 3.2.4      | SRAM Space                                            |    |

| 3.2.5      | Peripheral Space                                      |    |

| 3.2.6      | AES Key and Working Space Memory                      |    |

| 3.2.7      | External Memory Space                                 |    |

| 3.2.8      | External Device Space                                 |    |

| 3.2.9      | System Area (Private Peripheral Bus)                  |    |

| 3.2.10     | System Area (Vendor Defined)                          |    |

| 3.3 AHI    | B Interfaces                                          |    |

| 3.3.1      | Arm Core AHB Interfaces                               |    |

| 3.3.2      | Standard DMA                                          |    |

| 3.3.3      | Crypto Toolbox                                        |    |

| 3.3.4      | USB                                                   |    |

| 3.3.5      | AHB Targets                                           |    |

| 3.4 Per    | ripheral Register Map                                 |    |

| 3.4.1      | APB Peripheral Base Address Map                       |    |

| 4. Systen  | n, Power, Clocks, Reset                               |    |

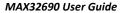

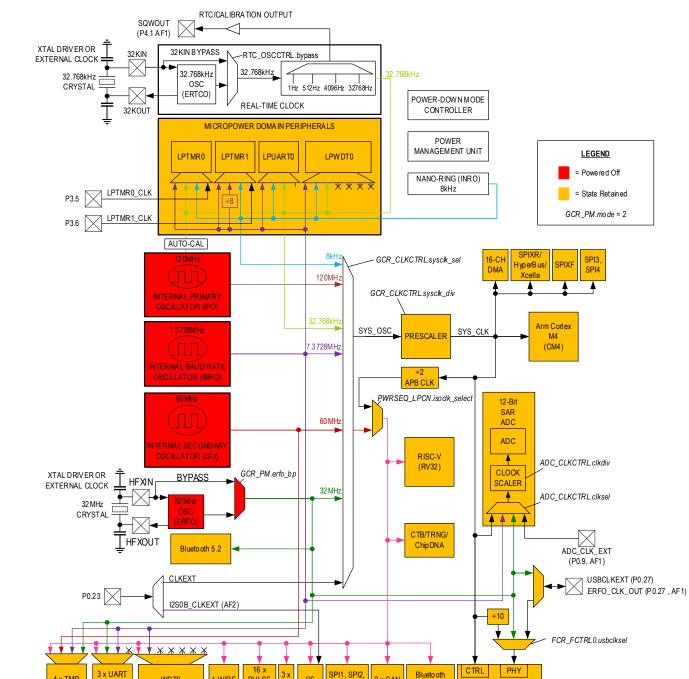

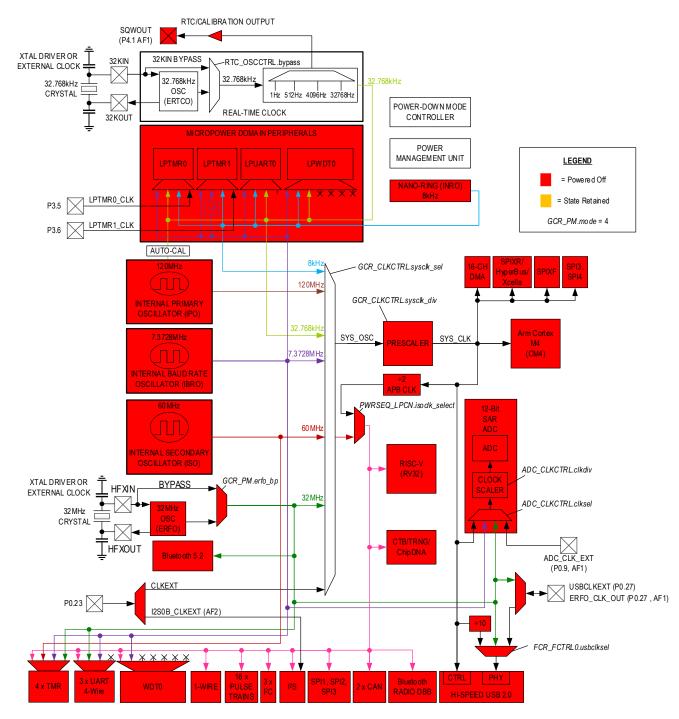

| 4.1 Osc    | cillator Sources                                      | 47 |

| 4.1.1      | 120MHz Internal Primary Oscillator (IPO)              |    |

| 4.1.2      | 32MHz External RF Oscillator (ERFO)                   |    |

| 4.1.3      | 60MHz Internal Secondary Oscillator (ISO)             |    |

| 4.1.4      | 7.3728MHz Internal Baud Rate Oscillator (IBRO)        |    |

| 4.1.5      | 32.768kHz External Real-Time Clock Oscillator (ERTCO) |    |

| 4.1.6      | 8kHz Internal Nano-Ring Oscillator (INRO)             |    |

| 4.2 Sys    | tem Oscillator (SYS_OSC)                              | 50 |

| 4.2.1            | System Oscillator Selection                       | 51  |

|------------------|---------------------------------------------------|-----|

| 4.2.2            | System Clock (SYS_CLK)                            |     |

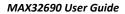

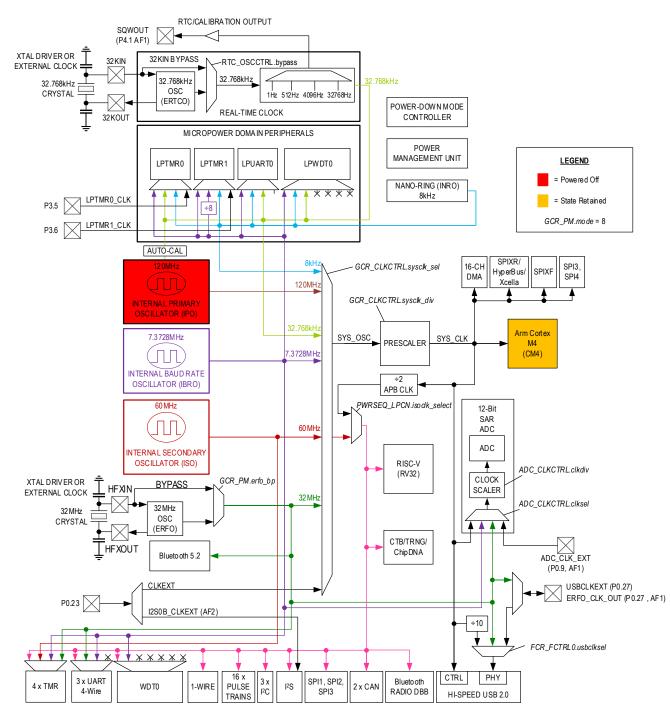

| 4.3 Op           | erating Modes                                     | 54  |

| 4.3.1            | ACTIVE Mode                                       | 54  |

| 4.3.2            | SLEEP                                             |     |

| 4.3.3            | Low-Power Mode (LPM)                              |     |

| 4.3.4            | Micropower Mode (UPM)                             |     |

| 4.3.5            | STANDBY                                           |     |

| 4.3.6            | BACKUP                                            | 62  |

| 4.3.7            | Operating Modes Wake-up Sources                   | 64  |

| 4.4 Dev          | vice Resets                                       | 64  |

| 4.4.1            | Peripheral Reset                                  | 65  |

| 4.4.2            | Soft Reset                                        |     |

| 4.4.3            | System Reset                                      | 65  |

| 4.4.4            | Power-On Reset                                    | 65  |

| 4.5 Un           | ified Internal Cache Controllers (ICC)            | 65  |

| 4.5.1            | Enabling the Instruction Cache Controller         | 65  |

| 4.5.2            | Disabling the ICC                                 |     |

| 4.5.3            | Invalidating the ICC Cache and Tag RAM            |     |

| 4.5.4            | Flushing the ICC                                  |     |

| 4.5.5            | Internal Cache Control Registers (ICC)            |     |

| 4.5.6            | ICCO Register Details                             | 66  |

| 4.6 RA           | M Memory Management                               | 67  |

| 4.6.1            | On-Chip Cache Management                          | 67  |

| 4.6.2            | RAM Zeroization                                   |     |

| 4.7 Mis          | scellaneous Control Registers (MCR)               |     |

|                  | Miscellaneous Control Register Details            |     |

| 4.7.1<br>4.8 Lov | v-Power General Control Registers (LPGCR)         |     |

|                  |                                                   |     |

| 4.8.1            | Low-Power General Control Registers Details       | 73  |

| 4.9 Pov          | wer Sequencer Registers (PWRSEQ)                  |     |

| 4.9.1            | Power Sequencer Register Details                  |     |

| 4.10             | Trim System Initialization Registers (TRIMSIR)    | 81  |

| 4.10.1           | Trim System Initialization Register Details       | 82  |

|                  | Global Control Registers (GCR)                    |     |

| 4.11.1           |                                                   |     |

|                  | System Initialization Registers (SIR)             |     |

| 4.12             |                                                   |     |

| 4.12.1           | System Initialization Register Details            |     |

| 4.13             | Function Control Registers (FCR)                  |     |

| 4.13.1           | 8                                                 |     |

| 4.14             | Global Control Function Registers (GCFR)          | 107 |

| 5. Interru       | upts and Exceptions                               | 108 |

| 5.1 CM           | 14 Interrupt and Exception Features               | 108 |

| 5.2 CM           | 14 Interrupt Vector Table                         | 108 |

| 5.3 RV.          | 32 Interrupt Vector Table                         | 111 |

| 6. Gener         | al-Purpose I/O (GPIO) and Alternate Function Pins | 113 |

| 6.1        | Instances                                                                       | 114 |

|------------|---------------------------------------------------------------------------------|-----|

| 6.2        | Configuration                                                                   | 114 |

| e          | 6.2.1 Peripheral Clock Enable                                                   | 114 |

| e          | 5.2.2 Power-On-Reset Configuration                                              | 114 |

| E          | 5.2.3 Serial Wire Debug Configuration                                           |     |

|            | 5.2.4 Pin Function Configuration                                                |     |

|            | 5.2.5 Input Mode Configuration                                                  |     |

|            | 5.2.6 Output Mode Configuration                                                 |     |

| 6.3        |                                                                                 |     |

| 6.4        | 5                                                                               |     |

|            | 5.4.1 Reset State                                                               |     |

|            | 5.4.2 Input Mode Usage                                                          |     |

|            | 5.4.3 Output Mode Usage                                                         |     |

|            | 5.4.4 Alternate Function Usage                                                  |     |

| 6.5        |                                                                                 |     |

|            | 5.5.1 GPIO Interrupt Handling                                                   |     |

|            | 5.5.2 Using GPIO for Wake-Up from Low-Power Modes                               |     |

|            | 5.5.3 Using GPIOWAKE for Wake-Up from DEEPSLEEP, BACKUP, and STORAGE            |     |

| 6.6        | 5                                                                               |     |

| -          | 5.6.1 GPIO Register Details                                                     |     |

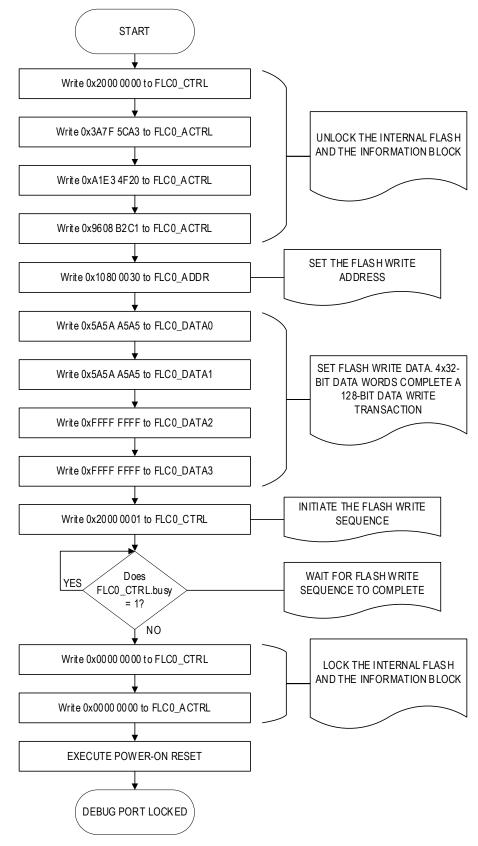

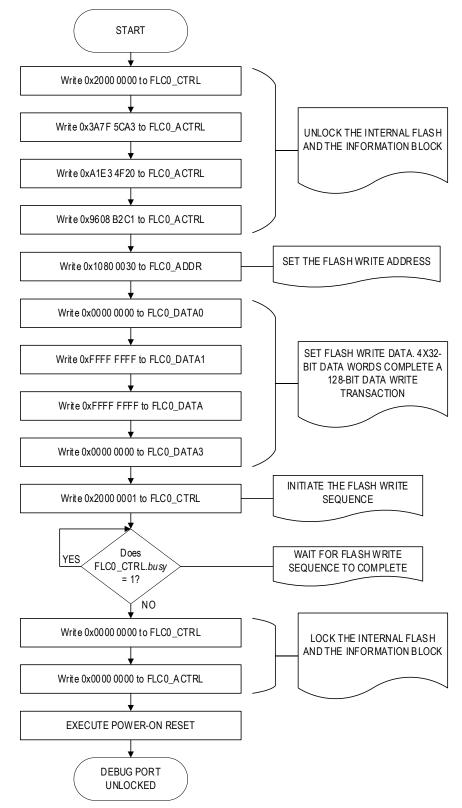

| 7. C       | Debug Access Port (DAP)                                                         | 128 |

| 7.1        | Instances                                                                       | 128 |

| 7.2        | Access Control                                                                  | 128 |

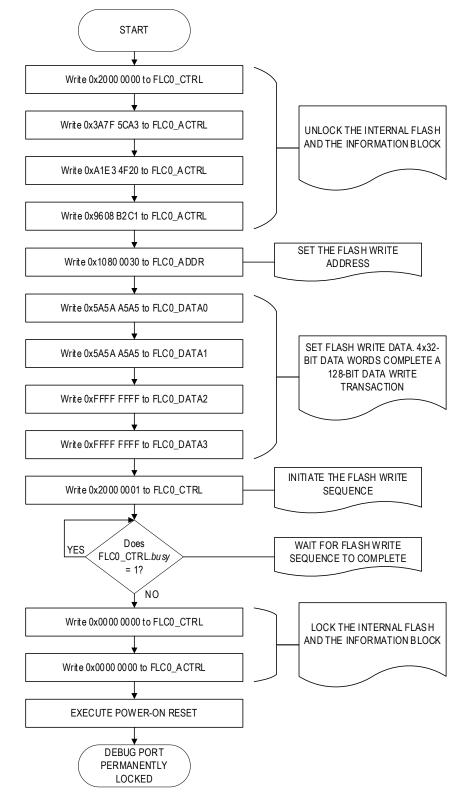

| 7          | 7.2.1 Locking the DAP                                                           | 128 |

| 7.3        | Pin Configuration                                                               | 132 |

| 8. F       | -lash Controller (FLC)                                                          | 133 |

| 8.1        | Instances                                                                       | 133 |

| 8.2        | Usage                                                                           | 133 |

|            | 3.2.1 Clock Configuration                                                       |     |

|            | 3.2.2 Lock Protection                                                           |     |

|            | 3.2.3 Flash Write Width                                                         |     |

|            | 3.2.4 Flash Write                                                               |     |

| 8          | B.2.5         Page Erase                                                        | 134 |

| 8          | 3.2.6 Mass Erase                                                                | 135 |

| 8.3        | Registers                                                                       | 135 |

| 8          | 3.3.1 Register Details                                                          | 136 |

|            | Semaphores                                                                      |     |

| 9.1        |                                                                                 |     |

| 9.2        |                                                                                 |     |

| 9.2<br>9.3 |                                                                                 |     |

|            |                                                                                 |     |

|            | 9.3.1Reset9.3.2CM4 Semaphore Interrupt Generation                               |     |

|            | 9.3.2CM4 Semaphore Interrupt Generation9.3.3RV32 Semaphore Interrupt Generation |     |

| 9.4        |                                                                                 |     |

|            |                                                                                 |     |

| L<br>L     | 9.4.1   Register Details                                                        | 143 |

| 10.   | Standard DMA (DMA)                                                                             | 148 |

|-------|------------------------------------------------------------------------------------------------|-----|

| 10.1  | Instances                                                                                      | 148 |

| 10.2  | Peripheral Clock Enable                                                                        | 149 |

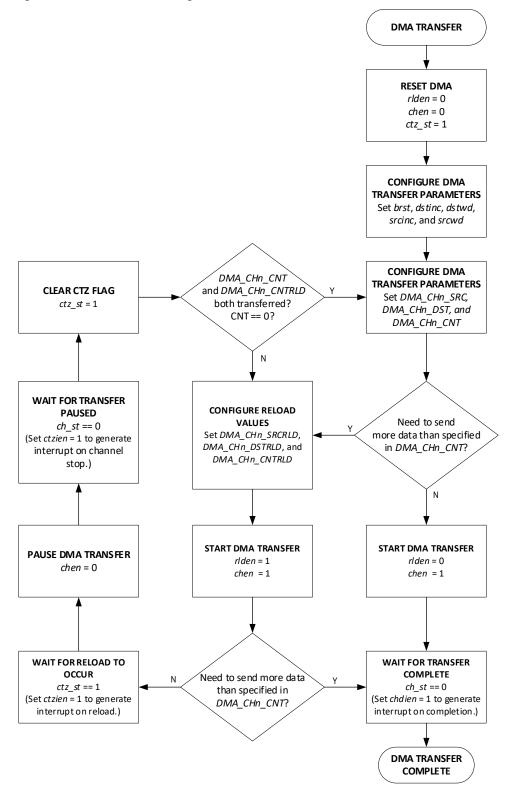

| 10.3  | DMA Channel Operation (DMA_CH)                                                                 | 149 |

| 10    | .3.1 DMA Channel Arbitration and DMA Bursts                                                    | 149 |

| 10    | .3.2 DMA Source and Destination Addressing                                                     |     |

|       | .3.3 Data Movement from Source to DMA                                                          |     |

|       | .3.4 Data Movement from DMA to Destination                                                     |     |

| 10.4  | -                                                                                              |     |

| 10.5  | Count-To-Zero (CTZ) Condition                                                                  |     |

| 10.6  | Chaining Buffers                                                                               |     |

| 10.7  | DMA Interrupts                                                                                 |     |

| 10.8  | Channel Timeout Detect                                                                         |     |

| 10.9  | Memory-to-Memory DMA                                                                           | 157 |

| 10.10 | DMA Registers                                                                                  | 157 |

| 10    | .10.1 Register Details                                                                         |     |

| 10.11 | DMA Channel Register Summary                                                                   | 157 |

| 10.12 | DMA Channel Registers                                                                          | 158 |

| 10    | .12.1 Register Details                                                                         | 158 |

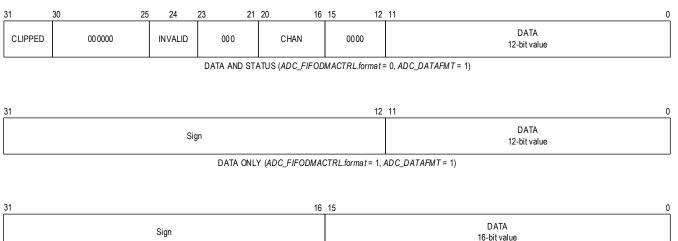

| 11.   | ADC                                                                                            | 163 |

| 11.1  | Operation                                                                                      | 163 |

| 11    | .1.1 Peripheral Clock Enable                                                                   |     |

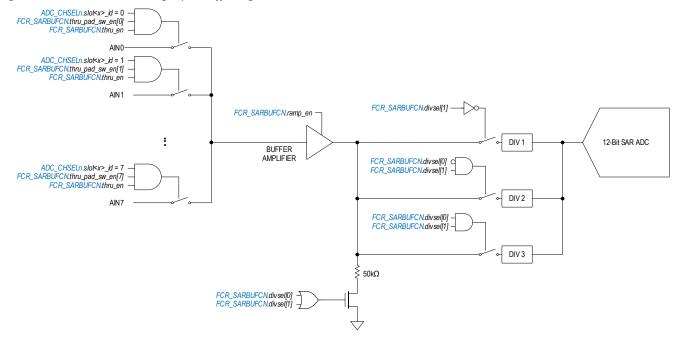

| 11.2  | Input Channels                                                                                 |     |

| 11.3  | Analog Input Buffer                                                                            |     |

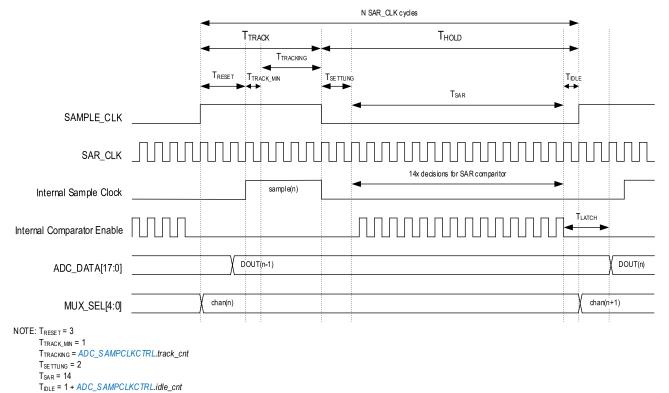

| 11.4  | Clocks and Timing                                                                              |     |

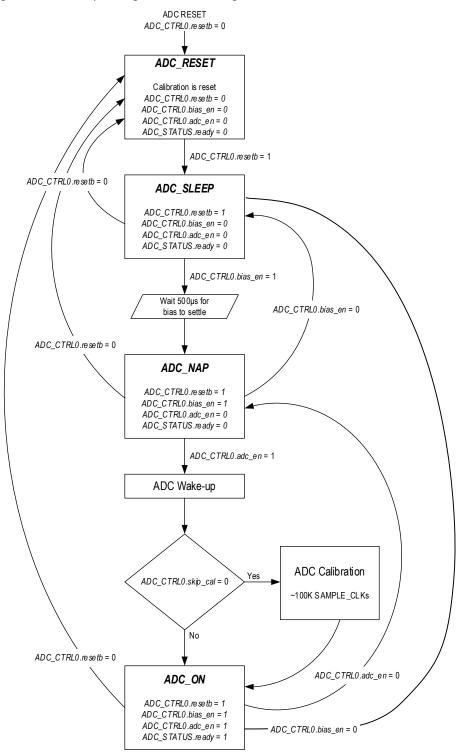

| 11.5  | Operating Modes                                                                                | 167 |

| 11    | .5.1 ADC Initialization                                                                        |     |

| 11.6  | ADC SFR Interface                                                                              | 170 |

| 11    | .6.1 Determination of Bias and Wake-up Counter Settings                                        |     |

|       | .6.2 Using the ADC SFR Interface to Load the Reference Trim, and Bias/Wake-up Counter Settings |     |

|       | .6.3 1.25V Internal Reference Trim                                                             |     |

|       | .6.4 2.048V Internal Reference Trim                                                            |     |

|       | .6.5 External Reference Trim                                                                   |     |

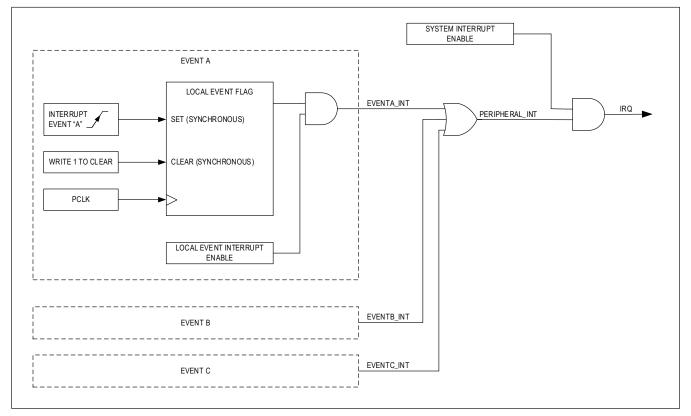

| 11.7  | Interrupts                                                                                     |     |

| 11.8  | FIFO Operation                                                                                 |     |

| 11.9  | Averaging                                                                                      |     |

| 11.10 |                                                                                                |     |

| 11.11 |                                                                                                |     |

|       | .11.1 Conversion Sequence Triggers                                                             |     |

|       | .11.2 Single Conversion Sequences                                                              |     |

|       | .11.3 Continuous Conversion Sequences                                                          |     |

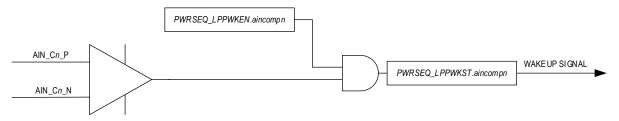

| 11.12 | Low-Power Analog Wake-Up Comparators                                                           | 181 |

| 11.13        | Registers                                                           | 182 |

|--------------|---------------------------------------------------------------------|-----|

| 11.1         | .3.1 Register Details                                               | 182 |

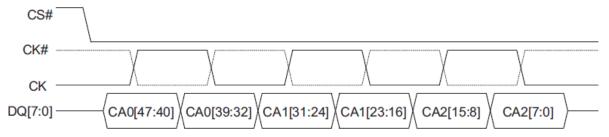

| 12.          | HyperBus/Xccela External Memory Interface (HPB)                     | 191 |

| 12.1         | HyperBus/Xccela Signal Descriptions                                 |     |

| 12.2         | Peripheral Clock Enable                                             |     |

| 12.3         | Related Specifications                                              |     |

| 12.4         | Reading and Writing to a Slave Device from Firmware                 |     |

| 12.5         | External Memory Data Cache                                          |     |

| 12.5         |                                                                     |     |

| 12.5         | 5                                                                   |     |

| 12.5         | 5.3 Invalidating the EMCC                                           | 194 |

| 12.5         | 8                                                                   |     |

| 12.5         | 0                                                                   |     |

| 12.6         | Memory Transfers                                                    |     |

| 12.7         | External Memory Reset                                               |     |

| 12.8         | Interrupts                                                          |     |

| 12.9         | Registers                                                           |     |

| 12.9         | 0.1 Register Details                                                | 197 |

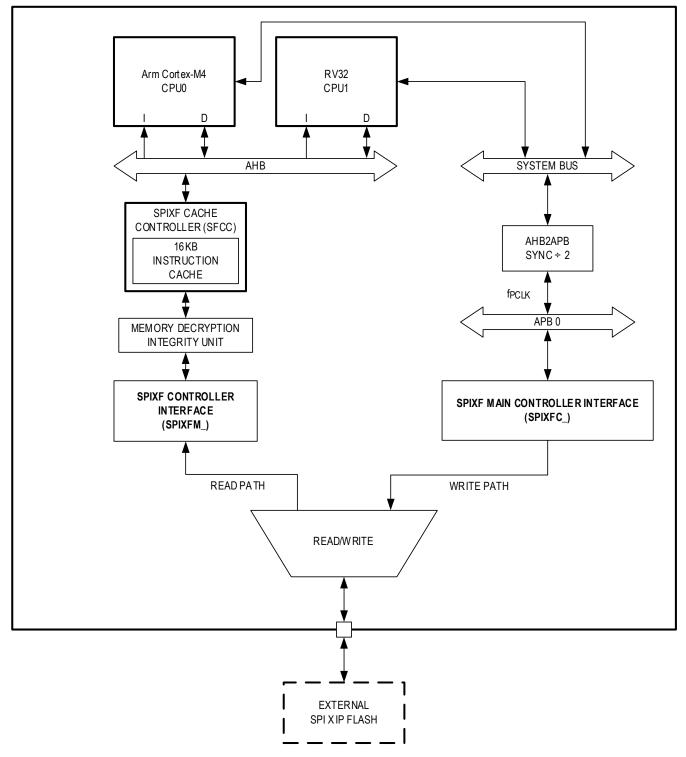

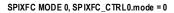

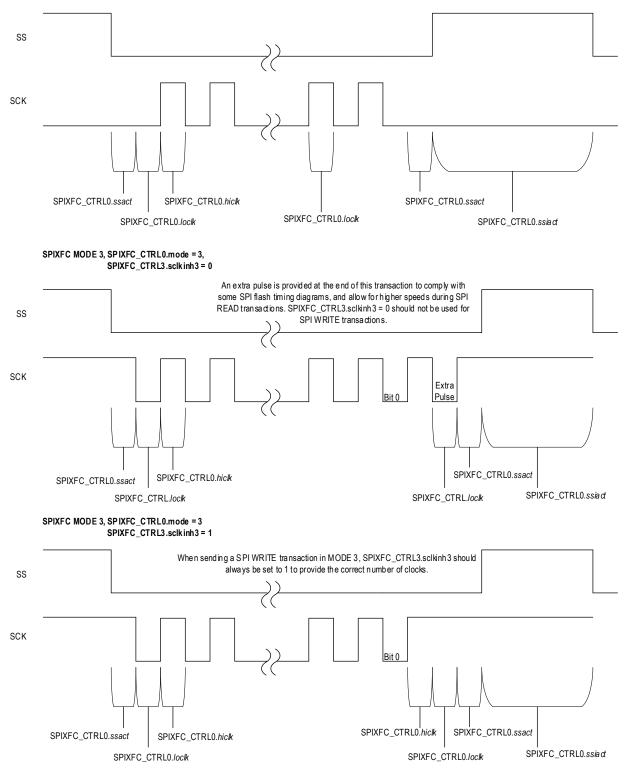

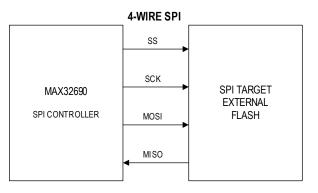

| 13.          | SPI-XiP External Memory Interface                                   |     |

| 13.1         | Overview                                                            |     |

| 13.2         | SPIXF                                                               |     |

| 13.2         |                                                                     |     |

| 13.2         |                                                                     |     |

| 13.3         | External SPI Flash Encryption                                       | 223 |

| 13.3         |                                                                     |     |

| 13.3         | 0                                                                   |     |

| 13.3         | 0                                                                   |     |

| 13.3         | 3.4 Address Translation<br>External SPI On-the-Fly Flash Decryption |     |

| 13.4         |                                                                     |     |

| 13.4         |                                                                     |     |

| 13.4         | 11 0                                                                |     |

| 13.4<br>13.4 |                                                                     |     |

| 13.4<br>13.5 | SPIXR                                                               |     |

| 13.5         |                                                                     |     |

| 13.5         |                                                                     |     |

| 13.5         | -                                                                   |     |

| 13.5         | -                                                                   |     |

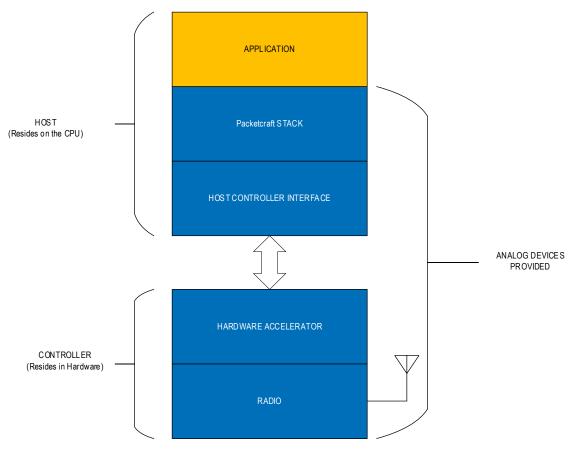

| 14.          | Bluetooth 5 Low Energy (LE) Radio                                   | 242 |

| 14.1         | Power-Efficient Design                                              |     |

| 14.2         | Bluetooth Hardware Accelerator                                      |     |

| 14.3         | Packetcraft Software Stack                                          |     |

| 14.4         | Pins                                                                |     |

| 14.5 Configuration                                               | 244 |

|------------------------------------------------------------------|-----|

| 14.5.1 Kick Starting the ERFO                                    |     |

| 14.6 Documentation                                               | 244 |

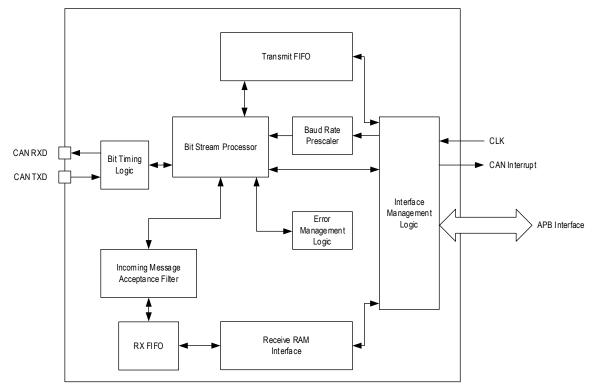

| 15. Controller Area Network (CAN)                                | 245 |

| 15.1 Instances                                                   | 246 |

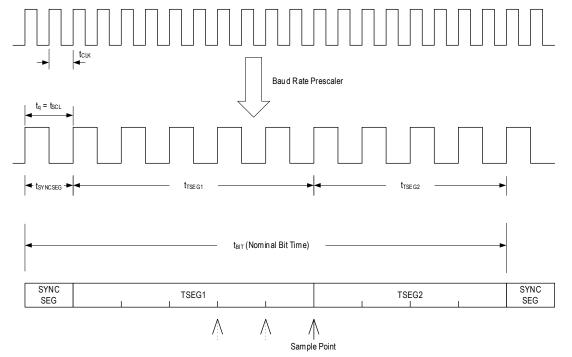

| 15.2 Bit Timing                                                  | 246 |

| 15.3 Operating Modes                                             | 247 |

| 15.3.1 Peripheral Clock Enable                                   |     |

| 15.3.2 Reset Mode                                                |     |

| 15.3.3 Normal Mode                                               |     |

| 15.3.4 Listen-Only Mode                                          |     |

| 15.3.5 Test Mode                                                 |     |

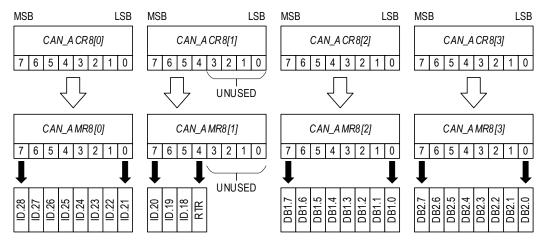

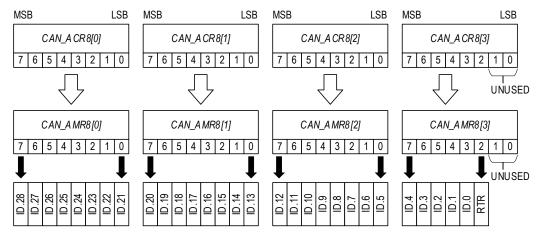

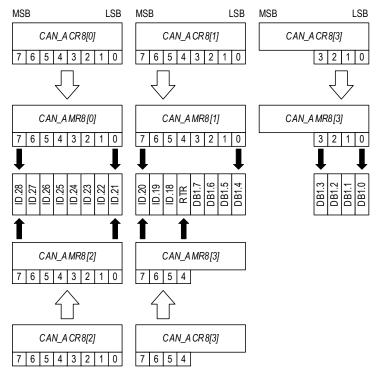

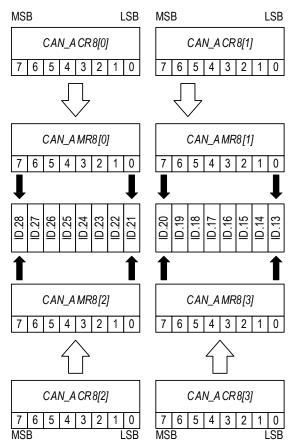

| 15.5 Acceptance Codes and Filtering                              |     |

|                                                                  |     |

| 15.5.1 Single Acceptance Filter<br>15.5.2 Dual Acceptance Filter |     |

| 15.6 FIFO Interface                                              |     |

| 15.6.1 Memory Buffer FIFO Layout for Base Frames                 | 252 |

| 15.6.2 Memory Buffer FIFO Layout for Extended Frame Messages     | 255 |

| 15.7 CAN Registers                                               | 257 |

| 15.7.1 Register Details                                          |     |

| 16. USB 2.0 High-Speed Host Interface with PHY (USBHS)           |     |

| 16.1 Instances                                                   |     |

| 16.2 USB HS Bus Signals                                          | 275 |

| 16.3 USB HS Device Endpoints                                     | 276 |

| 16.4 Peripheral Clock Enable                                     | 277 |

| 16.5 Reset and Clock                                             | 277 |

| 16.6 Suspend and Resume States                                   | 277 |

| 16.7 Packet Size                                                 | 277 |

| 16.8 Endpoint 0 Control Transactions                             | 278 |

| 16.8.1 Endpoint 0 Error Handling                                 | 278 |

| 16.9 Bulk Endpoints Operation and Options                        | 278 |

| 16.9.1 Bulk IN Endpoints                                         | 278 |

| 16.9.2 Bulk OUT Endpoints                                        |     |

| 16.10 Interrupt Endpoints                                        |     |

| 16.10.1 Interrupt IN Endpoints                                   |     |

| 16.10.2 Interrupt OUT Endpoints<br>16.11 Isochronous Endpoints   |     |

| 16.11.1 Isochronous IN Endpoints                                 |     |

| 16.11.2 Isochronous OUT Endpoints                                |     |

| 16.12 USBHS Device Registers                                     |     |

| 16.12.1 USBHS Device Register Details                            | 282 |

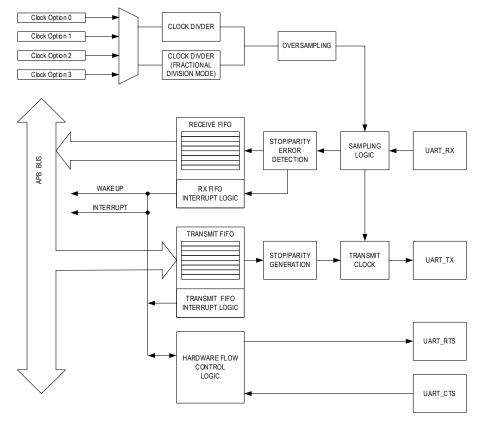

| 17. Universal Asynchronous Receiver/Transmitter (UART)           |     |

| 17.1 Instances                                                    |     |

|-------------------------------------------------------------------|-----|

| 17.1.1 Peripheral Clock Enable                                    |     |

| 17.2 DMA                                                          | 305 |

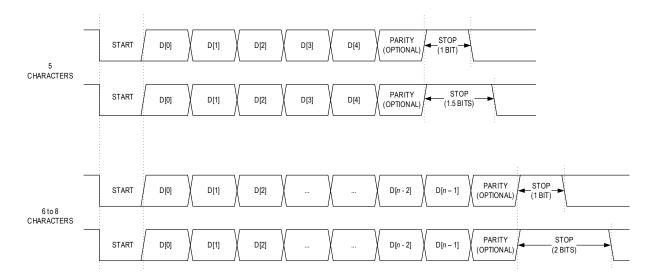

| 17.3 UART Frame                                                   |     |

| 17.4 FIFOs                                                        | 306 |

|                                                                   |     |

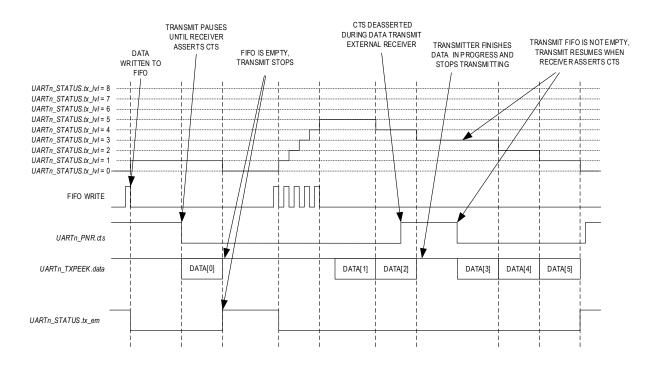

| 17.4.1 Transmit FIFO Operation                                    |     |

| 17.4.2 Flushing                                                   |     |

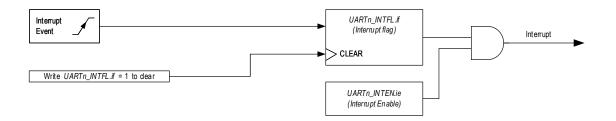

| 17.5 Interrupt Events                                             |     |

|                                                                   |     |

| 17.5.1 Frame Error<br>17.5.2 Parity Error                         |     |

| 17.5.2 Party Error                                                |     |

| 17.5.4 Overrun                                                    |     |

| 17.5.5 Receive FIFO Threshold                                     |     |

| 17.5.6 Transmit FIFO Half-Empty                                   |     |

| 17.5.7 Transmit FIFO Almost Empty                                 |     |

| 17.6 LPUART Wake-up Events                                        | 309 |

| 17.6.1 Receive FIFO Threshold                                     | 309 |

| 17.6.2 Receive FIFO Full                                          |     |

| 17.6.3 Receive Not Empty                                          |     |

| 17.7 Inactive State                                               |     |

| 17.8 Receive Sampling                                             |     |

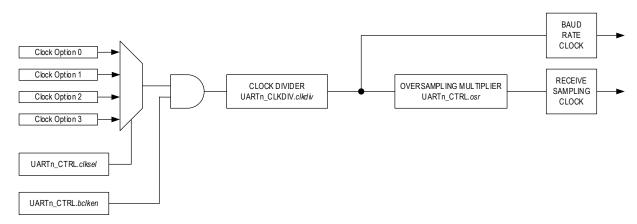

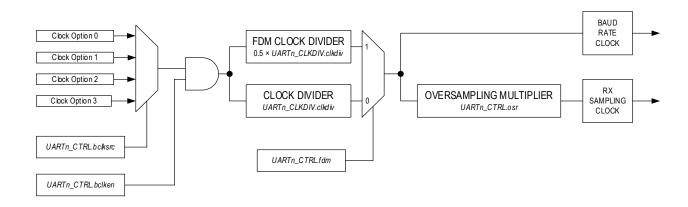

| 17.9 Baud Rate Generation                                         |     |

| 17.9.1 UART Clock Sources                                         |     |

| 17.9.1 UART Clock Sources                                         |     |

| 17.9.3 Baud Rate Calculation                                      |     |

| 17.10 Low-Power Mode Operation of LPUARTs for 9600 Baud and Below |     |

| 17.10.1 Configuring an LPUART for Low-Power Modes of Operation    |     |

| 17.10.1 Configuring an EroArt for Low-Fower Modes of Operation    |     |

|                                                                   |     |

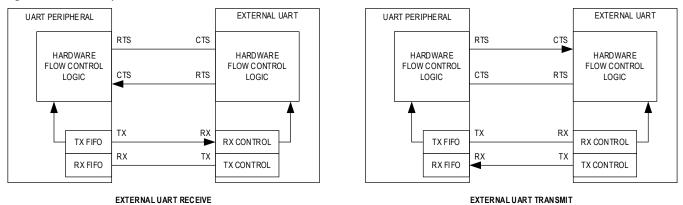

| 17.11.1Automated HFC17.11.2Software-Controlled HFC                |     |

| 17.11.2 Software-Controlled HFC <i>17.12 UART Registers</i>       |     |

| -                                                                 |     |

| 17.12.1 Register Details                                          |     |

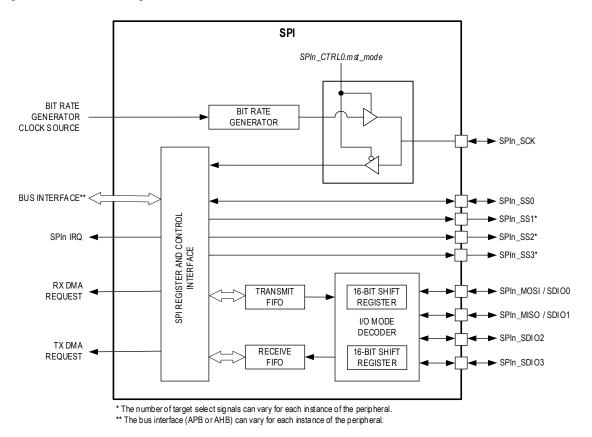

| 18. Serial Peripheral Interface (SPI)                             | 321 |

| 18.1 Instances                                                    |     |

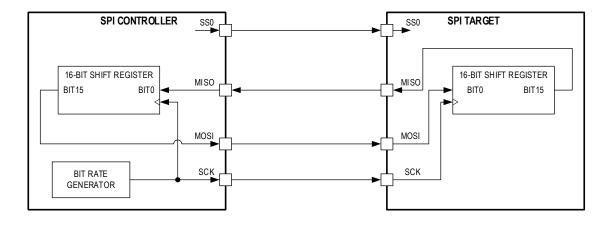

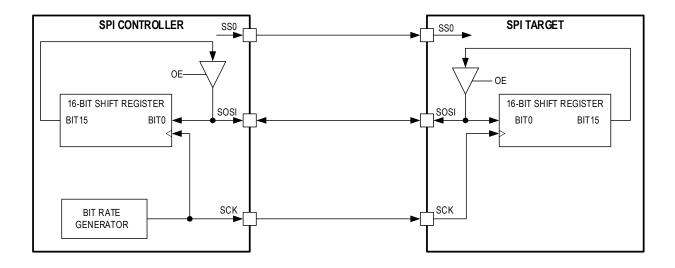

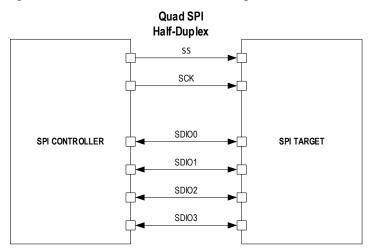

| 18.2 SPI Formats                                                  | 322 |

| 18.2.1 Four-Wire SPI                                              |     |

| 18.2.2 Three-Wire SPI                                             |     |

| 18.3 Pin Configuration                                            |     |

| 18.3.1 SPI Alternate Function Mapping                             |     |

| 18.3.2 Four-Wire Format Configuration                             |     |

| 18.3.3 Three-Wire Format Configuration                            |     |

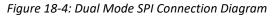

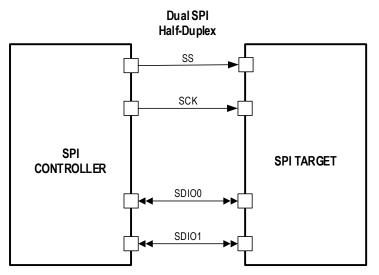

| 18.3.4 Dual Mode Format Configuration                             |     |

| 18.3.5 Quad-Mode Format Pin Configuration                         |     |

| 18.4 SPI Clock Configuration                                      |     |

| 18.4.1 Peripheral Clock Enable                                    | 326 |

|                                                                   |     |

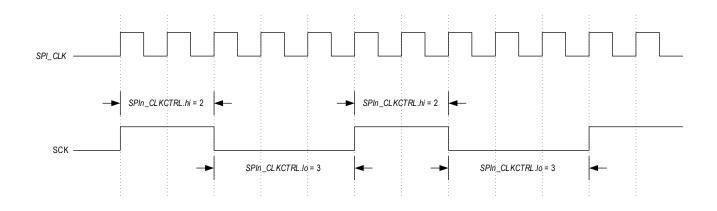

| 18.4.2 Serial Clock                                                     |     |

|-------------------------------------------------------------------------|-----|

| 18.4.3 SPI Peripheral Clock                                             |     |

| 18.4.4 Controller Mode Serial Clock Generation                          |     |

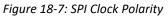

| 18.4.5 Clock Phase and Polarity Control                                 |     |

| 18.4.6 SPI FIFOs                                                        |     |

| 18.4.7 SPI Interrupts and Wake-ups                                      |     |

| 18.5 SPI Registers                                                      |     |

| 18.5.1 Register Details                                                 |     |

| 19. I <sup>2</sup> C Controller/Target Serial Communications Peripheral | 340 |

| 19.1 I <sup>2</sup> C Controller/Target Features                        | 340 |

| 19.2 Instances                                                          | 340 |

| 19.3 <i>l</i> <sup>2</sup> <i>C</i> Overview                            | 341 |

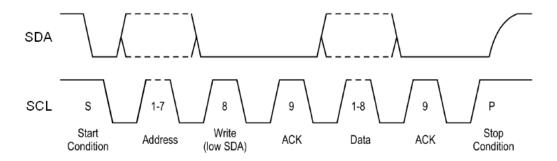

| 19.3.1 I <sup>2</sup> C Bus Terminology                                 | 341 |

| 19.3.2 I <sup>2</sup> C Transfer Protocol Operation                     | 341 |

| 19.3.3 START and STOP Conditions                                        |     |

| 19.3.4 Controller Operation                                             |     |

| 19.3.5 Acknowledge and Not Acknowledge                                  |     |

| 19.3.6 Bit Transfer Process                                             |     |

| 19.4 Configuration and Usage                                            | 343 |

| 19.4.1 Peripheral Clock Enable                                          | 343 |

| 19.4.2 SCL and SDA Bus Drivers                                          | 343 |

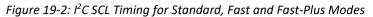

| 19.4.3 SCL Clock Configurations                                         | 343 |

| 19.4.4 SCL Clock Generation for Standard, Fast and Fast-Plus Modes      | 343 |

| 19.4.5 SCL Clock Generation for Hs-Mode                                 | 344 |

| 19.4.6 Controller Mode Addressing                                       |     |

| 19.4.7 Controller Mode Operation                                        |     |

| 19.4.8 Target Mode Operation                                            |     |

| 19.4.9 Interrupt Sources                                                |     |

| 19.4.10 Transmit FIFO and Receive FIFO                                  |     |

| 19.4.11 Transmit FIFO Preloading                                        |     |

| 19.4.12 Interactive Receive Mode (IRXM)                                 |     |

| 19.4.13 Clock Stretching                                                |     |

| 19.4.14       Bus Timeout         19.4.15       DMA Control             |     |

| 19.4.15 DMA Control                                                     |     |

|                                                                         |     |

| 19.5.1 Register Details                                                 |     |

| 20. Inter-Integrated Sound Interface (I <sup>2</sup> S)                 |     |

| 20.1 Instances                                                          |     |

| 20.1.1 I <sup>2</sup> S Bus Lines and Definitions                       |     |

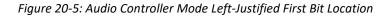

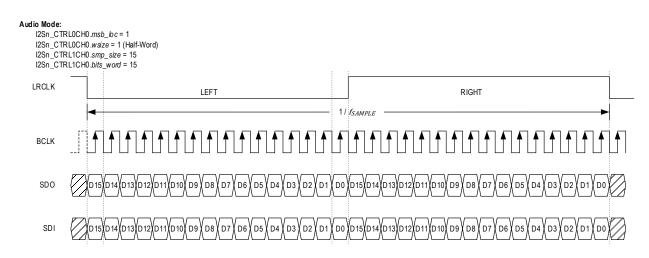

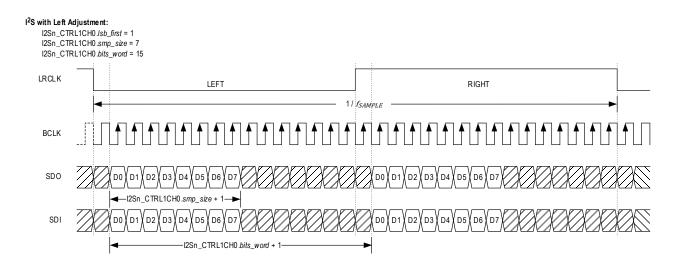

| 20.2 Details                                                            | 375 |

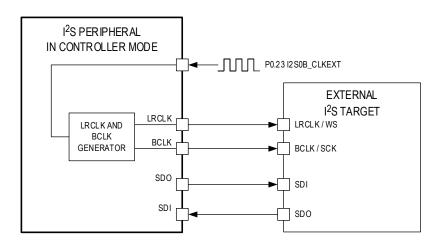

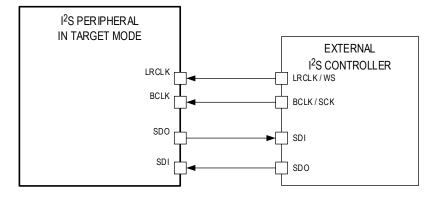

| 20.3 Controller and Target Mode Configuration                           | 376 |

| 20.4 Peripheral Clock Enable                                            | 376 |

| 20.5 Clocking                                                           | 377 |

| 20.5.1 BCLK Generation for Controller Mode                              | 377 |

| 20.5.2 LRCLK Period Calculation                                         | 378 |

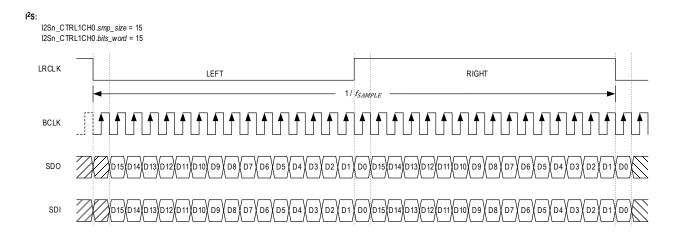

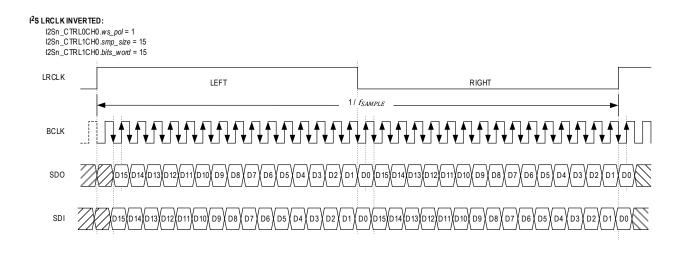

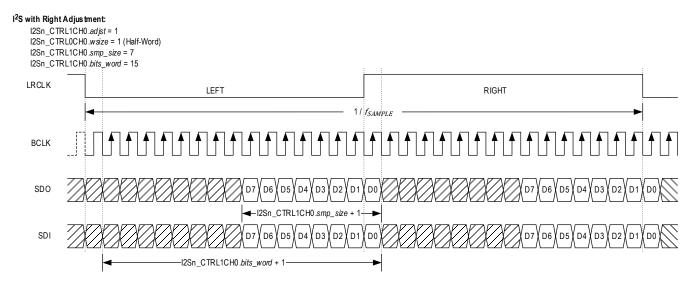

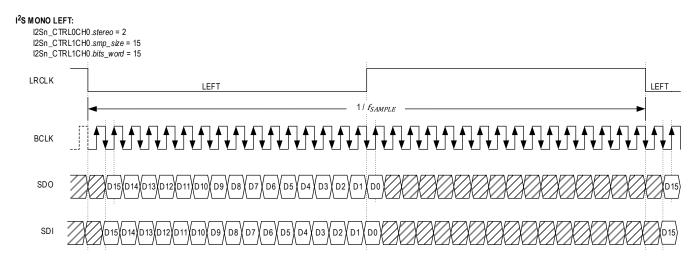

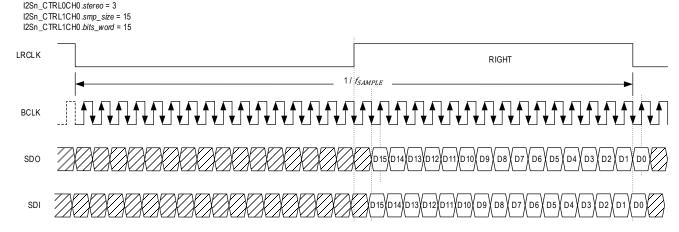

| 20.6 Data Formatting                                                    | 378 |

| 20.6.1 Sample Size                                                      | 378 |

| 20.6. |                                                         |     |

|-------|---------------------------------------------------------|-----|

| 20.6. |                                                         |     |

| 20.6. |                                                         |     |

| 20.6. | .5 Stereo/Mono Configuration Transmit and Receive FIFOs |     |

| 20.7  |                                                         |     |

| 20.7. |                                                         |     |

| 20.7. |                                                         |     |

| 20.7. |                                                         |     |

| 20.7. |                                                         |     |

| 20.7. | 0                                                       |     |

| 20.7. | 71 0                                                    |     |

| 20.8  | Interrupt Events                                        | 384 |

| 20.8. | .1 Receive FIFO Overrun                                 | 385 |

| 20.8. | .2 Receive FIFO Threshold                               | 385 |

| 20.8. | .3 Transmit FIFO Half-Empty                             | 385 |

| 20.8. | .4 Transmit FIFO One Entry Remaining                    | 385 |

| 20.9  | Direct Memory Access                                    | 385 |

| 20.10 | Block Operation                                         | 386 |

| 20.10 |                                                         |     |

| 20.11 | Registers                                               | 386 |

| 20.12 | 1.1 Register Details                                    | 386 |

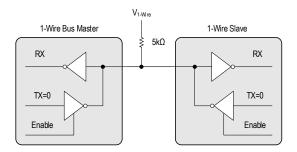

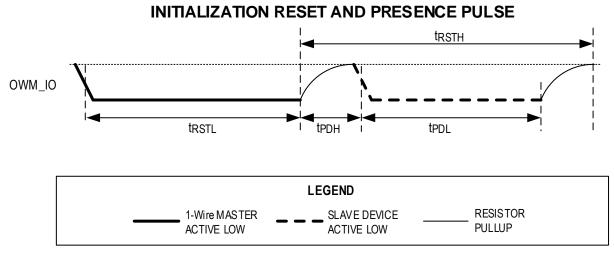

| 21. 1 | L-Wire Master (OWM)                                     |     |

|       |                                                         |     |

| 21.1  | 1-Wire Master Features                                  |     |

| 21.2  | 1-Wire Pins and Configuration                           |     |

| 21.2. |                                                         |     |

| 21.2. |                                                         |     |

| 21.2. | I                                                       |     |

| 21.2. | 8                                                       |     |

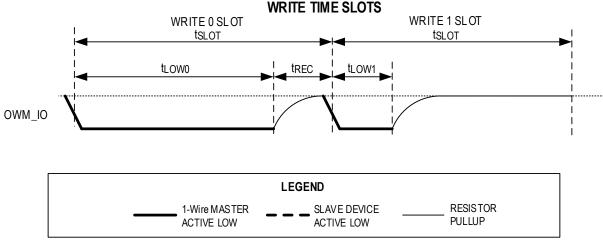

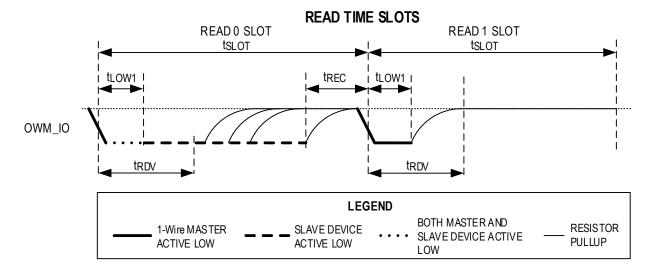

| 21.3  | 1-Wire Protocol                                         | 392 |

| 21.3. | .1 Networking Layers                                    | 393 |

| 21.3. |                                                         |     |

| 21.3. |                                                         |     |

| 21.3. |                                                         |     |

| 21.3. |                                                         |     |

| 21.3. |                                                         |     |

| 21.3. | •                                                       |     |

| 21.4  | 1-Wire Operation                                        |     |

| 21.4  |                                                         |     |

| 21.4. | 1-Wire Data Reads                                       |     |

| 21.5  |                                                         |     |

| 21.5. | 0 0                                                     |     |

| 21.5. | 5                                                       |     |

| 21.6  | Registers                                               | 401 |

| 21.6. | .1 Register Details                                     | 401 |

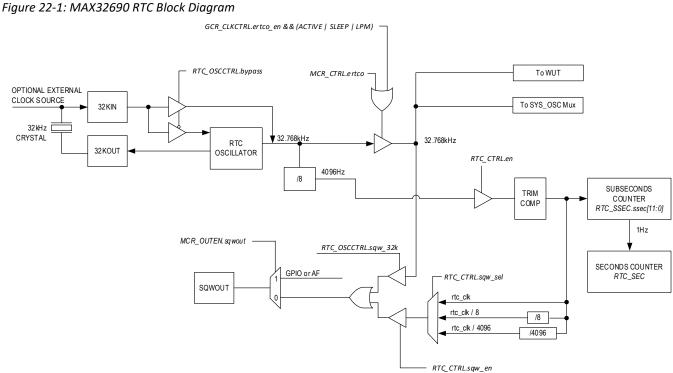

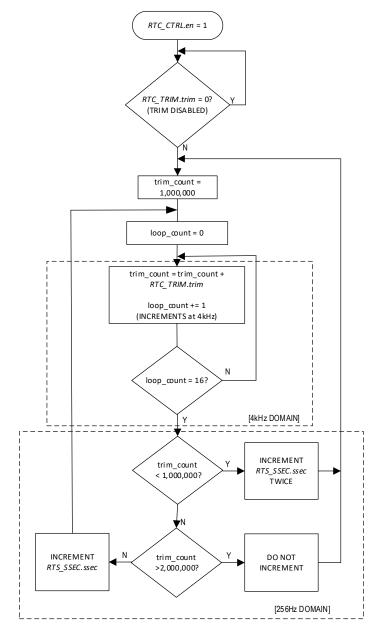

|       | Real-Time Clock (RTC)                                   |     |

| 22.1  | Overview                                                |     |

|       | Instances                                               |     |

| 22.2  |                                                         |     |

| 22.3  | Register Access Control                                 | 407 |

| 22.3.1            | RTC_SEC and RTC_SSEC Read Access Control            |     |

|-------------------|-----------------------------------------------------|-----|

| 22.3.2            | RTC Write Access Control                            |     |

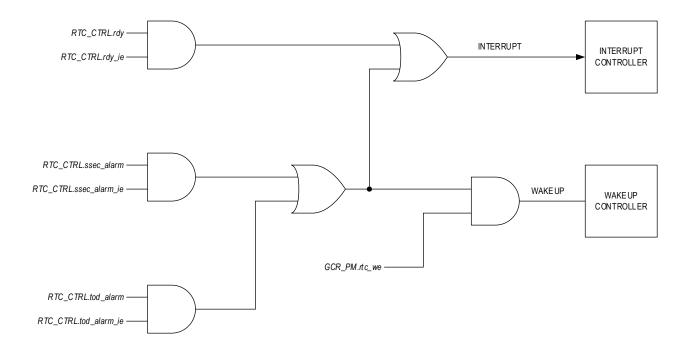

| 22.4 R            | TC Alarm Functions                                  | 408 |

| 22.4.1            | Time-of-Day Alarm                                   | 408 |

| 22.4.2            | Sub-Second Alarm                                    | 408 |

| 22.4.3            | RTC Interrupt and Wake-up Configuration             |     |

| 22.5 Sc           | quare Wave Output                                   | 410 |

| 22.6 R            | TC Calibration                                      |     |

| 22.7 R            | egisters                                            |     |

| 22.7.1            | Register Details                                    | 413 |

| 23. Time          | ers (TMR/LPTMR)                                     |     |

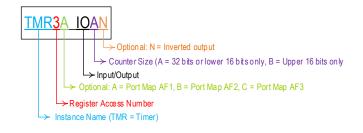

| 23.1 In           | stances                                             | 418 |

| 23.2 B            | asic Timer Operation                                | 418 |

| 23.2.1            | Peripheral Clock Enable                             | 418 |

| 23.3 3.           | 2-Bit Single / 32-Bit Cascade / Dual 16-Bit         | 419 |

| 23.4 Ti           | imer Clock Sources                                  |     |

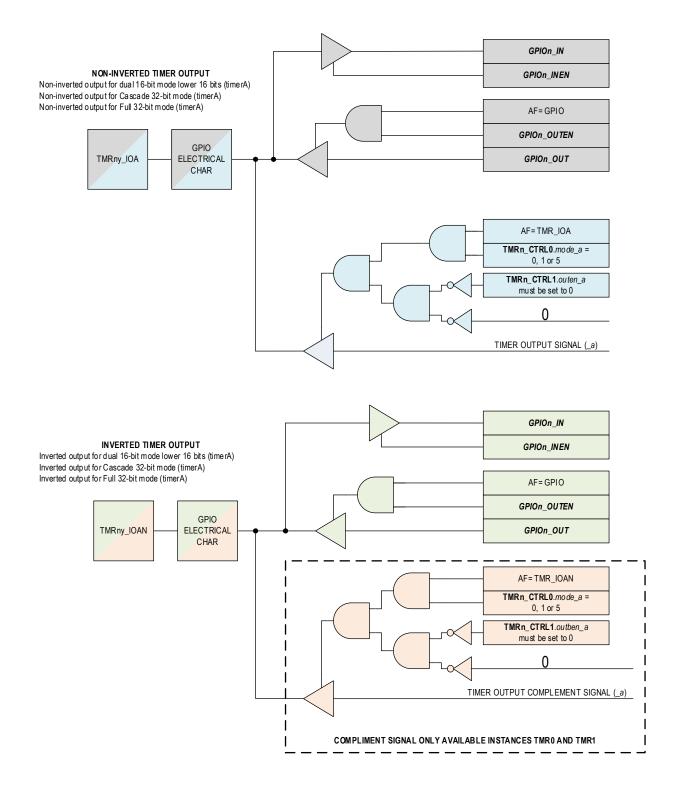

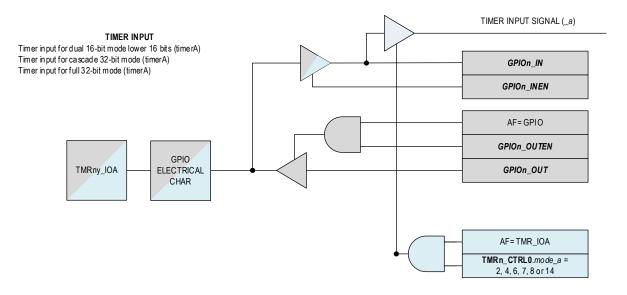

| 23.5 Ti           | imer Pin Functionality                              |     |

| 23.6 W            | /ake-up                                             |     |

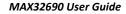

| 23.7 O            | perating Modes                                      | 423 |

| 23.7.1            | One-Shot Mode (0)                                   |     |

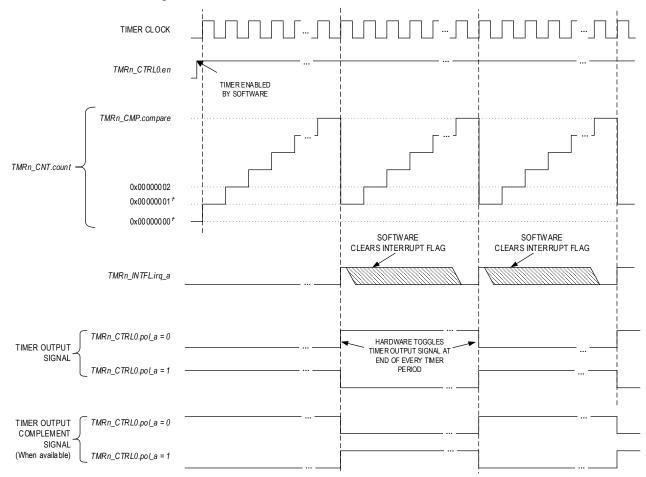

| 23.7.2            | Continuous Mode (1)                                 |     |

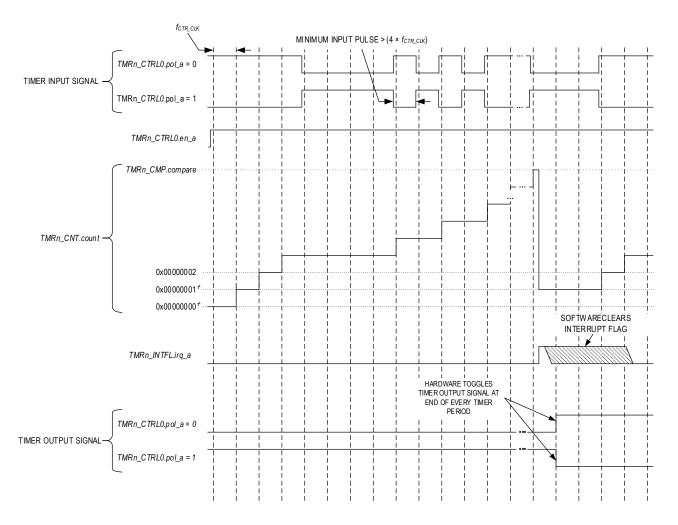

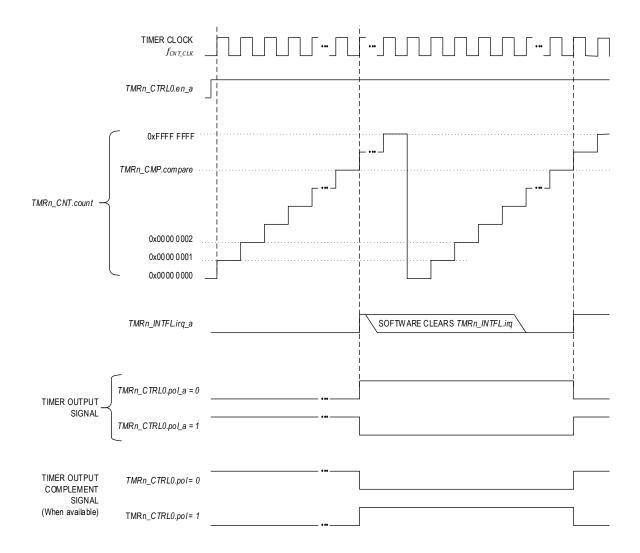

| 23.7.3            | Counter Mode (2)                                    | 429 |

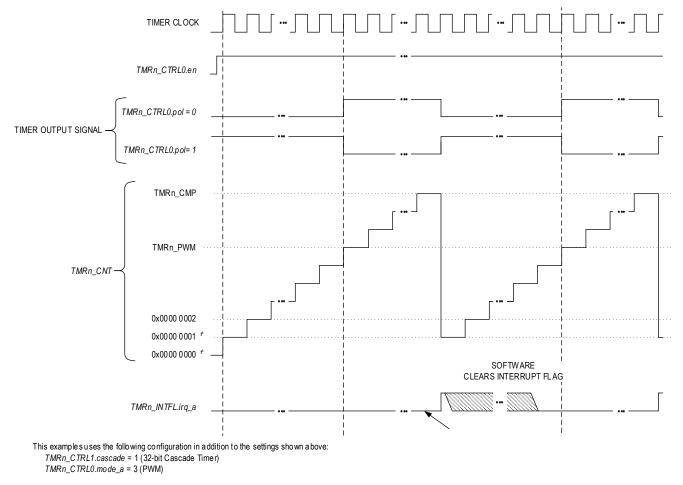

| 23.7.4            | PWM Mode (3)                                        |     |

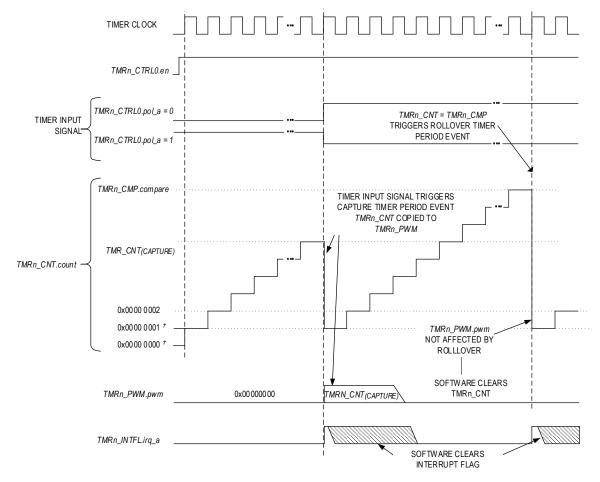

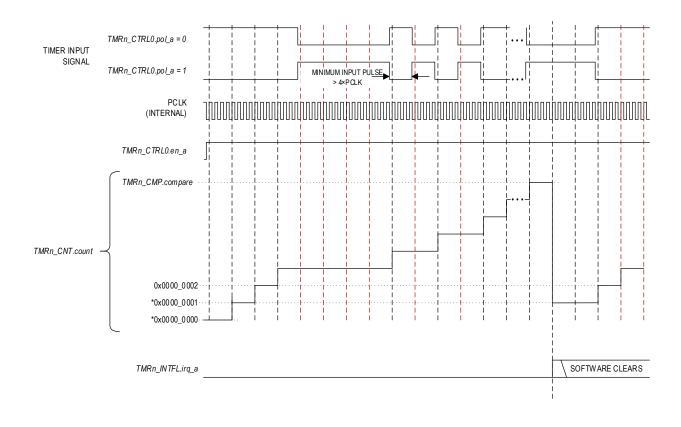

| 23.7.5            | Capture Mode (4)                                    |     |

| 23.7.6            | Compare Mode (5)                                    |     |

| 23.7.7            | Gated Mode (6)                                      |     |

| 23.7.8            | Capture/Compare Mode (7)                            |     |

| 23.7.9<br>23.7.10 | Dual Edge Capture Mode (8) Inactive Gated Mode (14) |     |

|                   | egisters                                            |     |

| 23.8.1            | Register Details                                    |     |

|                   | xe-Up Timer (WUT)                                   |     |

| 24.1 In           | stances                                             |     |

| 24.2 B            | asic Operation                                      |     |

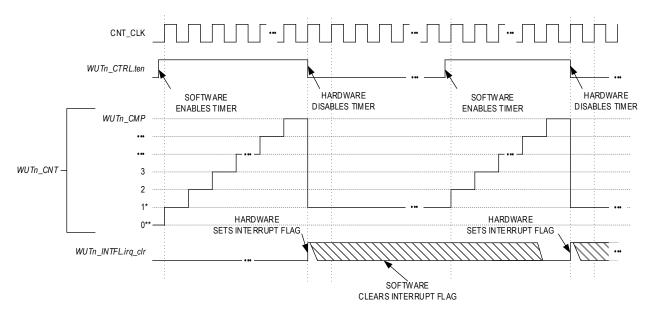

|                   | ne-Shot Mode (0)                                    |     |

| 24.3.1            | One-Shot Mode Timer Period                          |     |

| 24.3.2            | One-Shot Mode Configuration                         |     |

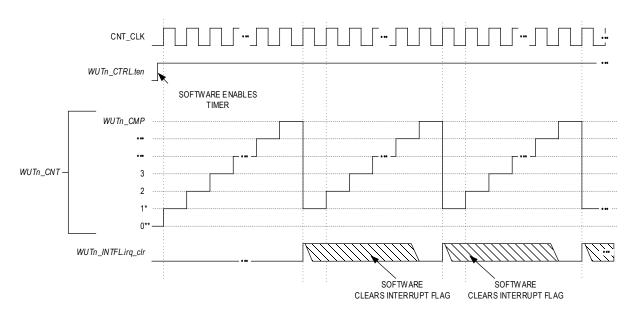

|                   | ontinuous Mode (1)                                  |     |

| 24.4.1            | Continuous Mode Timer Period                        |     |

| 24.4.2            | Continuous Mode Configuration                       |     |

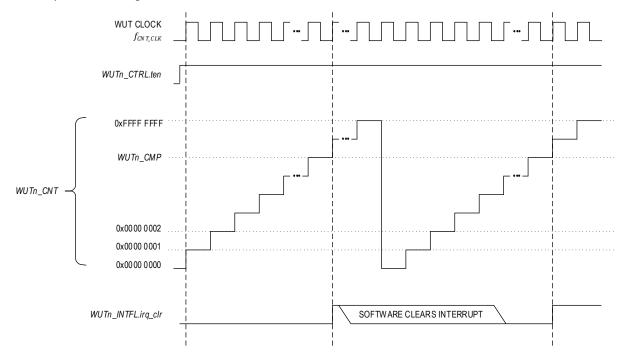

| 24.4.3            | Compare Mode (5)                                    |     |

| 24.5 R            | egisters                                            |     |

| 24.5.1            | Register Details                                    |     |

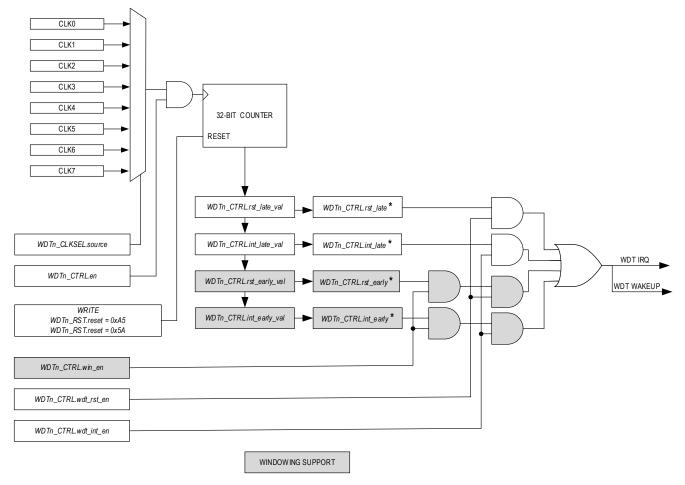

| 25. Wat           | chdog Timer (WDT)                                   | 458 |

| 25.2       Peripheral Clack Enable       459         25.3       Using the WDT as a Long-Interval Timer       460         25.3.1       Using the WDT as a Long-Interval Wake-up Timer       460         25.4       WDT Fead Sequence       460         25.5       WDT Early Reset       462         25.5.1       WDT Early Reset       462         25.5.2       WDT Early Reset       463         25.5.4       WDT Late Reset       463         25.5.4       WDT Late Reset       463         25.5       WDT Late Reset       464         25.6       Initializing the WDT       465         25.7       Resets       465         25.8       Registers       466         25.9       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.4       Engine       470         26.5       Robing and Disabling a Pulse Train Output Modes       470         26.6       Atomic Enable       470         26.6       Atomic Disable       471         26.6       Atomic Disable       472         26.6       Atomic Disable       472 <th>25.1</th> <th>Instances</th> <th> 459</th>                     | 25.1  | Instances                                    | 459 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------|-----|

| 25.3.1       Using the WDT as a Long-Interval Wake-up Timer       460         25.4       WDT Feed Sequence       460         25.5       WDT Early Reset       462         25.5.1       WDT Early Reset       463         25.5.2       WDT Early Reset       463         25.5.3       WDT Early Reset       463         25.5.4       WDT Early Reset       463         25.5.7       MDT Early Reset       464         25.6       initializing the WDT       465         25.7       Resets       466         25.8       Registers       466         25.8       Registers       466         25.8       Register Details       466         26.8       Fulse Train Engine (PT)       470         26.4       Engine       470         26.5       Furbing and Disabling o Pulse Train Output Modes       470         26.4       Engine       470         26.5       Furbing and Disabling o Pulse Train Output       472         26.6       Atomic Pulse Train Atomic Enable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Enable       473         26.7       Halt                                                         | 25.2  | Peripheral Clock Enable                      | 459 |

| 25.3.2       Using the WDT as a Long-Interval Wake-up Timer       460         25.4       WDT Feed Sequence       460         25.5       WDT Events       462         25.5.1       WDT Early Interrupt       463         25.5.2       WDT Early Interrupt       463         25.5.4       WDT Late Interrupt       463         25.5.4       WDT Late Interrupt       464         25.6       Initializing the WDT       465         25.7       Register Details       466         25.8.1       Register Details       466         25.8.1       Register Details       466         25.8       Register Details       466         25.8.1       Register Details       466         25.8       Register Details       466         25.8       Register Details       466         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabiling a Pulse Train Output       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Enable </td <td>25.3</td> <td>Usage</td> <td> 460</td>          | 25.3  | Usage                                        | 460 |

| 25.4       WDT Feed Sequence       460         25.5       WDT Events       462         25.5.1       WDT Early Reset       463         25.5.2       WDT Early Reset       463         25.5.3       WDT Late Reset       463         25.6       Initializing the WDT       465         25.7       Resets       465         25.8       Registers       466         25.8.1       Registers       466         26.6       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Finabing and Disabing a Vuster Train Output Modes       470         26.4       Engine       470         26.5       Finabing and Disabing a Vuster Train Output       472         26.6       Pulse Train Output Modes       472         26.6.1       Pulse Train Atomic Enable       472         26.7       Holt and Disable       472         26.8       Interrupts       473         26.9       Registero Etails       474         27.1                                                                                           | 25.3. |                                              |     |

| 25.5       WDT Events       462         25.5.1       WDT Early Interrupt       663         25.5.2       WDT Late Niterrupt       663         25.5.4       WDT Late interrupt       664         25.6       Intilizing the WDT       465         25.7       Resists       465         25.8       Register Details       466         25.7       Resister       466         25.8       Register Details       466         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output Modes       470         26.6       Atomic Pulse Train Atomic Enable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Enable       473         26.6.1       Pulse Train Atomic Enable       473         26.6.2       Pulse Train Atomic Enable       473         26.6.3       Interrupts       473         26.6.4       Intoruptise       473                                                                                     |       |                                              |     |

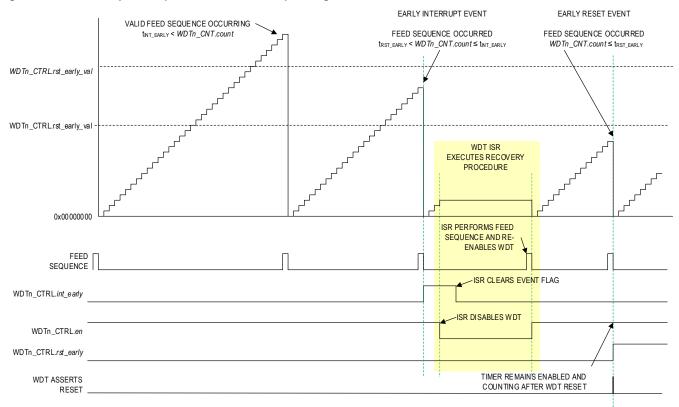

| 25.5.1       WDT Early Reset       462         25.5.2       WDT Late Reset       463         25.5.3       WDT Late Interrupt       464         25.6       Initializing the WDT       465         25.7       Resets       465         25.8       Registers       466         25.8       Registers       466         25.8       Register Details       466         26.1       Instances       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output Modes       470         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Output Enable and Disable       472         26.6.2       Pulse Train Atomic Disable       473         26.5.3       Interrupts       473         26.4       Interrupts       473         26.5       Instance Clock Enable       472         26.6       Atomic Pulse Train Output Enable and Disable       473         26.7       Hait and Disable                                                                  |       |                                              |     |

| 25.5.2       WDT Early Interrupt       463         25.5.3       WDT Late Interrupt       464         25.6       Initializing the WDT       465         25.7       Resets       465         25.8       Registers       466         25.8.1       Register Details       466         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling o Pulse Train Output Modes       470         26.4       Engine       470         26.5       Enabling and Disabling o Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Disable       472         26.6.2       Pulse Train Atomic Disable       472         26.6.3       Interrupts       473         26.9       Registers       473         26.9       Registers       473         26.9       Registers       473         26.1       Register Details       474         27.1       Peripheral Clock Enable       472                                                                       |       |                                              |     |

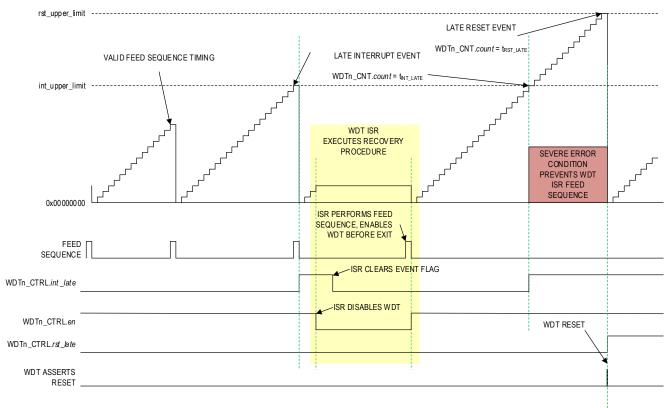

| 25.5.3       WDT Late Reset       463         25.6       Initializing the WDT       464         25.7       Resets       465         25.8       Register Details       466         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       470         26.6.1       Pulse Train Atomic Disable       472         26.6       Atomic Pulse Train Output Enable       472         26.6       Atomic Pulse Train Atomic Disable       473         26.7       Holt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.8       Interrupts       473         26.9       Register Details       473         27.0       Cryptographic Toolbox (CTB)       488                                                                                               |       | ,                                            |     |

| 25.6       Initializing the WDT       465         25.7       Resets       465         25.8       Registers       466         25.8.1       Register Details       466         25.8.1       Register Details       466         25.8.1       Register Details       466         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Knodes       470         26.5.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Momic Disable       472         26.6.3       Interrupts       473         26.6.4       Interrupts       473         26.5       Halt and Disable       472         26.6.4       Interrupts       473         26.5       Pulse Train Atomic Enable       473         26.6       Atomic Pulse Train Momic Disable       473         26.7       Halt and Disable       473         26.8       Interrupts       473 <tr< td=""><td></td><td>, , ,</td><td></td></tr<>                                      |       | , , ,                                        |     |

| 25.7       Rests       465         25.8       Registers       466         25.8.1       Register Details       466         26.       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Modes       470         26.6.1       Pulse Train Output Enable and Disable       472         26.6.2       Pulse Train Atomic Enable       472         26.6.3       Interrupts       473         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       473         26.8       Interrupts       473         26.9.1       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.3       CT                                                        | 25.5. | 4 WDT Late Interrupt                         | 464 |

| 25.8       Registers       466         25.8.1       Register Details       466         26.       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Modes       470         26.5       Enabling and Disable and Disable       472         26.6       Atomic Pulse Train Atomic Enable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       472         26.6.3       Interrupts       473         26.6.4       Interrupts       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9.1       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488                                                                 | 25.6  | Initializing the WDT                         | 465 |

| 25.8.1       Register Details       466         26.       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Modes       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       472         26.6.3       Interrupts       473         26.6       Interrupts       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOS       488                                                                 | 25.7  | Resets                                       | 465 |

| 26.       Pulse Train Engine (PT)       470         26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.4       Engine       470         26.4       Engine       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       473         26.6.3       Interrupts       473         26.6.4       Interrupts       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization <t< td=""><td>25.8</td><td>Registers</td><td> 466</td></t<>          | 25.8  | Registers                                    | 466 |

| 26.1       Instances       470         26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Frabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6       Atomic Pulse Train Atomic Enable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       472         26.6.3       Interrupts       473         26.6       Interrupts       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       488         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       491         27.5.1       Hash                                                        |       |                                              |     |

| 26.2       Peripheral Clock Enable       470         26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Enable       472         26.6.3       Pulse Train Atomic Disable       472         26.6.4       Interrupts       473         26.6.5       Pulse Train Atomic Disable       473         26.6.6       Nuse Train Atomic Disable       473         26.6.1       Pulse Train Atomic Disable       473         26.6.2       Pulse Train Atomic Disable       473         26.6.3       Interrupts       473         26.4       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.4       Block Cipher Engine       490                                               | 26. P | Pulse Train Engine (PT)                      |     |

| 26.3       Features       470         26.4       Engine       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Enable       472         26.6.3       Pulse Train Atomic Enable       472         26.6.4       Halt and Disable       472         26.6.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.5.1       Hash Operation       491         27.5.1       Hash Operation       491         27.5.1       Hash Operation       493         27.6 <t< td=""><td>26.1</td><td>Instances</td><td> 470</td></t<> | 26.1  | Instances                                    | 470 |

| 26.4       Engine       470         26.4.1       Pulse Train Output Modes       470         26.5       Enabling and Disabling a Pulse Train Output       472         26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       472         26.6.3       Pulse Train Atomic Disable       472         26.6.4       Interrupts       473         26.6       Registers       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       488         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.5.1       Hash Operation       491         27.5.1       Hash Operation       493         27.6       Hamming Code Operation       493         27                                               | 26.2  | Peripheral Clock Enable                      |     |

| 26.4.1       Pulse Train Output Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26.3  | Features                                     | 470 |

| 26.5       Enabling and Disabling a Pulse Train Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26.4  | Engine                                       | 470 |

| 26.6       Atomic Pulse Train Output Enable and Disable       472         26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       472         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.5.1       Hash Operation       491         27.5.1       Hash Operation       493         27.6.1       Hamming Code Operation       493                                                                                                                                                                                                                                                                               | 26.4. | 1 Pulse Train Output Modes                   | 470 |

| 26.6.1       Pulse Train Atomic Enable       472         26.6.2       Pulse Train Atomic Disable       473         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5.1       Hash Operation       493         27.6.1       Hamming Code Operation       494                                                                                                                                                                                                                                                                                                                                                                     | 26.5  | Enabling and Disabling a Pulse Train Output  | 472 |

| 26.6.2       Pulse Train Atomic Disable       472         26.7       Halt and Disable       473         26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       489         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5.1       Hash Operation       493         27.6.1       Hamming Code Operation       494                                                                                                                                                                                                                                                                                                                                                                                                                              | 26.6  | Atomic Pulse Train Output Enable and Disable | 472 |

| 26.7       Halt and Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26.6. |                                              |     |

| 26.8       Interrupts       473         26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       491         27.5       Hash Engine       491         27.5.1       Hash Operation       493         27.6.1       Hamming Code Operation       493                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                              |     |

| 26.9       Registers       473         26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5       Hash Operation       493         27.6.1       Hamming Code Operation       493                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                              |     |

| 26.9.1       Register Details       474         27.       Cryptographic Toolbox (CTB)       488         27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5       Hash Operation       493         27.6.1       Hamming Code Engine       493                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                              |     |

| 27.       Cryptographic Toolbox (CTB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26.9  | -                                            |     |

| 27.1       Peripheral Clock Enable       488         27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5       Hash Operation       491         27.6       Hamming Code Engine       493         27.6.1       Hamming Code Operation       494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                                              |     |

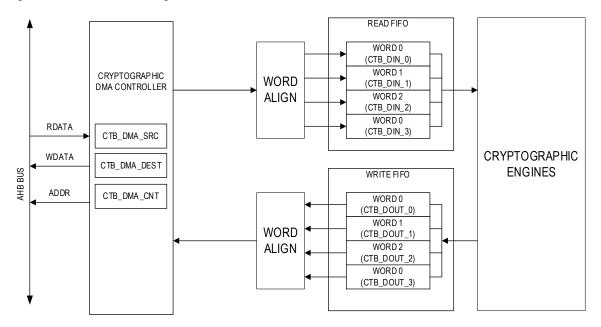

| 27.2       Cryptographic DMA (CDMA)       488         27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.5       Hash Engine       491         27.5.1       Hash Operation       493         27.6       Hamming Code Engine       493         27.6.1       Hamming Code Operation       494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27. C |                                              |     |

| 27.3       CTB FIFOs       489         27.4       Block Cipher Engine       490         27.4.1       Cipher Key Storage and Initialization       490         27.4.2       Operation       491         27.4.3       AES GCM and CCM       491         27.5       Hash Engine       491         27.6.1       Hamming Code Engine       493         27.6.1       Hamming Code Operation       494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27.1  |                                              |     |