- 1. Data Converter History

- 2. Fundamentals of Sampled Data Systems

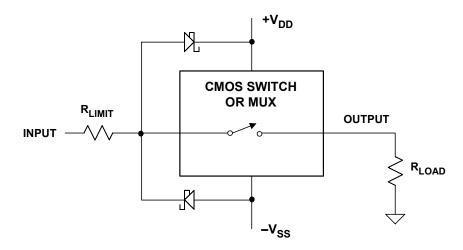

- 3. Data Converter Architectures

- 4. Data Converter Process Technology

- 5. Testing Data Converters

- 6. Interfacing to Data Converters

- ♦ 7. Data Converter Support Circuits

- 7.1 Voltage References

- 7.2 Low Dropout Linear Regulators

- 7.3 Analog Switches and Multiplexers

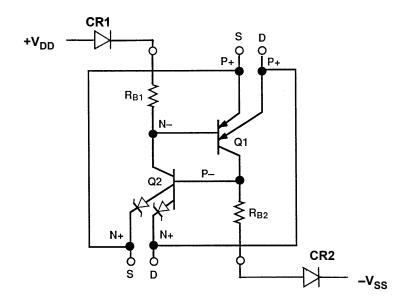

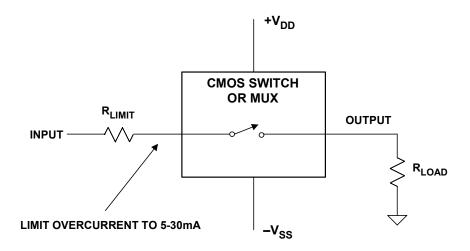

- 7.4 Sample-and-Hold Circuits

- 8. Data Converter Applications

- 9. Hardware Design Techniques

- I. Index

# CHAPTER 7 DATA CONVERTER SUPPORT CIRCUITS

#### **SECTION 7.1: VOLTAGE REFERENCES**

Walt Jung, Walt Kester, James Bryant

Reference circuits and linear regulators actually have much in common. In fact, the latter could be functionally described as a reference circuit, but with greater current (or power) output. Accordingly, almost all of the specifications of the two circuit types have great commonality (even though the performance of references is usually tighter with regard to drift, accuracy, etc.). This section discusses voltage references, and the next section covers linear regulators, with emphasis on their low dropout operation for highest power efficiency.

#### **Precision Voltage References**

Voltage references have a major impact on the performance and accuracy of analog systems. A  $\pm 5$ -mV tolerance on a 5-V reference corresponds to  $\pm 0.1\%$  absolute accuracy—only 10 bits. For a 12-bit system, choosing a reference that has a  $\pm 1$ -mV tolerance may be far more cost effective than performing manual calibration, while both high initial accuracy and calibration will be necessary in a system making absolute 16-bit measurements. Note that many systems make *relative* measurements rather than absolute ones, and in such cases the absolute accuracy of the reference is not important, although noise and short-term stability may be. Figure 7.1 summarizes some key points of the reference selection process.

Temperature drift or drift due to aging may be an even greater problem than absolute accuracy. The initial error can always be trimmed, but compensating for drift is difficult. Where possible, references should be chosen for temperature coefficient and aging characteristics which preserve adequate accuracy over the operating temperature range and expected lifetime of the system.

Noise in voltage references is often overlooked, but it can be very important in system design. It is generally specified on data sheets, but system designers frequently ignore the specification and assume that voltage references do not contribute to system noise.

There are two dynamic issues that must be considered with voltage references: their behavior at start-up, and their behavior with transient loads. With regard to the first, always bear in mind that voltage references *do not power up instantly* (this is true of references inside ADCs and DACs as well as discrete designs). Thus it is rarely possible to turn on an ADC and reference, whether internal or external, make a reading, and turn off again within a few microseconds, however attractive such a procedure might be in terms of energy saving.

Regarding the second point, a given reference IC may or may not be well suited for pulse-loading conditions, dependent upon the specific architecture. Many references use low power, and therefore low bandwidth, output buffer amplifiers. This makes for poor behavior under fast transient loads, which may degrade the performance of fast ADCs (especially successive approximation and flash ADCs). Suitable decoupling can ease the problem (but some references oscillate with capacitive loads), or an additional external broadband buffer amplifier may be used to drive the node where the transients occur.

References, like almost all other ICs today, are fast migrating to such smaller packages such as SO-8 and MSOP, and the even more tiny SOT-23 and SC-70, enabling much higher circuit densities within a given area of real estate. In addition to the system size reductions these steps bring, there are also tangible reductions in standby power and cost with the smaller and less expense ICs.

- ◆ Tight Tolerance Improves Accuracy, Reduces System Costs

- **♦** Temperature Drift Affects Accuracy

- ♦ Long-Term Stability, Low Hysteresis Assures Repeatability

- Noise Limits System Resolution

- Dynamic Loading Can Cause Errors

- ♦ Power Consumption is Critical to Battery Systems

- ♦ Tiny Low Cost Packages Increase Circuit Density

Figure 7.1: Choosing Voltage References for High Performance Systems

#### **Types of Voltage References**

In terms of the functionality of their circuit connection, standard reference ICs are often only available in *series*, or *three-terminal* form (V<sub>IN</sub>, Common, V<sub>OUT</sub>), and also in positive polarity only. The series types have the potential advantages of lower and more stable quiescent current, standard pre-trimmed output voltages, and relatively high output current without accuracy loss. *Shunt*, or *two-terminal* (i.e., diode-like) references are more flexible regarding operating polarity, but they are also more restrictive as to loading. They can in fact eat up excessive power with widely varying resistor-fed voltage inputs. Also, they sometimes come in non-standard voltages. All of these various factors tend to govern when one functional type is preferred over the other.

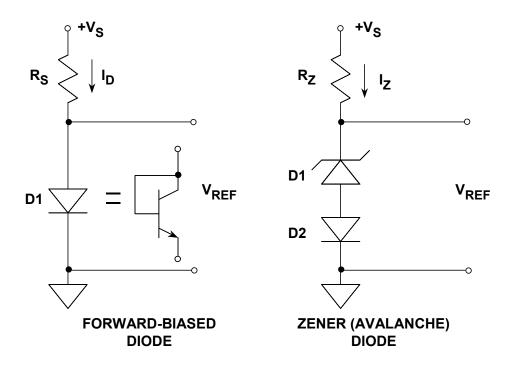

Some simple diode-based references are shown in Figure 7.2. In the first of these, a current driven forward biased diode (or diode-connected transistor) produces a voltage,  $V_f = V_{REF}$ . While the junction drop is somewhat decoupled from the raw supply, it has numerous deficiencies as a reference. Among them are a strong TC of about -0.3%/°C, some sensitivity to loading, and a rather inflexible output voltage: it is only available in 600-mV jumps.

By contrast, these most simple references (as well as all other shunt-type regulators) have a basic advantage, which is the fact that the polarity is readily reversible by flipping connections and reversing the drive current. However, a basic limitation of all shunt regulators is that load current must always be less (usually appreciably less) than the driving current, I<sub>D</sub>.

Figure 7.2: Simple Diode Reference Circuits

In the second circuit of Figure 7.2, a Zener or avalanche diode is used, and an appreciably higher output voltage realized. While true *Zener* breakdown occurs below 5 V, *avalanche* breakdown occurs at higher voltages and has a positive temperature coefficient. Note that diode reverse breakdown is referred to almost universally today as *Zener*, even though it is usually avalanche breakdown. With a D1 breakdown voltage in the 5- to 8-V range, the net positive TC is such that it equals the negative TC of forward-biased diode D2, yielding a net TC of 100 ppm/°C or less with proper bias current. Combinations of such carefully chosen diodes formed the basis of the early single package "temperature-compensated Zener" references, such as the 1N821-1N829 series.

The temperature-compensated Zener reference is limited in terms of initial accuracy, since the best TC combinations fall at odd voltages, such as the 1N829's 6.2 V. And, the scheme is also limited for loading, since for best TC the diode current must be carefully controlled. Unlike a fundamentally lower voltage (<2 V) reference, Zener diode based references must of necessity be driven from voltage sources appreciably higher than 6-V levels, so this precludes operation of Zener references from 5-V system supplies. References based on low TC Zener (avalanche) diodes also tend to be noisy, due to the basic noise of the breakdown mechanism. This has been improved greatly with *monolithic* Zener types, as is described further below.

At this point, we know that a reference circuit can be functionally arranged into either a series or shunt operated form, and the technology within may use either bandgap based or

Zener diode based circuitry. In practice there are all permutations of these available, as well as a third major technology category. The three major reference technologies are now described in more detail.

#### **Bandgap References**

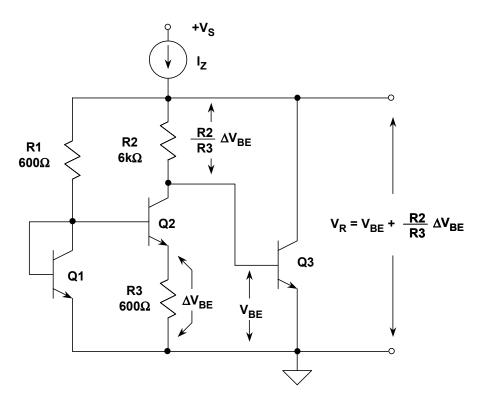

The development of low voltage (<5 V) references based on the bandgap voltage of silicon led to the introductions of various ICs which could be operated on low voltage supplies with good TC performance. The first of these was the LM109 (Reference 1), and a basic bandgap reference cell is shown in Figure 7.3.

Figure 7.3: Basic Bandgap Reference

This circuit is also called a " $\Delta V_{BE}$ " reference because the differing current densities between matched transistors Q1-Q2 produces a  $\Delta V_{BE}$  across R3. It works by summing the  $V_{BE}$  of Q3 with the amplified  $\Delta V_{BE}$  of Q1-Q2, developed across R2. The  $\Delta V_{BE}$  and  $V_{BE}$  components have opposite polarity TCs;  $\Delta V_{BE}$  is proportional-to-absolute-temperature (PTAT), while  $V_{BE}$  is complementary-to-absolute-temperature (CTAT). The summed output is  $V_R$ , and when it is equal to 1.205 V (silicon bandgap voltage), the TC is a minimum.

The bandgap reference technique is attractive in IC designs because of several reasons; among these are the relative simplicity, and the avoidance of Zeners and their noise. However, very important in these days of ever decreasing system power supplies is the fundamental fact that bandgap devices operate at low voltages, i.e., <5 V. Not only are they used for stand-alone IC references, but they are also used within the designs of many other ICs, such as ADCs and DACs.

Buffered forms of 1.2-V two terminal shunt bandgap references, such as the AD589 IC, remain stable under varying load currents. The AD589 (introduced in 1980), a 1.235-V reference, handles 50  $\mu$ A to 5 mA with an output impedance of 0.6  $\Omega$ , and TCs ranging between 10 and 100 ppm/°C. The more recent and functionally similar AD1580, a 1.225-V shunt reference, is in the tiny SOT-23 package and handles the same nominal currents as the AD589, with TCs of 50 and 100 ppm/°C. The ADR510 shunt reference supplies 1.000 V, and the ADR512 supplies 1.200 V.

However, the basic designs of Figure 7.3 suffer from load and current drive sensitivity, plus the fact that the output needs accurate scaling to more useful levels, i.e., 2.5 V, 5 V, etc. The load drive issue is best addressed with the use of a buffer amplifier, which also provides convenient voltage scaling to standard levels.

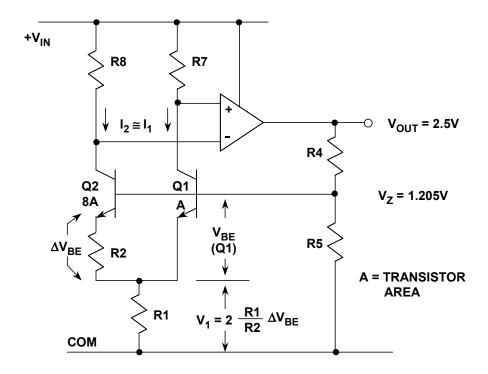

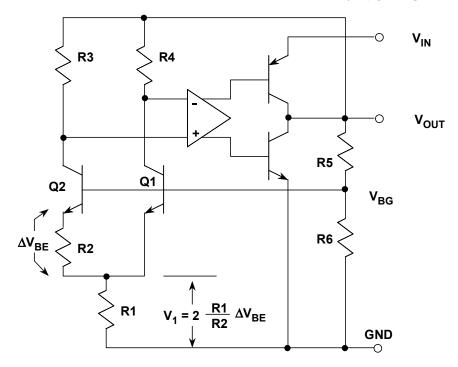

An improved three-terminal bandgap reference, the AD580 (introduced in 1974) is shown in Figure 7.4. Popularly called the "Brokaw Cell" (see References 2 and 3), this circuit provides on-chip output buffering, which allows good drive capability and standard output voltage scaling. The AD580 was the first precision bandgap based IC reference, and variants of the topology have influenced further generations of both industry standard references such as the REF01, REF02, and REF03 series, as well as more recent ADI bandgap parts such as the REF19x series, the AD680, AD780, the AD1582-85 series, the ADR38x series, the ADR39x series, and recent SC-70 and SOT-23 offerings of improved versions of the REF01, REF02, and REF03 (designated ADR01, ADR02, and ADR03).

The AD580 has two 8:1 emitter-scaled transistors Q1-Q2 operating at identical collector currents (and thus 1/8 current densities), by virtue of equal load resistors and a closed loop around the buffer op amp. Due to the resultant smaller  $V_{BE}$  of the 8× area Q2, R2 in series with Q2 drops the  $\Delta V_{BE}$  voltage, while R1 (due to the current relationships) drops a PTAT voltage V1:

$$V_1 = 2 \times \frac{R1}{R2} \times \Delta V_{BE} \quad . \tag{Eq. 7.1}$$

The bandgap cell reference voltage  $V_Z$  appears at the base of Q1, and is the sum of  $V_{BE}$  (Q1) and  $V_1$ , or 1.205 V, the bandgap voltage:

$$\begin{split} V_Z &= V_{BE(Q1)} + V_1 & \text{Eq. 7.2} \\ &= V_{BE(Q1)} + 2 \times \frac{R1}{R2} \times \Delta V_{BE} & \text{Eq. 7.3} \\ &= V_{BE(Q1)} + 2 \times \frac{R1}{R2} \times \frac{kT}{q} \times \ln \frac{J1}{J2} & \text{Eq. 7.4} \\ &= V_{BE(Q1)} + 2 \times \frac{R1}{R2} \times \frac{kT}{q} \times \ln 8 & \text{Eq. 7.5} \\ &= 1.205 \text{V} \,. & \text{Eq. 7.6} \end{split}$$

Note that J1 = current density in Q1, J2 = current density in Q2, and J1/J2 = 8.

Figure 7.4: AD580 Precision Bandgap Reference Uses Brokaw Cell (1974)

However, because of the presence of the R4/R5 (laser trimmed) thin film divider and the op amp, the actual voltage appearing at  $V_{OUT}$  can be scaled higher, in the AD580 case 2.5 V. Following this general principle,  $V_{OUT}$  can be raised to other practical levels, such as for example in the AD584, with taps for precise 2.5-, 5-, 7.5-, and 10-V operation. The AD580 provides up to 10-mA output current while operating from supplies between 4.5 and 30 V. It is available in tolerances as low as 0.4%, with TCs as low as 10 ppm/°C.

Many of the recent developments in bandgap references have focused on smaller package size and cost reduction, to address system needs for smaller, more power efficient and less costly reference ICs. Among these are several recent bandgap-based IC references.

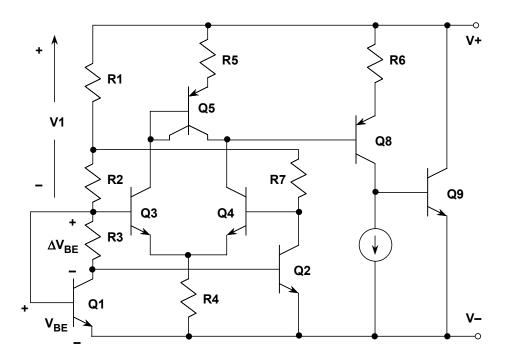

The AD1580 (introduced in 1996) is a shunt mode IC reference which is functionally quite similar to the classic shunt IC reference, the AD589 (introduced in 1980) mentioned above. A key difference is the fact that the AD1580 uses a newer, small geometry process, enabling its availability within the tiny SOT-23 package. The very small size of this package allows use in a wide variety of space limited applications, and the low operating current lends itself to portable battery powered uses. The AD1580 circuit is shown in simplified form in Figure 7.5.

In this circuit, transistors Q1 and Q2 form the bandgap core, and are operated at a current ratio of 5 times, determined by the ratio of R7 to R2. An op amp is formed by the differential pair Q3-Q4, current mirror Q5, and driver/output stage Q8-Q9. In closed loop equilibrium, this amplifier maintains the bottom ends of R2-R7 at the same potential.

Figure 7.5: AD1580 1.2-V Shunt Type Bandgap Reference has Tiny Size in SOT-23 Footprint

As a result of the closed loop control described, a basic  $\Delta V_{BE}$  voltage is dropped across R3, and a scaled PTAT voltage also appears as V1, which is effectively in series with  $V_{BE}$ . The nominal bandgap reference voltage of 1.225 V is then the sum of Q1's  $V_{BE}$  and V1. The AD1580 is designed to operate at currents as low as 50  $\mu$ A, also handling maximum currents as high as 10 mA. It is available in grades with voltage tolerances of  $\pm 1$  or  $\pm 10$  mV, and with corresponding TCs of 50 or 100 ppm/°C. Newer members of the Analog Devices' family of shunt regulators are the ADR510 (1.000 V), and the ADR512 (1.200 V).

The ADR520 (2.048 V), ADR525 (2.500 V), ADR530 (3.000 V), ADR540 (4.096 V), ADR545 (4.5 V), and ADR550 (5.0 V) are the latest in the shunt regulator family, with initial accuracies of 0.2%, and available in either SC-70 or SOT-23 packages.

The AD1582-AD1585 series comprises a family of *series* mode IC references, which produce voltage outputs of 2.5, 3.0, 4.096 and 5.0 V. Like the AD1580, the series uses a small geometry process to allow packaging within an SOT-23. The AD1582 series specifications are summarized in Figure 7.6.

The circuit diagram for the series, shown in Figure 7.7, may be recognized as a variant of the basic Brokaw bandgap cell, as described under Figure 7.4. In this case Q1-Q2 form the core, and the overall loop operates to produce the stable reference voltage  $V_{BG}$  at the base of Q1. A notable difference here is that the op amp's output stage is designed with push-pull common-emitter stages. This has the effect of requiring an output capacitor for stability, but it also provides the IC with relatively low dropout operation.

The low dropout feature means essentially that  $V_{\rm IN}$  can be lowered to as close as several hundred mV above the  $V_{\rm OUT}$  level without disturbing operation. The push-pull operation also means that this device series can actually both sink and source currents at the output, as opposed to the classic reference operation of sourcing current (only). For the various output voltage ratings, the divider R5-R6 is adjusted for the respective levels.

◆ V<sub>OUT</sub>: 2.500, 3.000, 4.096, & 5.000V

♦ 2.7V to 12V Supply Range (200mV Headroom)

Supply Current : 65μA max

Initial Accuracy: ±0.1% max

◆ Temperature Coefficient: 50 ppm/°C max

Noise: 70μV p-p (0.1Hz - 10Hz)

♦ Noise: 50µV rms (10Hz - 10kHz)

◆ Long-Term Drift: 100ppm/1khrs

♦ High Output Current: ±5mA min

◆ Temperature Range –40°C to +85°C

Low Cost SOT-23 Package

Figure 7.6: AD1582-AD1585 2.5-V to 5-V Series-Type Bandgap Reference Specifications

The AD1582-series is designed to operate with quiescent currents of only 65  $\mu A$  (maximum), which allows good power efficiency when used in low power systems with varying voltage inputs. The rated output current for the series is 5 mA, and they are available in grades with voltage tolerances of  $\pm 0.1$  or  $\pm 1\%$  of  $V_{OUT}$ , with corresponding TCs of 50 or 100 ppm/°C.

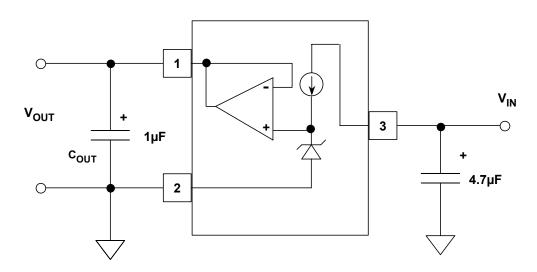

Because of stability requirements, devices of the AD1582 series must be used with both an output and input bypass capacitor. Recommended optimum values for these are shown in the hookup diagram of Figure 7.8. For the electrical values noted, it is likely that tantalum chip capacitors will be the smallest in size.

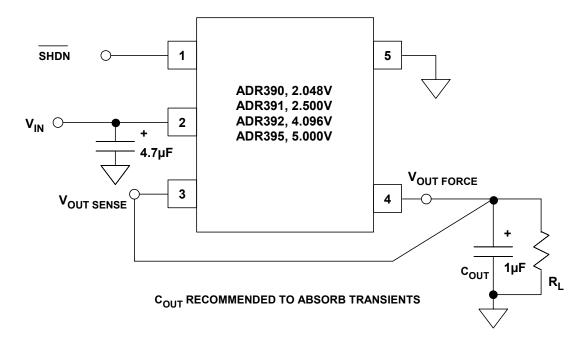

ADR38x and ADR39x-series are low dropout (300 mV) bandgap references in SOT-23 packages. Noise is typically 5- $\mu$ V p-p in the 0.1 Hz to 10 Hz bandwidth. Quiescent current is typically 100  $\mu$ A, and the ADR39x-series have a shutdown pin (shutdown current < 3  $\mu$ A) as well as a "sense" pin for Kelvin sensing. A connection diagram for the ADR39x series is shown in Figure 7.9, and key specifications for the family are shown in Figure 7.10. The ADR38x and ADR39x-series do not require an output capacitor for stability, regardless of the load conditions. However, at least a 1- $\mu$ F capacitor is recommended to filter out noise. Larger capacitors may be desirable to act as a source of stored energy for transient loads.

Figure 7.7: AD1582-AD1585 2.5-V to 5-V Series-Type Bandgap References in SOT-23 Footprint

AD1582-1585:  $C_{\mbox{OUT}}$  REQUIRED FOR STABILITY ADR380, ADR381:  $C_{\mbox{OUT}}$  RECOMMENDED TO ABSORB TRANSIENTS

Figure 7.8: AD1582-AD1585 Series Connection Diagram

Figure 7.9: ADR390, ADR391, ADR392, ADR395 Connection Diagram

- ◆ V<sub>OUT</sub>: 2.048, 2.500, 4.096, & 5.000V

- ◆ 2.3V to 15V Supply Range (300mV Headroom)

- ♦ Supply Current : 120µA max

- Initial Accuracy: ±6mV max

- ◆ Temperature Coefficient: 25 ppm/°C max

- ♦ Noise: 5µV p-p (0.1Hz 10Hz)

- ◆ Long-Term Drift: 50ppm/1khrs

- ♦ High Output Current: +5mA min

- ◆ Temperature Range –40°C to +85°C

- ♦ Shutdown Feature: <3µA max</p>

- Kelvin Sensing (Force and Sense Pins)

- ♦ Low Cost SOT-23 (5 pin) Package

Figure 7.10: ADR390-ADR395 2.048-V to 5-V Series-Type Bandgap Reference Specifications

#### **Buried Zener References**

In terms of the design approaches used within the reference core, the two most popular basic types of IC references consist of the bandgap and buried Zener units. Bandgaps have been discussed, but Zener based references warrant some further discussion.

In an IC chip, surface operated diode junction breakdown is prone to crystal imperfections and other contamination, thus Zener diodes formed at the surface are more noisy and less stable than are *buried* (or sub-surface) ones. ADI Zener based IC references employ the much preferred buried Zener. This improves substantially upon the noise and drift of surface-mode operated Zeners (see Reference 4). Buried Zener references offer very low temperature drift, down to the 1-2 ppm/°C (AD588 and AD586), and the lowest noise as a percent of full-scale, i.e., 100 nV/\dagger Hz or less. On the downside, the operating current of Zener type references is usually relatively high, typically on the order of several mA.

An important general point arises when comparing noise performance of different references. The best way to do this is to compare the ratio of the noise (within a given bandwidth) to the dc output voltage. For example, a 10-V reference with a 100-nV/√Hz noise density is 6-dB more quiet in relative terms than is a 5-V reference with the same noise level.

#### XFET® References

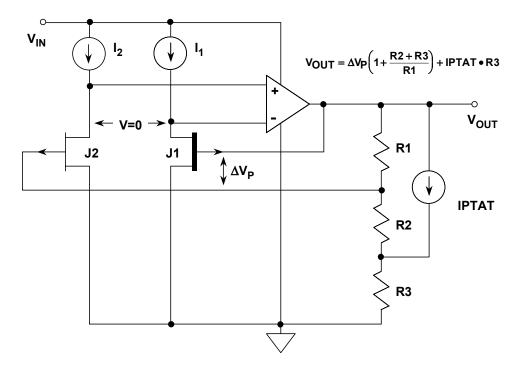

A third and relatively new category of IC reference core design is based on the properties of junction field effect (JFET) transistors. Somewhat analogous to the bandgap reference for bipolar transistors, the JFET based reference operates a pair of junction field effect transistors with different pinchoff voltages, and amplifies the differential output to produce a stable reference voltage. One of the two JFETs uses an extra ion implantation, giving rise to the name XFET® (eXtra implantation junction Field Effect Transistor) for the reference core design.

The basic topology for the XFET reference circuit is shown in Figure 7.11. J1 and J2 are the two JFET transistors, which form the core of the reference. J1 and J2 are driven at the same current level from matched current sources, I1 and I2. To the right, J1 is the JFET with the extra implantation, which causes the difference in the J1-J2 pinchoff voltages to differ by 500 mV. With the pinchoff voltage of two such FETs purposely skewed, a differential voltage will appear between the gates for identical current drive conditions and equal source voltages. This voltage,  $\Delta V_P$ , is:

$$\Delta V_P = V_{P1} - V_{P2} , \qquad \qquad \text{Eq. 7.7}$$

where V<sub>P1</sub> and V<sub>P2</sub> are the pinchoff voltages of FETs J1 and J2, respectively.

Figure 7.11: ADR290-ADR293 2.048-V to 5-V XFET® References Feature High Stability and Low Power

Note that, within this circuit, the voltage  $\Delta V_P$  exists between the *gates* of the two FETs. We also know that, with the overall feedback loop closed, the op amp axiom of zero input differential voltage will hold the sources of the two JFETs at the same potential. These source voltages are applied as inputs to the op amp, the output of which drives feedback divider R1-R3. As this loop is configured, it stabilizes at an output voltage from the R1-R2 tap which does in fact produce the required  $\Delta V_P$  between the J1-J2 gates. In essence, the op amp amplifies  $\Delta V_P$  to produce  $V_{OUT}$ , where

$$V_{OUT} = \Delta V_P \left( 1 + \frac{R2 + R3}{R1} \right) + \left( I_{PTAT} \right) (R3).$$

Eq. 7.8

As can be noted, this expression includes the basic output scaling (leftmost portion of the right terms), plus a rightmost temperature dependent term including  $I_{PTAT}$ . The  $I_{PTAT}$  portion of the expression compensates for a basic negative temperature coefficient of the XFET core, such that the overall net temperature drift of the reference is typically in a range of 3 to 8 ppm/°C.

During manufacture, the R1-R3 scaling resistance values are adjusted to produce the different voltage output options of 2.048, 2.5, 4.096 and 5.0 V for the ADR290, ADR291, ADR292 and ADR293 family (ADR29x). This ADR29x family of series mode references is available in 8 pin packages with a standard footprint. They operate from supplies of  $V_{OUT}$  plus 500 mV to 15 V, with a maximum quiescent current of 12  $\mu$ A, and output currents of up to 5 mA. A summary of specifications for the family appears in Figure 7.12.

- V<sub>OUT</sub>: 2.048, 2.500, 4.096, & 5.000V

- ◆ 2.7V to 15V Supply Range (0.5V Headroom)

- ♦ Supply Current : 12µA max

- ♦ Initial Accuracy: ±0.1%

- **♦** Temperature Coefficient: 8 ppm/°C max

- Low-Noise: 6μV p-p (0.1 10Hz)

- ♦ Wideband Noise: 420nV/√Hz @ 1kHz

- ♦ Long-Term Drift: 50ppm/1000 hours

- High Output Current: 5mA min

- ◆ Temperature Range –40°C to +125°C

- Standard REF02 Pinout

- ♦ 8-Lead Narrow Body SOIC, 8-Lead TSSOP

Figure 7.12: ADR290-ADR293 XFET® Series Specifications

The ADR43x-series are the second generation of low noise, low drift XFET references. Standard voltage outputs are 2.048, 2.500, 3.000, 4.096, and 5.000 V. These devices operate from supplies of  $V_{OUT}+1$  V to 18 V with quiescent currents of 0.5-mA maximum and output currents of  $\pm 10$  mA. Temperature drift is 3-ppm/°C maximum. The 0.1-Hz to 10-Hz noise is an incredibly low 1.5- $\mu$ V p-p. This ADR43x family of series mode references is available in 8 pin packages with a standard footprint. Key specifications for the family are summarized in Figure 7.13.

- ◆ V<sub>OLIT</sub>: 2.048, 2.500, 3.000, 4.096, & 5.000V

- ♦ 3V to 18V Supply Range (1V Headroom)

- ♦ Supply Current : 500µA

- ♦ Initial Accuracy: ±0.05%

- ◆ Temperature Coefficient: 3 ppm/°C max

- ♦ Low-Noise: 1.75µV p-p (0.1 10Hz)

- ♦ Wideband Noise: 60nV/√Hz @ 1kHz

- Long-Term Drift: 50ppm/1000 hours

- ♦ High Output Current: ±10mA min

- ◆ Temperature Range –40°C to +125°C

- 8-Lead MSOP, 8-Lead TSSOP

Figure 7.13: ADR430-ADR439 XFET® Series Specifications

The XFET architecture offers performance improvements over bandgap and buried Zener references, particularly for systems where operating current is critical, yet drift and noise performance must still be excellent. XFET noise levels are lower than bandgap based bipolar references operating at an equivalent current, the temperature drift is low and linear at 3-8 ppm/°C (allowing easier compensation when required), and the series has lower hysteresis than bandgaps. Thermal hysteresis is a low 50 ppm over a –40°C to +125°C range, less that half that of a typical bandgap device. Finally, the long-term stability is excellent, typically only 50 ppm/1000 hours.

Figure 7.14 summarizes the pro and con characteristics of the three reference architectures; bandgap, buried Zener, and XFET.

| BANDGAP                               | BURIED ZENER                          | XFET®                                   |

|---------------------------------------|---------------------------------------|-----------------------------------------|

| < 5V Supplies                         | > 5V Supplies                         | < 5V Supplies                           |

| High Noise<br>@ High Power            | Low Noise<br>@ High Power             | Low Noise<br>@ Low Power                |

| Fair Drift and<br>Long Term Stability | Good Drift and<br>Long Term Stability | Excellent Drift and Long Term Stability |

| Fair Hysteresis                       | Fair Hysteresis                       | Low Hysteresis                          |

Figure 7.14: Characteristics of Reference Architectures

Modern IC references come in a variety of styles, but series operating, fixed output positive types do tend to dominate. These devices can use bandgap-based bipolars, JFETs, or buried Zeners at the device core, all of which has an impact on the part's ultimate performance and application suitability. They may or may not also be low power, low noise, and/or low dropout, and be available within a certain package. Of course, in a given application, any single one of these differentiating factors can drive a choice, thus it behooves the designer to be aware of all the different devices available.

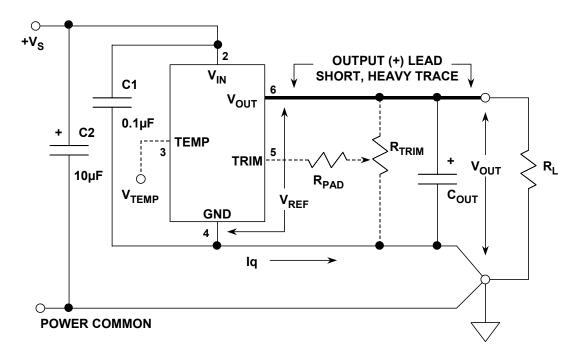

Figure 7.15 shows the standard footprint for such a series type IC positive reference in an 8 pin package (Note that pin numbers shown refer to the standard pin for that function). There are several details which are important. Many references allow optional trimming by connecting an external trim circuit to drive the references' *trim* input pin (5). Some bandgap references also have a high impedance PTAT output (V<sub>TEMP</sub>) for temperature sensing (pin 3). The intent here is that no appreciable current be drawn from this pin, but it can be useful for such non-loading types of connections as comparator inputs, to sense temperature thresholds, etc.

Figure 7.15: Standard Positive Output Three Terminal Reference Hookup (8-pin DIP Pinout)

All references should use decoupling capacitors on the input pin (2), but the amount of decoupling (if any) placed on the output (pin 6) depends upon the stability of the reference's output op amp with capacitive load. Simply put, there is no hard and fast rule for capacitive loads here. For example, some three terminal types *require* the output capacitor for stability (i.e., REF19x and AD1582-85 series), while with others it is optional for performance improvement (AD780, REF43, ADR29x, ADR43x, AD38x, AD39x, ADR01, ADR02, ADR03). Even if the output capacitor is optional, it may still be required to supply the energy for transient load currents, as presented by some ADC reference input circuits. The safest rule then is that you should use the data sheet to verify what are the specific capacitive loading ground rules for the reference you intend to use, for the load conditions your circuit presents.

#### **Voltage Reference Specifications**

#### **Tolerance**

It is usually better to select a reference with the required value and accuracy and to avoid external trimming and scaling if possible. This allows the best TCs to be realized, as tight tolerances and low TCs usually go hand-in-hand. Tolerances as low as approximately 0.04% can be achieved with the AD586, AD780, REF195, and ADR43x-series, while the AD588 is 0.01%. If and when trimming must be used, be sure to use the recommended trim network with no more range than is absolutely necessary. When/if additional external scaling is required, a precision op amp should be used, along with ratio-accurate, low TC tracking thin film resistors.

#### Drift

The XFET and buried Zener reference families have the best long term drift and TC performance. The XFET ADR43x-series have TCs as low as 3 ppm/°C. TCs as low as 1-2 ppm/°C are available with the AD586 and AD588 buried Zener references, and the AD780 bandgap reference is almost as good at 3 ppm/°C.

The XFET series achieve long terms drifts of 50 ppm/1000 hours, while the buried Zener types come in at 25 ppm/1000 hours. Note that where a figure is given for long term drift, it is usually drift expressed in ppm/1000 hours. There are 8766 hours in a year, and many engineers multiply the 1000-hour figure by 8.77 to find the annual drift—this is not correct, and can in fact be quite pessimistic. Long term drift in precision analog circuits is a "random walk" phenomenon and increases with the *square root* of the elapsed time (this supposes that drift is due to random micro-effects in the chip and not some overriding cause such as contamination). The 1 year figure will therefore be about  $\sqrt{8.766} \approx 3$  times the 1000-hour figure, and the ten year value will be roughly 9 times the 1000-hour value. In practice, things are a little better even than this, as devices tend to stabilize with age.

The accuracy of an ADC or DAC can be no better than that of its reference. Reference temperature drift affects fullscale accuracy as shown in Figure 7.16. This table shows system resolution and the TC required to maintain ½ LSB error over an operating temperature range of 100°C. For example, a TC of about 1 ppm/°C is required to maintain ½ LSB error at 12 bits. For smaller operating temperature ranges, the drift requirement will be less. The last three columns of the table show the voltage value of ½ LSB for popular full scale ranges.

|      |                            | ½ LSB WEIGHT (mV)                |      |      |

|------|----------------------------|----------------------------------|------|------|

|      |                            | 10, 5, AND 2.5V FULLSCALE RANGES |      |      |

| BITS | REQUIRED<br>DRIFT (ppm/°C) | 10V                              | 5V   | 2.5V |

| 8    | 19.53                      | 19.53                            | 9.77 | 4.88 |

| 9    | 9.77                       | 9.77                             | 4.88 | 2.44 |

| 10   | 4.88                       | 4.88                             | 2.44 | 1.22 |

| 11   | 2.44                       | 2.44                             | 1.22 | 0.61 |

| 12   | 1.22                       | 1.22                             | 0.61 | 0.31 |

| 13   | 0.61                       | 0.61                             | 0.31 | 0.15 |

| 14   | 0.31                       | 0.31                             | 0.15 | 0.08 |

| 15   | 0.15                       | 0.15                             | 0.08 | 0.04 |

| 16   | 0.08                       | 0.08                             | 0.04 | 0.02 |

Figure 7.16: Reference Temperature Drift Requirements for Various System Accuracies (1/2 LSB Criteria, 100°C Span)

#### **Supply Range**

IC reference supply voltages range from about 3 V (or less) above rated output, to as high as 30 V (or more) above rated output. Exceptions are devices designed for low dropout, such as the REF19x, AD1582-AD1585, ADR38x, ADR39x series. At low currents, the REF195 can deliver 5 V with an input as low as 5.1 V (100-mV dropout). Note that due to process limits, some references may have more restrictive maximum voltage input ranges, such as the AD1582-AD1585 series (12 V), the ADR29x series (15 V), and the ADR43x series (18 V).

#### **Load Sensitivity**

Load sensitivity (or output impedance) is usually specified in  $\mu V/mA$  of load current, or  $m\Omega$ , or ppm/mA. While figures of 70 ppm/mA or less are quite good (AD780, REF43, REF195, ADR29x, ADR43x), it should be noted that external wiring drops can produce comparable or worse errors at high currents, without care in layout. Load current dependent errors are minimized with short, heavy conductors on the (+) output and on the ground return. For the highest precision, buffer amplifiers and Kelvin sensing circuits (AD588, AD688, ADR39x) are used to ensure accurate voltages at the load.

The output of a buffered reference is the output of an op amp, and therefore the source impedance is a function of frequency. Typical reference output impedance rises at 6 dB/octave from the dc value, and is nominally about 10  $\Omega$  at a few hundred kHz. This impedance can be lowered with an external capacitor, provided the op amp within the reference remains stable for such loading.

#### **Line Sensitivity**

Line sensitivity (or regulation) is usually specified in  $\mu$ V/V, (or ppm/V) of input change, and is typically 25 ppm/V (–92 dB) in the REF43, REF195, AD680, AD780, ADR29x, ADR39x, and ADR43x. For dc and very low frequencies, such errors are easily masked by noise.

As with op amps, the line sensitivity (or power supply rejection) of references degrades with increasing frequency, typically 30 to 50 dB at a few hundred kHz. For this reason, the reference input should be highly decoupled (LF and HF). Line rejection can also be increased with a low dropout pre-regulator, such as one of the ADP3300-series parts.

Figure 7.17 summarizes the major reference specifications along with typical values available.

Tolerance:

AD588 0.01%ADR43x, AD780, REF195 0.04%

Drift (TC):

AD586, AD588

AD780, ADR42x, ADR43x,

ADR01, ADR02, ADR03

Drift (long term):

ADR29x,ADR42x, ADR43x

AD588

50 ppm/1000 hours

25 ppm/1000 hours

Supply Range:

REF19x, ADR38x, ADR39x, V<sub>OUT</sub> plus 0.3V-15V

AD158x, AD780

Load Sensitivity

Toppm/mA (350mΩ @ 5V)

Line Sensitivity

25ppm/V (-92 dB @ 5V)

Figure 7.17: Voltage Reference DC Specifications (Typical Values Available)

#### Noise

Reference noise is not always specified, and when it is, there is not total uniformity on how it is measured. For example, some devices are characterized for peak-to-peak noise in a 0.1-Hz to 10-Hz bandwidth, while others are specified in terms of wideband rms or peak-to-peak noise over a specified bandwidth. The most useful way to specify noise (as with op amps) is a plot of noise voltage spectral density  $(nV/\sqrt{Hz})$  versus frequency.

Low noise references are important in high resolution systems to prevent loss of accuracy. Since white noise is statistical, a given noise density must be related to an equivalent peak-to-peak noise in the relevant bandwidth. Strictly speaking, the peak-to-peak noise in a gaussian system is infinite (but its probability is infinitesimal). Conventionally, the figure of  $6.6 \times \text{rms}$  is used to define a practical peak value—statistically, this occurs less than 0.1% of the time. This peak-to-peak value should be less than ½ LSB in order to maintain required accuracy. If peak-to-peak noise is assumed to be 6 times the rms value, then for an N-bit system, reference voltage fullscale  $V_{REF}$ , reference noise bandwidth (BW), the required noise voltage spectral density  $E_n$  (V/ $\sqrt{\text{Hz}}$ ) is given by:

$$E_n \le \frac{V_{REF}}{12 \cdot 2^N \cdot \sqrt{BW}}.$$

Eq. 7.9

For a 10-V, 12-bit, 100-kHz system, the noise requirement is a modest 643 nV/ $\sqrt{\text{Hz}}$ . Figure 7.18 shows that increasing resolution and/or lower fullscale references make noise

requirements more stringent. The 100-kHz bandwidth assumption is somewhat arbitrary, but the user may reduce it with external filtering, thereby reducing the noise. Most good IC references have noise spectral densities around  $100 \text{ nV}/\sqrt{\text{Hz}}$ , so additional filtering is obviously required in most high resolution systems, especially those with low values of  $V_{\text{RFF}}$ .

|      | NOISE DENSITY (nV/√Hz) FOR       |     |      |

|------|----------------------------------|-----|------|

|      | 10, 5, AND 2.5V FULLSCALE RANGES |     |      |

| BITS | 10V                              | 5V  | 2.5V |

| 12   | 643                              | 322 | 161  |

| 13   | 322                              | 161 | 80   |

| 14   | 161                              | 80  | 40   |

| 15   | 80                               | 40  | 20   |

| 16   | 40                               | 20  | 10   |

Figure 7.18: Reference Noise Requirements for Various System Accuracies (1/2-LSB / 100-kHz Criteria)

Some references, for example the AD587 buried Zener type have a pin designated as the *noise reduction pin* (see data sheet). This pin is connected to a high impedance node preceding the on-chip buffer amplifier. Thus an externally connected capacitor  $C_N$  will form a low pass filter with an internal resistor, to limit the effective noise bandwidth seen at the output. A 1- $\mu$ F capacitor gives a 3-dB bandwidth of 40 Hz. Note that this method of noise reduction is by no means universal, and other devices may implement noise reduction differently, if at all.

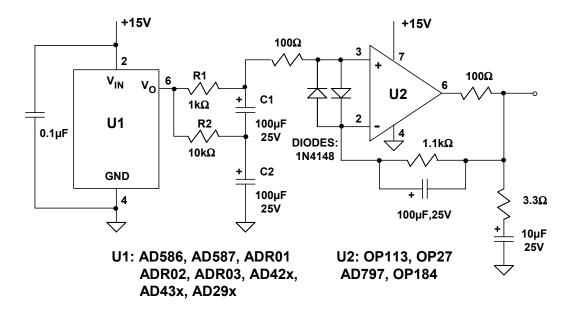

There are also general purpose methods of noise reduction, which can be used to reduce the noise of any reference IC, at any standard voltage level. The reference circuit of Figure 7.19 (References 5 and 6) is one such example. This circuit uses external filtering and a precision low-noise op amp to provide both very low noise and high dc accuracy. Reference U1 is a 2.5-, 3.0-, 5-, or 10-V reference with a low noise buffered output. The output of U1 is applied to the R1-C1/C2 noise filter to produce a corner frequency of about 1.7 Hz. Electrolytic capacitors usually imply dc leakage errors, but the bootstrap connection of C1 causes its applied bias voltage to be only the relatively small drop across R2. This lowers the leakage current through R1 to acceptable levels. Since the filter attenuation is modest below a few Hertz, the reference noise still affects overall performance at low frequencies (i.e., <10 Hz).

Figure 7.19: Combining Low-noise Amplifier with Extensive Filtering Yields Exceptional Reference Noise Performance of (1.5 to 5 nV) /√Hz @ 1 kHz

The output of the filter is then buffered by a precision low noise unity-gain follower, such as the OP113EP. With less than  $\pm 150$ - $\mu V$  offset error and under 1- $\mu V$ /°C drift, the buffer amplifier's dc performance will not seriously affect the accuracy/drift of most references. For example, an ADR292E for U1 will have a typical drift of 3 ppm/°C, equivalent to 7.5  $\mu V$ /°C, higher than the buffer amplifier.

Almost any op amp will have a current limit higher than a typical IC reference. Further, even lower noise op amps are available for 5- to 10-V use. The AD797 offers 1-kHz noise performance less than  $2 \text{ nV}/\sqrt{\text{Hz}}$  in this circuit, compared to about  $5 \text{ nV}/\sqrt{\text{Hz}}$  for the OP113. With any amplifier, Kelvin sensing can be used at the load point, a technique which can eliminate I×R related output voltage errors.

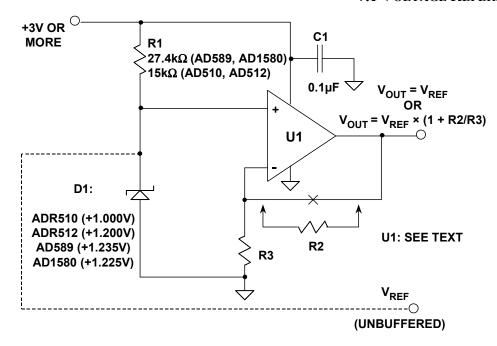

#### **Scaled References**

A useful approach when a non-standard reference voltage is required is to simply buffer and scale a basic low voltage reference diode. With this approach, a potential difficulty is getting an amplifier to work well at such low voltages as 3 V. A workhorse solution is the low power reference and scaling buffer shown in Figure 7.20. Here a low current 1.2-V two terminal reference diode is used for D1, which can be either a 1.200-V ADR512, 1.235-V AD589, or the 1.225-V AD1580. Resistor R1 sets the diode current in either case, and is chosen for the diode minimum current requirement at a minimum supply of 2.7 V. Obviously, loading on the unbuffered diode must be minimized at the  $V_{REF}$  node.

Figure 7.20: Rail-to-rail Output Op Amps Allow Greatest Flexibility in Low Dropout References

The amplifier U1 both buffers and optionally scales up the nominal 1.0 or 1.2-V reference, allowing much higher source/sink output currents. Of course, a higher op amp quiescent current is expended in doing this, but this is a basic tradeoff of the approach. Quiescent current is amplifier dependent, ranging from 45  $\mu A/c$ hannel with the OP196/296/496 series to 1000-2000  $\mu A/c$ hannel with the OP284 and OP279. The former series is most useful for very light loads (<2 mA), while the latter series provide device dependent outputs up to 50 mA. Various devices can be used in the circuit as shown, and their key specs are summarized in Figure 7.21.

| DEVICE*       | Iq, mA      | Vsat (+)     | Vsat (–)        | Isc, mA   |

|---------------|-------------|--------------|-----------------|-----------|

|               | per channel | V (min @ mA) | V (max @ mA)    | min       |

| OP281/481     | 0.003       | 4.93 @ 0.05  | 0.075 @ 0.05    | ± 3.5     |

| OP193/293     | 0.017       | 4.20 @ 1     | 0.280 @ 1 (typ) | ± 8       |

| OP196/296/496 | 0.045       | 4.30 @ 1     | 0.400 @ 1       | ± 4 (typ) |

| AD8541/42/44  | 0.045       | 4.97 @ 1     | 0.025 @ 1       | ± 60      |

| OP777         | 0.220       | 4.91 @ 1     | 0.126 @ 1       | ± 10      |

| AD820/822     | 0.620       | 4.89 @ 2     | 0.055 @ 2       | ± 15      |

| OP184/284/484 | 1.250**     | 4.85 @ 2.5   | 0.125 @ 2.5     | ± 7.5     |

| AD8531/32/34  | 1.400       | 4.90 @ 10    | 0.100 @ 10      | ± 250     |

<sup>\*</sup> Typical device specifications @ Vs = +5V, TA = 25°C, unless otherwise noted \*\* Maximum

**Figure 7.21:** Op Amps Useful in Low Voltage Rail-Rail References and Regulators

In Figure 7.20, without gain scaling resistors R2-R3,  $V_{OUT}$  is simply equal to  $V_{REF}$ . With the use of the scaling resistors,  $V_{OUT}$  can be set anywhere between a lower limit of  $V_{REF}$ , and an upper limit of the positive rail, due to the op amp's rail-rail output swing. Also, note that this buffered reference is inherently low dropout, allowing a +4.5-V (or more) reference output on a +5-V supply, for example. The general expression for  $V_{OUT}$  is shown in the figure, where  $V_{REF}$  is the reference voltage.

Amplifier standby current can be further reduced below 20  $\mu$ A, if an amplifier from the OP181/281/481 or the OP193/293/493 series is used. This choice will be at some expense of current drive, but can provide very low quiescent current if necessary. All devices shown operate from voltages down to 3 V (except the OP279, which operates at 5 V).

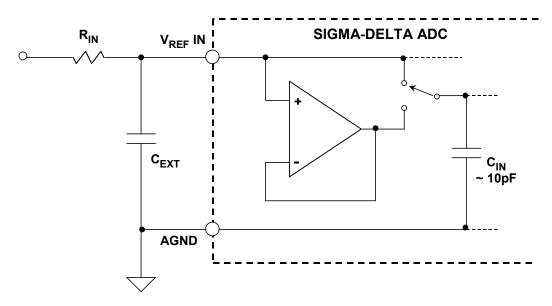

#### **Voltage Reference Pulse Current Response**

The response of references to dynamic loads is often a concern, especially in applications such as driving some ADCs and DACs. Fast changes in load current invariably perturb the output, often outside the rated error band. For example, the reference input to a sigma-delta ADC may be the switched capacitor circuit shown in Figure 7.22. The dynamic load causes current spikes in the reference as the capacitor  $C_{\rm IN}$  is charged and discharged. As a result, noise may be induced on the ADC reference circuitry.

**Figure 7.22:** Switched Capacitor Input of Sigma-Delta ADC Presents a Dynamic Load to the Voltage Reference

Although sigma-delta ADCs have an internal digital filter, transients on the reference input can still cause appreciable conversion errors. Thus it is important to maintain a low noise, transient free potential at the ADC's reference input. Be aware that if the reference source impedance is too high, dynamic loading can cause the reference input to shift by more than 5 mV.

A bypass capacitor on the output of a reference may help it to cope with load transients, but many references are unstable with large capacitive loads. Therefore it is quite

important to verify that the device chosen will satisfactorily drive the output capacitance required. In any case, the converter reference inputs should always be decoupled—with at least 0.1  $\mu$ F, and with an additional 5-50  $\mu$ F if there is any low frequency ripple on its supply. See Figure 7.15 (again).

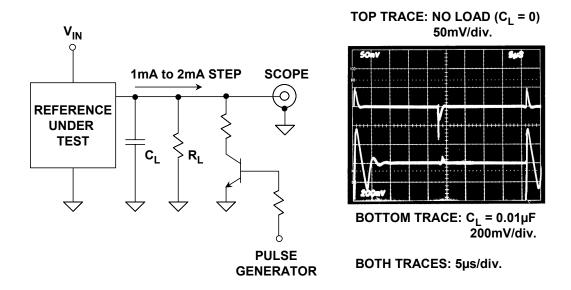

Since some references misbehave with transient loads, either by oscillating or by losing accuracy for comparatively long periods, it is advisable to test the pulse response of voltage references which may encounter transient loads. A suitable circuit is shown in Figure 7.23. In a typical voltage reference, a step change of 1 mA produces the transients shown. Both the duration of the transient, and the amplitude of the ringing *increase* when a 0.01-µF capacitor is connected to the reference output.

Figure 7.23: Make Sure Reference is Stable with Large Capacitive Loads

Where possible, a reference should be designed to drive large capacitive loads. The AD780 is designed to drive unlimited capacitance without oscillation, it has excellent drift and an accurate output, in addition to relatively low power consumption. Other references which are useful with output capacitors are the REF19x, the AD1582-AD1585 series, the ADR29x-series, and the ADR43x-series.

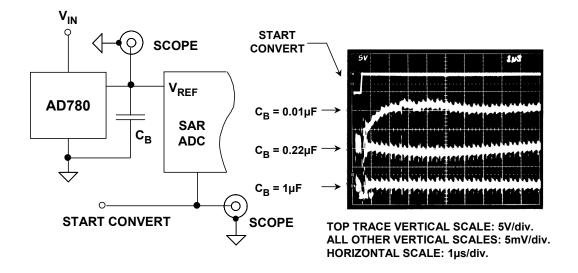

As noted above, reference bypass capacitors are useful when driving the reference inputs of successive-approximation ADCs. Figure 7.24 illustrates reference voltage settling behavior immediately following the "Start Convert" command. A small capacitor (0.01  $\mu$ F) does not provide sufficient charge storage to keep the reference voltage stable during conversion, and errors may result. As shown by the bottom trace, decoupling with  $a \ge 1-\mu$ F capacitor maintains the reference stability during conversion.

Where voltage references are required to drive large capacitances, it is also critically important to realize that their turn-on time will be prolonged. Experiment may be needed to determine the delay before the reference output reaches full accuracy, but it will certainly be much longer than the time specified on the data sheet for the same reference in a low capacitance loaded state.

Figure 7.24: Successive Approximation ADCs Can Present a Dynamic Transient Load to the Reference

#### **Low Noise References for High Resolution Converters**

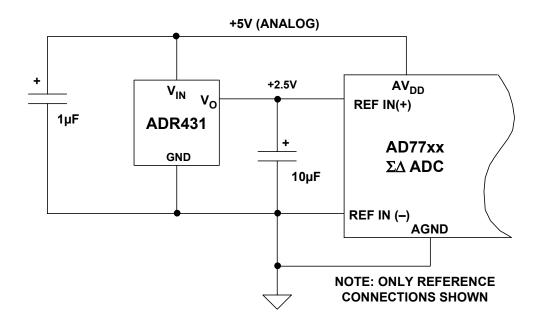

High resolution converters (both sigma-delta and high speed ones) can benefit from recent improvements in IC references, such as lower noise and the ability to drive capacitive loads. Even though many data converters have internal references, the performance of these references is often compromised because of the limitations of the converter process. In such cases, using an external reference rather than the internal one often yields better overall performance. For example, the AD7710-series of 22-bit ADCs has a 2.5-V internal reference with a 0.1-Hz to 10-Hz noise of 8.3- $\mu$ V rms (2600 nV/ $\nu$ Hz), while the AD780 reference noise is only 0.67  $\mu$ V rms (200 nV/ $\nu$ Hz). The internal noise of the AD7710-series in this bandwidth is about 1.7- $\mu$ V rms. The use of the AD780 increases the effective resolution of the AD7710 from about 20.5 bits to 21.5 bits.

Figure 7.25 shows the low noise ADR431 used as the +2.5-V reference for the AD77xx-series ADCs. Optimally, the use of the ADR433 (3-V output) enhances the dynamic range of the ADC, while lowering overall system noise as described above. In addition, the ADR43x-series allow a large decoupling capacitor on its output thereby minimizing conversion errors due to transients.

There is one possible but yet quite real problem when replacing the internal reference of a converter with a higher precision external one. The converter in question may have been trimmed during manufacture to deliver its specified performance with a relatively inaccurate internal reference. In such a case, using a more accurate external reference with the converter may actually introduce additional gain error! For example, the early AD574 had a guaranteed uncalibrated gain accuracy of 0.125% when using an internal 10-V reference (which itself had a specified accuracy of only  $\pm 1\%$ ). It is obvious that if such a device, having an internal reference which is at one end of the specified range, is used with an external reference of exactly 10 V, then its gain will be about 1% in error.

Figure 7.25: The AD431 XFET Reference is Ideal for Driving Precision Sigma-Delta ADCs

## REFERENCES: 7.1 VOLTAGE REFERENCES

- 1. Bob Widlar, "New Developments in IC Voltage Regulators," **IEEE Journal of Solid State Circuits**, Vol. SC-6, February, 1971.

- 2. Paul Brokaw, "A Simple Three-Terminal IC Bandgap Voltage Reference," **IEEE Journal of Solid State Circuits**, Vol. SC-9, December, 1974.

- Paul Brokaw, "More About the AD580 Monolithic IC Voltage Regulator," Analog Dialogue, 9-1, 1975.

- 4. Dan Sheingold, Section 20.2 within **Analog-Digital Conversion Handbook**, **3d. Edition**, Prentice-Hall, 1986.

- 5. Walt Jung, "Build an Ultra-Low-Noise Voltage Reference," **Electronic Design Analog Applications Issue**, June 24, 1993.

- 6. Walt Jung, "Getting the Most from IC Voltage References," Analog Dialogue, 28-1, 1994, pp. 13-21.

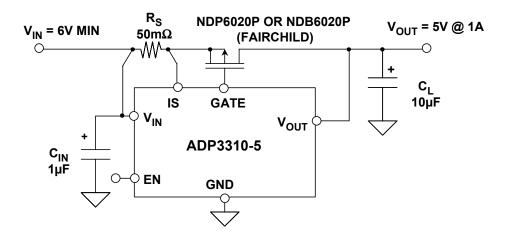

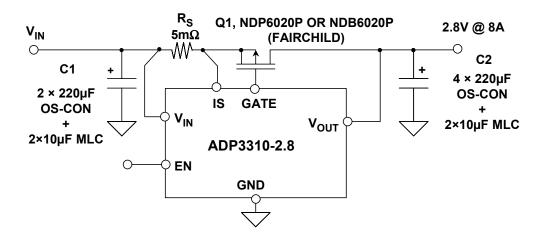

# SECTION 7.2: LOW DROPOUT LINEAR REGULATORS Walt Jung

#### Introduction

Linear IC voltage regulators have long been standard power system building blocks. After an initial introduction in 5-V logic voltage regulator form, they have since expanded into other standard voltage levels spanning from 1.5 to 24 V, handling output currents from as low as 100 mA (or less) to as high as 5 A (or more). For several good reasons, linear style IC voltage regulators have been valuable system components since the early days. One reason is the relatively low noise characteristic vis-à-vis the switching type of regulator. Others are a low parts count and overall simplicity compared to discrete solutions. But, because of their power losses, these linear regulators have also been known for being relatively inefficient. Early generation devices (of which many are still available) required 2 V or more of unregulated input above the regulated output voltage, making them lossy in power terms.

More recently however, linear IC regulators have been developed with more liberal (i.e., lower) limits on minimum input-output voltage. This voltage, known more commonly as *dropout* voltage, has led to what is termed the *low drop out* regulator, or more popularly, the LDO. Dropout voltage ( $V_{MIN}$ ) is defined simply as that minimum input-output differential where the regulator undergoes a 2% reduction in output voltage. For example, if a nominal 5.0-V LDO output drops to 4.9 V (-2%) under conditions of an input-output differential of 0.5 V, by this definition the LDO's  $V_{MIN}$  is 0.5 V.

As will be shown in this section, dropout voltage is extremely critical to a linear regulator stage's power efficiency. The lower the voltage allowable across a regulator while still maintaining a regulated output, the less power the regulator dissipates as a result. A low regulator dropout voltage is the key to this, as it takes this lower dropout to maintain regulation as the input voltage lowers. In performance terms, the bottom line for LDOs is simply that more useful power is delivered to the load and less heat is generated in the regulator. LDOs are key elements of power systems that must provide stable voltages from batteries, such as portable computers, cellular phones, etc. This is simply because they maintain their regulated output down to lower points on the battery's discharge curve. Or, within classic mains-powered raw dc supplies, LDOs allow lower transformer secondary voltages, reducing system susceptibility to shutdown under brownout conditions as well as allowing cooler operation.

#### **Linear Voltage Regulator Basics**

A brief review of three terminal linear IC regulator fundamentals is necessary to understanding the LDO variety. As it turns out, almost all LDOs available today, as well as many of the more general three terminal regulator types, are *positive leg, series style* regulators. This simply means that they control the regulated voltage output by means of a pass element which is in series with the positive side of the unregulated input.

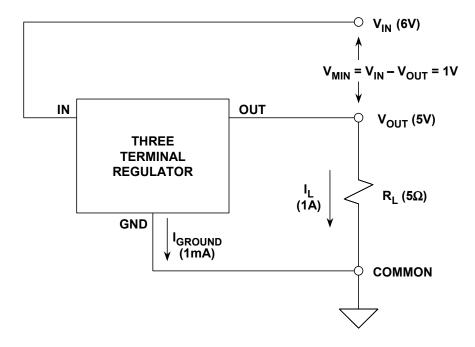

This is shown more clearly in Figure 7.26, which is a hookup diagram for a hypothetical three terminal style regulator. To reiterate what was said earlier in the chapter about reference ICs, in terms of their basic functionality, many standard voltage regulator ICs are available in the series three-terminal form as is shown here ( $V_{IN}$ , GND or Common,  $V_{OUT}$ ).

Figure 7.26: A Basic Three Terminal Voltage Regulator

This diagram also allows some statements to be made about power losses in the regulator. There are two components to power which are dissipated in the regulator, one a function of  $V_{IN}-V_{OUT}$  and  $I_L$ , plus a second which is a function of  $V_{IN}$  and  $I_{ground}$ . If we call the total power  $P_D$ , this then becomes:

$$P_D = (V_{IN} - V_{OUT})(I_L) + (V_{IN})(I_{ground})$$

. Eq. 7.10

Obviously, the magnitude of the load current and the regulator dropout voltage both greatly influence the power dissipated. However, it is also easy to see that for a given  $I_L$ , as the dropout voltage is lowered, the first term of  $P_D$  is reduced. With an intermediate dropout voltage rating of 1 V, a 1-A load current will produce 1 W of heat in this regulator, which will require a heat sink for continuous operation. It is this first term of the regulator power which usually predominates, at least for loaded regulator conditions.

The second term, being proportional to  $I_{ground}$  (typically only 1-2 mA, sometimes even less) usually only becomes significant when the regulator is unloaded, and the regulator's quiescent or standby power then produces a constant drain on the source  $V_{\rm IN}$ .

## DATA CONVERTER SUPPORT CIRCUITS 7.2 LOW DROPOUT LINEAR REGULATORS

However, it should be noted that in some types of regulators (notably those which have very low  $\beta$  pass devices such as lateral PNP transistors) the I<sub>ground</sub> current under load can actually run quite high. This effect is worst at the onset of regulation, or when the pass device is in saturation, and can be noted by a sudden I<sub>ground</sub> current "spike", where the current jumps upward abruptly from a low level. All LDO regulators using bipolar transistor pass devices which can be saturated (such as PNPs) can show this effect. It is much less severe in PNP regulators using vertical PNPs (since these have a higher intrinsic  $\beta$ ) and doesn't exist to any major extent in PMOS LDOs (since PMOS transistors are controlled by voltage level, not current).

In the example shown, the regulator delivers  $5 \text{ V} \times 1 \text{ A}$ , or 5 W to the load. With a dropout voltage of 1 V, the input power is 6-V times the same 1 A, or 6 W. In terms of power efficiency, this can be calculated as:

$$P_{EFF}(\%) = 100 \times \frac{P_{OUT}}{P_{IN}},$$

Eq. 7.11

where  $P_{OUT}$  and  $P_{IN}$  are the total output and input powers, respectively.

In these sample calculations, the relatively small portion of power related to I<sub>ground</sub> will be ignored for simplicity, since this power is relatively small. In an actual design, this simplifying step may not be justified.

In the case shown, the efficiency would be  $100 \times 5/6$ , or about 83%. But by contrast, if an LDO were to be used with a dropout voltage of 0.1 V instead of 1 V, the input voltage can then be allowed to go as low as 5.1 V. The new efficiency for this condition then becomes  $100 \times 5/5.1$ , or 98%. It is obvious that an LDO can potentially greatly enhance the power efficiency of linear voltage regulator systems.

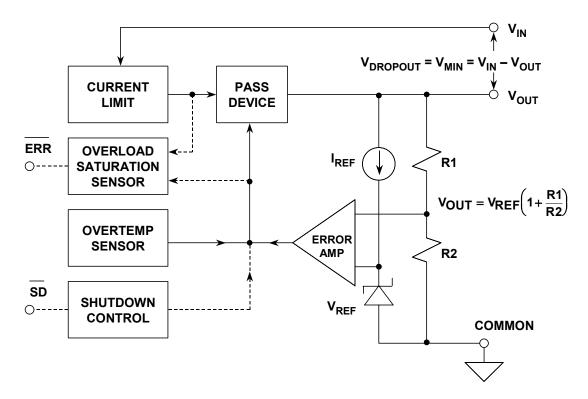

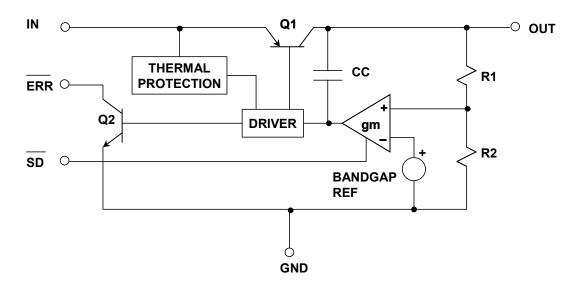

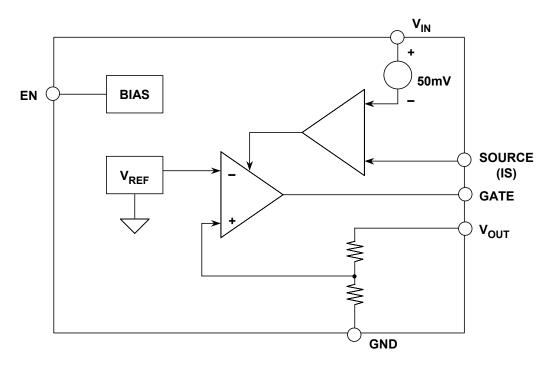

A more detailed look within a typical regulator block diagram reveals a variety of elements, as is shown in Figure 7.27.

In this diagram virtually all of the elements shown can be considered to be fundamentally necessary, the exceptions being the shutdown control and saturation sensor functions (shown dotted). While these are present on many current regulators, the shutdown feature is relatively new as a standard function, and certainly isn't part of standard three-terminal regulators. When present, shutdown control is a logic level controllable input, whereby a digital HIGH (or LO) is defined as regulation active (or vice-versa).

The error output, ERR, is useful within a system to detect regulator overload, such as saturation of the pass device, thermal overload, etc. The remaining functions shown are always part of an IC power regulator.

Figure 7.27: Block Diagram of a Voltage Regulator

In operation, a voltage reference block produces a stable voltage  $V_{REF}$ , which is almost always a bandgap based voltage, typically  $\sim 1.2$  V, which allows output voltages of 3 V or more from supplies as low as 5 V. This voltage is presented to one input of an error amplifier, with the other input connected to the  $V_{OUT}$  sensing divider, R1-R2. The error amplifier drives the pass device, which in turn controls the output. The resulting regulated voltage is then simply:

$$V_{OUT} = V_{REF} \left( 1 + \frac{R1}{R2} \right).$$

Eq. 7.12

With a typical bandgap reference voltage of 1.2 V, the R1/R2 ratio will be approximately 3/1 for a 5-V output. When standby power is critical, several design steps will be taken. The resistor values of the divider will be high, the error amplifier and pass device driver will be low power, and the reference current  $I_{REF}$  will also be low. By these means the regulator's unloaded standby current can be reduced to a mA or less using bipolar technology, and to only a few  $\mu$ A in CMOS parts. In regulators which offer a shutdown mode, the shutdown state standby current will be reduced to a  $\mu$ A or less.

Nearly all regulators will have some means of current limiting and over temperature sensing, to protect the pass device against failure. Current limiting is usually by a series sensing resistor for high current parts, or alternately by a more simple drive current limit to a controlled  $\beta$  pass device (which achieves the same end). For higher voltage circuits, this current limiting may also be combined with voltage limiting, to provide complete load line control for the pass device.

All power regulator devices will also have some means of sensing over-temperature, usually by means of a fixed reference voltage and a  $V_{BE}$ -based sensor monitoring chip temperature. When the die temperature exceeds a dangerous level (above  $\sim 150^{\circ}$ C), this can be used to shutdown the chip, by removing the drive to the pass device. In some cases an error flag output may be provided to warn of this shutdown (and also loss of regulation from other sources).

#### Pass Devices and their Associated Tradeoffs

The discussion thus far has not treated the pass device in any detail. In practice, this major part of the regulator can actually take on quite a number of alternate forms. Precisely which type of pass device is chosen has a major influence on almost all major regulator performance issues. Most notable among these is the dropout voltage,  $V_{\text{MIN}}$ .

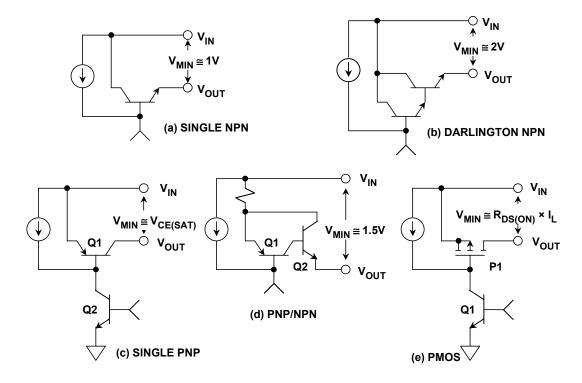

Figure 7.28a through 7.28e illustrates a number of pass devices which are useful within voltage regulator circuits, shown in simple schematic form. On the figure is also listed the salient  $V_{\mbox{MIN}}$  for the device as it would typically be used, which directly indicates its utility for use in an LDO. Not shown in these various mini-figures are the remaining circuits of a regulator.

It is difficult to fully compare all of the devices from their schematic representations, since they differ in so many ways beyond their applicable dropout voltages. For this reason, the chart of Figure 7.29 is useful.

Figure 7.28: Pass Devices Useful in Voltage Regulators

| Α                     | В                     | C                        | D                        | E                                                       |

|-----------------------|-----------------------|--------------------------|--------------------------|---------------------------------------------------------|

| SINGLE<br>NPN         | DARLINGTON<br>NPN     | SINGLE<br>PNP            | PNP/NPN                  | PMOS                                                    |

| V <sub>MIN</sub> ~ 1V | V <sub>MIN</sub> ~ 2V | V <sub>MIN</sub> ~ 0.1V  | V <sub>MIN</sub> ~ 1.5V  | V <sub>MIN</sub> ~ R <sub>DS(ON)</sub> × I <sub>L</sub> |

| I <sub>L</sub> < 1A   | I <sub>L</sub> > 1A   | I <sub>L</sub> < 1A      | I <sub>L</sub> > 1A      | I <sub>L</sub> > 1A                                     |

| Follower              | Follower              | Inverter                 | Inverter                 | Inverter                                                |

| Low Z <sub>OUT</sub>  | Low Z <sub>OUT</sub>  | High Z <sub>OUT</sub>    | High Z <sub>OUT</sub>    | High Z <sub>OUT</sub>                                   |

| Wide BW               | Wide BW               | Narrow BW                | Narrow BW                | Narrow BW                                               |

| C <sub>L</sub> Immune | C <sub>L</sub> Immune | C <sub>L</sub> Sensitive | C <sub>L</sub> Sensitive | C <sub>L</sub> Sensitive                                |

Figure 7.29: Pros and Cons of Voltage Regulator Pass Devices

This chart compares the various pass elements in greater detail, allowing easy comparison between the device types, dependent upon which criteria is most important. Note that columns A-E correspond to the schematics of Figure 7.28a-7.28e. Note also that the pro/con comparison items are in *relative* terms, as opposed to a hard specification limit for any particular pass device type.

For example, it can be seen that the all NPN pass devices of columns A and B have the attributes of a follower circuit, which allows high bandwidth and provides relative immunity to cap loading because of the characteristic low  $Z_{OUT}$ . However, neither the single NPN nor the Darlington NPN can achieve low dropout, for any load current. This is because the  $V_{BE}(s)$  of the pass device appears in series with the input, preventing its saturation, and thus setting a  $V_{MIN}$  of about 1 or 2 V.

By contrast, the inverting mode device connections of both columns C and E do allow the pass device to be effectively saturated, which lowers the associated voltage losses to a minimum. This single factor makes these two pass device types optimum for LDO use, at least in terms of power efficiency.

For currents below 1 A, either a single PNP or a PMOS pass device is most useful for low dropout, and they both can achieve a  $V_{MIN}$  of 0.1 V or less at currents of 100 mA. The dropout voltage of a PNP will be highly dependent upon the actual device used and the operating current, with vertical PNP devices being superior for saturation losses, as well as minimizing the  $I_{ground}$  spike when in saturation. PMOS pass devices offer the potential for the lowest possible  $V_{MIN}$ , since the actual dropout voltage will be the product of the device  $R_{DS(ON)}$  and  $I_L$ . Thus a low  $R_{DS(ON)}$  PMOS device can always be chosen to minimize  $V_{MIN}$  for a given  $I_L$ . PMOS pass devices are typically *external* to the LDO IC, making the IC actually a controller (as opposed to a complete and integral LDO). PMOS pass devices can allow currents up to several amps or more with very low dropout voltages. The PNP/NPN connection of column D is actually a hybrid hookup, intended to boost the current of a single PNP pass device. This it does, but it also adds the

## DATA CONVERTER SUPPORT CIRCUITS 7.2 LOW DROPOUT LINEAR REGULATORS

$V_{BE}$  of the NPN in series (which cannot be saturated), making the net  $V_{MIN}$  of the connection about 1.5 V.

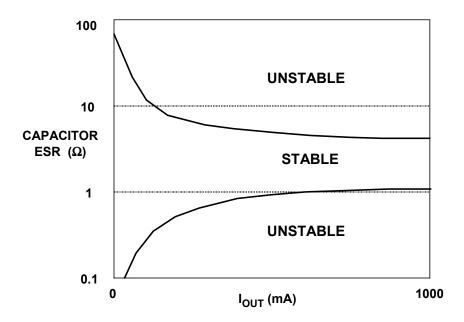

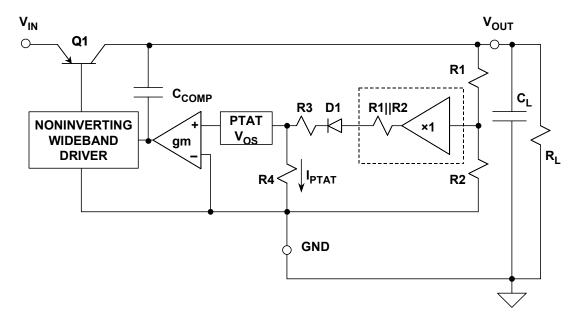

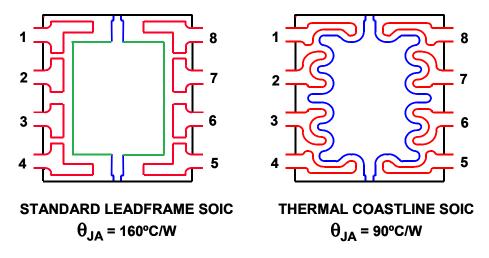

All of the three connections C/D/E have the characteristic of high output impedance, and require an output capacitor for stability. The fact that the output cap is part of the regulator frequency compensation is a most basic application point, and one which needs to be clearly understood by the regulator user. This factor, denoted by "C<sub>L</sub> sensitive", makes regulators using them generally critical as to the exact C<sub>L</sub> value, as well as its ESR (equivalent series resistance). Typically this type of regulator must be used only with a specific size as well as type of output capacitor, where the ESR is controlled with respect to both time and temperature to fully guarantee regulator stability. Fortunately, some recent Analog Devices LDO IC circuit developments have eased this burden on the part of the regulator user a great deal, and will be discussed below in further detail.

Some examples of standard IC regulator architectures illustrate the points above regarding pass devices, and allow an appreciation of regulator developments leading up to more recent LDO technologies.

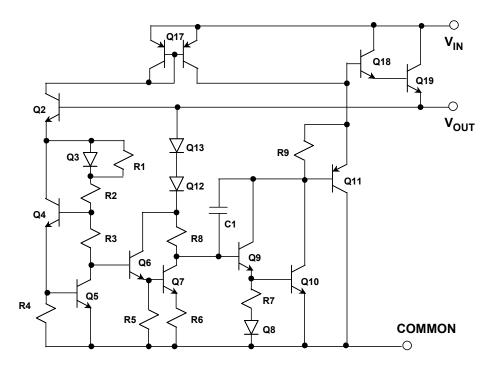

The classic LM309 5-V/1-A three-terminal regulator (see Reference 1) was the originator in a long procession of regulators. This circuit is shown in much simplified form in Figure 7.30, with current limiting and over temperature details omitted. This IC type is still in standard production today, not just in original form, but in family derivatives such as the 7805, 7815 etc., and their various low and medium current alternates. Using a Darlington pass connection for Q18-Q19, the design has never been known for low dropout characteristics (~1.5-V typical), or for low quiescent current (~5 mA). It is however relatively immune to instability issues, due to the internal compensation of C1, and the buffering of the emitter follower output. This helps make it easy to apply.

The LM109/309 bandgap voltage reference actually used in this circuit consists of a more involved scheme, as opposed to the basic form which was described with Figure 7.3. Resistor R8 drops a PTAT voltage, which drives the Darlington connected error amplifier, Q9-Q10. The negative TC  $V_{BE}$ s of Q9-Q10 and Q12-Q13 are summed with this PTAT voltage, and this sum produces a temperature-stable 5-V output voltage. Current buffering of the error amplifier Q10 is provided by PNP Q11, which drives the NPN pass devices.

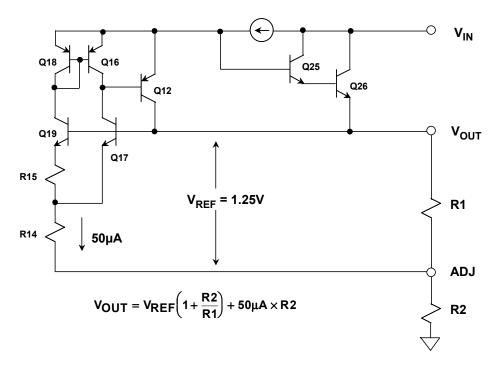

Later developments in references and three-terminal regulation techniques led to the development of the voltage adjustable regulator. The original IC to employ this concept was the LM317 (see Reference 2), which is shown in simplified schematic form in Figure 7.31. Note that this design does not use the same  $\Delta V_{BE}$  form of reference as in the LM309. Instead, Q17-Q19, etc. are employed as a form of a Brokaw bandgap reference cell (see Figure 7.4 again, and Reference 3).

Figure 7.30: Simplified Schematic of LM309 Fixed 5-V/1-A Three-Terminal Regulator

Figure 7.31: Simplified Schematic of LM317 Adjustable Three-terminal Regulator

This adjustable regulator bootstraps the reference cell transistors Q17-Q19 and the error amplifier transistors Q16-Q18. The output of the error amplifier drives Darlington pass transistors Q25-Q26, through buffer Q12. The basic reference cell produces a fixed voltage of 1.25 V, which appears between the  $V_{OUT}$  and ADJ pins of the IC as shown. External scaling resistors R1 and R2 set up the desired output voltage, which is:

$$V_{OUT} = V_{REF} \left( 1 + \frac{R2}{R1} \right) + 50 \mu A \times R2$$

. Eq. 7.13

As can be noted, the voltage output is a scaling of  $V_{REF}$  by R2-R1, plus a small voltage component which is a function of the 50- $\mu$ A reference cell current. Typically, the R1-R2 values are chosen to draw >5 mA, making the rightmost term relatively small by comparison. The design is internally compensated, and in many applications will not necessarily need an output bypass capacitor.

Like the LM309 fixed voltage regulator, the LM317 series has relatively high dropout voltage, due to the use of Darlington pass transistors. It is also not a low power IC (quiescent current typically 3.5 mA). The strength of this regulator lies in the wide range of user voltage adaptability it allows.

Subsequent variations on the LM317 pass device topology modified the method of output drive, substituting a PNP/NPN cascade for the LM317's Darlington NPN pass devices. This development achieves a lower  $V_{\text{MIN}}$ , 1.5 V or less (see Reference 4). The modification also allows all of the general voltage programmability of the basic LM317, but at some potential increase in application sensitivity to output capacitance. This sensitivity is brought about by the fundamental requirement for an output capacitor for the IC's frequency compensation, which is a differentiation from the original LM317.

# **Low Dropout Regulator Architectures**

As has been shown thus far, all LDO pass devices have the fundamental characteristics of operating in an inverting mode. This allows the regulator circuit to achieve pass device saturation, and thus low dropout. A by-product of this mode of operation is that this type of topology will necessarily be more susceptible to stability issues. These basic points give rise to some of the more difficult issues with regard to LDO performance. In fact, these points influence both the design and the application of LDOs to a very large degree, and in the end, determine how they are differentiated in the performance arena.

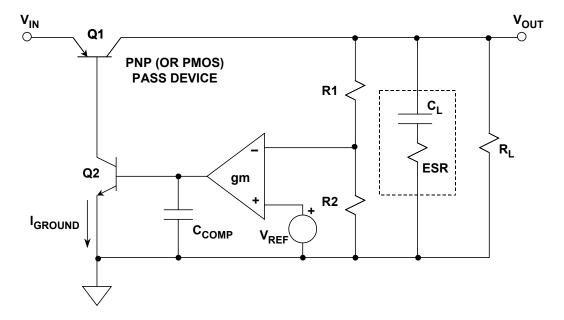

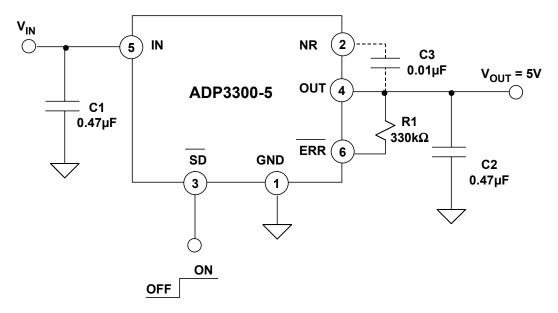

A traditional LDO architecture is shown in Figure 7.32, and is generally representative of actual parts employing either a PNP pass device as shown, or alternately, a PMOS device. There are both dc and ac design and application issues to be resolved with this architecture, which are now discussed.

Figure 7.32: Traditional LDO Architecture

In dc terms, perhaps the major issue is the type of pass device used, which influences dropout voltage and ground current. If a lateral PNP device is used for Q1, the  $\beta$  will be low, sometimes only on the order or 10 or so. Since Q1 is driven from the collector of Q2, the relatively high base current demanded by a lateral PNP results in relatively high emitter current in Q2, or a high  $I_{ground}$ . For a typical lateral PNP based regulator operating with a 5-V/150-mA output,  $I_{ground}$  will be typically ~18 mA, and can be as high as 40 mA. To compound the problem of high  $I_{ground}$  in PNP LDOs, there is also the "spike" in  $I_{ground}$ , as the regulator is operating within its dropout region. Under such conditions, the output voltage is out of tolerance, and the regulation loop forces higher drive to the pass device, in an attempt to maintain loop regulation. This results in a substantial spike upward in  $I_{ground}$ , which is typically internally limited by the regulator's saturation control circuits.

PMOS pass devices do not demonstrate a similar current spike in  $I_{ground}$ , since they are voltage controlled. But, while devoid of the  $I_{ground}$  spike, PMOS pass devices do have some problems of their own. Problem number one is that high quality, low  $R_{ON}$ , low threshold PMOS devices generally aren't compatible with many IC processes. This makes the best technical choice for a PMOS pass device an external part, driven from the collector of Q2 in the figure. This introduces the term "LDO controller", where the LDO architecture is completed by an external pass device. While in theory NMOS pass devices would offer lower  $R_{ON}$  choice options, they also demand a boosted voltage supply to turn on, making them impractical for a simple LDO. PMOS pass devices are widely available in low both  $R_{ON}$  and low threshold forms, with current levels up to several amperes. They offer the potential of the lowest dropout of any device, since dropout can always be lowered by picking a lower  $R_{ON}$  part.

The dropout voltage of lateral PNP pass devices is reasonably good, typically around 300 mV at 150 mA, with a maximum of 600 mV. These levels are however considerably bettered in regulators using vertical PNPs, which have a typical  $\beta$  of ~150 at currents of 200 mA. This leads directly to an  $I_{ground}$  of 1.5 mA at the 200-mA output current. The

# DATA CONVERTER SUPPORT CIRCUITS 7.2 LOW DROPOUT LINEAR REGULATORS

dropout voltage of vertical PNPs is also an improvement vis-à-vis that of the lateral PNP regulator, and is typically 180 mV at 200 mA, with a maximum of 400 mV.

There are also major ac performance issues to be dealt with in the LDO architecture of Figure. 7.32. This topology has an inherently high output impedance, due to the operation of the PNP pass device in a common-emitter (or common-source with a PMOS device) mode. In either case, this factor causes the regulator to appear as a high source impedance to the load.

The internal compensation capacitor of the regulator,  $C_{COMP}$ , forms a fixed frequency pole, in conjunction with the  $g_m$  of the error amplifier. In addition, load capacitance  $C_L$  forms an output pole, in conjunction with  $R_L$ . This particular pole, because it is a second (and sometimes variable) pole of a two-pole system, is the source of a major LDO application problem. The  $C_L$  pole can strongly influence the overall frequency response of the regulator, in ways that are both useful as well as detrimental. Depending upon the relative positioning of the two poles in the frequency domain, along with the relative value of the ESR of capacitor  $C_L$ , it is quite possible that the stability of the system can be compromised for certain combinations of  $C_L$  and ESR. Note that  $C_L$  is shown here as a real capacitor, which is actually composed of a pure capacitance plus the series parasitic resistance ESR.

Without a heavy duty exercise into closed-loop stability analysis, it can safely be said that LDOs, like other feedback systems, need to satisfy certain basic stability criteria. One of these is the gain-versus-frequency rate-of-change characteristic in the region approaching the system's unity loop gain crossover point. For the system to be closed loop stable, the phase shift must be less than 180° at the point of unity gain. In practice, a good feedback design needs to have some phase margin, generally 45° or more to allow for various parasitic effects. While a single pole system is intrinsically stable, two pole systems are *not* necessarily so—they may in fact be stable, or they may also be unstable. Whether or not they are stable for a given instance is highly dependent upon the specifics of their gain-phase characteristics.

If the two poles of such a system are widely separated in terms of frequency, stability may not be a serious problem. The emitter-follower output of a classic regulator like the LM309 is an example with widely separated pole frequencies, as the very low  $Z_{OUT}$  of the NPN follower pushes the output pole due to load capacitance far out in frequency, where it does little harm. The internal compensation capacitance (C1 of Fig. 7.30, again) then forms part of a *dominant pole*, which reduces loop gain to below unity at the much higher frequencies where the output pole does occur. Thus stability is not necessarily compromised by load capacitance in this type of regulator.

Figure 7.33 summarizes the various dc and ac design issues of LDOs.

DC AC Lateral PNP Pass Device: Two Pole Compensation System High I<sub>GROUND</sub> ◆ C₁ ESR Critical to Stability Vertical PNP Pass Device: Low I<sub>GROUND</sub> Low V<sub>MIN</sub> ◆ Requires Large C<sub>L</sub> **PMOS Pass Device: Lowest I<sub>GROUND</sub> Variation** ♦ Requires"Zoned" C<sub>1</sub> ESR Low V<sub>MIN</sub> (Max/Min ESR Limits Over Time **Ampere Level Output Currents** and Temperature)

Figure 7.33: DC and AC Design Issues in Low Dropout Regulators

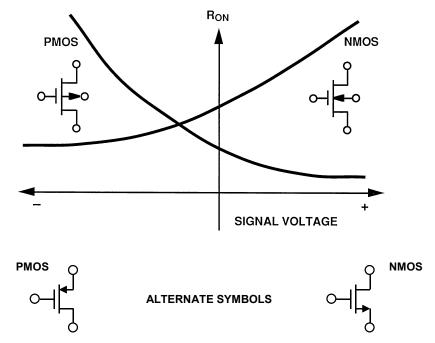

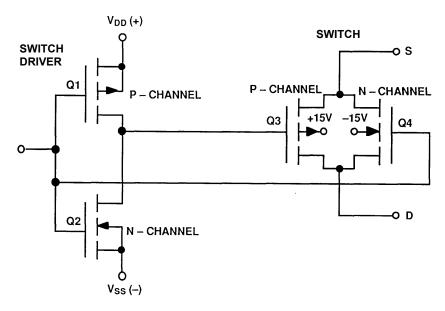

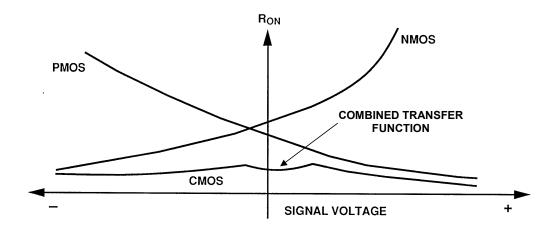

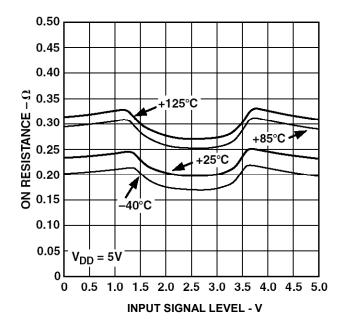

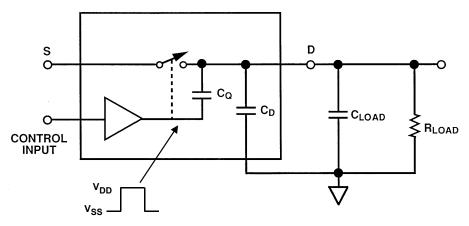

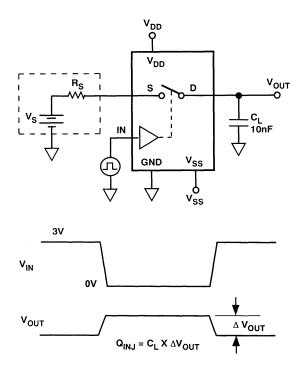

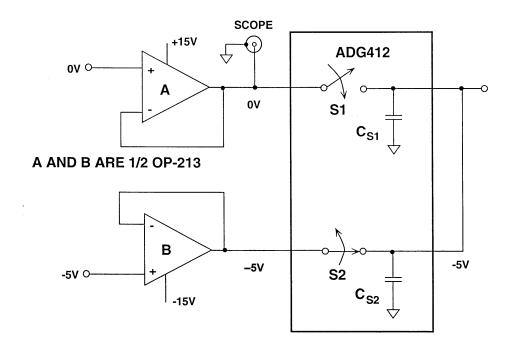

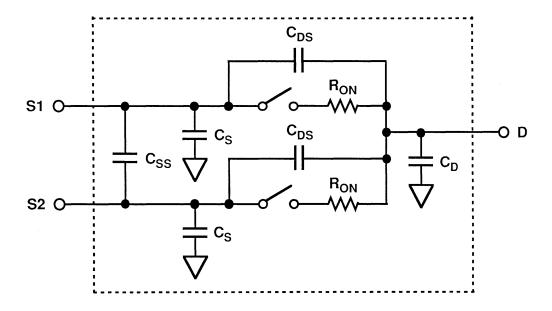

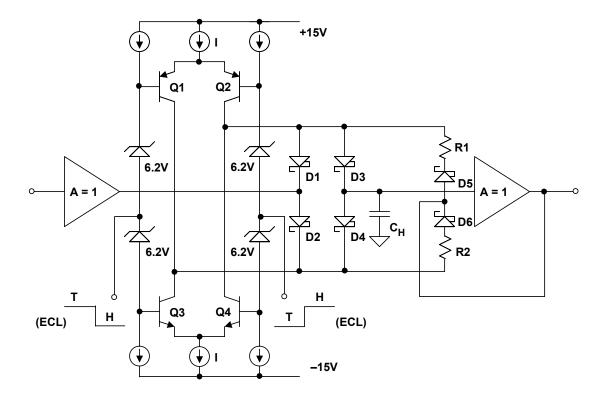

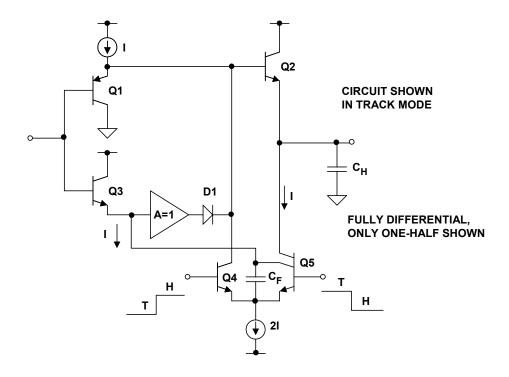

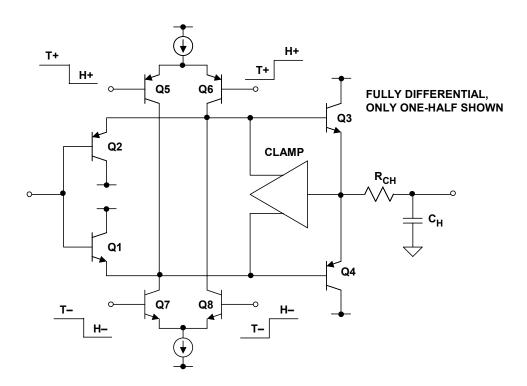

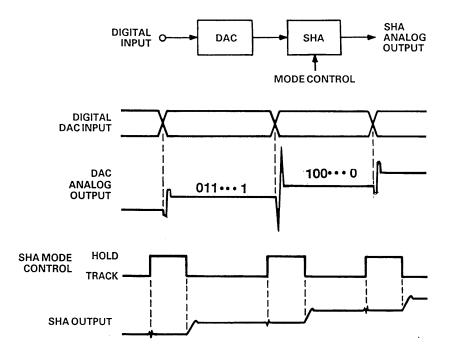

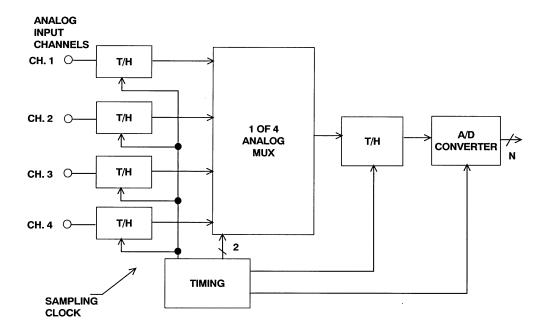

By their nature however, LDOs simply can't afford the luxury of emitter follower outputs, they must instead operate with pass devices capable of saturation. Thus, given the existence of two or more poles (one or more internal and a second formed by external loading) there is the potential for the cumulative gain-phase to add in a less than satisfactory manner. The potential for instability under certain output loading conditions is, for better or worse, a fact-of-life for most LDO topologies.