# **AN-617** アプリケーション・ノート

### ウェーハ・レベル・チップ・スケール・パッケージ WAFER LEVEL CHIP SCALE PACKAGE

著者:ウェーハ・レベル・パッケージ開発チーム

### 概要

Wafer Level Chip Scale Package (WLCSP) は、パッケージングプ ロセスの全てをウェーハ状態で加工するフリップチップ技術の一 種です。 WLCSP はダイの回路面上に加工された半田ボール (バ ンプ) によりプリント回路基板 (PCB) へ裏返しに実装されます。 これらの半田ボールのサイズは一般的なフリップチップ技術に比 べるとかなり大きく(リフロー前で250~300 µm)、アンダーフィ ルは要求されません。この技術には他にも以下のような利点があ ります。

- 1次レベルのパッケージ材(封止材、リードフレーム、また は有機基板) が無いため、大幅な省スペース化を実現でき ます。たとえば、8バンプ WLCSP が使用する基板面積は8 ピン SOIC が使用する基板面積のわずか 8%です。

- 標準的なプラスチックパッケージで使用されるワイヤボン ドやリードが無いため、インダクタンスが低減するなど、 電気的性能が向上します。

- リードフレームと封止材が無いため、軽量化と薄型化を実 現できます。

- 実装時に低質量ダイのセルフアライメント特性により、実装 歩留まりが向上されます。

### 目的

このアプリケーション・ノートは、エンドユーザ向けに下記につ いて説明します。

- WLCSP の構造と構成

- WLCSP の標準的な寸法

- PCB の設計

- 表面実装ガイドライン

- WLCSP の信頼性

- 熱特性

- リワーク

- 出荷形態

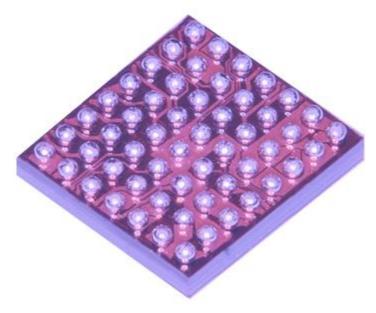

図1. 7×8配列のウェーハ・レベル・チップ・スケール・パッケージ(WLCSP)の写真

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用に よって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利 の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標 は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2007-2012 Analog Devices, Inc. All rights reserved.

Rev. D

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06(6350)6868

# **AN-617**

# アプリケーション・ノート

# 目次

| 微要         | 1 |

|------------|---|

| 目的         |   |

| 構造と構成      | 3 |

| WLCSP の構造  |   |

| WLCSP の構成  | 4 |

| WLCSP の寸法  | 4 |

| PCB の設計    | 5 |

| スタンドオフ     | 5 |

| ソルダーマスクの設計 | 5 |

| 基板の材料      | 5 |

| さまざまな推奨事項  | 6 |

| 基板の設計      | 6 |

| 実装の留意事項    | 7  |

|------------|----|

| 半田印刷工程     | 7  |

| 部品搭載工程     | 7  |

| リフロー工程     | 7  |

| WLCSP の信頼性 | 8  |

| 熱特性        | 9  |

| リワーク       | 10 |

| 出荷形態       | 11 |

| 仕様         | 11 |

| ESD 保護     | 11 |

| 引き剥がし強度    | 11 |

| 供給方向       | 11 |

| ピン1の方向     | 11 |

|            |    |

### 構造と構成

### WLCSP の構造

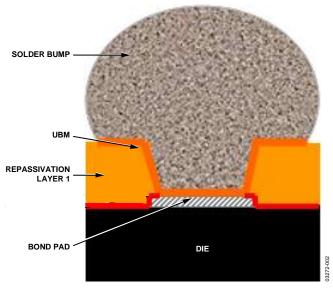

アナログ・デバイセズの WLCSP はダイレクトバンプタイプと、再配線(RDL)タイプという2種類に分類できます。ダイレクトバンプタイプは、アクティブ回路面へのストレス・バッファの役割を果たす有機リパッシベーション層とアンダーバンプメタル層(UBM)、半田バンプで構成されています。アクティブ回路面はボンドパッドの開口部を除き、リパッシベーションで全体が覆われています。また、ボンドパッド開口部上にはUBMが蒸着されています。UBMはさまざまな層を積み重ねた構造であり、拡散層、バリア層、湿潤層、耐酸化層として機能します。このUBM上に半田ボールを落とし(この方法はボールドロップといわれます)、これをリフローして半田バンプを形成します(図2参照)。

図 2. ダイレクトバンプタイプの代表的な構造

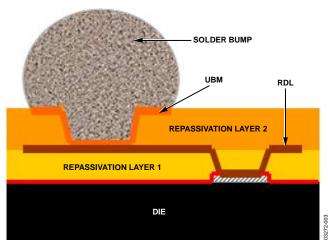

RDL タイプは、ワイヤボンディング用に設計されたダイ(ボンドパッドはダイの周囲に配列)から WLCSP を作るものです。ダイレクトバンプタイプとは異なり、 RDL タイプの WLCSP では 二層のリパッシベーションを使用します。最初のリパッシベーションをダイ上に塗布し、ボンドパッド部を開口しておきます。RDL 層を蒸着して、ペリフェラルアレイをエリアアレイ状に再配線します。その後は、ダイレクトバンプと同じように、第二のリパッシベーション層、UBM、半田バンプという構造になります(図3参照)。

図3. RDL タイプの代表的な構造

何れのタイプもボールドロップ処理後に、ウェーハの裏面研磨、レーザーマーキング、個片化を行い、テープ&リールに収納します。オプションとして、裏面ラミネートを裏面研磨後に追加し、個片化処理中に発生するダイ割れの低減やパッケージの取り扱いを容易にする方法もあります。

Rev. D - 3/11 -

### WLCSP の構成

アナログ・デバイセズの WLCSP 製品はすべて、標準ピッチが  $0.5\,\mathrm{mm}$  または  $0.4\,\mathrm{mm}$  です。このため、各ピン配列には、それぞれのバンプやピッチに対応する最小ダイサイズ (パッケージサイズ) があります。ピッチが  $0.5\,\mathrm{mm}$  または  $0.4\,\mathrm{mm}$  の最小ダイサイズを表 1 に示します。

表 1. 0.5 mm および 0.4 mm ピッチの WLCSP 最小ダイサイズ

|              | Maximum | Minimum Die Size                       |                                        |  |

|--------------|---------|----------------------------------------|----------------------------------------|--|

| Array        | I/O     | Pitch = 0.5 mm                         | Pitch = 0.4 mm                         |  |

| 2 × 2        | 4       | $1.0 \text{ mm} \times 1.0 \text{ mm}$ | $0.8 \text{ mm} \times 0.8 \text{ mm}$ |  |

| 2 × 3        | 6       | 1.0 mm × 1.5 mm                        | 0.8 mm × 1.2 mm                        |  |

| $3 \times 3$ | 9       | 1.5 mm × 1.5 mm                        | 1.2 mm × 1.2 mm                        |  |

| 3 × 4        | 12      | 1.5 mm × 2.0 mm                        | 1.2 mm × 1.6 mm                        |  |

| $4 \times 4$ | 16      | 2.0 mm × 2.0 mm                        | 1.6 mm × 1.6 mm                        |  |

| $4 \times 5$ | 20      | 2.0 mm × 2.5 mm                        | 1.6 mm × 2.0 mm                        |  |

| 5 × 5        | 25      | 2.5 mm × 2.5 mm                        | 2.0 mm × 2.0 mm                        |  |

| 5 × 6        | 30      | 2.5 mm × 3.0 mm                        | 2.0 mm × 2.4 mm                        |  |

| 6 × 6        | 36      | 3.0 mm × 3.0 mm                        | 2.4 mm × 2.4 mm                        |  |

| 6 × 7        | 42      | 3.0 mm × 3.5 mm                        | 2.4 mm × 2.8 mm                        |  |

| 7 × 7        | 49      | 3.5 mm × 3.5 mm                        | 2.8 mm × 2.8 mm                        |  |

| $7 \times 8$ | 56      | 3.5 mm × 4.0 mm                        | 2.8 mm × 3.2 mm                        |  |

| $8 \times 8$ | 64      | 4.0 mm × 4.0 mm                        | 3.2 mm × 3.2 mm                        |  |

| 8 × 9        | 72      | 4.0 mm × 4.5 mm                        | 3.2 mm × 3.6 mm                        |  |

| 9 × 9        | 81      | 4.5 mm × 4.5 mm                        | 3.6 mm × 3.6 mm                        |  |

| 9 × 10       | 90      | 4.5 mm × 5.0 mm                        | 3.6 mm × 4.0 mm                        |  |

| 10×10        | 100     | 5.0 mm × 5.0 mm                        | 4.0 mm × 4.0 mm                        |  |

### WLCSP の寸法

代表的なバンプの直径、高さ、およびシリコンの厚みとそれらの 許容誤差を表 2に示します。

表 2. 0.5 mm および 0.4 mm ピッチの WLCSP パッケージ寸法

| Dimension               | Tolerance | 0.5 mm Pitch | 0.4 mm l | Pitch  |

|-------------------------|-----------|--------------|----------|--------|

| Bump<br>Diameter        | ±40 μm    | 320 µm       | 260 µm   |        |

| Bump Height             | ±30 μm    | 240 μm       | 200 μm   |        |

| Silicon<br>Thickness    | ±30 μm    | 360 μm       | 400 μm   | 300 µm |

| Total Package<br>Height | ±60 μm    | 600 μm       | 600 µm   | 500 µm |

Rev. D — 4/11 —

### PCBの設計

### スタンドオフ

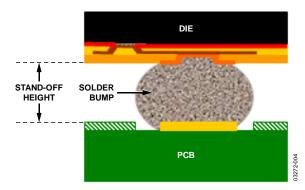

実装後の PCB とダイ表面との隙間(スタンドオフ)は、PCB に スクリーン印刷される半田ボール径とパッド径によって変動します。代表的な寸法を表 3に示します。 $300~\mu m$  のボールは直径  $250~\mu m$  の NSMD パッドに、 $250~\mu m$  のボールは直径  $200~\mu m$  の NSMD パッドに、 $150~\mu m$  のボールは直径  $110~\mu m$  の NSMD パッドにそれぞれ搭載したときの寸法です。

表 3. 実装後の代表的な WLCSP 寸法

| Solder Ball<br>Size (µm) | Total Package Height Before<br>Board Mount (mm) | Standoff Height (mm) |

|--------------------------|-------------------------------------------------|----------------------|

| 300                      | $0.600 \pm 0.06$                                | $0.190 \pm 0.03$     |

| 250                      | $0.500 \pm 0.06$                                | $0.140 \pm 0.03$     |

| 150                      | $0.315 \pm 0.015$                               | $0.120 \pm 0.03$     |

図 4. 実装後の WLCSP 半田接合部断面

### ソルダーマスクの設計

PCBの製造には、次の2種類のパッドパターンが有ります。

- Non solder mask defined (NSMD): PCB 上のパッド径 (これにパッケージ I/O を接続します) がソルダーマスクの開口径より小さいもの。

- Solder mask defined (SMD): ソルダーマスクの開口径がパッド径より小さいもの。

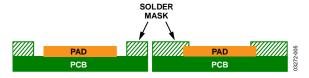

この2つのタイプのパッドパターンの断面比較を図5に示します。

図 5. NSMD と SMD のパッドパターンの断面図

パッドのエッチング寸法はソルダーマスクの開口径より厳密に制御されるため、SMDよりも NSMD のほうが推奨されます。また、NSMDパッドの場合、ソルダーマスクの開口部からパッドが完全に露出するため、パッドの側面も半田で覆われることになり、実装後の接合信頼性が向上します。(図4参照)

NSMD パッドに接続する配線パターンの幅はパッド径の 60%以下にする必要があります。更に PCB 設計でビアインパッドを使用する場合は、半田接合のボイドができないようにビアを充填して平坦にメッキを施す必要があります。

基板設計時には、基板メーカーでのソルダーマスク位置合わせ精度能力をチェックして、ソルダーマスクの開口サイズがパッド外径より 50 μmになるようにします。使用される実際のパッド寸法

は、半田バンプ径の 80%にしてください。必要な規定を満たすために、パッドの厚さは 1/2 oz 未満にする必要があります。また、パターン幅はパッド径の 60%以下の値を推奨します。ソルダーマスクの開口径はパッド径  $+100~\mu m$  にしてください。推奨パッド寸法を表4に示します。

表 4. 推奨パッド寸法

| Bump Diameter (mm) | Pad Diameter<br>(mm) | Solder Mask<br>Diameter (mm) |

|--------------------|----------------------|------------------------------|

| $0.320 \pm 0.04$   | $0.250 \pm 0.015$    | $0.350 \pm 0.015$            |

| $0.260 \pm 0.04$   | $0.200 \pm 0.015$    | $0.300 \pm 0.015$            |

| $0.160 \pm 0.04$   | $0.110 \pm 0.015$    | $0.210 \pm 0.015$            |

### 基板の材料

WLCSP は標準的なガラスエポキシ基板に対応します。更に標準FR-4をより熱膨張係数 (CTE) の小さい高温 FR-4に変えることで実装信頼性を向上させることが可能です。PCBの CTE は、金属層の数、ラミネート材料、パターン密度などの条件で変動します。基板のガラス転移温度は、組立品の適用温度を上回っていることが理想的です。

パッド上の仕上げ層は、実装の歩留まりと信頼性に大きく影響します。

- 最も適した表面仕上げとして有機表面保護材 (OSP) を推奨 します。保管期間は6カ月です。

- OSPの代わりに浸漬銀または浸漬錫も使用できます。

- 無電解のニッケル浸漬金 (ENIG) は脆化を防ぐために厚さ  $e^{0.02} = 0.05$   $\mu m$  に制限すれば許容できます。

- 基板は薄いほど柔軟性が高く、その結果、温度サイクルにおける接続信頼性が高くなります。工業用に使用されている標準的な基板の厚みは 0.4 ~2.3 mm です。どの厚みを選択するかは、実装後のシステム組立部品に求められる仕様によります。

Rev. D - 5/11 -

### さまざまな推奨事項

- パッド/ソルダーマスク位置合わせの許容誤差 = ± 25 μm

- ソルダーマスクはレーザダイレクトイメージング (LDI) が 可能なものを使用してください。

- 個別アライメントマークを使用してください。

- シルクスクリーンとデバイスのフットプリントの間隔を維持してください。

### 基板の設計

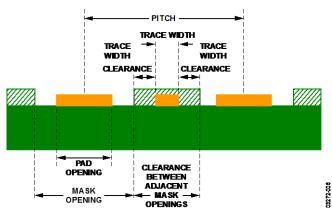

デバイスの機能が増大して小型化が進むほど、基板の製造は難しくなります。現在、業界では狭ピッチ化(400  $\mu$ m)による多配列化へと向かっていますが、基板製造技術に基づく形状の制約が存在するため基板表面層だけの配線では一般に設計が不可能な領域が増えてきています。パターン(幅と間隔)は、ソルダーマスクの各開口部間に収まらなければなりません。75  $\mu$ m パターン幅の標準的なクリアランスは各側面でそれぞれ 25  $\mu$ m となります。したがって、この場合の必要最少間隙は25  $\mu$ m +75  $\mu$ m +25  $\mu$ m =125  $\mu$ m です。隣接する2つのパッドの間に75  $\mu$ m のパターンを配線するには、隣接するソルダーマスク開口部間の間隙を125  $\mu$ m 以上の幅にする必要があります。PCB の標準的な配線/間隙のルールを図6と表5に示します。

図 6. PCB の標準的な配線/間隙のルール

ソルダーマスクの標準開口径が 350  $\mu m$  で、ピッチが 500  $\mu m$  の場合、ソルダーマスク開口部間の間隙は 150  $\mu m$  になります。

これは 75  $\mu$ m パターンで必要な間隙値 125  $\mu$ m より大きいため、パターンを表面層に配線することができます。同様に、ソルダーマスクの標準開口径が 300  $\mu$ m で、ピッチが 400  $\mu$ m であれば、ソルダーマスク開口部間の間隙は 100 $\mu$ m しかありません。この間隙値は 125  $\mu$ m より小さいため、表面層にパターンを配線することができません。これに代わる方法として、ビアインパッドを使って配線することが考えられます(表 5 参照)。

表 5. パターン幅が 75 µm の場合のパッドの寸法

| Pitch<br>(µm) | Mask<br>Size<br>(µm) | Clearance Between<br>Adjacent Mask Openings<br>(µm) | Comments                            |

|---------------|----------------------|-----------------------------------------------------|-------------------------------------|

| 500           | 350                  | 500 - (350/2 + 350/2) = 150                         | No issues routing (150 μm > 125 μm) |

| 400           | 300                  | 400 - (300/2 + 300/2) = 100                         | Issues routing (100 μm < 125 μm)    |

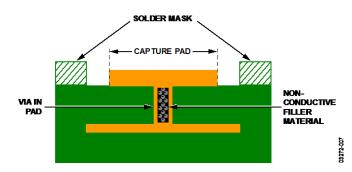

パッドにビアを設けることで、パターン間隙のクリアランスが増えます。しかし、開口径が 300  $\mu$ m の標準ビアの場合、半田がビアの中に垂れ下がって、半田接合が脆くなったり切断したりします。さらに、キャプチャパッドも半田パッドより大きくなってしまいます。レーザーによるマイクロビアを使用することで、基板に  $100\,\mu$ m の穴を開けることができ、メッキ処理後にはさらに  $50\,\mu$ m まで小さくできます。実装の歩留まりを最大にするために、半田接合のボイドができないようにビアを充填して平坦にメッキを施す必要があります。この例を図 7に示します。

図 7. ビアインパッドの断面構造図

Rev. D — 6/11 —

### 実装の留意事項

基板実装を行うために、リフロー前に半田ペーストを基板にスクリーン印刷する必要があります。以下にプロセスフローを示します。

- 1. 基板は実装前に 125°C で 24 時間乾燥してください。

- 2. WLCSP の受入れ検査

- 3. 半田ペーストの印刷と検査

- 4. 基板に WLCSP を搭載

- 5. 半田リフローと検査

- 6. フラックス洗浄 (オプション)

- 7. 検査

### 半田印刷工程

半田ペースト印刷では特別な注意が必要です。高さ、位置合わせのような工程すべてで検査を注意深く実施する必要があります。 さらに以下に注意してください。

- ステンシルのタイプ:レーザーカットまたは電気鋳造

- ステンシル厚(推奨値)

- 半田ボール径が 300 μm で 0.5mm ピッチのデバイス = 100 μm (4 ミル)

- 半田ボール径が 150 μm で 0.5mm ピッチのデバイス = 100 μm (4 ミル)

- 半田ボール径が 250 μm で 0.4mm ピッチのデバイス = 75 μm (3 ミル)

- スキージ

- タイプ:金属製

- 角度 = 60°

- 推奨半田ペースト: Alpha OM338T または千住金属工業 S70G type 4 (SAC305)

### 部品搭載工程

- 部品搭載にはビジョンアライメント機能を持った全自動搭載装置を使用してください。

- 搭載する力は最小とし、一般に150グラムにしてください。

- 搭載の精度を高めるために個別アライメントマークの使用を推奨します。

- リフロー前にアラインメント、ブリッジなどを確認するために X 線検査を行います。

#### リフロー工程

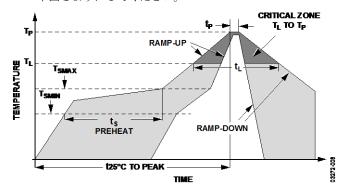

• 図8と表6に、JEDEC J-STD-D20 をベースにした推奨リフロープロファイルを示します。リフロープロファイルとピーク温度は、ボイド形成に大きな影響を与える可能性があるため注意が必要です。ピーク温度が低い場合は、長めの半田溶融時間(TAL)を必要とする可能性があります。

- リフローのピーク温度は、モイスチャーセンシティビティ レベル (MSL) に従って、パッケージが認定された最大温 度を超えないようにしてください。標準的な WLCSP デバイ スは MSL-1 です。

- 加熱炉は窒素パージを行い、炉内の酸素成分が 100 ppm を 下回るようにしてください。

図 8. 推奨リフロープロファイルの限界値

表 6. 推奨リフロープロファイルの限界値

| Profile Feature                                              | Pb Free          |

|--------------------------------------------------------------|------------------|

| Average Ramp Rate (T <sub>L</sub> to T <sub>P</sub> )        | 1.25°C/sec max   |

| Preheat                                                      |                  |

| Minimum Temperature (T <sub>SMIN</sub> )                     | 100°C            |

| Maximum Temperature (T <sub>SMAX</sub> )                     | 200°C            |

| Time ( $T_{SMIN}$ to $T_{SMAX}$ ), $t_S$                     | 60 sec to 75 sec |

| Ramp-Up Rate ( $T_{SMAX}$ to $T_L$ )                         | 1.25°C/sec       |

| Time Maintained Above Liquids (t <sub>L</sub> )              | ~50 sec          |

| Liquids Temperature (T <sub>L</sub> )                        | 217°C            |

| Peak Temperature (T <sub>P</sub> )                           | 260°C +0°C/-5°C  |

| Time Within 5°C of Actual Peak Temperature (t <sub>P</sub> ) | 20 sec to 30 sec |

| Ramp-Down Rate                                               | 3°C/sec max      |

| Time 25°C (t25°C) to Peak Temperature                        | 5 min max        |

実際のリフロー温度設定は、密度および熱負荷の影響に基づいて エンドユーザにて決定されます。詳細については、半田ペースト メーカーのデータシートなども参照してください。

注意: WLCSP (特にボールが大きいか高スタンドオフのパッケージ) は、一般にアンダーフィルを必要としません。もしアンダーフィルを採用される場合は、材料を慎重に選択、評価して、基板の組立工程/材料に適合することを確認してください。

Rev. D - 7/11 -

### WLCSPの信頼性

ダイを覆う封止材によって生じるパッケージ関連の一般的な問題は、封止材のないWLCSPではほとんどありません。たとえば、高温での電気的故障は、多くの場合封止材に起因するイオン不純物の移動が原因です。また、封止材の中に湿気が入り、ポプコーン現象または腐食が起こることもあります。WLCSPでは、このような故障はいずれもありません。それでも、PCBにダイを実装するため、温度サイクル中での半田破壊のような2次的なパッケージの問題を考慮する必要があります。

半田ボール内のエレクトロマイグレーションは、電流密度が最大になるポイント(すなわちパッシベーション開口部)で起きます。電流密度がかなり高ければ相分離が発生し、半田バンプと UBM の間でボイドが生じることがあります。

アルミニウムのような薄膜内のエレクトロマイグレーションと同じように、この場合も強い温度依存性があります。データシートの最大電流値の制限を確認してください。

アナログ・デバイセズは、故障メカニズムに基づいた新製品/新プロセスの包括的な認定評価を実施しています。通常の寿命条件で起きる可能性がある故障メカニズムについては、加速試験を行います。WLCSPに関連した故障メカニズムと適切なストレス試験の詳細を表7に示します。

表 7. WLCSP 故障メカニズム

| 故障メカニズム                       | 説明                                                                                      | ストレス試験                           |

|-------------------------------|-----------------------------------------------------------------------------------------|----------------------------------|

| 腐食                            | バンプまたは UBM の腐食は数種類の故障の原因になります。化学反応によって回路の断線が発生したり、デンドライト現象によって短絡や電流リークを発生することがあります。     | オートクレーブ/<br>高加速度ストレス試験<br>(HAST) |

| 拡散                            | 過度の金属間化合物の形成によって半田接合が脆化し、半田バンプの不良が発生<br>することがあります。                                      | 高温保存(HTS)                        |

| サーモマイグレーション/<br>エレクトロマイグレーション | 時間経過とともに半田バンプのマイグレーションが発生することがあります。過剰な Sn/Cu または Sn/Ni は、UBM/半田接合部でバンプの切断を発生させることがあります。 | 高温動作寿命(HTOL)                     |

| バンプ下地破壊                       | バンプ下のシリコンまたは表面保護膜に破壊が生じると、機能を喪失することが<br>あります。                                           | バンプ/ダイ・シェア強度                     |

| 熱機械的負荷による半田疲労                 | WLCSPと基板間の熱膨張係数差により、半田接合部に高ストレスが生じて半田<br>バンプの不良が発生することがあります。                            | 基板レベルでの温度サイク<br>ル                |

| 機械的負荷による半田疲労                  | 基板が過度に湾曲されると製品が故障することがあります。                                                             | 基板レベルでの落下試験                      |

|                               | さまざまな組立/試験動作中または実際の使用中に基板を繰り返し曲げると(周期的曲げ)、基板やパターン、半田接続部、部品などに亀裂が入り、電気的な故障が生じることがあります。   | 基板レベルでの曲げ試験                      |

Rev. D — 8/11 —

### 熱特性

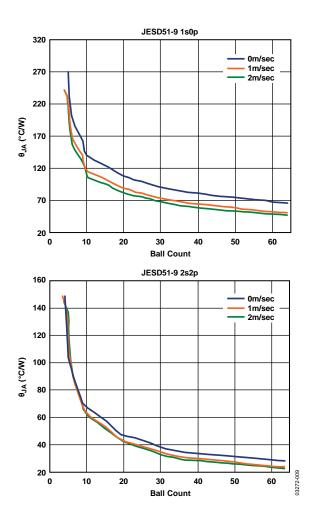

熱特性は、半田ボールから PCB への熱伝導によって左右されます。すなわち、WLCSP の熱特性を比較する場合にはボール数、基板の構造、銅パターンの密度などを加味する必要があります。また、グラウンドプレーンに接続する放熱用のボール数も考慮する必要があります。

比較シミュレーションは、WLCSP が JESD51-9 の標準評価基板 (1s0p: 1 層基板と 2s2p: 4 層基板) に完全に実装されていて、ダイのサイズは約 500  $\mu$ m ずつ増大するものと仮定することにより、簡略化することができます。表 8 に、ANSYS 市販コードに基づいた 3 次元有限要素法解析 (FEA) でモデル化した配列シリーズ、ダイサイズ、放熱用のボールの数を示します。

表 8. FEA のために検討されたパッケージ構造

| Array                 | Max I/O | Thermal Ball | Min Die Size (mm) |

|-----------------------|---------|--------------|-------------------|

| 2 × 2                 | 4       | 0            | 0.96 × 0.96       |

| $2 \times 1 \times 2$ | 5       | 0            | 1.3 × 0.9         |

| $2 \times 3$          | 6       | 1            | 0.95 × 1.45       |

| $3 \times 3$          | 9       | 1            | 1.3 × 1.3         |

| 3 × 4                 | 10      | 1            | $1.5 \times 2.0$  |

| $4 \times 4$          | 16      | 2            | $2.0 \times 2.0$  |

| 4 × 5                 | 20      | 2            | $2.0 \times 2.5$  |

| 5 × 5                 | 25      | 2            | $2.5 \times 2.5$  |

| 6 × 6                 | 36      | 4            | 3.0 × 3.0         |

| 8 × 8                 | 64      | 7            | $4.0 \times 4.0$  |

10 種類の配列で、周囲温度  $85^{\circ}$ C、1s0p と 2s2p の評価基板、0.25 W と 1.25 W の消費電力、3 種類のエアフロー条件によりモデル化しました。表 9 に代表的な結果を示し、図 9 に比較グラフを示します。

最も一般的な熱特性の評価尺度は、接合部温度と周囲温度間の熱抵抗熱抵抗  $(\theta_{IA})$  です。

$\theta_{JA}$  値は基板構造に依存します。銅層が多ければ、放熱効果が大きくなります。この関係は、低熱伝導評価基板(1s0p:1 層基板)と高伝導評価基板(2s2p:4 層基板)を比較することで明らかになります(図 9 参照)。

図 9. 1 層基板(1s0p)と 4 層基板(2s2p)の  $\theta_{JA}$ の比較(0.25 W)

Rev. D — 9/11 —

#### 表 9. 表 8 によるパッケージ構造のモデルから得られた代表的な結果

|                        |                       |        |         | θ <sub>JA</sub> (°C/W) |         |                        |                        |

|------------------------|-----------------------|--------|---------|------------------------|---------|------------------------|------------------------|

| Package Type PCB       | PCB                   | Power  | 0 m/sec | 1 m/sec                | 2 m/sec | θ <sub>JC</sub> (°C/W) | θ <sub>JB</sub> (°C/W) |

| 5L WLCSP               | 1S0P                  | 0.25 W | 266.6   | 231.5                  | 217.2   | 2.5                    | 57.6                   |

|                        |                       | 1.25 W | 249.5   | 224.3                  | 212.1   | 2.7                    | 56.3                   |

|                        | 2S2P                  | 0.25 W | 148.7   | 139.7                  | 136.5   | 2.5                    | 54.6                   |

|                        |                       | 1.25 W | 146.9   | 139.4                  | 136.4   | 2.6                    | 55.2                   |

| 20L WLCSP              | OL WLCSP 1S0P<br>2S2P | 0.25 W | 108.5   | 89.0                   | 82.3    | 0.6                    | 17.1                   |

|                        |                       | 1.25 W | 101.1   | 87.3                   | 81.2    | 0.6                    | 17.5                   |

|                        |                       | 0.25 W | 47.9    | 43.4                   | 42.1    | 0.7                    | 9.1                    |

|                        |                       | 1.25 W | 46.8    | 43.3                   | 42.1    | 0.7                    | 9.2                    |

| 64L WLCSP 1S0P<br>2S2P | 1S0P                  | 0.25 W | 65.5    | 50.4                   | 45.8    | 0.1                    | 7.1                    |

|                        |                       | 1.25 W | 60.6    | 49.7                   | 45.4    | 0.2                    | 7.3                    |

|                        | 2S2P                  | 0.25 W | 28.0    | 23.8                   | 22.8    | 0.2                    | 4.5                    |

|                        |                       | 1.25 W | 26.9    | 23.7                   | 22.7    | 0.2                    | 4.5                    |

### リワーク

WLCSPのリワークは、ボールグリッドアレイ(BGA)パッケージのリワークと同じように行います。次の手順でリワークを実施します。

- 1. リワーク処理中の吸湿ダメージを防ぐために基板を乾燥します。リワーク対象のデバイスも約 125~130℃で乾燥される必要があります。

- リワークステーションにおいて、ノズルから噴き出るホットエアにより、実装時のリフロープロファイルを再現します。温度が鉛フリー半田の融点(約217°C)に達したら、リワーク処理をするデバイスを取り外すことができます。デバイ

スは、リワークステーションのバキュームワンドで取り出 すことができます。

- 3. デバイスを取り除いたら、残りの半田が均一に広がるようにパッドを再調整します。

- 4. 再調整されたパッドにクリーニング不要のフラックスを塗布して、新しいデバイスを搭載します。

- 5. 再現された実装リフロープロファイルによりリワークス テーションにて新しいデバイスを実装します。このとき、 パッケージが認定された最大温度を超えないように注意し てください。

Rev. D — 10/11 —

### 出荷形態

近年の全自動実装装置は非常に高い精度で毎時数千個の部品をピックアップし、搭載することができます。この動作を達成するために、部品搬送システムは一定の方向に高速で部品を供給する必要があり、マシンの要求に確実に連動していなければなりません。こうした条件を満たす現在入手できる最適な梱包材はテープ&リールです。アナログ・デバイセズのテープ&リールシステムは、大部分の全自動実装装置と完全互換です。

### 仕様

アナログ・デバイセズのテープ&リールの仕様は、EIA Standard 481「Taping of Surface-Mount Components for Automatic Placement」に準拠しています。

### ESD 保護

アナログ・デバイセズのテープ&リールは、静電気放電 (ESD) に対して非常に優れた保護機能を備えています。

テープ&リール材料はすべて静電拡散材です。非防湿包装のリールは、ESD 導電性コーティングを施した箱または導電性 ESD バッグに入れて出荷します。この保護対策を生かすために、袋の開封は必ず ESD が管理された作業エリアで行ってください。

### 引き剥がし強度

引き剥がし強度は 8 mm幅のテープで  $10\sim100 \text{ g}$ 、12 mm 以上の幅のテープで  $10\sim130 \text{ g}$  です。いずれも、室温、引き剥がし速度  $300\pm10 \text{ mm/min}$ 、引き角度  $175\sim180^\circ$ という条件での試験結果です。

### 供給方向

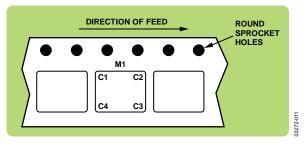

供給方向とは、エンドユーザがテープを引き出す方向のことです。 すべての製品の供給方向は、スプロケットホールが手前に来るよ うにリールを持った状態で反時計まわりとなります(図10参照)。

図 10. 供給方向

### ピン1の方向

デバイスは、供給方向とスプロケットホールによってピン1が正しい向きになるように巻かれています。ピン1の向きは、スプロケットホールを基準にC1からC4の方向になります(図11参照)。

図 11. ピン1の向き

©2007-2012 Analog Devices, Inc. All rights reserved. 商標および登録商標は、それぞれの所有者の財産です。

Rev. D — 11/11 —