## SC70 パッケージ採用の 2.7 V~5.5 V、<100 µA 8/10/12 ビット *nano*DAC <u>SPI インターフェース 付き</u>

### AD5601/AD5611/AD5621

#### 特長

6 ピンの SC70 パッケージを採用 マイクロパワー動作: 5 V で最大 100 μA パワーダウン電流: 3 V で 0.2 μA (typ)

電源電圧: 2.7 V~5.5 V 単調性をデザインにより保証

停電(電圧低下)検出機能付きのパワーオン・リセット(0V 出力)

3種類のパワーダウン機能

シュミット・トリガー入力付きの低消費電力シリアル・イン ターフェース

レール to レール動作の出力バッファ・アンプを内蔵

SYNC 割り込み機能を内蔵

ゼロ・コード誤差を最小化

SC70 採用のバッファ付き 8 ビット DAC、AD5601

B バージョン: ±0.5 LSB INL

SC70 採用のバッファ付き 10 ビット DAC、AD5611

B バージョン: ±0.5 LSB INL A バージョン: ±4 LSB INL

SC70 採用のバッファ付き 12 ビット DAC、AD5621

B バージョン: ±1 LSB INL A バージョン: ±6 LSB INL

### アプリケーション

電圧レベル設定 携帯型バッテリ駆動の計装機器 ゲインとオフセットのデジタル調整

プログラマブルな電圧源と電流源

プログラマブルな減衰器

#### 概要

nanoDAC<sup>®</sup>ファミリの AD5601/AD5611/AD5621 メンバーは、8/10/12 ビット・バッファ付きシングル電圧出力 DAC であり、2.7 V~5.5 V の単電源で動作し、消費電流は 5 V で 75  $\mu$ A (typ)で、小型の SC70 パッケージを採用しています。内蔵高精度出力アンプにより、レール to レール出力振幅が可能になっています。

AD5601/AD5611/AD5621 は、最大 30 MHz のクロック・レートで動作し、かつ SPI、QSPI<sup>TM</sup>、MICROWIRE<sup>TM</sup>、DSP インターフェースの各規格と互換性を持つ多機能の 3 線式シリアル・インターフェースを内蔵しています。

AD5601/AD5611/AD5621 は、消費電流を 3 V で 0.2  $\mu$  A (typ)まで減少させるパワーダウン機能を持っています。

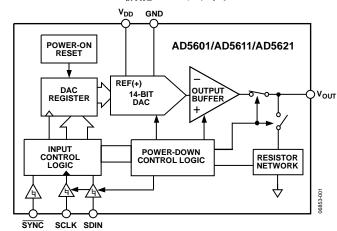

#### 機能ブロック図

図 1.

表 1.関連デバイス

| Part Number | Description                                                     |

|-------------|-----------------------------------------------------------------|

| AD5641      | 2.7 V to 5.5 V, <100 μA, 14-bit <i>nano</i> DAC in SC70 package |

パワーダウン・モードでは、出力負荷をソフトウェアから選択することができます。このデバイスはシリアル・インターフェースを使ってパワーダウン・モードに設定することができます。

これらのデバイスは、通常動作での消費電力が小さいため、ポータブルなバッテリ駆動の装置に最適です。小型パッケージと低消費電力とを組み合わせたこれらのnanoDACデバイスは、スペースと消費電力の制約が厳しいアプリケーションでバイアス電圧または制御電圧を発生するなどのレベル設定機能として最適です。

#### 製品のハイライト

- 省スペースの6ピンSC70パッケージを採用。

- 2. 低消費電力、単電源動作。AD5601/AD5611/AD5621 は 2.7~5.5 V の単電源で動作し、最大消費電流は 100μA であるため、バッテリ駆動のアプリケーショ ンに最適。

- 3. 内蔵出力バッファ・アンプはレール to レール振幅の DAC 出力が可能で、スルーレートは  $0.5 \text{ V/}\mu\text{s}$  (typ)。

- 4. リファレンス電圧は電源から発生。

- 5. 最大 30 MHz のクロック速度を持つ高速シリアル・インターフェースを内蔵。非常に小さい消費電力向けにデザイン。インターフェースは書き込みサイクルでのみパワーアップ。

- パワーダウン機能を内蔵。パワーダウン時の DAC 消費電流は 3 V で 0.2μA(typ)。停電検出でパワーオンを実行。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2005-2008 Analog Devices, Inc. All rights reserved.

Rev. D

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

# 目次

| 特長1                                                     | 出力アンプ                                              | 14 |

|---------------------------------------------------------|----------------------------------------------------|----|

| アプリケーション1                                               | シリアル・インターフェース                                      | 14 |

| 概要1                                                     | 入力シフトレジスタ                                          | 14 |

| 機能ブロック図1                                                | SYNC 割り込み                                          | 14 |

| 製品のハイライト1                                               | パワーオン・リセット                                         | 16 |

| 改訂履歴2                                                   | パワーダウン・モード                                         | 16 |

| 仕様3                                                     | マイクロプロセッサ・インターフェース                                 | 16 |

| タイミング特性4                                                | アプリケーション                                           | 18 |

| 絶対最大定格5<br>ESD の注意                                      | AD5601/AD5611/AD5621 の電源としてのリファ<br>電圧の選択           |    |

| ピン配置およびピン機能説明                                           | AD5601/AD5611/AD5621 を使用した両電源動作                    | 18 |

| 代表的な性能特性7                                               | AD5601/AD5611/AD5621 の電流絶縁インターフ                    |    |

| 用語13                                                    | での使用                                               |    |

| 動作原理14                                                  | 電源のバイパスとグラウンド接続                                    |    |

| DAC セクション14                                             | 外形寸法                                               |    |

| 抵抗ストリング14                                               | オーダー・ガイド                                           | 20 |

| 改訂履歴                                                    |                                                    |    |

| 5/08—Rev. C to Rev. D                                   | 7/05—Rev. A to Rev. B                              |    |

| Changes to General Description Section                  | Changes to Figure 48                               | 17 |

| Changes to Table 23                                     | Changes to Galvanically Isolated Interface Section |    |

| Changes to Choosing a Reference as Power Supply for the | Changes to Figure 52                               | 19 |

| AD5601/AD5611/AD5621 Section                            |                                                    |    |

| Changes to Ordering Guide                               | 3/05—Rev. 0 to Rev. A                              |    |

| 440E D D D G                                            | Changes to Timing Characteristics                  | 4  |

| 12/07—Rev. B to Rev. C                                  | Changes to Absolute Maximum Ratings                |    |

| Changes to Features                                     | Changes to Full Scale Error Section                |    |

| Changes to AD5601/AD5611/AD5621 to ADSP-2101            | Changes to Theory of Operation                     |    |

| Interface Section                                       | Changes to Prover Down Modes                       |    |

| Updated Outline Dimensions 20                           | Changes to Power Down Modes                        | 13 |

| Changes to Ordering Guide                               | 1/05—Revision 0: Initial Version                   |    |

| Changes to Ordering Guide                               | 1/05 Revision of initial version                   |    |

## 仕様

特に指定がない限り、 $V_{DD}$  = 2.7  $V\sim$ 5.5 V;  $R_L$  = 2  $k\Omega$  (GND  $\sim$ 接続);  $C_L$  = 200 pF (GND  $\sim$ 接続); すべての仕様は  $T_{MIN}\sim T_{MAX}$ で規定。A/B グレードの温度範囲は-40  $C\sim +125$  C、typ は 25 C での値。

表 2.

|                                      |     | A Grade      | e         |     | B Grade | e                 |               |                                                |

|--------------------------------------|-----|--------------|-----------|-----|---------|-------------------|---------------|------------------------------------------------|

| Parameter                            | Min | Тур          | Max       | Min | Typ     | Max               | Unit          | Test Conditions/Comments                       |

| STATIC PERFORMANCE                   |     |              |           |     |         |                   |               |                                                |

| AD5601                               |     |              |           |     |         |                   |               |                                                |

| Resolution                           |     |              |           | 8   |         |                   | Bits          |                                                |

| Relative Accuracy <sup>1</sup> (INL) |     |              |           |     |         | ±0.5              | LSB           |                                                |

| Differential Nonlinearity (DNL)      |     |              |           |     |         | ±0.5              | LSB           | Guaranteed monotonic by design                 |

| AD5611                               |     |              |           |     |         |                   |               |                                                |

| Resolution                           | 10  |              |           |     |         |                   | Bits          |                                                |

| Relative Accuracy <sup>1</sup> (INL) |     |              | ±4        |     |         | ±0.5              | LSB           |                                                |

| Differential Nonlinearity (DNL)      |     |              | $\pm 0.5$ |     |         | ±0.5              | LSB           | Guaranteed monotonic by design                 |

| AD5621                               |     |              |           |     |         |                   |               |                                                |

| Resolution                           | 12  |              |           |     |         |                   | Bits          |                                                |

| Relative Accuracy <sup>1</sup> (INL) |     |              | ±6        |     |         | ±1                | LSB           |                                                |

| Differential Nonlinearity (DNL)      |     |              | ±0.5      |     |         | ±0.5              | LSB           | Guaranteed monotonic by design                 |

| Zero-Code Error                      |     | 0.5          | 10        |     | 0.5     | 10                | mV            | All 0s loaded to DAC register                  |

| Full-Scale Error                     |     | ±0.5         |           |     | ±0.5    |                   | mV            | All 1s loaded to DAC register                  |

| Offset Error                         |     | ±0.063       | ±10       |     | ±0.063  | ±10               | mV            | _                                              |

| Gain Error                           |     | $\pm 0.0004$ | ±0.037    |     | ±0.0004 | ±0.037            | %FSR          |                                                |

| Zero-Code Error Drift                |     | 5.0          |           |     | 5.0     |                   | μV/°C         |                                                |

| Gain Temperature Coefficient         |     | 2.0          |           |     | 2.0     |                   | ppm<br>FSR/°C |                                                |

| OUTPUT CHARACTERISTICS <sup>2</sup>  |     |              |           |     |         |                   | TSK/ C        |                                                |

| Output Voltage Range                 | 0   |              | $V_{DD}$  | 0   |         | $V_{\mathrm{DD}}$ | V             |                                                |

| Output Voltage Settling Time         |     | 6            | 10        |     | 6       | 10                | μs            | Code ¼ scale to ¾ scale                        |

| Slew Rate                            |     | 0.5          | 10        |     | 0.5     | 10                | V/µs          | South of South to Alberta                      |

| Capacitive Load Stability            |     | 470          |           |     | 470     |                   | pF            | $R_{\rm L} = \infty$                           |

| cupusiii. e Zsua zuemitj             |     | 1000         |           |     | 1000    |                   | pF            | $R_L = 2 k\Omega$                              |

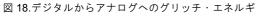

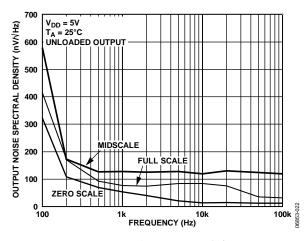

| Output Noise Spectral Density        |     | 120          |           |     | 120     |                   | nV/√Hz        | DAC code = midscale,1 kHz                      |

| Noise                                |     | 2            |           |     | 2       |                   | μV            | DAC code = midscale,                           |

| 1.0150                               |     | _            |           |     | -       |                   | F .           | 0.1 Hz to 10 kHz bandwidth                     |

| Digital-to-Analog Glitch Impulse     |     | 5            |           |     | 5       |                   | nV-s          | 1 LSB change around major carry                |

| Digital Feedthrough                  |     | 0.2          |           |     | 0.2     |                   | nV-s          |                                                |

| Short-Circuit Current                |     | 15           |           |     | 15      |                   | mA            | $V_{DD} = 3 \text{ V/5 V}$                     |

| DC Output Impedance                  |     | 0.5          |           |     | 0.5     |                   | Ω             |                                                |

| LOGIC INPUTS                         |     |              |           |     |         |                   |               |                                                |

| Input Current <sup>3</sup>           |     |              | ±2        |     |         | ±2                | μA            |                                                |

| Input High Voltage, V <sub>INH</sub> | 1.8 |              |           | 1.8 |         |                   | V             | $V_{DD} = 4.7 \text{ V to } 5.5 \text{ V}$     |

|                                      | 1.4 |              |           | 1.4 |         |                   | V             | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$     |

| Input Low Voltage, V <sub>INL</sub>  |     |              | 0.8       |     |         | 0.8               | V             | $V_{\rm DD} = 4.7 \text{ V to } 5.5 \text{ V}$ |

|                                      |     |              | 0.6       |     |         | 0.6               | V             | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$     |

| Pin Input Capacitance                |     | 3            |           |     | 3       |                   | pF            |                                                |

Rev.  $\mathbf{D}$  -3/20 -

|                                                    |     | A Grad | le  |     | B Gr | ade |      |                                                 |

|----------------------------------------------------|-----|--------|-----|-----|------|-----|------|-------------------------------------------------|

| Parameter                                          | Min | Typ    | Max | Min | Typ  | Max | Unit | Test Conditions/Comments                        |

| POWER REQUIREMENTS                                 |     |        |     |     |      |     |      |                                                 |

| $V_{ m DD}$                                        | 2.7 |        | 5.5 | 2.7 |      | 5.5 | V    | All digital inputs at $0 \text{ V}$ or $V_{DD}$ |

| $I_{\mathrm{DD}}$ for Normal Mode                  |     |        |     |     |      |     |      | DAC active and excluding load current           |

| $V_{DD} = \pm 4.5 \text{ V to } \pm 5.5 \text{ V}$ |     | 75     | 100 |     | 75   | 100 | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$            |

| $V_{DD} = \pm 2.7 \text{ V to } \pm 3.6 \text{ V}$ |     | 60     | 90  |     | 60   | 90  | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$            |

| $I_{DD}$ for All Power-Down Modes                  |     |        |     |     |      |     |      | $V_{IH} = V_{DD}$ and $V_{IL} = GND$            |

| $V_{DD} = \pm 4.5 \text{ V to } \pm 5.5 \text{ V}$ |     | 0.5    |     |     | 0.5  |     | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$            |

| $V_{DD} = \pm 2.7 \text{ V to } \pm 3.6 \text{ V}$ |     | 0.2    |     |     | 0.2  |     | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$            |

| POWER EFFICIENCY                                   |     |        | •   |     |      |     |      |                                                 |

| $ m I_{OUT}/I_{DD}$                                |     | 96     |     |     | 96   |     | %    | $I_{LOAD} = 2$ mA and $V_{DD} = \pm 5$ V        |

$<sup>^1</sup>$  直線性はコード範囲を縮小して計算(AD5621 ではコード 64 ~コード 4032、AD5611 ではコード 16~コード 1008、AD5601 ではコード 4 ~コード 252)。

### タイミング特性

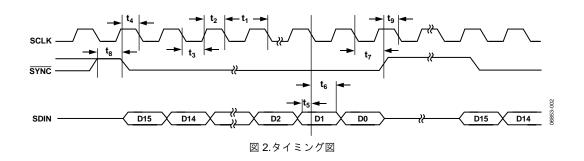

特に指定のない限り、 $V_{DD}=2.7\sim5.5~V$ ;すべての仕様は  $T_{MIN}\sim T_{MAX}$  で規定。 図 2 を参照してください。

#### 表 3.

| Parameter      | Limit <sup>1</sup> | Unit   | Test Conditions/Comments                           |

|----------------|--------------------|--------|----------------------------------------------------|

| $t_1^2$        | 33                 | ns min | SCLK cycle time                                    |

| $t_2$          | 5                  | ns min | SCLK high time                                     |

| $t_3$          | 5                  | ns min | SCLK low time                                      |

| $t_4$          | 10                 | ns min | SYNC to SCLK falling edge setup time               |

| $t_5$          | 5                  | ns min | Data setup time                                    |

| $t_6$          | 4.5                | ns min | Data hold time                                     |

| $t_7$          | 0                  | ns min | SCLK falling edge to SYNC rising edge              |

| $t_8$          | 20                 | ns min | Minimum SYNC high time                             |

| t <sub>9</sub> | 13                 | ns min | SYNC rising edge to next SCLK falling edge ignored |

$<sup>^1</sup>$  すべての入力信号は  ${\rm tr}={\rm tf}=1$  ns/V  $({\rm V}_{\rm DD}$ の 10%から 90%)で規定し、 $({\rm V}_{\rm IL}+{\rm V}_{\rm IH})/2$  の電圧レベルからの時間とします。

<sup>&</sup>lt;sup>2</sup> SCLK の最大周波数は 30 MHz。

-4/20Rev. D

<sup>&</sup>lt;0}  $^2$  デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>3</sup> すべてのピンに流入する合計電流。

### 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

#### 表 4.

| 2( 7.                           |                                            |  |  |

|---------------------------------|--------------------------------------------|--|--|

| Parameter                       | Rating                                     |  |  |

| V <sub>DD</sub> to GND          | -0.3 V to +7.0 V                           |  |  |

| Digital Input Voltage to GND    | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |

| V <sub>OUT</sub> to GND         | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |

| Operating Temperature Range     |                                            |  |  |

| Industrial (A/B Grades)         | −40°C to +125°C                            |  |  |

| Storage Temperature Range       | -65°C to +160°C                            |  |  |

| Maximum Junction Temperature    | 150°C                                      |  |  |

| SC70 Package                    |                                            |  |  |

| $\theta_{JA}$ Thermal Impedance | 433.34°C/W                                 |  |  |

| $\theta_{JC}$ Thermal Impedance | 149.47°C/W                                 |  |  |

| Lead Temperature, Soldering     |                                            |  |  |

| Vapor Phase (60 sec)            | 215°C                                      |  |  |

| Infrared (15 sec)               | 220°C                                      |  |  |

| ESD (Human Body Model)          | 2.0 kV                                     |  |  |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. **D** - 5/20 -

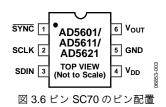

# ピン配置およびピン機能説明

### 表 5.ピン機能の説明

| ピン番号 | 記号                | 説明                                                                                  |

|------|-------------------|-------------------------------------------------------------------------------------|

| 1    | SYNC              | レベル検出のコントロール入力(アクティブ・ロー)。入力データのフレーム同期信号。SYNCがロー・レベ                                  |

|      |                   | ルになると、入力シフト・レジスタがイネーブルされ、データが次のクロックの立ち下がりエッジで転送                                     |

|      |                   | されます。このエッジの前にSYNCがハイ・レベルにならない限り、16番目のクロック・サイクルの後に                                   |

|      |                   | DAC が更新されます。このエッジの前にSYNCがハイ・レベルになると、SYNCの立ち上がりエッジは割                                 |

|      |                   | り込みとして機能し、書き込みシーケンスは DAC により無視されます。                                                 |

| 2    | SCLK              | シリアル・クロック入力。シリアル・クロック入力の立ち下がりエッジでデータが入力シフト・レジスタ                                     |

|      |                   | に入力されます。データは最大 30 MHz のレートで転送されます。                                                  |

| 3    | SDIN              | シリアル・データ入力。このデバイスは16ビット・シフト・レジスタを内蔵しています。データはシリ                                     |

|      |                   | アル・クロック入力の立ち下がりエッジでレジスタに入力されます。                                                     |

| 4    | $V_{\mathrm{DD}}$ | 電源入力。AD5601/AD5611/AD5621 は 2.7 V~5.5 V で動作することができます。 V <sub>DD</sub> は GND ヘデカップリン |

|      |                   | グする必要があります。                                                                         |

| 5    | GND               | グラウンド。AD5601/AD5611/AD5621 のすべての回路のグラウンド基準ポイント。                                     |

| 6    | $V_{OUT}$         | DAC からのアナログ出力電圧。出力アンプはレール to レール動作を行います。                                            |

Rev. **D** — 6/20 —

## 代表的な性能特性

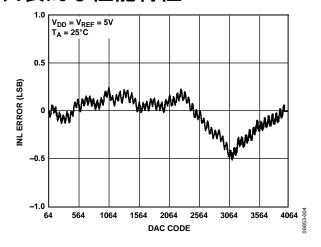

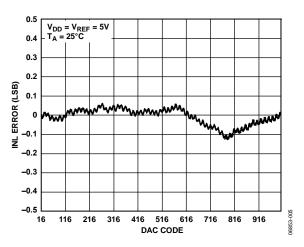

図 4.AD5621 の INL (typ)

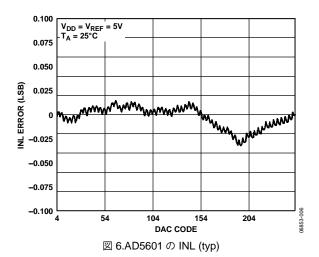

図 5.AD5611 の INL (typ)

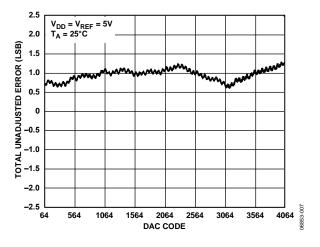

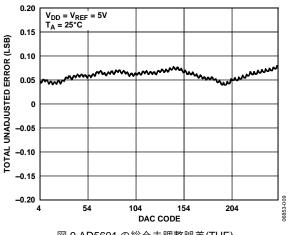

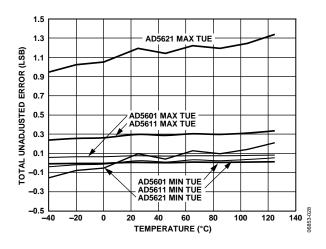

図 7.AD5621 の総合未調整誤差(TUE)

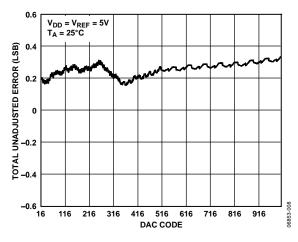

図 8.AD5611 の総合未調整誤差(TUE)

図 9.AD5601 の総合未調整誤差(TUE)

Rev. **D** - 7/20 -

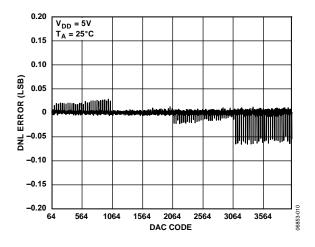

図 10.AD5621 の DNL (typ)

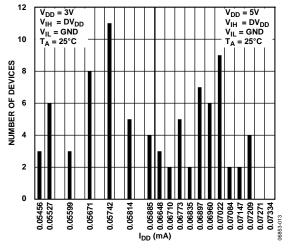

図 13.I<sub>DD</sub>のヒストグラム(3 V/5 V)

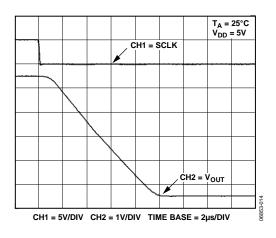

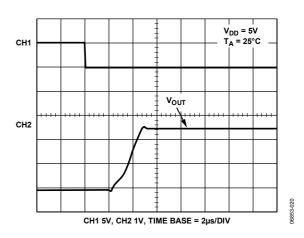

図 14.フル・スケール・セトリング・タイム

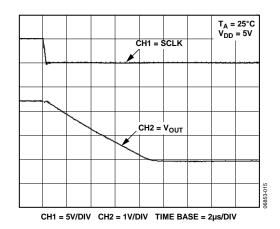

図 15.ハーフ・スケールのセトリング・タイム

Rev. **D** - 8/20 -

図 19.1/f ノイズ、0.1 Hz~10 Hz 帯域幅

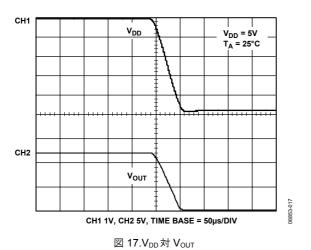

図 20.パワーダウン・モードの終了

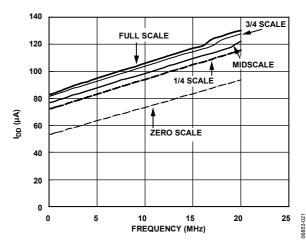

図 21.I<sub>DD</sub>対 SCLK 対コード

Rev. **D** - 9/20 -

図 22.ノイズ・スペクトル密度

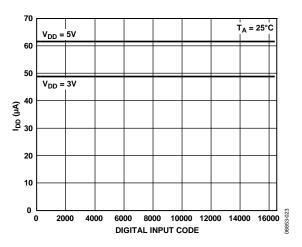

図 23.電源電流対デジタル入力コード

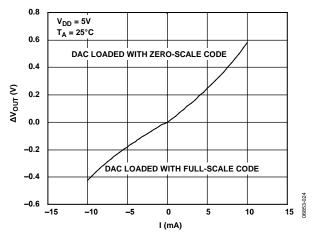

図 24.シンク能力とソース能力

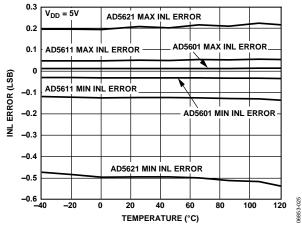

図 25.INL の温度特性(5 V)

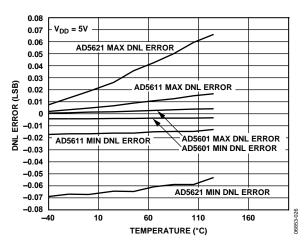

図 26.DNL の温度特性(5 V)

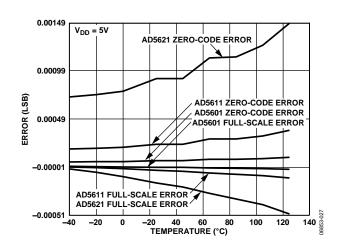

図 27.ゼロ・コード誤差とフル・スケール誤差の温度特性

Rev. **D** - 10/20 -

図 28.総合未調整誤差(TUE)の温度特性(5 V)

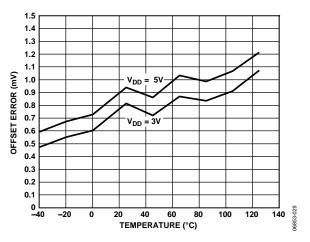

図 29.オフセット誤差の温度特性(3 V/5 V 電源)

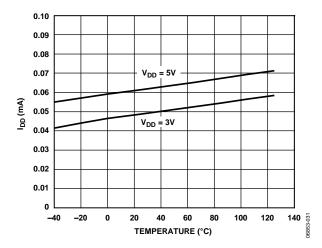

図 31.電源電流の温度特性(3 V/5 V 電源)

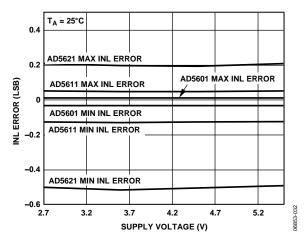

図 32.INL 対電源電圧、25℃

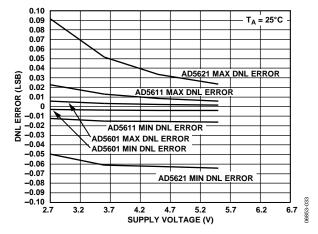

図 33.DNL 対電源電圧、25℃

Rev. **D** — 11/20 —

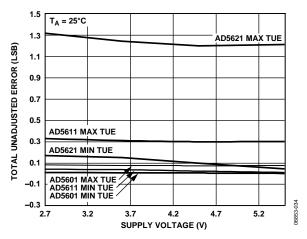

図 34.総合未調整誤差(TUE)対電源電圧、25℃

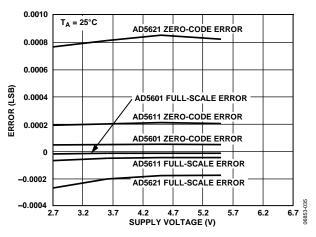

図 35.ゼロ・コード誤差およびフル・スケール誤差対 電源電圧、25℃

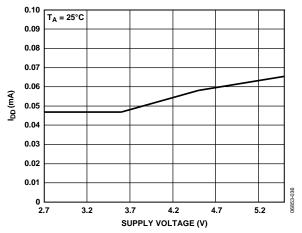

図 36.電源電流対電源電圧、25℃

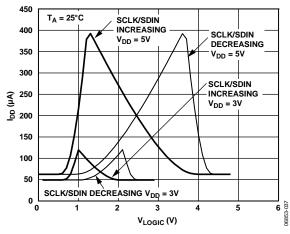

図 37.SCLK/SDIN 対ロジック電圧

Rev. **D** — 12/20 —

### 用語

#### 相対精度

DAC の場合、相対精度すなわち積分非直線性(INL)は、DAC 伝達関数の上下両端を結ぶ直線からの最大乖離(LSB 数で表示)を表します。INL 対コードのグラフについては、図 4~図 6 を参照してください。

#### 微分非直線性

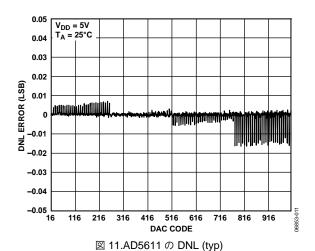

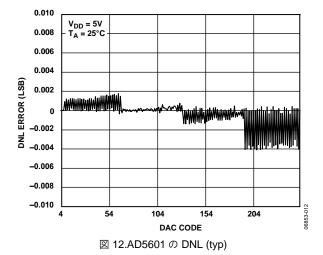

微分非直線性(DNL)は、隣接する 2つのコードの間における測定された変化と理論的な 1 LSB 変化との差をいいます。最大  $\pm 1$  LSB の微分非直線性の仕様は、単調性を保証するものです。この DAC はデザインにより単調性を保証しています。DNL 対コードのグラフについては、図 10~図 12 を参照してください。

#### ゼロ・コード誤差

ゼロ・コード誤差は、ゼロ・コード(0x0000)を DAC レジスタにロードしたときの出力として測定されます。理論的には出力は 0V である必要があります。

AD5601/AD5611/AD5621では DAC 出力が 0 V を下回ることができないため、ゼロ・コード誤差は常に正です。 DAC と出力アンプのオフセット誤差の組み合わせによりゼロ・コード誤差が発生します。ゼロ・コード誤差は mV で表します。ゼロ・コード誤差の温度特性については図 27 を参照してください。

### フル・スケール誤差

フル・スケール誤差は、フル・スケール・コード (0xFFFF)を DAC レジスタにロードしたときの出力として 測定されます。理論的には出力は  $V_{DD}-1$  LSB である必要があります。フル・スケール誤差は mV で表します。フル・スケール誤差の温度特性については図 27 を参照してください。

#### ゲイン誤差

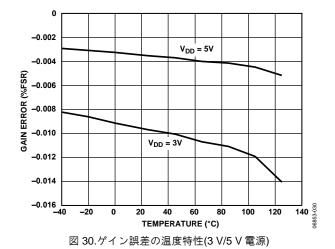

ゲイン誤差は DAC のスパン誤差を表します。理論値からの実際の DAC 伝達特性の傾きの差をフル・スケール範囲のパーセント値で表したものです。

#### 総合未調整誤差

総合未調整誤差(TUE)は、種々の誤差を考慮した出力誤差を表します。TUE 対コードのグラフについては、図7~図9を参照してください。

#### ゼロ・コード誤差ドリフト

ゼロ・コード誤差ドリフトは、温度変化によるゼロ・コード誤差の変化を表し、 $\mu V/\mathbb{C}$ で表されます。

#### ゲイン温度係数

ゲイン温度係数は、温度変化に対するゲイン誤差の変化を表し、(フル・スケール範囲のppm)/℃で表示します。

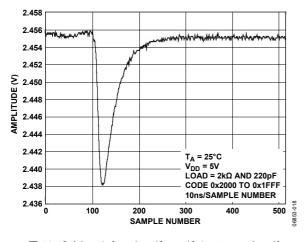

#### デジタルからアナログへのグリッチ・インパルス

デジタルからアナログへのグリッチ・インパルスは、DAC レジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルスを表します。通常、nV-secで表すグリッチの面積として規定され、主要なキャリ変化(0x2000から 0x1FFF)時に、デジタル・コードが 1 LSBだけ変化したときに測定されます。 図 18 を参照してください。

#### デジタル・フィードスルー

デジタル・フイードスルーは、DAC 出力の更新が行われていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。

nV-sec で規定され、データ・バス上でのフル・スケール変化時、すなわち全ビット 0 から全ビット 1 への変化、またはその逆の変化のときに測定されます。

Rev. D

### 動作原理

### DAC セクション

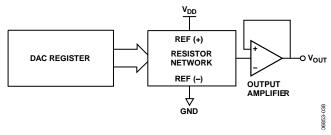

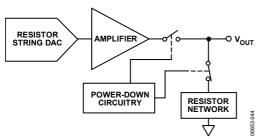

この AD5601/AD5611/AD5621 DAC は、CMOS プロセスを使って製造されています。このアーキテクチャは、ストリング DAC とそれに続く出力バッファ・アンプから構成されています。図 38 に、DAC アーキテクチャのブロック図を示します。

図 38.DAC アーキテクチャ

DACへの入力コーディングはストレート・バイナリを使っているため、理論出力電圧は次式で与えられます。

$$V_{OUT} = V_{DD} \times \left(\frac{D}{2^n}\right)$$

ここで、

Dは DAC レジスタにロードされたバイナリ・コードの 10 准表示

nは DAC のビット分解能。

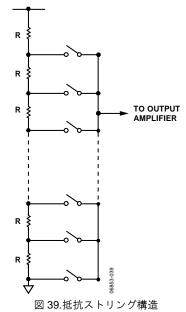

#### 抵抗ストリング

抵抗ストリング構造を図39に示します。DACは各値がRの抵抗ストリングから構成されています。DACレジスタにロードされるコードにより、ストリングのどのノードから電圧を分割して出力アンプへ供給するかが指定されます。スイッチの内の1つが閉じてストリングがアンプに接続されて、電圧が取り出されます。抵抗のストリングであるため、単調整が保証されます。

#### 出カアンプ

出力バッファアンプは、出力でレール to レール電圧を発生することができ、 $0 V \sim V_{DD}$ 出力範囲を発生します。

GND に接続された  $2 \, \mathrm{k}\Omega$  と、これに並列接続された  $1000 \, \mathrm{pF}$  の負荷を駆動することができます。図  $24 \, \mathrm{c}$ 、出力アンプのソース能力とシンク能力を示します。スルーレートは  $0.5 \, \mathrm{V/\mu s}$  であり、ハーフ・スケールでのセトリング・タイムは  $8 \, \mathrm{us}$  です。

#### シリアル・インターフェース

AD5601/AD5611/AD5621 は、SPI、QSPI、MICROWIRE の各インターフェース規格や大部分の DSP と互換性のある 3 線式シリアル・インターフェース(SYNC、SCLK、SDIN)を内蔵しています。図 2 に、代表的な書き込みシーケンスのタイミング図を示します。

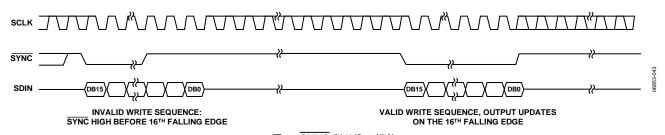

SYNCラインをロー・レベルにすると、書き込みシーケンスが開始されます。SDIN ラインからのデータは、SCLK の立ち下がりエッジで16 ビット・シフトレジスタに入力されます。シリアル・クロック周波数は30 MHzまで上げることができるので、AD5601/AD5611/AD5621は高速 DSP と互換性を持つことができます。16番目の立ち下がりクロック・エッジで最後のデータ・ビットが入力されて、プログラムされた機能が実行されます(DACレジスタ値の変更および/または動作モードの変更)。この時点で、SYNCラインをロー・レベルに維持するか、ハイ・レベルにすることができます。いずれの場合でも、SYNCの立ち下がりエッジで次の書き込みシーケンスを確実に開始できるようにするため、次の書き込みシーケンスの前に最小33 ns 間ハイ・レベルにする必要があります。

$V_{IN}$  = 0.8 V の場合よりは  $V_{IN}$  = 1.8 V の場合の方が $\overline{SYNC}$  バッファを流れる電流が大きくなるため、各書き込みシーケンスの間もSYNCをアイドル・ロー・レベルに維持して、前述のようにさらにデバイス消費電力を削減するようにします。ただし、次の書き込みシーケンスの開始前に1度ハイ・レベルに戻す必要があります。

#### 入力シフトレジスタ

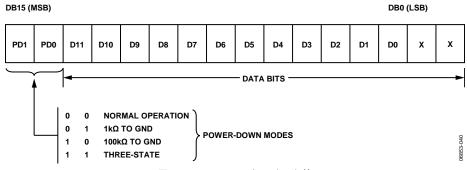

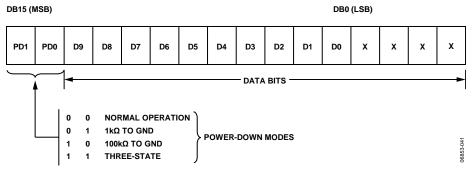

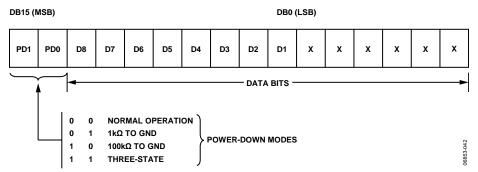

入力シフトレジスタは 16 ビット幅です(図 40 参照)。最初の 2 ビットはコントロール・ビットであり、デバイスの動作モードを決定します(ノーマル・モードまたは 3 種類のパワーダウン・モード)。各モードの詳細については、パワーダウン・モードのセクションを参照してください。AD5621 の場合、次の 12 ビットはデータ・ビットであり、SCLK の 16 番目の立ち下がりエッジで DAC レジスタに転送されます。最後の 2 ビットの情報は AD5621 から無視されます。AD5611 と AD5601 の入力シフト・レジスタ・マップにつていは、図 41 と図 42 を参照してください。

#### SYNC 割り込み

通常の書き込みシーケンスでは、SYNCラインは SCLK の少なくとも 16 個の立ち下がりエッジ間ロー・レベルに 維持され、DAC は 16 番目の立ち下がりエッジで更新されます。ただし、16 番目の立ち下がりエッジの前に SYNCをハイ・レベルにすると、これは書き込みシーケンスへの割込みとして機能します。シフトレジスタがリセットされて、書き込みシーケンスは無効と見なされます。DAC レジスタ値の更新も、動作モードの変更も行われません(図 43 参照)。

図 40.AD5621 の入力レジスタ値

図 41.AD5611 の入力レジスタ値

図 42.AD5601 の入力レジスタ値

図 43.SYNC 割り込み機能

Rev. **D** – 15/20 –

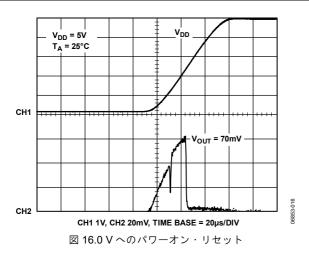

#### パワーオン・リセット

AD5601/AD5611/AD5621 は、パワーアップ時に出力電圧を制御するパワーオン・リセット回路を内蔵しています。DAC レジスタに 0 が設定されて、出力電圧は 0 V になります。このレベルは、DAC に有効な書き込みシーケンスが実行されるまで維持されます。この機能は、デバイスのパワーアップ時の DAC 出力状態が既知である必要のあるアプリケーションで特に便利です。

#### パワーダウン・モード

AD5601/AD5611/AD5621 には、4種類の動作モードがあります。これらのモードは、コントロール・レジスタのビット DB15 とビット DB14の2ビットを設定してソフトウェアから設定されます。表6に、ビット状態とデバイスの動作モードの対応を示します。

表 6.AD5601/AD5611/AD5621 の動作モード

| DB15 | DB14 | Operating Mode    |

|------|------|-------------------|

| 0    | 0    | Normal operation  |

|      |      | Power-down modes: |

| 0    | 1    | 1 kΩ to GND       |

| 1    | 0    | 100 kΩ to GND     |

| 1    | 1    | Three-state       |

両ビットを 0 に設定すると、デバイスは 5 V で最大  $100\mu A$  の消費電流でノーマル動作します。ただし、3 種類のパワーダウン・モードでは、電源電流が 3 V で  $0.2\mu A$ (typ)に減少します。

電源電流が減少するだけでなく、出力ステージも内部的 にアンプ出力から切り離されて既知の値を持つ抵抗回路 に接続されます。これは、デバイスの出力インピーダンスが既知であると同時にデバイスがパワーダウン・モードになるという利点を持っています。

出力が内部で  $1 k\Omega$  の抵抗または  $100 k\Omega$  の抵抗を経由して GND に接続されるか、または出力がオープン(スリー・ステート)になるかの 3 種類のオプションがあります。図 44 に出力ステージを示します。

図 44.パワーダウン時の出力ステージ

パワーダウン・モードのときは、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、およびその他の関係するすべてのリニア回路はすべてシャットダウンされます。ただし、DAC レジスタの値はパワーダウン・モードで影響を受けることはありません。パワーダウン・モードから抜け出す時間は、 $V_{DD}$  =5 V のときは 13  $\mu s$  (typ)で、 $V_{DD}$  =3 V のときは 16 $\mu s$  (typ)です。図 20 V に、グラフを示します。

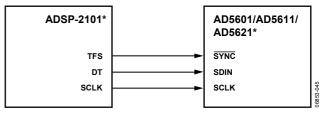

### マイクロプロセッサ・インターフェース AD5601/AD5611/AD5621 と ADSP-2101 とのインタ ーフェース

図 45 に、AD5601/AD5611/AD5621 と ADSP-2101 との間のシリアル・インターフェースを示します。ADSP-2101 は、SPORT 送信交番フレーミング・モードで動作するように設定する必要があります。ADSP-2101 の SPORT は、SPORT コントロール・レジスタを使って設定し、内部クロック動作、アクティブ・ロー・レベル・フレーミング、16 ビット・ワード長に設定する必要があります。送信は、SPORT をイネーブルした後に、Tx レジスタにワードを書きこむことにより、起動されます。

\*ADDITIONAL PINS OMITTED FOR CLARITY

図 45.AD5601/AD5611/AD5621 と ADSP-2101 との インターフェース

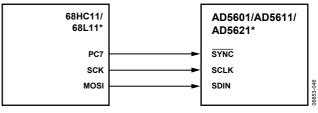

#### AD5601/AD5611/AD5621 と 68HC11/68L11 とのイン ターフェース

図 46 に、AD5601/AD5611/AD5621 と 68HC11/68L11 マイクロコントローラとの間のシリアル・インターフェースを示します。68HC11/68L11 の SCK が

AD5601/AD5611/AD5621 の SCLK を駆動し、MOSI 出力が DAC のシリアル・データ・ラインを駆動します。 SYNC信号は、ポート・ライン(PC7)から発生されます。 このインターフェースの正常動作のためには、

68HC11/68L11 で CPOL ビット= 0 かつ CPHA ビット= 1 の 設定を行う必要があります。データが DAC へ送信されると、 $\overline{SYNC}$ ラインがロー・レベルになります(PC7)。

68HC11/68L11 が上記のように設定された場合には、

MOSI に出力されるデータは SCK の立ち下がりエッジで有効になります。シリアル・データは 68HC11/68L11 から 8 ビットのバイトで転送され、送信サイクル内の 8 個の立ち下がりクロック・エッジが使用されます。データは MSB ファーストで転送されます。データを

AD5601/AD5611/AD5621 にロードするときは、最初の 8 ビットが転送された後にも PC7 をロー・レベルのままにして、DAC に対して 2番目のシリアル書き込み動作を実行します。このプロシージャの終わりに、PC7 をハイ・レベルにします。

\*ADDITIONAL PINS OMITTED FOR CLARITY

図 46.AD5601/AD5611/AD5621 と 68HC11/68L11 との インターフェース

Rev. **D** — 16/20 —

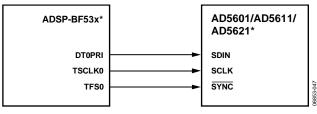

#### AD5601/AD5611/AD5621 と Blackfin® ADSP-BF53x とのインターフェース

図 47 に、AD5601/AD5611/AD5621 と Blackfin ADSP-BF53x マイクロプロセッサとの間のシリアル・インターフェースを示します。ADSP-BF53x ファミリは、シリアル通信とマルチプロセッサ通信用に 2 個のデュアル・チャンネル同期シリアル・ポート(SPORT0 と SPORT1)を内蔵しています。SPORT0 を使って AD5601/AD5611/AD5621 に接続し、DT0PRI が AD5601/AD5611/AD5621 の SDINピンを駆動し、TSCLK0 がデバイスの SCLK を駆動するようにインターフェースを設定します。 $\overline{SYNC}$ は TFS0 から駆動されます。

\*ADDITIONAL PINS OMITTED FOR CLARITY

図 47.AD5601/AD5611/AD5621 と Blackfin ADSP-BF53x とのインターフェース

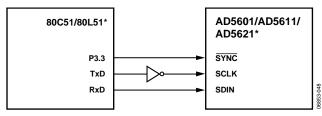

### AD5601/AD5611/AD5621 と 80C51/80L51 との インターフェース

図 48 に、AD5601/AD5611/AD5621 と 80C51/80L51 マイ クロコントローラとの間のシリアル・インターフェース を示します。このインターフェースでは、80C51/80L51 の TxD が AD5601/AD5611/AD5621 の SCLK を駆動し、 RxDがこのデバイスのシリアル・データ・ラインを駆動 します。SYNC信号は、この場合もポートのビット・プ ログラマブルなピンから発生されます。このケースでは ポート・ライン P3.3 を使用しています。データを AD5601/AD5611/AD5621 に転送するときは、P3.3 をロ ー・レベルにします。80C51/80L51 はデータを 8 ビット のバイトとして転送するため、送信サイクル内の8個の 立ち下がりクロック・エッジを使います。データを DAC にロードするときは、最初の8ビットが転送された後 P3.3 をロー・レベルのままにして、2番目の書き込みサ イクルを実行すると、データの2番目のバイトの転送が 開始されます。

このサイクルの完了後に P3.3 をハイ・レベルにします。 80C51/80L51 は、シリアル・データを LSB ファーストで 出力します。 AD5601/AD5611/AD5621 は、MSB ファーストでデータを受け取る必要があります。 80C51/80L51 の 送信ルーチンでは、このことを考慮しておく必要があります。

\*ADDITIONAL PINS OMITTED FOR CLARITY

図 48.AD5601/AD5611/AD5621 と 80C51/80L51 とのインターフェース

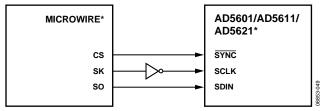

#### AD5601/AD5611/AD5621 と MICROWIRE との インターフェース

図 49 に、AD5601/AD5611/AD5621 とすべての MICROWIRE 互換デバイスとの間のインターフェースを 示します。シリアル・データはシリアル・クロックの立 ち下がりエッジで出力され、SK の立ち上がりエッジで AD5601/AD5611/AD5621 に入力されます。

\*ADDITIONAL PINS OMITTED FOR CLARITY

図 49.AD5601/AD5611/AD5621 と MICROWIRE とのインターフェース

Rev. **D** - 17/20 -

### アプリケーション

# AD5601/AD5611/AD5621 の電源としてのリファレンス電圧の選択

AD5601/AD5611/AD5621 は小型の SC70 パッケージを採用し、 $100\mu A$  未満の電源電流で動作します。このため、リファレンス電圧の選択はアプリケーションに依存します。省スペースが要求されるアプリケーションには、ADR02 が推奨されます。SC70 パッケージが使用可能であり、 $9 \text{ ppm/}^{\circ}\text{C}$ の優れたドリフト性能を持っています(R-8 パッケージでは  $3 \text{ ppm/}^{\circ}\text{C}$ )。さらに 0.1 Hz の範囲で  $3.4 \mu V$  p-p の非常に優れたノイズ性能を持っています。

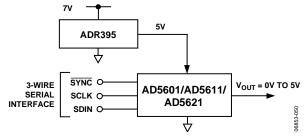

AD5601/AD5611/ AD5621 の要求する電源電流は極めて小さいため、このデバイスは低消費電力アプリケーションに最適です。この場合、電圧リファレンス ADR395 の使用が推奨されます。 $100\mu A$  未満の静止電流で済むため、必要に応じて1つのシステム内で複数のDAC を駆動することができます。また、 $0.1\sim10~Hz$  の範囲で $8~\mu V~p-p$  の非常に優れたノイズ性能も持っています。

図 50. AD5601/AD5611/AD5621 の電源として ADR395 を使用

AD5601/AD5611/AD5621 の電源としての使用が推奨される高精度リファレンスを表7に示します。

表 7.AD5601/AD5611/AD5621 の高精度リファレンス電圧

| Part No. | Initial<br>Accuracy<br>(mV max) | Temp Drift<br>(ppm/°C max) | 0.1 Hz to 10 Hz<br>Noise (µV p-p typ) |

|----------|---------------------------------|----------------------------|---------------------------------------|

| ADR435   | ±2                              | 3 (R-8)                    | 8                                     |

| ADR425   | ±2                              | 3 (R-8)                    | 3.4                                   |

| ADR02    | ±3                              | 3 (R-8)                    | 10                                    |

| ADR02    | ±3                              | 3 (SC70)                   | 10                                    |

| ADR395   | ±5                              | 9 (TSOT-23)                | 8                                     |

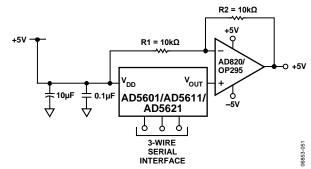

#### AD5601/AD5611/AD5621 を使用した両電源動作

AD5601/AD5611/AD5621 は単電源動作用にデザインされていますが、図 51 の回路を使うと、バイポーラ出力範囲も可能になります。図 51 の回路の出力電圧範囲は $\pm 5$  Vです。アンプ出力でのレール to レール動作は、AD820 または OP295 を出力アンプとして使うと、実現することができます。

図 51.AD5601/AD5611/AD5621 を使用した両電源動作

任意の入力コードに対する出力電圧は次のように計算することができます。

$$V_{OUT} = \left[V_{DD} \times \left(\frac{D}{2^{N}}\right) \times \left(\frac{RI + R2}{RI}\right) - V_{DD} \times \left(\frac{R2}{RI}\right)\right]$$

ここで、D は入力コードに等価な 10 進値 $(0\sim2^N)$ を表します。

$V_{DD}$  = 5 V、R1 = R2 = 10 k $\Omega$  のとき、

$$V_{OUT} = \left(\frac{10 \times D}{2^N}\right) - 5 \text{ V}$$

これは $\pm 5$  V の出力電圧範囲になり、0x0000 は-5 V の出力に、0x3FFF は+5 V の出力に、それぞれ対応します。

Rev. **D** — 18/20 —

# AD5601/AD5611/AD5621 の電流絶縁インターフェースでの使用

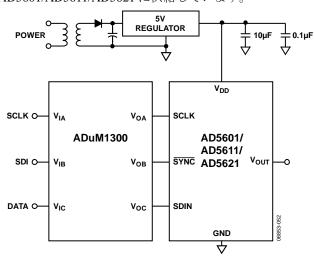

工業用環境のプロセス制御アプリケーションでは、電流 絶縁インターフェースを使って、DAC が動作している領域で発生する有害な同相電圧から制御回路を保護してアイソレーションすることが必要となることがあります。iCoupler®は 2.5 kV を超える絶縁を提供します。AD5601/AD5611/AD5621 は 3 線式シリアル・ロジック・インターフェースを使っているため、ADuM1300 の 3 チャンネル・デジタル・アイソレータにより必要な絶縁を提供することができます(図 52 参照)。デバイスの電源もトランスを使って絶縁する必要があります。トランスのDAC 側では、5 V のレギュレータが 5 V 電源をAD5601/AD5611/AD5621 に供給しています。

図 52.AD5601/AD5611/AD5621 の電流絶縁インターフェース での使用

#### 電源のバイパスとグラウンド接続

高精度が重要な回路では、ボード上の電源とグラウンド・リターンのレイアウトを注意深く行うことが役立ちます。AD5601/AD5611/AD5621を実装するPCBプリント回路ボードは、アナログ部とデジタル部を分離して、それぞれ専用のボード領域を持つようにする必要があります。複数のデバイスがAGNDとDGNDの接続を必要とするシステム内でAD5601/AD5611/AD5621を使用する場合は、この接続は1ヵ所で行う必要があります。グラウンド・ポイントはAD5601/AD5611/AD5621のできるだけ近くに配置する必要があります。

AD5601/AD5611/AD5621 の電源は、 $10 \, \mu F \, b \, 0.1 \, \mu F \, o \, n \, \nu$  デンサでバイパスする必要があります。コンデンサはデバイスのできるだけ近くに配置し、 $0.1 \mu F \, o \, n \, n \, \nu$  は理想的にはデバイスの近くに配置することが望まれます。 $10 \mu F \, n \, \nu$  デンサはタンタルのビーズ型を使います。 $0.1 \mu F \, n \, \nu$  デンサは、セラミック型コンデンサのような実効直列抵抗(ESR)が小さく、かつ実効直列インダクタンス(ESI)が小さいものを使う必要があります。この $0.1 \, \mu F \, o \, n \, \nu$  コンデンサは、内部ロジックのスイッチングにより発生する過渡電流に起因する高周波に対してグラウンドへの低インピーダンス・パスを提供します。

電源ラインはできるだけ太いパターンにしてインピーダンスを小さくし、電源ライン上のグリッチによる影響を軽減させるようにします。クロックとその他の高速スイッチング・デジタル信号は、デジタル・グラウンドを使ってボード上の他の部分からシールドする必要があります。デジタル信号とアナログ信号の交差は、できるだけ回避する必要があります。ボードの反対側のパターンは、互いに右角度となるように配置してボードを通過するフィードスルー効果を減少させます。最適なボード・レイアウト技術は、ボードの部品側をグラウンド・プレーン専用として使い、信号パターンはハンダ面に配置するマイクロストリップ技術ですが、2層ボードでは常に可能とは限りません。

Rev. **D** — 19/20 —

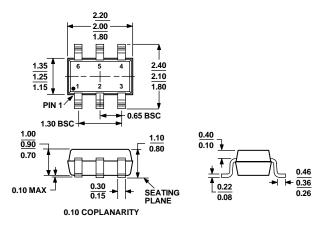

## 外形寸法

#### COMPLIANT TO JEDEC STANDARDS MO-203-AB

図 53.6 ピン薄型シュリンク・スモール・アウトライン・トランジスタ・パッケージ[SC70] (KS-6) 寸法: mm

### オーダー・ガイド

|                                | Temperature     |          |                                                            | Package |          |

|--------------------------------|-----------------|----------|------------------------------------------------------------|---------|----------|

| Model                          | Range           | INL      | Package Description                                        | Option  | Branding |

| AD5601BKSZ-500RL7 <sup>1</sup> | −40°C to +125°C | ±0.5 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3V      |

| AD5601BKSZ-REEL7 <sup>1</sup>  | −40°C to +125°C | ±0.5 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3V      |

| AD5611AKSZ-500RL7 <sup>1</sup> | −40°C to +125°C | ±4.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3U      |

| AD5611AKSZ-REEL7 <sup>1</sup>  | –40°C to +125°C | ±4.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3U      |

| AD5611BKSZ-500RL7 <sup>1</sup> | −40°C to +125°C | ±0.5 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3T      |

| AD5611BKSZ-REEL7 <sup>1</sup>  | −40°C to +125°C | ±0.5 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3T      |

| AD5621AKSZ-500RL7 <sup>1</sup> | -40°C to +125°C | ±6.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3S      |

| AD5621AKSZ-REEL71              | –40°C to +125°C | ±6.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3S      |

| AD5621BKSZ-500RL71             | –40°C to +125°C | ±1.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3R      |

| AD5621BKSZ-REEL71              | −40°C to +125°C | ±1.0 LSB | 6-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-6    | D3R      |

<sup>&</sup>lt;sup>1</sup>Z=RoHS 準拠製品。

Rev. **D** — 20/20 —