### 真のバイポーラ入力、デュアル、12/14 ビット 2 チャンネル、同時サンプリング SAR ADC

### AD7366/AD7367

#### 特長

デュアル 12/14 ビットの 2 チャンネル ADC 真のバイポーラ・アナログ入力 設定可能な入力範囲:

±10 V、±5 V、0 V~10 V ±12 V (3 V の外部リファレンス使用) スループット・レート: 1 MSPS 1 µs 以内での同時変換読み出し 高アナログ入力インピーダンス 低消費電流:

通常のモード: 8.3 mA (typ) シャットダウン・モード: 320 nA (typ) AD7366

50 kHz の入力周波数で 72 dB SNR 12 ビットのノーミス・コード AD7367

50 kHz の入力周波数で 76 dB SNR 14 ビットのノーミス・コード 正確な内蔵リファレンス: 2.5 V ± 0.2% 動作温度範囲: −40°C~+85°C 高速シリアル・インターフェースを内蔵 SPI®、QSPI™、MICROWIRE™、DSP と互換 *i*CMOS<sup>®</sup>プロセス技術 24 ピン TSSOP パッケージを採用

#### 概要

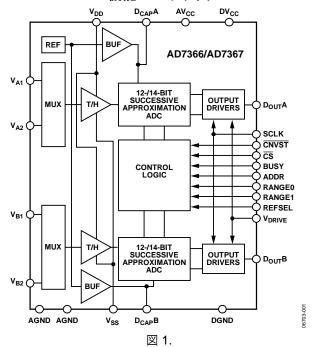

AD7366/AD7367<sup>1</sup>はデュアル 12/14 ビットの高速低消費 電力逐次比較型 A/D コンバータ(ADC)で、最大 1 MSPS のスループット・レートを持っています。デバイスは 2個のADCを内蔵しており、各々の前には2チャンネ ル・マルチプレクサと低ノイズ広帯域トラック・アン ド・ホールド・アンプが配置されています。

AD7366/AD7367 はアナログ・デバイセズの工業用 CMOS プロセス(iCMOS<sup>2</sup>)で製造されており、このプロ セスは低電圧 CMOS と高電圧 CMOS の利点を組み合わ せた技術プラットフォームを構成しています。iCMOS プロセスの採用により、AD7366/AD7367では高電圧バ イポーラ信号を許容すると同時に、消費電力とパッケ ージ・サイズの削減も可能になっています。

AD7366/AD7367 はバイポーラ・アナログ入力信号を ±10 V 範囲、±5 V 範囲、0 V~10 V 範囲で入力すること ができます。

AD7366/AD7367 は 2.5 V リファレンス電圧を内蔵して おり、外付けリファレンスを使うときにはこれをディ スエーブルすることができます。3 V のリファレンス 電圧を D<sub>CAP</sub>A ピンと D<sub>CAP</sub>B ピンに接続すると、 AD7366/AD7367 は真の±12 V バイポーラ・アナログ信 号を入力することができます。±12 V の入力範囲に対 して、最小 $\pm 12 \, V$  の  $V_{DD}$ 電源と  $V_{SS}$  電源が必要です。

#### 機能ブロック図

#### 製品のハイライト

- 1. AD7366/AD7367 には、真の±10 V、±5 V、±12 V バ イポーラ・アナログ信号(外付けリファレンス使用) と0V~10Vユニポーラ信号を入力することがで きます

- 2. 2個の完全な ADC 機能を内蔵しており、2 チャン ネルのサンプリングと変換を同時に実行すること ができます。

- 1 MSPS のシリアル・インターフェース (SPI/QSPI/DSP/MICROWIRE に互換)を内蔵していま す。

表 1.関連製品

| Device   | Resolution | Throughput<br>Rate | Number of<br>Channels |

|----------|------------|--------------------|-----------------------|

| AD7366   | 12-Bit     | 1 MSPS             | Dual, 2-channel       |

| AD7366-5 | 12-Bit     | 500 kSPS           | Dual, 2-channel       |

| AD7367   | 14-Bit     | 1 MSPS             | Dual, 2-channel       |

| AD7367-5 | 14-Bit     | 500 kSPS           | Dual, 2-channel       |

<sup>1</sup>米国特許 No. 6,731,232 により保護されています。

ナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、 利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有

©2007 Analog Devices, Inc. All rights reserved.

Rev. A

本

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

<sup>&</sup>lt;sup>2</sup> iCMOS プロセス技術。高い電圧レベルで高性能 IC を必要とす る工業用/計装装置 OEM のアナログ・システム設計者にとって、 iCMOS は耐圧 30 V で±15 V 電源で動作し、かつ消費電力とパッ ケージ・サイズを大幅に小さくし、AC性能と DC性能を強化したアナログ IC の開発を可能にする技術プラットフォームになり ます。

## 目次

| 特長            | 1  |

|---------------|----|

| 機能ブロック図       | 1  |

| 概要            | 1  |

| 製品のハイライト      | 1  |

| 改訂履歴          | 2  |

| 仕様            | 3  |

| タイミング仕様       | 7  |

| 絶対最大定格        | 8  |

| ESD の注意       | 8  |

| ピン配置およびピン機能説明 | 9  |

| 代表的な性能特性      | 11 |

| 用語            | 14 |

| 動作原理          | 16 |

| 回路説明          | 16 |

| コンバータの動作      | 16 |

| アナログ入力        | 16 |

| 伝達関数          | 17 |

| 代表的な接続図       | 18 |

| ドライバ・アンプの選択19                             |

|-------------------------------------------|

| リファレンス電圧19                                |

| 動作モード20                                   |

| ノーマル動作モード20                               |

| シャットダウン・モード21                             |

| パワーアップ時間21                                |

| シリアル・インターフェース22                           |

| マイクロプロセッサ・インターフェース24                      |

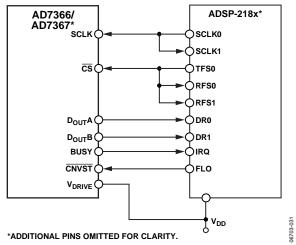

| AD7366/AD7367 と ADSP-218x とのインターフェース 24   |

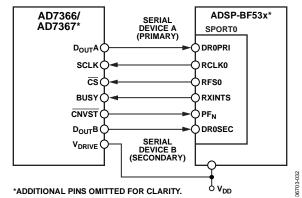

| AD7366/AD7367 と ADSP-BF53x とのインターフェース. 24 |

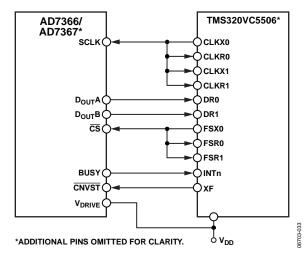

| AD7366/AD7367 と TMS320VC5506 とのインターフェー    |

| ス                                         |

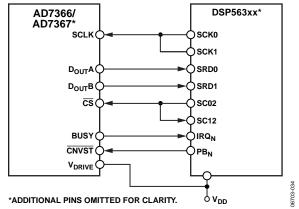

| AD7366/AD7367 と DSP563xx とのインターフェース 25    |

| アプリケーション情報27                              |

| レイアウトとグラウンド接続27                           |

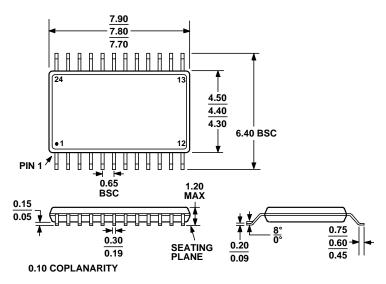

| 外形寸法28                                    |

| オーダー・ガイド28                                |

### 改訂履歴

#### 9/07—Rev. 0 to Rev. A

| Changes to Title               |    |

|--------------------------------|----|

| Changes to Specifications      |    |

| Changes to Figure 5            |    |

| Changes to Terminology Section |    |

| Changes to Figure 20           |    |

| Changes to Figure 28           |    |

| Updated Outline Dimensions     | 28 |

| Changes to Ordering Guide      | 28 |

|                                |    |

5/07—Revision 0: Initial Version

## 仕様

特に指定がない限り、AV $_{CC}$  = DV $_{CC}$  = 4.75 V  $\sim$  5.25 V、V $_{DD}$  = 11.5 V  $\sim$  16.5 V、V $_{SS}$  = -16.5 V  $\sim$  -11.5 V、V $_{DRIVE}$  = 2.7 V  $\sim$  5.25 V、 $_{SS}$  = 1.12 MSPS、 $_{SCLK}$  = 48 MHz、V $_{REF}$  = 2.5 V (内部/外部)、 $_{TA}$  =  $-40^{\circ}$ C  $\sim$  +85  $^{\circ}$ C  $_{\circ}$

#### 表 2.AD7366

| Parameter                                               | Min   | Тур   | Max     | Unit | Test Conditions/Comments                                                    |

|---------------------------------------------------------|-------|-------|---------|------|-----------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                     |       |       |         |      | f <sub>IN</sub> = 50 kHz sine wave                                          |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                | 70    | 72    |         | dB   |                                                                             |

| Signal-to-Noise + Distortion Ratio (SINAD) <sup>1</sup> | 70    | 71    |         | dB   |                                                                             |

| Total Harmonic Distortion (THD) <sup>1</sup>            |       | -85   | -78     | dB   |                                                                             |

| Spurious-Free Dynamic Range (SFDR)                      |       | -87   | -78     | dB   |                                                                             |

| Intermodulation Distortion (IMD) <sup>1</sup>           |       |       |         |      | fa = 49  kHz, fb = 51  kHz                                                  |

| Second-Order Terms                                      |       | -88   |         | dB   |                                                                             |

| Third-Order Terms                                       |       | -88   |         | dB   |                                                                             |

| Channel-to-Channel Isolation <sup>1</sup>               |       | -90   |         | dB   |                                                                             |

| SAMPLE AND HOLD                                         |       |       |         |      |                                                                             |

| Aperture Delay <sup>2</sup>                             |       |       | 10      | ns   |                                                                             |

| Aperture Jitter <sup>2</sup>                            |       | 40    |         | ps   |                                                                             |

| Aperture Delay Matching <sup>2</sup>                    |       | ±100  |         | ps   |                                                                             |

| Full Power Bandwidth                                    |       | 35    |         | MHz  | @ 3 dB, ±10 V range                                                         |

|                                                         |       | 8     |         | MHz  | @ 0.1 dB, ±10 V range                                                       |

| DC ACCURACY                                             |       |       |         |      |                                                                             |

| Resolution                                              | 12    |       |         | Bits |                                                                             |

| Integral Nonlinearity (INL) <sup>1</sup>                |       | ±0.5  | ±1      | LSB  |                                                                             |

| Differential Nonlinearity (DNL) <sup>1</sup>            |       | ±0.25 | ±0.5    | LSB  | Guaranteed no missed codes to 12 bits                                       |

| Positive Full-Scale Error <sup>1</sup>                  |       | ±1    | ±7      | LSB  | ±5 V and ±10 V analog input range                                           |

|                                                         |       | ±1    | ±6      | LSB  | 0 V to 10 V analog input range                                              |

| Positive Full-Scale Error Match <sup>1</sup>            |       | ±1.5  |         | LSB  | Matching from ADC A to ADC B                                                |

|                                                         |       | ±0.1  |         | LSB  | Channel-to-channel matching for ADC A and AD B                              |

| Zero Code Error <sup>1</sup>                            |       | ±0.5  | ±3      | LSB  | ±5 V and ±10 V analog input range                                           |

|                                                         |       | ±1    | ±6      | LSB  | 0 V to 10 V analog input range                                              |

| Zero Code Error Match <sup>1</sup>                      |       | ±1.5  |         | LSB  | Matching from ADC A to ADC B                                                |

|                                                         |       | ±0.1  |         | LSB  | Channel-to-channel matching for ADC A and ADC B                             |

| Negative Full-Scale Error <sup>1</sup>                  |       | ±1    | ±7      | LSB  | ±5 V and ±10 V analog input range                                           |

|                                                         |       | ±1    | ±6      | LSB  | 0 V to 10 V analog input range                                              |

| Negative Full-Scale Error Match <sup>1</sup>            |       | ±1.5  |         | LSB  | Matching from ADC A to ADC B                                                |

|                                                         |       | ±0.1  |         | LSB  | Channel-to-channel matching for ADC A and ADC B                             |

| ANALOG INPUT                                            |       |       |         |      |                                                                             |

| Input Voltage Ranges                                    |       |       |         |      | Programmed via RANGE pins; see Table 8                                      |

|                                                         |       |       | ±10     | V    |                                                                             |

|                                                         |       |       | ±5      | V    |                                                                             |

|                                                         |       |       | 0 to 10 | V    |                                                                             |

| DC Leakage Current                                      |       | ±0.01 | ±1      | μA   |                                                                             |

| Input Capacitance                                       |       | 9     |         | pF   | When in track, ±10 V range                                                  |

| •                                                       |       | 13    |         | pF   | When in track, ±5 V and 0 V to 10 V range                                   |

| Input Impedance                                         |       | 260   |         | kΩ   | ±10 V @ 1 MSPS                                                              |

| 1 1                                                     |       | 2.5   |         | МΩ   | ±10 V @ 100 kSPS                                                            |

|                                                         |       | 125   |         | kΩ   | ±5 V and 0 V to 10 V range @ 1 MSPS                                         |

|                                                         |       | 1.2   |         | ΜΩ   | ±5 V and 0 V to 10 V range @ 100 kSPS                                       |

| REFERENCE INPUT/OUTPUT                                  |       |       |         |      |                                                                             |

| Reference Output Voltage <sup>3</sup>                   | 2.495 | 2.5   | 2.505   | V    | ±0.2% max @ 25°C                                                            |

| Long-Term Stability                                     |       | 150   |         | ppm  | 1000 hours                                                                  |

| Output Voltage Hysteresis <sup>1</sup>                  |       | 50    |         | ppm  |                                                                             |

| Reference Input Voltage Range                           | 2.5   |       | 3.0     | V    |                                                                             |

| DC Leakage Current                                      |       | ±0.01 | ±1      | μA   | External reference applied to Pin D <sub>CAP</sub> A/Pin D <sub>CAP</sub> B |

|                                                         |       | 25    |         | pF   | ±5 V and ±10 V analog input range                                           |

| Input Canacitance                                       |       |       |         |      |                                                                             |

| Input Capacitance                                       |       | 17    |         | pF   | 0 V to 10 V analog input range                                              |

| Parameter                                               | Min                    | Тур        | Max   | Unit   | Test Conditions/Comments                                                                                 |

|---------------------------------------------------------|------------------------|------------|-------|--------|----------------------------------------------------------------------------------------------------------|

| REFERENCE INPUT/OUTPUT                                  |                        |            |       |        |                                                                                                          |

| Reference Output Voltage <sup>3</sup>                   | 2.495                  | 2.5        | 2.505 | V      | ±0.2% max @ 25°C                                                                                         |

| Long-Term Stability                                     |                        | 150        |       | ppm    | 1000 hours                                                                                               |

| Output Voltage Hysteresis <sup>1</sup>                  |                        | 50         |       | ppm    |                                                                                                          |

| Reference Input Voltage Range                           | 2.5                    |            | 3.0   | V      |                                                                                                          |

| DC Leakage Current                                      |                        | $\pm 0.01$ | ±1    | μΑ     | External reference applied to Pin D <sub>CAP</sub> A/Pin D <sub>CAP</sub> B                              |

| Input Capacitance                                       |                        | 25         |       | pF     | ±5 V and ±10 V analog input range                                                                        |

|                                                         |                        | 17         |       | pF     | 0 V to 10 V analog input range                                                                           |

| D <sub>CAP</sub> A, D <sub>CAP</sub> B Output Impedance |                        | 7          |       | Ω      |                                                                                                          |

| Reference Temperature Coefficient                       |                        | 6          | 25    | ppm/°C |                                                                                                          |

| V <sub>REF</sub> Noise                                  |                        | 20         |       | μV rms | Bandwidth = $3 \text{ kHz}$                                                                              |

| LOGIC INPUTS                                            |                        |            |       |        |                                                                                                          |

| Input High Voltage, V <sub>INH</sub>                    | $0.7 \times V_{DRIVE}$ |            |       | V      |                                                                                                          |

| Input Low Voltage, V <sub>INL</sub>                     |                        |            | 0.8   | V      |                                                                                                          |

| Input Current, I <sub>IN</sub>                          |                        | $\pm 0.01$ | ±1    | μΑ     | $V_{IN} = 0 \text{ V or } V_{DRIVE}$                                                                     |

| Input Capacitance, C <sub>IN</sub> <sup>2</sup>         |                        | 6          |       | pF     |                                                                                                          |

| LOGIC OUTPUTS                                           |                        |            |       |        |                                                                                                          |

| Output High Voltage, V <sub>OH</sub>                    | $V_{DRIVE} - 0.2$      |            |       | V      |                                                                                                          |

| Output Low Voltage, Vol                                 |                        |            | 0.4   | V      |                                                                                                          |

| Floating State Leakage Current                          |                        | $\pm 0.01$ | ±1    | μΑ     |                                                                                                          |

| Floating State Output Capacitance <sup>2</sup>          |                        | 8          |       | pF     |                                                                                                          |

| CONVERSION RATE                                         |                        |            |       |        |                                                                                                          |

| Conversion Time                                         |                        |            | 610   | ns     |                                                                                                          |

| Track/Hold Acquisition Time <sup>2</sup>                |                        |            | 140   | ns     | Full-scale step input                                                                                    |

| Throughput Rate                                         |                        |            | 1.12  | MSPS   | $4.75 \text{ V} \le V_{DRIVE} \le 5.25 \text{ V}, f_{SCLK} = 48 \text{ MHz}$                             |

|                                                         |                        | 1          |       | MSPS   | $2.7 \text{ V} \le V_{DRIVE} < 4.75 \text{ V}, f_{SCLK} = 35 \text{ MHz}$                                |

| POWER REQUIREMENTS                                      |                        |            |       |        | Digital inputs = 0 V or V <sub>DRIVE</sub>                                                               |

| $V_{cc}$                                                | 4.75                   |            | 5.25  | V      | See Table 7                                                                                              |

| $V_{ m DD}$                                             | +11.5                  |            | +16.5 | V      | See Table 7                                                                                              |

| $V_{ss}$                                                | -16.5                  |            | -11.5 | V      | See Table 7                                                                                              |

| $V_{ m DRIVE}$                                          | 2.7                    |            | 5.25  | V      |                                                                                                          |

| Normal Mode (Static)                                    |                        |            |       |        |                                                                                                          |

| $I_{DD}$                                                |                        | 370        | 550   | μA     | $V_{DD} = +16.5 \text{ V}$                                                                               |

| I <sub>SS</sub>                                         |                        | 40         | 60    | μA     | $V_{SS} = -16.5 \text{ V}$                                                                               |

| I <sub>CC</sub>                                         |                        | 1.5        | 2.25  | mA     | $V_{CC} = 5.5 \text{ V}$                                                                                 |

| Normal Mode (Operational)                               |                        | 1.0        | 2.20  |        | $f_S = 1.12 \text{ MSPS}$                                                                                |

| I <sub>DD</sub>                                         |                        | 1.8        | 2.0   | mA     | $V_{DD} = +16.5 \text{ V}$                                                                               |

| I <sub>SS</sub>                                         |                        | 1.5        | 1.6   | mA     | $V_{SS} = -16.5 \text{ V}$                                                                               |

| $I_{CC}$                                                |                        | 5          | 5.65  | mA     | $V_{CC} = 5.25 \text{ V}$ , internal reference enabled                                                   |

| Shutdown Mode                                           |                        |            | 0.00  |        | , ce 5.25 v, internal reference character                                                                |

| I <sub>DD</sub>                                         |                        | 0.01       | 1     | μA     | $V_{DD} = +16.5 \text{ V}$                                                                               |

| $I_{SS}$                                                |                        | 0.01       | 1     | μΑ     | $V_{SS} = -16.5 \text{ V}$                                                                               |

| $I_{CC}$                                                |                        | 0.3        | 3     | μΑ     | $V_{SS} = 10.3 \text{ V}$ $V_{CC} = 5.25 \text{ V}$                                                      |

| Power Dissipation                                       |                        | 0.5        | J     | μΑ     | V(C = 3.23 V                                                                                             |

| Normal Mode (Operational)                               |                        |            | 89.1  | mW     | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = 5.25 \text{ V}, f_S =$                     |

| 1401mai wode (Operational)                              |                        |            | 07.1  | 111 44 | $v_{DD} = +10.5 \text{ v}, v_{SS} = -10.5 \text{ v}, v_{CC} = 3.25 \text{ v}, t_{S} = 1.12 \text{ MSPS}$ |

|                                                         |                        | 50         |       | mW     | $\pm 10 \text{ V}$ input range, $f_S = 1.12 \text{ MSPS}$                                                |

|                                                         |                        | 70         |       | mW     | $\pm 5$ V and 0 V to 10 V input range, $f_S = 1.12$ MSPS                                                 |

| Shutdown Mode                                           |                        | 1.9        | 48.75 | μW     | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = 5.25 \text{ V}$                            |

Rev. A - 4/28 -

$<sup>^1</sup>$ 用語のセクションを参照してください。  $^2$  初期リリース時はサンプル・テストにより適合性を保証。  $^3$  25  $\mathbb{C}$  で規定された  $\mathbf{D}_{\mathsf{CAP}}\mathbf{A}$  ピンまたは  $\mathbf{D}_{\mathsf{CAP}}\mathbf{B}$  ピン。

特に指定がない限り、AV $_{CC}$  = DV $_{CC}$  = 4.75 V  $\sim$  5.25 V、V $_{DD}$  = 11.5 V  $\sim$  16.5 V、V $_{SS}$  = -16.5 V  $\sim$  -11.5 V、V $_{DRIVE}$  = 2.7 V  $\sim$  5.25 V、 $_{SS}$  = 1 MSPS、 $_{SCLK}$  = 48 MHz、V $_{REF}$  = 2.5 V (内部/外部)、 $_{TA}$  = -40°C  $\sim$  +85°C。

#### 表 3.AD7367

| Parameter                                               | Min   | Тур        | Max     | Unit | Test Conditions/Comments                        |

|---------------------------------------------------------|-------|------------|---------|------|-------------------------------------------------|

| DYNAMIC PERFORMANCE                                     |       |            |         |      | $f_{IN} = 50 \text{ kHz sine wave}$             |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                | 74    | 76         |         | dB   |                                                 |

| Signal-to-Noise + Distortion Ratio (SINAD) <sup>1</sup> | 73    | 75         |         | dB   |                                                 |

| Total Harmonic Distortion (THD) <sup>1</sup>            |       | -84        | -78     | dB   |                                                 |

| Spurious-Free Dynamic Range (SFDR)                      |       | -87        | -79     | dB   |                                                 |

| Intermodulation Distortion (IMD) <sup>1</sup>           |       |            |         |      | fa = 49  kHz, fb = 51  kHz                      |

| Second-Order Terms                                      |       | -91        |         | dB   |                                                 |

| Third-Order Terms                                       |       | -89        |         | dB   |                                                 |

| Channel-to-Channel Isolation <sup>1</sup>               |       | -90        |         | dB   |                                                 |

| SAMPLE AND HOLD                                         |       |            |         |      |                                                 |

| Aperture Delay <sup>2</sup>                             |       |            | 10      | ns   |                                                 |

| Aperture Jitter <sup>2</sup>                            |       | 40         |         | ps   |                                                 |

| Aperture Delay Matching <sup>2</sup>                    |       | ±100       |         | ps   |                                                 |

| Full Power Bandwidth                                    |       | 35         |         | MHz  | @ 3 dB, ±10 V range                             |

|                                                         |       | 8          |         | MHz  | @ 0.1 dB, ±10 V range                           |

| DC ACCURACY                                             |       |            |         |      | , ,                                             |

| Resolution                                              | 14    |            |         | Bits |                                                 |

| Integral Nonlinearity (INL) <sup>1</sup>                |       | ±2         | ±3.5    | LSB  |                                                 |

| Differential Nonlinearity (DNL) <sup>1</sup>            |       | ±0.5       | ±0.90   | LSB  | Guaranteed no missed codes to 14 bits           |

| Positive Full-Scale Error <sup>1</sup>                  |       | ±4         | ±20     | LSB  | ±5 V and ±10 V analog input range               |

| Toshive Full Beale Effor                                |       | ±5         | ±20     | LSB  | 0 V to 10 V analog input range                  |

| Positive Full-Scale Error Match <sup>1</sup>            |       | ±3         | ±20     | LSB  | Matching from ADC A to ADC B                    |

| 1 OSHIVE Pull-Scale Effor Watch                         |       | ±0.2       |         | LSB  | Channel-to-channel matching for ADC A and ADC B |

| Zero Code Error <sup>1</sup>                            |       | ±0.2<br>±1 | ±10     | LSB  | ±5 V and ±10 V analog input range               |

| Zelo Code Elloi                                         |       | ±1<br>±5   | ±20     | LSB  | 0 V to 10 V analog input range                  |

| Zero Code Error Match <sup>1</sup>                      |       |            | ±20     | LSB  | Matching from ADC A to ADC B                    |

| Zero Code Error Match                                   |       | ±3         |         | LSB  |                                                 |

| Namedian Entl Conta English                             |       | ±0.2       | . 20    | LSB  | Channel-to-channel matching for ADC A and ADC B |

| Negative Full-Scale Error <sup>1</sup>                  |       | ±4         | ±20     |      | ±5 V and ±10 V analog input range               |

| N C FUG LE MAIL                                         |       | ±5         | ±20     | LSB  | 0 V to 10 V analog input range                  |

| Negative Full-Scale Error Match <sup>1</sup>            |       | ±3         |         | LSB  | Matching from ADC A to ADC B                    |

| ANALY OR DANKE                                          |       | ±0.2       |         | LSB  | Channel-to-channel matching for ADC A and ADC B |

| ANALOG INPUT                                            |       |            |         |      |                                                 |

| Input Voltage Ranges                                    |       |            |         |      | Programmed via RANGE pins; see Table 8          |

|                                                         |       |            | ±10     | V    |                                                 |

|                                                         |       |            | ±5      | V    |                                                 |

|                                                         |       |            | 0 to 10 | V    |                                                 |

| DC Leakage Current                                      |       | $\pm 0.01$ | ±1      | μΑ   |                                                 |

| Input Capacitance                                       |       | 9          |         | pF   | When in track, ±10 V range                      |

|                                                         |       | 13         |         | pF   | When in track, ±5 V and 0 V to 10 V range       |

| Input Impedance                                         |       | 260        |         | kΩ   | ±10 V @ 1 MSPS                                  |

|                                                         |       | 2.5        |         | ΜΩ   | ±10 V @ 100 kSPS                                |

|                                                         |       | 125        |         | kΩ   | ±5 V and 0 V to 10 V range @ 1 MSPS             |

|                                                         |       | 1.2        |         | ΜΩ   | ±5 V and 0 V to 10 V range @ 100 kSPS           |

| REFERENCE INPUT/OUTPUT                                  |       |            |         |      |                                                 |

| Reference Output Voltage <sup>3</sup>                   | 2.495 | 2.5        | 2.505   | V    | ±0.2% max @ 25°C                                |

| Long-Term Stability                                     |       | 150        |         | ppm  | 1000 hours                                      |

| Output Voltage Hysteresis <sup>1</sup>                  |       | 50         |         | ppm  |                                                 |

| Reference Input Voltage Range                           | 2.5   |            | 3.0     | V    |                                                 |

Rev. A - 5/28 -

| Parameter                                               | Min                    | Тур   | Max   | Unit   | Test Conditions/Comments                                                      |

|---------------------------------------------------------|------------------------|-------|-------|--------|-------------------------------------------------------------------------------|

| DC Leakage Current                                      |                        | ±0.01 | ±1    | μA     | External reference applied to Pin D <sub>CAP</sub> A/Pin D <sub>CAP</sub> B   |

| Input Capacitance                                       |                        | 25    |       | pF     | ±5 V and ±10 V analog input range                                             |

|                                                         |                        | 17    |       | pF     | 0 V to 10 V analog input range                                                |

| D <sub>CAP</sub> A, D <sub>CAP</sub> B Output Impedance |                        | 7     |       | Ω      |                                                                               |

| Reference Temperature Coefficient                       |                        | 6     | 25    | ppm/°C |                                                                               |

| V <sub>REF</sub> Noise                                  |                        | 20    |       | μV rms | Bandwidth = 3 kHz                                                             |

| LOGIC INPUTS                                            |                        |       |       |        |                                                                               |

| Input High Voltage, V <sub>INH</sub>                    | $0.7 \times V_{DRIVE}$ |       |       | V      |                                                                               |

| Input Low Voltage, V <sub>INL</sub>                     |                        |       | 0.8   | V      |                                                                               |

| Input Current, I <sub>IN</sub>                          |                        | ±0.01 | ±1    | μΑ     | $V_{IN} = 0 \text{ V or } V_{DRIVE}$                                          |

| Input Capacitance, C <sub>IN</sub> <sup>2</sup>         |                        | 6     |       | pF     |                                                                               |

| LOGIC OUTPUTS                                           |                        |       |       |        |                                                                               |

| Output High Voltage, VoH                                | $V_{DRIVE} - 0.2$      |       |       | V      |                                                                               |

| Output Low Voltage, V <sub>OL</sub>                     |                        |       | 0.4   | V      |                                                                               |

| Floating State Leakage Current                          |                        | ±0.01 | ±1    | μΑ     |                                                                               |

| Floating State Output Capacitance <sup>2</sup>          |                        | 8     |       | pF     |                                                                               |

| CONVERSION RATE                                         |                        |       |       |        |                                                                               |

| Conversion Time                                         |                        |       | 680   | ns     |                                                                               |

| Track/Hold Acquisition Time <sup>2</sup>                |                        |       | 140   | ns     | Full-scale step input                                                         |

| Throughput Rate                                         |                        |       | 1     | MSPS   | $4.75 \text{ V} \le V_{DRIVE} \le 5.25 \text{ V}, f_{SCLK} = 48 \text{ MHz}$  |

|                                                         |                        | 900   |       | kSPS   | $2.7 \text{ V} \le V_{DRIVE} < 4.75 \text{ V}, f_{SCLK} = 35 \text{ MHz}$     |

| POWER REQUIREMENTS                                      |                        |       |       |        | Digital inputs = $0 \text{ V or V}_{DRIVE}$                                   |

| $ m V_{CC}$                                             | 4.75                   |       | 5.25  | V      | See Table 7                                                                   |

| $V_{DD}$                                                | +11.5                  |       | +16.5 | V      | See Table 7                                                                   |

| $V_{SS}$                                                | -16.5                  |       | -11.5 | V      | See Table 7                                                                   |

| $V_{ m DRIVE}$                                          | 2.7                    |       | 5.25  | V      |                                                                               |

| Normal Mode (Static)                                    |                        |       |       |        |                                                                               |

| ${ m I}_{ m DD}$                                        |                        | 370   | 550   | μΑ     | $V_{DD} = +16.5 \text{ V}$                                                    |

| $I_{SS}$                                                |                        | 40    | 60    | μA     | $V_{SS} = -16.5 \text{ V}$                                                    |

| $I_{CC}$                                                |                        | 1.5   | 2.25  | mA     | $V_{CC} = 5.5 \text{ V}$                                                      |

| Normal Mode (Operational)                               |                        |       |       |        | $f_S = 1 \text{ MSPS}$                                                        |

| $ m I_{DD}$                                             |                        | 1.8   | 2.0   | mA     | $V_{DD} = +16.5 \text{ V}$                                                    |

| $I_{SS}$                                                |                        | 1.5   | 1.6   | mA     | $V_{SS} = -16.5 \text{ V}$                                                    |

| $I_{CC}$                                                |                        | 5     | 5.65  | mA     | $V_{CC} = 5.25$ V, internal reference enabled                                 |

| Shutdown Mode                                           |                        |       |       |        | ,                                                                             |

| ${ m I}_{ m DD}$                                        |                        | 0.01  | 1     | μΑ     | $V_{DD} = +16.5 \text{ V}$                                                    |

| I <sub>SS</sub>                                         |                        | 0.01  | 1     | μΑ     | $V_{SS} = -16.5 \text{ V}$                                                    |

| $I_{CC}$                                                |                        | 0.3   | 3     | μΑ     | $V_{CC} = 5.25 \text{ V}$                                                     |

| Power Dissipation                                       |                        |       |       | '      |                                                                               |

| Normal Mode (Operational)                               |                        | 80.7  | 89.1  | mW     | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = 5.25 \text{ V}$ |

| · · · · · · · · · · · · · · · · · · ·                   |                        | 50    |       | mW     | $\pm 10 \text{ V input range, } f_S = 1 \text{ MSPS}$                         |

|                                                         |                        | 70    |       | mW     | $\pm 5$ V and 0 V to 10 V input range, $f_S = 1$ MSPS                         |

| Shutdown Mode                                           |                        | 1.9   | 48.75 | μW     | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}, V_{CC} = 5.25 \text{ V}$ |

<sup>&</sup>lt;sup>1</sup> 用語のセクションを参照してください。 <sup>2</sup> 初期リリース時はサンプル・テストにより適合性を保証。

$<sup>^3</sup>$  25℃で規定された  $D_{CAP}A$  ピンまたは  $D_{CAP}B$  ピン。

#### タイミング仕様

特に指定がない限り、AV $_{CC}$  = DV $_{CC}$  = 4.75 V $\sim$ 5.25 V、V $_{DD}$  = 11.5 V $\sim$ 16.5 V、V $_{SS}$  = -16.5 V $\sim$ -11.5 V、V $_{DRIVE}$  = 2.7 V $\sim$ 5.25 V、T $_{A}$  = -40°C $\sim$ +85°C  $_{\circ}^{1}$ 。

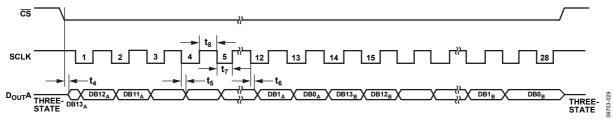

表 4.

|                       | Limit at $T_{MIN}$ , $T_{MAX}$                                      |                                                     |         |                                                                                                  |

|-----------------------|---------------------------------------------------------------------|-----------------------------------------------------|---------|--------------------------------------------------------------------------------------------------|

| Parameter             | $2.7~\mathrm{V} \leq \mathrm{V}_{\mathrm{DRIVE}} < 4.75~\mathrm{V}$ | $4.75 \text{ V} \leq V_{DRIVE} \leq 5.25 \text{ V}$ | Unit    | Test Conditions/Comments                                                                         |

| t <sub>CONVERT</sub>  |                                                                     |                                                     |         | Conversion time, internal clock; CNVST falling edge to BUSY                                      |

|                       |                                                                     |                                                     |         | falling edge                                                                                     |

|                       | 680                                                                 | 680                                                 | ns max  | AD7367                                                                                           |

|                       | 610                                                                 | 610                                                 | ns max  | AD7366                                                                                           |

| $f_{SCLK}$            | 10                                                                  | 10                                                  | kHz min | Frequency of serial read clock                                                                   |

|                       | 35                                                                  | 48                                                  | MHz max |                                                                                                  |

| $t_{QUIET}$           | 30                                                                  | 30                                                  | ns min  | Minimum quiet time required between the end of serial read and the start of the next conversion  |

| $t_1$                 | 10                                                                  | 10                                                  | ns min  | Minimum CNVST low pulse                                                                          |

| $t_2$                 | 40                                                                  | 40                                                  | ns min  | CNVST falling edge to BUSY rising edge                                                           |

| $t_3$                 | 0                                                                   | 0                                                   | ns min  | BUSY falling edge to MSB, valid when $\overline{\text{CS}}$ is low for t <sub>4</sub> prior to   |

|                       |                                                                     |                                                     |         | BUSY going low                                                                                   |

| $t_4$                 | 10                                                                  | 10                                                  | ns max  | Delay from CS falling edge until Pin 1 (D <sub>OUT</sub> A) and Pin 23                           |

|                       |                                                                     |                                                     |         | (D <sub>OUT</sub> B) are three-state disabled                                                    |

| $t_5^2$               | 20                                                                  | 14                                                  | ns max  | Data access time after SCLK falling edge                                                         |

| $t_6$                 | 7                                                                   | 7                                                   | ns min  | SCLK to data valid hold time                                                                     |

| $\mathbf{t}_7$        | $0.3 \times t_{SCLK}$                                               | $0.3 \times t_{SCLK}$                               | ns min  | SCLK low pulse width                                                                             |

| $t_8$                 | $0.3 \times t_{SCLK}$                                               | $0.3 \times t_{SCLK}$                               | ns min  | SCLK high pulse width                                                                            |

| $t_9$                 | 10                                                                  | 10                                                  | ns max  | CS rising edge to D <sub>OUT</sub> A, D <sub>OUT</sub> B, high impedance                         |

| t <sub>POWER-UP</sub> | 70                                                                  | 70                                                  | μs max  | Power-up time from shutdown mode; time required between CNVST rising edge and CNVST falling edge |

<sup>&</sup>lt;sup>1</sup> 初期リリース時はサンプル・テストにより適合性を保証。 すべての入力信号は  $t_R = t_F = 5$  ns  $(V_{DRIVE} \, \sigma \, 10\%$  から 90%)で規定し、1.6V の電圧レベルから の時間とします。 すべてのタイミング仕様は 25 pF の負荷容量を使用して規定。25 pF より大きい負荷容量では、デジタル・バッファまたはラッチを 使う必要があります。用語のセクション、図 25、図 26 を参照してください。

$<sup>^2</sup>$  出力が  $0.4\,\mathrm{V}$  または  $2.4\,\mathrm{V}$  を横切るために要する時間。

### 絶対最大定格

表 5.

| - 衣 3.                                                |                                                     |

|-------------------------------------------------------|-----------------------------------------------------|

| Parameter                                             | Rating                                              |

| V <sub>DD</sub> to AGND, DGND                         | -0.3 V to +16.5 V                                   |

| V <sub>SS</sub> to AGND, DGND                         | -16.5 V to +0.3 V                                   |

| V <sub>DRIVE</sub> to DGND                            | −0.3 V to DV <sub>CC</sub>                          |

| $V_{DD}$ to $AV_{CC}$                                 | $(V_{CC} - 0.3 \text{ V})$ to +16.5 V               |

| AV <sub>CC</sub> to AGND, DGND                        | -0.3 V to +7 V                                      |

| DV <sub>CC</sub> to AV <sub>CC</sub>                  | -0.3 V to +0.3 V                                    |

| DV <sub>CC</sub> to DGND                              | -0.3 V to +7 V                                      |

| $V_{DRIVE}$ to AGND                                   | −0.3 V to DV <sub>CC</sub>                          |

| AGND to DGND                                          | -0.3 V to +0.3 V                                    |

| Analog Input Voltage to AGND                          | $V_{SS} = 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |

| Digital Input Voltage to DGND                         | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$       |

| Digital Output Voltage to GND                         | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$       |

| D <sub>CAP</sub> A, D <sub>CAP</sub> B Input to AGND  | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$         |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                              |

| Operating Temperature Range                           | −40°C to +85°C                                      |

| Storage Temperature Range                             | −65°C to +150°C                                     |

| Junction Temperature                                  | 150°C                                               |

| TSSOP Package                                         |                                                     |

| $\theta_{JA}$ Thermal Impedance                       | 128°C/W                                             |

| $\theta_{JC}$ Thermal Impedance                       | 42°C/W                                              |

| Pb-Free Temperature, Soldering Reflow                 | 260°C                                               |

| ESD                                                   | 1.5 kV                                              |

$<sup>^{1}</sup>$ 最大  $100~\mathrm{mA}$  までの過渡電流ではラッチ・アップは生じません。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. A - 8/28 -

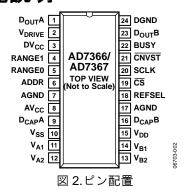

## ピン配置およびピン機能説明

表 6.ピン機能の説明

| 表 6.ヒ    | <u>こと機能の説明</u>                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ピン<br>番号 | 記号                                     | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1, 23    | D <sub>OUT</sub> A, D <sub>OUT</sub> B | シリアル・データ出力。データが各ピンにシリアル・データ・ストリームとして出力されます。ビットは SCLK 入力の立ち下がりエッジで出力され、データのアクセスには、AD7366 では 12 SCLK サイクルを、AD7367 では 14 SCLK サイクルを、それぞれ要します。両 ADC の同時変換結果が両ピンに同時に出力されます。データ・ストリームは、AD7366 では 12 ビットの変換データで、AD7367 では 14 ビットの変換データで、それぞれ構成され、MSB ファーストで出力されます。 $D_{OUT}A$ ピンまたは $D_{OUT}B$ ピンについて、AD7366 ではさらに 12 SCLK サイクル間、または AD7367 ではさらに 14 SCLK サイクル間、それぞれ $\overline{CS}$ をロー・レベルに保持すると、他の ADC からのデータがその $D_{OUT}$ ピンに出力されます。この機能を使うと、両 ADC の同時変換のデータをシリアル・フォーマットで $D_{OUT}A$ または $D_{OUT}B$ に集めて、1 つのシリアル・ポートのみを使うようにすることができます。詳細については、シリアル・インターフェースのセクションを参照してください。 |

| 2        | V <sub>DRIVE</sub>                     | ロジック電源入力。このピンに入力された電圧が、インターフェースで使用する電圧を決定します。このピンは DGND にデカップリングする必要があります。このピンの電圧範囲は $2.7~V$ ~5.25 $V$ であり、 $AV_{CC}$ と $DV_{CC}$ の電圧と異なることができますが、 $0.3~V$ 以上超えることはできません。 $AD7366$ で $1.12~MSPS$ のスループット・レートまたは $AD7367$ で $1~MSPS$ のスループット・レートを実現するためには、 $V_{DRIVE} \ge 4.75~V$ である必要があります。                                                                                                                                                                                                                                                                              |

| 3        | DV <sub>CC</sub>                       | デジタル電源電圧( $4.75V\sim5.25V$ )。 $DV_{CC}$ と $AV_{CC}$ の電圧は理想的には同電位である必要があります。 最適性能を得るためには $DV_{CC}$ ピンと $AV_{CC}$ ピンを接続して、両ピン間の電位差が過渡電圧であっても $0.3V$ 以上超えないようにする必要があります。この電源は $DGND$ にデカップリングする必要があります。 $DV_{CC}$ ピンに $10\mu F$ と $100n F$ のデカップリング・コンデンサを接続してください。                                                                                                                                                                                                                                                                                                          |

| 4, 5     | RANGE1,<br>RANGE0                      | アナログ入力範囲の選択のロジック入力。これらのピンの極性により、アナログ入力チャンネルの入力範囲が指定されます。アナログ入力のセクションと表8を参照してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6        | ADDR                                   | マルチプレクサ選択のロジック入力。この入力を使って、同時に変換するチャンネル対(ADCAと ADCBのチャンネル 1、または ADCAと ADCBのチャンネル 2)を選択します。このピンのロジック状態を BUSY の立ち上がりエッジでラッチして、次の変換に対してマルチプレクサを設定します。                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7, 17    | AGND                                   | アナログ・グラウンド。AD7366/AD7367上の全回路に対するグラウンド・リファレンス・ポイント。全アナログ入力信号と外付けリファレンス信号はこの AGND 電圧を基準とします。両AGNDピンはシステムの AGNDプレーンに接続する必要があります。AGND電圧と DGND電圧は理想的には同電位である必要があり、過渡的であっても差が 0.3 V を超えないようにする必要があります。                                                                                                                                                                                                                                                                                                                                                                         |

| 8        | $AV_{CC}$                              | 4.75 V~5.25 V のアナログ電源電圧。これは ADC コアの電源電圧です。 $AV_{cc}$ と $DV_{cc}$ の電圧は 理想的には同電位である必要があります。最適性能を得るためには $DV_{cc}$ ピンと $AV_{cc}$ ピンを接                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Rev. A - 9/28 -

|        | 記号                                     |                                                                                                                                                                                                                                                                       |

|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号     | BC 4                                   | ריים ביינים אינים אי<br>אינים ביינים אינים א                                      |

|        |                                        | 続して、両ピン間の電位差が過渡電圧であっても $0.3\mathrm{V}$ 以上超えないようにする必要があります。この電源は $\mathrm{AGND}$ にデカップリングする必要があります。 $\mathrm{AV}_\mathrm{CC}$ ピンに $\mathrm{10}\mathrm{\mu F}$ と $\mathrm{100}\mathrm{nF}$ の デカップリング・コンデンサを接続してください。                                                    |

| 9, 16  | D <sub>CAP</sub> A, D <sub>CAP</sub> B | デカップリング・コンデンサ・ピン。各 ADC のリファレンス・バッファをデカップリングするため、これらのピンにデカップリング・コンデンサを接続します。最適性能を得るためには、680 nF のデカップリング・コンデンサをこれらのピンに接続することが推奨されます。出力にバッファが付いている場合、内蔵リファレンス電圧をこれらのピンから出力して、システムの他の部分に供給することができます。                                                                      |

| 10     | V <sub>SS</sub>                        | 負電源電圧。このピンは、AD7366/AD7367 の高電圧アナログ入力構造に対する負電源電圧です。全アナログ入力範囲に対して- $11.5$ V の最大電圧より低い必要があります。詳細については、表 $7$ を参照。 $V_{SS}$ ピンに $10$ $\mu F$ と $100$ $nF$ のデカップリング・コンデンサを接続してください。                                                                                         |

| 11, 12 | $V_{A1}, V_{A2}$                       | ADCAのアナログ入力。両アナログ入力はシングルエンドです。これらのチャンネルのアナログ入力範囲は、RANGE0ピンとRANGE1ピンで指定されます。                                                                                                                                                                                           |

| 13, 14 | $V_{B2}, V_{B1}$                       | ADCBのアナログ入力。両アナログ入力はシングルエンドです。これらのチャンネルのアナログ入力範囲は、RANGE0ピンとRANGE1ピンで指定されます。                                                                                                                                                                                           |

| 15     | V <sub>DD</sub>                        | 正側電源電圧。このピンは、AD7366/AD7367 の高電圧アナログ入力構造に対する正電源電圧です。全アナログ入力範囲に対して $11.5\mathrm{V}$ の最小電圧より高い必要があります。詳細については、表 $7\mathrm{e}$ を参照してください。 $\mathrm{V}_{\mathrm{DD}}$ ピンに $10\mathrm{\mu}\mathrm{F}$ と $100\mathrm{n}\mathrm{F}$ のデカップリング・コンデンサを接続してください。                  |

| 18     | REFSEL                                 | 内部/外部リファレンス電圧選択のロジック入力。このピンをロジック・ハイに接続すると、オンチップ $2.5~V$ リファレンスが ADC A と ADC B のリファレンス・ソースとして使われます。 さらに、 $D_{CAP}A$ ピンと $D_{CAP}B$ ピンにデカップリング・コンデンサを接続する必要があります。 REFSEL ピンが GND に接続されると、外付けリファレンスを $D_{CAP}A$ ピン、 $D_{CAP}B$ ピンまたは両ピンを使って AD7366/ AD7367 に入力することができます。 |

| 19     | CS                                     | チップ・セレクト、アクティブ・ロー入力。このピンにより、シリアル・データ転送のフレーミングが行われます。 $\overline{\text{CS}}$ をロジック・ローにすると、出力バスがイネーブルされて、 $D_{\text{OUT}}A$ と $D_{\text{OUT}}B$ に変換結果が出力されます。                                                                                                           |

| 20     | SCLK                                   | シリアル・クロック、ロジック入力。シリアル・クロック入力は、AD7366/AD7367 からデータ<br>をアクセスする際に SCLK として使います。                                                                                                                                                                                          |

| 21     | CNVST                                  | 変換開始のロジック入力。このピンはエッジ検出です。この入力の立ち下がりエッジで、トラック・アンド・ホールドがホールド・モードになり、変換が開始されます。CNVSTが変換の完了時にロー・レベルになると、デバイスはパワーダウン・モードになります。この場合、CNVSTの立ち上がりエッジで、デバイスが再度パワーアップします。                                                                                                       |

| 22     | BUSY                                   | ビジー出力。変換が開始されると、BUSY はハイ・レベルになり、変換が完了するまでハイ・レベルを維持します。                                                                                                                                                                                                                |

| 24     | DGND                                   | デジタル・グラウンド。AD7366/AD7367上の全回路に対するアナログ・リファレンス・ポイント。DGNDピンはシステムのDGNDプレーンへ接続する必要があります。DGND電圧とAGND電圧は理想的には同電位である必要があり、過渡的であっても差が0.3 Vを超えないようにする必要があります。                                                                                                                   |

Rev. A - 10/28 -

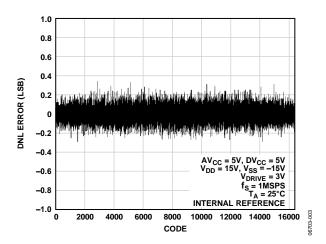

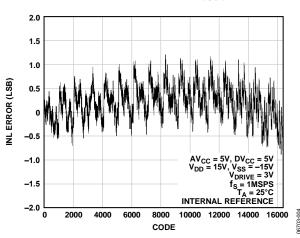

### 代表的な性能特性

特に指定のない限り、 $T_A = 25$ °C。

図 3.AD7367 の DNL (typ)

図 4.AD7367 の INL (typ)

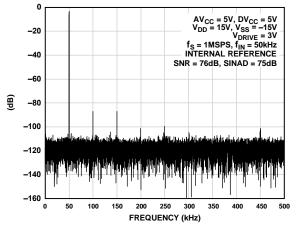

図 5.AD7367 の FFT

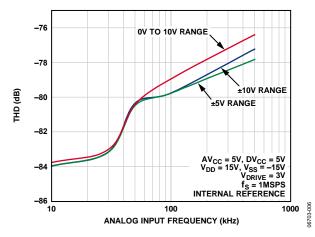

図 6.THD 対アナログ入力周波数

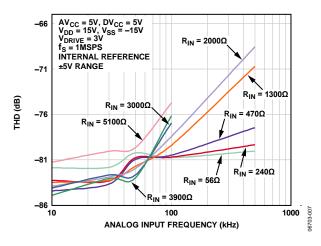

図 7.THD 対種々のソース・インピーダンスに対する アナログ入力周波数

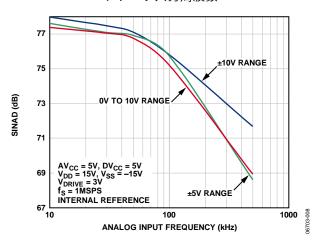

図 8.SINAD 対アナログ入力周波数

Rev. A - 11/28 -

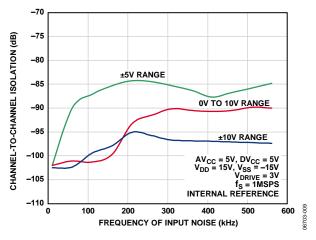

図 9.チャンネル間アイソレーション

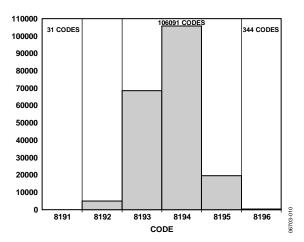

図 10. 200,000 個のサンプルに対する コードのヒストグラム

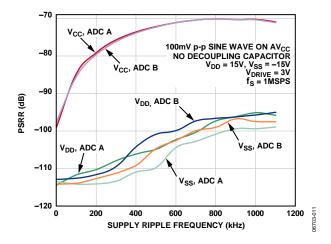

図 11.PSRR 対電源リップル周波数 電源デカップリングなし

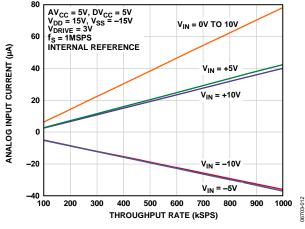

図 12.アナログ入力電流対スループット・レート

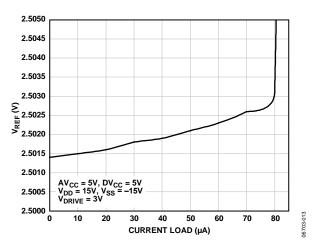

図 13.V<sub>REF</sub>対リファレンス電圧出力電流駆動

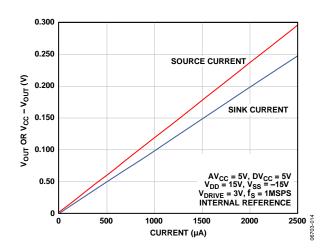

図 14.D<sub>OUT</sub> ソース電流対(V<sub>CC</sub> - V<sub>OUT</sub>) および D<sub>OUT</sub> シンク電流対 V<sub>OUT</sub>

Rev. A - 12/28 -

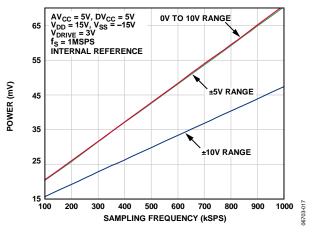

図 15.消費電力対サンプリング周波数 ノーマル・モード

### 用語

#### 微分非直線性(DNL)

ADCの2つの隣接コード間における1LSB変化の測定値と理論値の差をいいます。

#### 積分非直線性(INL)

ADC 伝達関数の両端を結ぶ直線からの最大偏差をいいます。伝達関数の両端とは、ゼロ・スケール(最初のコード遷移より 1 LSB 下のポイント)とフル・スケール (最後のコード遷移より 1 LSB 上のポイント)をいいます。

#### ゼロ・コード誤差

ミッドスケール変化(全0から全1への変化)の理想  $V_{IN}$  電圧(すなわちバイポーラ範囲では AGND - ½ LSB、ユニポーラ範囲では  $2 \times V_{REF} - 1$  LSB)からの差を意味します。

#### 正のフル・スケール誤差

オフセット誤差調整後の最後のコード遷移((011…110) から(011…111))と理論値(  $+4 \times V_{REF} - 1$  LSB または $+2 \times V_{REF} - 1$  LSB)との差を意味します。

#### 負のフル・スケール誤差

ゼロ・コード誤差調整後の最初のコード遷移 ((10...000)から(10...001))と理論値 $(-4 \times V_{REF} + 1 \text{ LSB})$ との差を意味します。

#### ゼロ・コード誤差の不一致

すべてのチャンネル間でのゼロ・コード誤差の差を意味します。

#### 正のフル・スケール誤差マッチ

すべてのチャンネル間での正のフル・スケール誤差の 差を意味します。

#### 負のフル・スケール誤差マッチ

すべてのチャンネル間での負のフル・スケール誤差の 差を意味します。

#### トラック・アンド・ホールド・アクイジション時間

変換終了後、トラック・アンド・ホールド・アンプはトラック・モードに戻ります。トラック・アンド・ホールド・アクイジション時間は、変換終了後にトラック・アンド・ホールド・アンプが最終値の±½LSB以内に出力が収まるために要する時間です。

#### 信号対ノイズ(+歪み)比 (SINAD)

これは、A/D コンバータ出力での信号対ノイズ(+歪み) 比の測定値です。信号は基本波の rms 振幅で表します。 ノイズは 1/2 サンプリング周波数( $f_S/2$ )までの全高調波 の和で表します(DC を除く)。この比はデジタル化処理 の量子化レベル数に依存し、レベル数が大きいほど、 量子化ノイズは小さくなります。正弦波を入力した場 合の、理想 N ビット・コンバータに対する信号対(ノイズ+歪み)比の理論値は次式で表されます。

信号対ノイズ(+歪み) = (6.02N + 1.76) dB

したがって、12 ビット・コンバータの場合、SINAD は 74 dB になります。

#### 総合高調波歪み(THD)

THD は高調波の rms 値総和と基本波の比です。 AD7366/AD7367 の場合、THD は次のように定義されます。

$$THD (dB) = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、

$V_{l}$ は基本波の rms 振幅。

$V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$ は、2 次~6 次の高調波の rms 振幅。

#### ピーク高調波またはスプリアス・ノイズ

高調波またはスプリアス・ノイズは、ADC 出力スペクトル内の(DC を除いて  $f_s/2$  まで)次に大きい成分の rms 値の、基本波 rms 値に対する比として定義されます。 通常、この仕様の値はスペクトル内の最大高調波により決定されますが、高調波がノイズ・フロアに埋もれている ADC の場合、ノイズ・ピークになります。

#### チャンネル間アイソレーション

チャンネル間アイソレーションは、任意の入力範囲内で動作している2つのチャンネル間でのクロストークのレベルの大きさを表します。フル・スケールの正弦波信号をすべての非選択入力チャンネルに入力し、50kHz信号を使って選択したチャンネルで信号の減衰を測定することにより決定します。このようにして得た値がAD7366/AD7367の全4チャンネル間でのtyp値になります(詳細については、図9を参照してください)。

#### 相互変調歪み (IMD)

非線形性を持つアクティブ・デバイスに 2つの周波数 fa および fb を含む正弦波を入力すると、さまざまな和 および差の周波数 mfa  $\pm$  nfb を持つ歪み成分が発生します。ここで、m、n=0、1、2、3、...です。相互変調歪 みの項とは、m または n がゼロでない項をいいます。 たとえば、2 次項には(fa+fb)と(fa-fb)が含まれ、3 次項には(2fa+fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb)、(2fa-fb) 、(2fa-fb) 、(2fa-fb

AD7366/AD7367 は、入力帯域幅の上限に近い2つの入力周波数を使う CCIF 標準を使ってテストされています。この場合、2次項は通常、元の正弦波の周波数から離れて位置し、3次項は通常、入力周波数に近い周波数に位置します。そのため、2次項と3次項は別々に指定されます。相互変調歪みの計算は THD の仕様に従います。すなわち、dBで表した個々の歪み成分の rms 総和の、基本波の和の rms 振幅に対する比になります。

#### 電源変動除去比(PSRR)

電源変動はフル・スケール変化に影響しますが、コンバータの直線性には影響を与えません。PSRR は、電源電圧の公称値からの変化で発生するフル・スケール変化ポイントの最大変化を表します(図 11 参照)。

#### サーマル(または出力電圧)ヒステリシス

サーマル(または出力電圧)ヒステリシスは、次のいずれかの温度サイクルを加えた後のリファレンス出力電圧の絶対最大変化として定義されます。

$$T_HYS + = +25^{\circ}C \rightarrow T_{MAX} \rightarrow +25^{\circ}C$$

または

$$T_HYS-=+25^{\circ}C \rightarrow T_{MIN} \rightarrow +25^{\circ}C$$

この値は次式を使って ppm で表されます。

$$V_{HYS} \text{ (ppm)} = \left| \frac{V_{REF} (25^{\circ}\text{C}) - V_{REF} (T_{HYS})}{V_{REF} (25^{\circ}\text{C})} \right| \times 10^{6}$$

ここで、

$V_{REF}(25^{\circ}C)$ は、25°C での  $V_{REF}$ 。  $V_{REF}(T_HYS)$ は、T\_HYS+または T\_HYS-での  $V_{REF}$ の最大変化。

### 動作原理

#### 回路説明

AD7366/AD7367 は、デュアルの高速、2 チャンネル、12/14 ビット、バイポーラ入力、同時サンプリング、シリアル ADC です。AD7366/AD7367 のアナログ入力には、 $\pm 10$  V 2 と  $\pm 5$  V の入力範囲のバイポーラ電圧を入力することができます。また、 $0\sim 10$  V のユニポーラ範囲を入力することもできます。AD7366/AD7367 には、高電圧アナログ入力構造に対する  $V_{DD}$  と  $V_{SS}$  の 2 つの電源が必要です。これらの電源は $\pm 11.5$  V 以上である必要があります。各アナログ入力範囲に対するこれらの電源の最小条件については、表 7 を参照してください。AD7366/AD7367 には、ADC コアの電源として 4.75 V  $\sim$  5.25 V の低電圧  $AV_{CC}$  電源が必要です。

表 7.リファレンス電圧と各アナログ入力範囲に対する電源条件

| Selected<br>Analog Input<br>Range (V) | Reference<br>Voltage (V) | Full-Scale<br>Input<br>Range (V) | AV <sub>CC</sub> (V) | Minimum<br>V <sub>DD</sub> /V <sub>SS</sub> (V) |

|---------------------------------------|--------------------------|----------------------------------|----------------------|-------------------------------------------------|

| ±10                                   | 2.5                      | ±10                              | 5                    | ±11.5                                           |

|                                       | 3.0                      | ±12                              | 5                    | ±12                                             |

| ±5                                    | 2.5                      | ±5                               | 5                    | ±11.5                                           |

|                                       | 3.0                      | ±6                               | 5                    | ±11.5                                           |

| 0 to 10                               | 2.5                      | 0 to 10                          | 5                    | ±11.5                                           |

|                                       | 3.0                      | 0 to 12                          | 5                    | ±12                                             |

AD7366/AD7367 は、2個のトラック・アンド・ホールド・アンプ、2個の逐次比較型 ADC、シリアル・インターフェースを内蔵し、2本の個別データ出力ピンを持っています。AD7366/AD7367 は、24 ピンの TSSOPパッケージを採用し、他のソリューションに比べて優れた省スペースを提供します。AD7366/AD7367 には、変換を開始させる CNVST信号が必要です。CNVSTの立ち下がりエッジで、両トラック・アンド・ホールドがホールド・モードになり、各変換が開始されます。変換が開始されると、BUSY信号がハイ・レベルになります。各逐次比較型 ADC のクロックは、内蔵発振器から供給されます。変換が完了すると、BUSY 信号はロー・レベルになります。BUSY の立ち下がりエッジで、トラック・アンド・ホールドはトラック・モードに戻ります。変換が終了すると、シリアル・クロック入力を使ってデバイスからデータがアクセスされます。

AD7366/AD7367 は 2.5 V のリファレンス電圧を内蔵していますが、外付けリファレンス電圧を使う場合には、これをディスエーブルすることができます。 ADC の内部リファレンス電圧をシステム内の他の場所で使う場合には、 $D_{CAP}A$  出力と  $D_{CAP}B$  出力を先ずバッファすることが必要です。パワーアップ時、デバイスが動作するためには、REFSEL ピンをハイ・レベルまたはロー・レベルにして、内部または外付けリファレンス・オプションを選択する必要があります。内部リファレンス電圧を使用する場合は、REFSEL ピンをハイ・レベルに接続する必要があります。あるいは、REFSELをGND に接続すると、外付けリファレンス電圧をDCAPA ピンと  $D_{CAP}B$  ピンを介して両 ADC に入力することができます。

アナログ入力は各 ADC に対する 2 つのシングルエンド 入力として構成することができます。RANGE ビットを 表 8 のように設定して、入力電圧範囲を選択すること ができます。

#### コンバータの動作

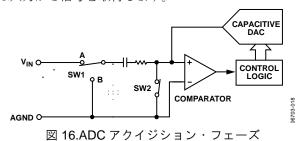

AD7366/AD7367 は、容量 DAC を採用した 2 個の逐次 比較型 ADC を内蔵しています。図 16 と図 17 に、片方 の ADC についての簡略化した回路図(アクイジショ ン・フェーズと変換フェーズ)を示します。ADC は、コ ントロール・ロジック、SAR、容量 DAC から構成され ています。図 16(アクイジション・フェーズ)では、 SW2 は閉じて、SW1 は位置 A にあり、コンパレータは 平衡状態にあり、サンプリング・コンデンサ・アレイ は入力から信号を取得します。

ADCが変換を開始すると(図 17)、SW2が開いて、SW1が位置 B に移動して、コンパレータが不平衡状態になります。コントロール・ロジックと電荷再配分型 DACを使って、サンプリング・コンデンサに対して一定量の電荷を加算および減算して、コンパレータを平衡状態に戻すようにします。コンパレータが平衡状態に戻ると、変換が完了します。コントロール・ロジックは

#### アナログ入力

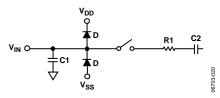

AD7366/AD7367 の各 ADC には、2 つのシングルエンド・アナログ入力があります。図 18 に、

AD7366/AD7367 のアナログ入力構造の等価回路を示します。2 個のダイオードは ESD 保護機能を提供します。アナログ入力信号は電源レールより 300mV 以上高くならないよう注意する必要があります。超えると、これらのダイオードが順方向にバイアスされて、サブストレートに電流が流れるようになります。これらのダイオードが損傷なしに許容できる最大電流は 10~mA です。抵抗はスイッチのオン抵抗で構成される集中定数部品です。これらの抵抗値は約  $170~\Omega$  (typ)です。コンデンサ C1 は主にピン容量に起因し、コンデンサ C2 は ADCのサンプリング・コンデンサです。C1 と C2 の合計集中定数容量は、 $\pm 10~\text{V}$  入力範囲では約 9~pF に、他のすべての入力範囲では約 13~pF に、それぞれなります。

図 18.等価アナログ入力構造

AD7366/AD7367 は真のバイポーラ入力電圧を処理することができます。アナログ入力範囲は、 $\pm 10\,\mathrm{V}$ 、 $\pm 5\,\mathrm{V}$  または  $0\,\mathrm{V}\sim 10\,\mathrm{V}$  に設定することができます。RANGE0 ピンと RANGE1 ピンのロジック・レベルにより、表 8 に示すように、入力範囲が選択されます。これらの範囲ビットは、変換前のアクイジション時間中に変更することはできませんが、それ以外は何時でも変更することができます。

表 8.アナログ入力範囲の選択

| RANGE1 | RANGE0 | Range Selected |

|--------|--------|----------------|

| 0      | 0      | ±10 V          |

| 0      | 1      | ±5 V           |

| 1      | 0      | 0 V to 10 V    |

| 1      | 1      | Do not program |

AD7366/AD7367 には、高電圧アナログ入力構造に対する  $V_{DD}$  と  $V_{SS}$  の 2 つの電源が必要です。これらの電源は±11.5 V 以上である必要があります。これらの電源条件については、表 7 を参照してください。

AD7366/AD7367 では、ADC コア電源として 4.75 V~5.25 V の低電圧 AV $_{CC}$ 電源、デジタル電源として 4.75 V ~5.25 V の DV $_{CC}$ 電源、インターフェース電源として 2.7 V~5.25 V の V $_{DRIVE}$  電源が必要です。

チャンネルの選択は、ADDR ピンを使って行います(表 9 参照)。ADDR ピンのロジック・レベルは、進行中の変換ではなく次の変換の BUSY 信号の立ち上がりエッジでラッチされます。AD7366/AD7367 に最初に電源が加えられるときのデフォルトのチャンネル選択は  $\mathbf{V}_{A1}$  と  $\mathbf{V}_{B1}$  です。

表 9.チャンネルの選択

| ADDR | Channels Selected |

|------|-------------------|

| 0    | $V_{A1}, V_{B1}$  |

| 1    | $V_{A2}, V_{B2}$  |

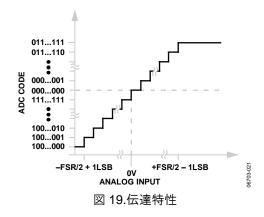

#### 伝達関数

AD7366/AD7367 の出力コーディングは 2 の補数です。 コード変化は LSB の連続する整数倍値(1 LSB、2 LSB など)で発生します。LSB サイズは選択したアナログ入 力範囲に依存します(表 10 参照)。理論伝達特性を図 19 に示します。

表 10.各アナログ入力範囲に対する LSB サイズ

|                | AD7366              |                  | AD7367              |                  |

|----------------|---------------------|------------------|---------------------|------------------|

| Input<br>Range | Full-Scale<br>Range | LSB Size<br>(mV) | Full-Scale<br>Range | LSB Size<br>(mV) |

| ±10 V          | 20 V/4096           | 4.88             | 20 V/16,384         | 1.22             |

| ±5 V           | 10 V/4096           | 2.44             | 10 V/16,384         | 0.61             |

| 0 V to 10 V    | 10 V/4096           | 2.44             | 10 V/16,384         | 0.61             |

トラック・アンド・ホールド

AD7366/AD7367 のトラック/ホールド・アンプにより、ADC はフル・スケール振幅の入力正弦波を正確に 12/14 ビット精度で変換することができます。トラック・アンド・ホールドの入力帯域幅は、ADC のナイキスト・レートより広くなっています。AD7366/AD7367 は最大 35 MHz の周波数を処理することができます。

トラック・アンド・ホールドは、CSの立ち下がりエッジの後にBUSY信号がロー・レベルになったときトラッキング・モードになります。トラック・アンド・ホールド・アンプが入力信号を取り込むときに要する時間は、サンプリング・コンデンサを充電する速度に依存します。ゼロ・ソース・インピーダンスでは、

AD7366 での 12 ビット・レベルと AD7367 での 14 ビット・レベルへ信号を取り込むための時間は 140 ns あれば十分です。 $\pm 10$  V、 $\pm 5$  V、0 V~10 V の範囲に対するアクイジション時間( $\pm \frac{1}{2}$  LSB 以内に整定)は 140 ns (typ)です。ADC は、 $\overline{CNVST}$ の立ち下がりエッジでホールド・モードに戻ります。

必用とされるアクイジション時間は次式で計算されます。

$t_{ACQ} = 10 \times ((R_{SOURCE} + R) C)$

ここで、Cはサンプリング容量。

Rは、トラック・アンド・ホールド・アンプから入力を見た抵抗。

$R_{SOURCE}$ には、アナログ入力のその他のソース・インピーダンスも含む必要があります。

AD7366/AD7367 には、他のバイポーラ ADC とは異なり、抵抗アナログ入力構造がありません。

AD7366/AD7367では、バイポーラ・アナログ信号が直接サンプリング・コンデンサへサンプルされます。このため、AD7366/AD7367のアナログ入力インピーダンスは高くなります。アナログ入力インピーダンスは次式で計算できます。

$Z = 1/(f_S \times C_S)$

ここで、

fsはサンプリング周波数。

Csはサンプリング・コンデンサ値。

$C_s$  は選択したアナログ入力範囲に依存します(アナログ入力のセクション参照)。1 MSPS の動作では、 $\pm 10$  V 範囲に対するアナログ入力インピーダンスは 260 k $\Omega$  (typ)です。サンプリング周波数が低くなると、アナログ入力インピーダンスはさらに大きくなります。アナログ入力インピーダンスが大きくなると、アナログ入力の駆動に必要な電流は減少します(詳細については、図 7 を参照してください)。

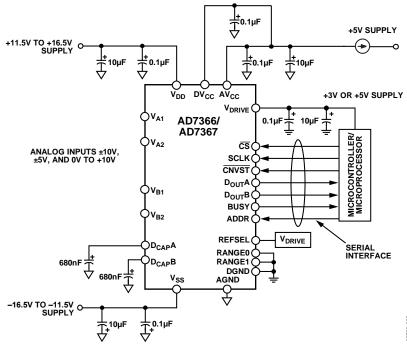

#### 代表的な接続図

図 20 に、AD7366/AD7367 の一般的な接続図を示します。この接続では、AGND ピンはシステムのアナログ・グラウンド・プレーンに接続され、DGND ピンはシステムのデジタル・グラウンド・プレーンに接続されています。AD7366/AD7367 の各アナログ入力には、バイポーラの各シングルエンド・アナログ信号を入力することができす。また、AD7366/AD7367 は内蔵または外付けのリファレンス電圧で動作することができます。図 20 では、AD7366/AD7367 は内部 2.5 V リファレンス電圧で動作するように構成されています。内部リファレンス電圧で動作するときは、680 nF のデカップリング・コンデンサが必要です。

$AV_{CC}$ ピンと  $DV_{CC}$ ピンは 5 V 電源電圧に接続されています。 高電圧アナログ入力構造に対して  $V_{DD}$  と  $V_{SS}$  の 2 つの電源が必要です。これらのピンの電圧は $\pm 11.5$  V 以上である必要があります(詳細については、表 7  $を参照してください)。 <math>V_{DRIVE}$ ピンは、マイクロプロセッサの電源電圧に接続されています。  $V_{DRIVE}$ 入力へ加えられる電圧が、シリアル・インターフェースの電圧を制御します。  $V_{DRIVE}$ は 3 V または 5 V に設定することができます。

図 20.内部リファレンス電圧を使用する代表的な接続図

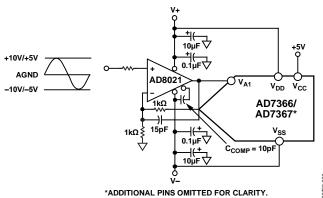

#### ドライバ・アンプの選択

AD7366/AD7367には、シングルエンド・モードで動作するアナログ入力が合計 4 個あります。両 ADC のアナログ入力には、3 種類のアナログ入力範囲を設定することができます。信号ソースが高インピーダンスを持つアプリケーションでは、アナログ入力をバッファした後に ADC アナログ入力へ接続することが推奨されます。図 21 に、シングルエンド・モードでの AD7366/AD7367 の構成を示します。

THD と SNR が重要であるアプリケーションでは、AD7366/AD7367 のアナログ入力を低インピーダンス・ソースから駆動する必要があります。ソース・インピーダンスが大きいと、ADC の AC 性能に大きな影響を与えるため、入力バッファ・アンプの使用が必要になります。

アンプを使わないでアナログ入力を駆動するときは、ソース・インピーダンスを小さい値に制限する必要があります。最大ソース・インピーダンスは、アプリケーションの許容可能な THD の大きさに依存します。ソース・インピーダンスが増加すると THD が大きくなるため、性能が低下します。図7に、種々のソース・インピーダンスに対する THD 対アナログ入力周波数を示します。AD7366/AD7367は、入力範囲と選択したアナログ入力設定に応じて、ソース・インピーダンスを図7のように処理することができます。

AD7366/AD7367のアナログ入力が選択可能である性質から、入力の駆動に使用するオペアンプの選択は、特定のアプリケーションによって決まり、選択したアナログ入力電圧範囲に依存します。

ドライバ・アンプは、フル・スケール・ステップに対して AD7366/AD7367 の規定されたアクイジション時間内に 14 ビット・レベル(0.0061%)にセトリングできる必要があります。AD8021 のようなオペアンプは、シングルエンド・モードで動作するときこの条件を満たします。AD8021 には外部補償 NPO タイプのコンデンサが必要です。AD8022 は、デュアル・バージョンが必要とされる高周波アプリケーションでも使用することができます。低周波アプリケーションに対しては、オペアンプ AD797、AD845、AD8610 が推奨されます。

図 21.AD8021 をアナログ入力の駆動に使用した代表的 な接続図

#### VDRIVE

AD7366/AD7367 には、シリアル・インターフェースが動作する電圧を制御する  $V_{DRIVE}$ 機能もあります。 VDRIVE を使うと、ADC は 3 V と 5 V のプロセッサに容易にインターフェースすることができます。たとえば、AD7366/AD7367 が  $V_{CC}=5$  V で動作する場合、  $V_{DRIVE}$  ピンは 3 V 電源に接続することができるため、低い電圧のデジタル・プロセッサで大きなダイナミック・レンジが可能になります。したがって、 D7366/AD7367 を $\pm 10$  V の入力範囲で使っても、3 V のデジタル製品にインターフェースすることができます。

AD7366 では 1.12 MSPS の最大スループット・レートを、または AD7367 では 1 MSPS を、それぞれ実現する場合、 $V_{DRIVE}$  は 4.75 V 以上である必要があります(表2と表3参照)。2.7  $V < V_{DRIVE} < 4.75$  V での最大スループット・レートは、AD7366 では 1 MSPS に、AD7367 では 900 kSPS に、それぞれなります。

#### リファレンス電圧

AD7366/AD7367 は、2.5 V の内蔵リファレンス電圧または外付けリファレンス電圧で動作することができます。REFSEL ピンのロジック状態で、内蔵リファレンス電圧を使用するか否かを指定します。内蔵リファレンス電圧は、REFSEL ピンがハイ・レベルのとき両ADC に対して選択されます。REFSEL ピンが GND に接続されると、外付けリファレンスを  $D_{CAP}A$  ピンと  $D_{CAP}B$  ピンを使って入力することができます。パワーアップ時、デバイスが動作するためには、REFSEL ピンをハイ・レベルまたはロー・レベルにする必要があります。AD7366/AD7367 に適するリファレンス・ソースとしては、AD780、AD1582、ADR431、REF193、ADR391 などがあります。

内蔵リファレンス電圧回路は、 $2.5\,V$ のバンド・ギャップ・リファレンス電圧とリファレンス電圧・バッファから構成されています。AD7366/AD7367を内蔵リファレンス電圧モードで動作させときは、 $2.5\,V$ の内蔵リファレンス電圧が  $D_{CAP}A$  ピンと  $D_{CAP}B$  ピンから出力されるので、これを  $680\,nF$  のコンデンサで AGND ヘデカップリングする必要があります。内蔵リファレンス電圧をシステム内の他の場所で使う前にバッファすることが推奨されます。内蔵リファレンス電圧は、 $\pm 10\,V$ のアナログ入力範囲で最大  $150\,\mu A$  を、 $\pm 5\,V$  範囲と  $0\,V \sim 10\,V$  範囲で  $70\,\mu A$  を、それぞれ供給することができます。

ADC 変換に内蔵リファレンス電圧の動作が必要な場合は、パワーアップ時に REFSEL ピンをハイ・レベルにする必要があります。リファレンス・バッファは、パワーアップのために 70 μs を要し、パワーアップ時に680 nF のデカップリング・コンデンサが充電されます。

AD7366/AD7367 は、 $2.5\,V\sim3\,V$ のリファレンス電圧に対して仕様が規定されています。3Vのリファレンス電圧を選択すると、アナログ入力範囲は、 $\pm12\,V$ 、 $\pm6\,V$ 、 $0\,V\sim12\,V$  になります。これらの範囲に対しては、 $V_{DD}$   $\geq +12\,V$  で、かつ  $V_{SS} \leq -12\,V$  である必要があります。

### 動作モード

AD7366/AD7367 の動作モードは、変換終了時のCNVST 信号のロジック状態により選択されます。 ノーマル・モードとシャットダウン・モードの 2 つの動作モード があります。これらの動作モードは、柔軟なパワー・マネジメント・オプションを提供するようにデザイン されています。これらオプションは、さまざまなアプリケーション条件に対して消費電力/スループット・レートの比を最適化するために選択することができます。

#### ノーマル動作モード

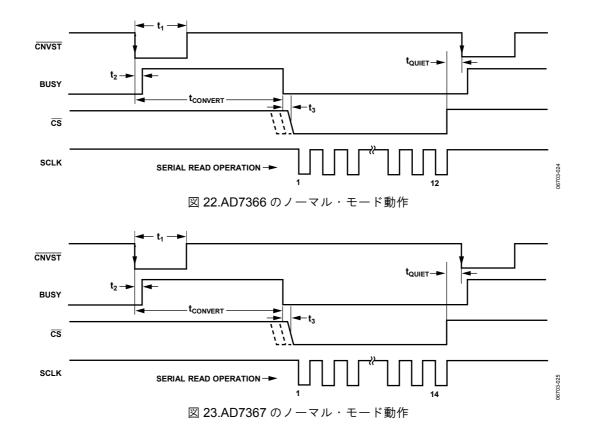

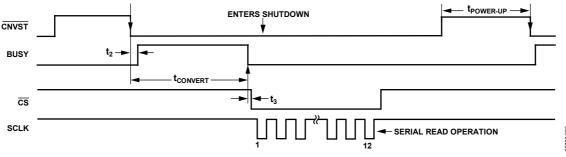

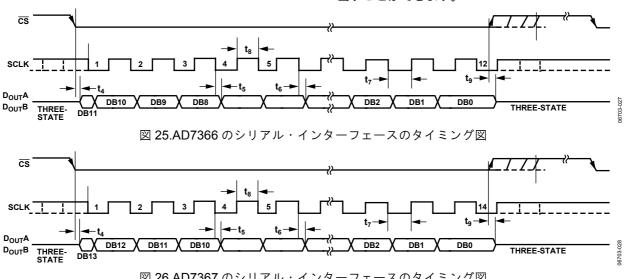

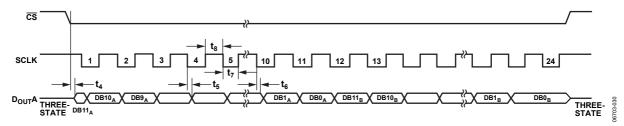

ノーマル・モードは、高速スループット・レートを必要とするアプリケーションを対象としています。ノーマル・モードでは、AD7366/AD7367 が常時フル・パワーオン状態にあるためパワーアップ時間を気にする必要はありません。図 22 に、ノーマル・モードでのAD7366 の一般的な動作を示します。図 23 には、AD7367 のノーマル・モードを示します。