# MSOP/QFNパッケージ採用の1.5LSB INL、 250kSPS、18ビットPulSAR差動A/Dコンバータ

**AD7691**

### 特長

ノー・ミスコードの18ビット分解能

スループット:250kSPS

INL:  $\pm 0.75$ LSB (typ),  $\pm 1.5$ LSB (max) (FSR $\emptyset \pm 6$  ppm) ダイナミック・レンジ:102dB (typ) @250kSPS オーバーサンプリング・ダイナミック・レンジ:125dB @1kSPS

ノイズフリー・コード分解能:20ビット@1kSPS

有効分解能: 22.7ビット@1kSPS SINAD: 101.5dB (typ) @1kHz THD: -125dB (typ) @1kHz 真の差動アナログ入力範囲:±V<sub>REF</sub> V<sub>REF</sub>=VDDまで両入力0V~V<sub>REF</sub>

パイプライン遅延なし

2.3~5Vの単電源動作、1.8V/2.5V/3V/5Vロジックとのイン

ターフェース可能

SPI/QSPI™/MICROWIRE™/DSP互換シリアル・インター

複数のADCのデイジーチェーン接続が可能 オプションのBUSYインジケータ機能

消費雷力

2.5V/100kSPSで1.35mW、5V/100kSPSで4mW 2.5V/100SPSで1.4µW

スタンバイ電流:1nA

10ピン・パッケージ:MSOP (MSOP-8と同じサイズ) およ び3mm×3mmのQFN (LFCSP) (SOT-23と同じサイズ) 18ビットAD7690および16ビットAD7693/AD7688/AD7687 とピン互換

# アプリケーション

バッテリ駆動機器 データ・アクイジション 地震データ・アクイジション・システム

計測機器 医療機器

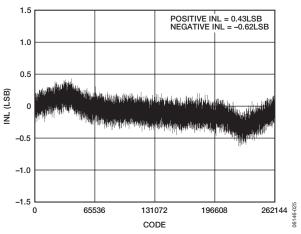

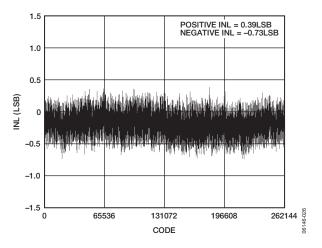

図1. コード 対 積分非直線性(5V)

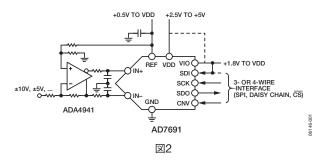

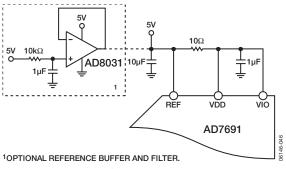

### アプリケーション図

表1. MSOP、QFN(LFCSP)/SOT-23パッケージの 14/16/18ビットPulSAR®ADC

| Туре                             | 100<br>kSPS      | 250<br>kSPS      | 400 kSPS to<br>500 kSPS | ≥1000<br>kSPS    | ADC<br>Driver          |

|----------------------------------|------------------|------------------|-------------------------|------------------|------------------------|

| 18-Bit True<br>Differential      |                  | AD7691           | AD7690                  | AD7982<br>AD7984 | ADA4941-1<br>ADA4841-x |

| 16-Bit True<br>Differential      | AD7684           | AD7687           | AD7688<br>AD7693        |                  | ADA4941-1<br>ADA4841-x |

| 16-Bit<br>Pseudo                 | AD7680<br>AD7683 | AD7685<br>AD7694 | AD7686                  | AD7980           | ADA4841-x              |

| Differential                     |                  | , , , , ,        |                         |                  |                        |

| 14-Bit<br>Pseudo<br>Differential | AD7940           | AD7942           | AD7946                  |                  | ADA4841-1              |

AD7691は、2.3~5Vの単電源 (VDD) で動作する、電荷再配 分型の18ビット逐次比較型A/Dコンバータ (ADC) です。低消 費電力かつノー・ミスコードで高速の18ビット・サンプリング ADC、変換クロック、多機能シリアル・インターフェース・ ポートを内蔵しています。IN+とIN-ピン間の電位差をCNV の立上がりエッジでサンプリングします。これらのピン電圧は 通常、0V~REFの電圧範囲で反対の位相を持ちます。リファ レンス電圧REFは外部から供給し、電源電圧に設定できます。

消費電力はスループットに比例します。

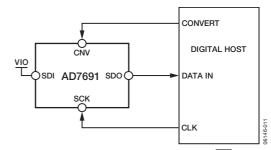

SPI互換のシリアル・インターフェースは、SDI入力を使用し て1本の3線式バス上で複数のADCをデイジーチェーン接続で き、さらにオプションのBUSYインジケータを使用することも できます。1.8V、2.5V、3V、5Vのロジックに互換で、独立し たVIO電源を使用します。

AD7691は10ピンMSOPまたは10ピンOFN(LFCSP)パッ ケージを採用し、-40~+85℃の温度範囲で動作するように仕 様が規定されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる論とされている。 せん。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもので もありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します。

- トはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 © 2006-2007 Analog Devices, Inc. All rights reserved.

REV. A

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 本 社/ 〒105-6891 電話03 (5402) 8200

| 1   |

|-----|

| /K' |

|     |

| 特長            | ドライバ・アンプの選択                                    | 16 |

|---------------|------------------------------------------------|----|

| アプリケーション1     | シングルエンド/差動変換ドライバ                               | 16 |

| アプリケーション図1    | リファレンス電圧入力                                     | 16 |

| 概要1           | 電源                                             | 17 |

| 改訂履歴2         | リファレンスからADCへの電源供給                              | 17 |

| 仕様3           | デジタル・インターフェース                                  | 17 |

| タイミング仕様5      | BUSYインジケータを使用しない3線式CSモード                       |    |

| 絶対最大定格7       | BUSYインジケータを使用する3線式CSモード                        |    |

| 熱抵抗7          | BUSYインジケータを使用しない4線式 $\overline{\text{CS}}$ モード | 20 |

| ESDに関する注意7    | BUSYインジケータを使用する4線式 $\overline{\text{CS}}$ モード  | 21 |

| ピン配置とピン機能の説明8 | BUSYインジケータを使用しないチェーン・モード                       | 22 |

| 代表的な性能特性9     | BUSYインジケータを使用するチェーン・モード                        | 23 |

| 用語の説明13       | アプリケーション設計上の注意                                 | 24 |

| 動作原理14        | レイアウトのポイント                                     | 24 |

| 回路の説明14       | AD7691の性能評価                                    | 24 |

| コンバータの動作14    | 外形寸法                                           |    |

| 代表的な接続図15     | オーダー・ガイド                                       | 25 |

| アナログ入力15      |                                                |    |

|               |                                                |    |

# 改訂履歴

## 11/07—Rev. 0 to Rev. A

| Deleted QFN Package in Development References Universal  |

|----------------------------------------------------------|

| Changes to Features, Applications, Figure 1 and Figure 2 |

| Changes to Accuracy, Table 2                             |

| Changes to Power Dissipation, Table 3                    |

| Added Thermal Resistance Section                         |

| Changes to Figure 22                                     |

| Changes to Format                                        |

| Changes to Terminology Section                           |

| Changes to Format and Figure 29                          |

| Inserted Figure 31                                       |

| Changes to Format                                        |

| Changes to Figure 44                                     |

| Changes to Figure 46                                     |

| Updated QFN Outline Dimensions                           |

| Changes to Ordering Guide                                |

7/06—Revision 0: Initial Version

# 仕様

$VDD=2.3\sim5.25V$ 、 $VIO=2.3V\sim VDD$ 、 $V_{REF}=VDD$ 、特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。

### 表2

| Parameter                               | Conditions/Comments                               | Min        | Тур         | Max               | Unit             |

|-----------------------------------------|---------------------------------------------------|------------|-------------|-------------------|------------------|

| RESOLUTION                              |                                                   | 18         |             |                   | Bits             |

| ANALOG INPUT                            |                                                   |            |             |                   |                  |

| Voltage Range, V <sub>IN</sub>          | IN+-(IN-)                                         | $-V_{REF}$ |             | $+V_{REF}$        | V                |

| Absolute Input Voltage                  | IN+, IN-                                          | -0.1       |             | $V_{REF} + 0.1$   | V                |

| Common-Mode Input Range                 | IN+, IN-                                          | 0          | $V_{REF}/2$ | $V_{REF}/2 + 0.1$ | V                |

| Analog Input CMRR                       | $f_{IN} = 250 \text{ kHz}$                        |            | 65          |                   | dB               |

| Leakage Current at 25℃                  | Acquisition phase                                 |            | 1           |                   | nA               |

| Input Impedance <sup>1</sup>            |                                                   |            |             |                   |                  |

| THROUGHPUT                              |                                                   |            |             |                   |                  |

| Conversion Rate                         | VDD = 4.5 V to 5.25 V                             | 0          |             | 250               | kSPS             |

|                                         | VDD = 2.3 V to 4.5 V                              | 0          |             | 180               | kSPS             |

| Transient Response                      | Full-scale step                                   |            |             | 1.8               | μs               |

| ACCURACY                                |                                                   |            |             |                   |                  |

| No Missing Codes                        |                                                   | 18         |             |                   | Bits             |

| Integral Linearity Error                |                                                   | -1.5       | ±0.75       | +1.5              | LSB <sup>2</sup> |

| Differential Linearity Error            |                                                   | -1         | ±0.5        | +1.25             | LSB <sup>2</sup> |

| Transition Noise                        | REF = VDD = 5 V                                   |            | 0.75        |                   | LSB <sup>2</sup> |

| Gain Error <sup>3</sup>                 | VDD = 4.5  V to  5.25  V                          | -40        | ±2          | +40               | LSB <sup>2</sup> |

|                                         | VDD = 2.3  V to  4.5  V                           | -80        | ±2          | +80               | LSB <sup>2</sup> |

| Gain Error Temperature Drift            |                                                   |            | ±0.3        |                   | ppm/℃            |

| Zero Error <sup>3</sup>                 | VDD = 4.5  V to  5.25  V                          | -0.8       | ±0.1        | +0.8              | mV               |

|                                         | VDD = 2.3  V to  4.5  V                           | -3.5       | ±0.7        | +3.5              | mV               |

| Zero Temperature Drift                  |                                                   |            | ±0.3        |                   | ppm/℃            |

| Power Supply Sensitivity                | $VDD = 5 V \pm 5\%$                               |            | ±0.25       |                   | LSB <sup>2</sup> |

| AC ACCURACY <sup>4</sup>                |                                                   |            |             |                   |                  |

| Dynamic Range                           | $V_{REF} = 5 \text{ V}$                           | 101        | 102         |                   | dB               |

| Oversampled Dynamic Range <sup>5</sup>  | $f_{IN} = 1 \text{ kSPS}$                         |            | 125         |                   | dB               |

| Signal-to-Noise                         | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   | 100        | 101.5       |                   | dB               |

|                                         | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}$ | 95         | 96.5        |                   | dB               |

| Spurious-Free Dynamic Range             | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   |            | -125        |                   | dB               |

| Total Harmonic Distortion               | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   |            | -118        |                   | dB               |

| Signal-to-(Noise + Distortion)          | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   | 100        | 101.5       |                   | dB               |

|                                         | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}$ | 95         | 96.5        |                   | dB               |

| Intermodulation Distortion <sup>6</sup> |                                                   |            | 115         |                   | dB               |

REV. A -3-

<sup>| 「</sup>アナログ入力」を参照。

| 2 LSBは最下位ビットを意味します。入力範囲が±5Vの場合、ILSB=38.15µV。

| 3 「用語の説明」を参照。これらの仕様にはすべての温度範囲の変動が含まれますが、外部リファレンスによる誤差分は含まれません。

| 4 dB表示の仕様はすべてフルスケール入力 (FSR) を基準とします。特に指定のない限り、フルスケールより0.5dB低い入力信号でテスト。

| 5 ダイナミック・レンジは、ADCをオーバーサンプリングしてスループットf<sub>s</sub>=250kSPSで動作させ、 さらにf<sub>o</sub>のポストデジタル・フィルタ処理をして出力ワードレートを取得して測定。

$<sup>^{6}</sup>$   $f_{\rm INI}\!=\!21.4 {\rm kHz},~f_{\rm IN2}\!=\!18.9 {\rm kHz}$  (フルスケールより7dB低い周波数)

$VDD=2.3\sim5.25V$ 、 $VIO=2.3\sim VDD$ 、 $V_{REF}=VDD$ 、特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。

## 表3

| Parameter                       | Conditions/Comments                     | Min              | Тур  | Max               | Unit         |

|---------------------------------|-----------------------------------------|------------------|------|-------------------|--------------|

| REFERENCE                       |                                         |                  |      |                   |              |

| Voltage Range                   |                                         | 0.5              |      | VDD + 0.3         | V            |

| Load Current                    | 250  kSPS, REF = 5  V                   |                  | 60   |                   | μA           |

| SAMPLING DYNAMICS               |                                         |                  |      |                   |              |

| −3 dB Input Bandwidth           |                                         |                  | 2    |                   | MHz          |

| Aperture Delay                  | VDD = 5 V                               |                  | 2.5  |                   | ns           |

| DIGITAL INPUTS                  |                                         |                  |      |                   |              |

| Logic Levels                    |                                         |                  |      |                   |              |

| $ m V_{IL}$                     |                                         | -0.3             |      | $+0.3 \times VIO$ | V            |

| $ m V_{IH}$                     |                                         | $0.7 \times VIO$ |      | VIO + 0.3         | V            |

| ${ m I}_{ m IL}$                |                                         | -1               |      | +1                | μA           |

| $I_{IH}$                        |                                         | -1               |      | +1                | μA           |

| DIGITAL OUTPUTS                 |                                         |                  |      |                   |              |

| Data Format                     | Serial 18-bit, twos complement          |                  |      |                   |              |

| Pipeline Delay <sup>1</sup>     |                                         |                  |      |                   |              |

| $ m V_{OL}$                     | $I_{SINK} = +500 \mu\text{A}$           |                  |      | 0.4               | V            |

| $V_{OH}$                        | $I_{SOURCE} = -500 \mu A$               | VIO – 0.3        |      |                   | V            |

| POWER SUPPLIES                  |                                         |                  |      |                   |              |

| VDD                             | Specified performance                   | 2.3              |      | 5.25              | V            |

| VIO                             | Specified performance                   | 2.3              |      | VDD + 0.3         | V            |

| VIO Range                       |                                         | 1.8              |      | VDD + 0.3         | V            |

| Standby Current <sup>2, 3</sup> | VDD and VIO = 5 V, $T_A = 25^{\circ}$ C |                  | 1    | 50                | nA           |

| Power Dissipation               | VDD = 2.5  V, 100  SPS throughput       |                  | 1.4  |                   | μW           |

|                                 | VDD = 2.5  V, 100  kSPS throughput      |                  | 1.35 |                   | mW           |

|                                 | VDD = 2.5  V, 180  kSPS throughput      |                  | 2.4  |                   | mW           |

|                                 | VDD = 5 V, 100 kSPS throughput          |                  | 4.24 | 5                 | mW           |

|                                 | VDD = 5 V, 250 kSPS throughput          |                  | 10.6 | 12.5              | mW           |

| Energy per Conversion           |                                         |                  | 50   |                   | nJ/sample    |

| TEMPERATURE RANGE <sup>4</sup>  |                                         |                  |      |                   |              |

| Specified Performance           | $T_{MIN}$ to $T_{MAX}$                  | -40              |      | + 85              | $\mathbb{C}$ |

**—4** — REV. A

変換結果は変換直後に出力。

<sup>2</sup> すべてのデジタル入力を必要に応じてVIOまたはGNDに接続。

<sup>3</sup> アクイジション時。

<sup>4</sup> 拡張温度範囲については代理店および弊社営業部にお問い合わせください。

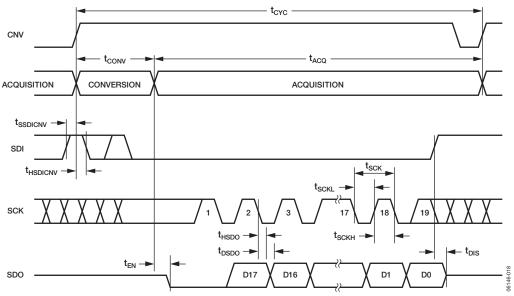

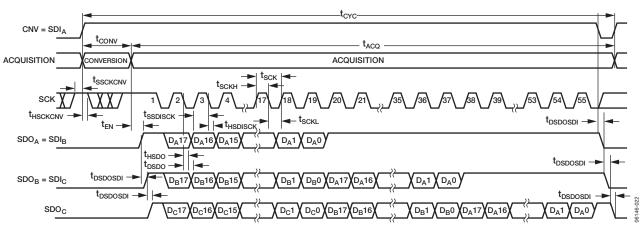

タイミング仕様  $VDD=4.5\sim5.25V$ 、 $VIO=2.3\sim VDD$ 、 $V_{REF}=VDD$ 、特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。  $^{1}$

| Parameter                                                                | Symbol               | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data Available                       | t <sub>CONV</sub>    | 0.5 |     | 2.2 | μs   |

| Acquisition Time                                                         | $t_{ACQ}$            | 1.8 |     |     | μs   |

| Time Between Conversions                                                 | t <sub>CYC</sub>     | 4   |     |     | μs   |

| CNV Pulse Width (CS Mode)                                                | t <sub>CNVH</sub>    | 10  |     |     | ns   |

| SCK Period (CS Mode)                                                     | t <sub>SCK</sub>     | 15  |     |     | ns   |

| SCK Period (Chain Mode)                                                  | t <sub>SCK</sub>     |     |     |     |      |

| VIO Above 4.5 V                                                          |                      | 17  |     |     | ns   |

| VIO Above 3 V                                                            |                      | 18  |     |     | ns   |

| VIO Above 2.7 V                                                          |                      | 19  |     |     | ns   |

| VIO Above 2.3 V                                                          |                      | 20  |     |     | ns   |

| SCK Low Time                                                             | t <sub>SCKL</sub>    | 7   |     |     | ns   |

| SCK High Time                                                            | t <sub>SCKH</sub>    | 7   |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                   | $t_{HSDO}$           | 4   |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                     | $t_{DSDO}$           |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 14  | ns   |

| VIO Above 3 V                                                            |                      |     |     | 15  | ns   |

| VIO Above 2.7 V                                                          |                      |     |     | 16  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 17  | ns   |

| CNV or SDI Low to SDO D17 MSB Valid (CS Mode)                            | t <sub>EN</sub>      |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 15  | ns   |

| VIO Above 2.7 V                                                          |                      |     |     | 18  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 22  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) | $t_{DIS}$            |     |     | 25  | ns   |

| SDI Valid Setup Time from CNV Rising Edge (CS Mode)                      | t <sub>SSDICNV</sub> | 15  |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                       | t <sub>HSDICNV</sub> | 0   |     |     | ns   |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                   | t <sub>SSCKCNV</sub> | 5   |     |     | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                    | t <sub>HSCKCNV</sub> | 10  |     |     | ns   |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                  | t <sub>SSDISCK</sub> | 3   |     |     | ns   |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                   | t <sub>HSDISCK</sub> | 4   |     |     | ns   |

| SDI High to SDO High (Chain Mode with Busy Indicator)                    | $t_{DSDOSDI}$        |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 15  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 26  | ns   |

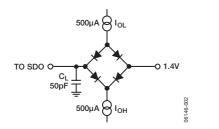

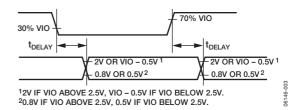

<sup>1</sup> 負荷条件については、図3と図4を参照。

REV. A -5-

$VDD=2.3\sim4.5V$ 、 $VIO=2.3\sim VDD$ 、 $V_{REF}=VDD$ 、特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}$ で規定。 <sup>1</sup>

### 表5

| Parameter                                                                                            | Symbol               | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data Available                                                   | t <sub>CONV</sub>    | 0.5 |     | 3.7 | μs   |

| Acquisition Time                                                                                     | $t_{ACQ}$            | 1.8 |     |     | ns   |

| Time Between Conversions                                                                             | $t_{CYC}$            | 5.5 |     |     | μs   |

| CNV Pulse Width (CS Mode)                                                                            | $t_{CNVH}$           | 10  |     |     | ns   |

| SCK Period (CS Mode)                                                                                 | t <sub>SCK</sub>     | 25  |     |     | ns   |

| SCK Period (Chain Mode)                                                                              | t <sub>SCK</sub>     |     |     |     |      |

| VIO Above 3 V                                                                                        |                      | 29  |     |     | ns   |

| VIO Above 2.7 V                                                                                      |                      | 35  |     |     | ns   |

| VIO Above 2.3 V                                                                                      |                      | 40  |     |     | ns   |

| SCK Low Time                                                                                         | t <sub>SCKL</sub>    | 12  |     |     | ns   |

| SCK High Time                                                                                        | t <sub>SCKH</sub>    | 12  |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                                               | $t_{HSDO}$           | 5   |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                                                 | $t_{DSDO}$           |     |     |     |      |

| VIO Above 3 V                                                                                        |                      |     |     | 24  | ns   |

| VIO Above 2.7 V                                                                                      |                      |     |     | 30  | ns   |

| VIO Above 2.3 V                                                                                      |                      |     |     | 35  | ns   |

| CNV or SDI Low to SDO D17 MSB Valid (CS Mode)                                                        | $t_{EN}$             |     |     |     |      |

| VIO Above 2.7 V                                                                                      |                      |     |     | 18  | ns   |

| VIO Above 2.3 V                                                                                      |                      |     |     | 22  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance $(\overline{\text{CS}}\ \text{Mode})$ | $t_{\rm DIS}$        |     |     | 25  | ns   |

| SDI Valid Setup Time from CNV Rising Edge (CS Mode)                                                  | t <sub>SSDICNV</sub> | 30  |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                                                   | t <sub>HSDICNV</sub> | 0   |     |     | ns   |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                                               | t <sub>SSCKCNV</sub> | 5   |     |     | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                                                | t <sub>HSCKCNV</sub> | 8   |     |     | ns   |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                                              | t <sub>SSDISCK</sub> | 8   |     |     | ns   |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                                               | t <sub>HSDISCK</sub> | 10  |     |     | ns   |

| SDI High to SDO High (Chain Mode with Busy Indicator)                                                | $t_{DSDOSDI}$        |     |     | 36  |      |

<sup>」</sup>負荷条件については、図3と図4を参照。

図3. デジタル・インターフェース・タイミング測定時の 負荷回路

図4. タイミング測定の電圧レベル

# 絶対最大定格

#### 表6

| Parameter                             | Rating                                  |  |  |

|---------------------------------------|-----------------------------------------|--|--|

| Analog Inputs (IN+, IN-) <sup>1</sup> | GND -0.3 V to VDD + 0.3 V or<br>±130 mA |  |  |

| REF                                   | GND -0.3 V to VDD + 0.3 V               |  |  |

| Supply Voltages                       |                                         |  |  |

| VDD, VIO to GND                       | -0.3 V to +7 V                          |  |  |

| VDD to VIO                            | ±7V                                     |  |  |

| Digital Inputs to GND                 | -0.3  V to VIO + 0.3  V                 |  |  |

| Digital Outputs to GND                | -0.3  V to VIO + 0.3  V                 |  |  |

| Storage Temperature Range             | -65°C to +150°C                         |  |  |

| Junction Temperature                  | 150℃                                    |  |  |

| Lead Temperature Range                | JEDEC J-STD-20                          |  |  |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

### 熱抵抗

$\theta_{1A}$ は最悪の条件、すなわち回路ボードに表面実装パッケージを ハンダ付けした状態で規定しています。

表7. 熱抵抗

| Package Type        | $\theta_{\text{JA}}$ | $\theta_{\text{JC}}$ | Unit |

|---------------------|----------------------|----------------------|------|

| 10-Lead MSOP        | 200                  | 44                   | °C/W |

| 10-Lead QFN (LFCSP) | 43.4                 | 6.5                  | °C/W |

## ESDに関する注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスで高エネルギーの静電放電が発生した場合、損傷を生じる可能性があります。性能劣化や機能低下を防止するため、ESDに対して適切な予防措置をとることが推奨されます。

REV. A -7-

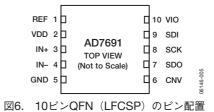

# ピン配置とピン機能の説明

図5. 10ピンMSOPのピン配置

### 表8. ピン機能の説明

| <br>ピン番号 | 記号  | タイプ1 | 説明                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | REF | AI   | リファレンス電圧入力。REFの範囲は0.5V~VDDです。GNDピンを基準とします。このピンは、ピンの近くで10μFコンデンサを使ってGNDにデカップリングする必要があります。                                                                                                                                                                                                                                                                               |

| 2        | VDD | P    | 電源                                                                                                                                                                                                                                                                                                                                                                     |

| 3        | IN+ | AI   | 正側差動アナログ入力。 $IN-$ ピンを基準とします。 $IN+$ ピンの入力範囲は $V_{REF}/2$ を中心する $0\sim V_{REF}$ で、 $IN-$ ピンに対して $180$ 度位相がずれている必要があります。                                                                                                                                                                                                                                                  |

| 4        | IN- | AI   | 負側差動アナログ入力。 $IN+$ ピンを基準とします。 $IN-$ ピンの入力範囲は $V_{REF}/2$ を中心する $0\sim V_{REF}$ で、 $IN+$ ピンに対して $180$ 度位相がずれている必要があります。                                                                                                                                                                                                                                                  |

| 5        | GND | P    | 電源グラウンド                                                                                                                                                                                                                                                                                                                                                                |

| 6        | CNV | DI   | 変換入力。この入力には複数の機能があります。入力信号の立上がりエッジで、変換を開始し、デバイスのインターフェース・モード(チェーン・モードまたは $\overline{CS}$ モード)を選択します。 $\overline{CS}$ モードでは、このピンがローレベルのとき $\overline{SDO}$ ピンがイネーブルされます。チェーン・モードでは、 $\overline{CNV}$ がハイレベルのときにデータを読み出す必要があります。                                                                                                                                         |

| 7        | SDO | DO   | シリアル・データ出力。変換結果がこのピンに出力されます。SCKに同期します。                                                                                                                                                                                                                                                                                                                                 |

| 8        | SCK | DI   | シリアル・データ・クロック入力。デバイスが選択されると、変換結果がこのクロックによってシフト出力されます。                                                                                                                                                                                                                                                                                                                  |

| 9        | SDI | DI   | シリアル・データ入力。この入力には複数の機能があります。次のように、ADCのインターフェース・モードを選択します。 CNVの立上がりエッジでSDIがローレベルの場合、チェーン・モードが選択されます。このモードでは、1本のSDOラインに接続された複数のADCの変換結果をデイジーチェーン接続できます。SDIのデジタル・データ・レベルは、SCKの18周期分の遅延でSDO上に出力されます。 CNVの立上がりエッジでSDIがハイレベルの場合、 $\overline{\text{CS}}$ モードが選択されます。このモードでは、SDIまたはCNVのいずれかがローレベルのときにシリアル出力信号をイネーブルすることができます。変換完了時にSDIまたはCNVがローレベルのときは、BUSYインジケータ機能がイネーブルされます。 |

| 10       | VIO | P    | 入出力インターフェースのデジタル電源。ホスト・インターフェース電源(1.8V、2.5V、3V、5V)と同じ公称電圧。                                                                                                                                                                                                                                                                                                             |

<sup>|</sup> と同じ公称電圧。 | AI=アナログ入力、DI=デジタル入力、DO=デジタル出力、P=電源

─8 ─ REV. A

# 代表的な性能特性

図7. 積分非直線性 対 コード、2.5V

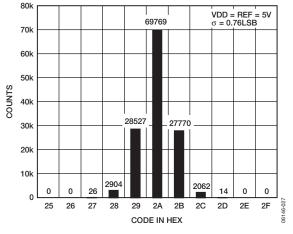

図8. コード中央でのDC入力のヒストグラム、5V

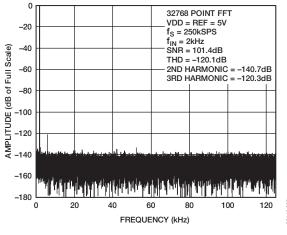

図9. 2kHz FFTプロット、5V

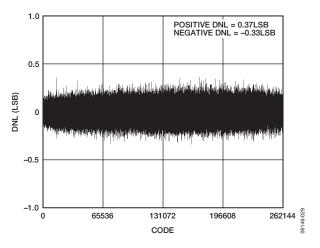

図10. 微分非直線性 対 コード、5V

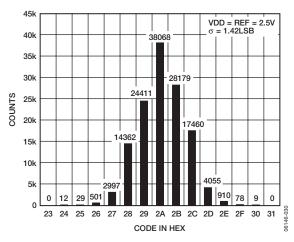

図11. コード中央でのDC入力のヒストグラム、2.5V

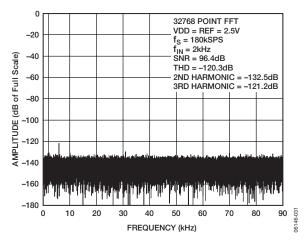

図12. 2kHz FFTプロット、2.5V

REV. A — 9 —

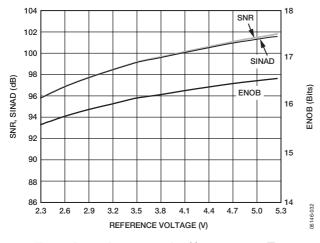

図13. SNR、SINAD、ENOB 対 リファレンス電圧

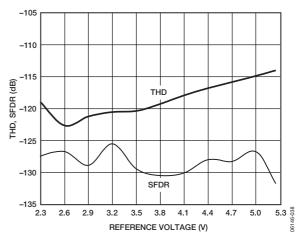

図16. THD、SFDR 対 リファレンス電圧

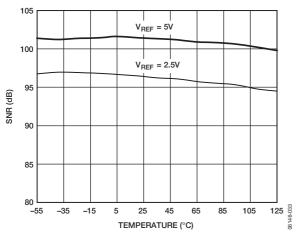

図14. SNRの温度特性

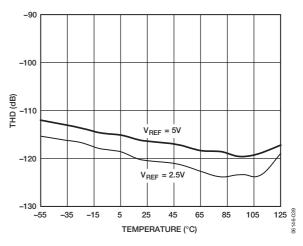

図17. THDの温度特性

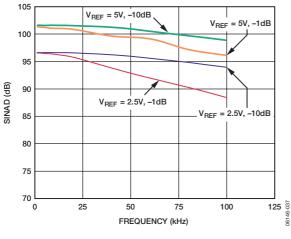

図15. SINADの周波数特性

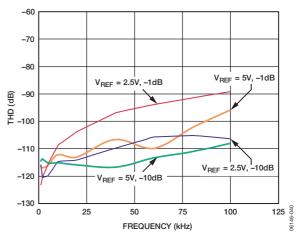

図18. THDの周波数特性

— 10 — REV. A

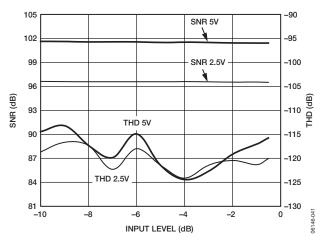

図19. SNR、THD 対 入力レベル

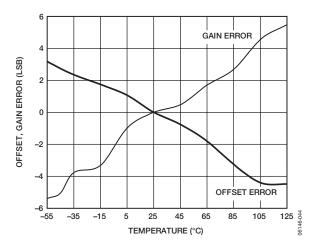

図22. ゼロ誤差、ゲイン誤差の温度特性

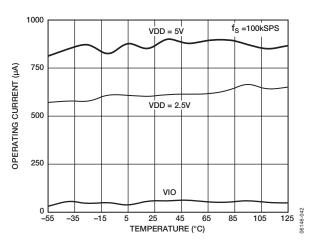

図20. 動作電流の温度特性

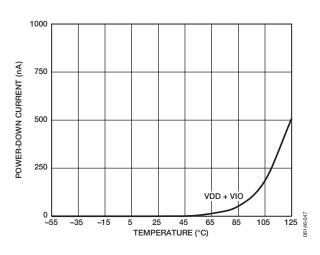

図23. パワーダウン電流の温度特性

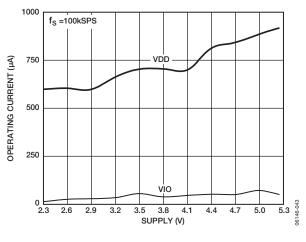

図21. 動作電流 対 電源

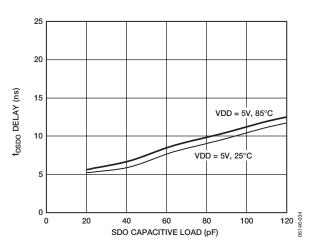

図24. t<sub>DSDO</sub>遅延 対 容量付加および電源

REV. A — 11 —

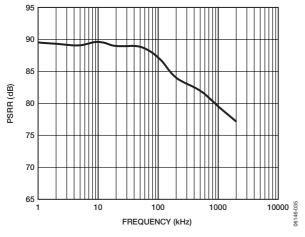

図25. PSSRの周波数特性

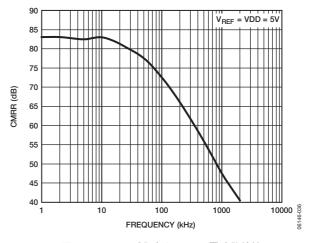

図26. アナログ入力CMRRの周波数特性

# 用語の説明

#### 最下位ビット(LSB)

最下位ビット、つまりLSBは、コンバータにより示される最小のインクリメントです。Nビットの分解能を持つADCでは、ボルト単位で表したLSBは次のとおりです。

$$LSB(V) = \frac{V_{INpp}}{2^{N}}$$

#### 積分非直線性誤差 (INL)

直線性誤差とは、負側フルスケールと正側フルスケールを結ぶ 直線と実際の各コード出力との差を意味します。負側フルス ケールとして使用するポイントは、最初のコード遷移より 0.5LSBだけ下に存在します。正側フルスケールは、最後の コード遷移より1.5LSB高いレベルと定義されます。偏差は各 コードの中央と真の直線との距離として測定されます(図28を 参照)。

#### 微分非直線性誤差(DNL)

理想的なADCでは、各コード遷移は1LSBだけ離れた位置で発生します。微分非直線性とは、この理論値からの最大偏差のことです。通常は、ノー・ミスコードが保証される分解能として規定されることもあります。

#### ゼロ誤差

理想的なミッドスケール入力電圧 (OV) と、ミッドスケール出力コード (OLSB) を発生する実際の電圧との差をいいます。

#### ゲイン誤差

最初の遷移(100…00から100…01)は、公称負側フルスケールより0.5LSB高いアナログ電圧で発生します( $\pm 5$ V範囲では-4.999981V)。最後の遷移(011…10から011…11)は、公称正側フルスケールより1.5LSB低いアナログ電圧で発生します( $\pm 5$ V範囲では+4.999943V)。ゲイン誤差は、最後の遷移の実際のレベルと最初の遷移の実際のレベルとの差と、対応する理論値間の差との偏差をLSB数またはフルスケール範囲のパーセント値で表します。

#### スプリアスフリー・ダイナミック・レンジ (SFDR)

入力信号のRMS振幅値とピーク・スプリアス信号のRMS値との差を意味し、dB値で表します。

#### 有効ビット数(ENOB)

サイン波を入力したときの分解能の測定値であり、ビット数で表します。SINADとの関係は次式で表すことができます。

$ENOB = (SINAD_{dB} - 1.76)/6.02$

#### ノイズフリーのコード分解能

これを超えると個々のコードを分解できなくなるビット数。これは次式で求められます。

*Noise-Free Code Resolution*= $log_2(2^N/Peak-to-Peak Noise)$

#### 有効分解能

これは次式で求められ、ビット数で表します。

Effective Resolution =  $log_2(2^N/RMS Input Noise)$

#### 全高調波歪み (THD)

最初の5つの高調波成分のRMS値の総和と、フルスケール入力信号のRMS値との比であり、dB値で表します。

#### ダイナミック・レンジ

フルスケールのRMS値と、入力を短絡して測定したRMSノイズとの比で、dB値で表します。

#### S/N比 (SNR)

実際の入力信号のRMS値と、ナイキスト周波数より下の全スペクトル成分のRMS値総和から高調波成分とDC成分を除いた値との比で、dB値で表します。

#### 信号/ノイズ十歪みの比(SINAD)

実際の入力信号のRMS値と、ナイキスト周波数より下の全スペクトル成分のRMS値総和(DC以外の高調波成分を含む)との比であり、dB値で表します。

#### アパーチャ遅延

アクイジション性能を表し、CNV入力の立下がりエッジから、 入力信号が変換用にホールドされるまでの時間として測定され ます。

### 過渡応答

フルスケールのステップ関数が与えられてから、ADCが入力を 正常に受け取るまでに要する時間です。

REV. A — 13 —

# 動作原理

回路の説明

AD7691は、逐次比較型アーキテクチャを採用した、高速、低消費電力、単電源、高精度の18ビットADCです。

AD7691は、毎秒250,000サンプル(250kSPS)の変換が可能で、変換と変換の間はパワーダウンします。たとえば、1kSPSで動作する場合は消費電力が $50\mu$ Wとなり、バッテリ駆動のアプリケーションに最適です。

AD7691はトラック&ホールドを内蔵し、パイプライン遅延やレイテンシはなく、多チャンネルを多重化するアプリケーションにとって理想的な製品です。

$2.3 \sim 5.25$ V電源で仕様規定されており、 $1.8 \sim 5$ Vの任意のデジタル・ロジック・ファミリーにインターフェースできます。10ピンMSOPまたは省スペースと柔軟な構成を実現する小型のQFN (LFCSP) で提供されます。

18ビットAD7690、16ビットAD7687、AD7688とピン互換性があります。

#### コンバータの動作

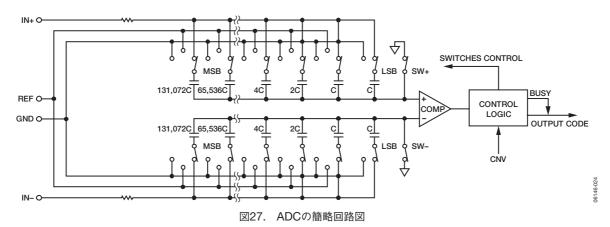

AD7691は、電荷再配分式DACをベースにした逐次比較型ADCです。図27にADCの簡略回路を示します。この容量性DACは、2進数の重みを持った18個のコンデンサで構成される2列の同じアレイを備えています。各アレイはコンパレータの2つの入力に接続されています。

アクイジション・フェーズでは、コンパレータの入力に接続さ れたアレイの端子は、SW+とSW-を経由してGNDに接続さ れます。すべての独立したスイッチはアナログ入力に接続され ます。したがって、コンデンサ・アレイはサンプリング・コン デンサとして使用され、IN+とIN-入力でアナログ信号を取り 込みます。アクイジション・フェーズが完了してCNV入力がハ イレベルになると、変換フェーズが開始されます。変換フェー ズが開始されると、まずSW+とSW-が開きます。次に、2つ のコンデンサ・アレイが入力から切り離されて、GND入力に 接続されます。したがって、アクイジション・フェーズの終わ りに取り込まれた入力IN+とIN-の間の差動電圧がコンパレー タ入力に接続され、コンパレータの平衡が失われます。コンデ ンサ・アレイの各エレメントをGNDとREFの間でスイッチン グすることにより、コンパレータ入力を2進数重みの電圧ス テップ  $(V_{REF}/2, V_{REF}/4...V_{REF}/262,144)$  で変化させます。制 御口ジックがこれらのスイッチをトグルして (MSBから開始)、 コンパレータを再度平衡状態にします。この処理が終了すると、 制御ロジックがADC出力コードとBUSY信号インジケータを発生します。

AD7691は変換クロックを内蔵しているため、変換処理の際にシリアル・クロック(SCK)は不要です。

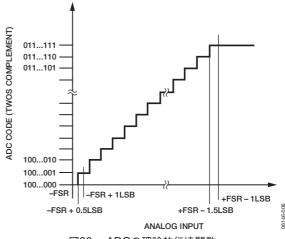

#### 伝達関数

AD7691の理論伝達特性を図28と表9に示します。

図28. ADCの理論的伝達関数

表9. 出力コードと入力電圧の理論値

| Description      | Analog Input<br>V <sub>REF</sub> = 5 V | Digital Output<br>Code (Hex) |

|------------------|----------------------------------------|------------------------------|

| FSR – 1 LSB      | +4.999962 V                            | 0x2FFFF¹                     |

| Midscale + 1 LSB | +38.15 μV                              | 0x00001                      |

| Midscale         | 0 V                                    | 0x00000                      |

| Midscale – 1 LSB | -38.15 μV                              | 0x3FFFF                      |

| -FSR + 1 LSB     | -4.999962 V                            | 0x20001                      |

| -FSR             | -5 V                                   | 0x20000 <sup>2</sup>         |

$<sup>^1</sup>$  アナログ入力範囲より上のコードでもあります( $V_{REF}{\sim}V_{GND}$ より上の $V_{IN+}{\sim}V_{IN-}$ )。

— 14 — REV. A

$<sup>^2</sup>$  アナログ入力範囲より下のコードでもあります( $V_{GND}$ より下の $V_{IN^+}{\sim}V_{IN^-}$ )。

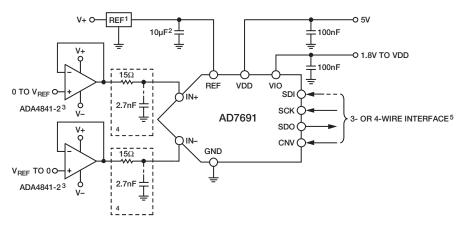

### 代表的な接続図

図29に、複数の電源を使用した場合の推奨接続図の例を示します。

- 1 SEE VOLTAGE REFERENCE INPUT SECTION FOR REFERENCE SELECTION.

- <sup>2</sup>C<sub>REF</sub> IS USUALLY A 10μF CERAMIC CAPACITOR (X5R).

<sup>3</sup>SEE TABLE 9 FOR ADDITIONAL RECOMMENDED AMPLIFIERS.

- <sup>4</sup>OPTIONAL FILTER. SEE ANALOG INPUT SECTION.

- <sup>5</sup>SEE THE DIGITAL INTERFACE SECTION FOR MOST CONVENIENT INTERFACE MODE.

図29. 複数の電源を使用した代表的なアプリケーション

### アナログ入力

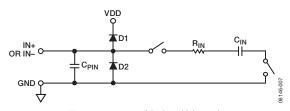

図30に、AD7691の入力構造の等価回路を示します。

ダイオードD1とD2は、アナログ入力IN+とIN-のESD保護用 です。アナログ入力信号が電源レールより0.3V以上高くならな いように注意してください。これらのダイオードが順方向にバ イアスされて、電流が流れてしまうためです。ダイオードは、 最大130mAの順方向バイアス電流を処理できます。たとえば、 この状態は入力バッファ (U1) の電源がVDDと異なるときに 発生します。このような場合、短絡回路の電流制限機能を持つ 入力バッファなどを使ってデバイスを保護できます。

図30. アナログ入力の等価回路

このアナログ入力構造を使うと、IN+とIN-との間の真の差動 信号のサンプリングが可能になります。このような差動入力を 使用することにより、両入力の同相信号が除去されます。

アクイジション・フェーズでは、アナログ入力 (IN+、IN-) のインピーダンスは、 $R_{IN}$ と $C_{IN}$ の直列接続回路とコンデンサ  $C_{PIN}$ との並列組み合わせとしてモデル化できます。 $C_{PIN}$ は主に ピン容量です。 $R_{IN}$ は $3k\Omega$ (typ)で、直列抵抗とスイッチのオ ン抵抗で構成されます。 $C_{IN}$ は30pF(typ)で、主にADCサン プリング・コンデンサです。

スイッチが開いている変換フェーズでは、入力インピーダンス は $C_{PIN}$ に制限されます。 $R_{IN}$ と $C_{IN}$ で単極ローパス・フィルタが 構成されるので、折返しが除去されて、ノイズが制限されま

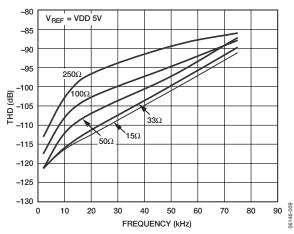

駆動回路のソース・インピーダンスが小さい場合は、AD7691 を直接駆動できます。ソース・インピーダンスが大きい場合は、 AC性能、特に全高調波歪み (THD) が大きな影響を受けます。 DC性能は、入力インピーダンスの影響をあまり受けません。 最大ソース・インピーダンスは、許容可能なTHDの値によって 異なります。

THDは、ソース・インピーダンスと最大入力周波数の関数とし て低下します (図31)。

図31. THD 対 アナログ入力周波数およびソース抵抗

REV. A **— 15 —**

#### ドライバ・アンプの選択

AD7691の駆動は簡単ですが、ドライバ・アンプは次の条件を満たす必要があります。

• AD7691のS/N比と過渡ノイズ性能を維持するため、ドライバ・アンプによるノイズをできるだけ低く抑える必要があります。ドライバから発生するノイズは、AD7691アナログ入力回路の $R_{\rm IN}$ と $C_{\rm IN}$ から構成される単極ローパス・フィルタまたは外付けフィルタ(使用した場合)によって除去されます。アンプに起因するS/N比の劣化は、次のとおりです。

$SNR_{LOSS} =$

$$20 \log \left( \frac{V_{NADC}}{\sqrt{V_{NADC}^2 + \frac{\pi}{2} f_{-3\text{dB}} (Ne_{N+})^2 + \frac{\pi}{2} f_{-3\text{dB}} (Ne_{N-})^2}} \right)$$

ここで、

$V_{NADC}$ は、 $\mu$ V単位で表したADCのノイズであり、次式で表すことができます。

$$V_{NADC} = \frac{\frac{V_{INpp}}{2\sqrt{2}}}{\frac{SNR}{10^{\frac{SNR}{20}}}}$$

$f_{-3\text{dB}}$ はAD7691のMHzで表した入力帯域幅(2MHz)、すなわち入力フィルタのカットオフ周波数(使用した場合)。

Nは、アンプのノイズ・ゲイン(たとえば、バッファ構成では 1)。

$e_{N+}$ と $e_N$ は、IN+とIN-に接続されたオペアンプの等価入力ノイズ電圧密度であり、単位は $nV/\sqrt{Hz}$ です。この近似は、アンプ周りの抵抗が小さいときに使用できます。大きな抵抗を使用する場合には、ノイズ寄与率は2乗和平方根になります。

- ACアプリケーションの場合、ドライバはAD7691に見合う THD性能を持つ必要があります。

- 多チャンネルを多重化するアプリケーションの場合、ドライバ・アンプとAD7691アナログ入力回路は共に、コンデンサ・アレイのフルスケール・ステップに対して18ビット・レベル (0.0004%、4ppm) でセトリングする必要があります。アンプのデータシートでは、一般に0.1~0.01%でのセトリングが規定されています。しかし、これは18ビット・レベルでのセトリング時間とは大幅に異なることがあるため、ドライバを選択する前に確認する必要があります。

表10. 推奨ドライバ・アンプ

| Amplifier         | Typical Application                                        |  |  |  |

|-------------------|------------------------------------------------------------|--|--|--|

| ADA4941-1         | Very low noise, low power single-ended-to-<br>differential |  |  |  |

| ADA4841-x         | Very low noise, small, and low power                       |  |  |  |

| AD8655            | 5 V single supply, low noise                               |  |  |  |

| AD8021            | Very low noise and high frequency                          |  |  |  |

| AD8022            | Low noise and high frequency                               |  |  |  |

| OP184             | Low power, low noise, and low frequency                    |  |  |  |

| AD8605,<br>AD8615 | 5 V single supply, low power                               |  |  |  |

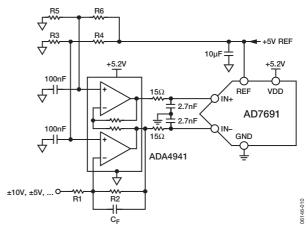

### シングルエンド/差動変換ドライバ

シングルエンド・アナログ信号(ユニポーラまたはバイポーラ)を使用するアプリケーションでは、シングルエンド/差動変換ドライバADA4941-1により、デバイスへの差動入力が可能となります。図32に回路図を示します。

図32. シングルエンド/差動変換ドライバ回路

R1とR2は、入力範囲とADC範囲( $V_{REF}$ )との間の減衰比を設定するときに使います。R1、R2、 $C_F$ は、入力抵抗、信号帯域幅、折り返し除去機能、およびノイズ寄与率に応じて選択します。たとえば、 $4k\Omega$ インピーダンスで $\pm 10V$ の範囲の場合は、R2= $1k\Omega$ 、R1= $4k\Omega$ とします。

R3とR4はADCのIN-入力上のコモンモードの設定に、R5とR6はIN+上のコモンモードの設定に、それぞれ使います。コモンモードは、 $V_{REF}/2$ に近い値に設定する必要があります。ただし、単電源が必要な場合は、 $V_{REF}/2$ よりいくらか大きな値に設定してADA4941-1の出力段にヘッドルームを与えることができます。たとえば、単電源で±10Vの範囲の場合は、R3=8.45k $\Omega$ 、R4=11.8k $\Omega$ 、R5=10.5k $\Omega$ 、R6=9.76k $\Omega$ とします。

#### リファレンス電圧入力

AD7691のリファレンス電圧入力REFは、動的入力インピーダンスを持っています。したがって、REFピンとGNDピンとの間を効果的にデカップリングした低インピーダンス源で駆動する必要があります(「レイアウト」を参照)。

REFを超低インピーダンス源(AD8031またはAD805を使用 するリファレンス・バッファなど)で駆動する場合、 $10\mu$ F (X5R、0805サイズ)のセラミック・チップ・コンデンサでデカップリングを行えば最適な性能を得ることができます。

バッファなしのリファレンス電圧を使用する場合、デカップリング値は使用するリファレンスに依存します。たとえば、低温度ドリフトのADR43xリファレンスを使用する場合は、 $22\mu$ F(X5R、1206サイズ)のセラミック・チップ・コンデンサを使って最適な性能を得ることができます。

必要に応じて、 $2.2\mu$ Fまで小さくした小さなリファレンス・デカップリング・コンデンサ値を使って、性能、特にDNLへの影響を最小限に抑えることができます。

この場合、REFピンとGNDピンとの間に小さなセラミック・デカップリング・コンデンサ(100nFなど)を追加する必要はありません。

#### 雷源

AD7691では、コア電源VDDとデジタル入出力インターフェース電源VIOの2種類の電源ピンを使用しています。VIOでは、1.8V~VDDの任意のロジックに直接インターフェースできます。所要電源数を減らすため、VIOとVDDピンを相互に接続できます。AD7691は、VIOとVDDの間の電源シーケンスに依存しません。また、図25に示すように、広い周波数範囲で電源変動に対して安定しています。

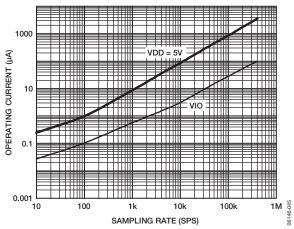

AD7691は各変換フェーズの終わりで自動的にパワーダウンするため、消費電力はサンプリング・レートに比例します。したがって、このデバイスは低サンプリング・レート(場合によっては数ヘルツ)と低消費電力のバッテリ駆動アプリケーションに最適です。

図33. サンプリング・レート 対 動作電流

### リファレンス電圧からADCへの電源供給

簡素なアプリケーションの場合は、図34に示すように、動作電流の小さいAD7691にリファレンス回路から直接電源を供給できます。リファレンス・ラインは次の電源で駆動できます。

- システム電源(直接駆動)

- ADR43xなど、十分な電流出力能力を持つリファレンス電

- AD8031などのリファレンス・バッファ。図34に示すように、 これはシステム電源をフィルタすることもできます。

図34. アプリケーション回路の一例

### デジタル・インターフェース

AD7691のピン数は少ないですが、シリアル・インターフェース・モードが柔軟性を提供します。

CSモードの場合、AD7691はSPI、QSPI、デジタル・ホスト、DSP (Blackfin® ADSP-BF53x、ADSP-219xなど)と互換性があります。このモードでは、3線式または4線式のインターフェースを使用できます。CNV、SCK、SDO信号を使用する3線式インターフェースは、配線接続が最小限に抑えられるので、絶縁アプリケーションなどに適しています。SDI、CNV、SCK、SDO信号を使用する4線式インターフェースの場合は、変換を開始するCNV信号を読出しタイミング(SDI)と無関係に使用できます。これは、低ジッタ・サンプリングや同時サンプリングなどのアプリケーションに有用です。

チェーン・モードではデイジーチェーン機能を使用できます。この場合は、SDI入力を使って、シフト・レジスタに似た1本のデータ・ライン上で複数のADCをカスケード接続することができます。

デバイスがどのモードで動作するかは、CNV立上がりエッジが発生したときのSDIレベルで決まります。SDIがハイレベルのときは $\overline{CS}$ モードが選択され、SDIがローレベルのときはチェーン・モードが選択されます。SDIとCNVを接続してSDIのホールド時間を決めるときには、チェーン・モードが選択されます。

いずれのモードでも、データビットの前にスタート・ビットを 挿入するオプションがあります。このスタート・ビットは BUSY信号インジケータとして使用でき、デジタル・ホストに 割込みをかけてデータの読出しをトリガできます。BUSYイン ジケータを使用しない場合は、読出し前に最大変換時間が経過 するまで待つ必要があります。

BUSYインジケータ機能は次の場合にイネーブルされます。

- チェーン・モードでは、CNVの立上がりエッジでSCKがハイレベルのとき(図46を参照)。

REV. A — 17 —

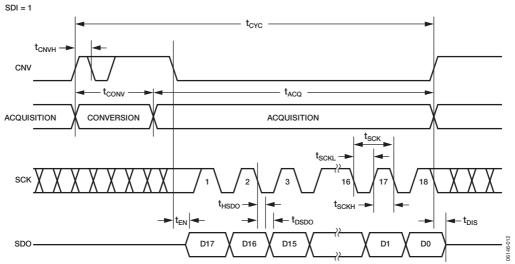

# BUSYインジケータを使用しない3線式CS モード

このモードは通常、1個のAD7691をSPI互換のデジタル・ホストに接続しているときに使用します。図35に接続図を、図36に対応するタイミングを示します。

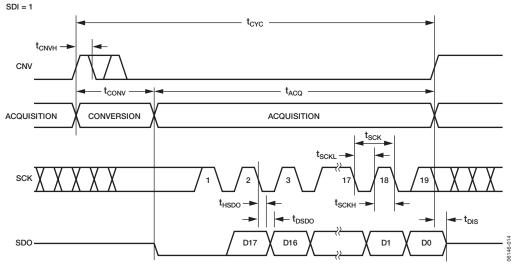

SDIをVIOに接続している場合、CNVの立上がりエッジで変換が開始され、CSモードが選択されて、SDOが高インピーダンスになります。高インピーダンス状態はCNVの状態に関わりなく変換処理が完了するまで維持されます。これは、CNVをローレベルにして他のSPIデバイス(アナログ・マルチプレクサなど)を選択する場合などに有用です。ただし、CNVは最小変換時間が経過する前にハイレベルに戻り、最大変換可能時間の間ハイレベルを維持して、BUSY信号インジケータの発生を防止する必要があります。変換が完了すると、AD7691はアクイジション・フェーズに入り、パワーダウンします。CNVがローレベルになると、MSBがSDOに出力されます。残りのデータビットは後続のSCK立下がりエッジでクロック出力されます。

データはSCKの両エッジで有効です。立上がりエッジでデータを取り込むことはできますが、デジタル・ホストはSCKの立下がりエッジを使ってより高速な読出しレートを実現できます(ただしホールド時間が許容できる場合)。SCKの18番目の立下がりエッジの後またはCNVがハイレベルになるときのいずれか早いほうで、SDOが高インピーダンス状態に戻ります。

図35. BUSYインジケータを使用しない3線式 $\overline{CS}$ モードの接続図(SDIハイレベル)

図36. BUSYインジケータを使用しない3線式OSモードのシリアル・インターフェース・タイミング (SDIハイレベル)

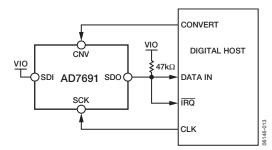

# BUSYインジケータを使用する3線式CSモード

このモードは通常、1個のAD7691を、割込み入力を持つSPI互換のデジタル・ホストに接続しするときに使用します。

図37に接続図を、図38に対応するタイミングを示します。

SDIをVIOに接続している場合、CNVの立上がりエッジで変換 が開始され、 $\overline{\text{CS}}$ モードが選択されて、 $\overline{\text{SDO}}$ が高インピーダン スになります。高インピーダンス状態はCNVの状態に関わりな く変換処理が完了するまで維持されます。最小変換時間の前に CNVを使って他のSPIデバイス(アナログ・マルチプレクサな ど)を選択できますが、最小変換時間が経過する前にローレベ ルに戻って最大変換可能時間の間ローレベルを維持し、BUSY 信号インジケータが確実に発生されるようにする必要がありま す。変換が完了すると、SDOは高インピーダンスから低イン ピーダンスになります。SDOラインをプルアップしてこの変化 を割込み信号として使用し、デジタル・ホストにより制御され るデータ読出しを開始できます。この後、AD7691はアクイジ ション・フェーズに入り、パワーダウンします。データビット は、後続のSCK立下がりエッジでMSBファーストでクロック 出力されます。データはSCKの両エッジで有効です。立上がり エッジでデータを取り込むことはできますが、デジタル・ホス

トはSCKの立下がりエッジを使ってより高速な読出しレートを 実現できます(ホールド時間が許容される場合)。オプション の19番目のSCK立下がりエッジの後またはCNVがハイレベル になるときのいずれか早いほうで、SDOが高インピーダンス状態に戻ります。

複数のAD7691が同時に選択された場合、SDO出力ピンは損傷 やラッチアップの問題を引き起こすことなくこの競合を処理し ます。余分な電力消費を防ぐため、この競合はできるだけ短時 間に抑えることを推奨します。

図37. BUSYインジケータを使用しない3線式CSモードの 接続図(SDIハイレベル)

図38. BUSYインジケータを使用する3線式 $\overline{\text{CS}}$ モードのシリアル・インターフェース・タイミング(SDIハイレベル)

REV. A — 19 —

# BUSYインジケータを使用しない4線式CS モード

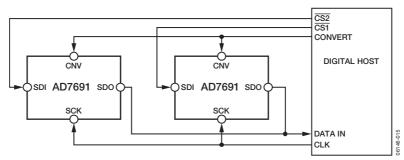

このモードは通常、複数のAD7691をSPI互換のデジタル・ホストに接続するときに使用します。

図39に2個のAD7691を使用した接続回路の例を、図40に対応 するタイミングを示します。

SDIがハイレベルの場合、CNVの立上がりエッジで変換が開始され、CSモードが選択されて、SDOが高インピーダンスになります。このモードでは、変換フェーズとその後のデータ読出し時にCNVをハイレベルに維持します。(SDIとCNVがローレベルの場合は、SDOがローレベルに駆動されます。)最小変換時間の前にSDIを使って他のSPIデバイス(アナログ・マルチプレクサなど)を選択できますが、SDIは最小変換時間が経過

する前にハイレベルに戻り、最大変換可能時間の間ハイレベルを維持して、BUSY信号インジケータの発生を防止する必要があります。変換が完了すると、AD7691はアクイジション・フェーズに入り、パワーダウンします。各ADCの処理結果は、SDI入力をローレベルにして読み出すことができます。SDI入力がローレベルになると、MSBがSDOに出力されます。残りのデータビットは後続のSCK立下がりエッジでクロック出力されます。データはSCKの両エッジで有効です。立上がりエッジでデータを取り込むことはできますが、デジタル・ホストはSCKの立下がりエッジを使ってより高速な読出しレートを実現できます(ホールド時間が許容される場合)。SCKの18番目の立下がりエッジの後またはCNVがハイレベルになるときのいずれか早いほうで、SDOが高インピーダンス状態に戻ります。その結果、もう一方のAD7691の読出しが可能となります。

図39. BUSYインジケータを使用しない4線式CSモードの接続図

— 20 — REV. A

# BUSYインジケータを使用する4線式CSモード

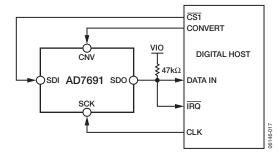

このモードは通常、1個のAD7691を、割込み入力を持つSPI互換のデジタル・ホストに接続するときに使います。アナログ入力のサンプリングに使用するCNVは、データ読出し選択用の信号に依存しないようにする必要があります。この条件は、CNVで低ジッタが要求されるアプリケーションにとって特に重要です。

図41に接続図を、図42に対応するタイミングを示します。

SDIがハイレベルの場合、CNVの立上がりエッジで変換が開始され、CSモードが選択されて、SDOが高インピーダンスになります。このモードでは、変換フェーズとその後のデータ読出し時にCNVをハイレベルに維持します。(SDIとCNVがローレベルの場合は、SDOがローレベルに駆動されます。)最小変換時間の前にSDIを使って他のSPIデバイス(アナログ・マルチプレクサなど)を選択できますが、SDIは最小変換時間が経過する前にローレベルに戻り、最大変換可能時間の間ローレベルを維持して、BUSY信号インジケータが確実に発生されるようにする必要があります。変換が完了すると、SDOは高インピーダンスから低インピーダンスになります。SDOラインをプルアップしてこの遷移を割込み信号として使用し、デジタル・ホストにより制御されるデータ読出しを開始できます。この後、

AD7691はアクイジション・フェーズに入り、パワーダウンします。データビットは、後続のSCK立下がりエッジでMSBファーストでクロック出力されます。データはSCKの両エッジで有効です。立上がりエッジでデータを取り込むことはできますが、デジタル・ホストはSCKの立下がりエッジを使ってより高速な読出しレートを実現することができます(ホールド時間が許容される場合)。オプションの19番目のSCK立下がりエッジの後またはSDIがハイレベルになるときのいずれか早いほうで、SDOが高インピーダンス状態に戻ります。

図41. BUSYインジケータを使用する4線式CSモードの接続図

図42. BUSYインジケータを使用する4線式CSモードのシリアル・インターフェース・タイミング

REV. A — 21 —

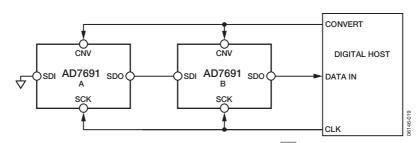

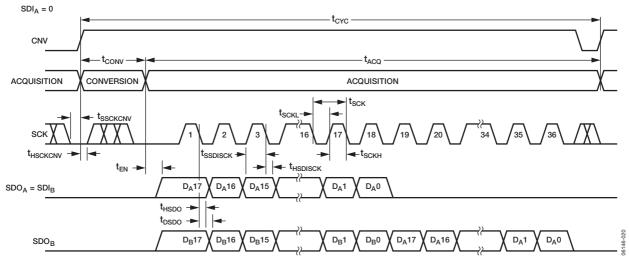

## BUSYインジケータを使用しないチェーン・ モード

このモードでは、3線式シリアル・インターフェースで複数のAD7691をデイジーチェーン接続できます。この機能は、絶縁型マルチコンバータ・アプリケーション、インターフェース能力が小さいシステムなどで部品数や接続配線数を最小限にしたい場合に役立ちます。データ読出しは、シフト・レジスタのクロック駆動に似ています。

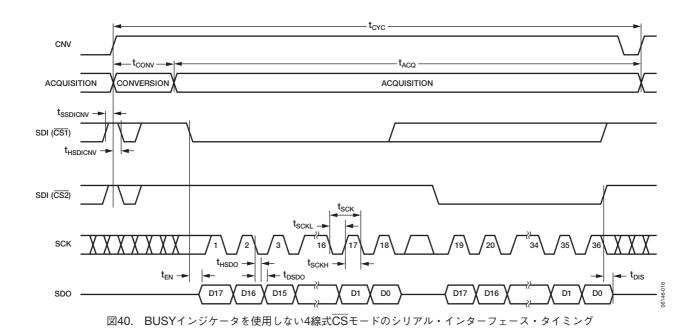

図43に2個のAD7691の接続例を、図44に対応するタイミングを示します。

SDIとCNVがローレベルの場合、SDOはローレベルに駆動されます。SCKがローレベルの場合、CNVの立上がりエッジで変換が開始され、チェーン・モードが選択されて、BUSYインジケータがディスエーブルされます。このモードでは、変換

フェーズとその後のデータ読出し時にCNVをハイレベルに維持します。変換が完了すると、MSBがSDOに出力され、AD7691はアクイジション・フェーズに入り、パワーダウンします。内部シフト・レジスタに格納されている残りのデータビットは、後続のSCK立下がりエッジでクロック出力されます。各ADCでは、内部シフト・レジスタにSDIから入力され、SCKの立下がりエッジでクロック出力されます。チェーン接続された各ADCは、MSBファーストでデータを出力します。N個のADCを読み出すには18×Nクロックが必要となります。データはSCKの両エッジで有効です。立上がりエッジでデータを取り込むことはできますが、SCKの立下がりエッジを使用するデジタル・ホストではより高速な読出しレート、すなわちより多くのAD7691のチェーン接続を実現できます(ホールド時間が許容できる場合)。最大変換レートは、全読出し時間の長さによって低下する場合があります。

図43. BUSYインジケータを使用しない4線式CSモードの接続図

図44. BUSYインジケータを使用しないチェーン・モードのシリアル・インターフェース・タイミング

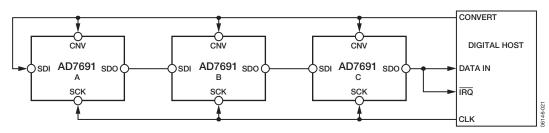

### BUSYインジケータを使用するチェーン・ モード

このモードでは、3線式シリアル・インターフェースで複数のAD7691をデイジーチェーン接続すると同時に、BUSYインジケータも使用できます。この機能は、絶縁型マルチコンバータ・アプリケーション、インターフェース能力の小さいシステムなどで部品数や接続配線数を最小限にしたい場合に役立ちます。データ読出しは、シフト・レジスタのクロック駆動に似ています。

図45に3個のAD7691の接続例を、図46に対応するタイミングを示します。

SDIとCNVがローレベルの場合、SDOはローレベルに駆動されます。SCKがハイレベルの場合、CNVの立上がりエッジで変換が開始され、チェーン・モードが選択されて、BUSYインジケータ機能がイネーブルされます。このモードでは、変換フェーズとその後のデータ読出し時にCNVをハイレベルに維持

します。チェーン接続されたすべてのADCで変換が完了すると、 デジタル・ホスト側に最も近いADC(図45、CのAD7691)の SDOピンがハイに駆動されます。SDOのこの変化をBUSYイン ジケータとして使用し、デジタル・ホストで制御されるデータ 読出しを開始できます。この後、AD7691はアクイジション・ フェーズに入り、パワーダウンします。内部シフト・レジスタ に格納されたデータビットは、後続のSCK立下がりエッジで MSBファーストでクロック出力されます。各ADCでは、内部 シフト・レジスタにSDIから入力され、SCKの立下がりエッジ でクロック出力されます。チェーン接続された各ADCは、 MSBファーストでデータを出力します。N個のADCを読み出 すには18×N+1のクロックが必要となります。立上がりエッ ジでデータを取り込むことはできますが、SCKの立下がりエッ ジを使用するデジタル・ホストではより高速な読出しレート、 すなわちより多くのAD7691のチェーン接続を実現できます (ホールド時間が許容できる場合)。

図45. BUSYインジケータを使用するチェーン・モードの接続図

図46. BUSYインジケータを使用するチェーン・モードのシリアル・インターフェース・タイミング

REV. A — 23 —

# アプリケーションでの注意事項

#### レイアウト

AD7691を実装するプリント回路ボードは、アナログ部とデジタル部を分離し、ボード内でそれぞれをまとめて配置するように設計してください。AD7691では、全アナログ信号をボードの左側で、全デジタル信号を右側で扱うように配置されているため、この作業が容易に行えます。

AD7691の下のアナログ・グラウンド・プレーンをシールドとして使用しない場合は、チップにノイズが混入するのを防ぐため、デバイスの真下にデジタル・ラインを配置しないでください。CNVやクロックなどの高速スイッチング信号は、アナログ信号パスの近くを通過しないようにします。また、デジタル信号とアナログ信号は交差しないようにしてください。

グラウンド・プレーンは複数使用します。デジタル部とアナログ部で共用することもできますが、別々に使用することもできます。後者の場合、プレーンをAD7691の下で接続してください。

AD7691のリファレンス電圧入力REFは、動的入力インピーダンスを持っているため、最小の寄生インダクタンスでデカップリングする必要があります。これを行う場合は、デカップリング用セラミック・コンデンサを、電源ピンREFとGNDの近くに、理想的にはこれらのピンのすぐ隣に配置して、それを幅広い低インピーダンス・パターンに接続します。

AD7691の電源VDDとVIOは、セラミック・コンデンサ100nF (typ) でデカップリングします。コンデンサはAD7691の近くに配置し、短い太いパターンで接続して低インピーダンス・パスを構成し、電源ライン上のグリッチによる影響を削減してください。

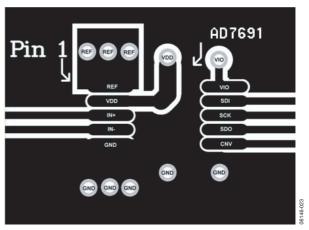

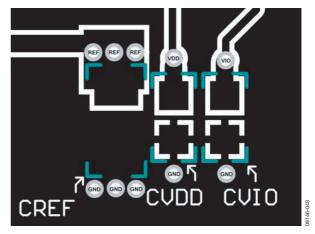

これらの規則に従ったレイアウトの一例を図47と図48に示します。

### AD7691の性能評価

AD7691の他の推奨レイアウトの概要は、AD7691評価用ボードのドキュメント(EVAL-AD7691-CBZ)に示してあります。評価用ボードのパッケージには、組立およびテスト済みの評価用ボード、ドキュメント、それにEVAL-CONTROL BRD3Zを介してPCからボードを制御するソフトウェアが同梱されています。

図47. AD7691のレイアウト例(上部レイヤ)

図48. D7691のレイアウト例(下部レイヤ)

— 24 — REV. A

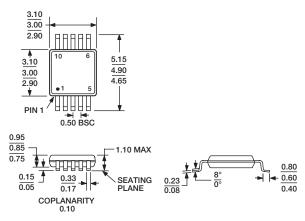

# 外形寸法

COMPLIANT TO JEDEC STANDARDS MO-187-BA

図49. 10ピン・ミニ・スモール・アウトライン・パッケージ [MSOP] (RM-10)

寸法単位:mm

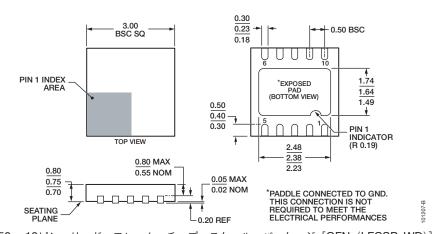

図50. 10ピン・リード・フレーム・チップ・スケール・パッケージ [QFN (LFCSP\_WD)]

3mm×3mmボディ、極薄、デュアル・リード

(CP-10-9)

寸法単位:mm

## オーダー・ガイド

| Model                              | Temperature Range | Package Description    | Package Option | Branding | Ordering Quantity |

|------------------------------------|-------------------|------------------------|----------------|----------|-------------------|

| AD7691BCPZRL <sup>1</sup>          | -40°C to +85°C    | 10-Lead QFN (LFCSP_WD) | CP-10-9        | C4E      | Reel, 5,000       |

| AD7691BCPZRL71                     | -40°C to +85°C    | 10-Lead QFN (LFCSP_WD) | CP-10-9        | C4E      | Reel, 1,500       |

| AD7691BRMZ <sup>1</sup>            | -40°C to +85°C    | 10-Lead MSOP           | RM-10          | C4E      | Tube, 50          |

| AD7691BRMZ-RL71                    | -40°C to +85°C    | 10-Lead MSOP           | RM-10          | C4E      | Reel, 1,000       |

| EVAL-AD7691CBZ <sup>1</sup>        |                   | Evaluation Board       |                |          |                   |

| EVAL-CONTROL BRD2Z <sup>1, 2</sup> |                   | Controller Board       |                |          |                   |

| EVAL-CONTROL BRD3Z <sup>1,2</sup>  |                   | Controller Board       |                |          |                   |

REV. A -25-