# 高温度動作、16 ビット、 600 kSPS PulSAR® ADC

データシート AD7981

特長

超高温度動作:

仕様温度範囲:-55℃~+175℃

高性能

ノーミッシング・コードが保証された 16 ビット分解能 待ち時間/パイプライン遅延のない 600kSPS スループット

SNR: 1 kHz の入力周波数で 91 dB(typ) THD: 1 kHz の入力周波数で-102 dB(typ) INL: ±2.0LSB(max) DNL: ±0.9LSB(max)

低消費電力:

600 kSPS で 2.25mW(typ)(VDD のみ) 600 kSPS で 4.65 mW(typ)(合計)

10kSPS で 70μW(typ)

•小型フットプリント

10 ピン、3 mm × 5 mm、単一金属ワイヤボンディング MSOP

擬似差動アナログ入力範囲

0 V~VREF (VREF は 2.4~5.1V)

使いやすさ

1.8 V/2.5 V/3 V/5 V ロジック・インターフェースで 2.5V 単 電源で動作

SPI-/QSP-/MICROWIRE-/DSP 互換デジタル・インターフェース

複数 ADC のディジーチェーン接続と BUSY 表示

アプリケーション

地下穴掘削と地下穴用計測器

航空電子機器

重工業用機器

高温度環境下でのモニタリング

概要

AD7981<sup>1</sup> は、高温度動作用に設計された 16 ビット、逐次比較型のアナログ・デジテル・コンバータ (ADC)です。 AD7981 は、単電源 VDD で低消費電力を維持しながら最大 600 kSPS のサンプリング・レートが可能です。高速スループット、高精度、高温度で動作する逐次比較型(SAR)ADCで、汎用シリアル・ポート・インターフェース(SPI)を備え、小型パッケージに収容されていいます。

AD7981 は、CNV の立ち上がりエッジで、グラウンドセンス (IN-) に対してアナログ入力信号 IN+(0V~REF)をサンプリングします。リファレンス電圧(REF)は、外部から与えられ、電源電圧(VDD)とは独立に設定できます。AD7981 の消費電力は、スループットに正比例します。

また、SPI 互換シリアル・インターフェースは、SDI 入力を使用して1つの3線式バス上に複数のADCをディジーチェーン1米国特許 No. 6,703,961 により保護されています。

代表的なアプリケーション回路

42.

接続する機能を備え、またオプションとして BUSY を表示することができます。別電源 VIO を使って、 $1.8\,V$ 、 $2.5\,V$ 、 $3\,V$ 、または $5\,V$  ロジックとインターフェースすることができます。

スペースに制約のあるアプリケーションのために、AD7981 は、10 ピン、ミニ・スモールアウトラインパッケージ(MSOP) を採用し、-55℃~+175℃の動作仕様となっています。このパッケージは、超高温度でもたえられるように設計されており、単一金属ワイヤボンディングを採用し、最高温度定格で最大1000時間の動作試験が行われています。

AD7981 は、アナログ・デバイセズ社によって提供されている 高温度品質評価製品シリーズの1つです。 現在入手可能な高 温度製品の全製品については、高温度製品リストを参照して ください。また品質評価データは www.analog.com/hightemp.で 入手可能です

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。 仕様は予告なく変更されることがあります。アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗黙的に許諾するものではありません。商標および登録商標は、それぞれの所有者の財産です。

Rev. 0

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200 データシート AD7981

# 目次

| 特長1             | アナログ  |

|-----------------|-------|

| アプリケーション1       | ドライバ  |

| 代表的なアプリケーション回路1 | 電圧リフ  |

| 概要1             | 電源電圧  |

| 改訂履歴2           | デジタル  |

| 仕様3             | CS €- |

| タイミング仕様5        | CS €- |

| 絶対最大定格6         | CS ±− |

| ESD の注意6        | CS €- |

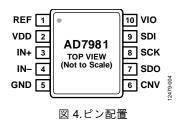

| ピン配置およびピン機能説明7  | チェーン  |

| 代表的な性能特性8       | チェーン  |

| 用語12            | アプリケー |

| 動作原理13          | プリント  |

| 回路説明13          | 外形寸法  |

| 代表的な接続図 14      | オーダー  |

|   | アナログ人刀                           | .15 |

|---|----------------------------------|-----|

|   | ドライバ・アンプの選択                      | 15  |

|   | 電圧リファレンス入力                       | 16  |

|   | 電源電圧                             | 16  |

|   | デジタル・インターフェース                    | .16 |

|   | <u>CS</u> モード 3 線式、BUSY 表示なし     | .17 |

|   | <u>CS</u> モード 3 線式、BUSY 表示あり     | .18 |

|   | <del>CS</del> モード 4 線式、BUSY 表示なし | .19 |

|   | <u>CS</u> モード 4 線式、BUSY 表示あり     | .20 |

|   | チェーン・モード、BUSY 表示なし               | .21 |

|   | チェーン・モード、BUSY 表示あり               | .22 |

| 7 | プリケーション情報                        | 23  |

|   | プリント回路基板(PCB)レイアウト               | .24 |

| 7 | 形寸法                              | 25  |

|   | ナーガー・ガノド                         | 0.5 |

# 改訂履歴

10/14—REVISION 0:初版

# 仕様

特に指定しない限り、VDD=2.5V、VIO = 2.3V  $\sim$  5.5V、V<sub>REF</sub> = 5V、T<sub>A</sub> = -55  $^{\circ}$ C  $\sim$  +175  $^{\circ}$ C

| Parameter                                       | Test Conditions/Comments                          | Min   | Тур         | Max              | Unit             |

|-------------------------------------------------|---------------------------------------------------|-------|-------------|------------------|------------------|

| RESOLUTION                                      |                                                   | 16    |             |                  | Bits             |

| ANALOG INPUT                                    |                                                   |       |             |                  |                  |

| Voltage Range                                   | IN+ - IN-                                         | 0     |             | $V_{\text{REF}}$ | V                |

| Absolute Input Voltage                          | IN+                                               | -0.1  |             | $V_{REF} + 0.1$  | V                |

|                                                 | IN-                                               | -0.1  |             | +0.1             | V                |

| Analog Input Common-Mode Rejection Ratio (CMRR) | $f_{IN} = 100 \text{ kHz}$                        |       | 60          |                  | dB               |

| Leakage Current at 25°C                         | Acquisition phase                                 | 1     |             |                  | nA               |

| Input Impedance                                 |                                                   | See t | he Analog I | nput section     |                  |

| ACCURACY                                        |                                                   |       |             |                  |                  |

| No Missing Codes                                |                                                   | 16    |             |                  | Bits             |

| Differential Nonlinearity                       | $V_{REF} = 5 V$                                   | -0.9  | ±0.4        | +0.9             | LSB1             |

|                                                 | $V_{REF} = 2.5 \text{ V}$                         |       | ±0.5        |                  | LSB <sup>1</sup> |

| Integral Nonlinearity                           | $V_{REF} = 5 V$                                   | -2.0  | $\pm 0.7$   | +2.0             | LSB <sup>1</sup> |

|                                                 | $V_{REF} = 2.5 \text{ V}$                         |       | ±0.6        |                  | LSB <sup>1</sup> |

| Transition Noise                                | $V_{REF} = 5 V$                                   |       | 0.75        |                  | LSB <sup>1</sup> |

|                                                 | $V_{REF} = 2.5 \text{ V}$                         |       | 1.2         |                  | LSB <sup>1</sup> |

| Gain Error <sup>2</sup>                         | T <sub>MIN</sub> to T <sub>MAX</sub>              |       | ±2          |                  | LSB <sup>1</sup> |

| Gain Error Temperature Drift                    |                                                   |       | $\pm 0.35$  |                  | ppm/°            |

| Zero Error <sup>2</sup>                         | T <sub>MIN</sub> to T <sub>MAX</sub>              | -1    | $\pm 0.08$  | +1               | mV               |

| Zero Temperature Drift                          |                                                   |       | 0.45        |                  | ppm/°0           |

| Power Supply Sensitivity                        | $VDD = 2.5 V \pm 5\%$                             |       | $\pm 0.1$   |                  | LSB <sup>1</sup> |

| THROUGHPUT                                      |                                                   |       |             |                  |                  |

| Conversion Rate                                 |                                                   | 0     |             | 600              | kSPS             |

| Transient Response                              | Full-scale step                                   |       |             | 290              | ns               |

| AC ACCURACY <sup>3</sup>                        |                                                   |       |             |                  |                  |

| Dynamic Range                                   | $V_{REF} = 5 V$                                   |       | 92          |                  | dB               |

|                                                 | $V_{REF} = 2.5 \text{ V}$                         |       | 87          |                  | dB               |

| Oversampled Dynamic Range <sup>4</sup>          | OSR = 256                                         |       | 110         |                  | dB               |

| Signal-to-Noise Ratio (SNR)                     | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   | 89    | 91          |                  | dB               |

|                                                 | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}$ |       | 86          |                  | dB               |

| Spurious-Free Dynamic Range (SFDR)              | $f_{IN} = 1 \text{ kHz}$                          | 104   |             |                  | dB               |

| Total Harmonic Distortion (THD)                 | $f_{IN} = 1 \text{ kHz}$                          | -102  |             |                  | dB               |

| Signal-to-Noise-and-Distortion (SINAD)          | $f_{IN} = 1 \text{ kHz}, V_{REF} = 5 \text{ V}$   |       | 90.5        |                  | dB               |

|                                                 | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}$ |       | 85.5        |                  | dB               |

<sup>&</sup>lt;sup>1</sup> LSB=1 ビット。入力範囲が 5 V の場合、1LSB = 76.3μV。

<sup>2 (</sup>用語のセクションを参照)。これらの仕様には、すべての温度範囲の変動が含まれますが、外部リファレンス電圧の変動による影響は含まれません。

3 すべての AC 精度仕様(dB)は、入力フル・スケール範囲(FSR)と呼ばれます。特に指定しない限り、フル・スケールより 0.5 dB 低い入力信号でテストされます。

4 オーバーサンプリングされたダイナミック・レンジは、ADC 出力 FFT で DC から最大 f<sub>8</sub>/(2×OSR)まで測定されたノイズパワー(小入力用)に対するピーク信号パ ワーの比率です。ここで、fsは、ADC サンプル・レート、OSR は、オーバーサンプリング比です。

データシー

# AD7981

特に指定しない限り、VDD=2.5V、VIO = 2.3V  $\sim$  5.5V、V<sub>REF</sub> = 5V、T<sub>A</sub> = -55  $^{\circ}$ C  $\sim$  +175  $^{\circ}$ C

表 2.

| Parameter                          | Test Conditions/Comments                                          | Min                                      | Тур                | Max              | Unit      |

|------------------------------------|-------------------------------------------------------------------|------------------------------------------|--------------------|------------------|-----------|

| REFERENCE                          |                                                                   |                                          |                    |                  |           |

| Voltage Range                      |                                                                   | 2.4                                      |                    | 5.1              | V         |

| Load Current                       | $600 \text{ kSPS}, V_{REF} = 5 \text{ V}$                         |                                          | 330                |                  | μΑ        |

| SAMPLING DYNAMICS                  |                                                                   |                                          |                    |                  |           |

| -3 dB Input Bandwidth              |                                                                   |                                          | 10                 |                  | MHz       |

| Aperture Delay                     | VDD = 2.5 V                                                       |                                          | 2.0                |                  | ns        |

| DIGITAL INPUTS                     |                                                                   |                                          |                    |                  |           |

| Logic Levels                       |                                                                   |                                          |                    |                  |           |

| $V_{\mathrm{IL}}$                  | VIO > 3 V                                                         | -0.3                                     |                    | $0.3 \times VIO$ | V         |

|                                    | VIO ≤ 3 V                                                         | -0.3                                     |                    | $0.1 \times VIO$ | V         |

| $V_{IH}$                           | VIO > 3 V                                                         | $0.7 \times VIO$                         |                    | VIO + 0.3        | V         |

|                                    | VIO ≤ 3 V                                                         | $0.9 \times VIO$                         |                    | VIO + 0.3        | μΑ        |

| $ m I_{IL}$                        |                                                                   | -1                                       |                    | +1               | μΑ        |

| $ m I_{IH}$                        |                                                                   | -1                                       |                    | +1               | μΑ        |

| DIGITAL OUTPUTS                    |                                                                   |                                          |                    |                  |           |

| Data Format                        |                                                                   | S                                        | erial 16 bits stra | aight binary     |           |

| Pipeline Delay                     |                                                                   | Conversion results available immediately |                    |                  |           |

|                                    |                                                                   | a                                        |                    |                  |           |

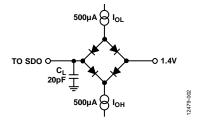

| $V_{OL}$                           | $I_{SINK} = 500 \mu A$                                            |                                          |                    | 0.4              | V         |

| $V_{OH}$                           | $I_{SOURCE} = -500 \mu A$                                         | VIO – 0.3                                |                    |                  | V         |

| POWER SUPPLIES                     |                                                                   |                                          |                    |                  |           |

| VDD                                |                                                                   | 2.375                                    | 2.5                | 2.625            | V         |

| VIO                                | Specified performance                                             | 2.3                                      |                    | 5.5              | V         |

| VIO Range                          |                                                                   | 1.8                                      |                    | 5.5              | V         |

| Standby Current <sup>1, 2</sup>    | VDD and VIO = 2.5 V                                               |                                          | 0.35               |                  | μΑ        |

| Power Dissipation                  | $VDD = 2.625 \text{ V}, V_{REF} = 5 \text{ V}, VIO = 3 \text{ V}$ |                                          |                    |                  |           |

| Total                              | 10 kSPS                                                           |                                          | 70                 |                  | μW        |

|                                    | 600 kSPS                                                          |                                          | 4.65               | 7.0              | mW        |

| VDD Only                           | 600 kSPS                                                          |                                          | 2.25               |                  | mW        |

| REF Only                           | 600 kSPS                                                          |                                          | 1.5                |                  | mW        |

| VIO Only                           | 600 kSPS                                                          |                                          | 0.9                |                  | mW        |

| Energy per Conversion              |                                                                   |                                          | 7.75               |                  | nJ/sample |

| TEMPERATURE RANGE                  |                                                                   |                                          |                    |                  |           |

| Specified Performance <sup>3</sup> | T <sub>MIN</sub> to T <sub>MAX</sub>                              | -55                                      |                    | +175             | °C        |

$<sup>^1</sup>$ 必要に応じてすべてのデジタル入力を VIO または GND に接続。  $^2$  アクイジション・フェーズで。

<sup>3</sup>最高温度定格で最大 1000 時間の動作を認定。

## タイミング仕様

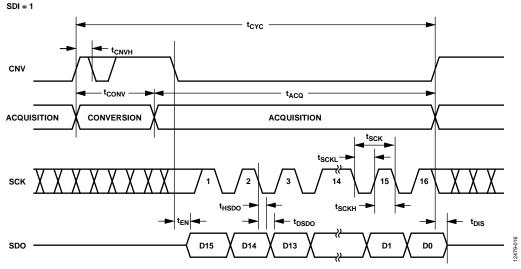

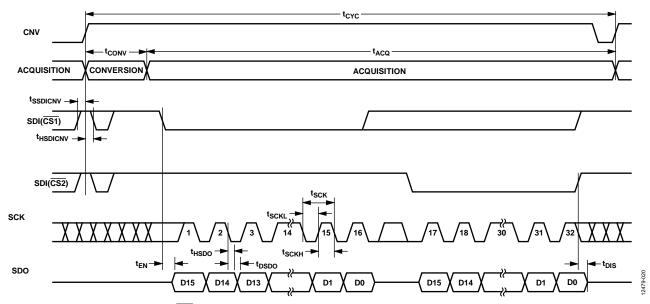

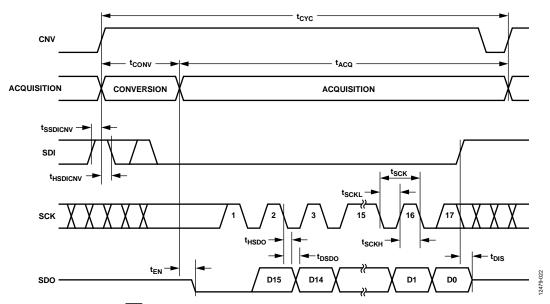

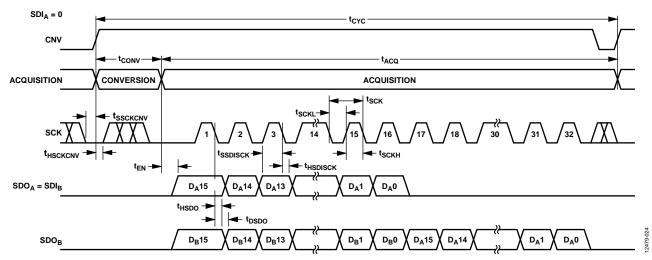

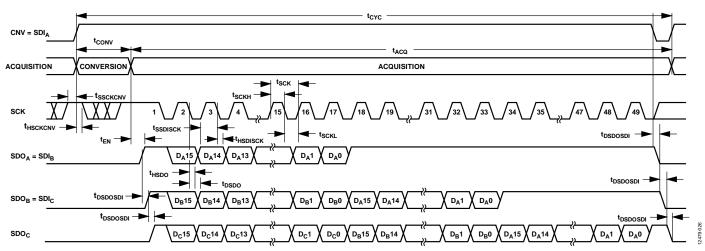

特に指定しない限り、 $T_A = -55$   $\mathbb{C}$   $\sim +175$   $\mathbb{C}$ 、VDD = 2.375  $V \sim 2.625$  V、VIO = 3.3  $V \sim 5.5$  V 詳細については、図 2 と図 3 を参照してください。

# 表 3.

| Parameter                                                                | Symbol               | Min  | Тур | Max | Unit |

|--------------------------------------------------------------------------|----------------------|------|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data Available                       | t <sub>CONV</sub>    | 625  |     | 900 | ns   |

| Acquisition Time                                                         | $t_{ACQ}$            | 290  |     |     | ns   |

| Time Between Conversions                                                 | $t_{CYC}$            | 1667 |     |     | ns   |

| CNV Pulse Width (CS Mode)                                                | $t_{CNVH}$           | 10   |     |     | ns   |

| SCK Period (CS Mode)                                                     | t <sub>SCK</sub>     |      |     |     |      |

| VIO Above 4.5 V                                                          |                      | 10.5 |     |     | ns   |

| VIO Above 3 V                                                            |                      | 12   |     |     | ns   |

| VIO Above 2.7 V                                                          |                      | 13   |     |     | ns   |

| VIO Above 2.3 V                                                          |                      | 15   |     |     | ns   |

| SCK Period (Chain Mode)                                                  | t <sub>SCK</sub>     |      |     |     |      |

| VIO Above 4.5 V                                                          |                      | 11.5 |     |     | ns   |

| VIO Above 3 V                                                            |                      | 13   |     |     | ns   |

| VIO Above 2.7 V                                                          |                      | 14   |     |     | ns   |

| VIO Above 2.3 V                                                          |                      | 16   |     |     | ns   |

| SCK Low Time                                                             | $t_{SCKL}$           | 4.5  |     |     | ns   |

| SCK High Time                                                            | $t_{SCKH}$           | 4.5  |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                   | $t_{ m HSDO}$        | 3    |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                     | $t_{ m DSDO}$        |      |     |     |      |

| VIO Above 4.5 V                                                          |                      |      |     | 9.5 | ns   |

| VIO Above 3 V                                                            |                      |      |     | 11  | ns   |

| VIO Above 2.7 V                                                          |                      |      |     | 12  | ns   |

| VIO Above 2.3 V                                                          |                      |      |     | 14  | ns   |

| CNV or SDI Low to SDO D15 MSB Valid (CS Mode)                            | $t_{EN}$             |      |     |     |      |

| VIO Above 3 V                                                            |                      |      |     | 10  | ns   |

| VIO Above 2.3 V                                                          |                      |      |     | 15  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) | $t_{ m DIS}$         |      |     | 20  | ns   |

| SDI Valid Setup Time from CNV Rising Edge                                | $t_{SSDICNV}$        | 5    |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                       | t <sub>HSDICNV</sub> | 2    |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (Chain Mode)                    | t <sub>HSDICNV</sub> | 0    |     |     | ns   |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                   | t <sub>SSCKCNV</sub> | 5    |     |     | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                    | t <sub>HSCKCNV</sub> | 5    |     |     | ns   |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                  | t <sub>SSDISCK</sub> | 2    |     |     | ns   |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                   | t <sub>HSDISCK</sub> | 3    |     |     | ns   |

| SDI High to SDO High (Chain Mode with Busy Indicator)                    | $t_{DSDOSDI}$        |      |     | 15  | ns   |

図 2.デジタル・インターフェース・タイミングの負荷回路

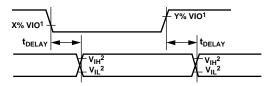

$^1 FOR~VIO \le 3.0V,~X=90~AND~Y=10;~FOR~VIO > 3.0V,~X=70~AND~Y=30.$   $^2 MINIMUM~V_{IH}~AND~MAXIMUM~V_{IL}~USED.~SEE~DIGITAL~INPUTS~SPECIFICATIONS~IN~TABLE~2.$

図 3.タイミング測定の電圧レベル

# 絶対最大定格

### 表 4.

| <u> 衣 4.</u>                       |                                             |

|------------------------------------|---------------------------------------------|

| Parameter                          | Rating                                      |

| Analog Inputs                      |                                             |

| IN+, IN- to GND <sup>1</sup>       | $-0.3 \text{ V to V}_{REF} + 0.3 \text{ V}$ |

|                                    | or ±130 mA                                  |

| Supply Voltage                     |                                             |

| REF, VIO to GND                    | -0.3 V to +6 V                              |

| VDD to GND                         | -0.3 V to +3 V                              |

| VDD to VIO                         | +3 V to −6 V                                |

| Digital Inputs to GND              | -0.3 V to VIO + 0.3 V                       |

| Digital Outputs to GND             | -0.3 V to VIO + 0.3 V                       |

| Storage Temperature Range          | −65°C to +150°C                             |

| Junction Temperature               | 176.4°C                                     |

| Thermal Impedance (10-Lead MSOP)   |                                             |

| $	heta_{ m JA}$                    | 200°C/W                                     |

| $	heta_{ m IC}$                    | 44°C/W                                      |

| Lead Temperature                   |                                             |

| Vapor Phase (60 sec)               | 215°C                                       |

| Infrared (15 sec)                  | 220°C                                       |

| ESD Ratings                        |                                             |

| Human Body Model                   | 2 kV                                        |

| Machine Model                      | 200 V                                       |

| Field-Induced Charged Device Model | 1.25 kV                                     |

<sup>「</sup>アナログ入力のセクションを参照。

上記の絶対最大定格を超えるストレスを加えると製品に恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上での製品動作を定めたものではありません。デバイスを最大動作状態に置くと製品の信頼性に影響を与えます。

## ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

# ピン配置およびピン機能説明

## 表 5.ピン機能の説明

| ピン番号 | 記号  | タイ<br>プ¹ | 説明                                                                                                                                                                                                                                                                                                                          |

|------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | REF | AI       | リファレンス入力電圧。REF 範囲は $2.4V\sim5.1V$ であり、GND ピンを基準にしています。REF はできるだけピンの近くで $10\mu$ F コンデンサによりデカップリングしてください。                                                                                                                                                                                                                     |

| 2    | VDD | P        | 電源                                                                                                                                                                                                                                                                                                                          |

| 3    | IN+ | AI       | アナログ入力。このピンは $IN-$ を基準とします。電圧範囲、たとえば $IN+$ と $IN-$ の差は $0V\sim V_{REF}$ です。                                                                                                                                                                                                                                                 |

| 4    | IN- | AI       | アナログ入力グラウンドセンス。このピンはアナログ・グラウンド・プレーンまたはリモート・センス・グラウンドに接続してください。                                                                                                                                                                                                                                                              |

| 5    | GND | P        | 電源グラウンド。                                                                                                                                                                                                                                                                                                                    |

| 6    | CNV | DI       | 変換入力。この入力は複数の機能を備えています。立ち上がりエッジで、変換が始まり、デバイスのインターフェース・モード、すなわちチェーンまたは CSモードが選択されます。CSモードでは、このピンがロー・レベルのとき SDO ピンがイネーブルされます。チェーン・モードでは、CNV がハイ・レベルのときにデータを読み取ってください。                                                                                                                                                         |

| 7    | SDO | DO       | シリアル・データ出力。変換結果はこのピンに出力されます。SCK に同期しています。                                                                                                                                                                                                                                                                                   |

| 8    | SCK | DI       | シリアル・データ・クロック入力。デバイスが選択されたとき、変換結果がこのクロックでシフトアウトされます。                                                                                                                                                                                                                                                                        |

| 9    | SDI | DI       | シリアル・データ入力。この入力は複数の機能を備えています。これらのビットは、ADCのインターフェース・モードを次のように選択します。                                                                                                                                                                                                                                                          |

|      |     |          | チェーン・モードは、CNV の立ち上がりエッジで SDI がハイ・レベルの場合に選択されます。このモードでは、SDI はデータ入力として使用され、複数の ADC の変換結果を 1本の SDO 線にディジーチェーン接続します。SDI のデジタル・データ・レベルが SDO に出力され、SCK の 16 サイクル分の遅延が加わります。 CNV の立ち上がりエッジ期間で SDI がハイ・レベルの場合は CSモードが選択されます。このモードでは、ロー・レベルのときには、SDI または CNV がシリアル出力信号を有効にします。変換が完了したときに SDI または CNV がロー・レベルの場合、BUSY 表示機能がイネーブルされます。 |

| 10   | VIO | P        | 入出力インターフェースのデジタル電源。通常は、ホストのインターフェース(1.8 V、2.5 V、3 V、5 V)と同じ電源が使われます。                                                                                                                                                                                                                                                        |

<sup>&</sup>lt;sup>1</sup> 1AI =アナログ入力、DI =デジタル入力、DO =デジタル出力、P =電源。

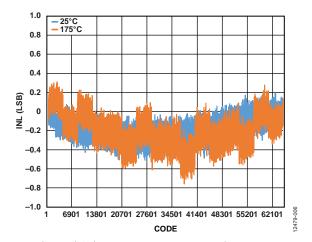

# 代表的な性能特性

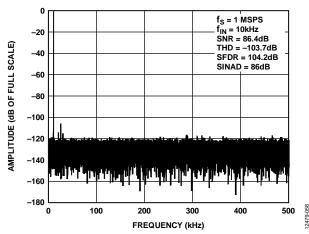

特に指定のない限り、VDD = 2.5 V、V<sub>REF</sub> = 5.0 V、VIO = 3.3 V。

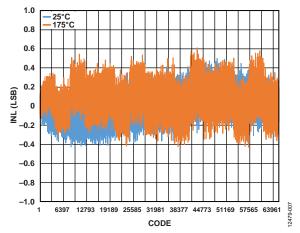

図 5.積分非直線性(INL)対コードおよび温度、V<sub>REF</sub> = 5.0V

図 6.積分非直線性(INL)対コードおよび温度、V<sub>REF</sub> = 2.5 V

0.5 0.4 0.3 0.2 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0 0.1 0

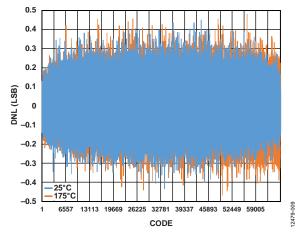

図 8.微分非直線性(DNL) 対コードおよび温度、V<sub>REF</sub> = 5.0 V

図 9.微分非直線性(DNL) 対コードおよび温度、V<sub>REF</sub> = 2.5 V

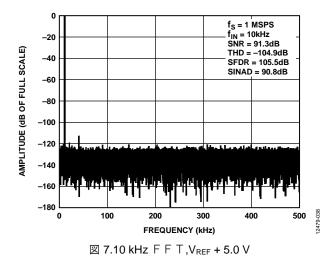

図 10.10 kHz F F T,V<sub>REF</sub> + 2.5 V

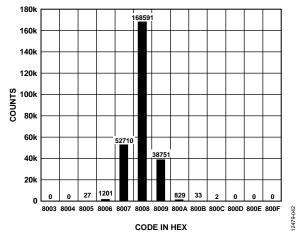

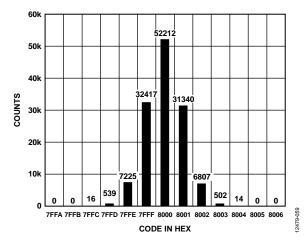

図 11.コード中心での DC 入力のヒストグラム、V<sub>REF</sub> = 5.0V

図 12.コード遷移での DC 入力のヒストグラム、 $V_{REF} = 5.0V$

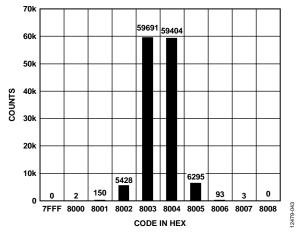

図 13.SINAD および ENOB 対基準電圧(V<sub>REF</sub>)

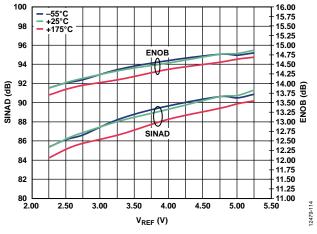

図 14.コード中心での DC 入力のヒストグラム、V<sub>REF</sub> = 2.5 V

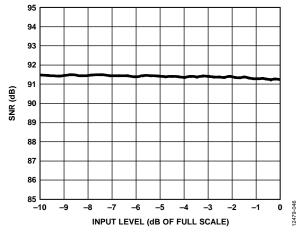

図 15.SNR 対入力レベル

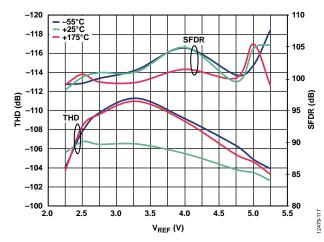

図 16.THD および SFDR 対基準電圧(V<sub>REF</sub>)

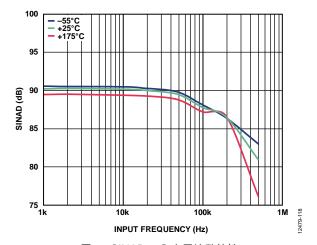

図 17.SINAD の入力周波数特性

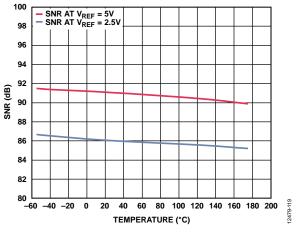

図 18.SHR の温度特性

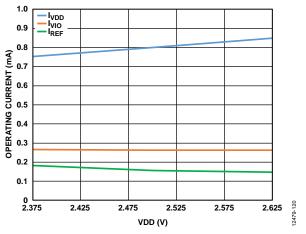

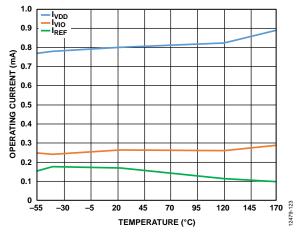

図 19.動作電流対電源電圧(VDD)

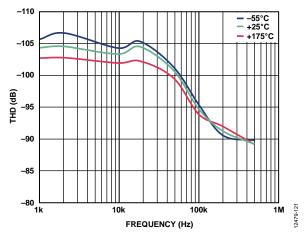

図 20.THD の周波数特性

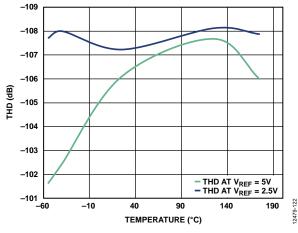

図 21.THD の温度特性

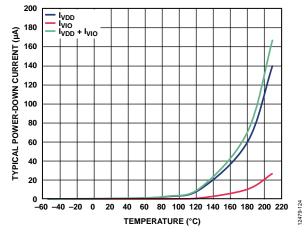

図 22.動作電流の温度特性

図 23.遮断電流の温度特性

# 用語

#### 積分非直線性(INL)

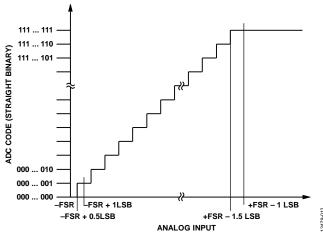

INLは、負側のフル・スケールと正側のフル・スケールを結ぶ直線と実際のコード出力との誤差として定義されます。負側フル・スケールとして使用されるポイントは、最初のコード遷移より½LSBだけ下に存在します。正側フル・スケールは、最後のコード遷移より1½LSBだけ上のレベルと定義されます。偏差は、各コードの中央と直線との間の距離として測定されます(図25を参照)

#### 微分非直線性(DNL)

理想的な ADC では、各コード遷移は 1 LSB だけ離れた位置で発生します。 DNL は、この理想値からの最大偏差を意味します。 微分非直線性は、ノーミス・コードが保証される分解能として規定されることがあります。

#### ゼロ誤差

最初の変化は、アナログ・グラウンドより 1/2 LSB 上のレベルで生じます( $0\sim5$  V の範囲で  $38.1\mu$ V)。オフセット誤差は、そのポイントから実際の変化までの差をいいます。

#### ゲイン誤差

最後の変化(111 ... 10 から 111 ... 11)は、公称フル・スケールより 1½ LSB 低いアナログ電圧で生じます(0 V $\sim$ 5 V の範囲で 4.999886 V)。ゲイン誤差は、オフセットが調整された後の理論レベルと最後の変化の実際レベルとの差のことです。

#### スプリアス・フリー・ダイナミック・レンジ(SFDR)

SFDR は入力信号の rms 振幅値と最大のスプリアス信号との 差を意味し、dB 値で表します。

### 有効ビット数(ENOB)

ENOBは、正弦波を入力したときの分解能の計測値です。 SINADとの関係は次式により示されます。

$ENOB = (SINAD_{dB} - 1.76)/6.02$

ビット数で表されます。

#### ノイズフリー・コード分解能

ノイズフリー・コード分解能は、超えると個々のコードが区別できなくなるビット数です。次式を使って計算されます。

ノイズフリー・コード分解能= log2(2<sup>N</sup>/Peak-to-Peak Noise)

ビット数で表されます。

#### 有効分解能

有効分解能は、次のように計算されます。

有効分解能= log2(2<sup>N</sup>/RMS Input Noise)

ビット数で表されます。

#### 総合高調波歪み(THD)

THDとは、基本波から 5 次高調波成分までの rms 値の総和の、フル・スケール入力信号の rms 値に対する比を意味し、デシベル値で表します。

#### ダイナミック・レンジ

ダイナミック・レンジは、入力を短絡して測定した合計 rms ノイズとフル・スケールの rms 値の比を表します。すべてのノイズ源と DNL アーティファクトを含めるように-60 dBFS の信号で測定されます。ダイナミック・レンジの値は dB で表されます。

## 信号対ノイズ比(SNR)

SNR は、実際の入力信号の rms 値と、ナイキスト周波数より下の全スペクトル成分の rms 値総和(高調波成分と DC 成分を除く)に対する比です。 SNR の値は、dB で表されます。

## 信号対ノイズ+歪み比(SINAD)

SINAD は、実際の入力信号の rms 値と、ナイキスト周波数より下の全スペクトル成分の rms 値総和(DC 以外の高調波を含む)との比です。 SINAD は、rms は、rms で表されます。

#### アパーチャ遅延

アパーチャ遅延は、アクイジション性能を表します。CNV 入力の立ち上がりエッジから入力信号が変換用に保持されまでの時間を表します。

#### 過渡応答

過渡応答は、フル・スケールのステップ関数が入力された後に ADC が正確に入力を取得するまでに要する時間です。

## 動作原理

## 回路説明

AD7981 は、単電源動作の逐次比較型アーキテクチャを採用した高速高精度低消費電力 16 ビット A/D コンバータ(ADC)です。

AD7981 は、毎秒 600,000 個のサンプル(600 kSPS)を変換でき、変換と変換の間にパワーダウンします。たとえば、10 k SPS動作時の消費電力が  $70\mu\text{W}$  (typ)であるため、バッテリ駆動のアプリケーションに最適です。

AD7981 は、トラック&ホールドを内蔵し、パイプライン遅延またはレイテンシがないため、マルチプレクスされた複数チャンネルのアプリケーションに最適です。

AD7981 は、1.8V~5V デジタル・ロジック・ファミリーに接続することができます。省スペースと柔軟な構成を兼ね備える 10 ピン MSOP に収納されています。

AD7981 は、18 ビットの AD7982 とピン互換です。.**コンバー タの動作**

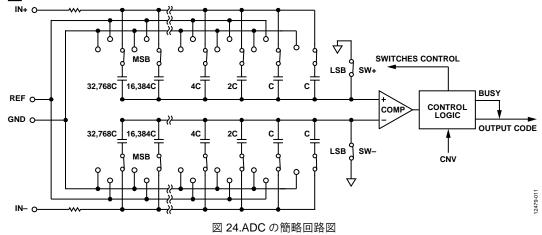

AD7981、電荷再分配型デジタル・アナログ・コンバータ (DAC)をベースとする逐次比較型 A/D コンバータです。 図 24 に、ADC の簡単化した回路図を示します。容量性 DAC は、2 進数の重みを持った 16 個コンデンサで構成される 2 個の同じアレイで構成されており、各アレイは 2 つのコンパレータ入力に接続されています。

アクイジション期間中は、コンパレータ入力に接続されたア レイのピンは、SW+と SW-スイッチを介して GND に接続さ れます。独立したすべてのスイッチはアナログ入力に接続さ れます。したがって、コンデンサ・アレイは、サンプリン グ・コンデンサとして使用されて、IN+入力と IN-入力上のア ナログ信号が取り込まれます。アクイジション・フェーズが 終わると、CNV入力がハイ・レベルになり、変換フェーズが 開始します。変換フェーズが開始すると、先ずSW+とSW-が 開きます。2つのコンデンサ・アレイは、入力から切り離され て、GND入力に接続されます。そのため、アクイジション・ フェーズの終わりに取り込まれた、入力 IN+と IN-の間の差動 電圧がコンパレータ入力に接続されて、コンパレータは平衡 しなくなります。コンデンサ・アレイの各エレメントを GND と REF の間でスイッチングすることにより、コンパレータ入 力を2進数重みの電圧ステップ(VREF/2, VREF/4 ... VREF/65,536). コントロール・ロジックがこれらのスイッチをトグルして (MSB から開始)、コンパレータが再度平衡するようにします。 この処理が終了すると、デバイスはアクイジション・フェーズ に戻り、コントロール・ロジックが ADC 出力コードと BUSY 信号表示を生成します。

AD7981 は、変換クロックを内蔵しているため、変換プロセスのためのシリアル・クロック SCK は不要です。

#### 伝達関数

AD7981 の理論伝達特性を図 25 と表 6 に示します。

図 25.ADC の理想的な伝達関数

#### 表 6.出力コードと理論入力電圧

|              | Analog Input    |                     |  |  |

|--------------|-----------------|---------------------|--|--|

| Description  | $V_{REF} = 5 V$ | Digital Output Code |  |  |

| FSR - 1 LSB  | 4. 999924       | 0xFFFF <sup>1</sup> |  |  |

|              | V               |                     |  |  |

| Midscale + 1 | 2. 500076       | 0x8001              |  |  |

| LSB          | V               |                     |  |  |

| Midscale     | 2.5 V           | 0x8000              |  |  |

| Midscale - 1 | 2. 499924       | 0x7FFF              |  |  |

| LSB          | V               |                     |  |  |

| -FSR + 1 LSB | 76.3 μV         | 0x0001              |  |  |

| -FSR         | 0 V             | $0x0000^2$          |  |  |

$<sup>^1</sup>$ これは、オーバーレンジ・アナログ入力のコードでもあります( $V_{\text{IN-}}$   $-V_{\text{IN-}}$

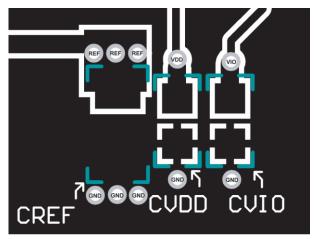

## 代表的な接続図

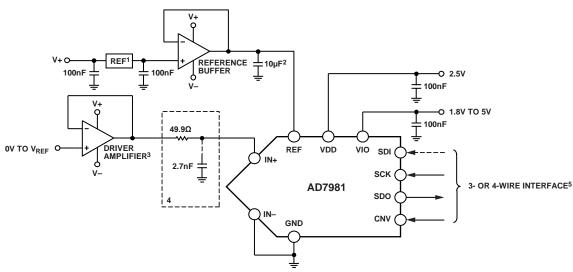

図 26 は、複数の電源が使用可能なときの AD7981 の推奨接続 図の例を示しています。

<sup>1</sup>SEE THE VOLTAGE REFERENCE INPUT SECTION FOR REFERENCE SELECTION.

$^2 C_{REF}$  IS USUALLY A  $10 \mu F$  CERAMIC CAPACITOR (X5R).  $^3 SEE$  THE DRIVER AMPLIFIER CHOICE SECTION.

<sup>4</sup>OPTIONAL FILTER. SEE THE ANALOG INPUT SECTION.

<sup>5</sup>SEE THE DIGITAL INTERFACE FOR THE MOST CONVENIENT INTERFACE MODE.

図 26.複数の電源を使用する代表的アプリケーション図

が  $V_{REF} - V_{CND}$ より高い)。  $^2$ これは、アンダーレンジ・アナログ入力のコードでもあります( $V_{IN+} -$ V<sub>IN-</sub>が V<sub>GND</sub>より低い)。

### アナログ入力

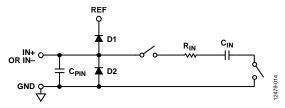

図 27 は、AD7981 のアナログ入力構造の等価回路を示します。

2つのダイオード D1 および D2 は、アナログ入力 IN+および IN-に対する ESD 保護を提供します。ダイオードが順バイアスになって伝導電流が流れるので、アナログ入力信号が電源レールより 0.3V 以上高くならないようにしてください。ラッチアップ試験の際にアナログ入力 IN+および IN-に 10ms のきわめて短時間加わる過渡現象は、ダイオードが、最大 130mA の順バイアス電流に対応できることを示します。たとえば、この状態は、入力バッファ(U1)の電源が VDD と異なるときに発生します。このような場合(たとえば、入力バッファが短絡)、電流制限機能を使用してデバイスを保護することができます。

図 27.等価アナログ入力回路

このアナログ入力構造を使うと、IN+と IN-との間の差動信号のサンプリングが可能になります。この差動入力の採用により、両入力に共存する信号が除去されます。

アクイジション・フェーズでは、アナログ入力(IN+または IN)のインピーダンスは、コンデンサ  $C_{PN}$  と、 $R_{IN}$  および  $C_{IN}$  の直列接続の回路との並列組み合わせとしてモデル化することができます。 $C_{PIN}$  は主にピン容量です。 $R_{PIN}$  は  $400\Omega$  (typ)であり、いくつかの直列抵抗とスイッチのオン抵抗から構成される集中定数です。 $C_{IN}$  は 30 pF(typ)であり、主に ADC サンプリング・コンデンサです。スイッチが開いている変換フェーズでは、入力インピーダンスは  $C_{PIN}$  に制限されます。 $R_{IN}$  と  $C_{IN}$ により、1 次ローパス・フィルタが構成されるため、不要な折り返し効果が削減され、ノイズが制限されます。

駆動回路のソース・インピーダンスが小さい場合は、AD7981 を直接駆動することができます。ソース・インピーダンスが大きい場合には、AC性能、特にTHDが大きい影響を受けます。DC性能は、入力インピーダンスからあまり影響を受けません。最大ソース・インピーダンスは、許容可能なTHDの大きさに依存します。THDは、ソース・インピーダンスと最大入力周波数の関数として性能低下します。

## ドライバ・アンプの選択

AD7981 の駆動は容易ですが、ドライバ・アンプは次の条件を満たさなければなりません。

• AD7981 の SNR 性能と遷移ノイズ性能を維持するには、ドライバ・アンプによって生成されるノイズをできるだけ低く抑える必要があります。ドライバから来るノイズは、 $R_{IN}$ と  $C_{IN}$ で構成された AD7981 アナログ入力回路の1次ローパス・フィルタによって、または外部フィルタ (使用した場合) によってフィルタリングされます。AD7981 のノイズは 47.3 $\mu$ V rms(typ)であるため、アンプに起因する SNR の性能低下は、次式で与えられます。

$$SNR_{LOSS} = 20 \log \left( \frac{47.3}{\sqrt{47.3^2 + \frac{\pi}{2} f_{-3dB} (Ne_N)^2}} \right)$$

ここで、

f-3dB は、AD7981 (10 MHz)の入力帯域幅(MHz)、または 入力フィルタのカットオフ周波数(使用した場合)です。

Nは、アンプのノイズ・ゲイン(たとえば、バッファ構成では 1)。

$e_N$ は、オペアンプの等価入力ノイズ電圧、単位はnV/VHz。

- ACアプリケーションの場合、ドライバはAD7981と釣り合うTHD性能を有する必要があります。

- 多チャンネルをマルチプレクスするアプリケーションの場合、ドライバ・アンプと AD7981 アナログ入力回路は、コンデンサ・アレイへのフル・スケール・ステップに対して16ビット・レベル(0.0015%、15 ppm)でセトリングする必要があります。アンプ・データシートでは、0.1%~0.01%でのセトリング・タイムが、よく指定され、16ビット・レベルでのセトリング・タイムと大幅に異なることがあり、ドライバ選択前に確認されなければなりませか。

AD8634 は、レール・ツー・レール出力、高精度、低消費電力、高温度対応デュアルアンプであり、AD7981 の入力の駆動に推奨されます。

## 電圧リファレンス入力

AD7981 のリファレンス電圧入力 REF は、動的入力インピー ダンスを持っています。このため、REF 入力と GND 入力と の間を効果的にデカップリングした低インピーダンス・ソースから駆動する必要があります(Printed Circuit Board (PCB) Layout の節参照)。

REFが、きわめて低いインピーダンス・ソースによって駆動される場合、セラミック・チップ・コンデンサで最適性能が得られます。AD7981には、高温対応低温ドリフト ADR225 2.5 V リファレンスおよび低消費電力 AD8634 リファレンス・バッファが推奨されます。

REF ピンは、最適性能を得るために少なくとも  $10\mu$ F(X5R、1206 サイズ)のセラミック・チップ・コンデンサでデカップリングされなければなりません。

REF ピンと GND ピンの間に小さい値のセラミック・デカップリング・コンデンサ(たとえば、100 nF)を追加する必要はありません。

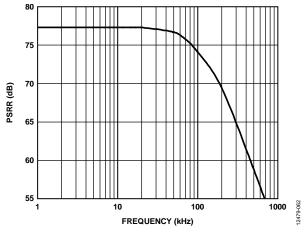

#### 電源電圧

AD7981 は、コア電源 VDD とデジタル入力/出力インターフェース電源 VIO の 2 種類の電源ピンを使用しています。VIO は、1.8V~5V の任意のロジックとの直接インターフェースを可能にします。必要な電源の数を減らすには、VIO と VDD を接続してください。AD7981 は、VIO と VDD の間の電源シーケンスに依存しません。さらに、広い周波数範囲で電源変動に対して安定です(図 28)。

図 28.PSRR の周波数特性

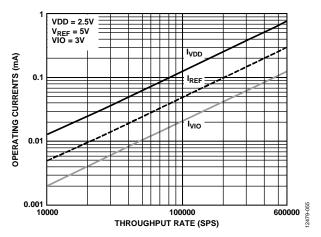

AD7981 は、変換フェーズの終わりに自動的にパワーダウンして、電力がサンプリング・レートと直線的に変化します。これにより、デバイスは、低いサンプリング・レート(数 Hz でも)および低消費電力アプリケーションに理想的です。

図 29.動作電流対スループット・レート

### デジタル・インターフェース

AD7981 のピン数は少ないですが、シリアル・インターフェース・モードで柔軟性を提供します。

AD7981は、CSモードのとき、SPI、QSPI™、MICROWIRE™ およびデジタル・ホストと互換性があります。AD7981インターフェースでは、3線式または4線式インターフェースを使用できます。CNV信号、SCK信号、SDO信号を使用する3線式インターフェースは、配線数が少ないため、たとえば、絶縁型アプリケーションに有用です。SDI信号、CNV信号、SCK信号、SDO信号を使う4線式インターフェースを使用すると、CNV(変換を開始します)をリードバック・タイミング(SDI)に依存しないようにすることができます。4線式インターフェースは、低ジッタ・サンプリング・アプリケーションまたは同時サンプリング・アプリケーションで便利です。

AD7981 をチェーン・モードで使うと、シフトレジスタに似たシングル・データ・ライン上での複数の ADC のカスケード接続に対して、SDI 入力を使うディジーチェーン機能を提供することができます。

デバイスが動作するモードは、CNV の立ち上がりエッジ時の SDI のレベルで決定されます。SDI がハイ・レベルの場合 は、 $\overline{CS}$ モードが選択され、SDI がロー・レベルの時にはチェーン・モードが選択されます。SDI ホールド・タイムは、SDI と CNV がお互いに接続されており、チェーン・モードが選択 される場合です。

いずれのモードでも、AD7981は、データ・ビットの先頭にスタート・ビットを生成するオプションを可能にする柔軟性を提供します。このスタート・ビットをBUSY信号表示と見なして、デジタル・ホストに対して割込みを行い、データの読み出しを開始させることができます。BUSY表示を使わない場合は、リードバックの前に最大変換時間の経過を待たなければなりません。

BUSY表示機能は、次のようにイネーブルされます。

- • CSモードでは、ADC変換が終了したとき CNV または SDI がロー・レベルになったとき(図 33 と図 37 を参照)。

- チェーン・モードでは、CNV立ち上がりエッジ期間に SCKがハイ・レベルになったとき(図 41 参照)。

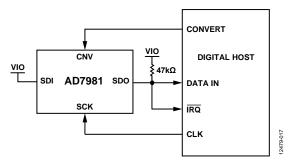

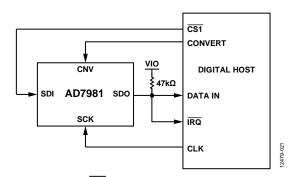

## CS モード 3 線式、BUSY 表示なし

3線式 $\overline{\text{CS}}$ モードBUSY表示なしは、一般に、単一のAD7981 を SPI 互換デジタル・ホストに接続するときに使用されます。図 30に接続図を、図 31に対応するタイミングを、それぞれ示します。

SDIを VIO に接続した状態では、CNV の立ち上がりエッジで変換が開始され、CSモードが選択され、SDO は高インピーダンスになります。変換が開始されたとき、その変換は、CNVの状態にかかわらず完了するまで続きます。CNV の状態を使用すると、たとえば CNV をロー・レベルにしてアナログ・マルチプレクサなどの他の SPI デバイスを選択することができます。ただし、CNV は、BUSY 信号表示の生成を回避するために、最小変換時間が経過する前にハイ・レベルに戻り、

次に最大変換時間の間ハイ・レベルのままでいなければなりません。変換が完了すると、AD7981はアクイジション・フェーズに入りパワーダウンします。

CNV がロー・レベルになると、MSB が SDO に出力されます。 残りのデータ・ビットは、後続の SCK の立ち下がりエッジで 出力されます。データは、SCK の両方のエッジで有効です。 立ち上がりエッジを使ってデータを取込むことができますが、 SCK の立ち下がりエッジを使うデジタル・ホストを使うと、 ホールド・タイムが許容できる限り、より高速な読み出しレートが可能になります。16番目の SCK 立ち下がりエッジの後、 または CNV がハイ・レベルになったときのいずれか早い方で、 SDO は高インピーダンスに戻ります。

図 28.3 線式 CSモード、BUSY 表示なしの接続図 (SDI ハイ)

図 29.3 線式 CSモード、BUSY 表示なしのシリアル・インターフェース・タイミング (SDI ハイ)

## <del>CS</del> モード3線式、BUSY 表示あり

3 線式  $\overline{\text{CS}}$ モード BUSY 表示ありは、一般に、単一の AD7981 を、割り込み入力を有する SPI 互換デジタル・ホストに接続するときに使用されます。図 32 に接続図を、図 33 に対応するタイミングを、それぞれ示します。

SDIを VIOに接続した状態では、CNV の立ち上がりエッジで変換が開始され、CSモードが選択され、SDO は高インピーダンスになります。CNV の状態に無関係に変換が完了するまでSDO は高インピーダンスを維持します。最小変換時間の前に、CNV を使ってアナログ・マルチプレクサのような他の SPI デバイスを選択することができますが、最小変換時間が経過する前に CNV がロー・レベルに戻り、最大変換時間の間ロー・レベルを維持して、BUSY 信号が確実に発生するようにする必要があります。

変換が完了すると、SDO は高インピーダンスから低インピーダンスになります。SDO ラインのプルアップ抵抗により、この

変化を割込み信号として使って、デジタル・ホストにより制御されるデータの読み出しを開始させることができます。その後AD7981はアクイジション・フェーズに入り、パワーダウンします。データ・ビットはMSBを先頭にして、後続のSCKの立ち下がりエッジで出力されます。データは、SCKの両エッジで有効です。立ち上がりエッジを使ってデータを取込むことができますが、SCKの立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、より高速な読み出しレートが可能になります。オプションの17番目のSCK立ち下がりエッジの後、またはCNVがハイ・レベルになったときのいずれか早い方で、SDOは高インピーダンスに戻ります。

複数の AD7981 を同時に選択した場合、SDO 出力ピンは損傷 またはラッチアップなしにこの接続を処理します。余分な電力消費を回避するためこの接続をできるだけ短くすることをお薦めします。

図 30.3 線式 CSモード、BUSY 表示ありの接続図(SDIハイ)

図 31.3 線式 CSモード、BUSY 表示ありのシリアル・インターフェース・タイミング (SDI ハイ)

## CS モード 4 線式、BUSY 表示なし

4線式 CSモード BUSY 表示なしは、一般に、複数の AD7981 を SPI 互換デジタル・ホストに接続するときに使用されます。 2 つの AD7981 デバイスを使用する接続図の例を図 34 に示し、対応するタイミングを図 35 に示します。

SDI がハイ・レベルの状態で、CNV の立ち上がりエッジで変換が開始され、CSモードが選択され、SDO は高インピーダンスになります。このモードでは、変換フェーズとそれに続くデータ・リードバックの間、CNV をハイ・レベルに維持する必要があります(SDI と CNV がロー・レベルの場合、SDO はロー・レベルに駆動されます)。最小変換時間の前に、SDI を使ってアナログ・マルチプレクサのような他の SPI デバイスを選択することができますが、最小変換時間が経過する前に

SDI がハイ・レベルに戻り、最大変換時間の間ハイ・レベル を維持して、BUSY 信号の発生を防止する必要があります。

変換が完了すると、AD7981 はアクイジション・フェーズに入りパワーダウンします。SDI 入力をロー・レベルにすると、各 ADC の変換結果を読み出すことができ、MSB が SDO へ出力されます。残りのデータ・ビットは、後続の SCK の立ち下がりエッジで出力されます。データは、両 SCK エッジで有効です。立ち上がりエッジを使ってデータを取込むことができますが、SCK の立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、より高速な読み出しレートが可能になります。16番目の SCK 立ち下がりエッジの後、または SDI がハイ・レベルになったときのいずれか早い方で、SDO は高インピーダンスに戻り、もう一方のAD7981 を読み出すことができるようになります。

図 32.4 線式 CSモード、BUSY 表示なしの接続図

図 33.4 線式 CSモード、BUSY 表示なしのシリアル・インターフェース・タイミング

## CS モード 4 線式、BUSY 表示あり

4線式 CSモード、BUSY 表示ありは、一般に、単一のAD7981を、割り込み入力を有するSPI 互換デジタル・ホストに接続するときに使用されます。データ読み取りの選択に使用される信号にかかわらず、アナログ入力をサンプリングするために使用されるCNV を維持しなければなりません。この条件は、CNV のジッタが小さいことが要求されるアプリケーションで特に重要です。

図 36 に接続図を、図 37 に対応するタイミングを、それぞれ示します。

SDI がハイ・レベルの状態で、CNV の立ち上がりエッジで変換が開始され、CSモードが選択され、SDO は高インピーダンスになります。このモードでは、変換フェーズとそれに続くデータ・リードバックの間、CNV をハイ・レベルに維持しなくてはなりません(SDI と CNV がロー・レベルの場合、SDOはロー・レベルに駆動されます)。最小変換時間の前に、CNVを使ってアナログ・マルチプレクサのような他の SPI デバイ

スを選択することができますが、最小変換時間が経過する前に SDI がロー・レベルに戻り、最大変換時間の間ロー・レベルを維持して、BUSY 信号が確実に発生するようにする必要があります。変換が完了すると、SDO は高インピーダンスからロー・レベルになります。

SDO ライン上のプルアップ抵抗によって、この変化を割込み信号として使って、デジタル・ホストにより制御されるデータのリードバックを開始させることができます。次に、AD7981 はアクイジション・フェーズに入り、パワーダウンします。データ・ビットは MSB を先頭にして、後続の SCKの立ち下がりエッジで出力されます。データは、両 SCK エッジで有効です。立ち上がりエッジを使ってデータを取込むことができますが、SCK の立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、より高速な読み出しレートが可能になります。オプションの 17番目の SCK 立ち下がりエッジの後、または SDI がハイ・レベルになったときのいずれか早い方で、SDO は高インピーダンスに戻ります。

図 34.4 線式 CSモード、BUSY 表示ありの接続図

図 35.4 線式  $\overline{\text{CS}}$ モード、BUSY 表示ありのシリアル・インターフェース・タイミング

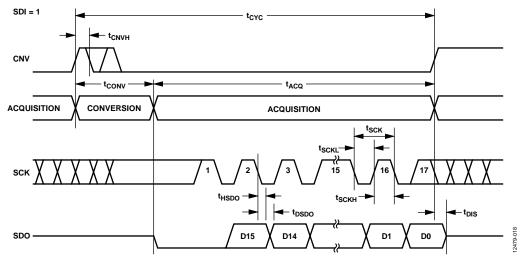

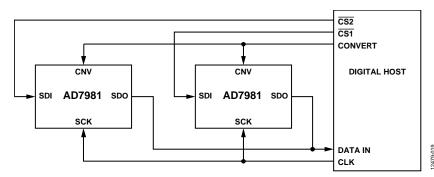

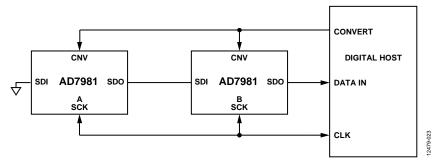

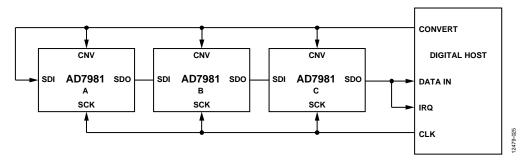

## チェーン・モード、BUSY 表示なし

BUSY表示器なしのチェーン・モードを使用して、3線式シリアル・インターフェース上の複数のAD7981デバイスをディジーチェーン接続することができます。この機能は部品数と接続配線数の削減に役立ちます。たとえば、絶縁された複数のコンバータを使用するアプリケーションまたはインターフェース能力が制限されているシステムではこの接続が使用されます。データのリードバックは、シフトレジスタをクロック駆動するのに似ています。

2 つの AD7981 デバイスを使用する接続図例が図 38 に示され、 対応するタイミングが図 39 に示されています。

SDIと CNV をロー・レベルにすると、SDO がロー・レベルに 駆動されます。SCK がロー・レベルのとき、CNV の立ち上が りエッジで変換が開始され、チェーン・モードが選択され、 BUSY 表示がディスエーブルされます。このモードでは、変 換フェーズとそれに続くデータ・リードバックの間、CNV が ハイ・レベルに維持されます。変換が完了すると、MSBが SDOに出力され、AD7981はアクイジション・フェーズに入りパワーダウンします。内部シフトレジスタに保存されている残りのデータ・ビットは、後続の SCK の立ち下がりエッジで出力されます。各 ADCで、SDIが内部シフトレジスタの入力に接続され、SCK の立ち下がりエッジでクロック駆動されます。チェーン内の各 ADCはデータの MSBを先頭に出力し、N個の ADCをリードバックするためには 16×N個のクロックが必要です。データは、両 SCK エッジで有効です。立ち上がりエッジを使ってデータを取込むことができますが、SCK の立ち下がりエッジを使うデジタル・ホストを使うと、ホールド・タイムが許容できる限り、より高速な読み出しレートが可能になり、かつチェーン内の AD7981デバイスの数を増やすことができます。合計リードバック時間により、最大変換レートは低減されます。

図 36.4 線式モード、BUSY 表示なしの接続図

図 37.4 線式モード、BUSY 表示なしのシリアル・インターフェース・タイミング

## チェーン・モード、BUSY 表示あり

BUSY表示ありのモードでも、3線式シリアル・インターフェースに複数の AD7981 をディジーチェーン接続することができ、同時に BUSY表示も提供できます。この機能は部品数と接続配線数の削減に役立ちます。たとえば、絶縁型の複数コンバータを使用するアプリケーションまたはインターフェース能力が制限されているシステムではこの接続が使用されます。データのリードバックは、シフトレジスタをクロック駆動するのに似ています。

3 つの AD7981 デバイスを使用する接続図例が図 40 に示され、 対応するタイミングが図 41 に示されています。

SDIと CNV をロー・レベルにすると、SDO がロー・レベルに 駆動されます。 SCK がハイ・レベルのとき、CNV の立ち上が りエッジで変換が開始され、チェーン・モードが選択され、 BUSY 表示機能がイネーブルされます。このモードでは、変 換フェーズとそれに続くデータ・リードバックの間、CNV が ハイ・レベルに維持されます。チェーン内のすべての ADC が その変換を完了したとき、デジタル・ホストに最も近い ADC の SDO ピン(図 40 に C と示された AD7981 ADC を参照)が、 ハイ・レベルに駆動されます。SDO上のこの変化を BUSY 表 示として使って、デジタル・ホストから制御されるデータ・ リードバックを開始することができます。次に、AD7981 は アクイジション・フェーズに入り、パワーダウンします。内 部シフトレジスタに保存されているデータ・ビットは、後続 の SCK の立ち下がりエッジで、MSB ファーストで出力され ます。各 ADC で、SDI が内部シフトレジスタの入力に接続さ れ、SCK の立ち下がりエッジでクロック駆動されます。チェ ーン内の各 ADC はデータの MSB を先頭に出力し、N 番目の ADC をリードバックするためには 16×N+1 個のクロックが必 要です。立ち上がりエッジを使ってデータを取込むことがで きますが、SCK の立ち下がりエッジを使うデジタル・ホスト を使うと、ホールド・タイムが許容できる限り、より高速な 読み出しレートが可能になり、かつチェーン内の AD7981 デ バイスの数を増やすことができます。

図 38.チェーン・モード、BUSY 表示ありの接続図

図 39.4 線式モード、BUSY 表示ありのシリアル・インターフェース・タイミング

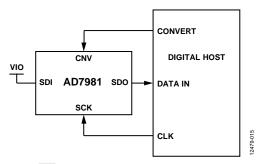

# アプリケーション情報

175℃以上の温度で、確実に動作できる低消費電力電子部品を必要とする工業が増えています。AD7981 は、そのようなタイプのアプリケーション向けに高温度において、センサからプロセッサへの高精度アナログ信号処理を可能にします。

図42は、データ収集装置の単純化した信号チェーンを示します。

地下穴掘削、航空電子や他の過酷な温度環境のアプリケーションでは、周囲の地質学的構成のような情報を収集するために様々なセンサからの信号がサンプリングされます。そのようなセンサは、電極、コイル、圧電素子、または他の変換器の形をとることがあります。加速度計とジャイロスコープは、傾斜、振動、および回転レートに関する情報を提供します。そのようなセンサには、帯域幅がきわめて低いものや、可聴周波

数領域やそれ以上の周波数情報を生成するものもあります。 AD7981 は、電力効率と精度を維持しながら、帯域幅要件の異なるセンサからデータをサンプリングするのには理想的です。 AD7981 はフットプリントが小さいため、地下穴掘削工具では通常きわめて狭いボード幅などのようにスペースに制約があるレイアウトでも、複数のチャネルを容易に含めることができます。さらに、フレキシブルなデジタル・インターフェースによって、要求の多い同時サンプリングアプリケーションが可能であり、また少ないピン数のシステムでのデイジーチェーン・リードバックも容易です。

入手可能な高温度製品の全製品のセレクション・テーブルについては、高温度製品リストを参照してください。またwww.analog.com/hightemp.にて品質評価データの入手可能です。

図 40.単純化したデータ収集システム信号チェーン

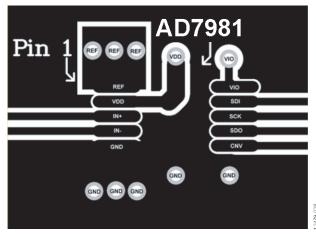

## プリント回路基板(PCB)レイアウト

AD7981 を実装する PCB は、アナログ部とデジタル部を分離して、ボード内でそれぞれをまとめて配置するようにデザインする必要があります。 AD7981 では、すべてのアナログ信号を左側に、すべてのデジタル信号を右側に配置しているため、この作業が容易になります。

AD7981の下のグラウンド・プレーンがシールドして使われてない限り、デジタル・ノイズがチップに結合するため、デジタル・ラインがデバイスの真下を通らないようにしてください。CNVやクロックのような高速スイッチング信号が、アナログ信号経路の近くを絶対に通らないようにしてください。デジタル信号とアナログ信号の交差は回避する必要があります。

少なくとも1つのグラウンド・プレーンを使用してください。 デジタル部とアナログ部に共通または分けて使うことができ ます。グラウンド・プレーンが分離している場合は、AD7981 の下でお互いのプレーンを接続してください。

AD7981 の電圧リファレンス入力 REF は動的入力インピーダンスを持つため、最小の寄生インダクタンスでデカップリングする必要があります。リファレンス・デカップリング・セラミック・コンデンサは、REF ピンと GND ピンの近くに、理想的には直接、幅広い低インピーダンス・トレースによって接続されなければなりません。

AD7981 の電源 VDD と VIO は AD7981 の近くに配置されたセラミック・コンデンサ(一般に 100 nF)によってデカップリングし、低インピーダンス経路を提供する短く幅広いパターンで接続して、電源ライン上のグリッチの影響を軽減します。

これらのルールに則ったレイアウトの例を図 43 と図 44 に示します。

図 43.AD7981 の PCB レイアウト例(最上層)

図 44.AD7981 の PCB レイアウト例(最下層)

479,02

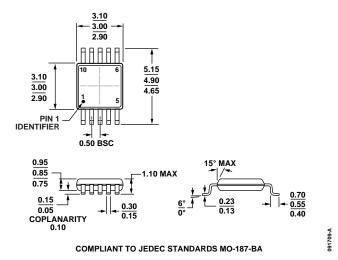

# 外形寸法

図 41.10 ピン・ミニ・スモール・アウトライン・パッケージ[MSOP] (RM-10) 寸法: mm

オーダー・ガイド

| Integral Nonlinearity (INL) |          | Temperature<br>Range | Ordering<br>Quantity | Package Description                | Package<br>Option | Branding |

|-----------------------------|----------|----------------------|----------------------|------------------------------------|-------------------|----------|

|                             |          | −55°C to             |                      | 10-Lead Mini Small Outline Package |                   |          |

| AD7981HRMZ                  | ±2.0 LSB | +175°C               | 50                   | [MSOP]                             | RM-10             | C7C      |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.