## ゼロ・ドリフト、単電源 レールtoレール入出力オペアンプ

## AD8571/AD8572/AD8574

### 特長

低オフセット電圧: 1 µV

入力オフセット・ドリフト: 0.005 µV/°C

レール to レールの入力振幅および出力振幅

5 V/2.7 V の単電源動作 高ゲイン: 145 dB (typ)

CMRR: 140 dB (typ) PSRR: 130 dB (typ)

極めて低い入力バイアス電流: 10 pA (typ)

低電源電流: オペアンプあたり 750 µA

過負荷回復時間: 50 µs 外付けコンデンサが不要

## アプリケーション

温度センサー 圧力センサー

高精度電流検出

ストレーン・ゲージ・アンプ

医療計測機器

熱電対アンプ

#### 概要

このファミリーのアンプは極めて小さいオフセット、ドリフト、バイアス電流を持っています。AD8571、AD8572、AD8574 は、それぞれシングル、デュアル、クワッド・アンプであり、レール to レールの入力振幅と出力振幅を持っており、2.7 V~5 Vの単電源動作を保証しています。

AD857x ファミリーは、これまで高価なオートゼロ・アンプまたはチョッパ安定化アンプでなければ提供できなかった利点を提供します。アナログ・デバイスの回路トポロジを使って、これらのゼロ・ドリフト・アンプは高精度と低価格を組み合わせています(外付けコンデンサは不要)。AD857x ファミリーは特許取得済みの拡散スペクトルおよびオート・ゼロ技術を採用して、ACアプリケーションでのチョッピング機能と信号周波数の干渉による相互変調の影響を解消します。

AD857x ファミリーのオフセット電圧およびドリフトはそれぞれ  $1 \mu V$  および  $0.005 \mu V / C$  と小さいため、誤差原因を許容できないアプリケーションに最適です。位置センサー、圧力センサー、医用機器、ストレーン・ゲージ・アンプでは、全動作温度範囲でドリフトがほぼゼロである利点を活用できます。 さらに多くのシステムで、AD857x ファミリーの提供するレール to レールの入力振幅と出力振幅を必要としています。

AD857x ファミリーの仕様は、拡張工業/車載温度範囲(-40°C  $\sim$  +125°C)で規定されています。AD8571 シングル・アンプは、8 ピン MSOP またはナローSOIC パッケージを採用しています。AD8572 デュアル・アンプは、8 ピン・ナローSOIC または表面実装 TSSOP パッケージを採用しています。AD8574 クワッド・アンプは、14 ピン・ナローSOIC または TSSOP パッケージを採用しています。

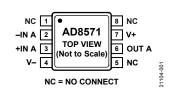

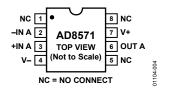

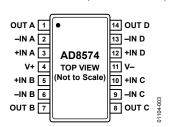

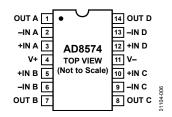

#### ピン配置

図1.8 ピン MSOP (RM サフィックス)

図2.8 ピン SOIC (R サフィックス)

図3.8 ピン TSSOP (RU サフィックス)

図4.8 ピン SOIC (R サフィックス)

図5.14 ピン TSSOP (RU サフィックス)

図6.14 ピン SOIC (R サフィックス)

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。 仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。 最新の内容については、英語版をご参照ください。 ©1999-2008 Analog Devices, Inc. All rights reserved.

本

## 目次

| 特長                                                                   | 1 正しいレイアウトで性能を最大化                                | 16          |

|----------------------------------------------------------------------|--------------------------------------------------|-------------|

| アプリケーション                                                             | 1 1/F ノイズ特性                                      | 17          |

| 概要                                                                   | 1 相互変調歪みをなくするランダム・オート・ゼロ                         | 補正17        |

| ピン配置                                                                 |                                                  |             |

| 改訂履壓                                                                 |                                                  |             |

| 仕様                                                                   |                                                  |             |

| 5 V 電気的特性                                                            |                                                  |             |

| 2.7 V 電気的特性                                                          | Λ                                                |             |

| 絶対最大定格                                                               | を量負荷の駆動                                          |             |

| <b>教特性</b>                                                           | ハワーノッノ動作                                         |             |

| ESD の注意                                                              | プレケーション情報                                        |             |

| 代表的な性能特性                                                             | 5 V 高精度ストレーン・ゲーシ                                 |             |

| 機能説明                                                                 | 3 V 計装 / ン /                                     | 20          |

|                                                                      | 品精度製電対アンプ                                        | 21          |

|                                                                      | 高精度電流計                                           | 21          |

| オート・ゼロ・アンプの原理1                                                       | 高精度雷圧コンパレータ                                      | 21          |

| オート・ゼロ・フェーズ1                                                         | 外形寸法                                             | 22          |

| 増幅フェーズ1                                                              | 5 オーダー・ガイド                                       |             |

| 高いゲイン、CMRR、PSRR1                                                     | 6                                                |             |

|                                                                      |                                                  |             |

| 改訂履歴                                                                 |                                                  |             |

| 6/08—Rev. C to Rev. D                                                | Updated Format                                   | I Iniversal |

| Changes to Figure 19 and Figure 20                                   |                                                  |             |

| Changes to Figure 44                                                 |                                                  |             |

| Changes to Figure 38                                                 |                                                  |             |

| Moved Figure 50 and Figure 511                                       |                                                  |             |

| Changes to Figure 66, Precision Current Meter Section, Layout, Figur |                                                  |             |

| 67, Equation 24, and Figure 682                                      |                                                  |             |

|                                                                      | Deleted SPICE Macro-Model for the AD857x Section |             |

| 5/07—Rev. B to Rev. C                                                | Updated Outline Dimensions                       | 22          |

| Changes to Features                                                  | 1 Changes to Ordering Guide                      | 23          |

| Changes to Table 1                                                   | 3                                                |             |

| Changes to Table 2                                                   | 4 7/03—Rev. 0 to Rev. A                          |             |

| Changes to Basic Auto-Zero Amplifier Theory Section1                 | 4 Renumbered Figures                             | Universal   |

| Changes to Figure 50                                                 | 5 Changes to Ordering Guide                      |             |

| Changes to Figure 55                                                 |                                                  |             |

| Changes to Figure 66                                                 | Cpatica Guillie Difficusions                     | 19          |

| Updated Outline Dimensions                                           |                                                  |             |

|                                                                      | 10/99—Revision 0: Initial Version                |             |

9/06—Rev. A to Rev. B

## 仕様

### 5 V 電気的特性

特に指定がない限り、 $V_S=5~V$ 、 $V_{CM}=2.5~V$ 、 $V_O=2.5~V$ 、 $T_A=25$ °C。

表1.

| Parameter                              | Symbol                   | Conditions                                                                                          | Min  | Typ   | Max  | Unit   |

|----------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|--------|

| INPUT CHARACTERISTICS                  |                          |                                                                                                     |      |       |      |        |

| Offset Voltage                         | $V_{OS}$                 |                                                                                                     |      | 1     | 5    | μV     |

|                                        |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                    |      |       | 10   | μV     |

| Input Bias Current                     | $I_{\mathrm{B}}$         |                                                                                                     |      | 10    | 50   | pA     |

| AD8571/AD8574                          |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                    |      | 1.0   | 1.5  | nA     |

| AD8572                                 |                          | $-40$ °C $\leq T_A \leq +85$ °C                                                                     |      | 160   | 300  | рA     |

|                                        |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                    |      | 2.5   | 4    | nA     |

| Input Offset Current                   | $I_{OS}$                 |                                                                                                     |      | 20    | 70   | рA     |

| AD8571/AD8574                          |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                    |      | 150   | 200  | pA     |

| AD8572                                 |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                               |      | 30    | 150  | pA     |

|                                        |                          | $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ +125 $^{\circ}$ C                                      |      | 150   | 400  | pA     |

| Input Voltage Range                    |                          |                                                                                                     | 0    |       | 5    | v      |

| Common-Mode Rejection Ratio            | CMRR                     | $V_{CM} = 0 \text{ V to 5 V}$                                                                       | 120  | 140   |      | dB     |

|                                        |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                              | 115  | 130   |      | dB     |

| Large Signal Voltage Gain <sup>1</sup> | $A_{VO}$                 | $R_L = 10 \text{ k}\Omega$ , $V_O = 0.3 \text{ V to } 4.7 \text{ V}$                                | 125  | 145   |      | dB     |

| 3 <u>3</u>                             | ***                      | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                     | 120  | 135   |      | dB     |

| Offset Voltage Drift                   | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                            | 120  | 0.005 | 0.04 | μV/°C  |

| OUTPUT CHARACTERISTICS                 | 2.103/21                 | 10 0 1 1A 1 120 0                                                                                   |      | 0.000 | 0.0. | μ., σ  |

| Output Voltage High                    | V <sub>OH</sub>          | $R_L = 100 \text{ k}\Omega \text{ to GND}$                                                          | 4.99 | 4.998 |      | v      |

| output voltage High                    | VOH                      | $R_L = 100 \text{ k}\Omega \text{ to GND } \text{@} -40^{\circ}\text{C to } +125^{\circ}\text{C}$   | 4.99 | 4.997 |      | v      |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to GND}$                                                           | 4.95 | 4.98  |      | v      |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to GND } $ $(a) -40^{\circ}\text{C to } +125^{\circ}\text{C}$      | 4.95 | 4.975 |      | v      |

| Output Voltage Low                     | $V_{OL}$                 | $R_L = 100 \text{ k}\Omega \text{ to V}+$                                                           | 4.73 | 1     | 10   | mV     |

| Output Voltage Low                     | V OL                     | $R_L = 100 \text{ k}\Omega \text{ to V} + \text{ (a)} -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |      | 2     | 10   | mV     |

|                                        |                          | _                                                                                                   |      |       |      |        |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to V}+$                                                            |      | 10    | 30   | mV     |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to V} + @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$            |      | 15    | 30   | mV     |

| Short-Circuit Limit                    | $I_{SC}$                 |                                                                                                     | ±25  | ±50   |      | mA     |

|                                        |                          | -40°C to +125°C                                                                                     |      | ±40   |      | mA     |

| Output Current                         | $I_{O}$                  |                                                                                                     |      | ±30   |      | mA     |

|                                        |                          | -40°C to +125°C                                                                                     |      | ±15   |      | mA     |

| POWER SUPPLY                           |                          |                                                                                                     |      |       |      |        |

| Power Supply Rejection Ratio           | PSRR                     | $V_S = 2.7 \text{ V to } 5.5 \text{ V}$                                                             | 120  | 130   |      | dB     |

|                                        |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                              | 115  | 130   |      | dB     |

| Supply Current per Amplifier           | $I_{SY}$                 | $V_{O} = 0 \text{ V}$                                                                               |      | 850   | 975  | μΑ     |

|                                        |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                              |      | 1000  | 1075 | μΑ     |

| DYNAMIC PERFORMANCE                    |                          |                                                                                                     |      |       |      |        |

| Slew Rate                              | SR                       | $R_L = 10 \text{ k}\Omega$                                                                          |      | 0.4   |      | V/µs   |

| Overload Recovery Time                 |                          |                                                                                                     |      | 0.05  | 0.3  | ms     |

| Gain Bandwidth Product                 | GBP                      |                                                                                                     |      | 1.5   |      | MHz    |

| NOISE PERFORMANCE                      |                          |                                                                                                     |      |       |      |        |

| Voltage Noise                          | e <sub>n</sub> p-p       | 0 Hz to 10 Hz                                                                                       |      | 1.3   |      | μV p-p |

|                                        |                          | 0 Hz to 1 Hz                                                                                        |      | 0.41  |      | μV p-p |

| Voltage Noise Density                  | $e_n$                    | f = 1  kHz                                                                                          |      | 51    |      | nV/√H  |

| Current Noise Density                  | i <sub>n</sub>           | f = 10  Hz                                                                                          |      | 2     |      | fA/√Hz |

<sup>「</sup>ゲイン・テストはテスト帯域幅に依存します。

### 2.7 V 電気的特性

特に指定がない限り、 $V_S=2.7~V$ 、 $V_{CM}=1.35~V$ 、 $V_O=1.35~V$ 、 $T_A=25$ °C。

### 表2.

| Parameter                              | Symbol                   | Conditions                                                                                                                                                                                                                                | Min   | Тур   | Max  | Unit   |

|----------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|--------|

| INPUT CHARACTERISTICS                  |                          |                                                                                                                                                                                                                                           |       |       |      |        |

| Offset Voltage                         | $V_{OS}$                 |                                                                                                                                                                                                                                           |       | 1     | 5    | μV     |

|                                        |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                                                                                                                                                          |       |       | 10   | μV     |

| Input Bias Current                     | $I_{\mathrm{B}}$         |                                                                                                                                                                                                                                           |       | 10    | 50   | pA     |

| AD8571/AD8574                          |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                    |       | 1.0   | 1.5  | nA     |

| AD8572                                 |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ +85°C                                                                                                                                                                                               |       | 160   | 300  | pA     |

|                                        |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+125$ °C                                                                                                                                                                                           |       | 2.5   | 4    | nA     |

| Input Offset Current                   | $I_{OS}$                 |                                                                                                                                                                                                                                           |       | 10    | 50   | pA     |

| AD8571/AD8574                          |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                    |       | 150   | 200  | pA     |

| AD8572                                 |                          | $-40$ °C $\leq T_A \leq +85$ °C                                                                                                                                                                                                           |       | 30    | 150  | pA     |

|                                        |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                    |       | 150   | 400  | pA     |

| Input Voltage Range                    |                          |                                                                                                                                                                                                                                           | 0     |       | 2.7  | V      |

| Common-Mode Rejection Ratio            | CMRR                     | $V_{CM} = 0 \text{ V to } 2.7 \text{ V}$                                                                                                                                                                                                  | 115   | 130   |      | dB     |

| common nacut regetion rumo             | Cinat                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                    | 110   | 130   |      | dB     |

| Large Signal Voltage Gain <sup>1</sup> | $A_{VO}$                 | $R_L = 10 \text{ k}\Omega$ , $V_O = 0.3 \text{ V to } 2.4 \text{ V}$                                                                                                                                                                      | 110   | 140   |      | dB     |

| gv 2.g valle all                       |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                    | 105   | 130   |      | dB     |

| Offset Voltage Drift                   | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                                                                                    | 105   | 0.005 | 0.04 | μV/°C  |

| OUTPUT CHARACTERISTICS                 | 2103/21                  | 10 C = 1A = +125 C                                                                                                                                                                                                                        |       | 0.005 | 0.01 | μννο   |

| Output Voltage High                    | $V_{\mathrm{OH}}$        | $R_L = 100 \text{ k}\Omega \text{ to GND}$                                                                                                                                                                                                | 2.685 | 2.697 |      | V      |

| Output Voltage High                    | V OH                     | $R_L = 100 \text{ k}\Omega \text{ to GND } @ -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                                                                                                | 2.685 | 2.696 |      | v      |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to GND}$                                                                                                                                                                                                 | 2.67  | 2.68  |      | v      |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to GND } $ $(0.0013)^{\circ}$ | 2.67  | 2.675 |      | v      |

| Output Voltage Low                     | $V_{ m OL}$              | $R_L = 100 \text{ k}\Omega \text{ to V}+$                                                                                                                                                                                                 | 2.07  | 1     | 10   | mV     |

| Output Voltage Low                     | V OL                     | $R_L = 100 \text{ k}\Omega \text{ to V} + \text{ (a)} -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                                                                                       |       | 2     | 10   | mV     |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to V} + \omega$ 40 C to +123 C                                                                                                                                                                           |       | 10    | 20   | mV     |

|                                        |                          | $R_L = 10 \text{ k}\Omega \text{ to V} +        \text$                                                                                                                                                                                    |       | 15    | 20   | mV     |

| Short-Circuit Limit                    | $I_{SC}$                 | K_ 10 K22 to V + (a) 40 C to +123 C                                                                                                                                                                                                       | ±10   | ±15   | 20   | mA     |

| Short-Circuit Limit                    | isc                      | -40°C to +125°C                                                                                                                                                                                                                           | 110   | ±10   |      | mA     |

| Output Current                         | $I_{\rm O}$              | 40 C to +125 C                                                                                                                                                                                                                            |       | ±10   |      | mA     |

| Output Current                         | 1()                      | -40°C to +125°C                                                                                                                                                                                                                           |       | ±5    |      | mA     |

| POWER SUPPLY                           |                          | 40 C to +125 C                                                                                                                                                                                                                            |       | ±3    |      | шл     |

| Power Supply Rejection Ratio           | PSRR                     | $V_S = 2.7 \text{ V to } 5.5 \text{ V}$                                                                                                                                                                                                   | 120   | 130   |      | dB     |

| 1 ower suppry rejection ratio          | 1 SKK                    | $V_S - 2.7 \text{ V to 3.3 V}$<br>$-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                                                  | 115   | 130   |      | dB     |

| Supply Current per Amplifier           | L                        | $V_{O} = 0 \text{ V}$                                                                                                                                                                                                                     | 113   | 750   | 900  | μА     |

| Suppry Current per Ampinner            | $I_{SY}$                 | $v_0 - 0$ v<br>$-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                                                                     |       | 950   | 1000 | · ·    |

| DYNAMIC PERFORMANCE                    | +                        | 70 C 2 1A 2 + 123 C                                                                                                                                                                                                                       |       | 950   | 1000 | μA     |

|                                        | CD                       | P = 10 kO                                                                                                                                                                                                                                 |       | 0.5   |      | W/a    |

| Slew Rate                              | SR                       | $R_L = 10 \text{ k}\Omega$                                                                                                                                                                                                                |       | 0.5   |      | V/µs   |

| Overload Recovery Time                 | CDD                      |                                                                                                                                                                                                                                           |       | 0.05  |      | ms     |

| Gain Bandwidth Product                 | GBP                      |                                                                                                                                                                                                                                           |       | 1     |      | MHz    |

| NOISE PERFORMANCE                      |                          | 011 / 1011                                                                                                                                                                                                                                |       | 2.0   |      | 17     |

| Voltage Noise                          | e <sub>n</sub> p-p       | 0 Hz to 10 Hz                                                                                                                                                                                                                             |       | 2.0   |      | μV p-p |

| Voltage Noise Density                  | e <sub>n</sub>           | f = 1 kHz                                                                                                                                                                                                                                 |       | 94    |      | nV/√Hz |

| Current Noise Density                  | i <sub>n</sub>           | f = 10  Hz                                                                                                                                                                                                                                |       | 2     |      | fA/√Hz |

<sup>「</sup>ゲイン・テストはテスト帯域幅に依存します。

Rev. D - 4/23 -

## 絶対最大定格

#### 表3.

| Parameter                               | Rating                       |

|-----------------------------------------|------------------------------|

| Supply Voltage                          | 6 V                          |

| Input Voltage                           | GND to $V_S + 0.3 \text{ V}$ |

| Differential Input Voltage <sup>1</sup> | ±5.0 V                       |

| ESD (Human Body Model)                  | 2000 V                       |

| Output Short-Circuit Duration to GND    | Indefinite                   |

| Storage Temperature Range               | −65°C to +150°C              |

| Operating Temperature Range             | −40°C to +125°C              |

| Junction Temperature Range              | −65°C to +150°C              |

| Lead Temperature (Soldering, 60 sec)    | 300°C                        |

<sup>&</sup>lt;sup>1</sup> 差動入力電圧は $\pm 5.0 \, \mathrm{V}$  または電源電圧のいずれか小さい方に制限されます。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格 の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものでは ありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 熱特性

$\theta_{JA}$ はワーストケース条件で規定。すなわち SOIC と TSSOP パッケージの場合、デバイスを回路ボードにハンダ付けした状態で $\theta_{JA}$ を規定。

#### 表4.熱抵抗

| Package Type       | $\theta_{\mathrm{JA}}$ | $\theta_{ m JC}$ | Unit |

|--------------------|------------------------|------------------|------|

| 8-Lead SOIC (R)    | 158                    | 43               | °C/W |

| 8-Lead MSOP (RM)   | 190                    | 44               | °C/W |

| 8-Lead TSSOP (RU)  | 240                    | 43               | °C/W |

| 14-Lead SOIC (R)   | 120                    | 36               | °C/W |

| 14-Lead TSSOP (RU) | 180                    | 36               | °C/W |

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. D -5/23 -

## 代表的な性能特性

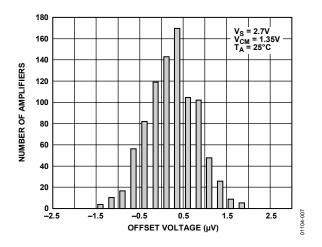

図7.入力オフセット電圧の分布

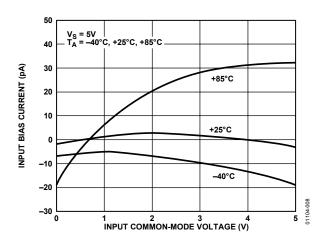

図8.入力バイアス電流対入力同相モード電圧

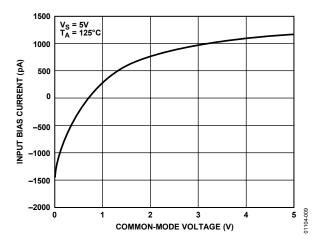

図9.入力バイアス電流対同相モード電圧

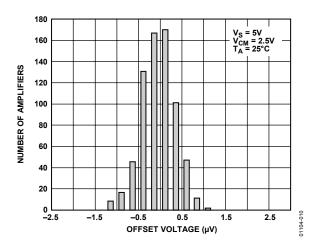

図10.入力オフセット電圧の分布

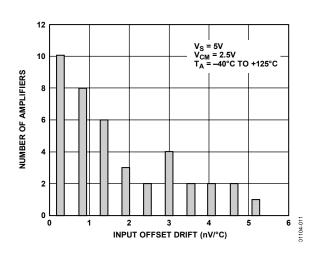

図11.入力オフセット電圧ドリフトの分布

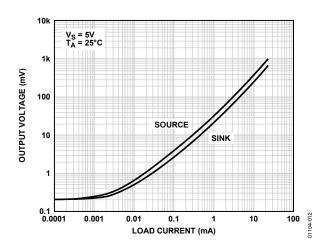

図12.電源レールまで近づく出力電圧対負荷電流

Rev. D -6/23 -

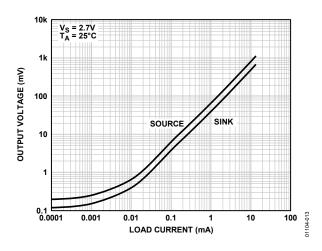

図13.電源レールまで近づく出力電圧対負荷電流

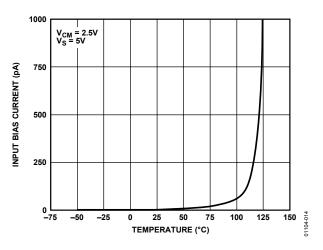

図14.入力バイアス電流の温度特性

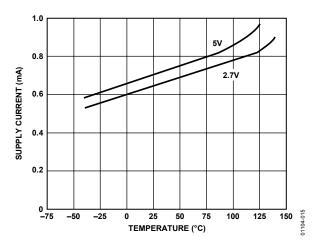

図15.電源電流の温度特性

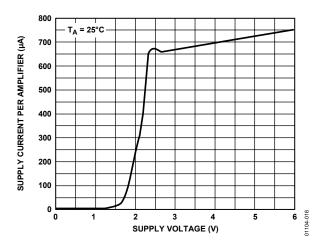

図16.アンプあたりの電源電流対電源電圧

図17.オープン・ループ・ゲインおよび位相シフトの周波数特性

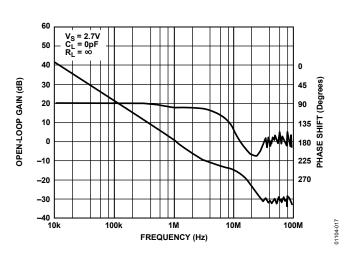

図18.オープン・ループ・ゲインおよび位相シフトの周波数特性

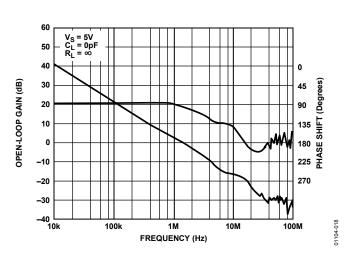

Rev. D - 7/23 -

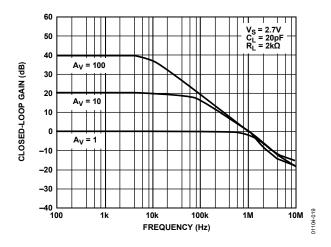

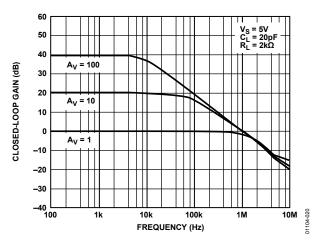

図19.クローズド・ループ・ゲインの周波数特性

図20.クローズド・ループ・ゲインの周波数特性

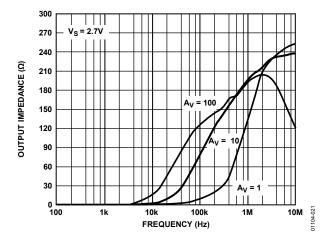

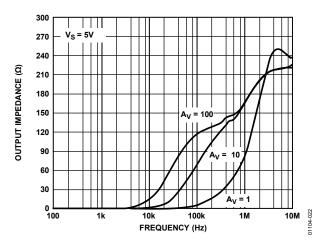

図21.出力インピーダンスの周波数特性

図22.出力インピーダンスの周波数特性

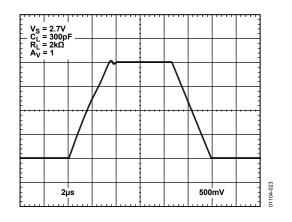

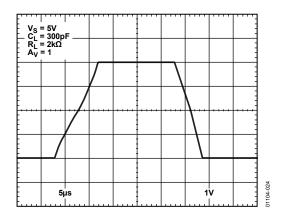

図23.大信号過渡応答

図24.大信号過渡応答

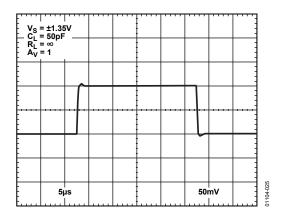

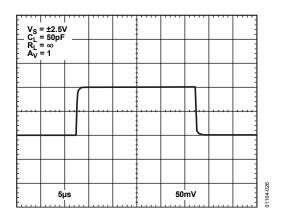

Rev. D -8/23 -

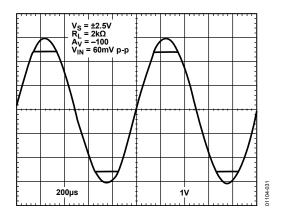

図25.小信号過渡応答

図26.小信号過渡応答

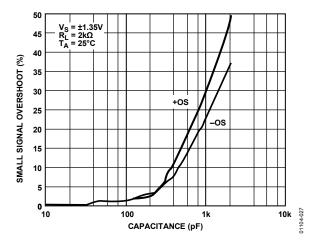

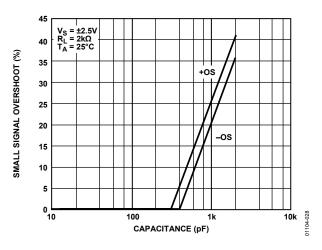

図27.小信号オーバーシュート対負荷容量

図28.小信号オーバーシュート対負荷容量

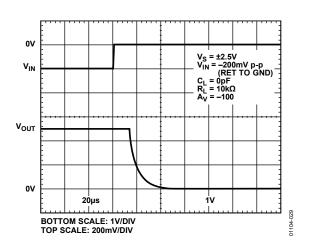

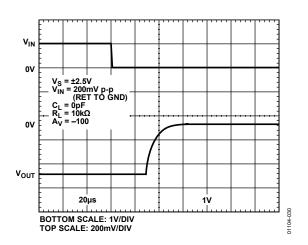

図29.正の過電圧回復時間

図30.負の過電圧回復時間

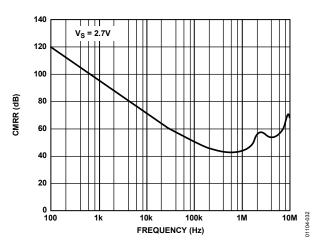

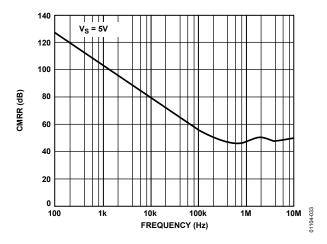

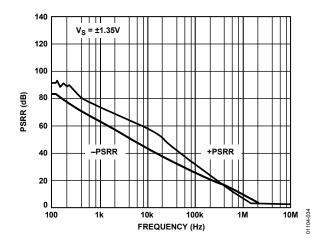

Rev. D - 9/23 -

図31.位相反転なし

図32.CMRR の周波数特性

図33.CMRR の周波数特性

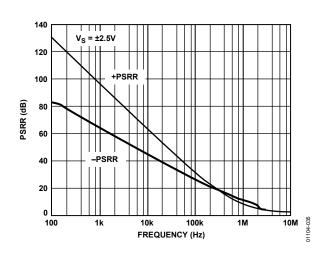

図34.PSRR の周波数特性

図35.PSRR の周波数特性

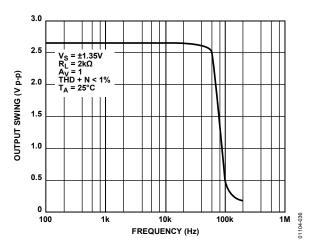

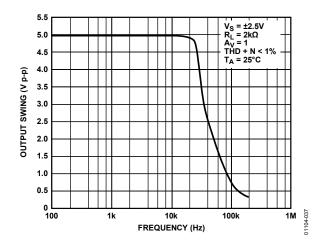

図36.最大出力振幅の周波数特性

Rev. D — 10/23 —

図37.最大出力振幅の周波数特性

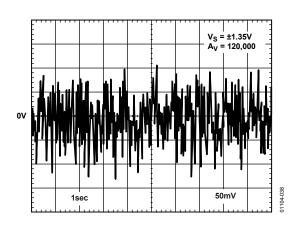

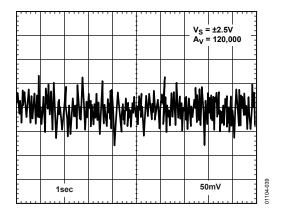

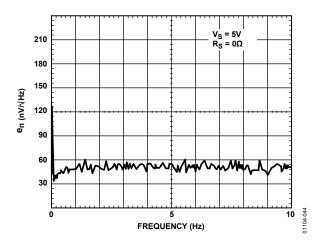

図38.0.1~10 Hz でのノイズ

図39.0.1~10 Hz でのノイズ

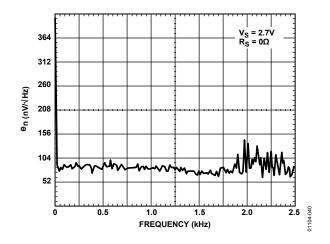

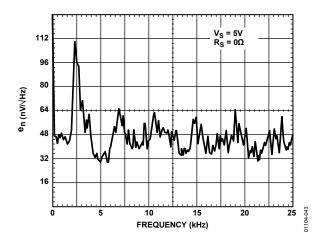

図40.電圧ノイズ密度、0 Hz~2.5 kHz

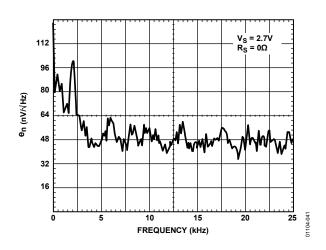

図41.電圧ノイズ密度、0 Hz~25 kHz

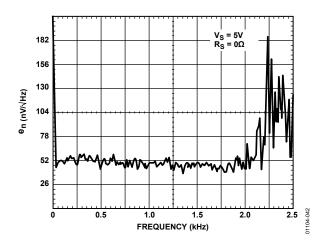

図42.電圧ノイズ密度、0 Hz~2.5 kHz

Rev. D — 11/23 —

図43.電圧ノイズ密度、0 Hz~25 kHz

図44.電圧ノイズ密度、0 Hz~10 Hz

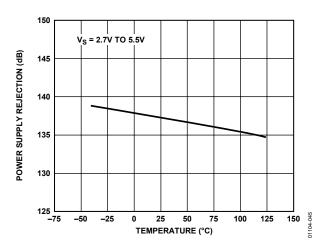

図45.電源除去比の温度特性

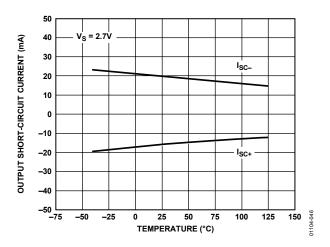

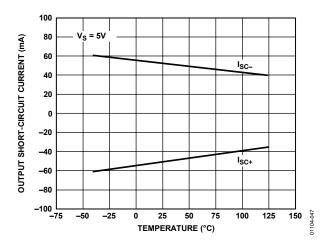

図46.出力短絡電流の温度特性

Rev. D — 12/23 —

図47.出力短絡電流の温度特性

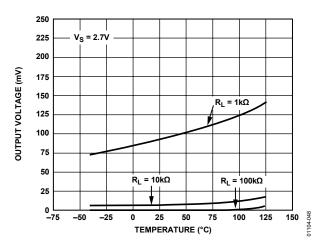

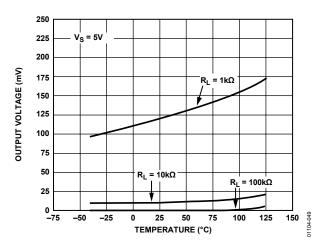

図48.電源レールまで近づく出力電圧の温度特性

図49.電源レールまで近づく出力電圧の温度特性

Rev. D — 13/23 —

## 機能説明

AD8571/AD8572/AD8574 は、ランダム周波数オート・ゼロ安定 化技術を使い高精度を実現した CMOS アンプです。 AD857x は、 自動補正回路の採用により広い温度範囲で低オフセット電圧を 維持し、ランダム化オート・ゼロ・クロック技術により、アン プ出力での相互変調歪み(IMD)誤差をなくしています。

AD857x は 2.7 V と低い単電源で動作することができます。 AD857x のオフセット電圧は  $1\mu$ V と極めて小さく、かつ IMD 積が存在しないため、出力電圧誤差が大きくなる危険性なしに高いゲインを容易に設定することができます。このため、DC 精度と AC 信号の低歪みを必要とするアプリケーションに最適なアンプになっています。 $5\,n$ V/°C と極めて小さい温度ドリフトにより、-40°C~+125°C の温度範囲で最小のオフセット電圧誤差を保証します。これらの機能の組み合わせにより、AD857x は多様な高感度計測アプリケーションと車載アプリケーションに対する優れた選択肢になっています。

#### アンプ・アーキテクチャ

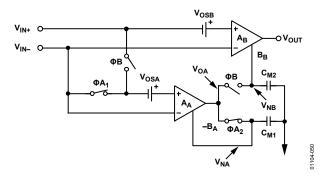

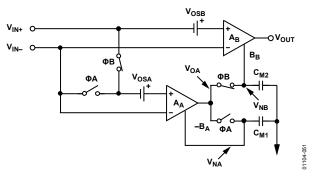

各 AD857x オペアンプは、メイン・アンプとメイン・アンプのオフセット電圧の補正に使われるセカンダリ・アンプの2つのアンプから構成されています。両アンプともレール to レールの入力ステージから構成されているため、両電源レールに到達する入力同相モード電圧範囲が可能です。入力ステージは、NMOS差動対とこれと並行動作する並列PMOS差動対から構成されています。差動入力ステージからの出力は、もう1つのゲイン・ステージに接続され、このゲイン・ステージの出力がレール to レールの出力ステージの駆動に使用されます。

アンプのこの広い電圧振幅は、2個の出力トランジスタをコモン・ソース構成で使用することにより実現されています。出力電圧範囲は、これらのトランジスタのドレイン—ソース間抵抗により制限されます。アンプの出力電流を大きくすると、これらのトランジスタにあるオン抵抗( $R_{DS}$ )のために、電圧降下が大きくなります。簡単に言えば、出力電流が大きくなると、出力電圧の振幅は出力電流が小さいときと同じようにレールまで近づきません。これは、すべてのレール to レール出力アンプの特性です。図 12 と図 13に、与えられた出力電流に対して、出力電圧が電源レールに近づく様子を示します。AD857x の出力は、約 50 mA の電流までに短絡保護されています。

AD857x アンプは、 $2 k\Omega$  負荷で 120 dB 以上のオープン・ループ・ゲインを発生する優れたゲイン特性を持っています。出力トランジスタはコモン・ソース構成であるため、出力ステージのゲイン、したがってアンプのオープン・ループ・ゲインは、負荷抵抗に依存します。負荷抵抗が小さいほどオープン・ループ・ゲインが小さくなります。これは、レール to レール出力アンプのもう1つの特性です。

### オート・ゼロ・アンプの原理

自動補正アンプは新しい技術ではありません。15 年以上前からさまざまな IC が存在し、いくつかの改善が行われています。AD857x デザインでは旧バージョンに多くの性能改善を行うと同時に、デバイス・コストの大幅な削減も行っています。このセクションでは、AD857x が極めて低いオフセット電圧と高いオープン・ループ・ゲインを提供できる方法について簡単に説明します。

アンプ・アーキテクチャのセクションに記載するように、各 AD857x オペアンプは 2 個のアンプを内蔵しています。一方はプライマリ・アンプとして使われ、他方は自動補正アンプ(ヌル・アンプ)として使われています。各アンプは、非反転入力と直列な DC 電圧源としてモデル化できる対応する入力オフセット電圧を持っています。図 50と図 51では、これらは  $V_{OSA}$  と  $V_{OSB}$  で表示されています。ここで、A はヌル・アンプを、B はプライマリ・アンプを、それぞれ表します。各アンプの+IN 入力と-IN 入力のオープン・ループ・ゲインは  $A_{X}$  で表します。また、両アンプは対応するオープン・ループ・ゲイン  $B_{X}$  を持つ 3 つ目の電圧入力も持っています。

図50.アンプのオート・ゼロ・フェーズ

図51.アンプの出力フェーズ

アンプの 2 つのスイッチの動作で指定されるオート・ゼロ・フェーズと増幅フェーズの 2 つの動作モードがあります。

Rev. D — 14/23 —

### オート・ゼロ・フェーズ

このフェーズでは、すべての  $\Phi A_X$  スイッチが閉じ、すべての  $\Phi B$  スイッチが開きます。ここで、ヌル・アンプの 2 つの入力を 短絡させてヌル・アンプをゲイン・ループから除きます。 もち ろん、ある程度のオフセット電圧が存在し、これを  $V_{OSA}$  で表します。これはヌル・アンプに固有であり、+IN 入力と-IN 入力の間の電位差を維持しています。ヌル・アンプ帰還ループが  $\Phi A_2$  で閉じられると、 $V_{OSA}$  がヌル・アンプ出力と AD857x の内部コンデンサ  $C_{MI}$  に現れます。数学的には、これを時間領域で次のように表すことができます。

$$V_{OA}[t] = A_A V_{OSA}[t] - B_A V_{OA}[t]$$

$$\tag{1}$$

これは次のように表すことができます。

$$V_{OA}[t] = \frac{A_A V_{OSA}[t]}{1 + B_A} \tag{2}$$

前の式は、ヌル・アンプのオフセット電圧とゲイン・ファクタの積がヌル・アンプ出力に現れ、したがって  $C_{MI}$  コンデンサにも現れることを示しています。

#### 増幅フェーズ

$\Phi B$  スイッチが閉じて、増幅フェーズのために  $\Phi A_X$  スイッチが 開くと、オフセット電圧が CMI 上に残るため、実質的にヌル・アンプのすべての誤差が補正されます。  $C_{MI}$  の電圧は  $V_{NA}$  で表されます。プライマリ・アンプの 2 つの入力間の電位差は、 $V_{IN}$  すなわち  $V_{IN} = (V_{IN+} - V_{IN-})$ で表されます。したがって、ヌル・アンプ出力は次のように表すことができます。

$$V_{OA}[t] = A_A(V_{IN}[t] - V_{OSA}[t]) - B_A V_{NA}[t]$$

(3)

$\Phi A_X$  が開くために  $C_{MI}$  が放電できないので、現時点(t)での電圧  $(V_{NA})$ は  $\Phi A_X$  が閉じたときのヌルアンプ出力の電圧 $(V_{OA})$ に一致します。自動補正スイッチング周波数の周期を  $T_S$  で表すと、アンプは  $0.5 \times T_S$  ごとに 2 つのフェーズ間で切り替わります。このため、増幅フェーズでは、

$$V_{NA}[t] = V_{NA} \left[ t - \frac{1}{2} T_S \right] \tag{4}$$

式4と式2を式3に代入すると、

$$V_{OA}[t] = A_A V_{IN}[t] + A_A V_{OSA}[t] - \frac{A_A B_A V_{OSA}[t - \frac{1}{2} T_S]}{1 + B_A}$$

(5)

簡単のために、自動補正頻度が  $V_{OSA}$  または  $V_{OSB}$  の電位変化に比べて高いと仮定することができます。オフセット電圧の変化は温度変動または長時間変化の関数であり、両者は AD857x のオート・ゼロ・クロック周波数よりかなり低速であるため、実質的に  $V_{OS}$  は時間不変と見なすことができるので、式 5 は次のように書き換えることができます。

$$V_{OA}[t] = A_A V_{IN}[t] + \frac{A_A (1 + B_A) V_{OSA} - A_A B_A V_{OSA}}{1 + B_A}$$

(6)

または

$$V_{OA}[t] = A_A \left( V_{IN}[t] + \frac{V_{OSA}}{1 + B_A} \right)$$

(7)

ここで、オート・ゼロ機能が明確になります。 $V_{OS}$  項が  $1/(1+B_A)$ に小さくなることに注意してください。これは、プライマリ・アンプを補正する前でも、ヌル・アンプが大幅に自分のオフセット電圧誤差を小さくする方法を示しています。このようにして、プライマリ・アンプ出力電圧が AD857x アンプ出力の電圧になります。これは次のように表されます。

$$V_{OUT}[t] = A_B(V_{IN}[t] + V_{OSB}) + B_B V_{NB}$$

(8)

増幅フェーズでは、 $\mathbf{V}_{\mathrm{OA}} = \mathbf{V}_{\mathrm{NB}}$ であるため、次のように書き換えることができます。

$V_{OUT}[t] =$

$$A_{B}V_{IN}[t] + A_{B}V_{OSB} + B_{B}\left[A_{A}\left(V_{IN}[t] + \frac{V_{OSA}}{1 + B_{A}}\right)\right]$$

(9)

項をまとめると、

$$V_{OUT}[t] =$$

$$V_{IN}[t](A_B + A_A B_B) + \frac{A_A B_B V_{OSA}}{1 + B_A} + A_B V_{OSB}$$

(10)

AD857x アーキテクチャは、 $A_A=A_B$ 、 $B_A=B_B$ 、かつ  $B_A>>1$  の 方法で最適化されます。さらに、ゲイン積  $A_AB_B$ は  $A_B$ より遥かに大きくなります。このため、式 10 は次のように簡単になります。

$$V_{OUT}[t] = V_{IN}[t]A_AB_A + A_A(V_{OSA} + V_{OSB})$$

$$\tag{11}$$

最も明確なのは、プライマリ・アンプとヌル・アンプのゲイン積です。この  $A_AB_A$  項そのものが、AD857x に極めて高いオープン・ループ・ゲインを与えています。 $V_{OSA}$  および  $V_{OSB}$  とアンプ全体の全実効入力オフセット電圧との関係を理解するために、次のアンプの一般式を使います。

$$V_{OUT} = k \times (V_{IN} + V_{OS, EFF})$$

(12)

ここで、

kはアンプのオープン・ループ・ゲイン。

$V_{OS, EFF}$ はその実効オフセット電圧。

式 12 を式 11 の形式にすると、

$$V_{OUT}[t] = V_{IN}[t]A_AB_A + V_{OS, EFF}A_AB_A$$

(13)

Rev. D — 15/23 —

したがって、

$$V_{OS,EFF} \approx \frac{V_{OSA} + V_{OSB}}{B_A} \tag{14}$$

このように、プライマリ・アンプとヌル・アンプのオフセット電圧は  $1/B_A$  になり、数ミリボルトの入力オフセット電圧(typ)からマイクロボルト未満の実効入力オフセット電圧にへ削減されます。この自動補正方式により、AD857x ファミリーのアンプは極めて高精度になります。

#### 高いゲイン、CMRR、PSRR

同相モードと電源除去比は、入力同相モード電圧または電源電圧の変化によりアンプに発生するオフセット電圧の大きさを表します。増幅フェーズのセクションで説明したように、AD857xの自動補正アーキテクチャにより、実質的にオフセット電圧が小さくされます。また、この技術は同相モード電圧振幅と電源の変動により発生するオフセット誤差も補正します。これにより、130~dB~bE を超える優れた CMRR と PSRR の値が得られます。自動補正は連続的に行われるため、これらの値はデバイスの全温度範囲( $-40^{\circ}$ C $\sim$ + $125^{\circ}$ C)で維持することができます。

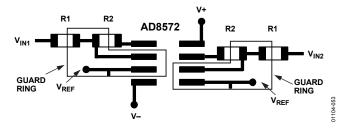

#### 正しいレイアウトで性能を最大化

AD857x の極めて高い入力インピーダンスと低オフセット電圧の最大性能を実現するためには、回路ボードのレイアウトで注意が必要です。PCB表面をクリーンにして、隣接パターン間でのリーク電流をなくするために湿気をなくす必要があります。回路ボードの表面コーティングを行うと、表面の湿気が少なくなり、湿度バリアが構成されて、ボード上の寄生抵抗が少なくなります。アンプ入力の周囲にガード・リングを設けると、さらにリーク電流が減ります。図 52に、ガード・リングの構成方法を、図 53に、表面実装レイアウトの上面図を、それぞれ示します。ガード・リングは特定の幅にする必要はありませんが、両入力の周囲で連続ループを構成する必要があります。ガード・リング電圧を非反転入力の電圧に一致させると、寄生容量も小さくなります。リーク電流をさらに小さくするときは、Teflon®スタンドオフ・インシュレータを使って部品を PCB に実装することができます。

図52.PCB リーク電流を小さくするガード・リングの レイアウトと接続

図53.ガード・リングを使った AD8572 SOIC レイアウトの上面図

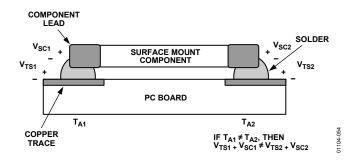

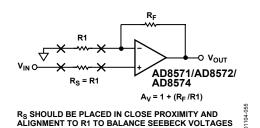

その他のオフセット誤差原因としては、回路ボード上の熱電電圧があります。この電圧はジーベック電圧とも呼ばれ、2つの異種メタルの接点で発生し、接点温度に比例します。回路ボード上の最も一般的なメタル接点はハンダーボード・パターン間とハンダー部品端子間の接点です。図 54に、熱電対誤差電圧の断面図を示します。一端の部品の PCB 温度( $T_{A1}$ )が他端( $T_{A2}$ )の温度と異なる場合、ジーベック電圧が一致しないため、熱電対誤差が発生します。

ダミー部品を使って熱電対誤差電圧を一致させると、この熱電対誤差を小さくすることができます。ダミー部品をその相手のできるだけ近くに配置して、両ジーベック電圧を一致させて、熱電対誤差を相殺させます。回路ボード上の周囲温度を一定に維持すると、さらにこの誤差を小さくすることができます。グラウンド・プレーンを使用すると、ボードへの熱の放散に役立ち、EMI ノイズの混入も減らすことができます。

図54.ジーベック電圧の不一致により発生する熱電対電圧誤差

図55.ダミー部品を使用した熱電対電圧誤差の相殺

Rev. D — 16/23 —

### 1/F ノイズ特性

オート・ゼロ・アンプのもう 1 つの利点は、フリッカ・ノイズを相殺する機能です。フリッカ・ノイズは 1/f ノイズとも呼ばれ、半導体デバイスの物理に固有なノイズで、周波数が 1 オクターブ低下するごとに 3 dB 増えます。アンプの 1/f コーナー周波数とは、フリッカ・ノイズがアンプの広帯域幅ノイズに等しくなる周波数です。低い周波数でフリッカ・ノイズが支配的になり、1 ヘルツより低い周波数で、または高精度 DC アプリケーションで大きな誤差を発生させます。

AD857x アンプは自己補正オペアンプであるため、低い周波数で大きくなるフリッカ・ノイズがありません。本質的に、低周波ノイズはゆっくり変化するオフセット誤差として扱われ、自動補正により大幅に削減されます。補正は、ノイズ周波数がDCに近づくほど効果的になり、周波数の低下とともに指数的にノイズが増加する傾向を相殺します。このために、1/f ノイズに敏感な標準の低ノイズ・アンプに比べて、DC近くで AD857x がノイズを削減できるようになります。

## 相互変調歪みをなくするランダム・オート・ゼロ 補正

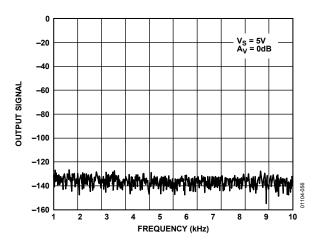

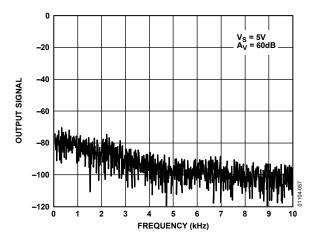

AD857x は、1 MHz までのゲインに対して従来型オペアンプとして使うことができます。デバイスのオート・ゼロ補正周波数は、2 kHz~4 kHz で均一な分布を持つ疑似ランダム・ジェネレータに基づいて連続的に変化します。自動補正クロックのランダム化により、アンプ出力でシンプルな広帯域幅ノイズとして現れる IMD 積の連続的なランダム化が発生します。この広帯域幅ノイズが 2 乗和平均と同じ方法で自然にアンプ電圧ノイズと組み合わさって、IMD のない出力が得られます。図 56 に、アンプをユニティ・ゲインに設定し、入力をグラウンドに接続したAD8572 のスペクトル出力を示します。図 57に、アンプのゲインを 60 dB としてスペクトル出力を示します。

図56.ユニティ・ゲイン設定の AD8572 出力のスペクトル解析

図57.ゲイン 60 dB を持つ AD857x の出力のスペクトル解析

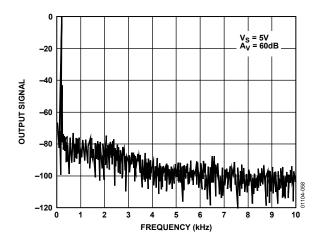

図 58 に、高ゲイン(60 dB)に設定した AD8572 に 1 mV 信号を入力したときのスペクトル出力を示します。スペクトル内に IMD 積が存在しないことに注意してください。出力信号の信号対ノイズ比(SNR)は、60 dB すなわち 0.1%より優れています。

図58. AD8572 を高ゲインに設定して入力信号を与えたときの スペクトル解析

Rev. D - 17/23 -

## 広帯域と外部抵抗ノイズについて

アンプの総合広帯域幅ノイズ出力は基本的に、アンプの入力電圧ノイズ、アンプの入力電流ノイズ、アンプの周囲で使われている外部抵抗のジョンソン・ノイズの 3 つのタイプのノイズの関数になっています。入力電圧ノイズ en は厳密に、使用しているアンプの関数です。抵抗のジョンソン・ノイズは、抵抗と温度の関数です。入力電流ノイズ in は、アンプの周囲で使用している抵抗に比例する等価電圧ノイズです。これらのノイズ・ソースは互いに相関がなく、これらの総合ノイズは 2 乗和平均の方法で合算されます。全体の式は次のように表されます。

$$e_{n, TOTAL} = \left[e_n^2 + 4kTr_s + (i_n r_s)^2\right]^{1/2}$$

(15)

ここで、

$e_n$ はアンプの入力電圧ノイズ。 $i_n$ はアンプの入力電流ノイズ。 $r_s$ は非反転端子に接続されたソース抵抗。kはボルツマン定数 $(1.38 \times 10^{-23} \text{ J/K})$ 。Tは、絶対温度で表した周囲温度 $(T = 273.15 + ^{\circ}\text{C})$ 。

AD857x の入力電圧ノイズ密度  $e_n$ は  $51\,nV/$ Hz で、入力ノイズ  $i_n$ は  $2\,fA/$ Hz。en,  $_{TOTAL}$ は、ソース抵抗が  $172\,k\Omega$  より小さい場合、入力電圧ノイズにより支配されます。ソース抵抗が  $172\,k\Omega$  より大きい場合、システムの全体ノイズは、抵抗自体のジョンソン・ノイズにより支配されます。

AD857x の入力電流ノイズは非常に小さいため、 $i_n$ は  $r_s>4$  G $\Omega$  でないかぎり支配的な項になりません。この 4 G $\Omega$  はソース抵抗の非現実的な値です。

総合ノイズ en, TOTAL は、単位 volts-per-square-root Hertz で表され、ある帯域幅での等価 rms ノイズは次のように表されます。

$$e_n = en, _{TOTAL} \times \sqrt{BW}$$

(16)

ここで、BWはヘルツで表した注目する帯域幅。

#### 出力オーバードライブ回復機能

AD857x アンプは、いずれかの電源レールからわずか 200 μs で 回復する優れたオーバードライブ回復機能を持っています。この特性は、誤差補正してメイン・アンプを有効な出力に戻すためにヌル・アンプが多くの時間を要するため、自動補正アンプ にとっては難しい特性です。図 29と図 30に、AD857x の正と負のオーバードライブ回復時間を示します。

自動補正アンプの出力オーバードライブ回復機能は、出力が過 負荷状態から最終電圧へ補正されるのに要する時間として定義 されます。この時間は、アンプを高ゲインに設定し、出力電圧 を電源レールまで駆動する入力信号を与えて測定されます。そ の後、入力電圧をアンプのリニア領域(通常は電源の中点)まで 低下させます。入力信号の低下から出力が最終値から 100 μV以 内に安定するまでの時間がオーバードライブ回復時間です。多 くの自動補正アンプは多くのオート・ゼロ・クロック・サイク ルを要して出力オーバードライブから回復し、出力が安定する までに数ミリセカンドを要するものもあります。

#### 入力過電圧保護機能

AD857x はレール to レール入力アンプですが、各入力の間の電位差が 5 V を超えないように注意する必要があります。通常の動作状態では、アンプは 2 つの入力が同電圧になるように出力を補正します。ただし、デバイスをコンパレータとして構成する場合、またはある異常動作状態の場合、各入力電圧が異なる電位に強制されることがあります。これにより、過電圧から入力ステージを保護するために AD857x 内部にあるダイオードを通して過大な電流が流れることがあります。

いずれかの入力が電源レールより 0.3 V 以上高くなると、大きな電流がアンプ内の ESD 保護ダイオードを流れます。これらのダイオードは、静電放電に対して入力トランジスタを保護するために入力と各電源レールとの間に接続されており、通常は逆バイアスされていまが、入力電圧が電源電圧を超えると、これらの ESD ダイオードは順方向にバイアスされます。電流制限がない場合、大きな電流がこれらのダイオードを流れて、デバイスの永久的な損傷が発生します。入力に過電圧が加えられる場合、適切な直列抵抗を挿入して、ダイオード電流を 2 mA 以下に制限する必要があります。

#### 出力位相の反転

出力位相の反転は、入力同相モード電圧が範囲を超えるとある種のアンプで発生します。同相モード電圧が同相モード範囲外になると、これらのアンプの出力は電源レールの反対側に突然ジャンプします。これは差動入力対が停止することに起因して、出力に誤動作を発生させる内部電圧の急激なシフトが生ずるためです。

AD857x アンプは、両入力が電源電圧以内に維持されている限り、出力位相の反転が発生しないように注意深くデザインされています。一方または両方の入力がいずれかの電源電圧を超えることがある場合は、抵抗を入力に直列に接続して、電流を 2 mA 未満に制限して、出力の位相が反転しないようにしてください。

Rev. D — 18/23 —

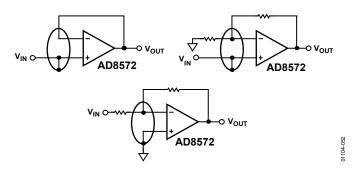

#### 容量負荷の駆動

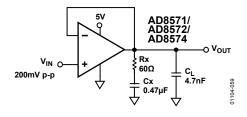

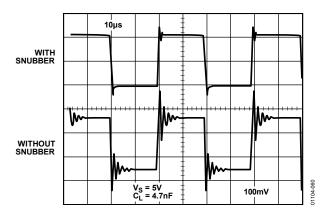

AD857x は優れた容量負荷駆動能力を持つため、5 V 単電源で最大 10 nF までを安全に駆動することができます。デバイスは安定ですが、容量負荷がアンプの帯域幅を制限します。容量負荷は、出力でのオーバーシュートとリンギングも大きくします。図 59に示す RC スナバ回路を使うと、容量負荷でのリンギングとオーバーシュートを小さくすることができます。

図59.容量負荷駆動のスナバ回路構成

スナバ回路は負荷容量によるアンプ帯域幅の損失を回復しませんが、この回路を使うと、アンプが駆動できる容量を大きくすることができると同時に、オーバーシュートとリンギングを小さく維持します。 図 60に、1 nF のコンデンサを駆動する AD857x の出力をスナバ回路ありの場合となしの場合について示します。

図60.スナバ回路の使用によりオーバーシュートとリンギングを大幅に削減

抵抗とコンデンサの最適値は、負荷容量の関数であり、実際の $C_L$ には漂遊容量が含まれて公称容量負荷から大きく異なるので、実験的に求めます。表 5に、開始点として使用できるスナバ回路値を示します。

表5.容量負荷駆動のスナバ回路値

| C <sub>L</sub> (nF) | Rx (Ω) | Cx      |

|---------------------|--------|---------|

| 1                   | 200    | 1 nF    |

| 4.7                 | 60     | 0.47 μF |

| 10                  | 20     | 10 μF   |

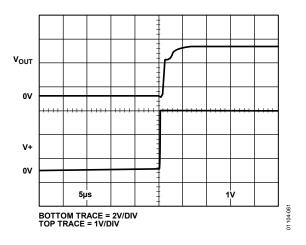

### パワーアップ動作

パワーアップ時、AD857x は 5  $\mu$ s 以内に有効出力に安定します。 図 61にアンプ出力と電源電圧のオシロスコープ写真を、図 62に テスト回路を、それぞれ示します。アンプをユニティ・ゲイン に設定すると、デバイスは最終出力電圧に安定するのに約 5  $\mu$ s を要します。これは、他の多くの自動補正アンプと比較して数百マイクロセカンド高速です。

図61.パワーアップ時の AD857x 出力の動作

図62.AD857x パワーアップ時間のテスト回路

Rev. D — 19/23 —

## アプリケーション情報

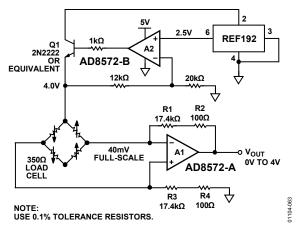

#### 5 V 高精度ストレーン・ゲージ

AD8572 は極めて低いオフセット電圧を持っているため、重量計やストレーン・ゲージのような高ゲインで高精度を必要とするアプリケーションに対して最適なアンプです。図 63に、単電源の高精度ストレーン・ゲージ計測システムの構成を示します。

REF192 は、A2 に 2.5 V の高精度リファレンス電圧を供給します。A2 アンプはこの電圧を増幅して、ストレーン・ゲージ抵抗ブリッジの上側に対して 4.0 V のリファレンス電圧を供給します。Q1 は、350  $\Omega$  ブリッジ回路の駆動電流を供給します。A1 を使ってブリッジ出力を増幅し、フルスケール出力電圧は次式で与えられます。

$$\frac{2 \times (RI + R2)}{R_R} \tag{17}$$

ここで、RBは負荷セルの抵抗。

図 63に示す値を使うと、出力電圧はストレーンなしの 0 V から フル・ストレーンの 4 V まで連続的に変化します。

図63.5 V 高精度ストレーン・ゲージ・アンプ

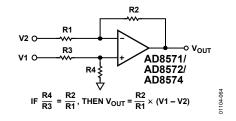

### 3 V 計装アンプ

AD857x ファミリーは高い同相モード除去比、高いオープン・ループ・ゲイン、3 V までの低い動作電源電圧を持つため、ディスクリート単電源計装アンプの優れたオペアンプ選択肢です。 AD857x の同相モード除去比は 120 dB を超えますが、システムの CMRR も外付け抵抗偏差の関数になっています。 図 64に示すディファレンス・アンプのゲインは次のようになります。

$$V_{OUT} = VI\left(\frac{R4}{R3 + R4}\right)\left(1 + \frac{RI}{R2}\right) - V2\left(\frac{R2}{RI}\right)$$

(18)

図64.AD857x をディファレンス・アンプとして使用

理想ディファレンス・アンプでは、抵抗比を次のように設定します。

$$A_V = \frac{R2}{R1} = \frac{R4}{R3} \tag{19}$$

システムの出力電圧を次のように設定します。

$$V_{OUT} = A_V (VI - V2) \tag{20}$$

部品偏差が有限であるため、4 本の抵抗の間の比が精確に等しくないので、不一致によりシステムの同相モード除去比が低下します。図 64から、この同相モード除去比は次のように表すことができます。

$$CMRR = \frac{R1R4 + 2R2R4 + R2R3}{2R1R4 - 2R2R3} \tag{21}$$

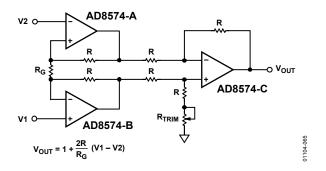

図 65に示す 3 個のオペアンプを使用する計装アンプ構成では、 出力ディファレンス・アンプはユニティ・ゲインに設定され、4 本のすべての抵抗値は一致しています。回路で使用される抵抗 偏差を δ で表すと、計装アンプのワーストケース CMRR は、次 式で表されます。

$$CMRR_{MIN} = \frac{1}{2\delta}$$

(22)

図65.ディスクリート計装アンプ構成

したがって、1%偏差の抵抗を使うと、ワーストケース・システム CMRR は 0.02 すなわち 34 dB になります。高い同相モード除去比を実現するためには、図 65に示すように、高精度抵抗または追加トリミング抵抗を使う必要があります。このトリミング抵抗値は、R 値とその偏差の積に一致する必要があります。たとえば、1%偏差の  $10~k\Omega$  抵抗を使うときは、直列トリミング抵抗を  $100~\Omega$  にする必要があります。

Rev. D — 20/23 —

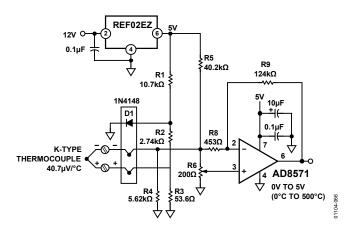

### 高精度熱電対アンプ

図 66 に、冷接点補償を持つ K タイプ熱電対アンプ構成を示します。AD8571 は、5 V 電源からでも、0°C~500°C で 0.02°C より優れた分解能を実現する十分な高精度を提供します。D1 は温度測定デバイスとして使い、熱電対の冷接点誤差を補正するため、2 つの終端接点のできるだけ近くに配置する必要があります。熱電対測定端を 0°C のアイス・バスに浸し、出力が 0 V になるように R6 を調節します。

図 66に示す値を使うと、出力電圧は  $10 \text{ mV/}^{\circ}$ C で温度に追従します。温度計測範囲を広くする場合には、R9 を  $62 \text{ k}\Omega$  に減らすことができます。これにより出力は  $5 \text{ mV/}^{\circ}$ C の変化となり、 $1000^{\circ}$ C までの計測が可能になります。

図66.冷接点補償を持つ高精度 K タイプ熱電対アンプ

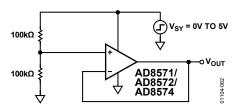

### 高精度電流計

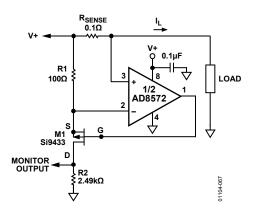

AD857x ファミリーは、単電源で低い入力バイアス電流と小さいオフセット電圧を持つため、高精度電流モニター用の優れたアンプになっています。アンプはレール to レール入力を持つため、ハイサイドまたはローサイドの電流モニターとして使うことができます。AD8572 の両アンプを使うと、負荷の電流供給とリターン・パスのモニター、すなわち故障検出のシンプルな方法が得られます。

図 67 に、ハイサイド電流モニター構成を示します。ここでは、アンプの入力同相モード電圧は正の電源電圧またはその近くにあります。アンプのレール to レール入力は、入力同相モード電圧が電源電圧である場合でも、高精度の測定を可能にします。CMOS 入力構造には入力バイアス電流が流れないため、最小の計測誤差が保証されます。

$0.1~\Omega$  の抵抗により AD857x の非反転入力に電圧降下が発生します。アンプ出力はこの電圧が反転入力に現れるまで補正され、これにより R1 に電流が流れ、R2 にも流れます。モニター出力は次式で表されます。

Monitor Output =

$$R2 \times (R_{SENSE}/R1) \times I_L$$

(23)

図 67に示す部品を使うと、モニター出力の伝達関数は 2.49 V/A になります。

図67.ハイサイド負荷電流モニター

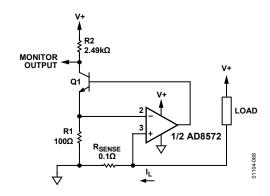

図 68 に、同等のローサイド・モニターを示します。この回路では、AD8572 への入力同相モード電圧はグラウンド付近にあります。この場合も、 $0.1~\Omega$  の抵抗により、リターン電流に比例する電圧降下が得られます。出力電圧は次式で表されます。

$$Monitor Output = V_{+} - \left(\frac{R2}{R1} \times R_{SENSE} \times I_{L}\right)$$

(24)

図 68に示す部品を使うと、モニター出力の伝達関数は V+-2.49 V/A になります。

図68.ローサイド負荷電流モニター

### 高精度電圧コンパレータ

AD857x をオープン・ループで動作させて高精度コンパレータとして使用することができます。AD857x をこの構成で動作させると、50  $\mu$ V 以下のオフセット電圧を持ちます。オフセット電圧のこの僅かな増加は、クローズド・ループ構成で最小オフセットを持つ自動補正アーキテクチャ動作すなわち負帰還が原因になって発生します。デバイスは 50  $\mu$ V のオーバードライブで、伝搬遅延は立ち上がりエッジでは 15  $\mu$ s に、立ち下がりエッジでは 8  $\mu$ s に、それぞれなります。

デバイスの最大差動電圧を超えないように注意する必要があります。詳細については、入力過電圧保護機能のセクションを参照してください。

Rev. D — 21/23 —

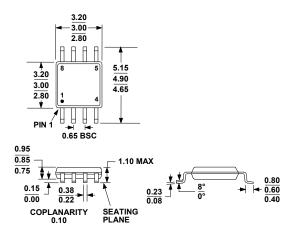

## 外形寸法

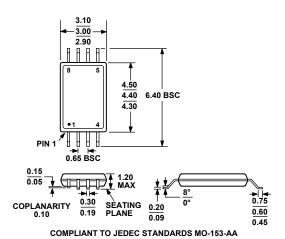

COMPLIANT TO JEDEC STANDARDS MO-187-AA

図69.8 ピン・ミニ・スモール・アウトライン パッケージ[MSOP] (RM-8) 寸法: mm

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

図70.8 ピン標準スモール・アウトライン パッケージ[SOIC\_N] ナロー・ボディ(R-8) 寸法: mm (インチ)

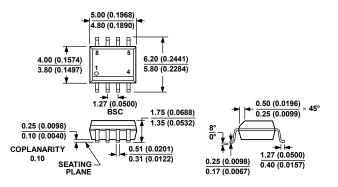

図71.8 ピン薄型シュリンク・スモール・アウトライン パッケージ[TSSOP] (RU-8) 寸法: mm

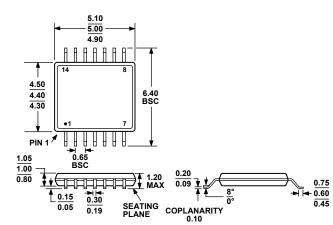

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

図72.14 ピン薄型シュリンク・スモール・アウトライン パッケージ[TSSOP] (RU-14) 寸法: mm

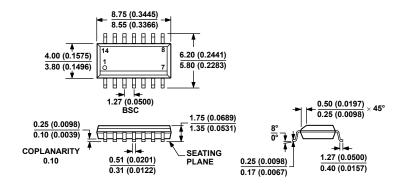

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

### オーダー・ガイド

| Model                        | Temperature Range | Package Description | Package Option | Branding |

|------------------------------|-------------------|---------------------|----------------|----------|

| AD8571AR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571AR-REEL                | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571AR-REEL7               | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ <sup>1</sup>       | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8571ARM-R2                 | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA      |

| AD8571ARM-REEL               | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA      |

| AD8571ARMZ-R2 <sup>1</sup>   | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA#     |

| AD8571ARMZ-REEL <sup>1</sup> | −40°C to +125°C   | 8-Lead MSOP         | RM-8           | AJA#     |

| AD8572AR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572AR-REEL                | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572AR-REEL7               | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ <sup>1</sup>       | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ-REEL <sup>1</sup>  | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARZ-REEL7 <sup>1</sup> | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8572ARU                    | −40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARU-REEL               | −40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARUZ <sup>1</sup>      | -40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8572ARUZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead TSSOP        | RU-8           |          |

| AD8574AR                     | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574AR-REEL                | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574AR-REEL7               | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ <sup>1</sup>       | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ-REEL <sup>1</sup>  | −40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8574ARU                    | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARU-REEL               | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARUZ <sup>1</sup>      | −40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8574ARUZ-REEL <sup>1</sup> | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠品。#は RoHS 準拠品を表し、上部または下部に表示。