# デュアル、16 ビット チャネライザー搭載 12.6 GSPS RF DAC

データシート

**AD9173**

#### 特長

マルチバンド・ワイヤレス・アプリケーションをサポート RF DAC ごとに 3 チャンネルのバイパス可能な複素データ 入力チャンネル

1 入力チャンネルあたり 1.54 GSPS の最大複素入力 データ・レート

1入力チャンネルあたり1個の独立したNCO

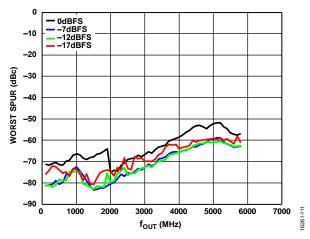

#### 独自の低スプリアス/低歪み設計

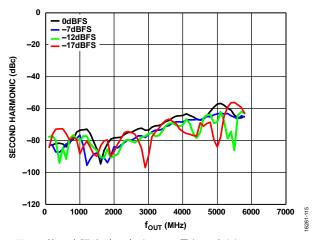

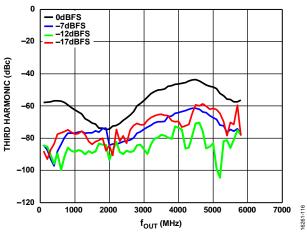

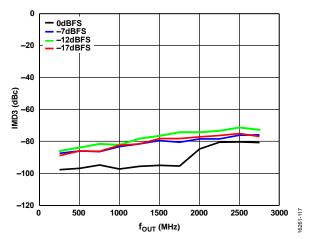

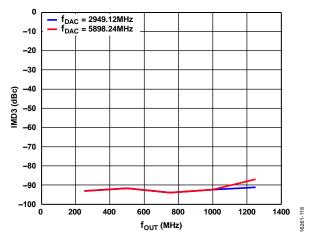

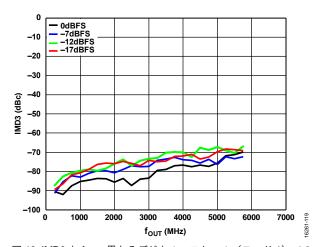

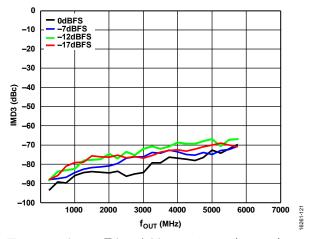

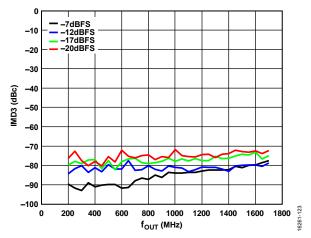

2 トーン IMD = -83 dBc

(1.8 GHz、-7 dBFS/トーンの RF 出力時)

SFDR < -80 dBc(1.8 GHz、-7 dBFS の RF 出力時)

8 レーン、15.4 Gbps の柔軟な JESD204B インターフェース シングルバンドおよびマルチバンドの用途に対応 高データ・スループットを実現する 12 ビット高密度モード をサポート

#### 複数チップの同期

JESD204B サブクラス 1 に対応

あらゆる入力データ・レートに対応する設定変更可能な

インターポレーション・フィルタ

構成可能なデータ・チャンネル・インターポレーション:

1x, 2x, 3x, 4x, 6x, 8x

構成可能な最終インターポレーション:

1x, 2x, 4x, 6x, 8x, 12x

DAC レートで動作する 48 ビット の最終 NCO により、

最大 6 GHz の周波数合成をサポート

送信イネーブル機能による一層の節電と下流回路の保護

高性能、低ノイズの PLL クロック逓倍器

12.6 GSPS の DAC 更新レートをサポート

分周比を選択可能なオブザベーション ADC クロック・ ドライバ

## 低消費電力

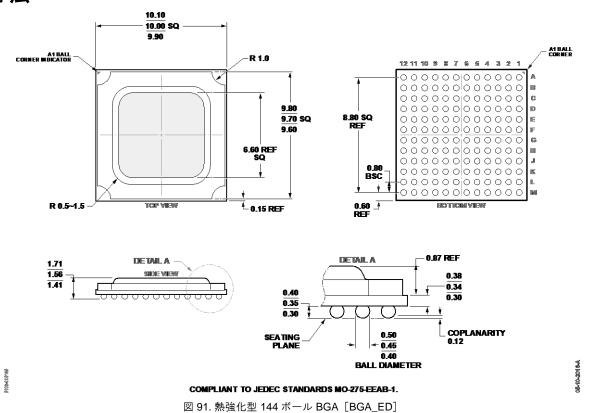

12 GSPS で 2.55 W(デュアル・チャンネル・モード) 10 mm × 10 mm、金属強化サーマル・リッド付き 144 ボール BGA\_ED、0.80 mm ピッチ

#### アプリケーション

ワイヤレス通信インフラストラクチャ マルチパンド基地局無線 マイクロ波/E パンド・パックホール・システム 計測器、自動試験装置(ATE)

## 概要

AD9173 は、最大 12.6 GSPS の DAC サンプル・レートをサポート する高性能なデュアル 16 ビット D/A コンバータ (DAC) です。 15.4 Gbps、8 レーンの JESD204B データ入力ポート、高性能のオンチップ DAC クロック逓倍器に加えて、シングルバンドとマルチバンドのダイレクト to 無線周波数 (RF) ワイヤレス・アプリケーションを対象としたデジタル信号処理機能を備えているのが特長です。

AD9173 は、バイパス可能な複素データ入力を各 RF DAC に 3 チャンネルずつ備えています。各データ入力チャンネルは、設定変更可能なゲイン段、インターポレーション・フィルタ、チャンネル数値制御発振器 (NCO) を備えているので、マルチバンド周波数の設計を柔軟に行えます。入力チャンネルあたり最大 1.54 GSPS の複素データ・レートがサポートされている他、複数の複素入力データ・ストリーム(1.54 GSPS の最大複素データ・レートまで)を集約できます。また、AD9173 ではチャネライザーをバイパスする超広帯域幅モードがサポートされ、3.08 GSPS(16 ビット・シリアライザ/デシリアライザ(SERDES)パッキングを使用する 11 ビット分解能)と、3.4 GSPS(12 ビット SERDES パッキングを使用する 11 ビット分解能)の最大データ・レートが提供されます。

AD9173 は 144 ボール BGA ED パッケージを採用しています。

#### 製品のハイライト

- 1. RF DAC あたり 3 チャンネルのバイパス可能な複素データ 入力チャンネルでシングルバンドとマルチバンドのワイヤ レス・アプリケーションをサポートします。最大複素入力 データ・レートは 11 ビット分解能で 1.54 GSPS、16 ビット 分解能で 1.23 GSPS です。各入力チャンネルには 1 つずつ 独立した NCO が備わっています。

- 超広帯域幅チャンネル・バイパス・モードでは、11 ビット 分解能で 16 ビット SERDES パッキングの場合 3.08 GSPS、 11 ビット分解能で 12 ビット SERDES パッキングの場合 3.4 GSPS の最大データ・レートがサポートされます。

- 3. 低消費電力のデュアル・コンバータによって、高帯域幅の マルチチャンネル・アプリケーションに必要とされる消費 電力を削減することができます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2018 Analog Devices, Inc. All rights reserved

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 40F 電話 052 (569) 6300

# 目次

| 世界                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 特長                           | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

| 製品のハイライト                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | アプリケーション                     | 1  |

| 改訂履歴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 概要                           | 1  |

| 機能ブロック図                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 製品のハイライト                     | 1  |

| 仕様       2         DC 仕様       2         最大 DAC 更新レート仕様       2         電源の DC 仕様       2         シリアル・ポートと CMOS ピンの仕様       2         デジタル入力データのタイミング仕様       2         JESD204B インターフェースの電気的仕様と速度仕様       10         入力データ・レートと信号帯域幅の仕様       10         AC 仕様       11         地対最大定格       13         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2         動作原理       25         シリアル・ポートの動作       25         データ・フォーマット       25 | 改訂履歴                         | 2  |

| DC 仕様                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 機能ブロック図                      | 3  |

| デジタル仕様       第         電源の DC 仕様       6         シリアル・ポートと CMOS ピンの仕様       8         デジタル入力データのタイミング仕様       9         JESD204B インターフェースの電気的仕様と速度仕様       10         入力データ・レートと信号帯域幅の仕様       10         AC 仕様       11         絶対最大定格       13         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2         動作原理       25         シリアル・ポートの動作       25         データ・フォーマット       25                                                  | 仕様                           | 2  |

| 最大 DAC 更新レート仕様                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DC 仕様                        | 2  |

| 電源の DC 仕様                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | デジタル仕様                       | 5  |

| シリアル・ポートと CMOS ピンの仕様       8         デジタル入力データのタイミング仕様       9         JESD204B インターフェースの電気的仕様と速度仕様       10         入力データ・レートと信号帯域幅の仕様       11         AC 仕様       11         絶対最大定格       12         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2c         動作原理       2c         シリアル・ポートの動作       2c         データ・フォーマット       2c                                                                                                  | 最大 DAC 更新レート仕様               | 5  |

| デジタル入力データのタイミング仕様       9         JESD204B インターフェースの電気的仕様と速度仕様       10         入力データ・レートと信号帯域幅の仕様       10         AC 仕様       11         絶対最大定格       12         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       22         動作原理       25         シリアル・ポートの動作       27         データ・フォーマット       27                                                                                                                                       | 電源の DC 仕様                    | 6  |

| JESD204B インターフェースの電気的仕様と速度仕様       10         入力データ・レートと信号帯域幅の仕様       11         AC 仕様       11         絶対最大定格       13         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2c         動作原理       2c         シリアル・ポートの動作       2c         データ・フォーマット       2c                                                                                                                                                                         | シリアル・ポートと CMOS ピンの仕様         | 8  |

| 入力データ・レートと信号帯域幅の仕様       10         AC 仕様       11         絶対最大定格       12         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       22         動作原理       25         シリアル・ポートの動作       27         データ・フォーマット       27                                                                                                                                                                                                                       | デジタル入力データのタイミング仕様            | 9  |

| AC 仕様       11         絶対最大定格       13         リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       22         動作原理       25         シリアル・ポートの動作       27         データ・フォーマット       27                                                                                                                                                                                                                                                           | JESD204B インターフェースの電気的仕様と速度仕様 | 10 |

| 絶対最大定格       13         リフロー・プロファイル       13         熱特性       12         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       22         動作原理       25         シリアル・ポートの動作       25         データ・フォーマット       25                                                                                                                                                                                                                                                                                  | 入力データ・レートと信号帯域幅の仕様           | 10 |

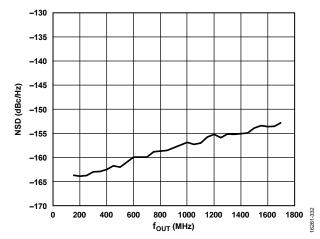

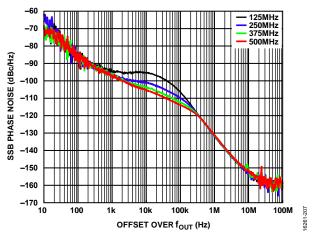

| リフロー・プロファイル       13         熱特性       13         ESD に関する注意       13         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2c         動作原理       2c         シリアル・ポートの動作       2c         データ・フォーマット       2c                                                                                                                                                                                                                                                                                                          | AC 仕様                        | 11 |

| 熱特性15ESD に関する注意15ピン配置およびピン機能説明14代表的な性能特性17用語の定義22動作原理25シリアル・ポートの動作25データ・フォーマット27                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 絶対最大定格                       | 13 |

| ESD に関する注意       15         ピン配置およびピン機能説明       14         代表的な性能特性       17         用語の定義       2c         動作原理       2c         シリアル・ポートの動作       2c         データ・フォーマット       2c                                                                                                                                                                                                                                                                                                                                                            | リフロー・プロファイル                  | 13 |

| ピン配置およびピン機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 熱特性                          | 13 |

| 代表的な性能特性       17         用語の定義       2c         動作原理       2c         シリアル・ポートの動作       2c         データ・フォーマット       2c                                                                                                                                                                                                                                                                                                                                                                                                                       | ESD に関する注意                   | 13 |

| 用語の定義       22         動作原理       25         シリアル・ポートの動作       27         データ・フォーマット       27                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ピン配置およびピン機能説明                | 14 |

| 動作原理                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 代表的な性能特性                     | 17 |

| シリアル・ポートの動作27<br>データ・フォーマット27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 用語の定義                        | 24 |

| データ・フォーマット27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 動作原理                         | 25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | シリアル・ポートの動作                  | 27 |

| シリアル・ポート・ピンの説明27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | データ・フォーマット                   | 27 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | シリアル・ポート・ピンの説明               | 27 |

| シリアル・ホート・オフション             | 27  |

|----------------------------|-----|

| JESD204B シリアル・データ・インターフェース | 29  |

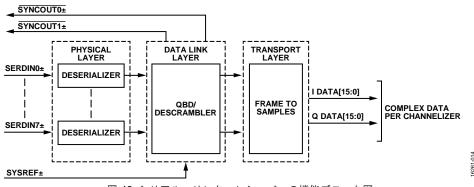

| JESD204B の概要               | 29  |

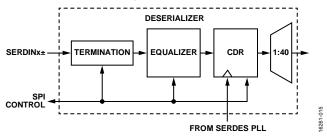

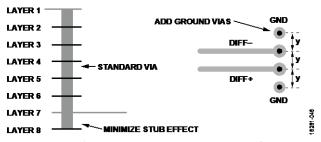

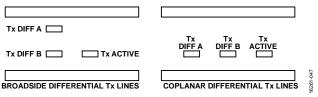

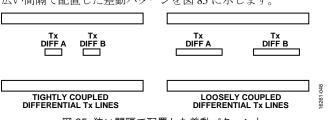

| 物理層                        | 32  |

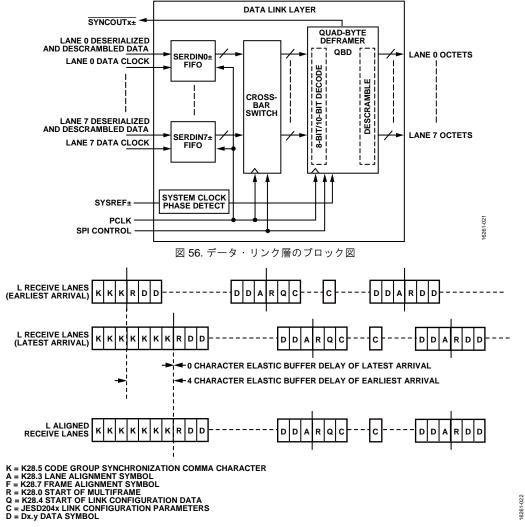

| データ・リンク層                   | 34  |

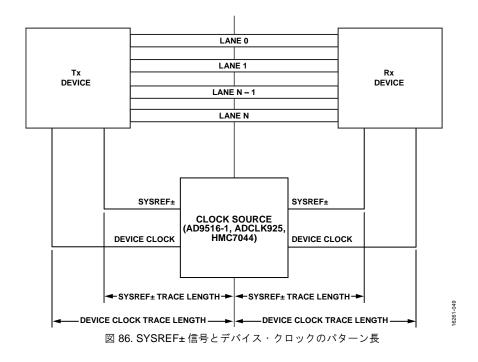

| LMFC 信号同期                  | 37  |

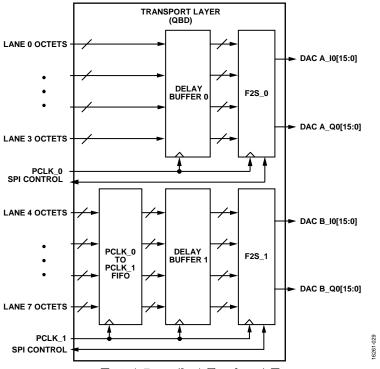

| トランスポート層                   | 42  |

| JESD204B のテスト・モード          | 43  |

| JESD204B のエラー・モニタリング       | 45  |

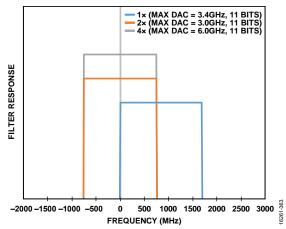

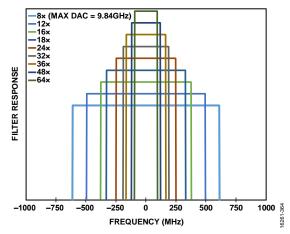

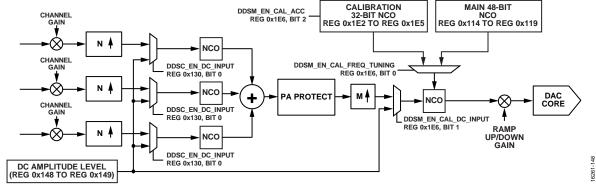

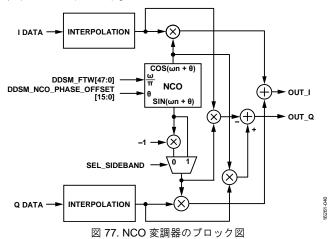

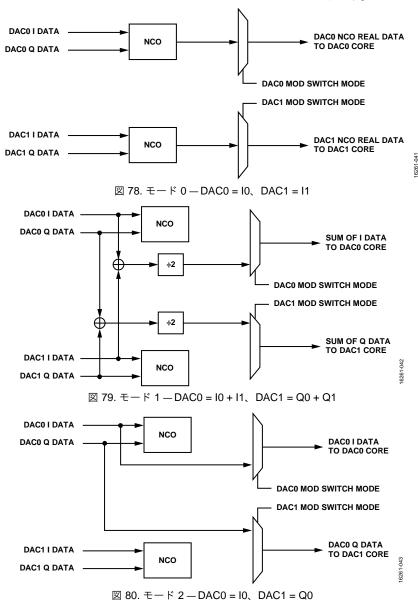

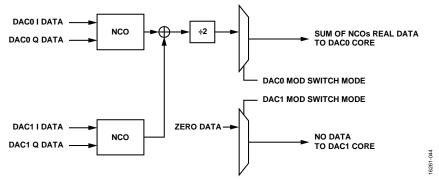

| デジタル・データパス                 | 48  |

| 合計データパス・インターポレーション         | 48  |

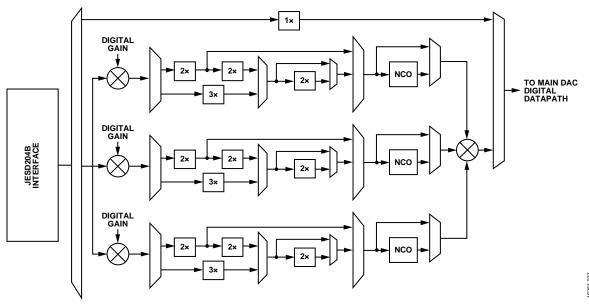

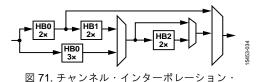

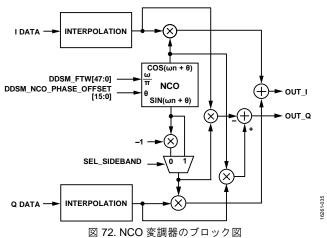

| チャンネル・デジタル・データパス           | 50  |

| メイン・デジタル・データパス             | 53  |

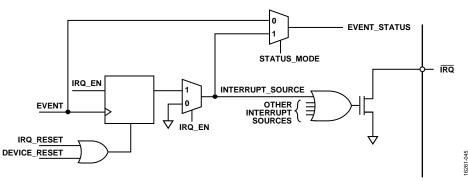

| 割込み要求動作                    | 59  |

| 割込みサービス・ルーチン               | 59  |

| アプリケーション情報                 | 60  |

| ハードウェアに関する考慮事項             | 60  |

| アナログ・インターフェースに関する考慮事項      | 63  |

| DAC 入力クロック設定               | 63  |

| クロック出力ドライバ                 | 65  |

| アナログ出力                     | 65  |

| スタートアップ・シーケンス              | 66  |

| レジスタの一覧                    | 73  |

| レジスタの詳細                    | 81  |

| 外形寸法                       | 142 |

|                            |     |

# 改訂履歴

11/2017—Revision 0: Initial Version

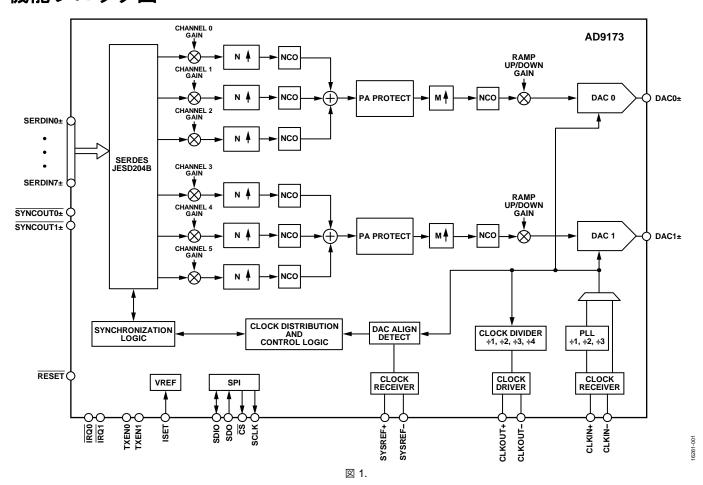

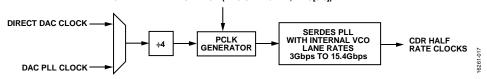

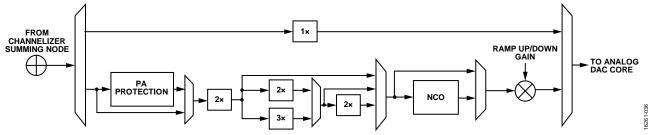

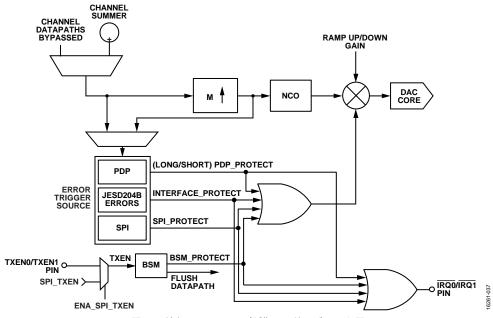

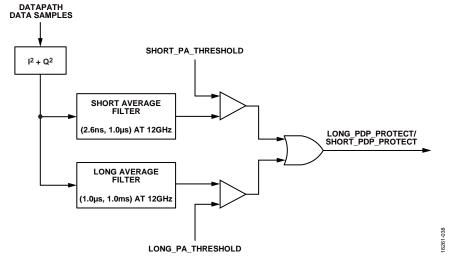

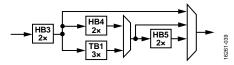

# 機能ブロック図

Rev. 0 - 3/142 -

# 仕様

# DC 仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20 mA。 最小値と最大値は  $T_{J}$  = -40  $^{\circ}$ C  $\sim$  +118  $^{\circ}$ C での値、代表値は  $T_{A}$  = 25  $^{\circ}$ C  $(T_{J}$  = 51  $^{\circ}$ C に相当)での値。

表 1.

| Parameter                                   | Test Conditions/Comments                     | Min   | Тур   | Max  | Unit   |

|---------------------------------------------|----------------------------------------------|-------|-------|------|--------|

| RESOLUTION                                  |                                              | 16    |       |      | Bit    |

| ACCURACY                                    |                                              |       |       |      |        |

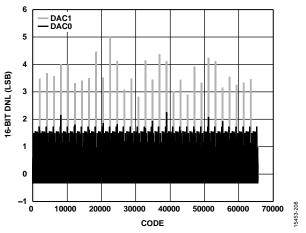

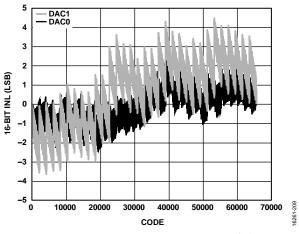

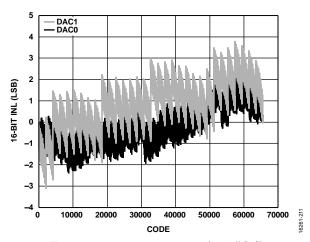

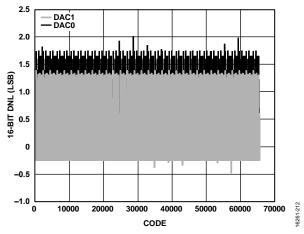

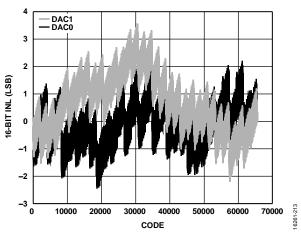

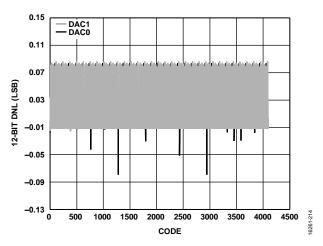

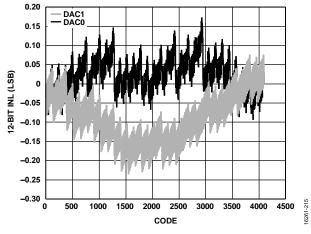

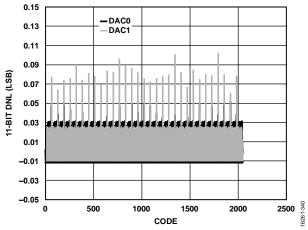

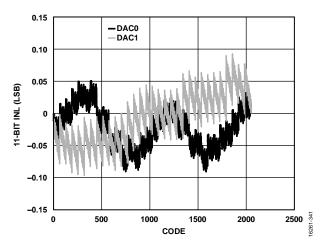

| Integral Nonlinearity (INL)                 |                                              |       | ±7    |      | LSB    |

| Differential Nonlinearity (DNL)             |                                              |       | ±7    |      | LSB    |

| ANALOG OUTPUTS (DAC0+, DAC0-, DAC1+, DAC1-) |                                              |       |       |      |        |

| Gain Error (with Internal ISET Reference)   |                                              |       | ±15   |      | %      |

| Full-Scale Output Current                   |                                              |       |       |      |        |

| Minimum                                     | $R_{SET} = 5 \text{ k}\Omega$                | 14.2  | 16    | 17.8 | mA     |

| Maximum                                     | $R_{SET} = 5 \text{ k}\Omega$                | 23.6  | 26    | 28.8 | mA     |

| Common-Mode Voltage                         |                                              |       | 0     |      | V      |

| Differential Impedance                      |                                              |       | 100   |      | Ω      |

| DAC DEVICE CLOCK INPUT (CLKIN+, CLKIN-)     |                                              |       |       |      |        |

| Differential Input Power                    | $R_{LOAD} = 100 \Omega$ differential on-chip |       |       |      |        |

| Minimum                                     |                                              |       | 0     |      | dBm    |

| Maximum                                     |                                              |       | 6     |      | dBm    |

| Differential Input Impedance <sup>1</sup>   |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                         | AC-coupled                                   |       | 0.5   |      | V      |

| CLOCK OUTPUT DRIVER (CLKOUT+, CLKOUT-)      |                                              |       |       |      |        |

| Differential Output Power                   |                                              |       |       |      |        |

| Minimum                                     |                                              |       | -9    |      | dBm    |

| Maximum                                     |                                              |       | 0     |      | dBm    |

| Differential Output Impedance               |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                         | AC-coupled                                   |       | 0.5   |      | V      |

| Output Frequency                            |                                              | 727.5 |       | 3000 | MHz    |

| TEMPERATURE DRIFT                           |                                              |       |       |      |        |

| Gain                                        |                                              |       | 10    |      | ppm/°C |

| REFERENCE                                   |                                              |       |       |      |        |

| Internal Reference Voltage                  |                                              |       | 0.495 |      | V      |

| ANALOG SUPPLY VOLTAGES                      |                                              |       |       |      |        |

| AVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

| AVDD1.8                                     |                                              | 1.71  | 1.8   | 1.89 | V      |

| DIGITAL SUPPLY VOLTAGES                     |                                              |       |       |      |        |

| DVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

| DAVDD1.0                                    |                                              | 0.95  | 1.0   | 1.05 | V      |

| DVDD1.8                                     |                                              | 1.71  | 1.8   | 1.89 | V      |

| SERDES SUPPLY VOLTAGES                      |                                              |       |       |      |        |

| SVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

<sup>&</sup>lt;sup>1</sup>詳細については、DAC入力クロック設定のセクションを参照してください。

Rev. 0 - 4/142 -

## デジタル仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC  $I_{OUTFS}$  = 20 mA。 最小値と最大値は  $T_J$  = -40 °C  $\sim$  +118 °C での値、代表値は  $T_A$  = 25 °C( $T_J$  = 51 °C に相当)での値。

表 2.

| Parameter                                                                        | Test Conditions/Comments                           | Min  | Тур | Max   | Unit |

|----------------------------------------------------------------------------------|----------------------------------------------------|------|-----|-------|------|

| DAC UPDATE RATE                                                                  |                                                    |      |     |       |      |

| Minimum                                                                          |                                                    |      |     | 2.91  | GSPS |

| Maximum <sup>1</sup>                                                             | 16-bit resolution, with interpolation              | 12.6 |     |       | GSPS |

|                                                                                  | 11-bit resolution, with interpolation              | 12.6 |     |       | GSPS |

|                                                                                  | 11-bit resolution, no interpolation                | 3.4  |     |       | GSPS |

| Adjusted <sup>2</sup>                                                            | 16-bit resolution, with interpolation <sup>3</sup> | 1.23 |     |       | GSPS |

|                                                                                  | 11-bit resolution, with interpolation              | 1.54 |     |       | GSPS |

|                                                                                  | 11-bit resolution, no interpolation <sup>4</sup>   | 3.4  |     |       | GSPS |

| DAC PHASE-LOCKED LOOP (PLL) VOLTAGE CONTROLLED OSCILLATOR (VCO) FREQUENCY RANGES |                                                    |      |     |       |      |

| VCO Output Divide by 1                                                           |                                                    | 8.74 |     | 12.42 | GSPS |

| VCO Output Divide by 2                                                           |                                                    | 4.37 |     | 6.21  | GSPS |

| VCO Output Divide by 3                                                           |                                                    | 2.91 |     | 4.14  | GSPS |

| PHASE FREQUENCY DETECT INPUT FREQUENCY RANGES                                    |                                                    |      |     |       |      |

| 9.96 GHz ≤ VCO Frequency ≤ 10.87 GHz                                             |                                                    | 25   |     | 225   | MHz  |

| VCO Frequency < 9.96 GHz or VCO Frequency > 10.87 GHz                            |                                                    | 25   |     | 770   | MHz  |

| DAC DEVICE CLOCK INPUT (CLKIN+, CLKIN-) FREQUENCY RANGES                         |                                                    |      |     |       |      |

| PLL Off                                                                          |                                                    | 2.91 |     | 12.6  | GHz  |

| PLL On                                                                           | M divider set to divide by 1                       | 25   |     | 770   | MHz  |

|                                                                                  | M divider set to divide by 2                       | 50   |     | 1540  | MHz  |

|                                                                                  | M divider set to divide by 3                       | 75   |     | 2310  | MHz  |

|                                                                                  | M divider set to divide by 4                       | 100  |     | 3080  | MHz  |

<sup>&</sup>lt;sup>1</sup>最大 DAC 更新レートは、選択した JESD204B モードと、その構成で使用するレーン・レートによって異なります。 レーン・レートと電源電圧レベルに応じた最大 DAC レートは表 3 に示します。

## 最大 DAC 更新レート仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC  $I_{OUTFS} = 20 \text{ mA}$ 。 最小値と最大値は  $T_J = -40 \, ^{\circ}\text{C} \sim +118 \, ^{\circ}\text{C}$  での値、代表値は  $T_A = 25 \, ^{\circ}\text{C}$  に相当)での値。

表 3.

| Parameter                   | Test Conditions/Comments | Min   | Тур | Max | Unit |

|-----------------------------|--------------------------|-------|-----|-----|------|

| MAXIMUM DAC UPDATE RATE     |                          |       |     |     |      |

| $SVDD1.0 = 1.0~V \pm 5\%$   |                          |       |     |     |      |

|                             | Lane rate > 11 Gbps      | 11.67 |     |     | GSPS |

|                             | Lane rate ≤ 11 Gbps      | 12.37 |     |     | GSPS |

| $SVDD1.0 = 1.0 V \pm 2.5\%$ |                          |       |     |     |      |

|                             | Lane rate > 11 Gbps      | 11.79 |     |     | GSPS |

|                             | Lane rate ≤ 11 Gbps¹     | 12.6  |     |     | GSPS |

<sup>&</sup>lt;sup>1</sup>表 2 に示すように、オンチップ PLL を使用する場合の最大 DAC 速度は、12.42 GSPS の最大 PLL 速度に制限されます。

Rev. 0 - 5/142 -

<sup>&</sup>lt;sup>2</sup> 調整 DAC 更新レートは、f<sub>DAC</sub> を使用モードの最小必要インターポレーション係数または最大チャンネル・データ・レートで除した値として計算します。 表 13 に示すように、モードが異なれば最大 DAC 更新レート、最小インターポレーション係数、最大チャンネル・データ・レートも異なります。

<sup>31.23</sup> GSPS の調整 DAC 更新レートは、すべての 16 ビット分解能モード動作を通じた最大の値です。詳細については、表 13 を参照してください。

<sup>4</sup> GSPS の調整 DAC 更新レートは、すべての 11 ビット分解能モード動作を通じた最大の値です。詳細については、表 13 を参照してください。

# 電源の DC 仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC  $I_{OUTFS}$  = 20 mA。 最小値と最大値は  $T_J$  = -40  $^{\circ}$ C  $\sim$  +118  $^{\circ}$ C での値、代表値は  $T_A$  = 25  $^{\circ}$ C  $(T_J$  = 51  $^{\circ}$ C に相当)での値。

表 4.

| Parameter                                 | Test Conditions/Comments                                                                                                                                                                                                                          | Min | Тур  | Max  | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| DUAL-LINK MODES                           |                                                                                                                                                                                                                                                   |     |      |      |      |

| Mode 1 (L = 2, M = 4, NP<br>= 16, N = 16) | 11.7965 GSPS DAC rate, 184.32 MHz PLL reference clock, 32× total interpolation (4×, 8×), 40 MHz tone at -3 dBFS, channel gain = -6 dB, channel NCOs = ±150 MHz, main NCO = 2 GHz, SYNCOUTx± in LVDS mode                                          |     |      |      |      |

| AVDD1.0                                   | All supply levels set to nominal values                                                                                                                                                                                                           |     | 725  | 1020 | mA   |

|                                           | All supply levels set to 5% tolerance                                                                                                                                                                                                             |     | 775  | 1120 | mA   |

| AVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 110  | 130  | mA   |

| DVDD1.0                                   | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                                                             |     |      |      |      |

|                                           | All supply levels set to nominal values                                                                                                                                                                                                           |     | 1270 | 1670 | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 1350 | 1850 | mA   |

| DVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 35   | 50   | mA   |

| SVDD1.0                                   |                                                                                                                                                                                                                                                   |     |      |      |      |

|                                           | All supply levels set to nominal values                                                                                                                                                                                                           |     | 290  | 510  | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 305  | 560  | mA   |

| Total Power Dissipation                   |                                                                                                                                                                                                                                                   |     | 2.55 | 3.38 | W    |

| Mode 4 (L = 4, M = 4, NP<br>= 16, N = 16) | 11.7965 GSPS DAC rate, 491.52 MHz PLL reference clock, $24 \times$ total interpolation ( $3 \times$ , $8 \times$ ), 40 MHz tone at $-3$ dBFS, channel gain = $-6$ dB, channel NCOs = $\pm 150$ MHz, main NCO = 2 GHz, SYNCOUTx $\pm$ in LVDS mode |     |      |      |      |

| AVDD1.0                                   |                                                                                                                                                                                                                                                   |     | 725  |      | mA   |

| AVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 110  |      | mA   |

| DVDD1.0                                   | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                                                             |     | 1340 |      | mA   |

| DVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 35   |      | mA   |

| SVDD1.0                                   |                                                                                                                                                                                                                                                   |     | 425  |      | mA   |

| Total Power Dissipation                   |                                                                                                                                                                                                                                                   |     | 2.75 |      | W    |

| Mode 0 (L = 1, M = 2, NP<br>= 16, N = 16) | 5.89824 GSPS DAC rate, 184.32 MHz PLL reference clock, 16× total interpolation (2×, 8×), 40 MHz tone at -3 dBFS, channel NCO disabled, main NCO = 1.8425 GHz, SYNCOUTx± in LVDS mode                                                              |     |      |      |      |

| AVDD1.0                                   | All supply levels set to nominal values                                                                                                                                                                                                           |     | 400  | 670  | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 425  | 745  | mA   |

| AVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 110  | 130  | mA   |

| DVDD1.0                                   | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                                                             |     |      |      |      |

|                                           | All supply levels set to nominal values                                                                                                                                                                                                           |     | 625  | 960  | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 670  | 1070 | mA   |

| DVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 35   | 50   | mA   |

| SVDD1.0                                   |                                                                                                                                                                                                                                                   |     | 175  | 340  | mA   |

| Total Power Dissipation                   |                                                                                                                                                                                                                                                   |     | 1.45 | 2.15 | W    |

| Mode 3 (L = 2, M = 2, NP<br>= 16, N = 16) | 11.7965 GSPS DAC rate, 184.32 MHz PLL reference clock, 24× total interpolation (3×, 8×), 40 MHz tone at -3 dBFS, channel NCO disabled, main NCO = 2.655 GHz, SYNCOUTx± in LVDS mode                                                               |     |      |      |      |

| AVDD1.0                                   | All supply levels set to nominal values                                                                                                                                                                                                           |     | 725  |      | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 775  |      | mA   |

| AVDD1.8                                   |                                                                                                                                                                                                                                                   |     | 110  |      | mA   |

| DVDD1.0                                   | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                                                             |     |      |      |      |

| 2.221.0                                   | All supply levels set to nominal values                                                                                                                                                                                                           |     | 1175 |      | mA   |

|                                           | All supplies at 5% tolerance                                                                                                                                                                                                                      |     | 1250 |      | mA   |

Rev. 0 - 6/142 -

| Parameter                                                              | Test Conditions/Comments                                                                                                                                                                              | Min | Тур  | Max   | Unit       |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|

| DVDD1.8                                                                |                                                                                                                                                                                                       |     | 35   |       | mA         |

| SVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 245  |       | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 250  |       | mA         |

| Total Power Dissipation                                                |                                                                                                                                                                                                       |     | 2.4  |       | W          |

| Mode 2 (L = 3, M = 6, NP<br>= 16, N = 16)                              | 12 GSPS DAC rate, 375 MHz PLL reference clock, 48× total interpolation (6×, 8×), 30 MHz tone at -3 dBFS, channel gain = -11 dB, channel NCOs = 20 MHz, main NCO = 2.1 GHz                             |     |      |       |            |

| AVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 735  | 1030  | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 785  | 1135  | mA         |

| AVDD1.8                                                                |                                                                                                                                                                                                       |     | 110  | 130   | mA         |

| DVDD1.0                                                                | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                 |     |      |       | mA         |

|                                                                        | All supply levels set to nominal values                                                                                                                                                               |     | 1370 | 1800  | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 1460 | 1980  | mA         |

| DVDD1.8                                                                |                                                                                                                                                                                                       |     | 35   | 50    | mA         |

| SVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 410  | 680   | mA         |

| 2.22.0                                                                 | All supplies at 5% tolerance                                                                                                                                                                          |     | 430  | 755   | mA         |

| Total Power Dissipation                                                | This applies at 5 % tolerance                                                                                                                                                                         |     | 2.77 | 3.69  | W          |

| SINGLE-LINK MODES                                                      |                                                                                                                                                                                                       |     | 2.77 | 5.07  | <b>'</b> ' |

| Mode 17 ( $L = 8$ , $M = 2$ , $NP$                                     | 3.4 GSPS DAC rate, 187.5 MHz PLL reference clock, $1 \times$ total interpolation $(1 \times, 1 \times)$ , 1.2                                                                                         |     |      |       |            |

| = 12, N = 11                                                           | GHz tone at $-3$ dBFS, channel and main NCOs disabled                                                                                                                                                 |     |      |       |            |

| AVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 260  | 510   | mA         |

| 11,001.0                                                               | All supplies at 5% tolerance                                                                                                                                                                          |     | 275  | 580   | mA         |

| AVDD1.8                                                                | This applies at 5 % tolerance                                                                                                                                                                         |     | 85   | 100   | mA         |

| DVDD1.0                                                                | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                 |     | 03   | 100   | 1111       |

| D 1 DD1.0                                                              | All supply levels set to nominal values                                                                                                                                                               |     | 300  | 610   | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 310  | 710   | mA         |

| DVDD1.8                                                                | All supplies at 5% tolerance                                                                                                                                                                          |     | 25   | 50    |            |

|                                                                        | All                                                                                                                                                                                                   |     |      |       | mA         |

| SVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 500  | 780   | mA         |

| T-4-1 D Dii+i                                                          | All supplies at 5% tolerance                                                                                                                                                                          |     | 505  | 860   | mA         |

| Total Power Dissipation                                                |                                                                                                                                                                                                       |     | 1.2  | 2.05  | W          |

| DUAL-LINK, MODE 3 (NCO<br>ONLY, SINGLE-<br>CHANNEL MODE, NO<br>SERDES) | 6 GSPS DAC rate, 300 MHz PLL reference clock, $8\times$ total interpolation ( $1\times$ , $8\times$ ), no input tone (dc internal level = $0x50FF$ ), channel NCO = $40$ MHz, main NCO = $1.8425$ GHz |     |      |       |            |

| Mode 3                                                                 |                                                                                                                                                                                                       |     |      |       |            |

| AVDD1.0                                                                |                                                                                                                                                                                                       |     |      |       |            |

|                                                                        | All supply levels set to nominal values                                                                                                                                                               |     | 410  | 660   | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 435  | 750   | mA         |

| AVDD1.8                                                                |                                                                                                                                                                                                       |     | 110  | 130   | mA         |

| DVDD1.0                                                                | Combined current consumption with the DAVDD1.0 supply                                                                                                                                                 |     |      |       |            |

|                                                                        | All supply levels set to nominal values                                                                                                                                                               |     | 500  | 780   | mA         |

|                                                                        | All supplies at 5% tolerance                                                                                                                                                                          |     | 515  | 950   | mA         |

| DVDD1.8                                                                | **                                                                                                                                                                                                    |     | 0.3  | 1     | mA         |

| SVDD1.0                                                                | All supply levels set to nominal values                                                                                                                                                               |     | 5    | 100   | mA         |

| ~                                                                      | All supplies at 5% tolerance                                                                                                                                                                          |     | 3    | 120   | mA         |

| Total Power Dissipation                                                |                                                                                                                                                                                                       |     | 1.1  | 1.671 | W          |

Rev. 0 - 7/142 -

| Parameter                              | Test Conditions/Comments                                                                      | Min | Тур  | Max   | Unit |

|----------------------------------------|-----------------------------------------------------------------------------------------------|-----|------|-------|------|

| DUAL-LINK, MODE 4 (NCO                 | 12 GSPS DAC rate, 500 MHz PLL reference clock, 32× total interpolation (4×, 8×), no           |     |      |       |      |

| ONLY, DUAL-CHANNEL<br>MODE. NO SERDES) | input tone (dc internal level = $0x2AFF$ ), channel NCOs = $\pm 150$ MHz, main NCO = $2$ GHz. |     |      |       |      |

| Mode 4                                 | Oliz                                                                                          |     |      |       |      |

| AVDD1.0                                | All supply levels set to nominal values                                                       |     | 750  | 1030  | mA   |

|                                        | All supplies at 5% tolerance                                                                  |     | 790  | 1130  | mA   |

| AVDD1.8                                |                                                                                               |     | 110  | 130   | mA   |

| DVDD1.0                                | Combined current consumption with the DAVDD1.0 supply                                         |     |      |       |      |

|                                        | All supply levels set to nominal values                                                       |     | 1200 | 1590  | mA   |

|                                        | All supplies at 5% tolerance                                                                  |     | 1300 | 1750  | mA   |

| DVDD1.8                                |                                                                                               |     | 0.3  | 1     | mA   |

| SVDD1.0                                |                                                                                               |     | 5    | 100   | mA   |

| Total Power Dissipation                |                                                                                               |     | 2.2  | 2.851 | W    |

# シリアル・ポートと CMOS ピンの仕様

表 5.

| 衣 5.                                             | 0                         | T10                                 | 1 NA: | <b>T</b> | N.4   | 11.2 |

|--------------------------------------------------|---------------------------|-------------------------------------|-------|----------|-------|------|

| Parameter                                        | Symbol                    | Test Comments/Conditions            | Min   | Тур      | Max   | Unit |

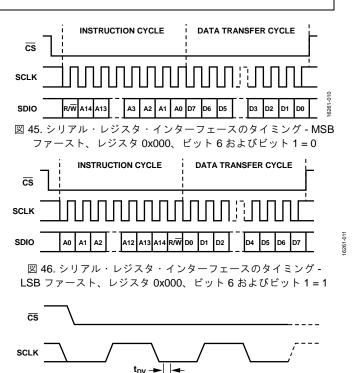

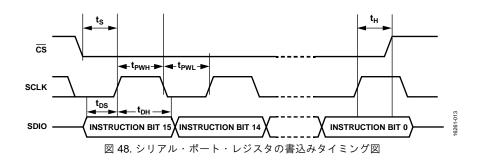

| WRITE OPERATION                                  |                           | See Figure 48                       |       |          |       |      |

| Maximum SCLK Clock Rate                          | $f_{SCLK}$ , $1/t_{SCLK}$ |                                     | 80    |          |       | MHz  |

| SCLK Clock High                                  | $t_{PWH}$                 | SCLK = 20 MHz                       | 5.03  |          |       | ns   |

| SCLK Clock Low                                   | $t_{PWL}$                 | SCLK = 20 MHz                       | 1.6   |          |       | ns   |

| SDIO to SCLK Setup Time                          | $t_{DS}$                  |                                     | 1.154 |          |       | ns   |

| SCLK to SDIO Hold Time                           | $t_{\mathrm{DH}}$         |                                     | 0.577 |          |       | ns   |

| CS to SCLK Setup Time                            | $t_S$                     |                                     | 1.036 |          |       | ns   |

| SCLK to CS Hold Time                             | t <sub>H</sub>            |                                     | -5.3  |          |       | ps   |

| READ OPERATION                                   |                           | See Figure 47                       |       |          |       |      |

| SCLK Clock Rate                                  | $f_{SCLK}$ , $1/t_{SCLK}$ |                                     |       |          | 48.58 | MHz  |

| SCLK Clock High                                  | $t_{PWH}$                 |                                     | 5.03  |          |       | ns   |

| SCLK Clock Low                                   | $t_{PWL}$                 |                                     | 1.6   |          |       | ns   |

| SDIO to SCLK Setup Time                          | $t_{DS}$                  |                                     | 1.158 |          |       | ns   |

| SCLK to SDIO Hold Time                           | $t_{\mathrm{DH}}$         |                                     | 0.537 |          |       | ns   |

| CS to SCLK Setup Time                            | $t_S$                     |                                     | 1.036 |          |       | ns   |

| SCLK to SDIO Data Valid Time                     | $t_{\mathrm{DV}}$         |                                     | 9.6   |          |       | ns   |

| SCLK to SDO Data Valid Time                      | $t_{DV}$                  |                                     | 13.7  |          |       | ns   |

| CS to SDIO Output Valid to High-Z                |                           | Not shown in Figure 47 or Figure 48 | 5.4   |          |       | ns   |

| CS to SDO Output Valid to High-Z                 |                           | Not shown in Figure 47 or Figure 48 | 9.59  |          |       | ns   |

| INPUTS (SDIO, SCLK, CS, RESET, TXEN0, and TXEN1) |                           |                                     |       |          |       |      |

| Voltage Input                                    |                           |                                     |       |          |       |      |

| High                                             | $V_{IH}$                  |                                     | 1.48  |          |       | V    |

| Low                                              | $V_{\rm IL}$              |                                     |       |          | 0.425 | V    |

| Current Input                                    |                           |                                     |       |          |       |      |

| High                                             | $I_{IH}$                  |                                     |       |          | ±100  | nA   |

| Low                                              | $I_{\rm IL}$              |                                     | ±100  |          |       | nA   |

| OUTPUTS (SDIO, SDO)                              |                           |                                     |       |          |       |      |

| Voltage Output                                   |                           |                                     |       |          |       |      |

| High                                             | $V_{OH}$                  |                                     |       |          |       |      |

| 0 mA load                                        |                           |                                     | 1.69  |          |       | V    |

| 4 mA load                                        |                           |                                     | 1.52  |          |       | V    |

Rev. 0 - 8/142 -

| Parameter                      | Symbol            | Test Comments/Conditions | Min  | Тур | Max   | Unit |

|--------------------------------|-------------------|--------------------------|------|-----|-------|------|

| Low                            | $V_{OL}$          |                          |      |     |       |      |

| 0 mA load                      |                   |                          |      |     | 0.045 | V    |

| 4 mA load                      |                   |                          |      |     | 0.175 | V    |

| Current Output                 |                   |                          |      |     |       |      |

| High                           | $I_{OH}$          |                          |      | 4   |       | mA   |

| Low                            | $I_{OL}$          |                          |      | 4   |       | mA   |

| INTERRUPT OUTPUTS (IRQ0, IRQ1) |                   |                          |      |     |       |      |

| Voltage Output                 |                   |                          |      |     |       |      |

| High                           | $V_{\mathrm{OH}}$ |                          | 1.71 |     |       | V    |

| Low                            | $V_{OL}$          |                          |      |     | 0.075 | V    |

# デジタル入力データのタイミング仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC I<sub>OUTFS</sub> = 20 mA。 最小値と最大値は  $T_J$  = -40  $^{\circ}$   $^{\circ$

表 6.

| Parameter                                                           | Test Conditions/Comments                                   | Min | Тур  | Max | Unit              |

|---------------------------------------------------------------------|------------------------------------------------------------|-----|------|-----|-------------------|

| LATENCY <sup>1</sup>                                                |                                                            |     |      |     |                   |

| Channel Interpolation Factor, Main<br>Datapath Interpolation Factor | LMFC_VAR_x = 12, LMFC_DELAY_x = 12, unless otherwise noted |     |      |     |                   |

| $1\times$ , $1\times^2$                                             | JESD204B Mode 15 <sup>3</sup>                              |     | 420  |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 16                                           |     | 440  |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 17                                           |     | 590  |     | DAC clock cycle   |

| $1\times$ , $8\times^2$                                             | JESD204B Mode 3                                            |     | 1390 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 8 <sup>3</sup>                               |     | 1820 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 9                                            |     | 1920 |     | DAC clock cycle   |

| $1\times$ , $12\times^2$                                            | JESD204B Mode 8 <sup>3</sup>                               |     | 2700 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 9                                            |     | 2840 |     | DAC clock cycle   |

| $2\times$ , $6\times^2$                                             | JESD204B Mode 3, Mode 4                                    |     | 1970 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5                                            |     | 1770 |     | DAC clock cycle   |

| $2\times$ , $8\times^2$                                             | JESD204B Mode 0                                            |     | 2020 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 3, Mode 4                                    |     | 2500 |     | DAC clock cycle   |

| $3\times$ , $6\times^2$                                             | JESD204B Mode 3, Mode 4                                    |     | 2880 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5, Mode 6                                    |     | 2630 |     | DAC clock cycle   |

| $3\times$ , $8\times^2$                                             | JESD204B Mode 3, Mode 4                                    |     | 3310 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5, Mode 6                                    |     | 2980 |     | DAC clock cycle   |

| $4\times$ , $6\times^2$                                             | JESD204B Mode 0, Mode 1, Mode 2                            |     | 2410 |     | DAC clock cycle   |

| $4\times$ , $8\times^2$                                             | JESD204B Mode 0, Mode 1, Mode 2                            |     | 3090 |     | DAC clock cycle   |

| $6\times$ , $6\times^2$                                             | JESD204B Mode 0, Mode 1, Mode 2                            |     | 3190 |     | DAC clock cycle   |

| $6\times$ , $8\times^2$                                             | JESD204B Mode 0, Mode 1, Mode 2                            |     | 4130 |     | DAC clock cycle   |

| $8\times$ , $6\times^2$                                             | JESD204B Mode 7                                            |     | 3300 |     | DAC clock cycle   |

| $8\times$ , $8\times^2$                                             | JESD204B Mode 7                                            |     | 4270 |     | DAC clock cycle   |

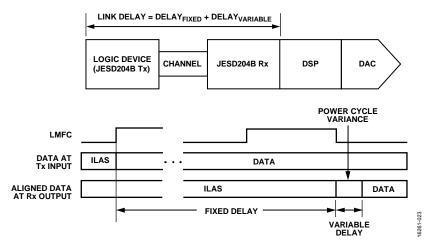

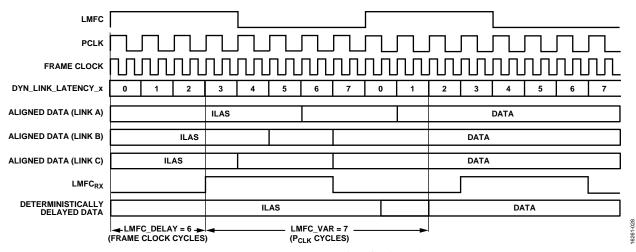

| DETERMINISTIC LATENCY                                               |                                                            |     |      |     |                   |

| Fixed                                                               |                                                            |     |      | 13  | PCLK <sup>4</sup> |

| Variable                                                            |                                                            |     |      | 2   | PCLK cycles       |

| SYSREF± TO LOCAL MULTIFRAME<br>CLOCK (LMFC) DELAY                   |                                                            |     | 0    |     | DAC clock cycles  |

<sup>「</sup>デバイス全体での合計遅延(またはパイプライン遅延)は次式で計算されます:

Rev. 0 – 9/142 –

合計遅延=インターフェース遅延+固定遅延+可変遅延+パイプライン遅延。

$<sup>^2</sup>$ この仕様項目の最初の値はチャンネル・インターポレーション係数で、2番目の値はメイン・データパス・インターポレーション係数です。

$<sup>^{3}</sup>$  LMFC\_VAR\_x = 7、LMFC\_DELAY\_x = 4

$<sup>^4</sup>$  PCLK は AD9173 の内部処理クロックで、その値はレーン・レート  $\div$  40 です。

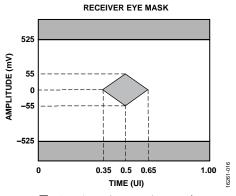

# JESD204B インターフェースの電気的仕様と速度仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC  $I_{OUTFS} = 20$  mA。 最小値と最大値は  $T_J = -40$  °C  $\sim +118$  °C での値、代表値は  $T_A = 25$  °C  $(T_J = 51$  °C に相当)での値。

表 7.

| Parameter                                                                 | Symbol             | Test Conditions/Comments                         | Min   | Тур  | Max   | Unit |

|---------------------------------------------------------------------------|--------------------|--------------------------------------------------|-------|------|-------|------|

| JESD204B SERIAL INTERFACE RATE (SERIAL LANE RATE)                         |                    |                                                  | 3     |      | 15.4  | Gbps |

| JESD204B DATA INPUTS                                                      |                    |                                                  |       |      |       |      |

| Input Leakage Current                                                     |                    | $T_A = 25^{\circ}C$                              |       |      |       |      |

| Logic High                                                                |                    | Input level = $1.0 \text{ V} \pm 0.25 \text{ V}$ |       | 10   |       | μΑ   |

| Logic Low                                                                 |                    | Input level = $0 \text{ V}$                      |       | -4   |       | μΑ   |

| Unit Interval                                                             | UI                 |                                                  | 333   |      | 66.7  | ps   |

| Common-Mode Voltage                                                       | $V_{RCM}$          | AC-coupled                                       | -0.05 |      | +1.1  | V    |

| Differential Voltage                                                      | $R_V_{DIFF}$       |                                                  | 110   |      | 1050  | mV   |

| Differential Impedance                                                    | Z <sub>RDIFF</sub> | At dc                                            | 80    | 100  | 120   | Ω    |

| SYSREF± INPUT                                                             |                    |                                                  |       |      |       |      |

| Differential Impedance                                                    |                    |                                                  |       | 100  |       | Ω    |

| DIFFERENTIAL OUTPUTS $(\overline{SYNCOUT0\pm}, \overline{SYNCOUT1\pm})^1$ |                    | Driving 100 $\Omega$ differential load           |       |      |       |      |

| Output Differential Voltage                                               | $V_{\mathrm{OD}}$  |                                                  | 320   | 390  | 460   | mV   |

| Output Offset Voltage                                                     | Vos                |                                                  | 1.08  | 1.12 | 1.15  | V    |

| SINGLE-ENDED OUTPUTS (SYNCOUT0±, SYNCOUT1±)                               |                    | Driving 100 Ω differential load                  |       |      |       |      |

| Output Voltage                                                            |                    |                                                  |       |      |       |      |

| High                                                                      | $V_{OH}$           |                                                  | 1.69  |      |       | V    |

| Low                                                                       | $V_{OL}$           |                                                  |       |      | 0.045 | V    |

| Current Output                                                            |                    |                                                  |       |      |       |      |

| High                                                                      | $I_{OH}$           |                                                  |       | 0    |       | mA   |

| Low                                                                       | $I_{OL}$           |                                                  |       | 0    |       | mA   |

<sup>&</sup>lt;sup>1</sup> IEEE 1596.3 LVDS 規格と互換。

# 入力データ・レートと信号帯域幅の仕様

特に指定のない限り、AVDD1.0 = 1.0 V、AVDD1.8 = 1.8 V、DVDD1.0 = 1.0 V、DVDD1.8 = 1.8 V、SVDD1.0 = 1.0 V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20 mA。最小値と最大値は  $I_{J}$  = -40  $^{\circ}$ C  $\sim$  +118  $^{\circ}$ C での値、代表値は  $I_{A}$  = 25  $^{\circ}$ C  $(I_{J}$  = 51  $^{\circ}$ C に相当)での値。

表 8.

| Parameter <sup>1</sup>                     | Test Conditions/Comments                                                                       | Min | Тур | Max  | Unit |

|--------------------------------------------|------------------------------------------------------------------------------------------------|-----|-----|------|------|

| INPUT DATA RATE PER INPUT CHANNEL          |                                                                                                |     |     |      |      |

|                                            | Channel and main datapaths bypassed (1× total interpolation), dual DAC mode, 11-bit resolution |     |     | 3400 | MSPS |

|                                            | 1 complex channel enabled, 16-bit resolution                                                   |     |     | 1230 | MSPS |

|                                            | 1 complex channel enabled, 11-bit resolution                                                   |     |     | 1540 | MSPS |

|                                            | 2 complex channels enabled                                                                     |     |     | 770  | MSPS |

|                                            | 3 complex channels enabled                                                                     |     |     | 385  | MSPS |

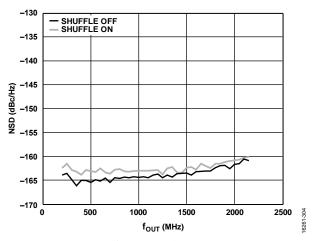

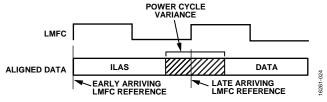

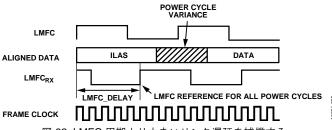

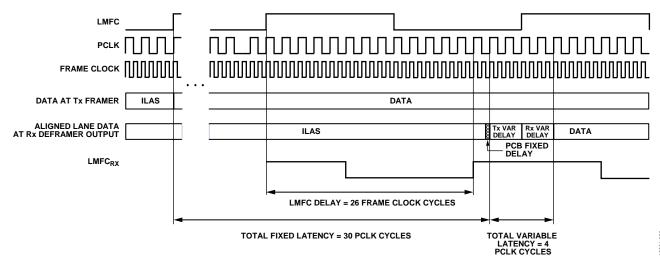

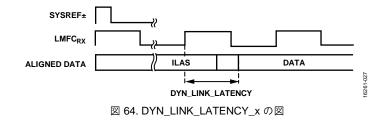

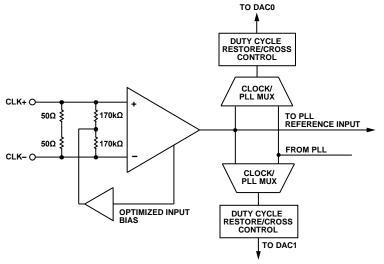

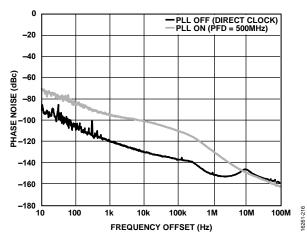

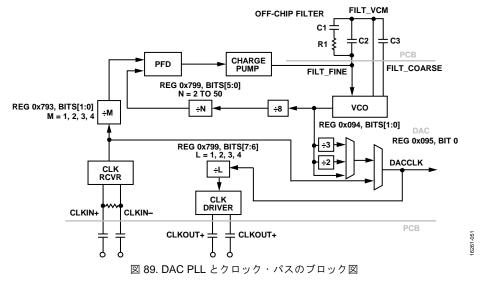

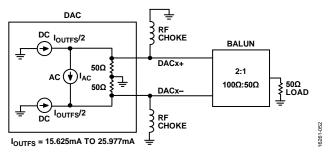

| COMPLEX SIGNAL BANDWIDTH PER INPUT CHANNEL |                                                                                                |     |     |      |      |