# デュアル・チャンネル ,20 MHz 10ビット分解能 CMOS A/DC

# AD9201

#### 特長

完全デュアル整合 A/DC

低消費電力: 215 mW(+3 V 電源使用時)

**単電源:**2.7 ~ 5.5 ∨ 微分非直線性誤差: 0.4 LSB アナログ入力パッファ内蔵

リファレンス内蔵 S/N比: 57.8 dB

有効ビット数:9ビット超

スプリアス・フリー・ダイナミック・レンジ: - 73 dB

ノー・ミッシング・コード保証

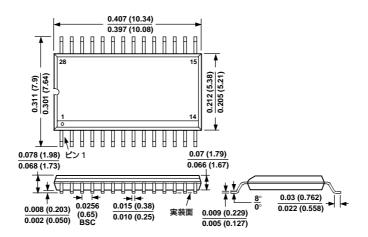

28ピン SSOP

#### 概要

AD9201 は、完全デュアル・チャンネル、20 MSPS、10 ビットの CMOS A/DC です。この AD9201 は、特に、2 つの A/DC の間で高い 整合性が求められるアプリケーション(たとえば、通信アプリケー ションにおける I/Q チャンネル )用に最適化されています。20 MHz のサンプリング・レートと広い入力帯域幅は、狭帯域チャンネルお よび拡散スペクトラム・チャンネルをともにカバーします。 AD9201 は、10ビット、20 MSPS の A/DC x 2、入力パッファ・アンプ ×2、内蔵の電圧リファレンスおよび、多重デジタル出力バッファを 備えています。

それぞれの A/DC の入力には、同時サンプリングのサンプル/ ホールド・アンプが組み込まれています。アナログ入力はバッファ されるので、ほとんどのアプリケーションにおいては、入力バッ ファ・オペアンプを外部接続する必要がありません。これらの A/ DC は、多段パイプライン構造を用いて、高精度とノー・ミッシン グ・コード保証を実現します。各 A/DC の出力は、多重デジタル出 カバッファにポートされます。

AD9201 は、先端の低コスト CMOS プロセスを使用して製造され、 2.7 ~ 5.5 V の単電源で動作し、215 mW(+3 V 電源使用時)しか電 力を消費しません。AD9201 は、シングルエンド信号または差動信 号が入力可能で、10 MHz のナイキスト入力周波数まで、さらにはそ れを超える周波数において優れたダイナミック特性が得られます。

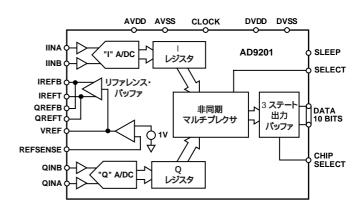

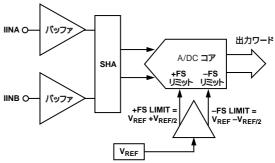

### 機能ブロック図

## 特長

1. デュアル 10ビット、20 MSPS A/DC

| およびQ チャンネル、あるいはダイバーシティ・チャンネル等 の情報をエンコードするための、スプリアス・フリー・ダイナ ミック特性を得るために最適化された、高性能 20 MSPS A/DC を 備えています。

2. 低消費電力

完全 CMOS デュアル A/DC 機能は、単電源で動作し、わずか 215 mW しか電力を消費しません(+3 V 電源使用時)。 AD9201 は、 2.7 ~ 5.5 V 電源で動作します。

3. 内蔵電圧リファレンス

AD9201 は、ピン経由で 1 V または 2 V にプログラムできる補償 バンドギャップ電圧リファレンスを内蔵しています。

- 4. アナログ入力パッファを内蔵しており、ほとんどのアプリケー ションにおいては外付けオペアンプが不要です。

- 5. 単一の10ビット・デジタル出力パス AD9201 の A/DC 出力は、単一の出力バスにインターリーブされ るので、ボード・スペースとデジタル・ピンの数を節減できます。

- 6. コンパクトなパッケージ AD9201 は、コンパクトな 28 ピン SSOP パッケージに機能を完全 に統合しています。

- 7. 製品ファミリー

デュアル A/DC AD9201 は、デュアル 8ビット A/DC(AD9281)と ピン・コンパチブルで、デュアル D/AC の姉妹製品としては、 AD9761 があります。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、 当社はその情報の利用、また利用したことにより引き起こされる第3者の特許または権 利の侵害に関して一切の責任を負いません。さらにアナログ・デバイセズ社の特許また は特許の権利の使用を許諾するものでもありません。

# AD9201 仕様

(特に指定のない限り、AVDD = +3 V DVDD = +3 V F<sub>SAMPLE</sub> = 20 MSPS ,VREF = 2 V ,INB = 0.5 V ,温度範囲 = T<sub>MIN</sub> ~ T<sub>MAX</sub> ,内蔵リファレンス使用 ,差動入力信号使用とします)

| , , , , , , , , , , , , , , , , , , , ,       |                    |       |                |        |                 |                                  |

|-----------------------------------------------|--------------------|-------|----------------|--------|-----------------|----------------------------------|

| パラメータ                                         | 記号                 | Min   | Тур            | Max    | 単位              | 条件                               |

| 分解能                                           |                    |       | 10             |        | ピット             |                                  |

| 変換レート                                         | Fs                 |       |                | 20     | MHz             |                                  |

| DC 精度                                         |                    |       |                |        |                 |                                  |

| 微分非直線性                                        | DNL                |       | ± 0.4          |        | LSB             | REFT = 1 V, REFB = 0 V           |

| 積分非直線性                                        | INL                |       | 1.2            |        | LSB             |                                  |

| 微分非直線性(SE)                                    | DNL                |       | ± 0.5          | ± 1    | LSB             | REFT = 1 V, REFB = 0 V           |

| 積分非直線性(SE)                                    | INL                |       | ± 1.5          | ± 2.5  | LSB             |                                  |

| ゼロ・スケール誤差 ,オフセット誤差                            | Ezs                |       | ± 1.5          | ± 3.8  | % FS            |                                  |

| フルスケール誤差 ,ゲイン誤差                               | E <sub>FS</sub>    |       | ± 3.5          | ± 5.4  | % FS            |                                  |

| ゲイン整合                                         |                    |       | $\pm 0.5$      |        | LSB             |                                  |

| オフセット整合                                       |                    |       | ± 5            |        | LSB             |                                  |

| アナログ入力                                        |                    |       |                |        |                 |                                  |

| 入力電圧範囲                                        | AIN                | - 0.5 |                | ADVV/2 | V               |                                  |

| 入力キャパシタンス                                     | C <sub>IN</sub>    |       | 2              |        | pF              |                                  |

| アパーチャ遅延                                       | t <sub>AP</sub>    |       | 4              |        | ns              |                                  |

| アパーチャの不確定性(ジッター)                              | t <sub>AJ</sub>    |       | 2              |        | ps              |                                  |

| アパーチャ遅延整合                                     |                    |       | 2              |        | ps              |                                  |

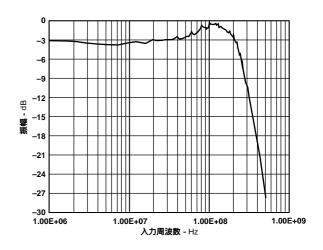

| <b>入力帯域幅( -</b> 3 dB <b>)</b>                 | BW                 |       |                |        |                 |                                  |

| 小信号( - 20 dB )                                |                    |       | 240            |        | MHz             |                                  |

| フルパワー(0dB)                                    |                    |       | 245            |        | MHz             |                                  |

| 内蔵リファレンス                                      |                    |       |                |        |                 |                                  |

| 出力電圧(1∨モード)                                   | VREF               |       | 1              |        | V               | REFSENSE = VREF                  |

| 出力電圧誤差 <b>(</b> 1 <b>∀ モード )</b>              |                    |       | ± 10           |        | mV              |                                  |

| 出力電圧(2 V モード)                                 | VREF               |       | 2              |        | V               | REFSENSE = GND                   |

| 出力電圧誤差(2 V モード)                               |                    |       | ± 15           |        | mV              |                                  |

| 負荷レギュレーション(1∨モード)                             |                    |       |                | ± 28   | mV              | <b>負荷電流</b> = 1 mA               |

| 負荷レギュレーション(2∨モード)                             |                    |       | ± 15           |        | mV              | <b>負荷電流</b> = 1 mA               |

| 電源                                            |                    |       |                |        |                 |                                  |

| 動作電圧                                          | AVDD               | 2.7   | 3              | 5.5    | V               | AVDD - DVDD≤2.3 V                |

|                                               | DRVDD              | 2.7   | 3              | 5.5    | V               |                                  |

| 電源電流                                          | I <sub>AVDD</sub>  |       | 71.6           |        | mA              | AVDD=3V                          |

| *** <b>=</b> -                                | I <sub>DRVDD</sub> |       | 0.1            | 0.45   | mA              | A. (22 2) (25 2) (               |

| 消費電力                                          | P <sub>D</sub>     |       | 215            | 245    | mW              | AVDD = DVDD = 3 V                |

| パワーダウン                                        |                    |       | 15.5           |        | mW              | STBY = AVDD, クロック = AVSS         |

| 電源変動除去比                                       | PSR                |       | 0.8            | 1.3    | %FS             |                                  |

| ダイナミック特性                                      |                    |       |                |        |                 |                                  |

| 信号対ノイズおよびひずみ比                                 | SINAD              | == 0  |                |        | 15              |                                  |

| f = 3.58 MHz                                  |                    | 55.6  | 57.3           |        | dB              |                                  |

| f = 10 MHz                                    | CNID               |       | 55.8           |        | dB              |                                  |

| S/N比                                          | SNR                | FF 0  | F7.0           |        | 40              |                                  |

| f = 3.58 MHz<br>f = 10 MHz                    |                    | 55.9  | 57.8<br>56.2   |        | dB<br>dB        |                                  |

| * 10 MHZ<br>総合高調波ひずみ                          | THD                |       | 20.2           |        | UD              |                                  |

| <b>総百両嗣及ひ9の</b><br>f=3.58 MHz                 | וחט                |       | - 69           | - 63.3 | dB              |                                  |

| f = 10 MHz                                    |                    |       | - 69<br>- 66.3 | - 03.3 | dB              |                                  |

| スプリアス・フリー・ダイナミック・レンジ                          | SFDR               |       | - 00.3         |        | UD              |                                  |

| f = 3.58 MHz                                  | וט טו              | - 66  | - 73           |        | dB              |                                  |

| f = 10 MHz                                    |                    | - 00  | - 73<br>- 70.5 |        | dB              |                                  |

| 1= 10 MHZ<br>2 <b>トーン相互変調ひずみ</b> <sup>2</sup> | IMD                |       | - 70.5<br>- 62 |        | dB              | f = 44.49 MHz <b>、</b> 45.52 MHz |

| 微分位相                                          | DP                 |       | 0.2            |        | 度               | NTSC 40 IRE <b>変調勾配</b>          |

| 微分ゲイン                                         | DG                 |       | 1              |        | <b>152</b><br>% | F <sub>S</sub> = 14.3 MHz        |

| クロストーク除去比                                     |                    |       | 68             |        | dB              | 1 5 - 17.0 1011 12               |

| ソロストーン除去し                                     |                    |       | 80             |        | uв              |                                  |

- 2 - Rev.D

| パラメータ                        | 記号              | Min  | Тур         | Max | 単位   | 条件                                                |

|------------------------------|-----------------|------|-------------|-----|------|---------------------------------------------------|

| ダイナミック特性(SE) <sup>3</sup>    |                 |      |             |     |      |                                                   |

| 信号対ノイズおよびひずみ比                | SINAD           |      |             |     |      |                                                   |

| f = 3.58 MHz                 |                 |      | 52.3        |     | dB   |                                                   |

| S/N <b>比</b>                 | SNR             |      |             |     |      |                                                   |

| f = 3.58 MHz                 |                 |      | 55.5        |     | dB   |                                                   |

| 総合高調波ひずみ                     | THD             |      |             |     |      |                                                   |

| f = 3.58 MHz                 |                 |      | <b>-</b> 55 |     | dB   |                                                   |

| スプリアス・フリー・ダイナミック・レンジ         | SFDR            |      |             |     |      |                                                   |

| f = 3.58 MHz                 |                 |      | - 58        |     | dB   |                                                   |

| デジタル入力                       |                 |      |             |     |      |                                                   |

| High <b>入力電圧</b>             | $V_{IH}$        | 2.4  |             |     | V    |                                                   |

| Low入力電圧                      | $V_{IL}$        |      |             | 0.3 | V    |                                                   |

| DC <b>リーク電流</b>              | I <sub>IN</sub> |      | ± 6         |     | μΑ   |                                                   |

| 入力キャパシタンス                    | $C_{IN}$        |      | 2           |     | pF   |                                                   |

| <b>ロジック出力(</b> DVDD = 3 V )  |                 |      |             |     |      |                                                   |

| High <b>レベル出力電圧</b>          |                 |      |             |     |      |                                                   |

| $(I_{OH} = 50 \mu A)$        | $V_{OH}$        |      | 2.88        |     | V    |                                                   |

| Lowレベル出力電圧                   | 0               |      |             |     |      |                                                   |

| $(I_{OL} = 1.5 \text{ mA})$  | $V_{OL}$        |      | 0.095       |     | V    |                                                   |

| <b>ロジック出力(</b> DVDD = 5 V )  |                 |      |             |     |      |                                                   |

| High <b>レベル出力電圧</b>          |                 |      |             |     |      |                                                   |

| (I <sub>OH</sub> = 50 μ A)   | $V_{OH}$        |      | 4.5         |     | V    |                                                   |

| Lowレベル出力電圧                   |                 |      |             |     |      |                                                   |

| ( I <sub>OL</sub> = 1.5 mA ) | $V_{OL}$        |      | 0.4         |     | V    |                                                   |

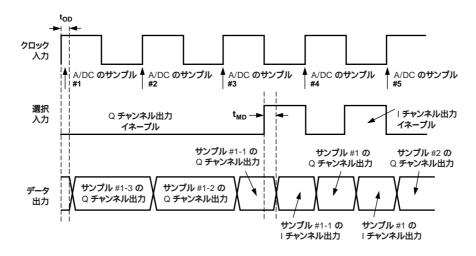

| データ有効までの遅延時間                 | $t_{OD}$        |      | 11          |     | ns   |                                                   |

| MUX <b>選択までの遅延時間</b>         | $t_{MD}$        |      | 7           |     | ns   |                                                   |

| データ・イネーブルまでの遅延時間             | $t_{\sf ED}$    |      | 13          |     | ns   | C <sub>L</sub> = 20 pF,出力レベルが最終値の<br>  90 % になるまで |

| デー <b>タ</b> High Z <b>遅延</b> | $t_{DHZ}$       |      | 13          |     | ns   | 90 % ICASK C                                      |

| クロック                         |                 |      |             |     |      |                                                   |

| クロック・パルス幅High                | $t_{CH}$        | 22.5 |             |     | ns   |                                                   |

| クロック・パルス幅Low                 | t <sub>CL</sub> | 22.5 |             |     | ns   |                                                   |

| パイプライン待ち時間                   | OL              |      | 3.0         |     | サイクル |                                                   |

注

仕様は、予告なく変更されることがあります。

**図** 1. A/DC **のタイミング図**

Rev.D - 3 -

AIN は2 V pp の差動入力 REFT = 1.5 V REFB = -0.5 V。

IMD は、2 つの入力信号のうち大きい方を参照します。

SE は、シングルエンド入力 REFT = 1.5 V REFB = -0.5 V。

## 最大絶対定格\*

| パラメータ      | 基準   | Min   | Max        | 単位 |

|------------|------|-------|------------|----|

| AVDD       | AVSS | - 0.3 | + 6.5      | V  |

| DVDD       | DVSS | - 0.3 | + 6.5      | V  |

| AVSS       | DVSS | - 0.3 | + 0.3      | V  |

| AVDD       | DVDD | - 6.5 | + 6.5      | V  |

| CLK        | AVSS | - 0.3 | AVDD + 0.3 | V  |

| デジタル出力     | DVSS | - 0.3 | DVDD + 0.3 | V  |

| AINA, AINB | AVSS | - 1.0 | AVDD + 0.3 | V  |

| VREF       | AVSS | - 0.3 | AVDD + 0.3 | V  |

| REFSENSE   | AVSS | - 0.3 | AVDD + 0.3 | V  |

| REFT, REFB | AVSS | - 0.3 | AVDD + 0.3 | V  |

| 接合温度       |      |       | + 150      |    |

| 保管温度       |      | - 65  | + 150      |    |

| リード温度      |      |       |            |    |

| 10 秒       |      |       | + 300      |    |

\* 上記の絶対最大定格を超えるストレスは、デパイスに永久的なダメージを与えることがあります。このリストはストレス定格を示すことだけを目的とし、これらの条件もしくは、本仕様書の動作に関するセクションに示した以外の条件におけるこのデパイスの機能的な動作を意味するものではありません。長時間にわたって絶対最大定格条件で使用すると、デパイスの信頼性に影響が現れることがあります。

オーダー・ガイド

| モデル         | 動作温度範囲             | パッケージ説明   | パッケージ・<br>オプション* |

|-------------|--------------------|-----------|------------------|

| AD9201ARS   | - 40 ~ <b>+</b> 85 | 28ピン SSOP | RS - 28          |

| AD9201-EVAL |                    | 評価ボード     |                  |

\*RS:シュリンク・スモール・アウトライン

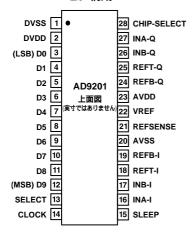

## ピン構成

# ピン機能の説明

|      | 100-10      |                           |

|------|-------------|---------------------------|

| ピン番号 | 名称          | 説明                        |

| 1    | DVSS        | デジタル・グラウンド                |

| 2    | DVDD        | デジタル電源                    |

| 3    | D0          | ピットの(LSB)                 |

| 4    | D1          | ビット1                      |

| 5    | D2          | ピット2                      |

| 6    | D3          | ピット3                      |

| 7    | D4          | ビット4                      |

| 8    | D5          | ビット5                      |

| 9    | D6          | ビット6                      |

| 10   | D7          | ビット7                      |

| 11   | D8          | ビット8                      |

| 12   | D9          | ビット9(MSB)                 |

| 13   | SELECT      | High:I チャンネル出力 ,          |

|      |             | Low:Q チャンネル出力             |

| 14   | CLOCK       | クロック                      |

| 15   | SLEEP       | High: <b>パワーダウン</b> ,     |

|      |             | Low: <b>通常動作</b>          |

| 16   | INA-I       | │ ↑チャンネル A入力              |

| 17   | INB-I       | Ⅰチャンネル B入力                |

| 18   | REFT-I      | <b>最大リファレンスのデカップリング</b> , |

|      |             | チャンネル                     |

| 19   | REFB-I      | 最小リファレンスのデカップリング,         |

|      |             | チャンネル                     |

| 20   | AVSS        | アナログ・グラウンド                |

| 21   | REFSENSE    | リファレンス選択                  |

| 22   | VREF        | 内部リファレンス出力                |

| 23   | AVDD        | アナログ電源                    |

| 24   | REFB-Q      | 最小リファレンスのデカップリング、         |

|      |             | Q チャンネル                   |

| 25   | REFT-Q      | 最大リファレンスのデカップリング、         |

|      |             | Qチャンネル                    |

| 26   | INB-Q       | Q チャンネル B 入力              |

| 27   | INA-Q       | Qチャンネル A 入力               |

| 28   | CHIP-SELECT | High:高インピーダンス,            |

|      |             | Low: <b>通常動作</b>          |

|      |             |                           |

# 仕様の定義

# 積分非直線性(INL)

INLは、"0" と "フルスケール" を結んだ直線からの各個別のコードの偏差を言います。"0" として使用するポイントは、最初のコード遷移の 1/2 LSB手前とします。また "フルスケール" は、最後のコード遷移を 1 + 1/2 LSB 超えたレベルとして定義されます。偏差は、この真の直線と特定の各コードの中点の距離から測定します。微分非直線性(DNL、ノー・ミッシング・コード)

理想的な A/DC のコード遷移は、正確に 1 LSB 間隔になります。 DNL は、この理想的な値からの偏差を言います。 DNL は、ノー・ミッシング・コード(NMC)が保証される分解能として仕様規定されることもあります。

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。 $4000 \lor$ もの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることもあります。このAD9201には当社独自のESD保護回路が備えられていますが、高エネルギーの静電放電にさらされたデバイスには回復不能な損傷が残ることもあります。したがって、性能低下や機能喪失を避けるために、適切なESD予防措置をとるようお奨めします。

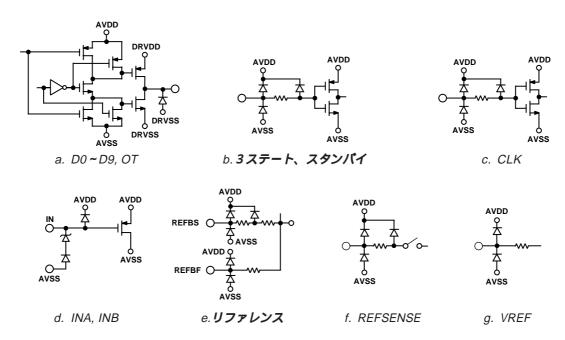

図 2. 等価回路

#### オフセット誤差

最初の遷移は、"0" より 1 LSB だけ高いレベルで生じる必要があります。オフセットは、実際に最初のコード遷移が発生したポイントとこのポイントとの偏差として定義されます。

#### オフセット整合

|チャンネルとQチャンネルのオフセット誤差の変化を言います。 有効ビット数(ENOB)

サイン波の場合、SINAD をビット数として表わすことができます。次の式

$$N = (SINAD - 1.76)/6.02$$

を使用すると、性能をNで表わして測定することができます。このNが有効ビット数です。

つまり、所定の入力周波数におけるサイン波入力に対するデバイスの有効ビット数は、SINADの測定値から計算によりダイレクトに求めることができます。

# 総合高調波ひずみ(THD)

THD は、入力信号の測定値の実行値と、第6高調波以下の高調波成分の和の実行値の比を言い、パーセンテージまたはデシベル値で示されます。

# S/N比(SNR)

SNRは、ナイキスト周波数以下のスペクトル成分から、第6高調波までの高調波成分およびDC成分を除いた残りのスペクトル成分の和の実行値に対する、入力信号の測定値の実行値の比を言います。SNRの値はデシベルで示されます。

### スプリアス・フリー・ダイナミック・レンジ(SFDR)

SFDRは、入力信号の振幅の実行値とピークのスプリアス信号の 差をデシベルで表した値です。

#### ゲイン誤差

最初のコード遷移は、定格の負のフルスケールの上側 1 LSB に相当するアナログ値で発生する必要があります。また、最後のコード 遷移は、= フルスケールの下側 1 LSB に相当するアナログ値で発生

する必要があります。ゲイン誤差は、最初と最後のコード遷移の差 の理想値に対する、最初と最後のコード遷移の差の実測値の偏差を 言います。

#### ゲイン整合

□ チャンネルと Q チャンネルのゲイン誤差の変化を言います。

パイプライン遅延(待ち時間)

変換の開始から対応する出力が処理可能となるまでのクロック 数を言います。新しい出力データは、各クロック・サイクルの立ち 上がりエッジで取り出すことができます。

### MUX 選択遅延

SELECT ピンのデータ・レベルの変化から出力ピンに有効なデータが現れるまでの遅延時間を言います。

# 電源変動除去比

この仕様は、電源電圧のmin値で得られる値から、電源電圧のmax 値で得られる値までの最大変化をフルスケールに対する比で示しま す。

# アパーチャ・ジッター

アパーチャ・ジッターは、連続サンプルに関するアパーチャ遅延の変動を言い、A/Dへの入力に含まれるノイズとして顕在化します。

### アパーチャ遅延

アパーチャ遅延は、クロック入力の立ち上がりエッジから、変換のための入力信号のラッチまでの測定値を言い、サンプル/ホールド・アンプ(SHA)の性能の尺度になります。

### 信号対ノイズおよびひずみ比(S/N+D,SINAD比)

S/N+Dは、ナイキスト周波数以下の入力信号以外のスペクトル成分の和の実行値に対する、入力信号の測定値の実行値の比を言います。入力信号以外のスペクトル成分には、高調波も含まれますが、直流成分は除かれます。S/N+Dの値はデシベルで示されます。

Rev.D - 5 -

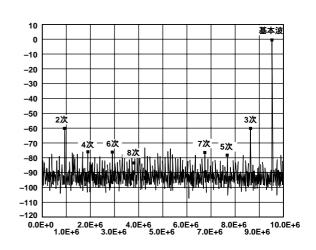

# AD9201 標準特性曲線

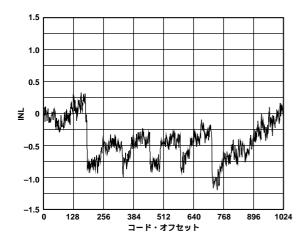

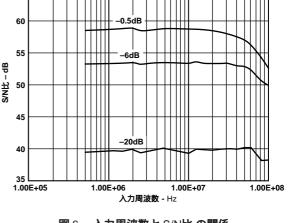

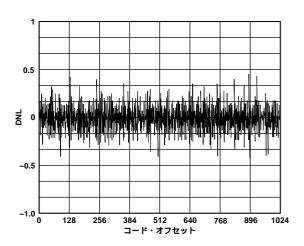

(特に指定のない限り、AVDD = +3 V ,DVDD = +3 V ,F<sub>s</sub> = 20 MHz(デューティ・サイクル = 50 % ),入力スパン = -0.5 ~ +1.5 V までの 2 V ,リファレンス: 2 V の内部リファレンス)

図 3. 代表的な INL(1 V 内蔵リファレンス)

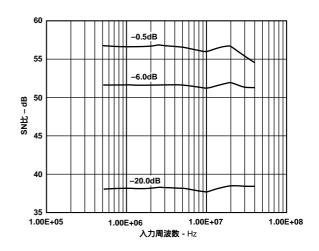

図 6. 入力周波数と S/N比 の関係

図 4. 代表的な DNL(1 V 内蔵リファレンス)

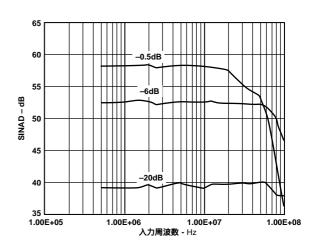

図7. 入力周波数と SINAD の関係

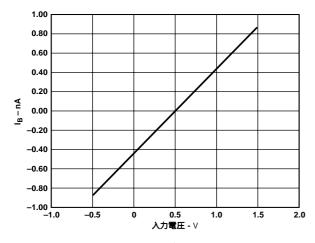

図 5. 入力電圧と入力パイアス電流の関係

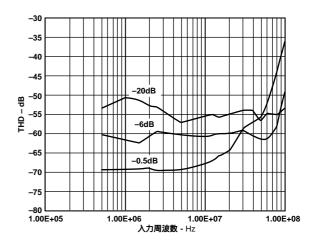

図8. 入力周波数と THD の関係

- 6 - Rev.D

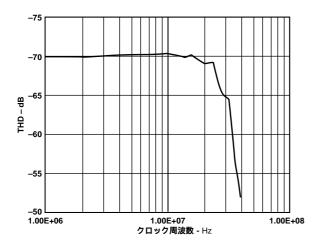

図 9. **クロック周波数と** THD **の関係(** f<sub>IN</sub> = 1MHz )

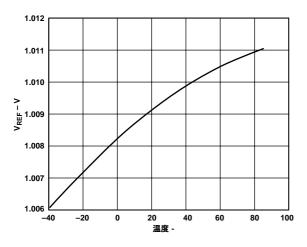

図 10. 温度と電圧リファレンス誤差の関係

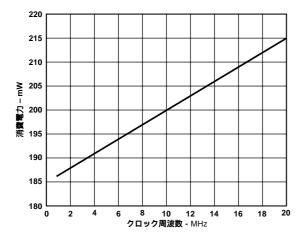

図 11. クロック周波数と消費電力の関係

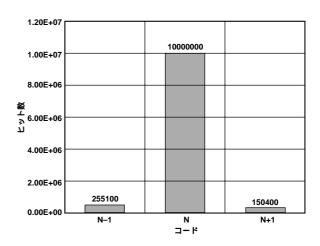

図 12. 実測に基づくヒストグラム

図 13. フルパワー帯域幅

図 14. 入力周波数(シングルエンド)と S/N比 の関係

Rev.D - 7 -

図 15. | チャンネルと Q チャンネルの同時オペレーション (差動入力)

# 動作原理

AD9201 には、A/D コンパータ×2、アナログ入力パッファ×2、内 蔵リファレンス、リファレンス・パッファ×1、および出力マルチプ レクサ×1が備わっています。このデータ・シートでは、説明を明 確にするために、2 つのコンバータを "I" チャンネルおよび "Q" チャ ンネルと呼んで区別することにします。これら2つのA/Dコンバー タは、入力クロックの立ち上がりエッジにおいて、それぞれの対応 する入力から同時にサンプリングを行います。2 つのコンバータ は、変換オペレーションを複数のより小さい A/D サブブロックに 分配し、精度は、各段に結果を渡すごとに順次高められます。この 分散変換を採用した結果、各コンパータが必要とするコンパレータ の数が、従来のフラッシュ・タイプの 10ビット A/DC で使用されて いた 1023 個から劇的に少なくなりました。各段にサンプル / ホー ルド機能が備わるので、初段で新しい入力のサンプリングを行いな がら、第2段以降でそれ以前のサンプルの処理を継続することが可 能です。これにより、入力のサンプリングを行ってから3クロック 周期の待ち時間で、それに対応する A/DC 出力により出力レジスタ が更新される"パイプライン処理"を実現しています。

AD9201 は、コンパータのアナログ入力のドライブ用に入力パッファ・アンプを備えているため、ほとんどのアプリケーションにおいて、入力信号用の外付けオペアンブが必要ありません。入力構成は完全差動ですが、シングルエンド入力信号および差動入力信号のいずれも容易に扱えるように、SHA のコモン・モード応答特性が設

計されています。この差動構成によって、広範囲な入力信号が扱えます。

AD9201 は、さらにオンチップのバンドギャップ・リファレンス およびリファレンス・バッファを備えています。 リファレンス・バッファは、グラウンド基準のリファレンスを、コンバータの内部 回路によって、使用により適したレベルにシフトします。2 つのコンバータは、同じリファレンスとリファレンス・バッファを共有します。この方法は、コンバータ間の最大可能ゲイン整合を実現すると同時に、チャンネル間のクロストークを最小化します(図 16 参照)。

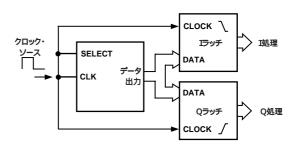

それぞれの A/D コンバータには、固有の出力ラッチがあり、入力クロックの立ち上がりエッジで更新されます。デジタル出力ピンに渡すチャンネルは、SELECT ピンを通じてコントロールされるロジック・マルチプレクサによって決定されます。出力ドライバは、それぞれ固有の電源(DVDD)を備えているので、各種のロジック・ファミリーとのインターフェースが得られます。なお、CHIP-SE-LECT ピンを使用すれば、出力を高インピーダンス状態に設定することができます。

AD9201 は、電源電圧に関して高い柔軟性を持っています。アナログおよびデジタル電源には、 $2.7\sim5.5\,\lor$ までの範囲の電源を独立、あるいは共通して使用することができます。

#### アナログ入力

図16は、2 つある A/D コンパータの一方のアナログ入力の等価回路です。PMOS ソース・フォロワが、アナログ入力ピンをパッファし、一般にスイッチ・キャパシタ A/D コンパータ入力構成に関連して生じるチャージ・キックパック問題を緩和します。これによりデバイスの入力インピーダンスが非常に高くなり、ハイ・インピーダンス・ソースからの効果的なドライブが可能になります。従って、AD9201は受動アンチエイリアス・フィルタからのダイレクトな駆動も可能です。

図 16. AD9201 のアナログ入力の等価回路

バッファ内のソース・フォロワには、さらに約1 V のレベル・シフト機能があるので、AD9201 はグラウンド、もしくはそれ以下の電位の入力を扱うことができます。しかし、このため、アナログ入力が正の電源に達するとひずみを生じます。高周波ひずみ特性を最適化するためには、図29 に従ってアナログ入力をセンタリングする必要があります。

アナログ入力ピンの容量性負荷は、アナログ電源(AVSS、AVDD) に対して4pFです。

フルスケールのセットポイントは、次に示す計算式から求めることができます( $\vee_{REF}$ は、内部または外部で生成したものを使用します)。

- FS =  $(V_{REF} V_{REF}/2)$ + FS =  $(V_{REF} + V_{REF}/2)$

- $V_{SPAN} = V_{REF}$

AD9201 では、 $1 \sim 2 \lor$  の範囲の各種の入力スパンを扱うことができます。 $1 \lor$  に満たないスパンについては、それに比例した S/N 比 の低下が予測されます。 $2 \lor$  のスパンを使用すれば、最高の J イズ特性が得られます。 $3 \lor$  のアナログ電源を使用する場合は、 $1 \lor$  のスパンでひずみがより低くなります。より大きなフルスケールでこのデバイスを使用する場合には、 $5 \lor$  のアナログ電源(AVDD)の使用が推奨されています。

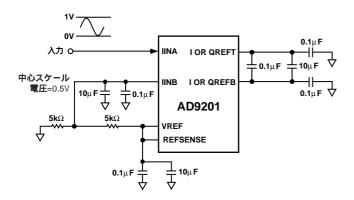

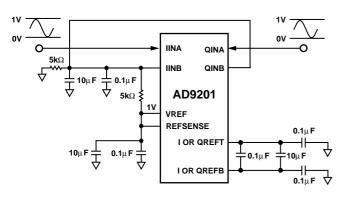

シングルエンド入力:シングルエンド入力信号を使用するときは、信号を一方の入力ピンに印加し、他方の入力ピンを中心スケール電圧に固定します。入力信号のフルスケール・スパンは、この中心スケール電圧によって決定されます。

例:0~1 V の範囲のシングルエンド入力を IINA に印加する場合は、コンパータを1 V リファレンス用に構成し(図17参照) IINB に0.5 V を印加します。

図 17. 0 ~ 1 ∨ シングルエンド入力信号用の構成例

なお、入力が高インピーダンスであることから、抵抗値の大きい抵抗分圧回路(消費電力を抑えるため)を使用してこのリファレンス・レベルを生成することができます。また、このピンへの高周波ノイズ結合を最小にするため、この入力に対しては、デカップリング・キャパシタの使用が推奨されています。デカップリングは、A/DC の直近で行います。

#### 差動入力

差動入力信号を使用すれば、入力範囲とバイアス・ポイントにより大きな柔軟性が得られるだけでなく、ひずみ特性、特に高周波入力信号に対するひずみ特性が改善できます。差動入力信号を使用するユーザーは、差動入力構成の利点を活用できます。

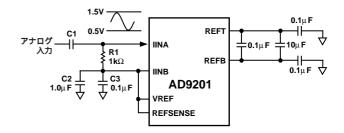

#### AC 結合入力

対象となる信号に DC 成分が含まれていない場合は、AC 結合を使用して最適パイアス・ポイントを容易に設定することができます。推奨構成の一例を図 18 に示します。 DC パイアス・ポイント用に選択した電圧(この場合は 1 V のリファレンス )を、1 k の抵

図 18. 0.5 ~ 1.5 V AC 結合シングルエンド入力用の構成例

抗(R1 およびR2)を介して IINA と IINB の両方に印加します。IINA は、キャパシタ C1 を介して入力信号ラインと結合し、IINB は、キャパシタ C2 および C3 を介してグラウンドとデカップリングします。トランス結合入力

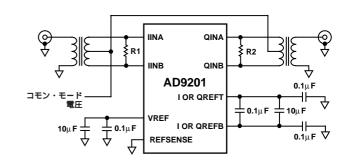

入力を AC 結合する別の方法は、トランスを使用する方法です。これは、DC 成分が除去できるだけでなく、AD9201 のアナログ入力の真の差動ドライブを可能にして、最適ひずみ特性をもたらします。図 19 に、トランス入力ドライブ構成の推奨例を示します。抵抗 R1 および R2 は、トランス結合の終端インピーダンスを決定します。トランスの 2 次巻線のセンター・タップは、コモン・モード・リファレンスに接続され、アナログ入力のパイアス・ポイントを設定します。

図 19. トランス結合入力用の構成例

#### クロストーク

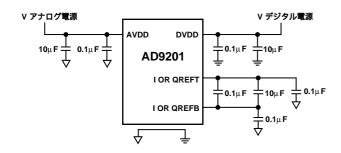

AD9201のピンアウトを始め、その内部レイアウトは、入力信号間のクロストークが最小になるように構成されています。高周波のクロストークを最小にする必要がある場合には、入力ピンに対して可能な限り良好なデカップリングを行う必要があります(図20参照)。R および C の値は、アンチエイリス処理の必要条件に応じてポールを形成します。また、リファレンス・ピンおよび電源にもデカップリングが必要です(図21参照)。

図 20. 入力負荷

図 21. リファレンスおよび電源のデカップリング

# リファレンスおよびリファレンス・バッファ

AD9201 に備わるリファレンスとパッファの回路は、最大の利便性と柔軟性が引き出せるように構成されています。このリファレンスの等価回路を図26に示します。5つのリファレンス・モードが用意され、所定のピンをストラップすることによってその1つを選択することができます(表 | 参照)。このピンをストラップすると、対応する動作モード用に内部の回路が自動的に再構成されます。

表し、モード表

| モード     | 入力スパン       | REFSENSE ピン | 図  |

|---------|-------------|-------------|----|

| 1 V     | 1 V         | VREF        | 22 |

| 2 V     | 2 V         | AGND        | 23 |

| プログラマブル | 1 + (R1/R2) | 図面参照        | 24 |

| 外付け     | =外付けリファレンス  | AVDD        | 25 |

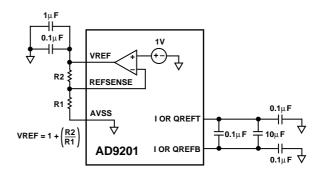

1 V モード(図22) 1 V モードでは、リファレンスが1V、入力フルスケールが1Vになります。高周波特性の最適化が求められるアプリケーション、あるいは電源電圧が4V未満の回路に適しています。このモードを設定するときは、REFSENSE ピンと VREF ピンを短絡します。

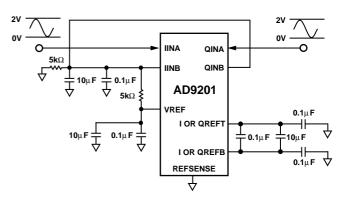

図 22. 0~1 V 入力

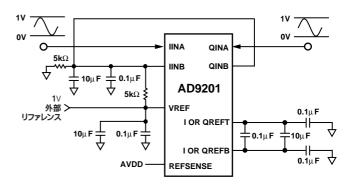

$2 \lor \Xi - F( 図 23)$   $2 \lor \Xi - F \cot x$  リファレンスが  $2 \lor x$  入力フルスケールが  $2 \lor C \cot y$  ます。  $5 \lor \Xi$  源を使用する、ノイズの影響を受けやすいアプリケーションに適しています。このモードを設定するときは、REFSENSE ピンをグラウンドに接続(AVSS と短絡)します。

図 23. 0 ~ 2 V 入力

外付け電圧設定モード(図24) このモードでは、内蔵リファレンスを使用しますが、外部の抵抗分圧回路を使用して、正確なリファレンス・レベルのスケーリングを行います。抵抗分圧回路の一端に VREF を印加し、抵抗分圧回路のタップ・ポイントとREFSENSEを接続します。リファレンス・レベル(および入力フルスケール)は、1 V×(R1 + R2)/R1 に等しくなります。この方法は、0.7 ~ 2.5 Vまでの範囲の電圧レベルに使用することができます。

図 24. プログラマブル・リファレンス

外付けリファレンス・モード(図25) このモードでは、内蔵リファレンスがディスエーブルになり、外付けリファレンスが VREF ピンに印加されます。このモードを設定するときは、REFSENSE ピンを AVDD に接続します。

図 25. 外付けリファレンス

- 10 -

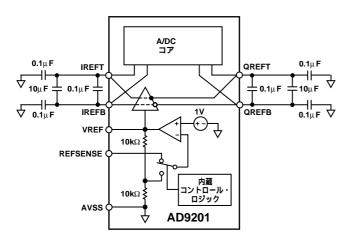

リファレンス・バッファ リファレンス・バッファ構造は、2つのA/Dコンバータ内の各種のサブブロックによる使用に適するように、VREFピンの電圧のレベル・シフトとバッファを行います。これら2つのコンバータは、同一のリファレンス・バッファ・アンプを共有し、互いの間のゲイン整合を可能な限り最良に維持します。高周波クロストークの最小化が重要事項となる場合は、図26に示すように、2つのコンバータ用にバッファしたリファレンスを、IREFBピン、IREFTピン、QREFBピン、およびQREFTピンにおいて個別にデカップリングします。

図 26. リファレンス・バッファの等価回路 および推奨外部デカップリング

ノイズの抑圧とクロストークに対する耐性に関して最良の結果を得るためには、図26に示すような4つのキャパシタを用いたバッファのデカップリング構成が効果的です。このデカップリングでは、コンパータICの近くにチップ・キャパシタを配置します。キャパシタの接続は、IREFT/IREFB または QREFT/QREFB のいずれかで行います。両側で接続を行う必要はありません。

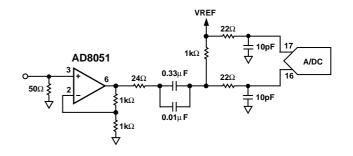

### AD9201 のドライブ

図 27 に、AD8051 を使用して AD9201 をドライブする構成を示します。 AD8051 は、 $3 \lor b \lor b \lor c$  で仕様が規定されていますが、 $b \lor b \lor b \lor c$  において最良の結果が得られます。この場合の A/DC の入力スパンは  $b \lor b \lor b \lor c$  とします。

図 27.

図 28. AD8051/AD9201 **の特性**

Rev.D - 11 -

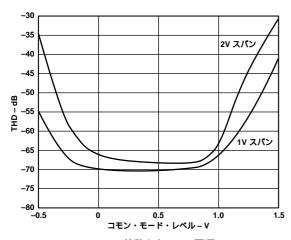

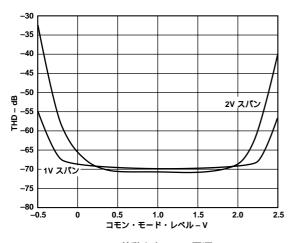

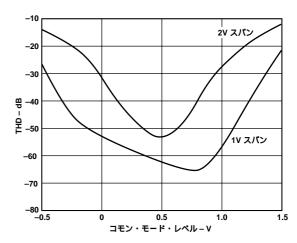

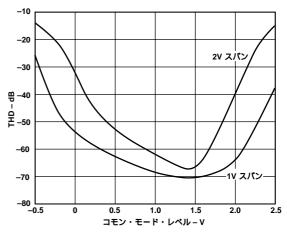

## コモン・モード特性

アナログ入力電圧のコモン・モード・ポイントに注意すると、AD9201 の性能を向上することができます。図 29 は、コモン・モード電圧(アナログ入力スパンの中心)および電源電圧の関数としてTHD を表わしたグラフです。

a. **差動入力**,3 V 電源

b. **差動入力**,5 V 電源

これらのグラフを観察すると、次のような結論が導かれます。

- 1. AD9201 の使用は、AVDD = 5 V とするともっとも容易になります。

- 2. 差動入力は、シングルエンド入力よりコモン・モード電圧の変動に対して耐性があります。

- 3. AVDD = 3 V とし、シングルエンド入力で AD9201 を動作させる 場合には、スパンを 1 V、同相モード電圧を 0.75 V にします。

c. シングルエンド入力,3 V 電源

d. シングルエンド入力,5 V 電源

**図** 29. CML 入力スパンおよび電源電圧と THD の関係(アナログ入力 = 1 MHz)

- 12 -

### デジタル入力および出力

AD9201 のデジタル・コントロール入力、CHIP-SELECT、CLOCK、SELECT および SLEEP は、すべて AVDD と AVSS を基準にしています。 スイッチング・スレッショルドは、AVDD/2 になります。

デジタル出力のフォーマットは、ストレート・バイナリです。低 消費電力モード機能も備わり、STBY をHigh にすると、クロックが ディスエーブルになり、AD9201 の無負荷電力が 22 mW 未満に抑え られます。

### クロック入力

AD9201 のクロックは、AVDD ピンから電圧供給されるインパータによって内部でパッファされます。この機能により AD9201 は、定格 AVDD/2 の CLK ピンの入力スレッショルドを用いて、+5 V または +3.3 V の CMOS ロジック入力信号のスイングを処理することができます。

AD9201のパイプライン構造は、入力クロックの立ち上がリエッジおよび立ち下がリエッジの両方で動作します。デューティ・サイクルの変動を最小に抑えるためには、クロック入力のドライブに高速もしくは高機能の CMOS( HC/HCT ,AC/ACT )ロジック・ファミリーの使用が推奨されます。 CMOS ロジックからは、対称電圧スレッショルド・レベルとともに、20 MSPS の動作のサポートに充分な立ち上がり、立ち下がり時間が得られます。性能レベルは下がりますが、わずかに高いクロック・レートでこのデバイスを動作させることも可能です。逆に、低いクロック・レートで AD9201をクロックすると、性能のわずかな向上が見られることがあります。

出力パッファが消費する電力は、クロック周波数に概ね比例し、 低いクロック・レートを用いれば、消費電力も下がります。

# デジタル出力

AD9201 の各出力ビット(D0 ~ D9)用に備わるオンチップ・バッファは、それぞれ DVDD 電源ピンから電圧供給され、AVDD とは分離されています。出力ドライバは、標準化により各種のロジック・ファミリーとの互換性が確保され、さらにグリッチ・エネルギの発生量は、最小になっています。また、どのような状況においても、出力データ・ビットの容量性負荷を 20 pF の仕様レベルより低く抑えるために、等しいファンアウトが推奨されます。

DVDD = 5 V を使用するときの AD9201 の出力信号スイングは、高速 CMOS ロジック・ファミリーおよび TTL ロジック・ファミリーの両方と互換性があります。 TTL については、複数種類の高速 TTL ファミリー(F, AS, S)をサポートできるように AD9201 のオンチップ出力ドライバが設計されています。 クロック・レートが 20 MSPS 未満のアプリケーションにおいては、これ以外の TTL ファミリーが適当となることもあります。 低い電圧の CMOS ロジックとインターフェースする場合には、AD9201 において DVDD = 3 V として 20 MSPS の動作を維持することができます。 いずれの場合でも、使用予定のロジック・ファミリーのデータ・シートを参照し、AD9201 の仕様との互換性をチェックしてください。

なお、1 出力ライン当たりのロジック負荷を 5 pF に制限すれば、 出力の遅延を 2 ns だけ短縮することができます。

# 3ステート出力

AD9201 の CHIP-SELECT ピンをHighにセットすると、デジタル出力が高インピーダンスになります。この機能は、回路内テストまたは評価を容易にするために備わっています。

#### 選択

SELECT ピンをLowに保持しているときは、出力ワードが "Q" レベルを表わします。この SELECT ピンをHighに維持しているときは、出力ワードが"!" レベルを表わします(図1参照)。

AD9201 の SELECT ピンおよび CLK ピンは、共通の信号ソースからドライブすることができます。データは、入力パルスの 5 ~ 11 ns 後に変化します。この場合、インターフェース・ラッチが、AD9201 の遅延時間に見合う充分なホールド時間を有していることを確認する必要があります(図 30 参照)。

図30. 代表的なディマルチプレクス接続

# アプリケーション

### QAM **復調における** AD9201 **の使用**

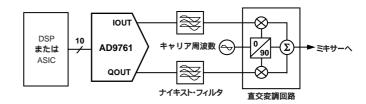

QAM は、デジタル通信システムにもっと広く使用されているデ ジタル変調方式の1つです。この変調テクニックは、FDMAをはじ め、スペクトル拡散(CDMA)ベースのシステムにも見ることがで きます。QAM 信号では、搬送波の振幅変調(AM 変調)および位相 変調(PM 変調)が行われます。送信機においては、位相が90°異 なる同一周波数の2つの搬送波を独立に変調することによって、こ の信号を生成します。この結果、同相(I:inphase)搬送波成分と、 この I 成分と 90°の位相差を持つ直交(Q: quadrature) 搬送波成分 が作られます。この後、I 成分とQ 成分が合成されて、所定のキャ リア周波数、つまり IF 周波数を持った QAM 信号が生成されます。 図 31 は、2×の補間を有する 10ビット D/AC AD9761 を使用し、QAM 変調回路をアナログ的に具体化する方法を示しています。デジタル 領域において QAM 信号を合成することも可能であり、その場合は、 QAM 信号を再構成するための D/AC が 1 つ必要になります。完全 (つまり、D/AC 内蔵)デジタル QAM モジュレータの一例として AD9853 が挙げられます。

図 31. 代表的なアナログ QAM 変調回路の構成

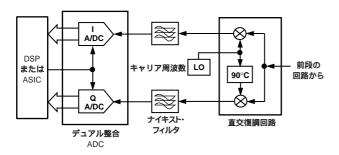

受信機においては、QAM 信号を元の I 成分と Q 成分に分離しま すが、そのプロセスは、基本的に先述の変調プロセスを逆順にたど る形になります。従来から使用されている一般的な QAM 復調回路 の構成を図32に示します。この例を参照すると、デュアル整合 A/ DC および直交復調回路を使用してアナログ領域において復調が行 われ、| および Q のベースパンド信号の復元とデジタル化が行われ ていることがわかります。直交復調回路は、一般に、2つのミキサー と、I および Q の局発(LO)の間に 90°の位相シフトを生じさせる ために必要な回路を含むシングルICです。ミキシングによりベー スパンドまで下げた I 信号と Q 信号を A/DC によりデジタル化す る前に、整合アナログ・フィルタを用いてフィルタ処理を行いま す。これらのフィルタは、しばしばナイキスト・フィルタまたは波 形整形フィルタと呼ばれ、混合プロセスにより生じた虚像(イメー ジ)および帯域外信号を除去します。整合ナイキスト・フィルタの 特性は、最適なS/N 比を提供し、記号間干渉を最小化できる明確な 境界を有するものとします。通常、各 A/DC は、QAM の記号レー トにおいて、より一般的には A/DC 出力をデジタル・フィルタによ リ処理することを前提として、QAM の記号レートの整数倍のレー トにおいて、それぞれに対応する入力を同時にサンプリングしま す。オーバーサンプリングおよびデジタル・フィルタリングを用い れば、アナログ・フィルタの実現が容易になり、複雑性を回避でき ます。またそれにより、キャリアおよび記号の復元とチューニング のために行うデジタル処理を向上することも可能になります。これ において、AD9201 等のデュアル A/DC を用いれば、優れたゲイン、 オフセット、および | チャンネルと Q チャンネル間の整合が確保さ れます。

図 32. 代表的なアナログ QAM 復調回路

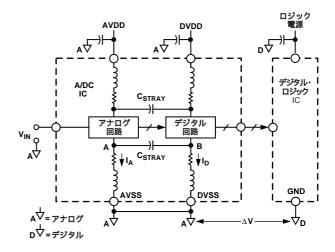

#### 接地およびレイアウトの規則

高性能デバイスの場合、最適性能を達成する上で、適切な接地とレイアウトのテクニックが非常に重要になります。AD9201のアナログ・グラウンドおよびデジタル・グラウンドは、システムにおける折り返し電流の管理を最適化するために、分離されています。グラウンドとの接続は、A/DCの近くで行う必要があります。ここでは、AD9201を備えるプリント回路基板(PCB)として、グラウンド面および電源面を備えた少なくとも4つの層を備えた構造の基板を推奨しています。グラウンド面と電源面を使用すると、次のような顕著な利点が得られます。

- 1. 信号パスおよびリターン・パスによって囲まれるループ面積が 最小になります。

- 2. グラウンド・パスおよび電源パスに関連するインピーダンスが 最小になります。

- 3. 電源面、PCB の絶縁層、およびグラウンド面によって、本質的な 分布容量が形成されます。

こういった特性は、電磁妨害雑音(EMI)を抑え、全体的な性能を 向上させます。

レイアウトの設計において重要なことは、入力信号とノイズの結合を防止することです。デジタル信号を入力信号トレースと平行にすることなく、またそれを入力回路から離して配線します。個別に設けたアナログ・グラウンドとデジタル・グラウンドは、AD9201 直下の固定グラウンド面で互いに直接接続します。電源とグラウンドの折り返し電流は、慎重な管理が必要です。一般則として、ミックスド・シグナルのレイアウトにおいては、重要なアナログ回路内にデジタル回路からの折り返し電流を通過させてはなりません。

AVSS および DVSS の過渡状態は、A/DC の性能を著しく低下させます。

アナログ・グラウンドとデジタル・グラウンドを A/DC の直下で接続できない場合は、図 33 に示した構成の可能性を検討します。

図 33. グラウンドおよび電源に関する考察

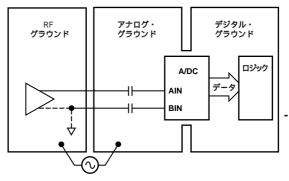

以上とは別の入力および接地のテクニックを図34に示します。 RF用のグラウンド面を分離していますが、これを行わないと信号の処理が困難になります。これらの信号は、差動またはシングルエンドでA/DC に配線されます(つまり、いずれの場合もドライバもしくはRFグラウンドに接続することができます)。A/DC は、RFとA/DC のアナログ・グラウンドの間に数百mV のノイズまたは信号があっても、良好に機能します。

図 34. RF 接地スキーム

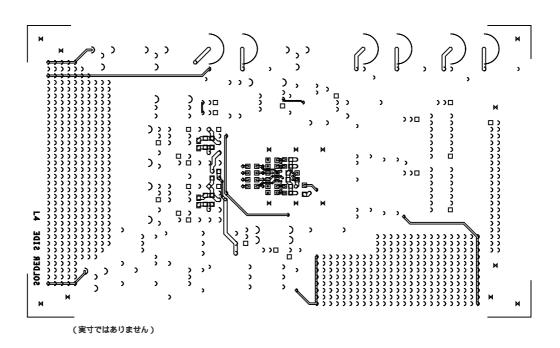

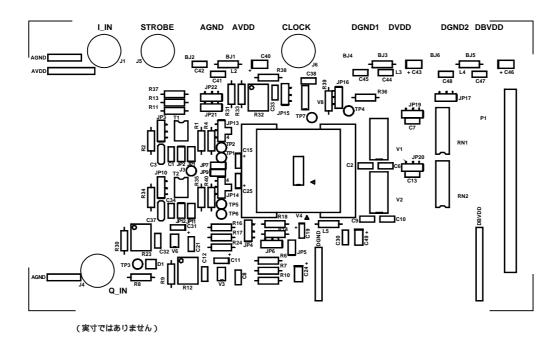

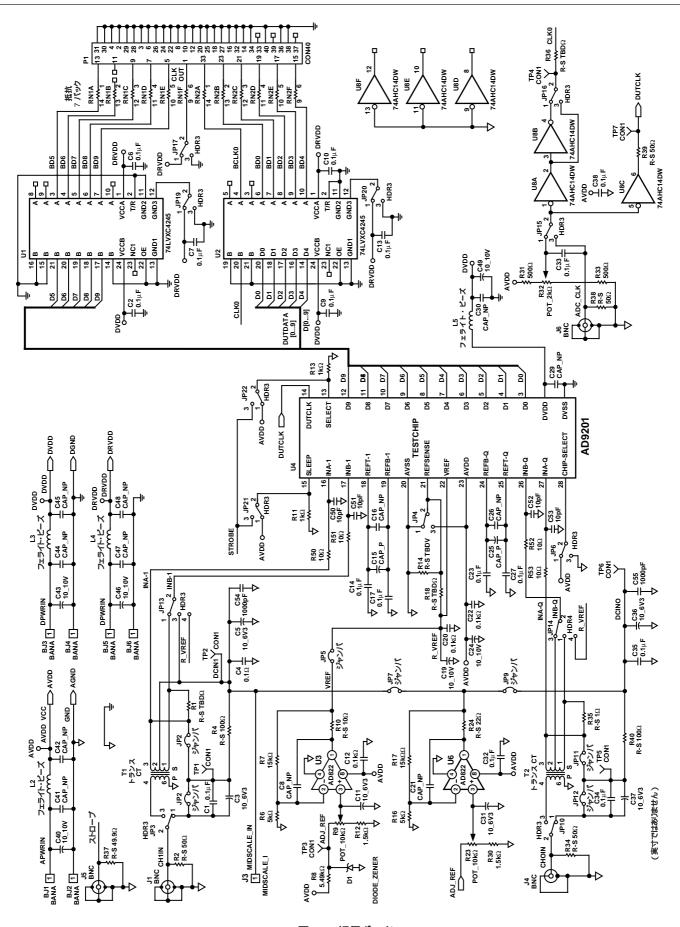

# 評価ボード

AD9201 の評価ボードは、"そのまま使用できる" 形で出荷されます。電源およびシグナル・ジェネレータは、図 35 に示すとおりに接続します。このように接続すれば、Q チャンネルの特性を観察することができます。 | チャンネルを観察する場合は、JP22 のピン 1 とピン 2 をジャンパにより接続します。また、| チャンネルと Q チャンネルをトグルする場合は、適切なジャンパ接続を行った後、CMOS レベルのパルス列を"ストローブ"ジャックに印加します。

図 35. 評価ボードの接続

Rev.D - 15 -

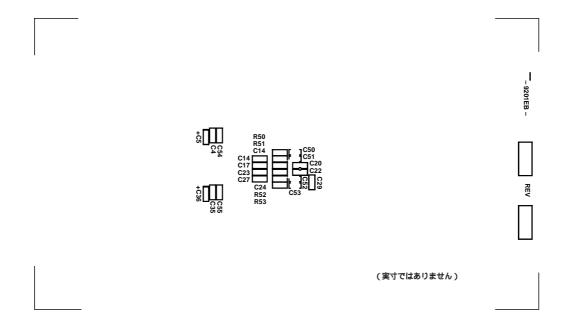

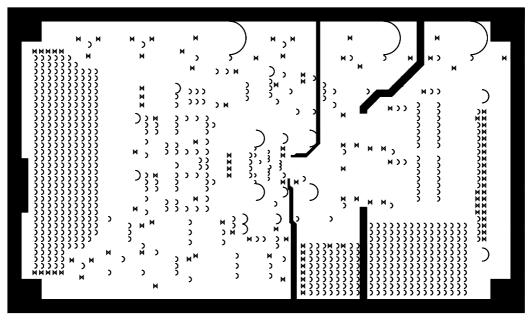

図 36. 評価ボードのソルダー側シルクスクリーン

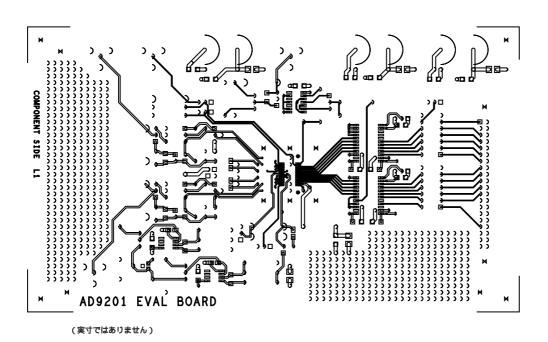

図 37. 評価ボードのコンポーネント側レイアウト

(実寸ではありません)

図 38. 評価ボードのグラウンド面レイアウト

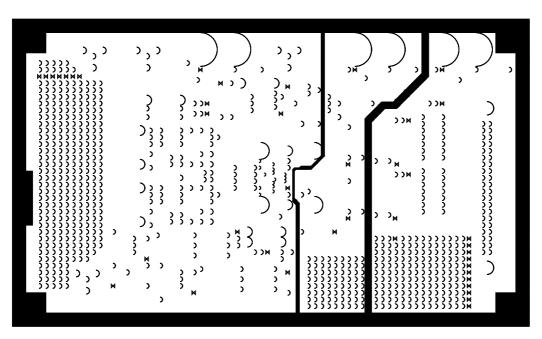

図 39. 評価ボードのソルダー側レイアウト

Rev.D - 17 -

図 40. 評価ボードのコンポーネント側シルクスクリーン

(実寸ではありません)

図 41. 評価ボードの電源面のレイアウト

- 18 - Rev.D

図 42. 評価ボード

Rev.D - 19 -

# 外形寸法 サイズはインチと(mm)で示します。

28ピン・シュリンク・スモール・アウトライン・パッケージ(SSOP) (RS-28)