# フラクショナル N PLL および VCO を内蔵する K バンド・ ダウンコンバータ

**ADMV4420** データシート

#### 特長

RF パランおよび LNA を内蔵する RF フロント・エンド 高ダイナミック・レンジの IF アンプを備えた ダブル・パランスド・アクティブ・ミキサー 低位相ノイズのマルチコア VCO を備えた フラクショナル N シンセサイザ

内蔵 LDO レギュレータによる 5V 電源動作

出力 P1dB: 7dBm 出力 IP3:16dBm 変換ゲイン: 36dB ノイズ指数:7dB

RF 入力周波数範囲: 16.95GHz~22.05GHz 内部 LO 周波数範囲: 16.75GHz~21.15GHz

IF 周波数範囲:900MHz~2500MHz

シングルエンド 50Ω 入力インピーダンスおよび

75Ω IF 出力インピーダンス 4線式 SPI を介してプログラム可能 32 ピン、5mm×5mm LFCSP

アプリケーション

衛星通信

ポイント to ポイントのマイクロ波通信

#### 概要

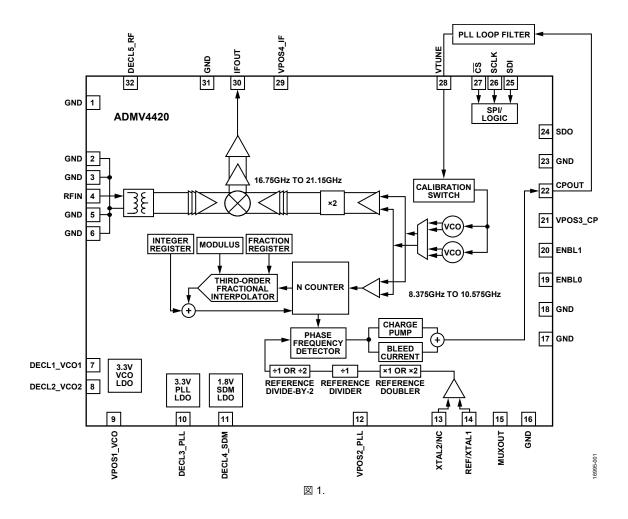

ADMV4420 は高集積のダブル・バランスド・アクティブ・ミキ サーで、フラクショナル N シンセサイザを内蔵しており、次世 代のKバンド衛星通信に最適です。

RF フロント・エンドは内蔵 RF バランと低ノイズ・アンプ (LNA) で構成されています。これにより 7dB という優れた単 側波帯ノイズ指数を実現しながら、外付け部品を最小限に抑え ます。更に、高ダイナミック・レンジの IF 出力アンプにより、 36dB(公称値)の変換ゲインを実現しています。

マルチコアの電圧制御発振器 (VCO) と内部 2 逓倍器を備えた 低位相ノイズのフラクショナル N フェーズ・ロック・ループ (PLL) が、ダブル・バランスド・ミキサーに必要なオンチッ プ LO 信号を生成するので、外付け部品を使って周波数合成を 行う必要がありません。マルチコア VCO が内蔵の自動キャリブ レーション・ルーチンを使用することにより、PLL が必要な設 定を選択して約 400μs でロックします。

PLL へのリファレンス入力には、差動励振を行う 50MHz の水晶 発振器を採用しています。リファレンス入力は、50MHzのシン グルエンド外部入力で駆動することもできます。PLL の位相周 波数検出器 (PFD) 比較周波数は、最大 50MHz まで動作します。

ADMV4420 は、シリコン・ゲルマニウム (SiGe) を使用するバ イポーラ相補型金属酸化膜半導体(BiCMOS)プロセスで製造 され、32 ピン、RoHS 準拠、露出パッド付きの 5mm × 5mm LFCSP パッケージで提供されます。このデバイスは、5V 電源使 用、-40°C~+85°C の温度範囲で仕様規定されています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2019 Analog Devices, Inc. All rights reserved

Rev 0

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 雷話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# 目次

| 特長1                                     |

|-----------------------------------------|

| アプリケーション1                               |

| 概要1                                     |

| 改訂履歴                                    |

| 機能ブロック図4                                |

| 仕様5                                     |

| 絶対最大定格6                                 |

| 熱抵抗                                     |

| ESD に関する注意                              |

| ピン配置およびピン機能の説明7                         |

| インターフェース回路図9                            |

| 代表的な性能特性10                              |

| IF = 900MHz でのローサイド・インジェクション LO 性能 10   |

| IF = 900MHz でのハイサイド・インジェクション LO 性能 12   |

| IF = 1700MHz でのローサイド・インジェクション LO 性能 14  |

| IF = 1700 MHz でのハイサイド・インジェクション LO 性能 16 |

| IF = 2500 MHz でのローサイド・インジェクション LO 性能 18 |

| IF = 2500 MHz でのハイサイド・インジェクション LO 性能 20 |

| LO=16.75GHz でのローサイド・インジェクション性能 22       |

| LO=16.75GHz でのハイサイド・インジェクション性能 24       |

| LO=18.95GHz でのローサイド・インジェクション性能 26       |

| LO=18.95 GHz でのハイサイド・インジェクション性能 28      |

| LO = 21.15GHz でのローサイド・インジェクション性能 30     |

| LO = 21.15 GHz でのハイサイド・インジェクション性能 32    |

| 位相ノイズ性能34                               |

| リターン損失と絶縁35                             |

| スプリアスおよび高調波性能36                         |

| 動作原理                                    |

| リファレンス入力段37                             |

| リファレンス 2 逓倍器、R カウンタ、RDIV2               |

| N カウンタ                                  |

| INT、FRAC、MOD、およびリファレンス・パスの関係 38         |

| インテジャーN モード38                           |

| 位相周波数検出器とチャージ・ポンプ                       |

| ループ・フィルタ39                              |

| CP 電流のセットアップ39                          |

| ブリード電流 (CP_BLEED) のセットアップ39             |

| MUXOUT                                  |

| デジタル・ロック検出40                            |

| イネーブル40                                 |

| IF 出力 — 外付けインダクタ/バイアス                          | 40                 |

|------------------------------------------------|--------------------|

| SPI 構成                                         | 40                 |

| VCO の自動キャリブレーションと 自動                           | レベル制御40            |

| プログラミング・シーケンス                                  | 40                 |

| コントロール・レジスタ                                    | 41                 |

| レジスタの詳細                                        | 42                 |

| アドレス 0x000、リセット:0x00、レジ<br>ADI_SPI_CONFIG_1    |                    |

| アドレス 0x001、リセット: 0x00、レジ                       |                    |

| ADI_SPI_CONFIG_2                               |                    |

| アドレス 0x003、リセット: 0x01、レジ                       |                    |

| アドレス 0x004、リセット: 0x03、レジ<br>PRODUCT_ID_L       | スタ名:               |

| アドレス 0x005、リセット: 0x00、レジ                       |                    |

| PRODUCT_ID_H                                   |                    |

| アドレス 0x00A、リセット: 0x00、レジ                       |                    |

| SCRATCHPAD                                     |                    |

| アドレス 0x00B、リセット: 0x00、レジ                       | _                  |

| アドレス 0x103、リセット: 0x6F、レジ                       |                    |

| アドレス 0x108、リセット: 0x05、レジ                       |                    |

|                                                | ジスタ名:INT_L 46      |

|                                                | -<br>スタ名:INT_H 46  |

|                                                | -<br>スタ名:FRAC_L46  |

|                                                | -<br>スタ名:FRAC M.46 |

| アドレス 0x204、リセット: 0x00、レジ                       | -<br>スタ名:FRAC_H 46 |

|                                                | -<br>スタ名: MOD L 47 |

| アドレス 0x209、リセット: 0x00、レジ                       | -<br>スタ名:MOD_M47   |

|                                                | -<br>スタ名: MOD H 47 |

|                                                | スタ名: R_DIV_L 48    |

|                                                | スタ名:R DIV H 48     |

| アドレス 0x20E、リセット: 0x00、レジ                       |                    |

| REFERENCE                                      |                    |

| アドレス 0x211、リセット: 0x00、レジ                       |                    |

| VCO_DATA_READBACK1                             |                    |

| アドレス 0x212、リセット: 0x00、レジ<br>VCO_DATA_READBACK2 | 49                 |

| アドレス 0x213、リセット: 0x01、レジ<br>PLL_MUX_SEL        |                    |

| アドレス 0x214、リセット: 0x98、レジ                       | スタ名:               |

| LOCK_DETECT                                    | 50                 |

| アドレス 0x215、リセット: 0x00、レジ                       | * *                |

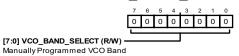

| VCO_BAND_SELECT<br>アドレス 0x216、リセット: 0x00、レジ    |                    |

| VCO_ALC_TIMEOUT                                |                    |

| アドレス 0x217、リセット: 0x01、レジ                       | スタ名:               |

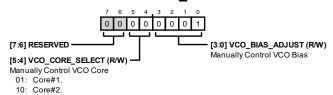

| VCO_MANUAL                                     | 51                 |

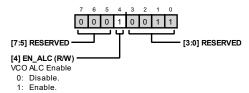

| アドレス 0x219 リセット・0x13 レジ                        | スタ名・ALC 51         |

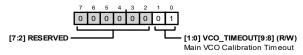

| アドレス 0x21C、リセット: 0x90、レジスタ名:<br>VCO_TIMEOUT1       |

|----------------------------------------------------|

| アドレス 0x21D、リセット: 0x01、レジスタ名:<br>VCO_TIMEOUT2       |

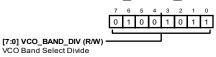

| アドレス 0x21E、リセット: 0x4B、レジスタ名:<br>VCO_BAND_DIV52     |

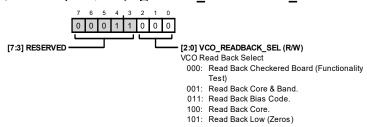

| アドレス 0x21F、リセット: 0x18、レジスタ名:<br>VCO_READBACK_SEL52 |

| アドレス 0x226、リセット: 0x02、レジスタ名: AUTOCAL               |

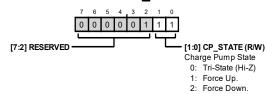

| アドレス 0x22C、リセット: 0x07、レジスタ名: CP_STATE54            |

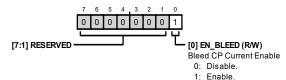

| アドレス 0x22D、リセット:0x01、レジスタ名:<br>CP_BLEED_EN54       |

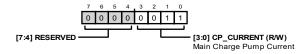

| アドレス 0x22E、リセット: 0x03、レジスタ名:<br>CP_CURRENT54       |

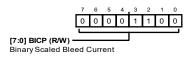

| アドレス 0x22F、リセット: 0x0C、レジスタ名: CP_BLEED 54           |

| 7 | アプリケーション情報  | 55 |

|---|-------------|----|

|   | 評価用ボード      | 55 |

| 5 | <b>朴形寸法</b> | 60 |

|   | オーダー・ガイド    | 60 |

# 改訂履歴

10/2018—Revision 0: Initial Version

Rev. 0 - 3/60 -

# 機能ブロック図

Rev. 0 - 4/60 -

# 仕様

特に指定のない限り、 $V_{VPOS1\_VCO} = V_{VPOS2\_PLL} = V_{VPOS3\_CP} = V_{VPOS4\_IF} = 5V$ 、RF 入力電力 = -40 dBm、PLL ループ・フィルタ帯域幅 = 60 kHz (位相マージン  $45^\circ$ ) とし、 $T_A = 25^\circ C$ 、50 MHz の 0 dBm 外部リファレンスで測定を実施。

表 1.

| Parameter                                                                             | Min    | Тур   | Max    | Unit   | Test Conditions/Comments                                       |

|---------------------------------------------------------------------------------------|--------|-------|--------|--------|----------------------------------------------------------------|

| RF INPUT                                                                              | IVIIII | 1 1/1 | IVIGA  | Offic  | 1000 CONTRIBUTIONS                                             |

| Frequency Range                                                                       | 16.95  |       | 22.05  | GHz    |                                                                |

| Input Return Loss                                                                     | 10.73  | -8.5  | 22.03  | dB     |                                                                |

| Input Impedance                                                                       |        | 50    |        | Ω      | Single-ended                                                   |

| LOCAL OSCILLATOR (LO)                                                                 | 16.75  |       | 21.15  | GHz    | Single chara                                                   |

| INTERNAL FREQUENCY RANGE                                                              |        |       |        |        |                                                                |

| VCO                                                                                   |        |       |        |        |                                                                |

| Frequency Range                                                                       | 8.375  |       | 10.575 | GHz    |                                                                |

| Tuning Sensitivity (k <sub>VCO</sub> )                                                |        | 50    |        | MHz/V  | Calculated with f <sub>VCO</sub> /VTUNE                        |

| VTUNE                                                                                 | 0      |       | 3      | V      |                                                                |

| IF OUTPUT                                                                             |        |       |        |        |                                                                |

| IF Frequency Range                                                                    | 900    |       | 2500   | MHz    |                                                                |

| Conversion Gain                                                                       | 26     | 36    |        | dB     | For entire IF and RF frequency range                           |

| Output 1 dB Compression Point<br>(Output P1dB)                                        |        | 7     |        | dBm    |                                                                |

| Output Third-Order Intercept (Output IP3)                                             |        | 16    |        | dBm    |                                                                |

| Noise Figure Gain Flatness                                                            |        | 7     |        | dB     | Single sideband with appropriate filtering                     |

| Gain Flainess                                                                         |        | ±1    |        | dB     | Across any 250 MHz bandwidth for an IF of 900 MHz to 2000 MHz  |

|                                                                                       |        | ±2    |        | dB     | Across any 250 MHz bandwidth for an IF of 2000 MHz to 2500 MHz |

| Output Impedance                                                                      |        | 75    |        | Ω      | Single-ended                                                   |

| Output Return Loss                                                                    |        | -6.5  |        | dB     |                                                                |

| SUPPLY VOLTAGE                                                                        |        |       |        |        |                                                                |

| $V_{	ext{VPOS1\_VCO}}, V_{	ext{VPOS2\_PLL}}, V_{	ext{VPOS3\_CP}}, V_{	ext{VPOS4 IF}}$ | 4.75   | 5.00  | 5.25   | V      |                                                                |

| TOTAL POWER CONSUMPTION                                                               |        |       |        |        |                                                                |

| Active Mode                                                                           |        | 1900  |        | mW     |                                                                |

| Sleep Mode                                                                            |        | 80    |        | mW     | All blocks powered down                                        |

| EXTERNAL PLL REFERENCE                                                                |        |       |        |        |                                                                |

| Frequency                                                                             |        | 50    |        | MHz    |                                                                |

| Amplitude                                                                             | 0.3    |       | 2.5    | V p-p  | Single-ended input, high impedance                             |

| CRYSTAL REFERENCE                                                                     |        |       |        |        |                                                                |

| Crystal Frequency                                                                     |        | 50    |        | MHz    | Fundamental mode                                               |

| Capacitance                                                                           |        | 10    |        | pF     |                                                                |

| PHASE FREQUENCY DETECTOR (PFD) FREQUENCY                                              |        | 50    |        | MHz    | Compare frequency                                              |

| REFERENCE SPURS                                                                       |        | -70   |        | dBm    |                                                                |

| FREQUENCY SETTLING                                                                    |        | 400   |        | μs     | After frequency change programmed; within 50 kHz resolution    |

| CLOSED-LOOP PHASE NOISE                                                               |        |       |        |        | LO frequency = 16.75 GHz to 21.15 GHz                          |

|                                                                                       |        | -80   |        | dBc/Hz | 10 kHz offset                                                  |

|                                                                                       |        | -85   |        | dBc/Hz | 100 kHz offset                                                 |

|                                                                                       |        | -116  |        | dBc/Hz | 1 MHz offset                                                   |

|                                                                                       |        | -125  |        | dBc/Hz | 10 MHz offset                                                  |

| LOGIC (ENBL0, ENBL1, SDO, SDI, SCLK,                                                  |        |       |        |        |                                                                |

| CS)                                                                                   |        |       |        |        |                                                                |

| Logic Low                                                                             | -0.3   | 0     | +0.5   | V      |                                                                |

| Logic High                                                                            | 1.2    | 3.3   | 3.6    | V      |                                                                |

Rev. 0 - 5/60 -

# 絶対最大定格

表 2

| 1 2.                                                              |                     |

|-------------------------------------------------------------------|---------------------|

| Parameter                                                         | Rating              |

| Supply Voltage (V <sub>VPOS1_VCO</sub> , V <sub>VPOS2_PLL</sub> , | 5.5 V               |

| $V_{VPOS3\_CP}$ , and $V_{VPOS4\_IF}$                             |                     |

| Digital Input/Output Signal (SCLK, SDI,                           | 3.6 V               |

| SDO, CS, ENBL1, and ENBL0)                                        |                     |

| RFIN                                                              | 0 dBm               |

| Source and Sink Current (MUXOUT)                                  | 300 μΑ              |

| Maximum Junction Temperature                                      | 125°C               |

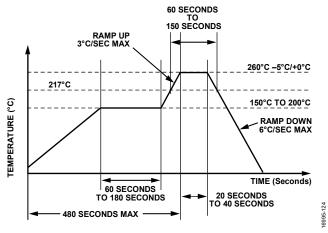

| Peak Reflow Temperature                                           | 260°C               |

| Operating Temperature Range                                       | −40°C to +85°C      |

| Storage Temperature Range                                         | −65°C to +150°C     |

| Electrostatic Discharge (ESD) Sensitivity                         |                     |

| Human Body Model (HBM)                                            | 500 V <sup>1</sup>  |

|                                                                   | $2000 \text{ V}^2$  |

|                                                                   | 1500 V <sup>3</sup> |

| Field Induced Charged Device Model (FICDM) <sup>1</sup>           | 500 V               |

<sup>&</sup>lt;sup>1</sup> ADMV4420 のすべてのピンに適用。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

図 2. 鉛フリー・リフロー・プロファイル

#### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

$\theta_{1A}$  は 1 立方フィートの密閉容器内で測定される自然対流下での周囲とジャンクション間の熱抵抗、 $\theta_{1C}$  はジャンクションとケース間の熱抵抗です。

表 3. 熱抵抗

| Package Type | $\theta_{JC}^{1}$ | $\theta_{JA}^{1}$ | Unit |

|--------------|-------------------|-------------------|------|

| CP-32-12     | 7.25              | 39.6              | °C/W |

$<sup>^{1}</sup>$   $\theta_{IA}$   $\geq$   $\theta_{IC}$  の値は、熱設計が考慮されたヒート・シンク付き PCB を測定することによって決定されます。

#### ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。 電荷を帯びたデバイスや回路ボードは、検知されな

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

Rev. 0 — 6/60 —

<sup>&</sup>lt;sup>2</sup> MUXOUT、ENBLO、ENBLI、SDO、SDI、SCLK、CSピンを除くすべてのピンに適用。

<sup>&</sup>lt;sup>3</sup> MUXOUT、ENBL0、ENBL1、SDO、SDI、SCLK、CSピンに適用。

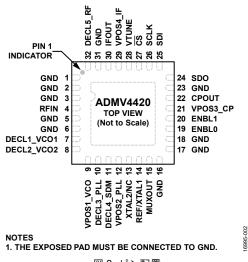

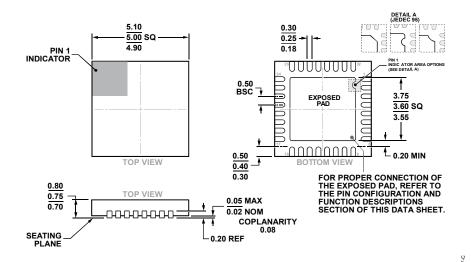

# ピン配置およびピン機能の説明

図 3. ピン配置

表 4. ピン機能の説明

| ピン番号                                    | 記号                                   | 説明                                                                                                                                                                                                                            |

|-----------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 5, 6,<br>16, 17, 18,<br>23, 31 | GND                                  | グラウンド。これらのピンとパッケージ底面は、RF/DCグラウンドに接続します。GNDインターフェース回路図については、図4を参照してください。                                                                                                                                                       |

| 4                                       | RFIN                                 | RF 入力ピン。このピンの入力インピーダンスは $50\Omega$ です。                                                                                                                                                                                        |

| 7, 8                                    | DECL1_VCO1,<br>DECL2_VCO2            | LDO レギュレータ用デカップリング・ピン。10μF のコンデンサをこのピンの近くに配置してください。                                                                                                                                                                           |

| 9                                       | VPOS1_VCO                            | 5V 電源ピン。0.1μF と 100pF のデカップリング・コンデンサをこのピンの近くに配置してください。                                                                                                                                                                        |

| 10, 11, 32                              | DECL3_PLL,<br>DECL4_SDM,<br>DECL5_RF | LDO 用デカップリング・ピン。10μF のコンデンサをこのピンの近くに配置してください。                                                                                                                                                                                 |

| 12                                      | VPOS2_PLL                            | 5V 電源。0.1μF と 100pF のデカップリング・コンデンサをこのピンの近くに配置してください。                                                                                                                                                                          |

| 13                                      | XTAL2/NC                             | 水晶発振器入力または未接続(No Connect)。外部水晶発振器使用時は、REF/XTAL1ピンと XTAL2/DNCピンの間に水晶発振器を接続します。REF/XTAL1ピンを通じて外部リファレンス入力信号を加える場合は、このピンを未接続(No Connect)ピンとして使用します。REF/XTAL1ピンを通じて外部リファレンス入力信号を加えるときは、InFのコンデンサを介してこのピンをグラウンドに接続してください(AC グラウンド)。 |

| 14                                      | REF/XTAL1                            | 外部リファレンス入力または水晶発振器入力。外部水晶発振器使用時は、XTAL1ピンと XTAL2ピンの間に水晶発振器を接続します。外部リファレンス入力として使用するときは、0.01μFの DC 阻止コンデンサを介してこのピンに外部リファレンス信号を加えてください。外部入力の構成については、図 121を参照してください。このピンは内部で 1.65V にバイアスされます。                                      |

| 15                                      | MUXOUT                               | PLLマルチプレクサ出力。                                                                                                                                                                                                                 |

| 19                                      | ENBL0                                | デバイス・イネーブル 0。公称値で動作させるには、このピンを 3.3V に接続してください。                                                                                                                                                                                |

| 20                                      | ENBL1                                | デバイス・イネーブル 1。公称値で動作させるには、このピンを 3.3V に接続してください。                                                                                                                                                                                |

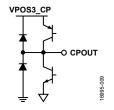

| 21                                      | VPOS3_CP                             | 5V 電源。0.1μF と 100pF のデカップリング・コンデンサをこのピンの近くに配置してください。                                                                                                                                                                          |

| 22                                      | CPOUT                                | シンセサイザ・チャージ・ポンプ出力。このピンは、ループ・フィルタを介して VTUNE (ピン 28) に接続します。                                                                                                                                                                    |

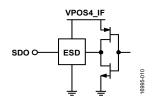

| 24                                      | SDO                                  | シリアル・ペリフェラル・インターフェース (SPI) データ出力。3.3V ロジック。                                                                                                                                                                                   |

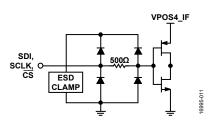

| 25                                      | SDI                                  | SPI データ入力。3.3V ロジック。                                                                                                                                                                                                          |

| 26                                      | SCLK                                 | SPI クロック。3.3V ロジック。                                                                                                                                                                                                           |

| 27                                      | CS                                   | SPIチップ・セレクト。3.3Vロジック。アクティブ・ロー。                                                                                                                                                                                                |

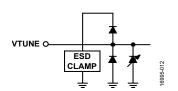

| 28                                      | VTUNE                                | VCOチューニング電圧。このピンはループ・フィルタの出力によって駆動されます。                                                                                                                                                                                       |

| 29                                      | VPOS4_IF                             | 5V電源。0.1μFと100pFのデカップリング・コンデンサをこのピンの近くに配置してください。                                                                                                                                                                              |

| 30                                      | IFOUT                                | IF 出力。このピンの出力インピーダンスは $75\Omega$ です。IF アンプの出力段はオープンコレクタ構成で、 $5V$ の DC バイアスを必要とします。バイアス・チョーク・インダクタを使用してください。詳細については、IF 出力 $-$ 外付けインダクタ $/$ バイアスのセクションを参照してください。                                                                |

|                                         | EPAD                                 | 露出パッド。露出パッドは GND に接続する必要があります。                                                                                                                                                                                                |

Rev. 0 - 7/60 -

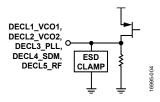

## インターフェース回路図

図 4. GND インターフェース回路図

図 5. DECL1\_VCO1、DECL2\_VCO2、DECL3\_PLL、DECL4\_SDM、および DECL5\_RF のインターフェース回路図

図 6. RFIN インターフェース回路図

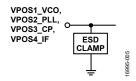

図 7. VPOS1\_VCO、VPOS2\_PLL、VPOS3\_CP、および VPOS4\_IF のインターフェース回路図

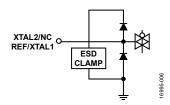

図 8. XTAL2/NC と REF/XTAL1 のインターフェース回路図

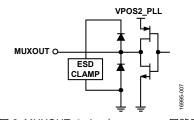

図 9. MUXOUT のインターフェース回路図

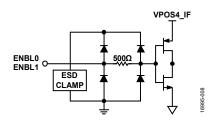

図 10. ENBL0 と ENBL1 のインターフェース回路図

図 11. CPOUT のインターフェース回路図

図 12. SDO のインターフェース回路図

図 13. SDI、SCLK、およびCSのインターフェース回路図

図 14. VTUNE のインターフェース回路図

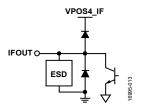

図 15. IFOUT のインターフェース回路図

Rev. 0 - 8/60 -

# 代表的な性能特性

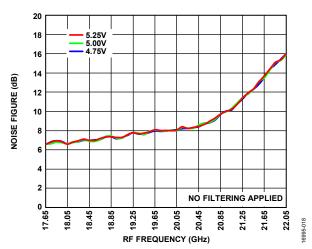

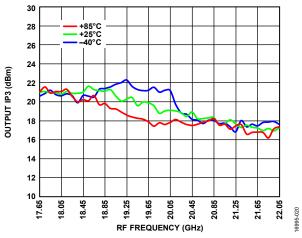

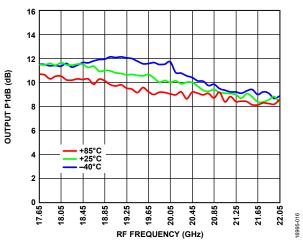

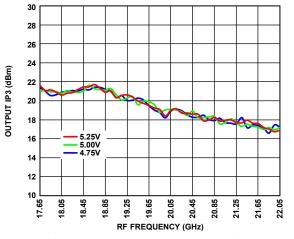

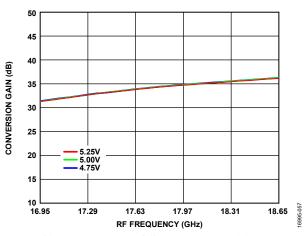

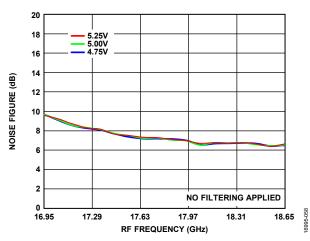

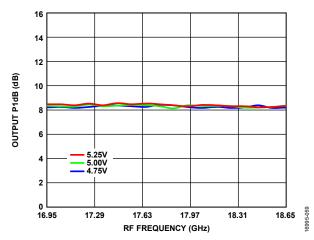

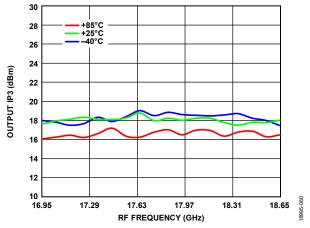

特に指定のない限り、 $V_{VPOS1\_VCO} = V_{VPOS2\_PLL} = V_{VPOS3\_CP} = V_{VPOS4\_F} = 5V$ 、RF 入力電力 = -40 dBm、PLL ループ・フィルタ帯域幅 = 60 kHz (位相マージン 45°) とし、50 MHz の 0 dBm 外部リファレンスで測定を実施。

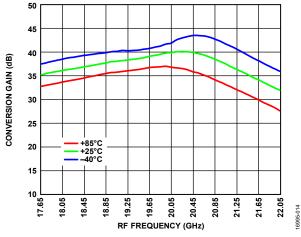

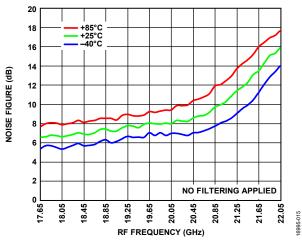

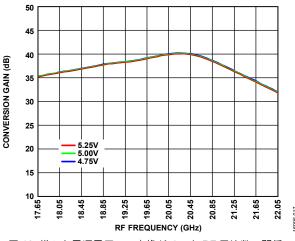

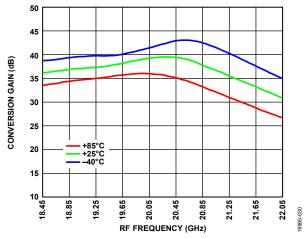

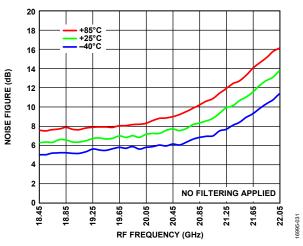

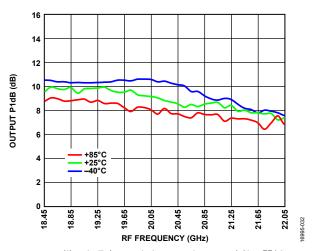

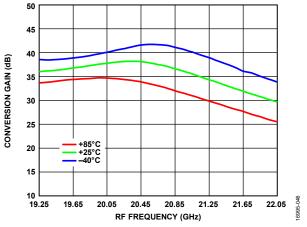

## IF = 900MHz でのローサイド・インジェクション LO 性能

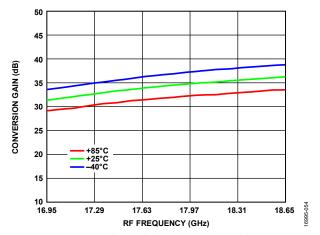

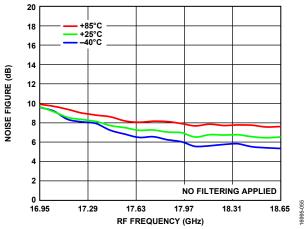

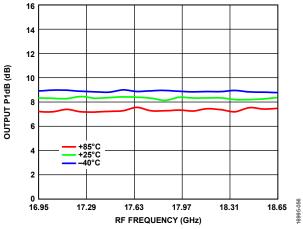

RFの最小周波数と最大周波数は、最小LO周波数 (16.75MHz) と最大LO周波数 (21.15GHz) によって制限されます。

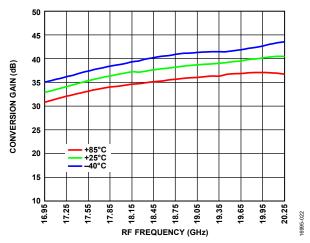

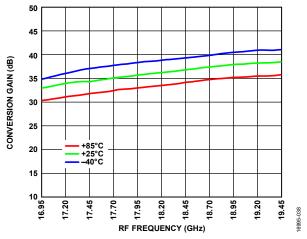

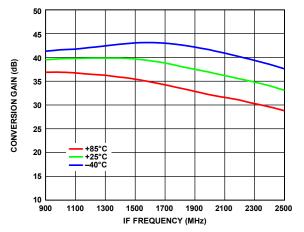

図 16. 様々な温度での変換ゲインと RF 周波数の関係

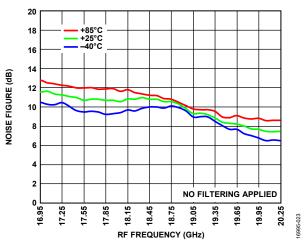

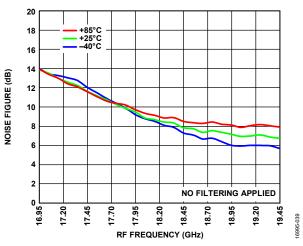

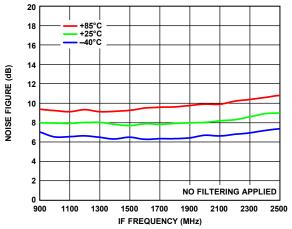

図 17. 様々な温度でのノイズ指数と RF 周波数の関係

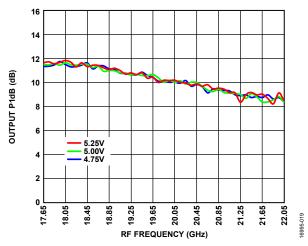

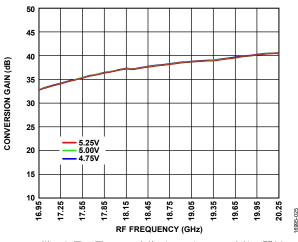

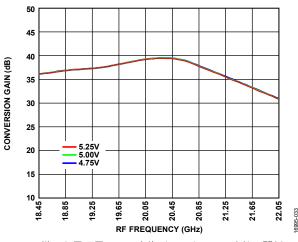

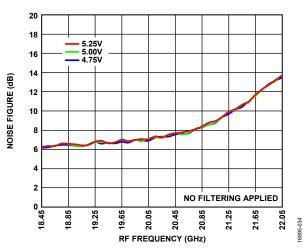

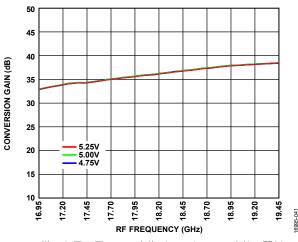

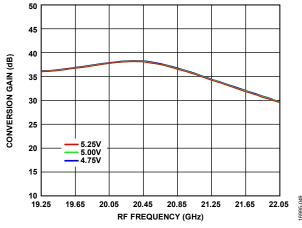

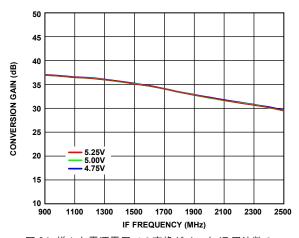

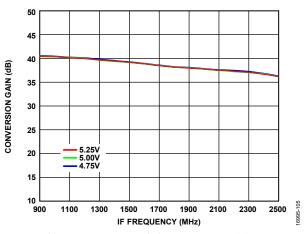

図 18. 様々な電源電圧での変換ゲインと RF 周波数の関係、  $T_A = 25^{\circ}C$

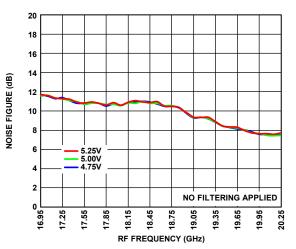

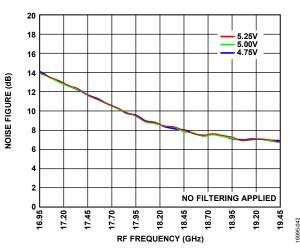

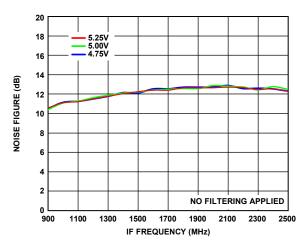

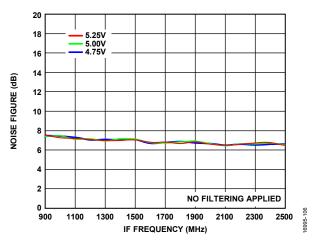

図 19. 様々な電源電圧でのノイズ指数と RF 周波数の関係、  $T_A = 25^{\circ}C$

Rev. 0 - 9/60 -

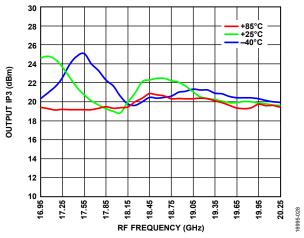

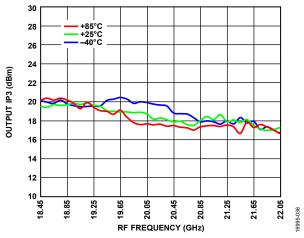

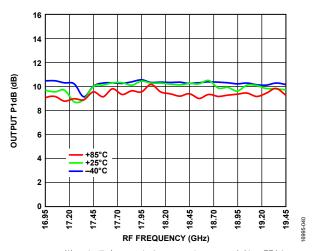

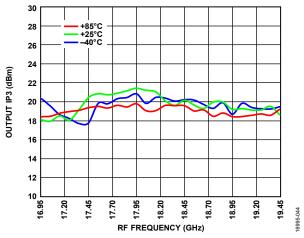

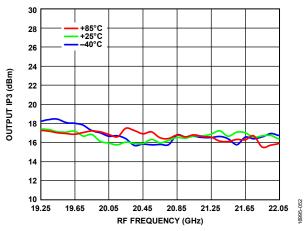

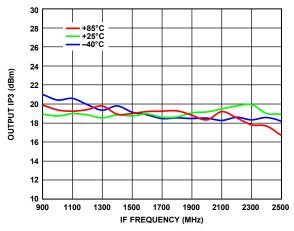

図 20. 様々な温度での出力 IP3 と RF 周波数の関係

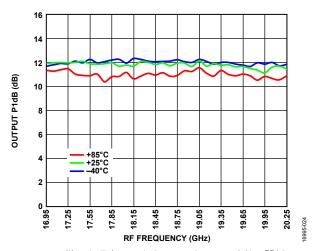

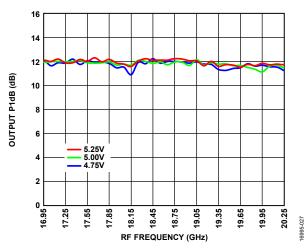

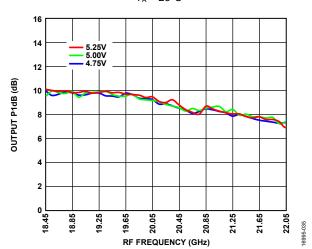

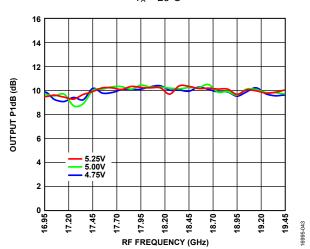

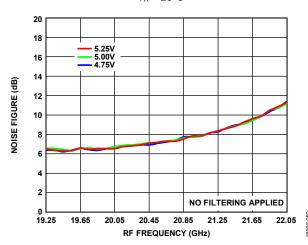

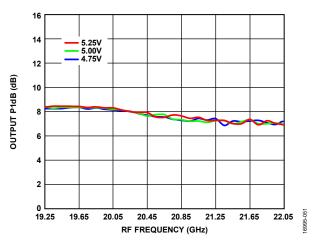

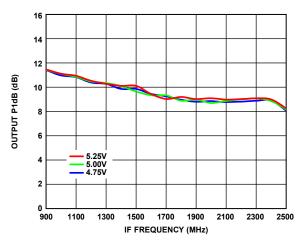

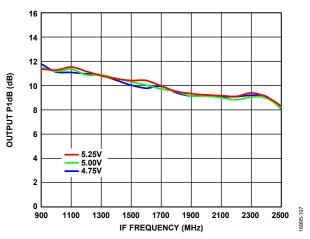

図 21. 様々な電源電圧での出力 P1dB と RF 周波数の関係、  $T_A=25^{\circ}C$

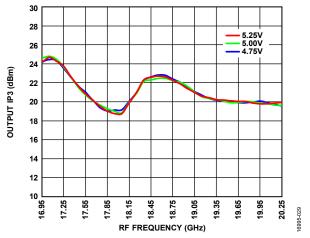

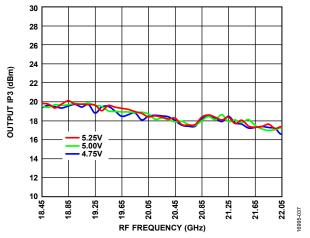

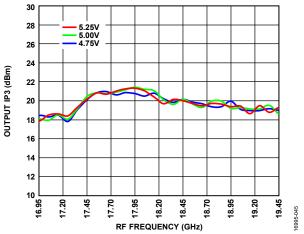

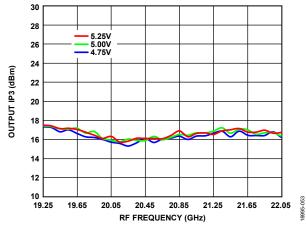

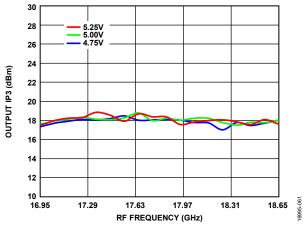

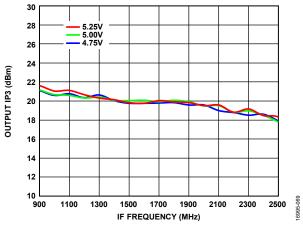

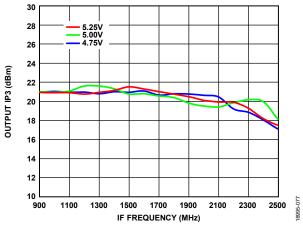

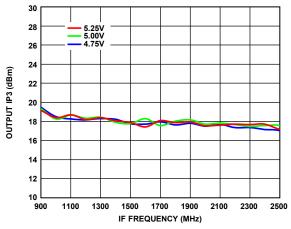

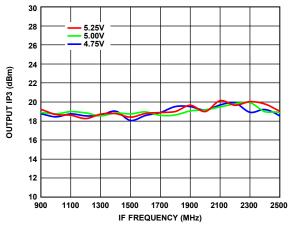

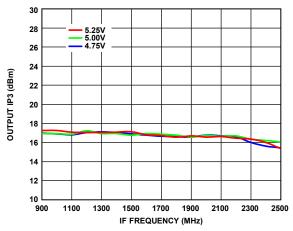

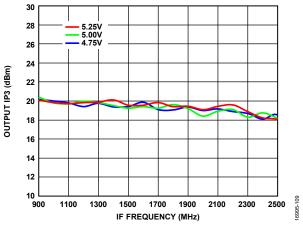

図 22. 様々な電源電圧での出力 IP3 と RF 周波数の関係、  $T_A=25^{\circ}C$

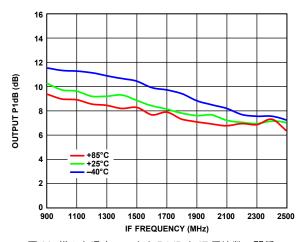

図 23. 様々な温度での出力 P1dB と RF 周波数の関係

Rev. 0 — 10/60 —

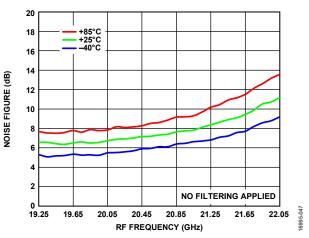

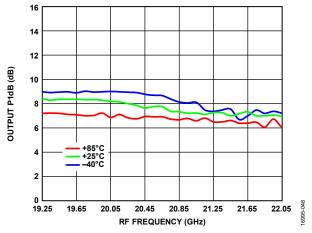

# IF = 900MHz でのハイサイド・インジェクション LO 性能

最大限の性能を得るために、RF最小周波数は16.95GHzに、RF最大周波数は最大LO周波数(21.15GHz)に制限されています。

図 24. 様々な温度での変換ゲインと RF 周波数の関係

図 25. 様々な温度でのノイズ指数と RF 周波数の関係

図 26. 様々な温度での出力 P1dB と RF 周波数の関係

図 27. 様々な電源電圧での変換ゲインと RF 周波数の関係、  $T_A=25^{\circ}C$

図 28. 様々な電源電圧でのノイズ指数と RF 周波数の関係、 T<sub>A</sub> = 25°C

図 29. 様々な電源電圧での出力 P1dB と RF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 11/60 —

図 30. 様々な温度での出力 IP3 と RF 周波数の関係

図 31. 様々な電源電圧での出力 IP3 と RF 周波数の関係、  $T_A=25^{\circ}\mathrm{C}$

Rev. 0 — 12/60 —

# IF = 1700MHz でのローサイド・インジェクション LO 性能

最大限の性能を得るために、RF最小周波数は最小LO周波数 (16.75GHz) に、RF最大周波数は 22.05GHz に制限されています。

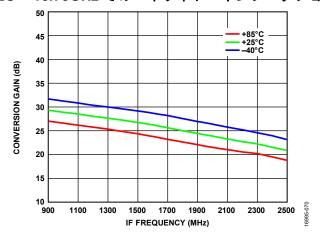

図 32. 様々な温度での変換ゲインと RF 周波数の関係

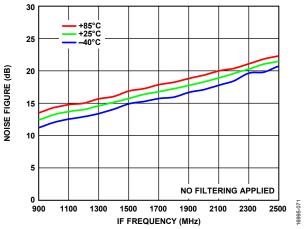

図 33. 様々な温度でのノイズ指数と RF 周波数の関係

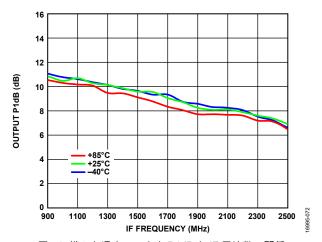

図 34. 様々な温度での出力 P1dB と RF 周波数の関係

図 35. 様々な電源電圧での変換ゲインと RF 周波数の関係、  $T_A = 25^{\circ}C$

図 36. 様々な電源電圧でのノイズ指数と RF 周波数の関係、 T<sub>A</sub> = 25°C

図 37. 様々な電源電圧での出力 P1dB と RF 周波数の関係、  $T_A = 25^{\circ}C$

Rev. 0 — 13/60 —

図 38. 様々な温度での出力 IP3 と RF 周波数の関係

図 39. 様々な電源電圧での出力 IP3 と RF 周波数の関係、  $T_A=25^{\circ}\mathrm{C}$

Rev. 0 — 14/60 —

# IF = 1700 MHz でのハイサイド・インジェクション LO 性能

最大限の性能を得るために、RF最小周波数は16.95GHzに、RF最大周波数は最大LO周波数(21.15GHz)に制限されています。

図 40. 様々な温度での変換ゲインと RF 周波数の関係

図 41. 様々な温度でのノイズ指数と RF 周波数の関係

図 42. 様々な温度での出力 P1dB と RF 周波数の関係

図 43. 様々な電源電圧での変換ゲインと RF 周波数の関係、  $T_A=25^{\circ}C$

図 44. 様々な電源電圧でのノイズ指数と RF 周波数の関係、 T<sub>A</sub> = 25°C

図 45. 様々な電源電圧での出力 P1dB と RF 周波数の関係、  $T_A = 25^{\circ}C$

Rev. 0 — 15/60 —

図 46. 様々な温度での出力 IP3 と RF 周波数の関係

図 47. 様々な電源電圧での出力 IP3 と RF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 16/60 —

# IF = 2500 MHz でのローサイド・インジェクション LO 性能

この構成では、最大限の性能を得るために RF 最小周波数が最小 LO 周波数 (16.75GHz) に、RF 最大周波数が 22.05GHz に制限されています。

図 48. 様々な温度での変換ゲインと RF 周波数の関係

図 49. 様々な温度でのノイズ指数と RF 周波数の関係

図 50. 様々な温度での出力 P1dB と RF 周波数の関係

図 51. 様々な電源電圧での変換ゲインと RF 周波数の関係、 T<sub>A</sub> = 25°C

図 52. 様々な電源電圧でのノイズ指数と RF 周波数の関係、 T<sub>A</sub> = 25℃

図 53. 様々な電源電圧での出力 P1dB と RF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 17/60 —

図 54. 様々な温度での出力 IP3 と RF 周波数の関係

図 55. 様々な電源電圧での出力 IP3 と RF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 18/60 —

# IF = 2500 MHz でのハイサイド・インジェクション LO 性能

最大限の性能を得るために、RF最小周波数は16.95GHzに、RF最大周波数は最大LO周波数(21.15GHz)に制限されています。

図 56. 様々な温度での変換ゲインと RF 周波数の関係

図 57. 様々な温度でのノイズ指数と RF 周波数の関係

図 58. 様々な温度での出力 P1dB と RF 周波数の関係

図 59. 様々な電源電圧での変換ゲインと RF 周波数の関係、 T<sub>A</sub> = 25°C

図 60. 様々な電源電圧でのノイズ指数と RF 周波数の関係、 T<sub>A</sub> = 25°C

図 61. 様々な電源電圧での出力 P1dB と RF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 19/60 —

図 62. 様々な温度での出力 IP3 と RF 周波数の関係

図 63. 様々な電源電圧での出力 IP3 と RF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 20/60 —

## LO = 16.75GHz でのローサイド・インジェクション性能

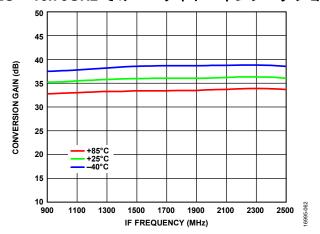

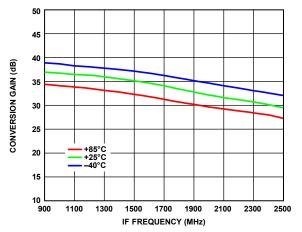

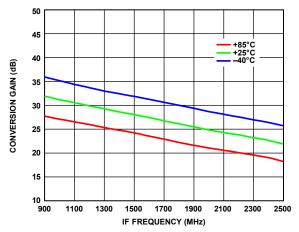

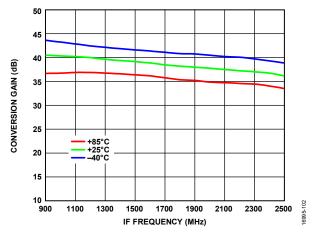

図 64. 様々な温度での変換ゲインと IF 周波数の関係

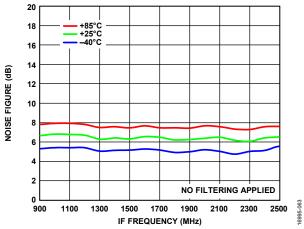

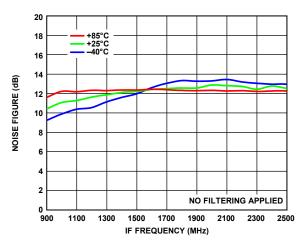

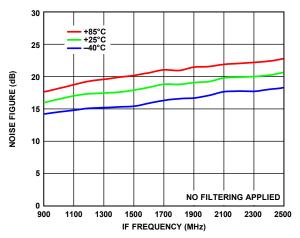

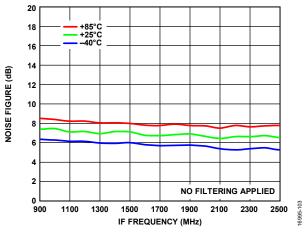

図 65. 様々な温度でのノイズ指数と IF 周波数の関係

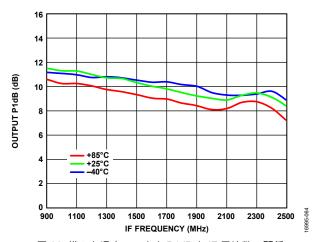

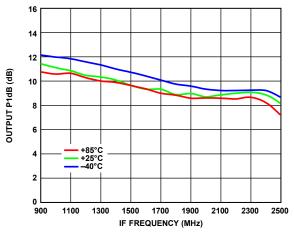

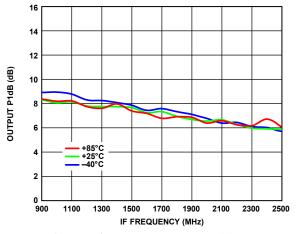

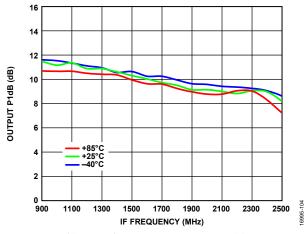

図 66. 様々な温度での出力 P1dB と IF 周波数の関係

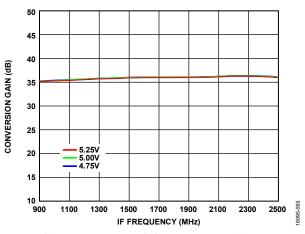

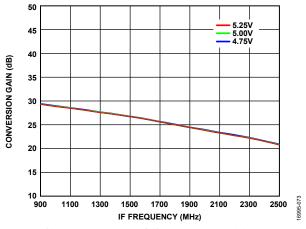

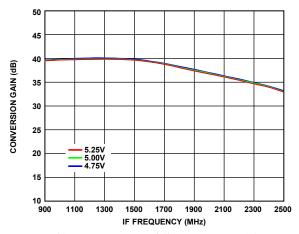

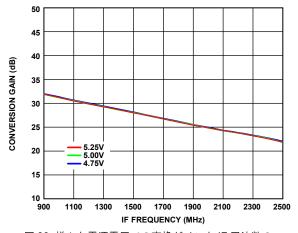

図 67. 様々な電源電圧での変換ゲインと IF 周波数の関係、 $T_A=25^{\circ}C$

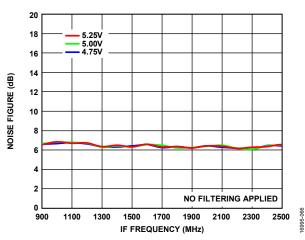

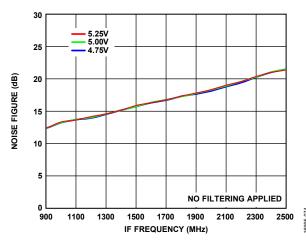

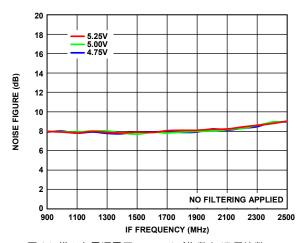

図 68. 様々な電源電圧でのノイズ指数と IF 周波数の関係、 T<sub>A</sub> = 25°C

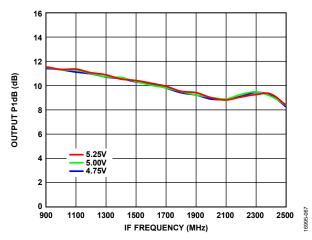

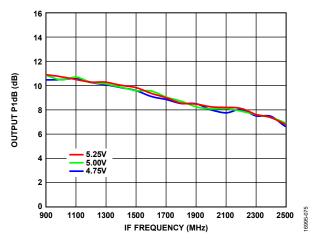

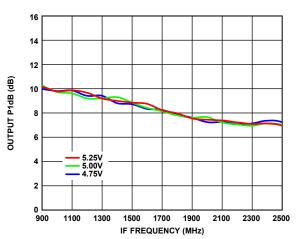

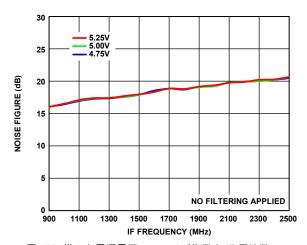

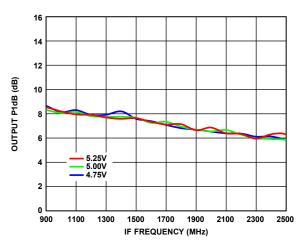

図 69. 様々な電源電圧での出力 P1dB と IF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 21/60 —

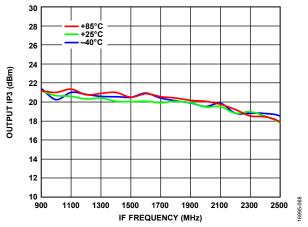

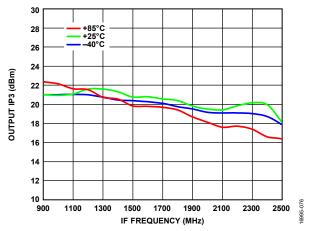

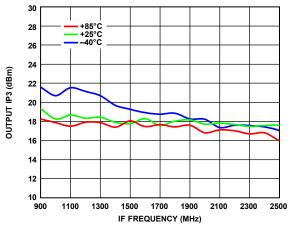

図 70. 様々な温度での出力 IP3 と IF 周波数の関係

図 71. 様々な電源電圧での出力 IP3 と IF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 22/60 —

# LO = 16.75GHz でのハイサイド・インジェクション性能

図 72. 様々な温度での変換ゲインと IF 周波数の関係

図 73. 様々な温度でのノイズ指数と IF 周波数の関係

図 74. 様々な温度での出力 P1dB と IF 周波数の関係

図 75. 様々な電源電圧での変換ゲインと IF 周波数の関係、 $T_A=25^{\circ}C$

図 76. 様々な電源電圧でのノイズ指数と IF 周波数の関係、 T<sub>A</sub> = 25°C

図 77. 様々な電源電圧での出力 P1dB と IF 周波数の関係、 T<sub>A</sub> = 25°C

Rev. 0 — 23/60 —

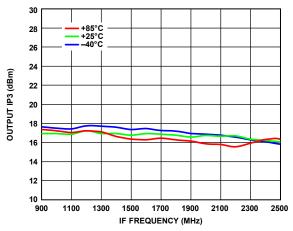

図 78. 様々な温度での出力 IP3 と IF 周波数の関係

図 79. 様々な電源電圧での出力 IP3 と IF 周波数の関係、 T<sub>A</sub> = 25℃

Rev. 0 — 24/60 —

## LO = 18.95GHz でのローサイド・インジェクション性能

図 80. 様々な温度での変換ゲインと IF 周波数の関係

図 81. 様々な温度でのノイズ指数と IF 周波数の関係

図 82. 様々な温度での出力 P1dB と IF 周波数の関係

図 83. 様々な電源電圧での変換ゲインと IF 周波数の 関係、T<sub>A</sub> = 25℃

図 84. 様々な電源電圧でのノイズ指数と IF 周波数の 関係、T<sub>A</sub> = 25℃

図 85. 様々な電源電圧での出力 P1dB と IF 周波数の 関係、T<sub>A</sub> = 25°C

Rev. 0 — 25/60 —

図 86. 様々な温度での出力 IP3 と IF 周波数の関係

図 87. 様々な電源電圧での出力 IP3 と IF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 26/60 —

## LO = 18.95 GHz でのハイサイド・インジェクション性能

図 88. 様々な温度での変換ゲインと IF 周波数の関係

図 89. 様々な温度でのノイズ指数と IF 周波数の関係

図 90. 様々な温度での出力 P1dB と IF 周波数の関係

図 91. 様々な電源電圧での変換ゲインと IF 周波数の 関係、T<sub>A</sub> = 25°C

図 92. 様々な電源電圧でのノイズ指数と IF 周波数の 関係、T<sub>A</sub> = 25℃

図 93. 様々な電源電圧での出力 P1dB と IF 周波数の 関係、T<sub>A</sub> = 25°C

Rev. 0 — 27/60 —

図 94. 様々な温度での出力 IP3 と IF 周波数の関係

図 95. 様々な電源電圧での出力 IP3 と IF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 28/60 —

# LO = 21.15GHz でのローサイド・インジェクション性能

図 96. 様々な温度での変換ゲインと IF 周波数の関係

図 97. 様々な温度でのノイズ指数と IF 周波数の関係

図 98. 様々な温度での出力 P1dB と IF 周波数の関係

図 99. 様々な電源電圧での変換ゲインと IF 周波数の 関係、T<sub>A</sub> = 25°C

図 100. 様々な電源電圧でのノイズ指数と IF 周波数の 関係、T<sub>A</sub> = 25°C

図 101. 様々な電源電圧での出力 P1dB と IF 周波数の 関係、T<sub>A</sub> = 25°C

Rev. 0 — 29/60 —

図 102. 様々な温度での出力 IP3 と IF 周波数の関係

図 103. 様々な電源電圧での出力 IP3 と IF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 30/60 —

## LO = 21.15 GHz でのハイサイド・インジェクション性能

図 104. 様々な温度での変換ゲインと IF 周波数の関係

図 105. 様々な温度でのノイズ指数と IF 周波数の関係

図 106. 様々な温度での出力 P1dB と IF 周波数の関係

図 107. 様々な電源電圧での変換ゲインと IF 周波数の関係、  $T_A = 25^{\circ}C$

図 108. 様々な電源電圧でのノイズ指数と IF 周波数の関係、  $T_A = 25^{\circ}C$

図 109. 様々な電源電圧での出力 P1dB と IF 周波数の関係 、T<sub>A</sub> = 25°C

Rev. 0 — 31/60 —

図 110. 様々な温度での出力 IP3 と IF 周波数の関係

図 111. 様々な電源電圧での出力 IP3 と IF 周波数の関係、  $T_A=25^{\circ}C$

Rev. 0 — 32/60 —

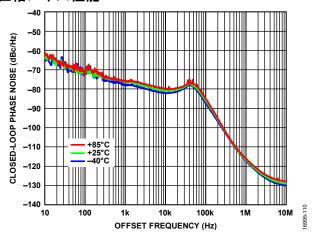

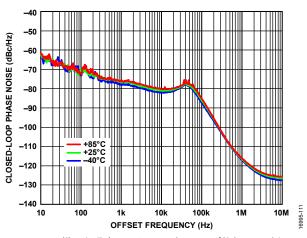

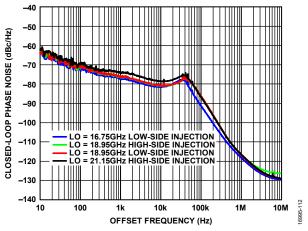

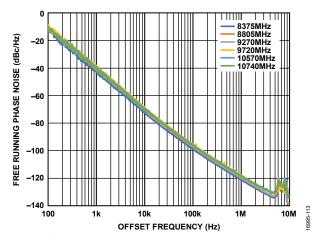

#### 位相ノイズ性能

図 112. 様々な温度でのクローズドループ位相ノイズと オフセット周波数の関係、IF = 900MHz、 ローサイド・インジェクション LO = 18.95GHz

図 113. 様々な温度でのクローズドループ位相ノイズと オフセット周波数の関係、IF = 900MHz、 ハイサイド・インジェクション LO = 18.95GHz

図 114. 様々な LO 周波数でのクローズドループ位相ノイズと オフセット周波数の関係、 $T_A = 25^{\circ}C$

図 115. 様々な VCO 周波数でのフリー・ランニング位相ノイズ とオフセット周波数の関係、T<sub>A</sub> = 25℃

Rev. 0 - 33/60 -

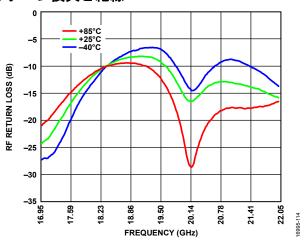

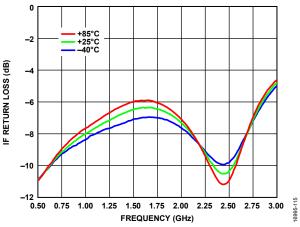

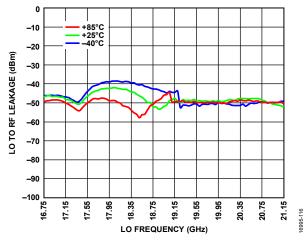

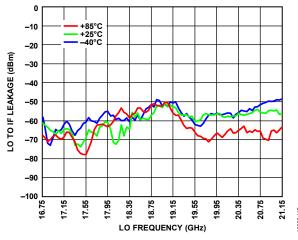

# リターン損失と絶縁

図 116. 様々な温度での RF リターン損失と周波数の関係、 LO = 18.95GHz

図 117. 様々な温度での IF リターン損失と周波数の関係、 LO = 18.95GHz、 $75\Omega$  出力システムに基づく

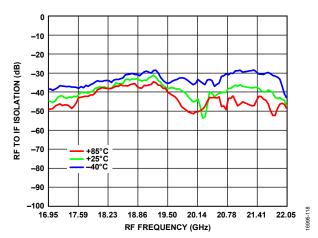

図 118. 様々な温度での LO-RF リークと LO 周波数の関係、ローサイド・インジェクション LO、IF = 900MHz

図 119. 様々な温度での LO-IF リークと LO 周波数の関係、 ローサイド・インジェクション LO、IF = 900MHz

図 120. 様々な温度での RF-IF リークと RF 周波数の関係、 LO = 21.15GHz

Rev. 0 - 34/60 -

## スプリアスおよび高調波性能

#### LO 高調波

すべての値は dBm 単位、測定位置は IF 出力です。 トレース損失 とコネクタ損失の影響は除去されています。

#### 表 5. IF 出力における LO 高調波

|                    | LO Harmonics (dBm) |     |     |     |     |  |

|--------------------|--------------------|-----|-----|-----|-----|--|

| LO Frequency (GHz) | 0.25               | 0.5 | 1   | 1.5 | 2   |  |

| 16.75              | -110               | -49 | -58 | -71 | -66 |  |

| 18.95              | -113               | -41 | -45 | -63 | -62 |  |

| 21.15              | -111               | -34 | -58 | -85 | -69 |  |

#### リファレンス入力(REFIN)高調波

すべての値は dBm 単位、測定位置は IF 出力です。 トレース損失 とコネクタ損失の影響は除去されています。 リファレンス周波数は 50MHz です。

表 6. IF 出力における REFIN 高調波

| REFIN              |     |     | REFI | N Harmonics (dBm) |     |     |     |     |

|--------------------|-----|-----|------|-------------------|-----|-----|-----|-----|

| Frequency<br>(MHz) | 1   | 2   | 3    | 4                 | 5   | 6   | 7   | 8   |

| 50                 | -78 | -46 | -60  | -47               | -57 | -56 | -61 | -59 |

#### IF 高調波

すべての値はdBm単位、測定位置はIF出力です。トレース損失とコネクタ損失の影響は除去されています。ダウンコンバートされたIF周波数は900MHzです。

#### 表 7. IF 出力における IF 高調波

|                    | IF Harmonics (dBm) |     |     |     |     |  |

|--------------------|--------------------|-----|-----|-----|-----|--|

| IF Frequency (MHz) | 1                  | 2   | 3   | 4   | 5   |  |

| 900                | -7                 | -42 | -58 | -89 | -90 |  |

## ダウンコンバータのスプリアス出力

特に指定のない限り、ミキサーのスプリアス積は IF 出力電力レベルから dBc 単位で測定しています。トレース損失とコネクタ損失の影響は除去されています。N/A は該当なしを表します。

RF = 19.85GHz、LO = 18.95GHz、IF = 0.9GHz、RF パワー = -40dBm。スプリアス周波数は(M × RF)+(N × LO/2)の絶対値です。

|        |    |     | N × LO |      |     |     |  |  |  |

|--------|----|-----|--------|------|-----|-----|--|--|--|

|        |    | 0   | 1      | 2    | 3   | 4   |  |  |  |

|        | -2 | -95 | -99    | -101 | -91 | -37 |  |  |  |

|        | -1 | -78 | -77    | 0    | -81 | -90 |  |  |  |

| M × RF | 0  | N/A | -46    | -50  | -65 | -56 |  |  |  |

|        | +1 | -78 | -98    | -80  | -88 | N/A |  |  |  |

|        | +2 | -95 | -88    | N/A  | N/A | N/A |  |  |  |

RF = 18.05GHz、LO = 18.95GHz、IF = 0.9GHz、RF パワー = -40dBm。スプリアス周波数は( $M \times RF$ )+( $N \times LO/2$ )の絶対値です。

|        |    | N × LO |     |      |     |     |

|--------|----|--------|-----|------|-----|-----|

|        |    | 0      | 1   | 2    | 3   | 4   |

| M × RF | -2 | -77    | -70 | 0    | -82 | -87 |

|        | -1 | -95    | -98 | -103 | -96 | -41 |

|        | 0  | N/A    | -45 | -49  | -64 | -55 |

|        | +1 | -77    | -98 | -93  | -89 | N/A |

|        | +2 | -95    | -89 | N/A  | N/A | N/A |

Rev. 0 - 35/60 -

# 動作原理

# リファレンス入力段

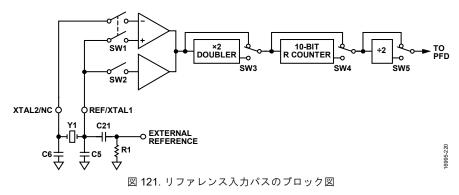

図 121 に示すリファレンス入力段は、差動励振を行う 50MHz の水晶発振器を使用しています。リファレンス入力は、50MHz のシングルエンド外部入力で駆動することもできます。入力設定の選択にはREF\_IN\_MODE ビット(レジスタ 0x20E、ビット 1)を使用します。水晶発振器モードを選択するには、このビットを 0 に設定して SW1 スイッチを閉じ、SW2 スイッチを開きます。シングルエンド・モードを選択するには、このビットを 1 に設定して SW2 スイッチを閉じ、SW1 スイッチを開きます。

水晶発振器には、等価直列抵抗(ESR)と負荷コンデンサを適切に定義できるようなものを選ぶ必要があります。最も厳しい条件での例を示すために、評価用ボードで選択した水晶発振器には  $100\Omega$  の最大 ESR が使われています。全温度範囲とあらゆるプロセス変動を通じて水晶発振器を起動できるようにするために、最大 ESR は  $40\Omega$  とすることを推奨します。公称水晶発振器用負荷コンデンサ( $C_{LOAD}$ )の容量は 10pF で、これは、C5 と C6 を直列に組み合わせた場合を前提に計算した値です。 $C_{LOAD}$  は  $8pF\sim12pF$  の間に保つことを推奨します。更に、水晶発振器モードでは C21 を取り付けないようにしてください。このコンデンサが水晶発振器の容量性負荷に影響を与え、更にそれによって発振が妨げられる可能性があるためです。

#### リファレンス2逓倍器、Rカウンタ、RDIV2

図 121 に示すリファレンス入力段の後には、より高い位相周波数検出器周波数(fpfd)の生成を可能にする内部リファレンス 2 逓倍ブロック(2 逓倍器)があります。fpfd を高くすることは、システム全体の位相ノイズ性能を向上させる上で有効です。通常、fpfd を 2 倍にすると、帯域内位相ノイズ性能が最大で3dBc/Hz向上します。リファレンス 2 逓倍器をイネーブルするには、EN\_REF\_X2 ビット(レジスタ 0x20E、ビット 2)を使用します。このビットにより、図 121 に示すように SW3 をトグルします。

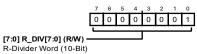

リファレンス 2 逓倍器ブロックの後段には、2 つの分周器、つまり 10 ビットの R カウンタ( $1\sim1023$  までカウント可能)と 2 分周ブロックがあります。これらの分周器を使用すると、入力リファレンス周波数( $f_{REF}$ )を分周して、より低い  $f_{PED}$  を生成することができます。これは、出力のフラクショナル N 整数境界スプリアスを最小限に抑える助けとなります。

R カウンタは、レジスタ 0x20C とレジスタ 0x20D の  $R_DIV$  ビットを使って設定します。 $R_DIV = 1$  の場合、SW4 スイッチは図 121 に示す位置になります。それ以外の場合は、SW4 スイッチは R カウンタを使用するようにトグルされます。

リファレンス 2 分周ブロックは RDIV2\_SEL ビット(レジスタ0x20E、ビット 0)を使ってイネーブルします。このビットにより、図 121 に示すように SW5 スイッチをトグルします。

Rev. 0 — 36/60 —

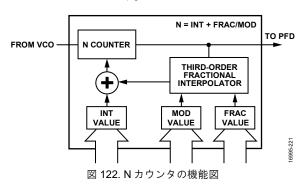

#### Nカウンタ

Nカウンタは、VCO からの PLL 帰還パスの分周比を設定します。 VCO 信号は、ダブル・バランスド・ミキサーで LO 周波数を得るために 2 逓倍されます。分周比は、このカウンタを構成するインテジャーN値(INT)、フラクショナル N値(FRAC)、およびモジュラス値(MOD)を使って決定されます。 INT、FRAC、および MOD 値の設定に使用するレジスタは、レジスタ  $0x200\sim$ レジスタ  $0x200\sim$ レジスタ  $0x200\sim$ レジスタ  $0x200\sim$

### INT、FRAC、MOD、およびリファレンス・パス の関係

INT、FRAC、および MOD 値をリファレンス・パスと共に使用することで、 $f_{PFD}$ の分周値を間隔として VCO 周波数を生成することができます。

fprd はリファレンス周波数(fref)とリファレンス・パス設定パラメータから計算できます。

$$f_{PFD} = f_{REF} \times \frac{1+D}{R \times (1+T)} \tag{1}$$

ここで、

Dはリファレンス2逓倍器ビット(0または1)、

Rは2進10ビット・プログラマブル・カウンタのリファレンス 分周比(1~1023)、

Tはリファレンス 2 分周ビットです(0 または 1)。

VCO 周波数 (fvco) は次式で計算します。

$$f_{VCO} = \frac{f_{LO}}{2} = f_{PFD} \times N \tag{2}$$

ここで、

fLoはミキサーを駆動するLOの周波数、

NはNカウンタの設定値です。

Nカウンタの値は次式で定義されます。

$$N = INT + \frac{FRAC}{MOD} = \frac{f_{LO}}{2f_{PFD}} = \frac{f_{VCO}}{f_{PFD}}$$

(3)

ここで、

INTは16ビット整数値(75~65,535)、

FRACは24ビット・プライマリ・モジュラス値の分子(0~16,777.215)、

*MOD*は24ビット・プライマリ・モジュラス値の分母(1~16,777,215)です。

N カウンタ値の INT 部分を得るには、フロア関数を使って切り下げを行います。

$$INT = FLOOR (N)$$

(4)

ここで、FLOOR はフロア関数です。

MOD パラメータの値を決定するには、チャンネル間隔のステップ・サイズ( $f_{CHSP}$ )と  $f_{PFD}$ を最初に選択する必要があります。

次に、 $f_{PFD}$ と最大公約数 (GCD) を使って MOD パラメータを計算します。

$$MOD = \frac{f_{PFD}}{GCD(f_{CHSP}, f_{PFD})}$$

(5)

FRAC 値は、与えられた N カウンタ値、INT 値、および MOD 値 に対して計算することができます。

$$FRAC = FLOOR \quad (MOD \times \quad (N-INT))$$

(6)

#### インテジャーN モード

FRAC 値がゼロの場合、シンセサイザはインテジャーN モードで動作します。

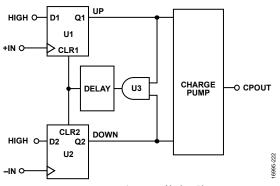

### 位相周波数検出器とチャージ・ポンプ

PFD は R カウンタと N カウンタから入力を受け取り、両者の位相差と周波数差に比例した出力を生成します。更にこの比例情報は、外部ループ・フィルタの駆動用電流を生成するチャージ・ポンプ(CP)回路に出力されて、VTUNE チューニング電圧を適切に増減させるために使われます。

図 123 に PFD と CP の簡略化した回路図を示します。PFD には 固定遅延素子が含まれており、これを使用して PFD の伝達関数 に不感帯が生じないようにして、リファレンス・スプリアス・レベルを一定にします。

図 123. PFD と CP の簡略回路図

#### ループ・フィルタ

PLL 用のループ・フィルタの決定には、PFD の周波数、N カウンタの値、VCOのチューニング感度特性(kvco)、選択した CP電流といった複数の要素が相互に関係します。fprdを高くすると帯域内位相ノイズが小さくなるという利点が得られますが、フラクショナル N モードで動作させたときの整数境界スプリアス・レベルの面で不利になります。逆に、fprd を低くするとインテジャーN モードで PLL を動作させることができ、それによって整数境界スプリアスをなくすことができますが、帯域内位相ノイズが大きくなってしまいます。このようなトレードオフがあるため、周波数プランニングと fprd の選択に注意して、エンド・アプリケーションにおいて適切な帯域内位相ノイズ性能を実現しながら、スプリアス・レベルを許容できるレベルに抑える必要があります。

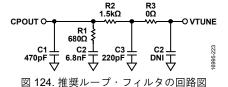

ADMV4420-EVALZ 評価用ボード上に実装されているループ・フィルタは、図 124に示すような 3 次パッシブ・フィルタです。フィルタは、以下のシミュレーション入力パラメータを使って設計されています。すなわち、 $f_{PFD}=50MHz$ 、 $k_{VCO}=80MHz/V$ 、 $f_{VCO}=9.4GHz$ 、 $I_{CP}=1.25mA$  です。これによって得られるループ・フィルタの帯域幅は 60kHz、位相マージンは  $45^{\circ}$  です。

ADMV4420 のループ・フィルタ・シミュレーションに関する詳細なガイダンスについては、アナログ・デバイセズのテクニカル・サポートへお問い合わせください。

#### CP 電流のセットアップ

特定の目的に合わせて設計されたループ・フィルタの場合は、 レジスタ 0x22E の  $CP_CURRENT$  値を調整することによって CP電流  $(I_{CP})$  を設定する必要があります。

CP電流は次式で表されます。

$$I_{CP} = (CP\_CURRENT + 1) \times 312.5\mu A \tag{7}$$

ここで、CP\_CURRENT は整数値(0~15)です。

CP\_CURRENT のデフォルト値は 3 で、この場合の電流値は 1.25mA です。適用可能な範囲は  $312.5\mu A \sim 5mA$  ( $312.5\mu A$  ステップ) です。

fprD を変更する場合、既存のループ・フィルタ部品に変更がないのであれば、以下の式に従って Icp の値を調整することを推奨します。

$$I_{CP(NEW)} = \frac{I_{CP(DEFAULT)} \times f_{PFD(DEFAULT)}}{f_{PFD(NEW)}} = \frac{1.25 \text{ mA} \times 50 \text{ MHz}}{f_{PFD(NEW)}}$$

(8)

ここで、

ICP (NEW) は新たに必要な ICP値、

ICP (DEFAULT) はデフォルトの ICP値、

fPFD (DEFAULT) はデフォルトの fPFD値、

fPFD (NEW) は必要な fPFD値です。

$I_{CP\ (NEW)}$  が得られたら、ラウンド関数(丸め関数)を使ってレジスタ 0x22E の  $CP\_CURRENT$  値を更新することができます。

$$CP\_CURRENT = ROUND \left( \frac{I_{CP(NEW)}}{312.5 \,\mu\text{A}} \right) - 1 \tag{9}$$

ここで、ROUND はラウンド関数です。

### ブリード電流(CP\_BLEED)のセットアップ

チャージ・ポンプはバイナリ・スケールのブリード電流( $I_{BLEED}$ )を含みますが、これはレジスタ 0x22F の  $CP\_BLEED$  値を使って設定します。ブリード電流は、フラクショナル N モードでの動作時に整数境界スプリアスを改善するため、PFD にわずかな位相オフセットを設定します。

一般にブリード電流は式 10 のとおりで、この式はほとんどのアプリケーションに適用可能な値を提供しますが、目的のアプリケーション向けに、実際の測定値から適切なブリード電流値を経験的に決定することにより、スプリアス・レベルを更に改善することができます。 適用可能な範囲は  $0\mu A \sim 956.25\mu A$  (3.75 $\mu A$  ステップ) です。

$$I_{BLEED} = CP\_BLEED \times 3.75 \,\mu\text{A} = \frac{4 \times I_{CP}}{N} \tag{10}$$

ここで、CP BLEED は整数値 (0~255) です。

$I_{BLEED}$  が得られたら、ラウンド関数を使ってレジスタ 0x22F の CP BLEED 値を更新できます。

$$CP\_BLEED = \text{ROUND}\left(\frac{I_{BLEED}}{3.75\,\mu\text{A}}\right)$$

(11)

ここで、 $I_{BLEED}$ は必要なチャージ・ポンプ・ブリード電流です。

#### **MUXOUT**

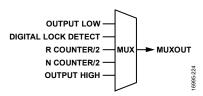

オンチップ・マルチプレクサ出力 (MUXOUT) は、デジタル・ロック検出機能を提供する他、様々な内部信号へのアクセスを可能にします。その代表的なブロック図を図 125 に示します。 MUXOUT ピンの状態は、レジスタ 0x213 の PLL\_MUX\_SEL の値で決まります。詳細については、表 31 を参照してください。

図 125. マルチプレクサの出力図

#### デジタル・ロック検出

MUXOUT ピンに出力されるデジタル・ロック検出機能には、レ ジスタ 0x214 で調整できる 2 つの機能があります。LD BIAS は 内部精度ウィンドウを調整し、LD COUNTはPLLロックを宣言 するための連続サイクル・カウントを調整します。これらの値 は、工場設定である 20μA と 8192 PFD サイクル・カウントのま まにしておくことを推奨します。特定アプリケーション用にこ れらの設定を調整する場合は、アナログ・デバイセズのテクニ カル・サポートへご相談ください。

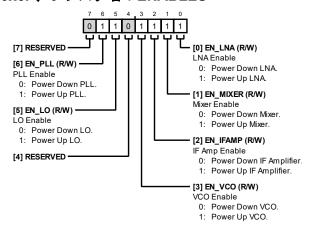

#### イネーブル

レジスタ 0x103 には、個々の回路ブロックのイネーブルが格納 されます。このレジスタを 0 に設定するとすべての回路ブロッ クがディスエーブルされ、消費電力は約 80mW となります。公 称動作とするには、このレジスタ内のすべてのイネーブル・ビ ットを1に設定してください(レジスタ値 0x6F)。ビット4と ビット7は予備なので、0に設定してください。

#### IF 出力 — 外付けインダクタ/バイアス

IF アンプ出力はオープンコレクタ構成で、VPOS4 IF 電源にプ ルアップされた外付けのバイアス用インダクタが必要です。イ ンダクタの推奨値は約 50nH で、少なくとも 150mA の電流容量 が必要です。この構成は DC 結合されているので、エンド・ア プリケーションの IF 出力と次段の間に直列コンデンサを置く必 要があります。この直列コンデンサの推奨最小値は 1nFです。

### SPI 構成

ADMV4420 の SPI は、4 ピン SPI ポートを介し、特定の機能や 動作に合わせてデバイスを構成することを可能にします。この インターフェースは柔軟性を更に高め、カスタマイズの可能性 を広げます。SPI は、SCLK、SDI、SDO、およびCSの 4 本の制 御ラインで構成されています。ADMV4420 のプロトコルは、書 込み/読出しビットと、その後に続く15ビットのレジスタ・ア ドレス、および8ビットのデータで構成されます。アドレス・ フィールドとデータ・フィールドは MSB ファースト構造で、 LSBで終了します。

書込み動作時は MSB を 0 に設定し、読出し動作時は MSB を 1に設定します。書込みサイクル・サンプリングは、SCLK の立 上がりエッジで行う必要があります。24 ビットのシリアル書込 みアドレスとデータは、SDI制御ライン上で MSB から LSB にシ フト・インされます。ADMV4420 の書込みサイクル用入力ロジ ック・レベルは、3.3V インターフェースをサポートしています。

読出しサイクルでは、R/W ビットと 15 ビットのアドレスが、 SDI 制御ライン上において SCLK の立上がりエッジでシフト・ インします。次に、SDO 制御ライン上において、SCLK の立下 がりエッジで 8 ビットのシリアル読出しデータがシフト・アウ トします (MSB ファースト)。読出しサイクルの出力ロジッ ク・レベルは 3.3V です。SDO の出力ドライバは SCLK の最後の 立上がりエッジ後にイネーブルされ、その読出しサイクルの終 了までアクティブな状態を保ちます。読出し動作中にCSのアサ ートが解除されると、SDO が高インピーダンス状態に戻り、次 の読出しトランザクションまでその状態が保たれます。CSはア クティブ・ローで、書込みまたは読出しシーケンスの終了時に アサートを解除する必要があります。

通信サイクルはCSのアクティブ・ロー入力で開始され、制御さ れます。CSピンにより、同じシリアル通信ライン上の複数のデ バイスが使用可能になります。 $\overline{CS}$ 入力がハイのときは、 $\overline{SDO}$  ピ ンが高インピーダンス状態になります。通信サイクル時は、チ ップ・セレクトはローになっていなければなりません。

SPI 通信プロトコルは、アナログ・デバイセズの SPI 標準に従っ ています。詳細については、ADI-SPI Serial Control Interface Standard (Rev 1.0) を参照してください。

### VCO の自動キャリブレーションと 自動レベル制御

マルチコア VCO は、内部自動キャリブレーション (AUTOCAL) および自動レベル制御 (ALC) ルーチンを使用します。このル ーチンは特定の周波数に合わせて VCO の設定を最適化し、N カ ウンタの整数値下位部分 (INT L) のプログラム後、約 400μs で PLL がロックされるようにします。公称値で使用する場合は、 AUTOCAL と ALC をレジスタ・マップに示すデフォルト値に維 持してください(表8を参照)。

#### プログラミング・シーケンス

いくつかのダブル・バッファ付きレジスタは、N カウンタ整数 値の下位部分(INT L)に書込みを行った後でなければ使用で きません。INT\_L レジスタはこれらのダブル・レジスタに対す るあらゆる変更に適用され、自動キャリブレーション・ルーチ ンを開始します。更に、INT Lレジスタへの書込み後は、SPIク ロック 16 サイクル分の時間を取ることを推奨します。

以下に推奨プログラミング・シーケンスを示します。

- 1. CP CURRENT レジスタ (レジスタ 0x22E) をプログラ

- 2. FRAC H レジスタ (レジスタ 0x204) をプログラム。

- 3. FRAC M レジスタ (レジスタ 0x203) をプログラム。

- 4. FRAC L レジスタ (レジスタ 0x202) をプログラム。

- 5. MOD H レジスタ (レジスタ 0x20A) をプログラム。

- MOD M レジスタ (レジスタ 0x209) をプログラム。 MOD L レジスタ (レジスタ 0x208) をプログラム。 7

- INT H レジスタ (レジスタ 0x201) をプログラム。 8

- INT L レジスタ (レジスタ 0x200) をプログラム。

- 10. 16 SPI クロック・サイクルをプログラム。

6.

# コントロール・レジスタ

表 8. コントロール・レジスタ・マップ

| Register<br>Address | Name                   | Bits  | Bit 7                     | Bit 6         | Bit 5               | Bit 4                         | Bit 3            | Bit 2     | Bit 1         | Bit 0                     | Reset | R/W |

|---------------------|------------------------|-------|---------------------------|---------------|---------------------|-------------------------------|------------------|-----------|---------------|---------------------------|-------|-----|

| 0x000               | ADI_SPI_<br>CONFIG 1   | [7:0] | SOFTRESET_                | LSB_<br>FIRST | ENDIAN_             | SDOACTIVE_                    | SDOACTIVE        | ENDIAN    | LSB_FIRST     | SOFTRESET                 | 0x00  | R/W |

| 0x001               | ADI_SPI_<br>CONFIG 2   | [7:0] | SINGLE_<br>INSTRUCTION    | CSB_<br>STALL | MASTER_<br>SLAVE RB |                               | RESE             | RVED      | N             | MASTER_SLAVE_<br>TRANSFER | 0x00  | R/W |

| 0x003               | CHIPTYPE               | [7:0] |                           |               |                     | •                             | CHIPTYPE         |           |               | •                         | 0x01  | R   |

| 0x004               | PRODUCT_<br>ID L       | [7:0] |                           |               |                     | P                             | RODUCT_ID_L      |           |               |                           | 0x03  | R   |

| 0x005               | PRODUCT_<br>ID H       | [7:0] |                           |               |                     | P                             | RODUCT_ID_H      |           |               |                           | 0x00  | R   |

| 0x00A               | SCRATCHPAD             | [7:0] |                           |               |                     | 5                             | SCRATCHPAD       |           |               |                           | 0x00  | R/W |

| 0x00B               | SPI REV                | [7:0] |                           |               |                     |                               | SPI REV          |           |               |                           | 0x00  | R   |

| 0x103               | ENABLES                | [7:0] | RESERVED                  | EN PLL        | EN LO               | RESERVED                      | EN VCO           | EN IFAMP  | EN MIXER      | EN LNA                    | 0x6F  | R/W |

| 0x108               | SDO LEVEL              | [7:0] |                           |               | RESERVEI            | )                             |                  | SDO LEVEL |               | RESERVED                  | 0x05  | R/W |

| 0x200               | INT L                  | [7:0] |                           |               |                     |                               | INT[7:0]         | _         |               |                           | 0xA7  | R/W |

| 0x201               | INT H                  | [7:0] |                           |               |                     |                               | INT[15:8]        |           |               |                           | 0x00  | R/W |

| 0x202               | FRAC L                 | [7:0] |                           |               |                     |                               | FRAC[7:0]        |           |               |                           | 0x02  | R/W |

| 0x203               | FRAC M                 | [7:0] |                           |               |                     |                               | FRAC[15:8]       |           |               |                           | 0x00  | R/W |

| 0x204               | FRAC H                 | [7:0] |                           |               |                     |                               | FRAC[23:16]      |           |               |                           | 0x00  | R/W |

| 0x208               | MOD L                  | [7:0] |                           |               |                     |                               | MOD[7:0]         |           |               |                           | 0x04  | R/W |

| 0x209               | MOD M                  | [7:0] |                           |               |                     |                               | MOD[15:8]        |           |               |                           | 0x00  | R/W |

| 0x20A               | MOD H                  | [7:0] |                           |               |                     | MOD[23:16]                    |                  |           | 0x00          | R/W                       |       |     |

| 0x20C               | R DIV L                | [7:0] |                           |               |                     |                               | R DIV[7:0]       |           | 0x01          | R/W                       |       |     |

| 0x20D               | R DIV H                | [7:0] |                           |               |                     | RESERVED                      | R DIV[9:8]       |           | 0x00          | R/W                       |       |     |

| 0x20E               | REFERENCE              | [7:0] |                           | RESERVED      |                     |                               | _ ' '            | 0x00      | R/W           |                           |       |     |

| 0x211               | VCO_DATA_<br>READBACK1 | [7:0] |                           |               |                     | VCO_DA                        | ATA_READBACK[7:0 |           |               | -1                        | 0x00  | R   |

| 0x212               | VCO_DATA_<br>READBACK2 | [7:0] |                           |               | RESERVEI            | )                             |                  | 1         | VCO_DATA_READ | BACK[10:8]                | 0x00  | R   |

| 0x213               | PLL_<br>MUX_SEL        | [7:0] |                           |               |                     | F                             | LL_MUX_SEL       | •         |               |                           | 0x01  | R/W |

| 0x214               | LOCK_<br>DETECT        | [7:0] | LD_BI/                    | AS            |                     | LD_COUNT                      |                  |           | RESERVE       | D                         | 0x98  | R/W |

| 0x215               | VCO_BAND_<br>SELECT    | [7:0] |                           |               | •                   | VCC                           | _BAND_SELECT     | •         |               |                           | 0x00  | R/W |

| 0x216               | VCO_ALC_<br>TIMEOUT    | [7:0] |                           | RE            | SERVED              |                               |                  | VCO_      | ALC_TIMEOUT   |                           | 0x00  | R/W |

| 0x217               | VCO_<br>MANUAL         | [7:0] | RESERV                    | ED            | VCO_C               | CORE_SELECT                   |                  | VCO_      | BIAS_ADJUST   |                           | 0x01  | R/W |

| 0x219               | ALC                    | [7:0] |                           | RESERVED      |                     | EN ALC                        |                  | R         | RESERVED      |                           | 0x13  | R/W |

| 0x21C               | VCO_<br>TIMEOUT1       | [7:0] |                           |               |                     | VO                            | O_TIMEOUT[7:0]   |           |               |                           | 0x90  | R/W |

| 0x21D               | VCO_<br>TIMEOUT2       | [7:0] |                           |               | F                   | RESERVED                      |                  |           | VCC           | _TIMEOUT[9:8]             | 0x01  | R/W |

| 0x21E               | VCO_BAND_<br>DIV       | [7:0] |                           | VCO_BAND_DIV  |                     |                               | 0x4B             | R/W       |               |                           |       |     |

| 0x21F               | VCO_<br>READBACK SEL   | [7:0] | RESERVED VCO_READBACK_SEL |               |                     | 0x18                          | R/W              |           |               |                           |       |     |

| 0x226               | AUTOCAL                | [7:0] |                           |               | I                   | RESERVED EN_ RESERVED AUTOCAL |                  |           | 0x02          | R/W                       |       |     |

| 0x22C               | CP STATE               | [7:0] |                           |               | I                   | RESERVED                      |                  |           |               | CP STATE                  | 0x07  | R/W |

| 2x22D               | CP BLEED EN            | [7:0] |                           |               |                     | RESERVED                      |                  |           |               | EN BLEED                  | 0x01  | R/W |

| 0x22E               | CP CURRENT             | [7:0] |                           | RE            | SERVED              |                               |                  | CF        | CURRENT       |                           | 0x03  | R/W |

| 0x22F               | CP BLEED               | [7:0] | 1                         |               |                     |                               | BICP             |           |               |                           | 0x0C  | R/W |

# レジスタの詳細

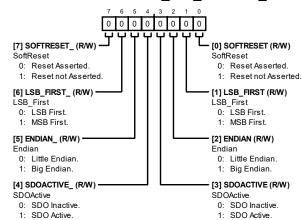

アドレス 0x000、リセット: 0x00、レジスタ名: ADI\_SPI\_CONFIG\_1

#### 表 9. ADI\_SPI\_CONFIG\_1 のビット説明

| ビット | ビット名       | 説明              | リセット | アクセス |

|-----|------------|-----------------|------|------|

| 7   | SOFTRESET_ | ソフト・リセット・ビット    | 0x0  | R/W  |

|     |            | 0:リセットをアサート     |      |      |

|     |            | 1: リセットをアサートしない |      |      |

| 6   | LSB_FIRST_ | LSB ファースト・ビット   | 0x0  | R/W  |

|     |            | 0: LSB ファースト    |      |      |

|     |            | 1: MSB ファースト    |      |      |

| 5   | ENDIAN_    | エンディアン・ビット      | 0x0  | R/W  |

|     |            | 0:リトル・エンディアン    |      |      |

|     |            | 1: ビッグ・エンディアン   |      |      |

| 4   | SDOACTIVE_ | SDO アクティブ・ビット   | 0x0  | R/W  |

|     |            | 0:SDO 非アクティブ    |      |      |

|     |            | 1: SDO アクティブ    |      |      |

| 3   | SDOACTIVE  | SDO アクティブ・ビット   | 0x0  | R/W  |

|     |            | 0:SDO 非アクティブ    |      |      |

|     |            | 1: SDO アクティブ    |      |      |

| 2   | ENDIAN     | エンディアン・ビット      | 0x0  | R/W  |

|     |            | 0:リトル・エンディアン    |      |      |

|     |            | 1: ビッグ・エンディアン   |      |      |

| 1   | LSB_FIRST  | LSBファースト・ビット    | 0x0  | R/W  |

|     |            | 0: LSB ファースト    |      |      |

|     |            | 1: MSB ファースト    |      |      |

| 0   | SOFTRESET  | ソフト・リセット        | 0x0  | R/W  |

|     |            | 0:リセットをアサート     |      |      |

|     |            | 1: リセットをアサートしない |      |      |

Rev. 0 — 41/60 —

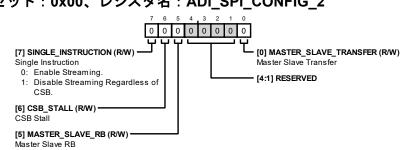

# アドレス 0x001、リセット: 0x00、レジスタ名: ADI\_SPI\_CONFIG\_2

#### 表 10. ADI\_SPI\_CONFIG\_2 のビット説明

| ビット   | ビット名                  | 説明 1                  | リセット | アクセス |

|-------|-----------------------|-----------------------|------|------|

| 7     | SINGLE_INSTRUCTION    | 単一命令ビット               | 0x0  | R/W  |

|       |                       | 0:ストリーミングを有効化         |      |      |

|       |                       | 1:CSBに関わらずストリーミングを無効化 |      |      |

| 6     | CSB_STALL             | CSB停止ビット              | 0x0  | R/W  |

| 5     | MASTER_SLAVE_RB       | マスター・スレーブ・リードバック・ビット  | 0x0  | R/W  |

| [4:1] | RESERVED              | 予備                    | 0x0  | R    |

| 0     | MASTER_SLAVE_TRANSFER | マスター・スレーブ転送ビット        | 0x0  | R/W  |

<sup>&</sup>lt;sup>1</sup> CSは CSB に対応しています。

Rev. 0 — 42/60 —

### アドレス 0x003、リセット: 0x01、レジスタ名: CHIPTYPE

7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 1

[7:0] CHIPTYPE (R) —— Chip Type (Read Only)

表 11. CHIPTYPE のビット説明

| ビット   | ビット名     | 説明                 | リセット | アクセス |

|-------|----------|--------------------|------|------|

| [7:0] | СНІРТҮРЕ | チップ・タイプ・ビット、読出し専用。 | 0x01 | R    |

### アドレス 0x004、リセット: 0x03、レジスタ名: PRODUCT ID L

7 6 5 4 3 2 1 0 0 0 0 0 0 0 1 1

[7:0] PRODUCT\_ID\_L (R) — Product\_ID\_L, Lower 8 Bits

表 12. PRODUCT\_ID\_L のビ<u>ット説明</u>

| ビット   | ビット名         | 説明                        | リセット | アクセス |

|-------|--------------|---------------------------|------|------|

| [7:0] | PRODUCT_ID_L | PRODUCT_ID_L ビット、下位 8 ビット | 0x03 | R    |

### アドレス 0x005、リセット: 0x00、レジスタ名: PRODUCT\_ID\_H

7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0

[7:0] PRODUCT\_ID\_H (R) — Product\_ID\_H, Higher 8 Bits

表 13. PRODUCT\_ID\_H のビット説明

| ビット   | ビット名         | 説明                        | リセット | アクセス |

|-------|--------------|---------------------------|------|------|

| [7:0] | PRODUCT_ID_H | PRODUCT_ID_H ビット、上位 8 ビット | 0x00 | R    |

### アドレス 0x00A、リセット: 0x00、レジスタ名: SCRATCHPAD

7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0

[7:0] SCRATCHPAD (R/W) ScratchPad

表 14. SCRATCHPAD のビット説明

| ビット   | ビット名       | 説明            | リセット | アクセス |

|-------|------------|---------------|------|------|

| [7:0] | SCRATCHPAD | スクラッチ・パッド・ビット | 0x00 | R/W  |

#### アドレス 0x00B、リセット:0x00、レジスタ名:SPI\_REV

7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0

[7:0] SPI\_REV (R)

SPI Register Map Revision

表 15. SPI\_REV のビット説明

| ビット   | ビット名    | 説明                     | リセット | アクセス |

|-------|---------|------------------------|------|------|

| [7:0] | SPI_REV | SPI レジスタ・マップ・リビジョン・ビット | 0x00 | R    |

Rev. 0 — 43/60 —

### アドレス 0x103、リセット: 0x6F、レジスタ名: ENABLES

#### 表 16. ENABLES のビット説明

| ビット | ビット名     | 説明               | リセット | アクセス |

|-----|----------|------------------|------|------|

| 7   | RESERVED | 予備               | 0x0  | R    |

| 6   | EN_PLL   | PLLイネーブル・ビット     | 0x1  | R/W  |

|     |          | 0: PLL をパワーダウン   |      |      |

|     |          | 1:PLLをパワーアップ     |      |      |

| 5   | EN_LO    | LOイネーブル・ビット      | 0x1  | R/W  |

|     |          | 0: LO をパワーダウン    |      |      |

|     |          | 1:LOをパワーアップ      |      |      |

| 4   | RESERVED | 予備               | 0x0  | R    |

| 3   | EN_VCO   | VCOイネーブル・ビット     | 0x1  | R/W  |

|     |          | 0: VCO をパワーダウン   |      |      |

|     |          | 1: VCO をパワーアップ   |      |      |

| 2   | EN_IFAMP | IF アンプ・イネーブル・ビット | 0x1  | R/W  |

|     |          | 0: IF アンプをパワーダウン |      |      |

|     |          | 1: IF アンプをパワーアップ |      |      |

| 1   | EN_MIXER | ミキサー・イネーブル・ビット   | 0x1  | R/W  |

|     |          | 0:ミキサーをパワーダウン    |      |      |

|     |          | 1:ミキサーをパワーアップ    |      |      |

| 0   | EN_LNA   | LNAイネーブル・ビット     | 0x1  | R/W  |

|     |          | 0: LNA をパワーダウン   |      |      |

|     |          | 1:LNAをパワーアップ     |      |      |

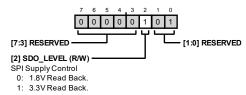

### アドレス 0x108、リセット: 0x05、レジスタ名: SDO\_LEVEL

#### 表 17. SDO LEVEL のビット説明

| ビット   | ビット名      | 説明            | リセット | アクセス |

|-------|-----------|---------------|------|------|

| [7:3] | RESERVED  | 予備            | 0x0  | R    |

| 2     | SDO_LEVEL | SPI 電源制御ビット   | 0x1  | R/W  |

|       |           | 0:1.8V リードバック |      |      |

|       |           | 1:3.3V リードバック |      |      |

| [1:0] | RESERVED  | 予備            | 0x1  | R/W  |

Rev. 0 — 44/60 —

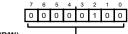

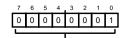

### アドレス 0x200、リセット:0xA7、レジスタ名:INT\_L

7 6 5 4 3 2 1 0 1 0 1 0 0 1 1 1 [7:0] INT[7:0] (RW)

表 18. INT\_L のビット説明

| ビット   | ビット名     | 説明                 | リセット | アクセス |

|-------|----------|--------------------|------|------|

| [7:0] | INT[7:0] | インテジャーNワード (16ビット) | 0xA7 | R/W  |

### アドレス 0x201、リセット: 0x00、レジスタ名: INT\_H

7 6 5 4 3 2 1 0

[7:0] INT[15:8] (R/W) — Integer-N Word (16-Bit)

Integer-N Word (16-Bit)

表 19. INT H のビット説明

| ビット   | ビット名      | 説明                  | リセット | アクセス |

|-------|-----------|---------------------|------|------|

| [7:0] | INT[15:8] | インテジャーNワード (16 ビット) | 0x0  | R/W  |

### アドレス 0x202、リセット: 0x02、レジスタ名: FRAC\_L

7 6 5 4 3 2 1 0 0 0 0 0 0 0 1 0

[7:0] FRAC[7:0] (R/W) —— Fractional-N Word (24-Bit)

<u>表 20. FRAC\_L の</u>ビット説明

| ビット   | ビット名      | 説明                   | リセット | アクセス |

|-------|-----------|----------------------|------|------|

| [7:0] | FRAC[7:0] | フラクショナル N ワード (24 ビッ | 0x2  | R/W  |

|       |           | F)                   |      |      |

### アドレス 0x203、リセット: 0x00、レジスタ名: FRAC\_M

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

[7:0] FRAC[15:8] (R/W) — Fractional-N Word (24-Bit)

表 21. FRAC\_M のビット説明

| ビット   | ビット名       | 説明                  | リセット   | アクセス |

|-------|------------|---------------------|--------|------|

| [7:0] | FRAC[15:8] | フラクショナル N ワード (24 ビ | `ッ 0x0 | R/W  |

|       |            | <b>         </b>    |        |      |

### アドレス 0x204、リセット: 0x00、レジスタ名: FRAC\_H

0 0 0 0 0 0 0 0

[7:0] FRAC[23:16] (R/W) — Fractional-N Word (24-Bit)

表 22. FRAC\_H のビット説明

| ビット   | ビット名        | 説明                     | リセット | アクセス |

|-------|-------------|------------------------|------|------|

| [7:0] | FRAC[23:16] | フラクショナル N ワード (24 ビット) | 0x0  | R/W  |

Rev. 0 — 45/60 —

### アドレス 0x208、リセット:0x04、レジスタ名:MOD\_L

[7:0] MOD[7:0] (R/W) Fractional-N Modulus (24-Bit)

表 23. MOD\_L のビット説明

| ビット   | ビット名     | 説明                   | リセット | アクセス |

|-------|----------|----------------------|------|------|

| [7:0] | MOD[7:0] | フラクショナル N モジュラス(24 ビ | 0x4  | R/W  |

|       |          | ット)                  |      |      |

### アドレス 0x209、リセット: 0x00、レジスタ名: MOD\_M

0 0 0 0 0 0 0 0

[7:0] MOD[15:8] (R/W)

Fractional-N Modulus (24-Bit)

表 24. MOD\_M のビット説明

| ビット   | ビット名      | 説明                      | リセット | アクセス |

|-------|-----------|-------------------------|------|------|

| [7:0] | MOD[15:8] | フラクショナル N モジュラス(24 ビット) | 0x0  | R/W  |

### アドレス 0x20A、リセット: 0x00、レジスタ名: MOD\_H

0 0 0 0 0 0 0 0

[7:0] MOD[23:16] (R/W) — Fractional-N Modulus (24-Bit)

表 25. MOD Hのビット説明

| ビット   | ビット名       | 説明                      | リセット | アクセス |

|-------|------------|-------------------------|------|------|

| [7:0] | MOD[23:16] | フラクショナル N モジュラス(24 ビット) | 0x0  | R/W  |

- 46/60 -Rev. 0

### アドレス 0x20C、リセット:0x01、レジスタ名:R\_DIV\_L

#### 表 26. R\_DIV\_L のビット説明

| ビット   | ビット名       | 説明                | リセット | アクセス |

|-------|------------|-------------------|------|------|

| [7:0] | R_DIV[7:0] | R 分周器ワード (10 ビット) | 0x1  | R/W  |

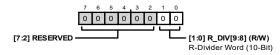

### アドレス 0x20D、リセット: 0x00、レジスタ名: R\_DIV\_H

#### 表 27. R DIV H のビット説明

| ビット   | ビット名       | 説明                | リセット | アクセス |

|-------|------------|-------------------|------|------|

| [7:2] | RESERVED   | 予備                | 0x0  | R    |

| [1:0] | R_DIV[9:8] | R 分周器ワード (10 ビット) | 0x0  | R/W  |

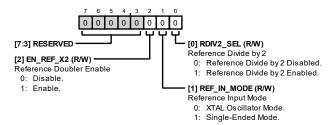

### アドレス 0x20E、リセット: 0x00、レジスタ名: REFERENCE

### 表 28. REFERENCE のビット説明

| ビット   | ビット名        | 説明                  | リセット | アクセス |

|-------|-------------|---------------------|------|------|

| [7:3] | RESERVED    | 予備                  | 0x0  | R    |

| 2     | EN_REF_X2   | リファレンス2逓倍器イネーブル・ビット | 0x0  | R/W  |

|       |             | 0:ディスエーブル           |      |      |

|       |             | 1:イネーブル             |      |      |

| 1     | REF_IN_MODE | リファレンス入力モード・ビット     | 0x0  | R/W  |

|       |             | 0:水晶発振器(XTAL)モード    |      |      |

|       |             | 1:シングルエンド・モード       |      |      |

| 0     | RDIV2_SEL   | リファレンス2分周ビット        | 0x0  | R/W  |

|       |             | 0:リファレンス2分周を無効化     |      |      |

|       |             | 1:リファレンス2分周を有効化     |      |      |

Rev. 0 — 47/60 —

### アドレス 0x211、リセット: 0x00、レジスタ名: VCO\_DATA\_READBACK1

7 6 5 4 3 2 1 0

[7:0] VCO\_DATA\_READBACK[7:0] (R) VCO Data Readback

表 29. VCO\_DATA\_READBACK1 のビット説明

|   | ビット   | ビット名                   | 説明            | リセット | アクセス |

|---|-------|------------------------|---------------|------|------|

| _ | [7:0] | VCO_DATA_READBACK[7:0] | VCOデータ・リードバック | 0x0  | R    |

### アドレス 0x212、リセット: 0x00、レジスタ名: VCO\_DATA\_READBACK2

[7:3] RESERVED [2:0] VCO\_DATA\_READBACK[10:8] (R) VCO Data Readback

#### 表 30.VCO\_DATA\_READBACK2 のビット説明

| ビット   | ビット名                    | 説明                | リセット | アクセス |

|-------|-------------------------|-------------------|------|------|

| [7:3] | RESERVED                | 予備                | 0x0  | R    |

| [2:0] | VCO_DATA_READBACK[10:8] | VCOデータ・リードバック・ビット | 0x0  | R    |

Rev. 0 — 48/60 —

### アドレス 0x213、リセット:0x01、レジスタ名:PLL\_MUX\_SEL

[7:0] PLL\_MUX\_SEL (R/W)

PLL Mux Select

00000000: Output Logic Low. 00000001: Digital Lock Detect. 00000100: RDiv-by-2 to Mux Out, Frequency =

REFIN/(2 x R)

00000101: NDiv-by-2 to Mux Out, Frequency =

VCO/(2 x N)

00001000: Output Logic High.

#### 表 31. PLL\_MUX\_SEL のビット説明

| ビット   | ビット名        | 説明                                             | リセット | アクセス |

|-------|-------------|------------------------------------------------|------|------|

| [7:0] | PLL_MUX_SEL | PLLマルチプレクサ選択ビット                                | 0x1  | R/W  |

|       |             | 00000000 : 出力ロジック・ロー                           |      |      |

|       |             | 00000001:デジタル・ロック検出                            |      |      |

|       |             | 00000100: R2 分周をマルチプレクサ出力へ、周波数 = REFIN/(2 × R) |      |      |

|       |             | 00000101: N2 分周をマルチプレクサ出力へ、周波数 = VCO/(2 × N)   |      |      |

|       |             | 00001000: 出力ロジック・ハイ                            |      |      |

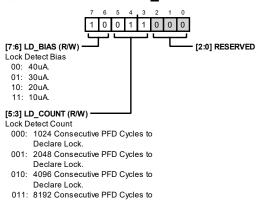

### アドレス 0x214、リセット: 0x98、レジスタ名: LOCK\_DETECT

Declare Lock.

### 表 32. LOCK DETECT のビット説明

| ビット   | ビット名     | 説明                          | リセット | アクセス |

|-------|----------|-----------------------------|------|------|

| [7:6] | LD_BIAS  | ロック検出バイアス・ビット               | 0x2  | R/W  |

|       |          | 00 : 40μA                   |      |      |

|       |          | 01 : 30μΑ                   |      |      |

|       |          | 10 : 20μΑ                   |      |      |

|       |          | 11 : 10μA                   |      |      |

| [5:3] | LD_COUNT | ロック検出カウント・ビット               | 0x3  | R/W  |

|       |          | 000:1024連続 PFD サイクルでロックを宣言  |      |      |

|       |          | 001:2048 連続 PFD サイクルでロックを宣言 |      |      |

|       |          | 010:4096 連続 PFD サイクルでロックを宣言 |      |      |

|       |          | 011:8192連続 PFD サイクルでロックを宣言  |      |      |

| [2:0] | RESERVED | 予備                          | 0x0  | R/W  |

-49/60 -Rev. 0

### アドレス 0x215、リセット: 0x00、レジスタ名: VCO\_BAND\_SELECT

#### 表 33. VCO\_BAND\_SELECT のビット説明

| ビット   | ビット名            | 説明                | リセット | アクセス |

|-------|-----------------|-------------------|------|------|

| [7:0] | VCO_BAND_SELECT | 手動でプログラムした VCO 帯域 | 0x0  | R/W  |

### アドレス 0x216、リセット:0x00、レジスタ名:VCO\_ALC\_TIMEOUT

#### 表 34. VCO ALC TIMEOUT のビット説明

| ビット   | ビット名            | 説明               | リセット | アクセス |

|-------|-----------------|------------------|------|------|

| [7:4] | RESERVED        | 予備               | 0x0  | R    |

| [3:0] | VCO_ALC_TIMEOUT | VCO ALC タイムアウト分周 | 0x0  | R/W  |

### アドレス 0x217、リセット: 0x01、レジスタ名: VCO\_MANUAL

#### 表 35. VCO MANUAL のビット説明

| ビット   | ビット名            | 説明            | リセット | アクセス |

|-------|-----------------|---------------|------|------|

| [7:6] | RESERVED        | 予備            | 0x0  | R    |

| [5:4] | VCO_CORE_SELECT | VCO コアの手動制御   | 0x0  | R/W  |

|       |                 | 01:コア1        |      |      |

|       |                 | 10:コア2        |      |      |

| [3:0] | VCO_BIAS_ADJUST | VCO バイアスの手動制御 | 0x1  | R/W  |

#### アドレス 0x219、リセット: 0x13、レジスタ名: ALC

#### 表 36. ALC のビット説明

| ビット   | ビット名     | 説明                | リセット | アクセス |

|-------|----------|-------------------|------|------|

| [7:5] | RESERVED | 予備                | 0x0  | R    |

| 4     | EN_ACL   | VCO ALC イネーブル・ビット | 0x1  | R/W  |

|       |          | 0:無効化             |      |      |

|       |          | 1:有効化             |      |      |

| [3:0] | RESERVED | 予備                | 0x3  | R/W  |

Rev. 0 - 50/60 -

### アドレス 0x21C、リセット: 0x90、レジスタ名: VCO\_TIMEOUT1

#### 表 37. VCO\_TIMEOUT1 のビット説明

| ビット   | ビット名             | 説明                       | リセット | アクセス |

|-------|------------------|--------------------------|------|------|

| [7:0] | VCO_TIMEOUT[7:0] | メイン VCO キャリブレーション・タイムアウト | 0x90 | R/W  |

### アドレス 0x21D、リセット: 0x01、レジスタ名: VCO\_TIMEOUT2

#### 表 38. VCO TIMEOUT2 のビット説明

| ビット   | ビット名             | 説明                       | リセット | アクセス |

|-------|------------------|--------------------------|------|------|

| [7:2] | RESERVED         | 予備                       | 0x0  | R    |

| [1:0] | VCO_TIMEOUT[9:8] | メイン VCO キャリブレーション・タイムアウト | 0x1  | R/W  |

### アドレス 0x21E、リセット: 0x4B、レジスタ名: VCO\_BAND\_DIV

#### 表 39. VCO\_BAND\_DIV のビット説明

| ビット   | ビット名         | 説明        | リセット | アクセス |

|-------|--------------|-----------|------|------|

| [7:0] | VCO_BAND_DIV | VCO帯域選択分周 | 0x4B | R/W  |

### アドレス 0x21F、リセット: 0x18、レジスタ名: VCO\_READBACK\_SEL

### 表 40. VCO READBACK SELのビット説明

| ビット   | ビット名             | 説明                           | リセット | アクセス |

|-------|------------------|------------------------------|------|------|

| [7:3] | RESERVED         | 予備                           | 0x3  | R    |

| [2:0] | VCO_READBACK_SEL | VCO リードバック選択                 | 0x0  | R/W  |

|       |                  | 000:リードバック・チェッカー・ボード (機能テスト) |      |      |

|       |                  | 001:リードバック・コアと帯域             |      |      |

|       |                  | 011: リードバック・バイアス・コード         |      |      |

|       |                  | 100: リードバック・コア               |      |      |

|       |                  | 101: リードバック・ロー (ゼロ)          |      |      |

Rev. 0 — 51/60 —

### アドレス 0x226、リセット: 0x02、レジスタ名: AUTOCAL

|                  | 7    | 6    | 5    | 4    | 3   | 2 | 1 | 0 |                |

|------------------|------|------|------|------|-----|---|---|---|----------------|

|                  | 0    | 0    | 0    | 0    | 0   | 0 | 1 | 0 |                |

|                  | ᆫ    |      |      | =    |     |   | 꾸 | 귝 |                |

| [7:2] RESERVED - |      |      |      | ı    |     |   |   | L | - [0] RESERVED |

| [1] EN_AUTOCAL   | (R/\ | N) - |      |      |     |   | J |   |                |

| Enable VCO Auto  | Ċal  | and  | d Lo | ck F | PLL |   |   |   |                |

0: Disable. 1: Enable.

#### 表 41. AUTOCAL のビット説明

| ビット   | ビット名       | 説明                                               | リセット | アクセス |

|-------|------------|--------------------------------------------------|------|------|

| [7:2] | RESERVED   | 予備                                               | 0x0  | R    |

| 1     | EN_AUTOCAL | VCO 自動キャリブレーションを有効にして PLL をロック<br>0:無効化<br>1:有効化 | 0x1  | R/W  |

| 0     | RESERVED   | 予備                                               | 0x0  | R    |

Rev. 0 - 52/60 -

### アドレス 0x22C、リセット: 0x07、レジスタ名: CP\_STATE

3: Normal Operation.

#### 表 42. CP\_STATE のビット説明

| ビット   | ビット名     | 説明                  | リセット | アクセス |

|-------|----------|---------------------|------|------|

| [7:2] | RESERVED | 予備                  | 0x1  | R    |

| [1:0] | CP_STATE | チャージ・ポンプ・ステート       | 0x3  | R/W  |

|       |          | 0:トライステート(高インピーダンス) |      |      |

|       |          | 1:強制アップ             |      |      |

|       |          | 2:強制ダウン             |      |      |

|       |          | 3:通常動作              |      |      |

### アドレス 0x22D、リセット: 0x01、レジスタ名: CP\_BLEED\_EN

#### 表 43. CP\_BLEED\_EN のビット説明

| ビット   | ビット名     | 説明               | リセット | アクセス |

|-------|----------|------------------|------|------|

| [7:1] | RESERVED | 予備               | 0x0  | R    |

| 0     | EN_BLEED | ブリード CP 電流のイネーブル | 0x1  | R/W  |

|       |          | 0:ディスエーブル        |      |      |

|       |          | 1:イネーブル          |      |      |

### アドレス 0x22E、リセット: 0x03、レジスタ名: CP\_CURRENT

### 表 44. CP\_CURRENT のビット説明

| ビット   | ビット名       | 説明                | リセット | アクセス |

|-------|------------|-------------------|------|------|

| [7:4] | RESERVED   | 予備                | 0x0  | R    |

| [3:0] | CP_CURRENT | メイン・チャージ・ポンプ電流ビット | 0x3  | R/W  |

### アドレス 0x22F、リセット: 0x0C、レジスタ名: CP\_BLEED

#### 表 45. CP BLEED のビット説明

| ビット   | ビット名 | 説明               | リセット | アクセス |

|-------|------|------------------|------|------|

| [7:0] | BICP | バイナリ・スケールのブリード電流 | 0xC  | R/W  |

Rev. 0 - 53/60 -

## アプリケーション情報

#### 評価用ボード

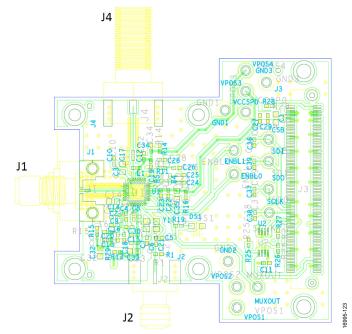

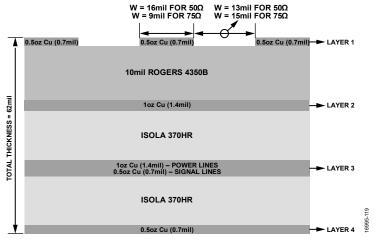

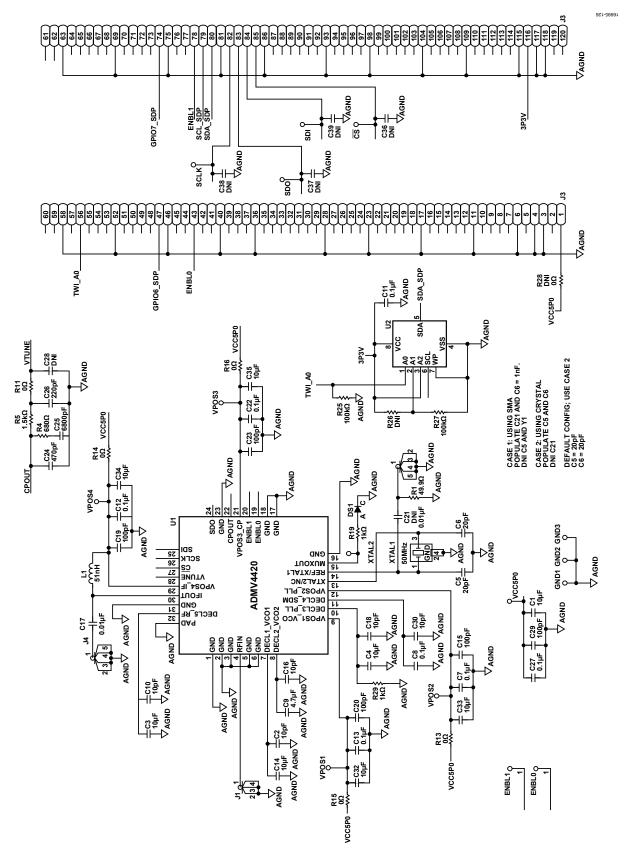

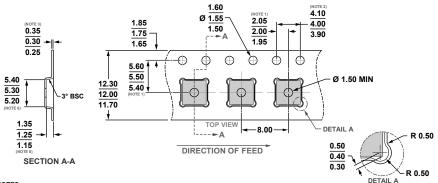

ADMV4420 の性能評価には、ADMV4420-EVALZ 評価用ボードを使用できます。図 126 と図 127 に ADMV4420-EVALZ 評価用ボードの使用できます。図 126 と図 127 に ADMV4420-EVALZ 評価用ボードの上面レイアウト図と断面レイアウト図を示します。RF 伝送ラインはコプレーナ導波路(CPWG)モデルを使って設計されており、ライン幅(W)は 16 ミル、グラウンドとのスペースは 13 ミルで、これに対する RF 入力(RFIN)と外部リファレンス入力(REF/XTAL1)の特性インピーダンスは  $50\Omega$  です。また、IF 出力(IFOUT)のライン幅は 9 ミル、グラウンドとのスペースは 15 ミルです。 PCB は、低損失を実現する Rogers 4350B 誘電体材料と、PCB を希望の厚さに抑えることのできる isola 370HR 誘電体材料から作られています。

ADMV4420-EVALZ評価用ボードは 4 層構成です。第 1 層には、チャージ・ポンプ、IF 電源(VPOS3\_CP と VPOS4\_IF)、マルチプレクサ出力信号(MUXOUT)トレースが収められており、これらは配置された周辺部品と一緒にルーティングされています。第 2 層はボード用グランド・プレーンを確保できるように配置されています。第 3 層には VCO(VPOS1\_VCO)電源、PLL(VPOS2\_PLL)電源、およびデジタル SPI 制御信号( $\overline{\text{CS}}$ 、SDI、SDO、および SCLK)トレースが、第 4 層のボード底面側にはチップ・イネーブル・トレース(ENBLO と ENBLI)が収められています。評価用ボード上では $\overline{\text{CS}}$ が CSB として表示されています。図 128~図 130 に第 2 層と第 4 層のルーティング詳細を示します。最適な RF 接地および熱接地を行うために、伝送ライン周囲、パッケージの露出パッド下、および PCB 全体に、できるだけ多くのメッキ貫通ビアを配置してください(図 128 参照)。

図 126. ADMV4420-EVALZ 評価用ボードのレイアウト、上面図(第 1 層)

Rev. 0 - 54/60 -

図 127. ADMV4420-EVALZ PCB、断面図

図 128. ADMV4420-EVALZ 評価用ボード、第 2 層

図 129. ADMV4420-EVALZ 評価用ボード、第 3 層

Rev. 0 - 55/60 -

図 130. ADMV4420-EVALZ 評価用ボード、第 4 層(下面側)

ADMV4420-EVALZ 評価用ボードと部品配置を図 126 に示します。ノイズの影響を最小限に抑えるために、LDO デカップリング・ピンと電源トレースにはデカップリング・コンデンサを取り付けます。評価用ボードの回路図を図 132 に、その鉛フリー・リフロー・プロファイルを図 2 に示します。

評価用ボードのパワーアップには 2 つのオプションがあります。 1 つめのオプションは、VCO、PLL、CP、および IF ブロック用の VPOS1、VPOS2、VPOS3、VPOS4 テスト・ポイント (VPOS1\_VCO ピン、VPOS2\_PLL ピン、VPOS3\_CP ピン、および VPOS4\_IF ピン) に 5V 電源を加え、GND1、GND2、または GND3 グラウンド・テスト・ピンのいずれか 1 つに 0V 電源を接続する方法です。このオプションでは、評価用ボードから抵抗 R13、R14、R15、および R16 を取り外してください。このオプションでは、各ブロックの電流を個別にモニタすることができます。

2 つめのオプションでボードをパワーアップするには、適切なグラウンド接続を行い、VCC5P0 テスト・ポイントを通じて電源を加える必要があります。このオプションでモニタできる電流は、ADMV4420 の合計電流だけです。評価用ボードのパワーアップ後は、分析、制御、評価用(ACE)ソフトウェアを使用することにより、SDP-S コントローラ・ボードを通じてターゲット構成に必要なデジタル設定をプログラムします。このソフトウェアは、分析、制御、評価用(ACE)製品ページからダウンロードできます。詳細については ADMV4420-EVALZ のユーザー・ガイドを参照してください。

図 132 に示すように、ADMV4420 に外部リファレンス入力を加えるにあたっては、2 つの異なるオプションがあります。これらのオプションに必要な設定を表 46 に示します。ケース 1 (Case 1) オプション使用時は、信号発生器を使い、J2 コネクタを通じて外部リファレンス入力を加えます。ケース 2 (Case 2) オプション使用時は、水晶発振器 (Y1) によって外部リファレンス入力を加えます。

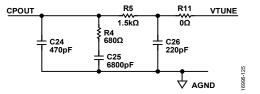

ループ・フィルタ回路は、ターゲットLO周波数を得るために、ADMV4420のチャージ・ポンプ出力ピン(CPOUT)からの CP電流出力を加えることによって VCO 制御電圧(VTUNE)を生成します。図 131 は推奨回路図で、表 47 は位相検出器周波数が50MHz のときのループ・フィルタ部品を示したものです。また、ループ・フィルタ部品を含むすべての材料のリストを表 48 に示します。評価用ボードの詳細については、ADMV4420-EVALZのユーザー・ガイドを参照してください。

表 46. 外部リファレンス入力の構成

| オプション            | 部品構成                                            |

|------------------|-------------------------------------------------|

| Case 1           | C21を取り付け。C6を InF のコンデンサに交                       |