# ANALOG 高度なパワー・マネジメントを内蔵した DEVICES チップ・スケールPAL/NTSCビデオ・エンコーダ

### ADV7174/ADV7179

#### 特長

ITU-R<sup>1</sup> BT601/BT656 YCrCbからPAL/NTSCへのビデオ・エ

高品質10ビット・ビデオDAC

SSAF™ (スーパー・サブ・エイリアス・フィルタ)

高度なパワー・マネジメント機能

CGMS (コピー・ジェネレーション・マネジメント・システム)

WSS (ワイド・スクリーン・シグナリング)

NTSC M, PAL N2, PAL B/D/G/H/I, PAL 60

27MHzクロック一個を使用(×2のオーバーサンプリング)

Macrovision 7.1 (ADV7174のみ)

80dBのビデオSNR

カラー・サブキャリア用の32ビット・ダイレクト・デジタル・シ ンセサイザ

マルチスタンダード・ビデオ出力をサポート:

コンポジット(CVBS)

コンポーネントSビデオ(Y/C)

ビデオ入力データ・ポートをサポート:

CCIR-656 4:2:2、8ビット・パラレル入力フォーマット

コンポジットおよびSビデオ同時出力または

RGB (SCART)/YUVビデオ出力が設定可能

プログラマブルな輝度信号フィルタ(ローパス[PAL/NTSC])

ノッチ、拡張SSAF、CIF、QCIF

プログラマブルな色度信号フィルタ(ローパス[0.65MHz、

1.0MHz、1.2MHz、2.0MHz]、CIF、QCIF)

プログラマブルなVBI (垂直ブランキング・インターバル) サブキャリアの周波数とフェーズがプログラマブル

輝度信号遅延がプログラマブル

各DACは個別にON/OFF制御が可能

CCIRおよびスクエア・ピクセル動作

外部ビデオ・ソースへのサブキャリア・ロック機能を内蔵

カラー信号制御/バースト信号制御

インターレース/ノン・インターレース動作

完全なビデオ・タイミング・ジェネレータを内蔵

プログラマブルなマルチモード・マスター/スレーブ動作

クローズド・キャプショニングをサポート

Teletext挿入ポート(PAL-WST)を装備

カラー・バー・ジェネレータを内蔵

電圧リファレンスを内蔵

2線式シリアルMPUインターフェース(I2C®互換および

Fast I2C)

単電源3.3V動作

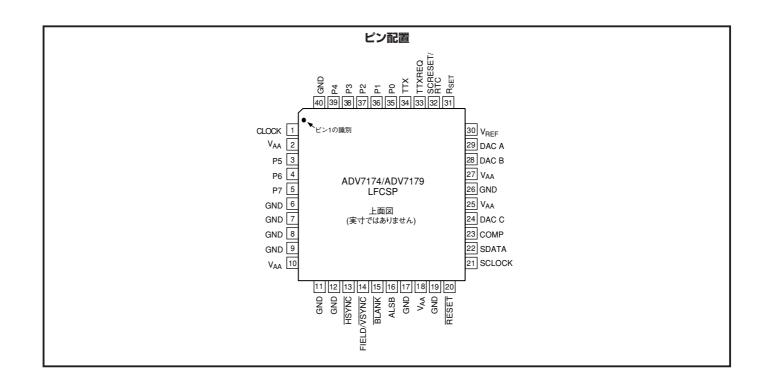

小型40ピン6mm×6mm LFCSPパッケージ

-40°C ~ +85°C

#### アプリケーション

携帯型ビデオ・アプリケーション

G3移動電話

デジタルカメラ

1 本書ではITU-RとCCIRを同じ意味で使っています(CCIR勧告はITU-Rで置換えられています)。

本書では、NはPAL-Combination-Nを意味しています。米国特許番号5,343,196、5,442,355およびその他の知的財産権により保護されています。米国特許番号4,631,603、4,577,216、4,819,098および その他の知的財産権により保護されています。Macrovision複製防止プロセスは非商用の家庭用だけにライセンスされており、デバイス内での使用のみに限定されています。最新のMacrovisionバージ ョンについては営業部門におたずねください。

SSAFはAnalog Devices, Inc.の商標です。

I<sup>2</sup>CはPhilips Semiconductorの登録商標です。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利 用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。 さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものでもありません。

\*日本語データシートは、REVISIONが古い場合があります。最新の内容については英語版をご参照ください。

REV.0

社/東京都港区海岸1-16-1 電話03(5402)8200 **〒105-6891** ニューピア竹芝サウスタワービル

大阪営業所/大阪府大阪市淀川区宮原3-5-36 電話06(6350)6868(代) 〒532-0003 新大阪MTビル2号

# ADV7174/ADV7179—仕様

**3.3V仕様**  $(V_{AA}=3.0V\sim3.6V^1, V_{REF}=1.235V, R_{SET}=150\,\Omega$ 。特に指定のない限り、すべての仕様は $T_{MIN}\sim T_{MAX}^2)$

| パラメータ                                          | 条件1                                                    | Min | Тур       | Max     | 単位        |

|------------------------------------------------|--------------------------------------------------------|-----|-----------|---------|-----------|

| スタティック性能 <sup>3</sup><br>分解能(各DAC)<br>精度(各DAC) |                                                        |     |           | 10      | ビット       |

| 積分非直線性                                         | $R_{\text{SET}}=300\Omega$                             |     | $\pm 0.6$ |         | LSB       |

| 微分非直線性                                         | 単調性を保証                                                 |     |           | $\pm 1$ | LSB       |

| デジタル入力 <sup>3</sup>                            |                                                        |     |           |         |           |

| 入力ハイレベル電圧、 $V_{	ext{INH}}$                     |                                                        | 2   |           |         | V         |

| 入力ローレベル電圧、 $V_{	ext{INL}}$                     |                                                        |     |           | 0.8     | V         |

| 入力電流、 $I_{IN}^{3,4}$                           | $V_{IN}$ =0.4Vまたは2.4V                                  |     |           | $\pm 1$ | $\mu$ A   |

| 入力容量、C <sub>IN</sub>                           |                                                        |     | 10        |         | pF        |

| デジタル出力3                                        |                                                        |     |           |         |           |

| 出力ハイレベル電圧、VoH                                  | $I_{\text{SOURCE}} = 400 \mu \text{ A}$                | 2.4 |           |         | V         |

| 出力ローレベル電圧、VoL                                  | $I_{SINK}=3.2mA$                                       |     |           | 0.4     | V         |

| スリーステート・リーク電流                                  |                                                        |     | 10        | 10      | μΑ        |

| スリーステート出力容量                                    |                                                        |     | 10        |         | pF        |

| アナログ出力3                                        |                                                        |     |           |         |           |

| 出力電流4.5                                        | $R_{SET}=150\Omega$ , $RL=37.5\Omega$                  | 33  | 34.7      | 37      | mA        |

| 出力電流6                                          | $R_{\text{SET}}=1041\Omega$ , $RL=262.5\Omega$         |     | 5         |         | mA        |

| DAC間のマッチング<br>出力適合性、V <sub>oc</sub>            |                                                        | 0   | 2.0       | 1.4     | %<br>V    |

| 出力過行性、Voc<br>出力インピーダンス、Rout                    |                                                        | 0   | 30        | 1.4     | $k\Omega$ |

| 出力容量、Cour                                      | I <sub>OUT</sub> =0mA                                  |     | 30        | 30      | pF        |

|                                                | 10017—0111A                                            |     |           |         | pr        |

| 電源条件 <sup>3、7</sup><br>V <sub>AA</sub>         |                                                        | 3.0 | 3.3       | 3.6     | V         |

| ノーマル消費電力モード                                    |                                                        | 3.0 | 3.3       | 3.0     | '         |

| I <sub>DAC</sub> (Max) <sup>8</sup>            | $R_{\text{SET}}=150\Omega$ , $R_{\text{L}}=37.5\Omega$ |     | 150       | 155     | mA        |

| I <sub>DAC</sub> (Min) <sup>8</sup>            | $R_{SET} = 1041 \Omega$ , $R_{L} = 262.5 \Omega$       |     | 20        |         | mA        |

| ${ m I_{CCT}}^9$                               |                                                        |     | 35        |         | mA        |

| 低消費電力モード                                       |                                                        |     |           |         |           |

| I <sub>DAC</sub> (Max) <sup>8</sup>            |                                                        |     | 80        |         | mA        |

| I <sub>DAC</sub> (Min) <sup>8</sup>            |                                                        |     | 20        |         | mA        |

| $I_{\rm CCT}$ $^9$                             |                                                        |     | 35        |         | mA        |

| スリープモード                                        |                                                        |     |           |         |           |

| $ m I_{DAC}^{10}$                              |                                                        |     | 0.1       |         | $\mu$ A   |

| I <sub>CCT</sub> 11                            |                                                        |     | 0.001     |         | μΑ        |

| 電源変動除去比                                        | COMP=0.1 μ F                                           |     | 0.01      | 0.5     | %/%       |

- 1 max/min仕様はこのレンジで保証。max/minは、3.0V~3.6Vでの代表的な値。

- 2 温度レンジT<sub>MIN</sub> ~T<sub>MAX</sub>は-40℃~+85℃。

- 3 キャラクタライゼーションにより保証。

- 4 37.5Ω負荷をフル駆動。

- 5 DACは3.3Vで35mA (yp)を出力することができます( $R_{SET}$ =150 $\Omega$ かつRL=37.5 $\Omega$ )。 最適性能はDAC電流18mAで得られます( $R_{SET}$ =300 $\Omega$ かつRL=75 $\Omega$ )。

- 6 最小駆動電流(バッファ付き/スケーラ付き出力負荷を使用)。

- 7 消費電力は、クロック周波数=27MHz、Max T<sub>J</sub>=110℃で測定。

- 8 l<sub>DAC</sub>は偏すべてのDACを駆動したときの合計電流(minはl<sub>DAC</sub>当たり5mA出力に、maxは1DAC当たり37mA出力に、それぞれ対応)。DACを個別にターンオフすると、それに対応してIDACが減ります。

2

- 9 Iccr (回路電流)は、デバイスを駆動するために必要な連続電流。

- 10 スリープモードでの合計DAC電流。 11 スリープモードでの合計連続電流。

仕様は予告なく変更されることがあります。

3.3Vタイミング仕様(V<sub>AA</sub>=3.0V~3.6V<sup>1</sup>、V<sub>REF</sub>=1.235V、R<sub>SET</sub>=150Ω。特に指定のない限り、すべての仕様はT<sub>MIN</sub>~T<sub>MAX</sub><sup>2</sup>)

| パラメータ                              | 条件1                 | Min | Тур | Max | 単位        |

|------------------------------------|---------------------|-----|-----|-----|-----------|

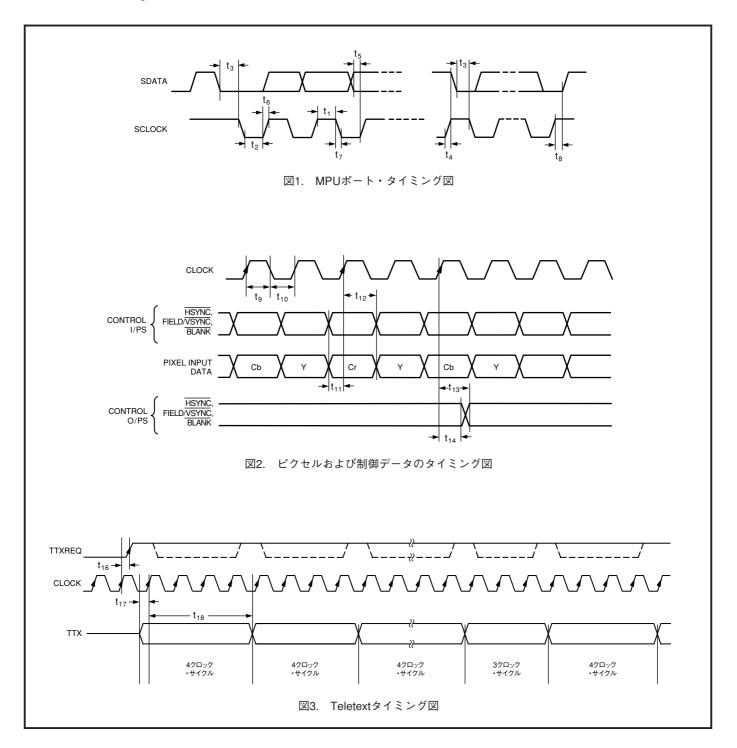

| MPUポート <sup>3、4</sup><br>SCLOCK周波数 |                     | 0   |     | 400 | kHz       |

| $SCLOCK$ のハイレベル・パルス幅、 $t_1$        |                     | 0.6 |     |     | μs        |

| $SCLOCK$ のローレベル・パルス幅、 $t_2$        |                     | 1.3 |     |     | μs        |

| ホールド時間(スタート状態)、t3                  | この時間が経過後に最初のクロックが発生 | 0.6 |     |     | $\mu$ s   |

| セットアップ時間(スタート状態)、t4                | 繰り返しスタート状態の場合       | 0.6 |     |     | $\mu$ s   |

| データ・セットアップ時間、t5                    |                     | 100 |     |     | ns        |

| SDATA、SCLOCK立ち上がり時間、t <sub>6</sub> |                     |     |     | 300 | ns        |

| SDATA、SCLOCK立ち下がり時間、t7             |                     |     |     | 300 | ns        |

| セットアップ時間(ストップ条件)、t <sub>8</sub>    |                     | 0.6 |     |     | μ s       |

| アナログ出力 <sup>3、5</sup>              |                     |     |     |     |           |

| アナログ出力遅延                           |                     |     | 7   |     | ns        |

| DACアナログ出力スキュー                      |                     |     | 0   |     | ns        |

| クロック制御および                          |                     |     |     |     |           |

| ピクセル・ポート4、5、6                      |                     |     |     |     |           |

| $f_{CLOCK}$                        |                     |     | 27  |     | MHz       |

| クロックのハイレベル時間、t,                    |                     | 8   |     |     | ns        |

| クロックのローレベル時間、t <sub>10</sub>       |                     | 8   |     |     | ns        |

| データ・セットアップ時間、t <sub>11</sub>       |                     | 3.5 |     |     | ns        |

| データ・ホールド時間、t <sub>12</sub>         |                     | 4   |     |     | ns        |

| $CONTROL$ のセットアップ時間、 $t_{11}$      |                     | 4   |     |     | ns        |

| $CONTROL$ のホールド時間、 $t_{12}$        |                     | 3   |     |     | ns        |

| デジタル出力アクセス時間、t <sub>13</sub>       |                     |     | 12  |     | ns        |

| デジタル出力のホールド時間、t <sub>14</sub> 4    |                     |     | 8   |     | ns        |

| パイプライン遅延、t15                       |                     |     | 48  |     | クロック・サイクル |

| TELETEXT <sup>3, 4, 7</sup>        |                     |     |     |     |           |

| デジタル出力アクセス時間、t <sub>16</sub>       |                     |     | 23  |     | ns        |

| データ・セットアップ時間、t <sub>17</sub>       |                     |     | 2   |     | ns        |

| データ・ホールド時間、t <sub>18</sub>         |                     |     | 6   |     | ns        |

| <br>RESETの制御³、4                    |                     |     |     |     |           |

| RESETのローレベル時間                      |                     | 6   |     |     | ns        |

#### 注

- 1 max/min仕様はこのレンジで保証。max/minは、3.0V~3.6Vでの代表的な値。

- 2 温度レンジT<sub>MIN</sub> ~T<sub>MAX</sub>は-40℃~+85℃。

- 3 TTL入力値はOV~3V、入力の立ち上がり/立ち下がり時間は3ns、10%~90%のポイントで測定。タイミング基準点は、入力と出力の50%値。アナログ出力負荷は10pF。

- 4 キャラクタライゼーションにより保証。

- 5 出力遅延は、CLOCK立ち上がりエッジの50%ポイントからフル・スケール変化の50%ポイントまでで測定。

- 6 ピクセル・ポートには次が含まれます。

ピクセル入力: P7~P0

ピクセル制御: HSYNC、FIELD/VSYNC、BLANK

クロック入力: CLOCK

7 Teletextポートには次が含まれます。

Teletext出力: TTXREQ Teletext入力: TTX

仕様は予告なく変更されることがあります。

4

#### 絶対最大定格1

| GND基準のV <sub>AA</sub> ・・・・・・・・・・・・・・・・・4V                   |

|-------------------------------------------------------------|

| デジタル入力ピンの電圧 $\cdots$ GND $-0.5$ V $\sim$ V $_{AA}+0.5$ V    |

| 保管温度( $T_s$ ) · · · · · · · · · · · · · · · · · · ·         |

| 接合温度(T <sub>J</sub> ) · · · · · · · · · · · · · · · · · · · |

| ピン温度(ハンダ処理、10秒)・・・・・・・260℃                                  |

| GND基準のアナログ出力 <sup>2</sup> ······GND-0.5V~V <sub>AA</sub>    |

#### 注

- 1 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

- 2 任意の電源またはグラウンドに対するアナログ出力の短絡時間は、無限とすることができます。

#### オーダー・ガイド

| 製品モデル      | 温度レンジ     | パッケージ | パッケージ・オプション |

|------------|-----------|-------|-------------|

| ADV7179KCP | 0℃~70℃    | LFCSP | LFCSP-40    |

| ADV7179BCP | -40℃~+85℃ | LFCSP | LFCSP-40    |

| ADV7174KCP | 0℃~70℃    | LFCSP | LFCSP-40    |

| ADV7174BCP | -40℃~+70℃ | LFCSP | LFCSP-40    |

注意

ESD (静電放電) の影響を受けやすいデバイスです。4000Vにおよぶ高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD防止措置をとるようお奨めします。

#### ピン機能の説明

| 記号               | 入力/出力 | 機能                                                                  |

|------------------|-------|---------------------------------------------------------------------|

| P7~P0            | I     | 8ビット、4:2:2、多重化YCrCbピクセル・ポート(P7~P0)                                  |

| CLOCK            | I     | TTLクロック入力。標準動作には安定した27MHz基準クロックが必要。あるいは、スクエア・ピク                     |

|                  |       | セル動作には24.5454MHz (NTSC)または29.5MHz (PAL)の使用が可能。                      |

| HSYNC            | I/O   | HSYNC (モード1およびモード2)制御信号。同期信号の出力(マスター・モード)または入力(スレ                   |

|                  |       | ーブ・モード)に設定可能。                                                       |

| FIELD/VSYNC      | I/O   | デュアル・ファンクション・フィールド(モード1)とVSYNC(モード2)の制御信号。これらの制御信号                  |

|                  |       | の出力(マスター・モード)または入力(スレーブ・モード)に設定可能。                                  |

| BLANK            | I/O   | ビデオ・ブランキング・制御信号。ロジック・レベル0のとき、ピクセル入力が無視されます。この                       |

|                  |       | 信号はオプションです。                                                         |

| SCRESET/RTC      | I     | モード・レジスタ2のMR22とMR21をセットすると、このピンは入力に設定されます。 サブキャリア                   |

|                  |       | のリセットピンとして設定することができ、その場合、このピンでローからハイへの変化が検出され                       |

|                  |       | ると、サブキャリアがフィールド0にリセットされます。あるいは、このピンをリアルタイム制御(RTC)                   |

|                  |       | 入力に設定することもできます。                                                     |

| $V_{REF}$        | I/O   | DACの電圧リファレンス入力または電圧リファレンス出力(1.235V)                                 |

| $R_{\text{SET}}$ | I     | このピンとGNDとの間に150Ωの抵抗を接続して、ビデオ信号のフル・スケール振幅の制御に使                       |

|                  |       | います。                                                                |

| COMP             | О     | 補償ピン。 $COMP$ と $V_{AA}$ の間に $0.1\mu$ $F$ のコンデンサを接続します。低消費電力モードで最適ダイ |

|                  |       | ナミック性能を得るために、COMPコンデンサの値を2.2 nFまで小さくすることができます。                      |

| DAC A            | О     | DAC出力(表I参照)                                                         |

| DAC B            | О     | DAC出力(表I参照)                                                         |

| DAC C            | О     | DAC出力(表I参照)                                                         |

| SCLOCK           | I     | MPUポート・シリアル・インターフェースのクロック入力                                         |

| SDATA            | I/O   | MPUポート・シリアル・データの入/出力                                                |

| ALSB             | I     | TTLアドレス入力。この信号は、MPUアドレスのLSBを設定します。                                  |

| RESET            | I     | この入力は、内蔵タイミング・ジェネレータをリセットし、ADV7174/ADV7179がデフォルト・モード                |

|                  |       | に設定されます。デフォルト・モードでは、NTSC動作、タイミング・スレーブ・モード0、8ビット動作、                  |

|                  |       | 2×コンポジットおよびSビデオ出力、DAC Bがパワーオン、DAC Dがパワーオフに設定されます。                   |

| TTX              | I     | Teletextデータ                                                         |

| TTXREQ           | О     | Teletextデータ要求信号。Teletextが選択されていない場合はデフォルトとしてGNDに接続。                 |

| $V_{AA}$         | P     | 電源(3.3V)                                                            |

| GND              | G     | グラウンド・ピン                                                            |

#### 概要

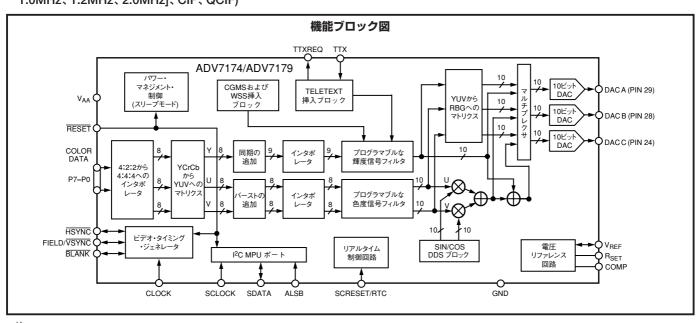

ADV7174/ADV7179は、CCIR-601 4:2:2のデジタル8ビット・コンポーネント・ビデオ・データを世界標準と互換性を持つ標準アナログ・ベースバンド・テレビ信号に変換する統合デジタル・ビデオ・エンコーダです。

拡張した輝度信号周波数応答とシャープな阻止帯域減衰特性を持つSSAF (スーパー・サブ・エイリアス・フィルタ)を内蔵しているため、最新のTVでスタジオ品質のビデオ再生が可能になり、最適な水平ライン分解能を得ることができます。

高度なパワー・マネジメント回路により、通常動作モードでもパワーダウンすなわちスリープモードでも消費電力が最適制御されます。

ADV7174/ADV7179は、PALとNTSCの両方のスクエア・ピクセル動作をサポートしています。両モデルとも、WSSおよびCGMS-Aのデータ制御生成機能を内蔵しています。

出力ビデオ・フレームは、受信データ・タイミング・リファレンス・コードに同期化されます。オプションとして、エンコーダはHSYNC、VSYNC、FIELDのタイミング信号を入力する(そして発生させる)ことができます。デバイスがマスター・モードのときは、これらのタイミング信号を調整して、パルス幅と位置を変更することができます。エンコーダでは、標準動作のピクセル・レート・クロック(27MHz)の2倍の信号が必要です。あるいは、NTSCでは24.5454MHzクロック、PALでは29.5MHzクロックが、スクエア・ピクセル・モード動作に必要です。すべての内部タイミングは、デバイス内部で発生されます。

独立したTeletextポートにより、垂直ブランキングの合い間にTeletext データを直接入力することができます。

ADV7174/ADV7179のモードは、2つのスレーブ・アドレスを持つ2線 式シリアル双方向ポート(I<sup>2</sup>C互換)を介して設定します。

ADV7174/ADV7179は、40ピンLFSCPパッケージを採用しています。

#### データ・パスの説明

PAL B/D/G/H/I/M/NモードとNTSC MおよびNモードの場合、YCrCb 4:2:2データは27MHzのデータ・レートでCCIR-656互換ピクセル・ポートから入力されます。このピクセル・データは、3つのデータ・パスに分離されます。一般に、Yは16~235のレンジを、CrとCbは128  $\pm$

112のレンジを持ちますが、Y、Cb、Crに1~254のデータを入力することができます。ADV7174/ADV7179は、PAL (B/D/G/H/I/M/N)標準とNTSC標準(ペデスタル有りおよび無し)をサポートしています。該当するSYNC、BLANK、バースト・レベルがYCrCbデータに追加されます。YにはMacrovision Antitapingレベル(ADV7174のみ)、クローズド・キャプショニング・レベル、Teletextレベルも追加され、データは補間されて27MHzのレートになります。補間されたデータは3つのデジタルFIRフィルタを使って、フィルタおよびスケールされます。

U信号とV信号は該当するサブキャリアのsine/cosineフェーズによって変調されてから加算され、色度信号がつくられます。輝度信号(Y)は、色度信号に対して輝度信号の $1\sim3$ サイクル(各サイクルは74ns)分遅延させることができます。その後、輝度信号と色度信号が加算されてコンポジット・ビデオ信号がつくられます。すべてのエッジのスルーレートは制限されています。

このYCrCbデータは、該当する同期レベルとBLANKレベルを持つ RGBデータをつくる際にも使われます。RGBデータは、コンポジット・ビデオ出力に同期化されます。RGBデータの代わりに、アナログYUVデータをつくることもできます。

3つの10ビットDACを使って、次の出力を発生できます。

- 1. コンポジット・ビデオ+コンポジット・ビデオ

- 2. Sビデオ+コンポジット・ビデオ

- 3. YPrPbビデオ

- 4. SCART RGBビデオ

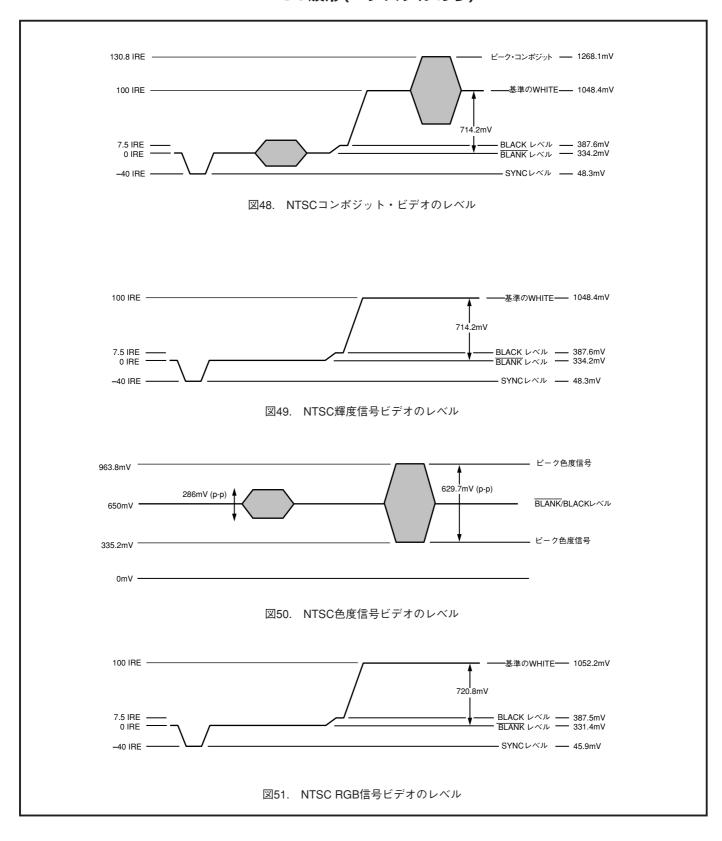

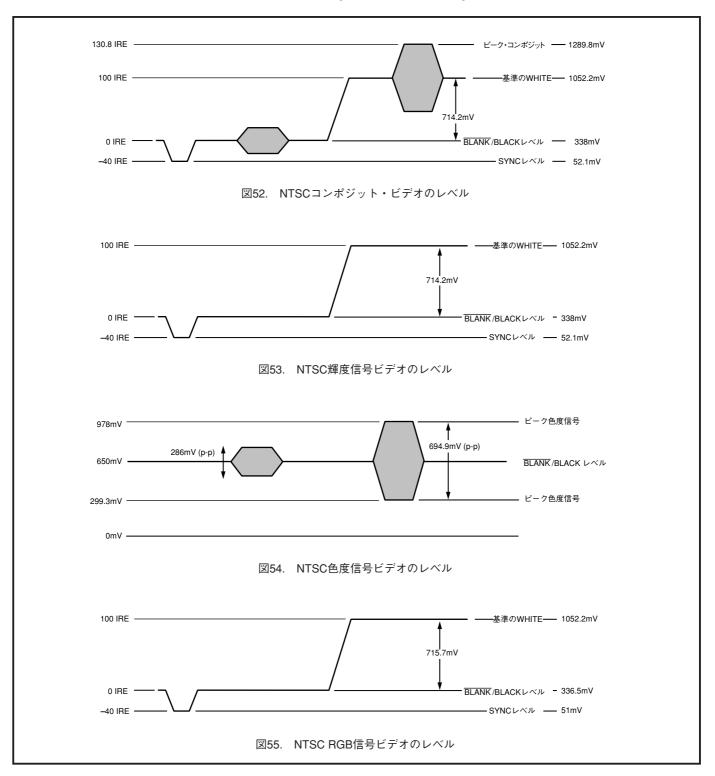

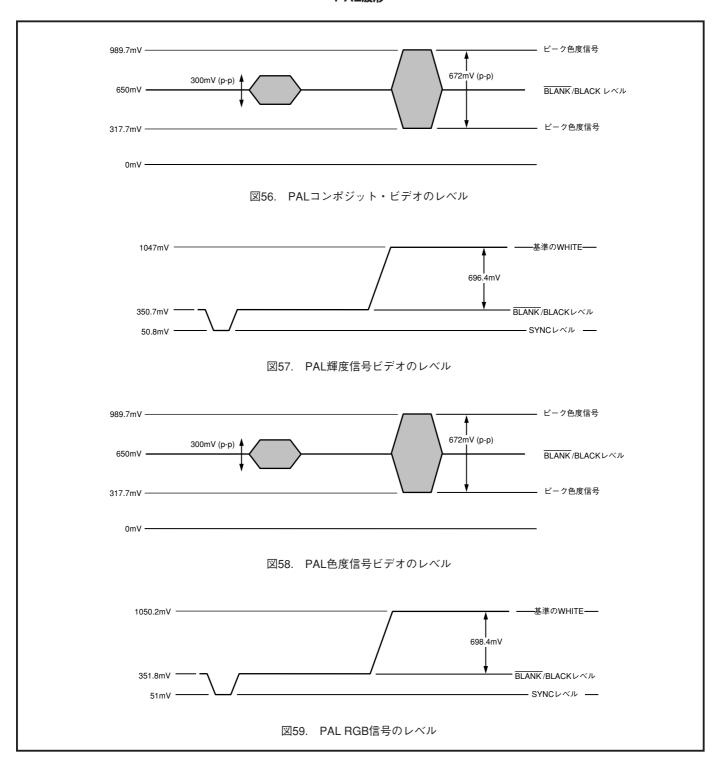

不要な場合は、各DACを個別にパワーオフすることができます。 アペンディックス6に、各ビデオ出力レベルを示します。

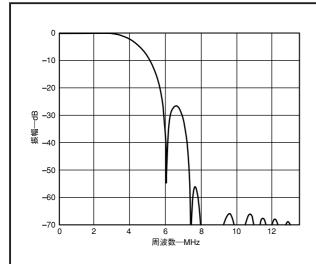

#### 内部フィルタの応答

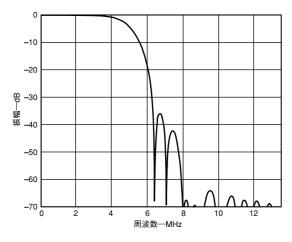

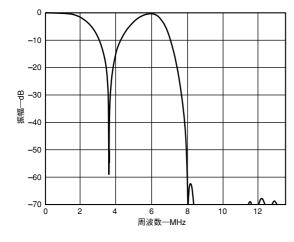

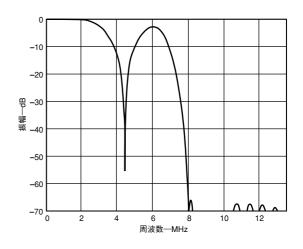

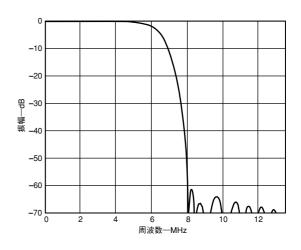

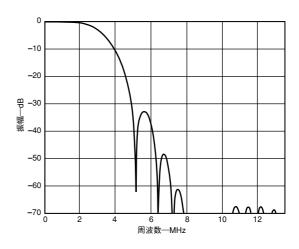

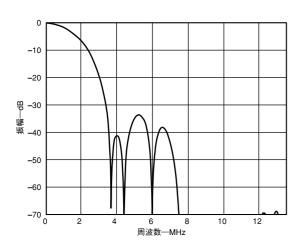

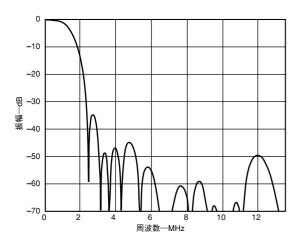

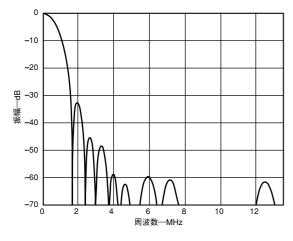

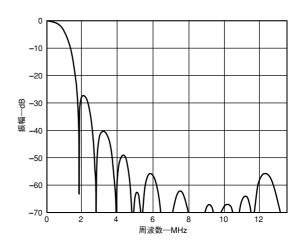

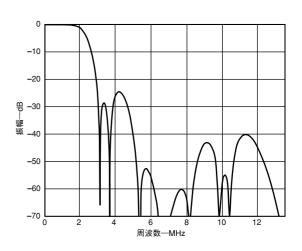

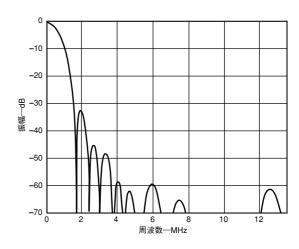

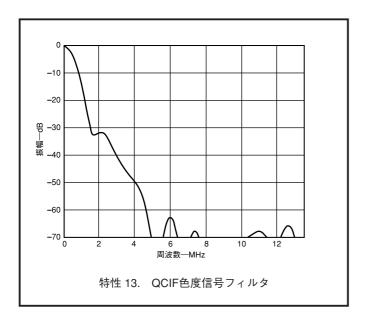

Yフィルタは、2種類のローパス応答、2種類のノッチ応答、1種類の拡張(SSAF)応答、1種類のCIF応答、1種類のQCIF応答など、複数の周波数応答をサポートしています。UVフィルタは、4種類のローパス応答、1種類のCIF応答、1種類のQCIF応答など、複数の周波数応答をサポートしています。図4と図5および特性1~13に、これらの応答を示します。

| フィルタ・タイプ   | フィルタの選択 |      |      | 通過帯域リップル<br>(dB) | 3dB帯域幅<br>(MHz) | 阻止帯域<br>カットオフ(MHz) | 阻止帯域減衰<br>(dB)  |

|------------|---------|------|------|------------------|-----------------|--------------------|-----------------|

|            | MR04    | MR03 | MR02 |                  |                 |                    |                 |

| ローパス(NTSC) | 0       | 0    | 0    | 0.091            | 4.157           | 7.37               | <b>-</b> 56     |

| ローパス(PAL)  | 0       | 0    | 1    | 0.15             | 4.74            | 7.96               | -64             |

| ノッチ(NTSC)  | 0       | 1    | 0    | 0.015            | 6.54            | 8.3                | -68             |

| ノッチ(PAL)   | 0       | 1    | 1    | 0.095            | 6.24            | 8.0                | -66             |

| 拡張(SSAF)   | 1       | 0    | 0    | 0.051            | 6.217           | 8.0                | <del>-</del> 61 |

| CIF `      | 1       | 0    | 1    | 0.018            | 3.0             | 7.06               | <del>-</del> 61 |

| QCIF       | 1       | 1    | 0    | 単調               | 1.5             | 7.15               | <b>-</b> 50     |

図4. 輝度信号用内部フィルタの仕様

| フィルタ・タイプ                                | フ         | フィルタの選択   |           | 通過帯域リップル<br>(dB)   | 3dB帯域幅<br>(MHz)    | 阻止帯域<br>カットオフ(MHz) | 阻止帯域減衰<br>(dB)      |

|-----------------------------------------|-----------|-----------|-----------|--------------------|--------------------|--------------------|---------------------|

| 1.3MHzローパス                              | MR07<br>0 | MR06<br>0 | MR05<br>0 | 0.084              | 1.395              | 3.01               | -45                 |

| 0.65MHzローパス<br>1.0MHzローパス<br>2.0MHzローパス | 0         | 0         | 0         | 単調<br>単調<br>0.0645 | 0.65<br>1.0<br>2.2 | 3.64<br>3.73       | –58.5<br>–49<br>–40 |

| Z.UMHZローハス<br>  予約済み<br>  CIF           | 1 1       | 0         | 0         | 0.0645             | 0.7                | 5.0<br>3.01        | -40<br>-45          |

| OCIF                                    | Ιi        | 1         | ò         | 単調                 | 0.5                | 4.08               | <b>-</b> 50         |

図5. 色度信号用内部フィルタの仕様

# ADV7174/ADV7179—代表的な性能特性

特性 1. NTSCローパス輝度信号フィルタ

特性 2. PALローパス輝度信号フィルタ

特性 3. NTSCノッチ輝度信号フィルタ

特性 4. PALノッチ輝度信号フィルタ

特性 5. 拡張モード(SSAF)輝度信号フィルタ

特性 6. CIF輝度信号フィルタ

REV.0

8

特性 7. QCIF輝度信号フィルタ

特性 8. 1.3MHzローパス色度信号フィルタ

特性 9. 0.65MHzローパス色度信号フィルタ

特性 10. 1.0MHzローパス色度信号フィルタ

特性 11. 2.0MHzローパス色度信号フィルタ

特性 12. CIF色度信号フィルタ

#### カラー・バーの牛成

ADV7174/ADV7179は、NTSCに対しては100/7.5/75/7.5カラー・バーを、PALに対しては100/0/75/0カラー・バーを発生するように設定することができます。モード・レジスタ1のMR17をロジック"1"に設定するとイネーブルされます。

#### スクエア・ピクセル・モード

ADV7174/ADV7179は、スクエア・ピクセル・モードで動作させることができます。NTSC動作に対しては、24.5454MHzの入力クロックが必要です。PAL動作に対しては、29.5MHzの入力クロックが必要です。内部タイミング・ロジックは、スクエア・ピクセル・モード動作に合わせて調整されます。

#### 色信号の制御

モード・レジスタ2のビットMR24を使って、ビデオ出力の色情報をONおよびOFFすることができます。

#### バースト信号の制御

モード・レジスタ2のビットMR25を使って、ビデオ出力のバースト情報をONおよびOFFすることができます。

#### NTSCペデスタルの制御

NTSCペデスタル制御レジスタを使って、奇数フィールドと偶数フィールドのペデスタルをライン毎に制御することができます。この機能により、垂直ブランキング・インターバルでペデスタルを制御できます。

#### ピクセル・タイミングの説明

ADV7174/ADV7179は、8ビットまたは16ビットのYCrCbモードで動作することができます。

#### 8ビットYCrCbモード

デフォルト・モードであり、多重化されたYCrCb入力をP7~P0のピクセル入力から入力できます。この入力は、Cb0、Y0 Cr0、Y1 Cb1、Y2、…のシーケンスに従います。Y、Cb、Crの各データは、クロックの立ち上がりエッジで入力されます。

#### サブキャリアのリセット

SCRESET/RTCピンとモード・レジスタ2のMR22ビットおよびMR21ビットを組合わせて使うと、ADV7174/ADV7179をサブキャリア・リセット・モードで使うことができます。この入力ピンでローからハイへの変化が検出されると、次のフィールドのスタート時に、サブキャリアはフィールド0にリセットされます。

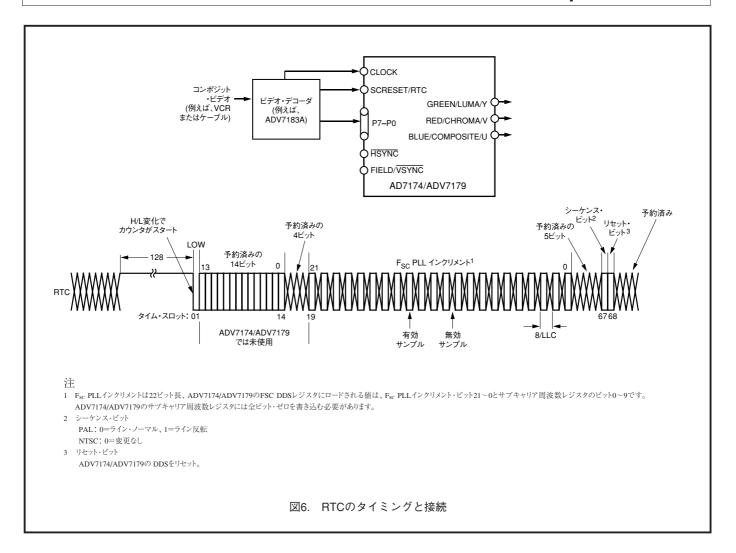

#### リアルタイム制御

SCRESET/RTCピンとモード・レジスタ2のMR22ビットおよびMR21ビットを組合わせて使うと、ADV7174/ADV7179を外部ビデオ信号源にロックすることができます。リアルタイム制御モードを使うと、ADV7174/ADV7179は自動的にサブキャリア周波数を変えて、ライン長の変化を補償します。RTCフォーマットでデジタル・データ・ストリームを出力するデバイス(例えば、図6のADV7185ビデオ・デコーダ)に接続すると、ADV7174/ADV7179はライン毎の補償サブキャリア周波数に自動的に変化します。このデジタル・データ・ストリームは67ビット幅で、サブキャリアはビット0~21に格納されています。各ビットは2クロック・サイクル長です。このモードを使う場合、4つのサブキャリア周波数レジスタ全部に00Hexを書き込む必要があります。

#### ビデオ・タイミングの説明

ADV7174/ADV7179は、既製品のMPEG1デコーダとMPEG2デコーダにインターフェースするように設計されています。したがって、ADV7174/ADV7179にはCCIR-656ピクセル・ポートから4:2:2 YCrCbピクセル・データを入力します。複数のビデオ・タイミング動作モードが用意されているので、システムのマスター・ビデオ・タイミング・ジェネレータまたはシステムのビデオ・タイミング・ジェネレータのスレーブとして設定することができます。ADV7174/ADV7179は、必要なすべての水平と垂直のタイミング周期とアナログ・ビデオ出力レベルを発生できます。

ADV7174/ADV7179は、アナログ同期パルスの幅と位置、ブランキング・レベル、カラー・バーストの包絡線を計算します。カラー・バーストは該当するラインでディスエーブルされ、必要に応じて鋸歯状波形と等化パルスが挿入されます。

さらに、ADV7174/ADV7179はスレーブ・モードでPALまたはNTSC のスクエア・ピクセル動作もサポートします。NTSCに対しては24.5454MHzの入力ピクセル・クロックが、PALに対しては29.5MHzの入力ピクセル・クロックが必要です。内部水平ライン・カウンタが、新しいクロック周波数に対して正しい位置に種々のビデオ波形の部分を配置します。

ADV7174/ADV7179には、4種類のマスター・タイミング設定と4種類のスレーブ・タイミング設定があります。タイミング制御は、双方向のHSYNCピン、BLANKピン、FIELD/VSYNCピンで行います。タイミング・パルス幅を変更するとき、および相互の関係で変更が発生するときには、タイミング・モード・レジスタ1を使うこともできます。

#### 垂直ブランキングへのデータ挿入

ライン同期またはプリ/ポスト等化パルスを持たないVBIのライン上で受信YCbCrデータのエンコーディングをすることが可能です(図8~図19参照)。この動作モードはパーシャル・ブランキングと呼ばれ、MR32を"1"に設定して選択します。このモードを使うと、任意のVBIデータ(オープンVBI)をエンコードされた出力波形に挿入することができます。このデータは、デジタル化された受信YCbCrデータ・ストリーム内に配置されます(例えば、WSSデータ、CGMS、VPSなど)。MR32を"0"に設定すると、これらのライン上でVBI全体をブランク(VBIデータの挿入なし)にすることができます。

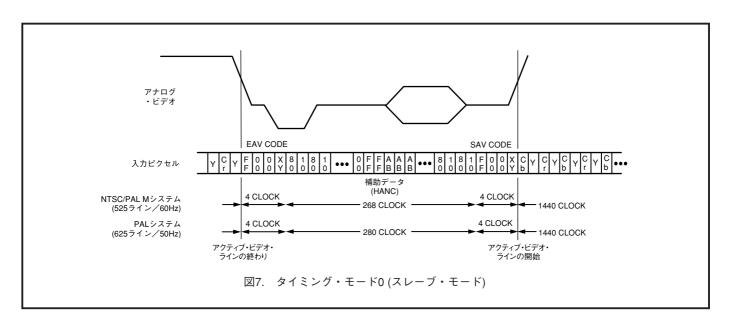

モード0 (CCIR-656): スレーブ・オプション (タイミング・レジスタ0 TR0=X X X X X 0 0 0)

ADV7174/ADV7179は、ピクセル・データのSAV (スタート・アクティブ・ビデオ)タイム・コードおよびEAV (エンド・アクティブ・ビデオ)タイム・コードによって制御されます。すべてのタイミング情報は、4バイトの同期パターンを使って送信されます。同期パターンは、アクティブ・ピクチャおよびリトレースの間に、各ラインの直前直後に送信されます。図7にモード0を示します。このモードでは、HSYNCピン、FIELD/VSYNCピン、BLANK (未使用時)ピンをハイレベルに接続しておく必要があります。

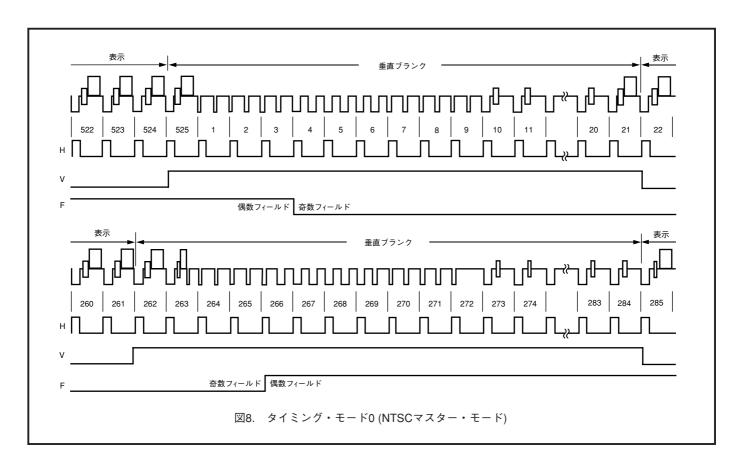

モード0 (CCIR-656): マスター・オプション (タイミング・レジスタ0 TR0=X X X X X 0 0 1)

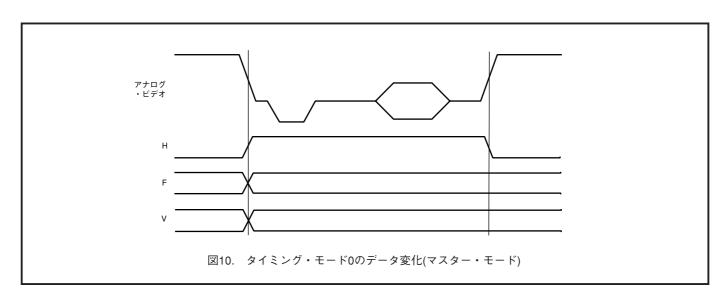

ADV7174/ADV7179は、CCIR-656標準のSAVおよびEAVタイム・コードに必要なH、V、Fの信号を発生します。HビットはHSYNCピン

に、VビットはBLANKピンに、FビットはFIELD/VSYNCピンに、それ ぞれ出力されます。モード0を図8 (NTSC)と図9 (PAL)に示します。ビデオ波形を基準とするH、V、Fの各変化を図10に示します。

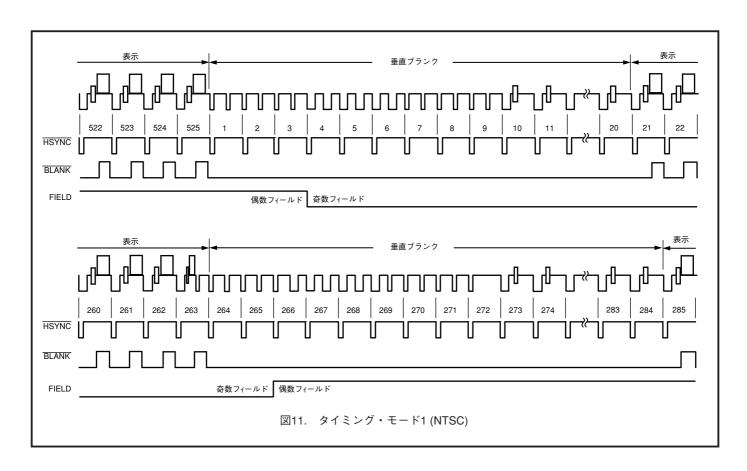

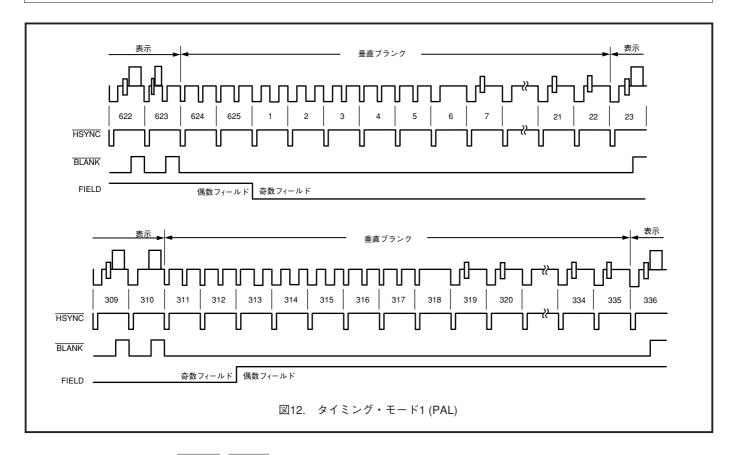

## モード1:スレーブ・オプションHSYNC、BLANK、FIELD (タイミング・レジスタ0 TR0=X X X X X 0 1 0)

このモードでは、ADV7174/ADV7179が、水平SYNC信号と奇数/ 偶数FIELD信号を受け取ります。HSYNCがローレベルのときのFIELD 入力の変化は、新しいフレームすなわち垂直リトレースを表します。 BLANK信号はオプションです。 $\overline{\text{BLANK}}$ 入力がディスエーブルされると、ADV7174/ADV7179はCCIR-624の規定に従い通常ブランクの全ラインを自動的にブランクにします。モード1を図11 (NTSC)と図12 (PAL)に示します。

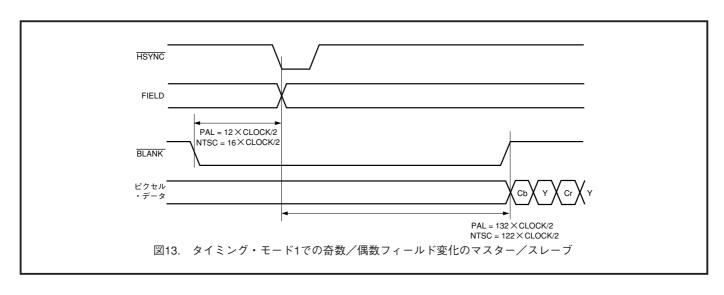

### モード1:マスター・オプションHSYNC、BLANK、FIELD (タイミング・レジスタ0 TR0=X X X X X 0 1 1)

このモードでは、ADV7174/ADV7179が、水平SYNC信号と奇数/偶数FIELD信号を発生できます。 $\overline{\text{HSYNC}}$ がローレベルのときのFIELD入力の変化は、新しいフレームすなわち垂直リトレースを表します。 $\overline{\text{BLANK}}$ 信号はオプションです。 $\overline{\text{BLANK}}$ 入力がディスエーブルされる

と、ADV7174/ADV7179はCCIR-624の規定に従い通常ブランクの全ラインを自動的にブランクにします。ピクセル・データは次のタイミング信号変化の後の立ち上がりクロック・エッジでラッチされます。モード1を図11 (NTSC)と図12 (PAL)に示します。図13に、ピクセル・データを基準とした奇数または偶数フィールド変化に対するHSYNC、BLANK、FIELDの各信号を示します。

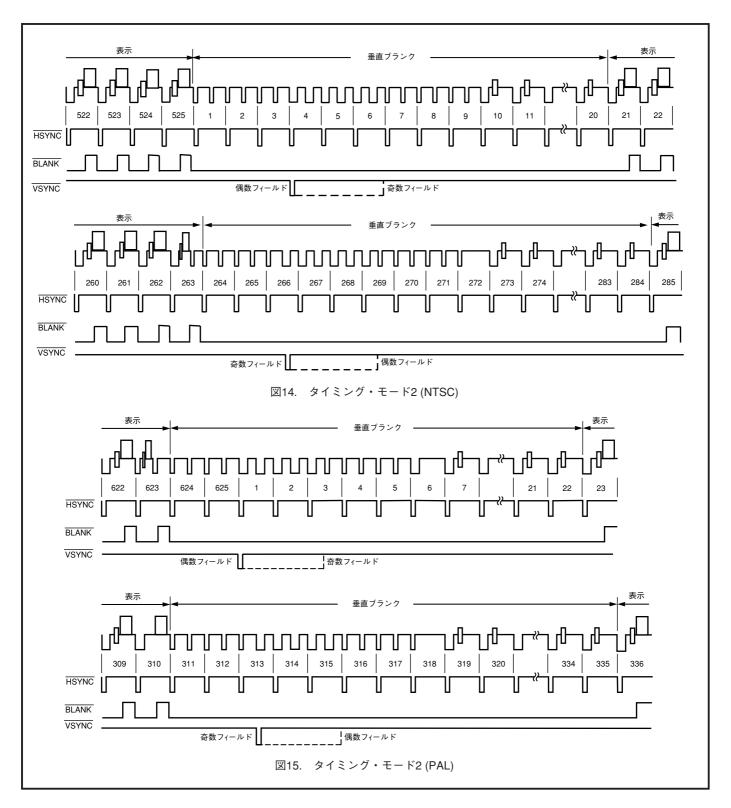

# モード2: スレーブ・オプション HSYNC、VSYNC、BLANK (タイミング・レジスタ0 TR0=X X X X X 1 0 0)

このモードでは、ADV7174/ADV7179が水平および垂直の同期信号を受け取ります。 $\overline{HSYNC}$ 入力と $\overline{VSYNC}$ 入力が同時にローレベルへ変化するときは、奇数フィールドの開始を意味します。 $\overline{HSYNC}$ がハイ

レベルのときのVSYNCのローレベルへの変化は、偶数フィールドの開始を意味します。BLANK信号はオプションです。BLANK入力がディスエーブルされると、ADV7174/ADV7179はCCIR-624の規定に従い通常プランクの全ラインを自動的にブランクにします。モード2を図14(NTSC)と図15(PAL)に示します。

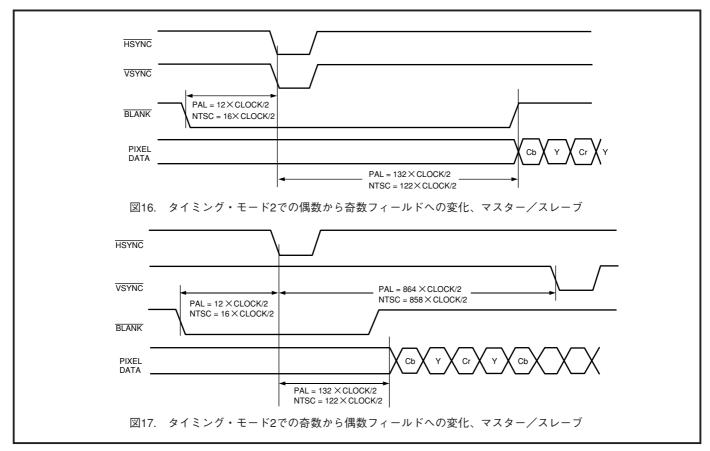

### モード2:マスター・オプションHSYNC、VSYNC、BLANK (タイミング・レジスタ0 TR0=X X X X X X 1 0 1)

このモードでは、ADV7174/ADV7179が水平および垂直の同期信号を発生できます。 $\overline{\text{HSYNC}}$ 入力と $\overline{\text{VSYNC}}$ 入力が同時にローレベルへ変化するときは、奇数フィールドの開始を意味します。 $\overline{\text{HSYNC}}$ がハイレベルのときの $\overline{\text{VSYNC}}$ のローレベルへの変化は、偶数フィールドの開始を意味します。 $\overline{\text{BLANK}}$ 入力がディ

スエーブルされると、ADV7174/ADV7179はCCIR-624の規定に従い通常ブランクの全ラインを自動的にブランクにします。モード2を図14 (NTSC)と図15 (PAL)に示します。図16に、ピクセル・データを基準とした偶数から奇数フィールドへの変化に対するHSYNC、BLANK、VSYNCの各信号を示します。図17に、ピクセル・データを基準とした奇数から偶数フィールドへの変化に対するHSYNC、BLANK、VSYNCの各信号を示します。

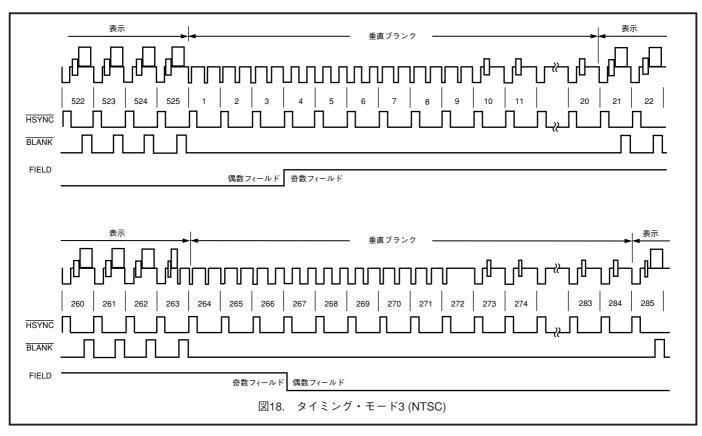

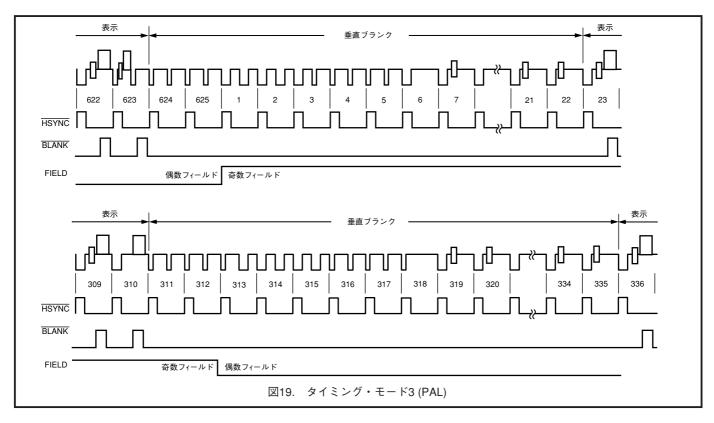

モード3:マスター/スレーブ・オプションHSYNC、BLANK、FIELD

(タイミング・レジスタ0 TR0=X X X X X 1 1 0またはX X X X X 1 1 1) このモードでは、ADV7174/ADV7179が水平SYNC信号および奇数/ 偶数FIELD信号を入力または発生します。 HSYNCがハイレベルのとき のFIELD入力の変化は、新しいフレームすなわち垂直リトレースを表します。 $\overline{\text{BLANK}}$ 信号はオプションです。 $\overline{\text{BLANK}}$ 入力がディスエーブルされると、ADV7174/ADV7179はCCIR-624の規定に従い通常ブランクの全ラインを自動的にブランクにします。モード3を図18 (NTSC)と図19 (PAL)に示します。

#### パワーオン・リセット

パワーアップ後に、リセット動作を実行する必要があります。RESETピンでのハイからローへの立ち下がりエッジで、リセットが実行されます。リセットではピクセル・ポートが初期化されるため、ピクセル入力P7~P0が選択されます。リセット後、ADV7174/ADV7179はNTSCモードで動作するように自動的に設定されます。サブキャリア周波数レジスタには、サブキャリア周波数コード21F07C16HEXがロードされます。モード・レジスタ0を除く他のすべてのレジスタには00Hが設定されます。モード・レジスタ0のビットMR44を除くすべてのビットは、ロジック・レベル"0"に設定されます。モード・レジスタ4のビットMR44はロジック"1"に設定されます。これにより、7.5 IREペデスタルがイネーブルされます。

#### SCHフェーズモード

SCHフェーズはデフォルト・モードに設定され、SCHフェーズ誤差の時間 的累積を防止するために、4フィールド(NTSC)毎または8 (PAL)フィールド 毎にリセットします。理想のシステムではゼロSCHフェーズ誤差が無限に維 持されますが、実際にはクロック周波数の変動があるため維持できません。 この影響は、SCHを発生する32ビットDDSを使うことにより軽減できます。

4または8フィールド毎にSCHフェーズをリセットすると、SCHフェーズ誤差の累積を防止し、4または8フィールド・シーケンスの開始時のSCHフェーズジャンプを非常に小さくできます。

ビデオ信号源が安定したタイミングを使用していない場合、または ADV7174/ADV7179がRTCモードに設定されている場合(MR21=1かつ MR22=1)には、SCHフェーズのリセットを行わないようにする必要があります。これらの条件(不安定なビデオ)の下では、サブキャリア・フェーズ・リセットをイネーブルし(MR22=0かつMR21=1)、リセットを行わないようにします。この設定では、SCHフェーズがリセットされず、出力ビデオが不安定な入力ビデオに追従することを意味します。サブキャリア・フェーズ・リセットを入力すると、次のフィールドの開始時にSCHフェーズがフィールドのにリセットされます(例えば、次のフィールドの開始時にサブキャリア・フェーズ・リセットをフィールド5 [PAL]で入力すると、SCHフェーズはフィールド0にリセットされます)。

#### MPUポートの説明

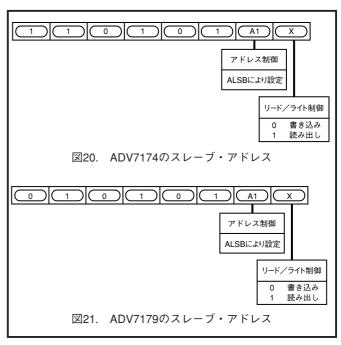

ADV7174/ADV7179は、複数のペリフェラルを駆動する2線式シリアル (I²C互換)マイクロプロセッサ・バスをサポートしています。シリアル・データ (SDATA)とシリアル・クロック(SCLOCK)の2本の入力が、バスに接続された任意のデバイス間で情報を転送します。各スレーブ・デバイスは独自のアドレスで識別されます。ADV7174/ADV7179では、読み出し動作と書き込み動作のために4つのスレーブ・アドレスを使うことができます。これらは各デバイスに固有のアドレスであり、図20と図21に示します。LSBで読み出し動作または書き込み動作を指定します。ロジック・レベル"1"は読み出し動作に、ロジック・レベル"0"は書き込み動作に対応します。ADV7174/ADV7179のALSBピンをロジック・レベル"0"またはロジック・レベル"1"に設定すると、A 1が設定されます。

バス上の様々なデバイスを制御するときは、次のプロトコルに従う必 要があります。先ず、マスター側がスタート状態を設定してデータ転送 を開始します。スタート状態は、SCLOCKがハイレベルのときに、 SDATA上でハイレベルからローレベルへの変化が発生することとして 定義されています。これは、アドレス/データ・ストリームが後ろに続く ことを示しています。すべてのペリフェラルはスタート状態に応答して、 次の8ビット(7ビット・アドレス+R/Wビット)をシフトします。各ビットは、 MSBからLSBへ転送されます。送信されたアドレスに対応するアドレス を持つペリフェラルは、9番目のクロック・パルス区間中に、データ・ラ インをローレベルにプルダウンして応答します。これはアクノリッジ・ビッ トと呼ばれています。この時点で、バス上の他のすべてのデバイスが 接続を辞退して、アイドル状態を維持します。アイドル状態では、各デ バイスはSDATAラインとSCLOCKラインをモニターして、スタート状態 と自分のアドレスの受信を待ちます。R/Wビットがデータの転送方向を 指定します。先頭バイトのLSBがロジック"0"のとき、マスターがペリフ エラルに情報を書き込むことを意味します。先頭バイトのLSBがロジッ ク"1"のとき、マスターがペリフェラルから情報を読込むことを意味しま

ADV7174/ADV7179はバス上の標準スレーブ・デバイスとして機能します。SDATAピン上のデータは8ビット長で、7ビット・アドレスとR/Wビットをサポートしています。ADV7174/ADV7179は内部レジスタに対するアクセスを可能にするため、26個のサブアドレスを持っています。このため、先頭バイトをデバイス・アドレスとして、2番目のバイトをサブアドレスの先頭として解釈します。サブアドレスの自動インクリメント機能により、サブアドレスの先頭からデータの書き込みまたは読み出しが可能です。データ転送は常にストップ状態によって終了します。すべてのレジスタを更新しなくても、固有のサブアドレス・レジスタを1個ずつアクセスすることもできます。ただし、サブキャリア周波数レジスタだけは、サブキャリア周波数レジスタのから順番に更新する必要があります。その後に、自動インクリメント機能を使ってインクリメントし、サブキャリア周波数レジスタ1、2、3をアクセスする必要があります。サブキャリア周波数レジスタ1、2、3をアクセスすることはできません。

ストップ状態とスタート状態は、データ転送の任意のステージで検出することができます。通常の読み出し動作と書き込み動作で、これらの状態が検出されると、直ちにアイドル状態になります。所与のSCLOCKのハイレベルの区間に、1スタート状態、1ストップ状態、または1ストップ状態に続いて1スタート状態だけを発生させることができます。無効なサブアドレスが指定されると、ADV7174/ADV7179はアックを発生しないでアイドル状態に戻ります。自動インクリメント・モード時に最高サブアドレスを超えると、次の動作が実行されます。

- 1. 読み出しモードでは、マスター・デバイスが非アクノリッジを発行する まで、最高サブアドレス・レジスタの値が出力され続けます。これは 読み出しの終了を意味します。非アクノリッジ状態は、9番目のパル スでSDATAラインがローレベルにならないときに発生します。

- 2. 書き込みモードでは、無効バイトのデータはサブアドレス・レジスタに ロードされず、ADV7174/ADV7179から非アクノリッジが発行されて、 デバイスはアイドル状態に戻ります。

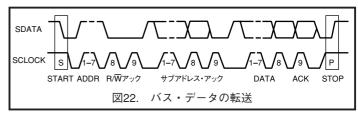

図22に、読み出しシーケンスでのデータ転送および、スタート状態とストップ状態の例を示します。

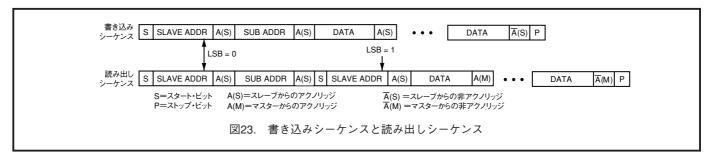

図23に、バスの書き込みおよびバス読み出しシーケンスを示します。

#### レジスタのアクセス

MPUは、書き込み専用レジスタであるサブアドレス・レジスタを除く、すべてのADV7174/ADV7179レジスタに対する書き込みまたは読み出しが行えます。サブアドレス・レジスタは、次の読み出し動作または書き込み動作でアクセスするレジスタを指定します。バスを経由するすべてのデバイスとの通信は、サブアドレス・レジスタへのアクセスで開始されます。ターゲット・アドレスに対して読み出し/書き込み動作が実行され、その後で次のアドレスにインクリメントされ、バス上でストップ・コマンドが検出されるまで繰り返します。

#### レジスタの設定

この節では、サブアドレス・レジスタ、モード・レジスタ、サブキャリア 周波数レジスタ、サブキャリア・フェーズ・レジスタ、タイミング・レジス タ、クローズド・キャプショニング拡張データ・レジスタ、クローズド・キャ プショニング・データ・レジスタ、NTSCペデスタル制御レジスタなどの 各レジスタの設定について説明します。

#### サブアドレス・レジスタ(SR7~SR0)

コミュニケーション・レジスタは、8ビットの書き込み専用レジスタです。 デバイスがバスからアクセスされ読み出し/書き込み動作が選択され た後に、サブアドレスが設定されます。サブアドレス・レジスタは、動作 の対象となるレジスタを指定します。

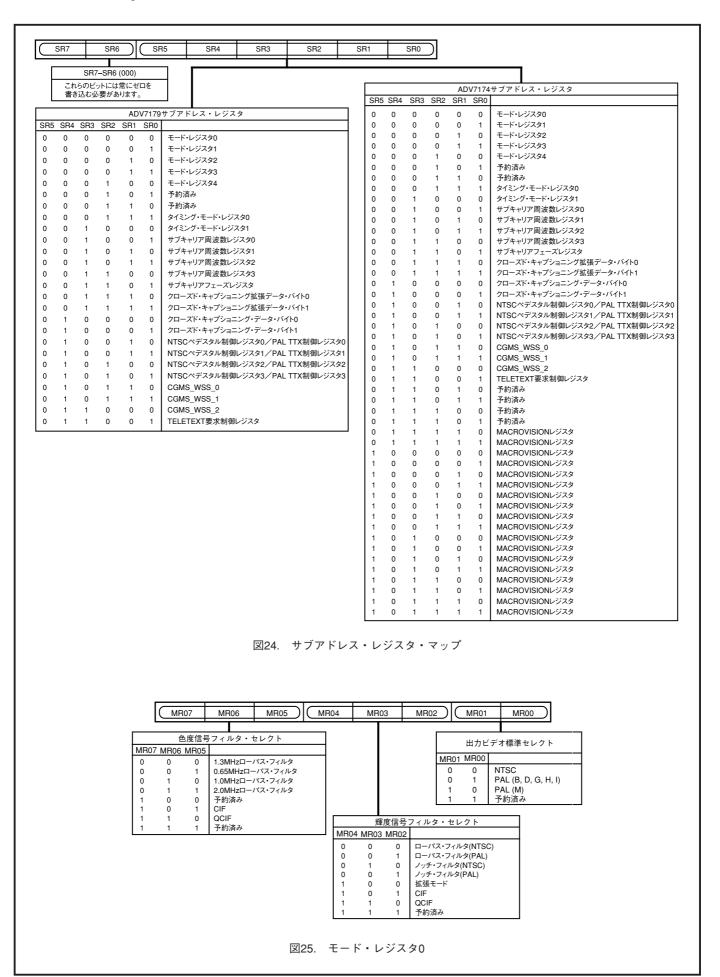

図24に、サブアドレス・レジスタによって制御される様々な動作を示します。SR7~SR6には常にゼロを書き込みます。

#### レジスタ・セレクト(SR5~SR0)

これらのビットで必要な開始アドレスを指定します。

#### モード・レジスタ0 MR0 (MR07~MR00)

#### (アドレス[SR4~SR0]=00H)

図25に、モード・レジスタ0によって制御される様々な動作を示します。 このレジスタは読み書きが可能です。

#### MR0ビットの説明

#### 出力ビデオ標準の選択(MR01~MR00)

これらのビットを使ってエンコード・モードを設定します。 ADV7174/ADV7179は、NTSC、PAL (B/D/G/H/I)、PAL (MとN)の各標準のビデオ出力を設定できます。

#### 輝度信号フィルタ制御(MR02~MR04)

これらのビットを使って、選択する輝度信号フィルタを指定します。フィルタの選択は、PALまたはNTSCの選択とは無関係に行えます。

#### 色度信号フィルタの制御(MR05~MR07)

これらのビットを使って色度信号フィルタを選択します。CIFフィルタまたはQCIFフィルタの選択と一緒に、カットオフ周波数が0.65MHz、1.0MHz、1.3MHz、または2MHzのローパス・フィルタを選択することができます。

#### モード・レジスタ1 MR1 (MR17~MR10)

#### (アドレス(SR4~SR0)=01H)

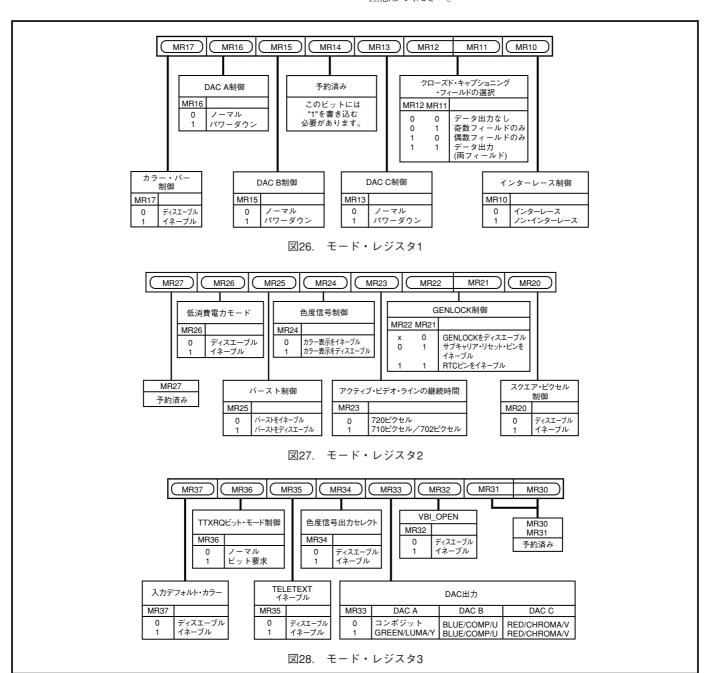

図26に、モード・レジスタ1によって制御される様々な動作を示します。 このレジスタは読み書きが可能です。

#### MR1ビットの説明

#### インターレースの制御(MR10)

このビットを使って、出力をインターレース・モードまたはノン・インターレース・モードに設定します。デバイスがコンポジット・ビデオ・モード時のみ、パワーダウン・モードが関係します。

#### クローズド・キャプショニング・フィールドの選択(MR12~MR11)

これらのビットを使って、クローズド・キャプショニング・データを表示するフィールドを制御します。クローズド・キャプショニング情報は、奇数フィールド、偶数フィールド、または両フィールドに表示することができます。

#### DACの制御(MR16~MR15およびMR13)

これらのビットを使ってDACをパワーダウンすることができます。アプリケーションで不要なDACがある場合に、パワーダウンを使ってADV7174/ADV7179の消費電力を削減することができます。

#### 予約済み(MR14)

このレジスタにはロジック"1"を書き込む必要があります。

#### カラー・バーの制御(MR17)

このビットを使って、内部カラー・バー・テスト・パターンの発生と出力を行うことができます。カラー・バーの設定は、NTSCの場合100/7.5/75/7.5、PALの場合100/0/75/0です。カラー・バーをイネーブルすると、ADV7174/ADV7179がマスター・タイミング・モードに設定されることに注意してください。

#### モード・レジスタ2 MR2 (MR27~MR20)

#### (アドレス[SR4~SR0]=02H)

モード・レジスタ2は8ビット幅のレジスタです。

図27に、モード・レジスタ2によって制御される様々な動作を示します。 このレジスタは読み書きが可能です。

#### MR2ビットの説明

#### スクエア・ピクセルの制御(MR20)

このビットを使って、スクエア・ピクセル・モードを設定します。スレーブ・モードでのみ使用可能です。NTSCの場合は、24.5454MHzのクロックを入力する必要があります。PALの場合は、29.5MHzのクロックを入力する必要があります。

#### Genlockの制御(MR22~MR21)

これらのビットは、ADV7174/ADV7179のgenlock機能を制御します。MR21をロジック・レベル"1"に設定すると、SCRESET/RTCピンは入力に設定されます。MR22をロジック・レベル"0"に設定すると、SCRESET/RTCピンはサブキャリア・リセット入力に設定されます。したがって、SCRESET/RTCピン上でローレベルからハイレベルへの変化があると、サブキャリアがフィールド0にリセットされます。MR22をロジック・レベル"1"に設定すると、SCRESET/RTCピンはリアルタイム制御入力に設定されます。

#### アクティブ・ビデオ・ライン継続時間(MR23)

このビットにより、2種類のアクティブ・ビデオ・ライン継続時間を切り替えます。"0"のときはCCIR REC601(720ピクセルPAL/NTSC)が選択され、"1"のときはITU-R.BT470標準のアクティブ・ビデオ継続時間(710ピクセル(NTSC)および702ピクセル(PAL))が選択されます。

#### 色度信号制御(MR24)

このビットを使って、ビデオ出力の色情報のONおよびOFFをイネーブルします。

#### バースト制御(MR25)

このビットを使って、ビデオ出力のバースト情報のONおよびOFFをイネーブルします。

#### 低消費電力モード(MR26)

このビットは、ADV7174/ADV7179の低消費電力モードをイネーブルします。この機能によりDAC電流が45%削減されます。

#### 予約済み(MR27)

このビットにはロジック"0"を書き込む必要があります。

#### モード・レジスタ3 MR3 (MR37~MR30)

#### (アドレス[SR4~SR0]=03H)

モード・レジスタ3は8ビット幅のレジスタです。

図28に、モード・レジスタ3によって制御される様々な動作を示します。

#### MR3ビットの説明

#### レビジョン・コード(MR30~MR31)

これらのビットは読み出し専用で、デバイスのレビジョンを表示します。

#### VBIオープン(MR32)

このビットで、垂直ブランキング・インターバル(VBI)内のデータをアナログ出力に出力するか、ブランクにするかを指定します。VBIデータの挿入は、スレーブ・モード0では使用できません。また、BLANK入力制御とVBIオープンが両方ともイネーブルされている場合は、BLANK入力制御の方が優先されます。すなわち、VBIデータの挿入は機能しません。

#### DAC出力(MR33)

このビットを使って、DAC出力をSCARTからEUROSCART設定へ切り替えます。すべてのDAC出力設定のリストを表Iに示します。

#### 色度信号出力の選択(MR34)

このアクティブ・ハイのビットを使うと、4番目のDACのコンポジット出力でYUVデータを、または4番目のDACに色度信号を出力することができます(0=CVBS; 1=色度信号)。

表I. DAC出力の設定マトリクス

| MR34 | MR40 | MR41 | MR33 | DAC A | DAC B | DAC C |

|------|------|------|------|-------|-------|-------|

| 0    | 0    | 0    | 0    | CVBS  | CVBS  | С     |

| 0    | 0    | 0    | 1    | Y     | CVBS  | C     |

| 0    | 0    | 1    | 0    | CVBS  | CVBS  | C     |

| 0    | 0    | 1    | 1    | Y     | CVBS  | C     |

| 0    | 1    | 0    | 0    | CVBS  | В     | R     |

| 0    | 1    | 0    | 1    | G     | В     | R     |

| 0    | 1    | 1    | 0    | CVBS  | U     | V     |

| 0    | 1    | 1    | 1    | Y     | U     | V     |

| 1    | 0    | 0    | 0    | C     | CVBS  | C     |

| 1    | 0    | 0    | 1    | Y     | CVBS  | C     |

| 1    | 0    | 1    | 0    | C     | CVBS  | C     |

| 1    | 0    | 1    | 1    | Y     | CVBS  | C     |

| 1    | 1    | 0    | 0    | C     | В     | R     |

| 1    | 1    | 0    | 1    | G     | В     | R     |

| 1    | 1    | 1    | 0    | C     | U     | V     |

| 1    | 1    | 1    | 1    | Y     | U     | V     |

CVBS:コンポジット・ビデオ・ベースバンド信号

Y:輝度コンポーネント信号(YUVまたはY/Cモード)

C: 色度信号(Y/Cモード)

U:色度コンポーネント信号(YUVモード)

V:色度コンポーネント信号(YUVモード)

R: REDコンポーネント・ビデオ(RGBモード)

G: GREENコンポーネント・ビデオ(RGBモード)

B: BLUEコンポーネント・ビデオ(RGBモード)

注

次の制御ビットを使って、各DACを個別にパワーオンまたはパワーオフすることができます(0=ON, 1=OFF)。

MR13—DAC C

MR15—DAC B

MR16—DAC A

#### Teletextイネーブル(MR35)

TTXピンでのTeletextデータの挿入をイネーブルするときは、このビットを"1"に設定します。

#### TTXREQビット・モード制御(MR36)

このビットは、連続ハイレベル信号(MR36=0)からビット幅の要求信号(MR36=1)へのTeletext要求信号の切り替えをイネーブルします。

#### 入力デフォルト・カラー(MR37)

このビットは、ゼロ入力ピクセル・データ(つまり非接続時)に対するDAC のデフォルト出力カラーを指定します。ロジック"0"を指定すると、00000000 に対応するカラーが表示されます。ロジック"1"を指定すると、00000000 ピクセル入力ビデオ・データに対して黒の出力カラーになります。

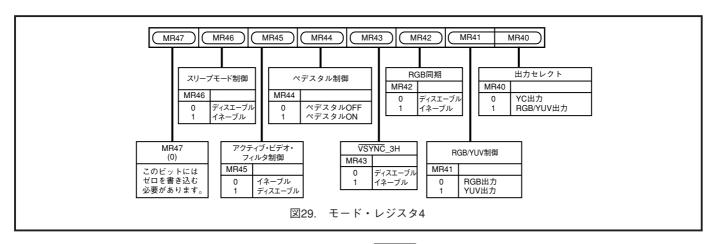

#### モード・レジスタ4 MR4 (MR47~MR40)

#### (アドレス(SR4~SR0)=04H)

モード・レジスタ4は8ビット幅のレジスタです。図29に、モード・レジスタ 4によって制御される様々な動作を示します。

#### MR4ビットの説明

#### 出力の選択(MR40)

このビットは、デバイスがコンポジット・ビデオ・モードまたはRGB/YUV モードのいずれになるかを指定します。RGB/YUVモードでは、コンポジット信号も使用可能であることに注意してください。

#### RGB/YUV制御(MR41)

このビットは、RGB DACの出力をYUV出力ビデオ標準に設定することをイネーブルします。

#### RGB同期(MR42)

このビットを使って、全RGB出力のエンコードした同期情報でRGB出力を設定します。

#### VSYNC\_3H (MR43)

スレーブ・モードでこのビットがイネーブル(1)されると、PALモードでは 2.5ライン間、NTSCモードでは3ライン間、VSYNCアクティブ・ロー入力を 駆動することが可能になります。マスター・モードでこのビットがイネーブル されると、ADV7174/ADV7179はNTSCモードでは3ライン間、PALモードでは2.5ライン間、アクティブ・ローVSYNC信号を出力します。

#### ペデスタル制御(MR44)

このビットは、NTSCコンポジット・ビデオ信号にペデスタルを発生するか否かを指定します。ADV7174/ADV7179がPALモードのときは、このビットは無効になります。

#### アクティブ・ビデオ・フィルタ制御(MR45)

このビットは、ラインのアクティブ・ビデオ部分の外側に使用するフィルタ・モードを制御します。このフィルタは、輝度信号フィルタの選択に関係なく同期信号の立ち上がりおよび立ち下がり時間が常に仕様を満たすようにします。ロジック"1"で、このモードがイネーブルされます。

#### スリープモード制御(MR46)

このビットをセット(1)すると、スリープモードがイネーブルされます。このモードがイネーブルされると、ADV7174/ADV7179の消費電力が200nA (typ値)に削減されます。ADV7174/ADV7179がスリープモードでも、PCレジスタは読み書き可能です。デバイスがスリープモード時に、MR46に"0"が設定されると、ADV7174/ADV7179はスリープモードから抜け出して、通常の動作を再開します。スリープモード中にRESET信号が入力されたときも、ADV7174/ADV7179はスリープモードから抜け出して、通常の動作を再開します。

#### 予約済み(MR47)

このビットにはロジック"0"を書き込む必要があります。

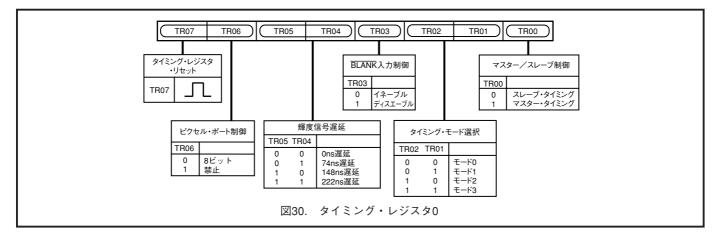

#### タイミング・モード・レジスタ0 (TR07~TR00)

#### (アドレス[SR4~SR0]=07H)

図30に、タイミング・レジスタ0によって制御される様々な動作を示します。このレジスタは読み書きが可能です。

#### TR0ビットの説明

#### マスター/スレーブ制御(TR00)

このビットは、ADV7174/ADV7179がマスター・モードまたはスレーブ・モードのいずれになるかを指定します。

#### タイミング・モード選択(TR02~TR01)

これらのビットは、ADV7174/ADV7179のタイミング・モードを制御します。これらのモードについては、「タイミング仕様」で詳しく説明します。

#### BLANK入力制御(TR03)

このビットは、デバイスがスレーブ・モードのとき、BLANK入力を使用 するか否かを指定します。

#### 輝度信号遅延(TR05~TR04)

これらのビットは、輝度信号遅延追加の有無を制御します。各ビットは、74nsの遅延を表します。

#### ピクセル・ポート制御(TR06)

このビットを使って、ピンP7~P0のピクセル・ポートで8ビット・データまたはYCrCbデータのいずれを入力するか指定します。

#### タイミング・レジスタ・リセット(TR07)

TR07をローからハイ、さらにローへ変化させる(トグルさせる)と、内部タイミング・カウンタがリセットされます。パワーアップ、リセット、または新しいタイミング・モードへの切り替え後にトグルする必要があります。

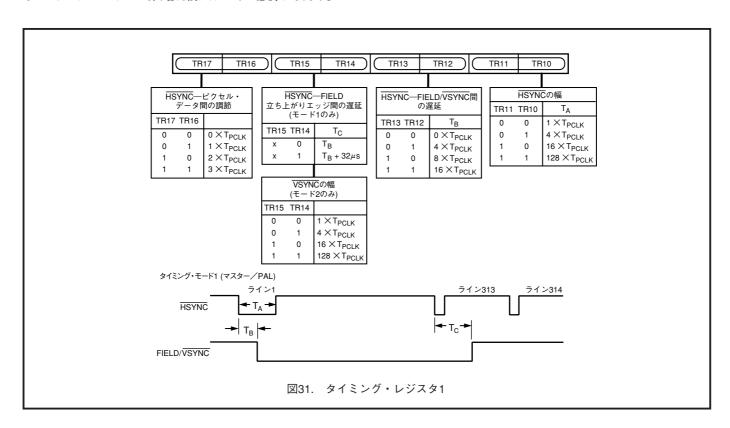

#### タイミング・モード・レジスタ1 (TR17~TR10)

(アドレス(SR4~SR0)=08H)

タイミング・レジスタ1は8ビット幅のレジスタです。

図31に、タイミング・レジスタ1によって制御される様々な動作を示します。このレジスタは読み書きが可能です。このレジスタを使って、マスター・モード・タイミング信号の幅と位置を調節することができます。

#### TR1ビットの説明

#### HSYNC幅(TR11~TR10)

これらのビットによりHSYNCパルス幅を調節します。

#### HSYNC-FIELD/VSYNC間の遅延(TR13~TR12)

これらのビットを使って、FIELD/VSYNC出力に対するHSYNC出力の位置を調節します。

#### HSYNC — FIELDの立ち上がりエッジ間の遅延(TR15~TR14)

ADV7174/ADV7179がタイミング・モード1のとき、これらのビットを使って、FIELD出力の立ち上がりエッジに対するHSYNC出力の位置を調節します。

#### VSYNC幅(TR15~TR14)

ADV7174/ADV7179がタイミング・モード2のとき、これらのビットを使ってVSYNCパルス幅を調節します。

#### HSYNC-ピクセル・データ間の調節(TR17~TR16)

ピクセル・データに対するHSYNCの位置の調節をイネーブルします。 この機能を使うと、CrコンポーネントとCbコンポーネントの交換が可能になります。この調整は、マスターおよびスレーブの両タイミング・モードで可能です。

### サブキャリア周波数レジスタ3~0 (FSC3~FSC0) (アドレス[SR4~SR0]=09H-0CH)

これらの8ビット幅レジスタを使ってサブキャリア周波数を設定します。これらのレジスタ値は、次式を使って計算します。

サブキャリア周波数レジスタ  $=\frac{2^{32}1}{F_{CLK}} \times F_{SCF}$

すなわち: NTSC モード,  $F_{CLK} = 27 \text{ MHz},$  $F_{SCF} = 3.5795454 \text{ MHz}$

サブキャリア周波数値 =  $\frac{2^{32} 1}{27 \times 10^6} \times 3.579545 \times 10^6$

#### = 21F07C16 HEX

図32に、4個のレジスタを使って周波数を設定する方法を示します。

#### サブキャリア・フェーズ・レジスタ(FP7~FP0) (アドレス[SR4~SR0]=0DH)

この8ビット幅レジスタを使って、サブキャリア・フェーズを設定します。各ビットは1.41°を表します。通常動作に対しては、このレジスタは00Hexに設定されます。

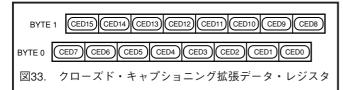

#### クローズド・キャプショニング偶数フィールド データ・レジスタ1~0 (CED15~CED0) (アドレス[SR4~SR0]=0E~0FH)

これらの8ビット幅レジスタを使って、偶数フィールド上のクローズド・キャプショニング拡張データ・バイトを設定します。図33に、レジスタ内での上位バイトと下位バイトの設定方法を示します。

#### クローズド・キャプショニング奇数フィールド データ・レジスタ1~0 (CCD15~CCD0) (サブアドレス[SR4~SR0]=10~11H)

これらの8ビット幅レジスタを使って、奇数フィールド上のクローズド・キャプショニング・データ・バイトを設定します。図34に、レジスタ内での上位バイトと下位バイトの設定方法を示します。

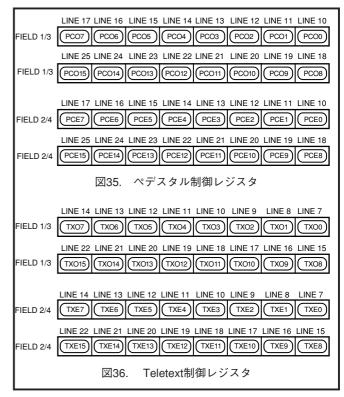

#### NTSCペデスタル/PAL TELETEXTの制御 レジスタ3~0 (PCE15~0、PCO15~0)/(TXE15~0、 TXO15~0)

#### (サブアドレス[SR4~SR0]=12~15H)

これらの8ビット幅レジスタを使って、奇数と偶数の両フィールドの垂直 ブランキングの合い間でライン毎にNTSCペデスタル/PAL Teletextを イネーブルします。図35と図36に4個の制御レジスタを示します。NTSCの 場合、これらのレジスタの任意のビットがロジック"1"のとき、対応するライン上でペデスタルをOFFにします。PALの場合、これらのレジスタの任意 のビットがロジック"1"のとき、対応するライン上でTeletextをONにします。

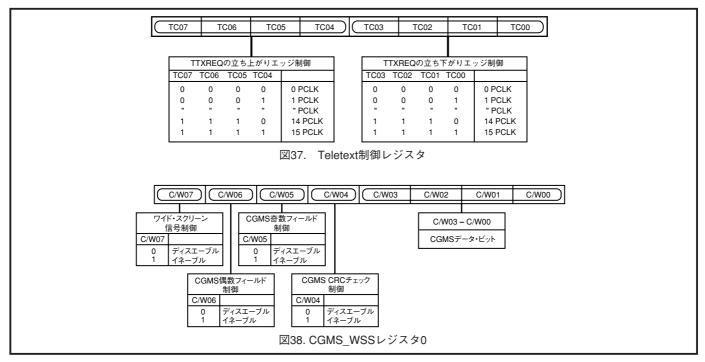

#### TELETEXT要求制御レジスタTC07 (TC07~TC00)

(アドレス[SR4~SR0]=19H)

Teletext制御レジスタは8ビット幅のレジスタです(図37)。

#### TTXREQ立ち上がりエッジ制御(TC07~TC04)

これらのビットは、TTXREQの立ち上がりエッジの位置を制御します。 ゼロ・クロック・サイクルから最大15クロック・サイクルまで設定することが できます(図37)。

#### TTXREQ立ち下がりエッジ制御(TC03~TC00)

これらのビットは、TTXREQの立ち下がりエッジの位置を制御します。ゼロ・クロック・サイクルから最大15クロック・サイクルまで設定することができます。Teletextデータに対しては、アクティブ・ウインドウを制御します。この値を増やすと、デフォルトの360より下のTeletextビット数が少なくなります。ビットTC07~TC04が変更されたときにビットTC03~TC00が00Hexの場合、TTXREQの立ち下がりエッジはTTXREQの立ち上がりエッジに追従します。すなわち、立ち下がりエッジと立ち上がりエッジの間隔は一定のままになります(図37)。

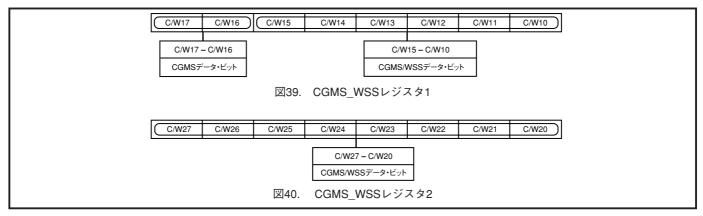

### CGMS\_WSSレジスタ0 C/W0 (C/W07~C/W00) (アドレス[SR4~SR0]=16H)

CGMS\_WSSレジスタ0は8ビット幅のレジスタです。図38に、このレジスタにより制御される動作を示します。

#### C/W0ビットの説明

#### CGMSデータ・ビット(C/W03~C/W00)

これらの4データ・ビットは、CGMSデータ出力ストリームの最後の4ビットです。これらのビット位置はCGMSデータだけであることに注意してください。すなわち、WSSデータはこの位置を使いません。

#### CGMS CRCチェックの制御(C/W04)

このビットがイネーブル(1)されると、CGMSデータの最後の6ビット(CRC チェック・シーケンス)は内部でADV7174/ADV7179により計算されます。このビットがディスエーブル(0)されると、レジスタ内のCRC値がCGMS データ・ストリームに出力されます。

#### CGMS奇数フィールド制御(C/W05)

このビットがセット(1)されると、CGMSが奇数フィールドに対してイネーブルされます。この機能は、NTSCモードでのみ有効であることに注意してください。

#### CGMS偶数フィールド制御(C/W06)

このビットがセット(1)されると、CGMSが偶数フィールドに対してイネーブルされます。この機能は、NTSCモードでのみ有効であることに注意してください。

#### WSS制御(C/W07)

このビットがセット(1)されると、ワイド・スクリーン・シグナリングがイネーブルされます。この機能は、PALモードでのみ有効であることに注意してください。

#### CGMS\_WSSレジスタ1 C/W1 (C/W17~C/W10)

(アドレス[SR4~SR0]=17H)

CGMS\_WSSレジスタ1は8ビット幅のレジスタです。図39に、このレジスタにより制御される動作を示します。

#### C/W1ビットの説明

#### CGMS/WSSデータ・ビット(C/W15~C/W10)

これらのビット位置は、CGMSデータとWSSデータで共用されます。 NTSCモードでは、これらのビットはCGMSデータになります。PALモードでは、これらのビットはWSSデータになります。

#### CGMSデータ・ビット(C/W17~C/W16)

これらのビットはCGMSデータ・ビット専用です。

#### CGMS\_WSSレジスタ2 C/W1 (C/W27 $\sim$ C/W20)

(アドレス[SR4~SR0]=18H)

CGMS\_WSSレジスタ2は8ビット幅のレジスタです。図40に、このレジスタにより制御される動作を示します。

#### C/W2ビットの説明

#### CGMS/WSSデータ・ビット(C/W27~C/W20)

これらのビット位置は、CGMSデータとWSSデータで共用されます。 NTSCモードでは、これらのビットはCGMSデータになります。PALモードでは、これらのビットはWSSデータになります。

26

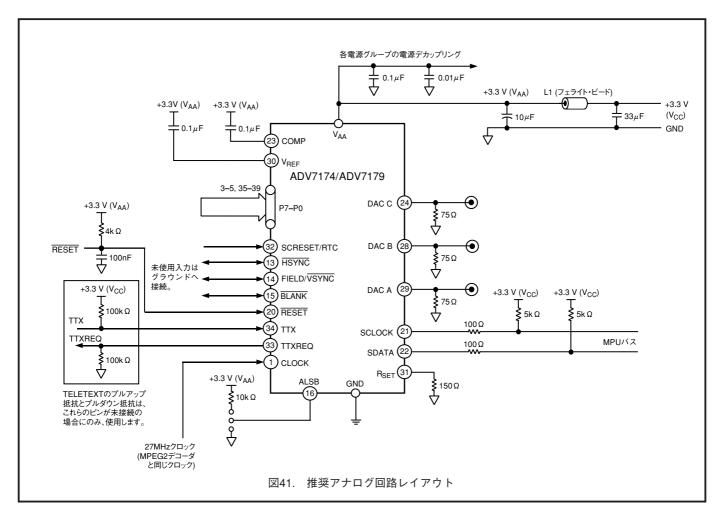

#### アペンディックス 1 ボードのデザインとレイアウトでの考慮事項

ADV7174/ADV7179は、高精度アナログ回路と高速デジタル回路を内蔵する高集積度の回路です。高速デジタル回路からアナログ回路への干渉を最小にするようにデザインされています。これと同じデザインとレイアウト技術をシステム・レベルのデザインにも適用して、高速かつ高精度の性能を達成するようにする必要があります。図41の推奨アナログ回路レイアウトに、デバイスとモニター間のアナログ・インターフェースを示します。

デジタル入力をシールドし、適切なデカップリングを使用することにより、ADV7174/ADV7179の電源ラインとグラウンド・ライン上のノイズを最小にするようにレイアウトを最適化する必要があります。VAAピン・グループとGNDピン・グループの間のリード長は最短にして、誘導性リンギングを最小化する必要があります。

#### グラウンド・プレーン

グラウンド・プレーンは、すべてのADV7174/ADV7179グラウンド・ピン、電圧リファレンス回路、ADV7174/ADV7179の電源バイパス回路、アナログ出力パターン、およびADV7174/ADV7179に接続されるすべてのデジタル信号パターンを覆う必要があります。グラウンド・プレーンはボードの共通グラウンド・プレーンになります。

#### 電源プレーン

ADV7174/ADV7179およびこれに接続されているすべてのアナログ回路は、アナログ電源プレーン $(V_{AA})$ を基準とするそれ自体の電源プレーンを持つ必要があります。この電源プレーンは必ず、フェライト・ビードを経由して1点で通常のPCB電源プレーン $(V_{CC})$ に接続します。このビードは、ADV7174/ADV7179から3インチ以内に配置する必要があります。

デバイスの電源プレーンとボードの電源プレーンを分離している金属ギャップは可能なかぎり狭くして、デバイスからボード全体への熱の流れを妨げないようにする必要があります。

PCB電源プレーンはPCボード上のすべてのデジタル・ロジックに電源を供給し、アナログ電源プレーンはすべてのADV7174/ADV7179電源ピンと電圧リファレンス回路に電源を供給する必要があります。

プレーン間のノイズ結合は、プレーン間ノイズが同相モードになるように配置できる限り、通常のPCB電源とグラウンド・プレーンの部分がアナログ電源プレーン部分と重ならないようにすることで減らすことができます。

#### 電源のデカップリング

最適性能を得るには、安定した動作が可能な限り最短のリード長でバイパス・コンデンサを接続し、リードのインダクタンスを小さくする必要があります。最適性能は、 $0.1\,\mu$  Fのセラミック・コンデンサによるデカップリングで得られます。ADV7174/ADV7179上の $V_{AA}$ ピンの各グループには、GNDへ接続した少なくとも1個の $0.1\,\mu$  Fのデカップリング・コンデンサが必要です。これらのコンデンサはできるだけデバイスの近くに配置します。

ADV7174/ADV7179は電源ノイズを除去する回路を内蔵していますが、この除去機能は周波数とともに減少することに注意することは重要です。高い周波数のスイッチング電源を使う場合、電源ノイズの削減に十分な注意を払い、アナログ電源プレーンへの電源に3ピン電圧レギュレータを使用することも検討してください。

#### デジタル信号の相互接続

ADV7174/ADV7179へのデジタル入力は、アナログ出力および、その他のアナログ回路からできるだけ離す必要があります。また、これらの入力信号はアナログ電源プレーンと重ならないようにする必要があります。

高いクロック・レートを使用しているので、ノイズの混入を避けるため、 ADV7174/ADV7179へのクロック・ラインは短くする必要があります。

デジタル入力のすべてのアクティブ終端抵抗は通常のPCB電源プレーン(Vcc)に接続し、アナログ電源プレーンには接続しないようにする必要があります。

#### アナログ信号の相互接続

ADV7174/ADV7179は出力コネクタのできるだけ近くに配置して、ノイズの混入とインピーダンス不整合による反射を小さくする必要があります。

ビデオ出力信号はグラウンド・プレーンに重なるように配置し、アナログ電源プレーンには重ならないようにして、高い周波数での電源除去比を大きくする必要があります。

デジタル入力(特にピクセル・データ入力信号とクロック信号)は、絶対にアナログ信号回路と重ならないように、できるだけ遠ざけて配置します。

最適性能を得るには、各出力はGNDに接続した75Ωの負荷抵抗を持つ必要があります。これらの抵抗はできるだけADV7174/ADV7179の近くに配置して、反射を小さくする必要があります。

ADV7174/ADV7179の入力はフローティングのままにしておくことはできません。未使用のすべての入力はグラウンドに接続しておく必要があります。

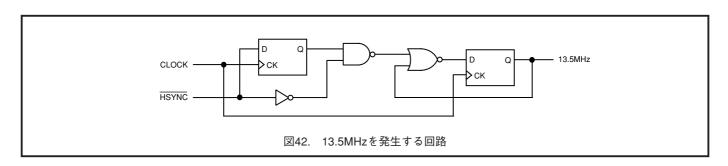

下に示す回路は、27MHzクロックとHSYNCパルスを使って13.5MHz 波形を発生する際に使うことができます。この波形から、27MHzクロックに同期した13.5MHzクロックを確実に発生することができます。MPEG

デコーダで13.5MHzクロックが必要な場合、この13.5MHzクロックを使うことができます。これにより、CrとCbのピクセル情報が正しいシーケンスでADV7174/ADV7179に入力されることが保証されます。

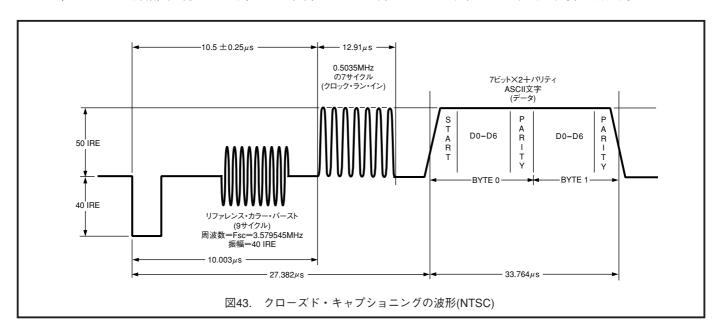

#### アペンディックス2 **クローズド・キャプショニング**

ADV7174/ADV7179は、カラー送信用の標準テレビ同期波形に準拠したクローズド・キャプショニングをサポートしています。クローズド・キャプショニングは、奇数フィールドのライン21と偶数フィールドのライン284のブランク・アクティブ・ライン区間で送信されます。

クローズド・キャプショニングは、キャプション・データに周波数ロックおよびフェーズロックした7サイクルの正弦波バーストで構成されています。クロック・ラン・イン信号の後、2データ・ビットの間、ブランキング・レベルが維持され、その後にロジック・レベル"1"のスタート・ビットが続きます。スタート・ビットの後ろには16ビットのデータが続きます。これらは、2個の8ビット・バイト、7ビットのデータ、1ビットの奇数パリティで構成されます。これらのバイトのデータは、クローズド・キャプショニング・データ・レジスタ0と1に格納されます。

ADV7174/ADV7179は拡張クローズド・キャプショニング動作もサポートしています。この機能は偶数フィールドでアクティブになり、スキャン・ライン284上にエンコードされています。この動作のデータはクローズド・キャプショニング拡張データ・レジスタ0と1に格納されます。

ライン21とライン284上でクローズド・キャプショニングをサポートする ためのすべてのクロック・ラン・イン信号とタイミングは、 ADV7174/ADV7179により自動的に発生されます。ライン21区間とライ ン284区間のすべてのピクセル入力は無視されます。FCC Code of Federal Regulations (CFR) 47 Section 15.119およびEIA-608により、ライン21とライン284に対するクローズド・キャプショニング情報が規定されています。

ADV7174/ADV7179はシングル・バッファリング方式を採用しています。これは、クローズド・キャプショニング・バッファの深さは1バイトであり、深さ2バイトの他のバッファリング・システムとは異なり、クローズド・キャプショニング・データの出力ではフレーム遅延が存在しないことを意味しています。データは、ライン21とライン284に出力される前、すなわち少なくとも1ライン前(ライン20またはライン283)にロードする必要があります。この方式の代表的な実施例としては、VSYNCを使ってマイクロプロセッサに割込んで、各フィールドで新しいデータ(2バイト)をロードする方法があります。送信する新しいデータがない場合は、両データ・レジスタにゼロをロードします。これは、NULLINGと呼ばれています。制御コードをロードすることも重要です。すべての制御コードはダブル・バイトでライン21に配置されており、TVはこれらを認識しません。"HelloWorld"のような奇数文字数のメッセージの場合、パッディングを行って偶数にして、キャプションの2バイト制御コードの終わりが同じフィールドに配置されるようにする必要があります。

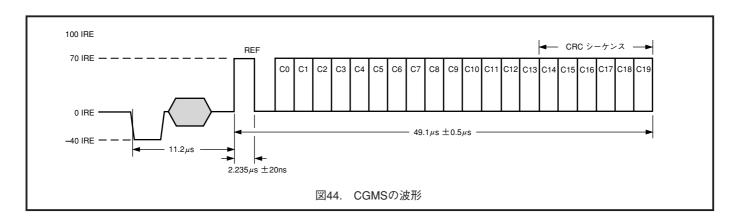

#### ァペンディックス3 コピー・ジェネレーション・マネジメント・システム(CGMS)

ADV7174/ADV7179は、標準に準拠したコピー・ジェネレーション・マネジメント・システム(CGMS)をサポートしています。CGMSデータは、奇数フィールドのライン20と偶数フィールドのライン283に送信されます。ビットC/W05とビットC/W06が、奇数フィールドと偶数フィールドにCGMSデータを出力するか否かを制御します。ADV7174/ADV7179がNTSCモードに設定された場合にのみCGMSデータを送信できます。CGMSデータは20ビット長であり、これらの各ビットの機能を下に示します。CGMSデータは、CGMSビットと同じ振幅と継続時間を持つリファレンス・パルスの後ろに続きます(図44)。これらのビットは、設定レジスタから次の順序で出力されます:C/W00=C16、C/W01=C17、C/W02=C18、C/W03=C19、C/W10=C8、C/W11=C9、C/W12=C10、

C/W13=C11、C/W14=C12、C/W15=C13、C/W16=C14、C/W17=C15、C/W20=C0、C/W21=C1、C/W22=C2、C/W23=C3、C/W24=C4、C/W25=C5、C/W26=C6、C/W27=C7。ビットC/W04がロジック"1"にセットされると、6ビットのCRCチェック・シーケンスを構成する最後の6ビット( $C19\sim C14$ )が、データ・レジスタ内のデータの下位14ビット( $C0\sim C13$ )に基づいてADV7174/ADV7179内で自動的に計算されて、その後残りの14ビットと一緒に20ビットのCGMSデータとして出力されます。CRCシーケンスの計算は、初期値=111111の多項式 $X^6+X+1$ に基づきます。C/W04がロジック"0"に設定されると、全20ビット( $C0\sim C19$ )がCGMSレジスタから直接出力されます(CRCは計算されないので、ユーザーが計算する必要があります)。

#### CGMSビットの機能

ワード0~6のビット

ワード1~4のビット

ワード2~6のビット

CRC-6ビットのCRC多項式=X<sup>6</sup>+X+1 (初期値111111)

ワード0 1 0

B1 アスペクト比 16:94:3

B2 表示フォーマット 文字ボックス 通常動作

B3 未定義

ワード0

B4、B5、B6 ビデオおよびその他の信号(例えば、オーディオ)についての識別情報

ワード1

B7、B8、B9、B10 ワード0と同時に発生する識別信号

ワード2

B11、B12、B13、B14 ワード0と同時に発生する識別信号と情報

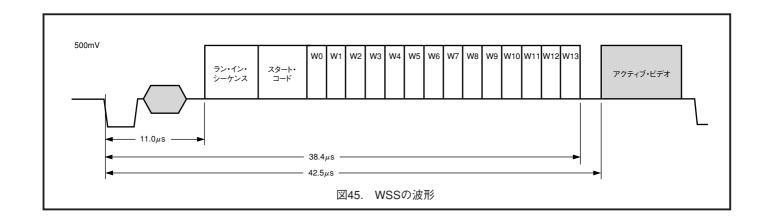

#### アペンディックス4 **ワイド・スクリーン・シグナリング**

ADV7174/ADV7179は、標準に準拠したワイド・スクリーン・シグナリング(WSS)をサポートしています。WSSデータは、ライン23で送信されます。ADV7174/ADV7179がPALモードに設定された場合にのみ、WSSデータを送信することができます。WSSデータは14ビット長であり、これらの各ビットの機能を下に示します。WSSデータは、ラン・イン・シーケンスとスタート・コードの後ろに続きます(図45)。これらのビットは、設定レジスタから次の順序で出力されます:C/W20=W0、C/W21=

W1、C/W22=W2、C/W23=W3、C/W24=W4、C/W25=W5、C/W26=W6、C/W27=W7、C/W10=W8、C/W11=W9、C/W12=W10、C/W13=W11、C/W14=W12、C/W15=W13。ビットC/W07がロジック"1"に設定されると、WSSデータのライン23での送信がイネーブルされます。ライン23の後ろの部分( $\overline{\text{HSYNC}}$ の立ち下がりエッジから42.5 $\mu$ s)は、ビデオの挿入に使うことができます。

#### CGMSビットの機能

ビット0~ビット2 アスペクト比/フォーマット/位置 ビット3は、ビット0~ビット2の奇数パリティ・チェック

| B0 | B1 | B2 | B3 | アスペクト比 | フォーマット    | 位置 |

|----|----|----|----|--------|-----------|----|

| 0  | 0  | 0  | 1  | 4:3    | フル・フォーマット | _  |

| 1  | 0  | 0  | 0  | 14:9   | 文字ボックス    | 中央 |

| 0  | 1  | 0  | 0  | 14:9   | 文字ボックス    | 上部 |

| 1  | 1  | 0  | 1  | 16:9   | 文字ボックス    | 中央 |

| 0  | 0  | 1  | 0  | 16:9   | 文字ボックス    | 上部 |

| 1  | 0  | 1  | 1  | >16:9  | 文字ボックス    | 中央 |

| 0  | 1  | 1  | 1  | 14:9   | フル・フォーマット | 中央 |

| 1  | 1  | 1  | 0  | 16:9   | _         |    |

B4 B9 B10 オープン・サブタイトルなし カメラ・モード 0 0 0 アクティブ・イメージ領域内のサブタイトル フィルム・モード 1 0 1 0 アクティブ・イメージ領域外のサブタイトル **B5** 1 標準コーディング 0 予約済み 1 B11 Motion Adaptive Color Plus 1 サラウンド・サウンド情報なし B6 0 ヘルパーなし サラウンド・サウンド・モード 0 1 変調済みヘルパー 1 予約済み B12 予約済み **B**7 予約済み B13

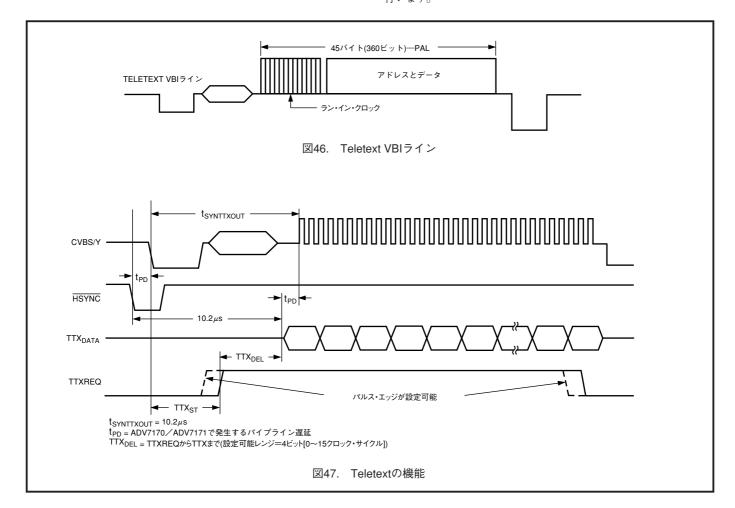

#### アペンディックス5 TELETEXTの挿入

$t_{PD}$ は、ADV7174/ADV7179がTTXの入力データを補間し、水平信号の前縁エッジから $t_{SYNTTXOUT}$ =10.2 $\mu$ s後に表示されるように、CVBS出力またはY出力に挿入する際に必要とする時間です。時間TTXDELは信号源でのパイプライン遅延時間であり、TTXデータを送信するためにTTXREQ信号によりゲーティングされます。

TTXREQ信号の立ち上がり/立ち下がりエッジの選択が可能なため、TTXデータは常に水平同期パルスの前縁エッジから $10.2\,\mu$  s後の正しい位置に挿入されるので、ソースが可変パイプライン遅延とのインターフェースが可能です。

TTXREQ信号幅は、常に6.9375Mビット/秒のテキスト・データ・レートで360(Teletext標準PAL-WSTに準拠するため)のTeletextビットを挿入できるように維持する必要があります。TC03~TC00をゼロに設定すると実現できます。Teletextイネーブル・ビット(MR35)がゼロに設定されると、挿入ウインドウは開かれません。

#### Teletextプロトコル

50HzでのTTXビット・クロック(6.9375MHz)とシステム・クロック(27MHz)の関係は、次のようになります。

$$(27 \text{ MHz } /4) = 6.75 \text{ MHz}$$

$(6.9375 \times 10^6 / 6.75 \times 10^6) = 1.027777$

したがって、37ビットのTTXは144クロック(27MHz)に対応し、各ビットはほぼ4クロック・サイクルの幅を持ちます。ADV7174/ADV7179は内部シーケンサと可変フェーズ補間フィルタを使ってフェーズジッタを最小に抑え、CVBS出力とY出力に出力可能な帯域制限した信号を発生します。

TTX入力では、ビット継続時間スキームが37 TTXビット毎すなわち 144クロック・サイクル毎に繰り返されます。プロトコルでは、TTXビット 10、19、28、37は3クロック・サイクルで、他のすべてのビットは4クロック・サイクルで送信することが必要です。37個のTTXビットの後の、次の3クロック・サイクルのビットは47、56、65、74です。この方式では、360個の全TTXビットの送信が終わるまで、次の37個のTTXビットの全サイクルが保持されます。すべてのTeletextラインは同じ方法で構成されます。Teletextラインの個別制御はTeletext設定レジスタを使って行います。

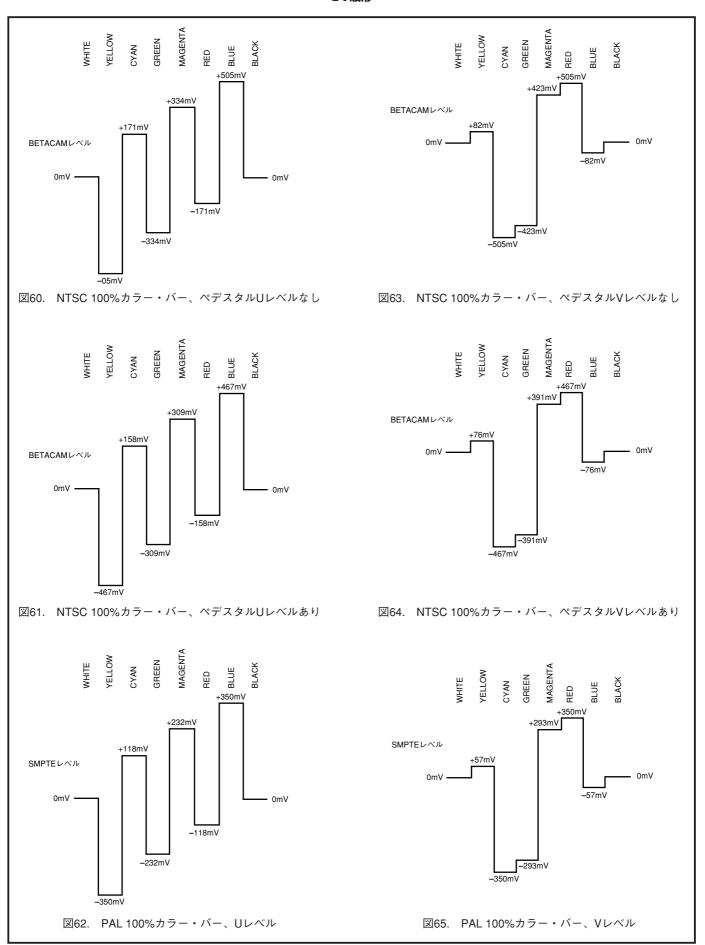

#### ァペンディックス6 NTSC波形(ペデスタルあり)

#### NTSC波形(ペデスタルなし)

#### PAL波形

#### UV波形

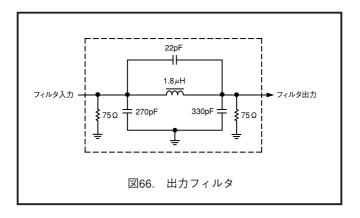

#### アペンディックス7 **オプションの出力フィルタ**

ADV7174/ADV7179のCVBS、Y、UV、色信号およびRGBの出力に出力フィルタが必要な場合には、図66に示すフィルタを使うことができます。図67にフィルタの特性を示します。ADV7174/ADV7179の出力をアナログ・モニターまたはアナログTVに接続する際は、多くの

場合、出力フィルタは不要です。ただし、サンプリングを行うシステム (例えば、デジタルTV)に出力信号を接続する場合は、折り返しノイズ を防ぐためフィルタが必要です。

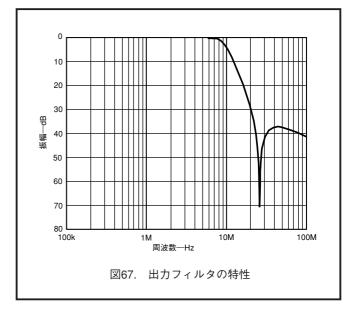

#### ァペンディックス8 オプションのDACバッファ

ADV7174/ADV7179のDAC出力に外付けバッファが必要な場合には、図68に示す構成が推奨されます。この構成では、DAC出力は最大電流(36mA)の半分(18mA)で動作します。この構成を使うと、ADV7174/ADV7179の消費電力を減らすことができ、 $R_{SET}$ =300 $\Omega$ 、 $R_{LOAD}$ =75 $\Omega$ でアナログ電流を50%削減することができます。3.3Vの $V_{AA}$ で18mAのDAC出力から最適性能を得ることができるので、3.3V動作にはこのモードが推奨されます。このバッファはビデオ出力に絶縁機能も追加します(図69のバッファ回路参照)。

絶対出力フル・スケール電流および電圧を計算するときは、次式を 使います。

$$\begin{split} &V_{\text{OUT}} = I_{\text{OUT}} \times R_{\text{LOAD}} \\ &I_{\text{OUT}} = \frac{(V_{\text{REF}} \times K)}{R_{\text{SET}}} \\ &K = 4.2146 \ \vec{\Xi}, \ V_{\text{REF}} = 1.235 \ V \end{split}$$

データ

#### アペンディックス9 レジスタの推奨値

ADV7174/ADV7179のレジスタは、ユーザーが必要な標準に応じて 設定することができます。

以下に、幾つかのビデオ標準に対する様々なレジスタ・フォーマットを 示します。

各ケースでは、すべてのDACをパワーアップし、かつBLANK入力制 御をディスエーブルして、出力をコンポジット出力に設定しています。さ らに、バーストおよびカラー情報を出力でイネーブルし、内部カラー・バ ー・ジェネレータはOFFに設定してあります。下の例では、スレーブ・フォ ーマットでタイミング・モードはモード0に設定してあります。タイミング・レ ジスタ0のTR02~TR00がタイミング・モードを制御します。 コマンド・レ ジスタの各ビットの詳細は、このデータシートの「レジスタ設定 |を参照し てください。新しいタイミング・モードを設定した後には、TR07をトグル する必要があります。タイミング・レジスタ1を使うと、タイミング信号の位 置と継続時間をさらに細かく制御できます。下の例では、このレジスタ はデフォルト・モードに設定してあります。

#### PAL B/D/G/H/I (F<sub>SC</sub>=4.43361875MHz)

| アドレ   | Z                     | データ   |

|-------|-----------------------|-------|

| 00Hex | モード・レジスタ0             | 05Hex |

| 01Hex | モード・レジスタ1             | 10Hex |

| 02Hex | モード・レジスタ2             | 00Hex |

| 03Hex | モード・レジスタ3             | 00Hex |

| 04Hex | モード・レジスタ4             | 00Hex |

| 07Hex | タイミング・レジスタ0           | 00Hex |

| 08Hex | タイミング・レジスタ1           | 00Hex |

| 09Hex | サブキャリア周波数レジスタ0        | CBHex |

| 0AHex | サブキャリア周波数レジスタ1        | 8AHex |

| 0BHex | サブキャリア周波数レジスタ2        | 09Hex |

| 0CHex | サブキャリア周波数レジスタ3        | 2AHex |

| 0DHex | サブキャリア・フェーズ・レジスタ      | 00Hex |

| 0EHex | クローズド・キャプショニング拡張レジスタ0 | 00Hex |

| 0FHex | クローズド・キャプショニング拡張レジスタ1 | 00Hex |

| 10Hex | クローズド・キャプショニング・レジスタ0  | 00Hex |

| 11Hex | クローズド・キャプショニング・レジスタ1  | 00Hex |

| 12Hex | ペデスタル制御レジスタ0          | 00Hex |

| 13Hex | ペデスタル制御レジスタ1          | 00Hex |

| 14Hex | ペデスタル制御レジスタ2          | 00Hex |

| 15Hex | ペデスタル制御レジスタ3          | 00Hex |

| 16Hex | CGMS_WSSレジスタ0         | 00Hex |

| 17Hex | CGMS_WSSレジスタ1         | 00Hex |

| 18Hex | CGMS_WSSレジスタ2         | 00Hex |

| 19Hex | Teletext要求制御レジスタ      | 00Hex |

| 0FHex | クローズド・キャプショニング拡張レジスタ1 | 00Hex |

| 10Hex | クローズド・キャプショニング・レジスタ0  | 00Hex |

| 11Hex | クローズド・キャプショニング・レジスタ1  | 00Hex |

| 12Hex | ペデスタル制御レジスタ0          | 00Hex |

| 13Hex | ペデスタル制御レジスタ1          | 00Hex |

| 14Hex | ペデスタル制御レジスタ2          | 00Hex |

| 15Hex | ペデスタル制御レジスタ3          | 00Hex |

| 16Hex | CGMS_WSSレジスタ0         | 00Hex |

| 17Hex | CGMS_WSSレジスタ1         | 00Hex |

| 18Hex | CGMS_WSSレジスタ2         | 00Hex |

| 19Hex | Teletext要求制御レジスタ      | 00Hex |

#### PAL N (F<sub>SC</sub>=4.43361875MHz)

|       | (1.30 11.1000101)     |       |

|-------|-----------------------|-------|

| アドレ   | ス                     | データ   |

| 00Hex | モード・レジスタ0             | 05Hex |

| 01Hex | モード・レジスタ1             | 10Hex |

| 02Hex | モード・レジスタ2             | 00Hex |

| 03Hex | モード・レジスタ3             | 00Hex |

| 04Hex | モード・レジスタ4             | 00Hex |

| 07Hex | タイミング・レジスタ0           | 00Hex |

| 08Hex | タイミング・レジスタ1           | 00Hex |

| 09Hex | サブキャリア周波数レジスタ0        | CBHex |

| 0AHex | サブキャリア周波数レジスタ1        | 8AHex |

| 0BHex | サブキャリア周波数レジスタ2        | 09Hex |

| 0CHex | サブキャリア周波数レジスタ3        | 2AHex |

| 0DHex | サブキャリア・フェーズ・レジスタ      | 00Hex |

| 0EHex | クローズド・キャプショニング拡張レジスタ0 | 00Hex |

| 0FHex | クローズド・キャプショニング拡張レジスタ1 | 00Hex |

| 10Hex | クローズド・キャプショニング・レジスタ0  | 00Hex |

| 11Hex | クローズド・キャプショニング・レジスタ1  | 00Hex |

| 12Hex | ペデスタル制御レジスタ0          | 00Hex |

| 13Hex | ペデスタル制御レジスタ1          | 00Hex |

| 14Hex | ペデスタル制御レジスタ2          | 00Hex |

| 15Hex | ペデスタル制御レジスタ3          | 00Hex |

| 16Hex | CGMS_WSSレジスタ0         | 00Hex |

| 17Hex | CGMS_WSSレジスタ1         | 00Hex |

| 18Hex | CGMS_WSSレジスタ2         | 00Hex |

| 19Hex | Teletext要求制御レジスタ      | 00Hex |

|       |                       |       |

#### PAL-60 (F<sub>SC</sub>=4.43361875MHz)

| アドレス  |                       | データ   |

|-------|-----------------------|-------|

| 00Hex | モード・レジスタ0             | 04Hex |

| 01Hex | モード・レジスタ1             | 10Hex |

| 02Hex | モード・レジスタ2             | 00Hex |

| 03Hex | モード・レジスタ3             | 00Hex |

| 04Hex | モード・レジスタ4             | 00Hex |

| 07Hex | タイミング・レジスタ0           | 00Hex |

| 08Hex | タイミング・レジスタ1           | 00Hex |

| 09Hex | サブキャリア周波数レジスタ0        | CBHex |

| 0AHex | サブキャリア周波数レジスタ1        | 8AHex |

| 0BHex | サブキャリア周波数レジスタ2        | 09Hex |

| 0CHex | サブキャリア周波数レジスタ3        | 2AHex |

| 0DHex | サブキャリア・フェーズ・レジスタ      | 00Hex |

| 0EHex | クローズド・キャプショニング拡張レジスタ0 | 00Hex |

| 0FHex | クローズド・キャプショニング拡張レジスタ1 | 00Hex |

| 10Hex | クローズド・キャプショニング・レジスタ0  | 00Hex |

| 11Hex | クローズド・キャプショニング・レジスタ1  | 00Hex |

| 12Hex | ペデスタル制御レジスタ0          | 00Hex |

| 13Hex | ペデスタル制御レジスタ1          | 00Hex |

#### PAL-60 (続き) (F<sub>SC</sub>=4.43361875MHz)

| アドレス  |                  | データ   |

|-------|------------------|-------|

| 14Hex | ペデスタル制御レジスタ2     | 00Hex |

| 15Hex | ペデスタル制御レジスタ3     | 00Hex |

| 16Hex | CGMS_WSSレジスタ0    | 00Hex |

| 17Hex | CGMS_WSSレジスタ1    | 00Hex |

| 18Hex | CGMS_WSSレジスタ2    | 00Hex |

| 19Hex | Teletext要求制御レジスタ | 00Hex |

#### パワーアップ・リセット値

#### NTSC (F<sub>sc</sub>=3.5795454MHz)

| MISC ( | $(F_{SC}=3.5795454WHZ)$ |       |

|--------|-------------------------|-------|

| アドレス   |                         | データ   |

| 00Hex  | モード・レジスタ0               | 00Hex |

| 01Hex  | モード・レジスタ1               | 10Hex |

| 02Hex  | モード・レジスタ2               | 00Hex |

| 03Hex  | モード・レジスタ3               | 00Hex |

| 04Hex  | モード・レジスタ4               | 10Hex |

| 07Hex  | タイミング・レジスタ0             | 00Hex |

| 08Hex  | タイミング・レジスタ1             | 00Hex |

| 09Hex  | サブキャリア周波数レジスタ0          | 16Hex |

| 0AHex  | サブキャリア周波数レジスタ1          | 7CHex |

| 0BHex  | サブキャリア周波数レジスタ2          | F0Hex |

| 0CHex  | サブキャリア周波数レジスタ3          | 21Hex |

| 0DHex  | サブキャリア・フェーズ・レジスタ        | 00Hex |

| 0EHex  | クローズド・キャプショニング拡張レジスタ0   | 00Hex |

| 0FHex  | クローズド・キャプショニング拡張レジスタ1   | 00Hex |

| 10Hex  | クローズド・キャプショニング・レジスタ0    | 00Hex |

| 11Hex  | クローズド・キャプショニング・レジスタ1    | 00Hex |

| 12Hex  | ペデスタル制御レジスタ0            | 00Hex |

| 13Hex  | ペデスタル制御レジスタ1            | 00Hex |

| 14Hex  | ペデスタル制御レジスタ2            | 00Hex |

| 15Hex  | ペデスタル制御レジスタ3            | 00Hex |

| 16Hex  | CGMS_WSSレジスタ0           | 00Hex |

| 17Hex  | CGMS_WSSレジスタ1           | 00Hex |

| 18Hex  | CGMS_WSSレジスタ2           | 00Hex |

| 19Hex  | Teletext要求制御レジスタ        | 00Hex |

|        |                         |       |

#### 外形寸法 40ピン・フレーム・チップ・スケール・パッケージ[LFCSP] (CP-40) 寸法表示: mm 6.00 BSC SQ 4.25 3.70 1.75 5.75 BSC SQ 上面図 裏面図 0.50 0.40 4.50 REF 12° MAX → / <del>-</del> 0.70 MAX 0.65 NOM 0.05 MAX 0.02 NOM 1.00 0.90 0.80 - 0.30 0.23 0.18 平坦性 0.08 L<sub>0.25</sub> REF JEDEC標準MO-220-VJJD-2に準拠

REV.0

# ADV7174/ADV7179