### 概要

低電力、高速、シリアル出力、10ビット、アナログ-ディジタルコンバータ(ADC)のMAX1072/MAX1075は、最高1.8Mspsで動作します。これらの製品は、真の差動入力を特長としており、シングルエンド入力に比べて、より高いノイズ耐性、歪みの改善、および広いダイナミックレンジを提供します。変換に必要なクロックは標準のSPI™/QSPI™/MICROWIRE™インタフェースが供給します。これらの製品は、ディジタル信号プロセッサ(DSP)の標準の同期シリアルインタフェースと容易に接続することができます。

MAX1072/MAX1075は、 $+4.75V\sim+5.25V$ の単一電源で動作し、外部リファレンスを必要とします。MAX1072はユニポーラアナログ入力で動作し、MAX1075はバイポーラアナログ入力を可能とします。これらの製品は、変換と変換の間での一時的パワーダウンモードと完全パワーダウンモードがあり、消費電流がそれぞれ1mA(typ)と1 $\mu$ A(max)に低減されます。さらに、もう1つの特長は、 $+1.8V\sim V_{DD}$ のディジタルロジックに直接接続可能な独立の電源入力( $V_L$ )を備えていることです。高速変換、低消費電力、優れたAC性能、およびDC精度( $\pm$ 0.5 LSB INL)を備えたMAX1072/MAX1075は、産業用プロセス制御、モータ制御、および基地局の各アプリケーションに最適です。

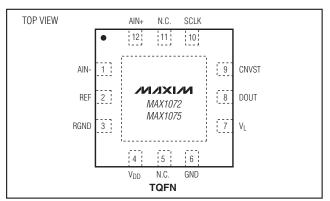

MAX1072/MAX1075は、12ピンTQFNパッケージで提供され、拡張(-40° $\sim+85$ °)温度範囲で使用することができます。

### アプリケーション \_\_\_\_\_

データ収集

紙幣鑑定

モータ制御

通信

携帯機器

# ピン配置

SPI/QSPIはMotorola, Inc.の商標です。 MICROWIREはNational Semiconductor Corp.の商標です。

#### 特長

- ◆ サンプリング速度: 1.8Msps

- ◆ 消費電力: わずか45mW (typ)

- ◆ シャットダウン電流:わずか1µA (max)

- ♦ 高速、SPI対応の3線シリアルインタフェース

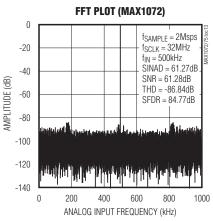

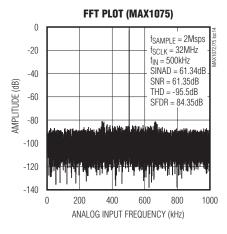

- ◆ S/(N + D): 61dB (入力周波数525kHzにおいて)

- ◆ 真の差動トラック/ホールド(T/H)内蔵

- ♦ 外部リファレンス

- ♦ パイプライン遅延なし

- ◆ 小型12ピンTQFNパッケージ

### 型番

| PART         | PART TEMP RANGE PIN-<br>PACKAGE |         | INPUT    |  |

|--------------|---------------------------------|---------|----------|--|

| MAX1072ETC+T | -40°C to +85°C                  | 12 TQFN | Unipolar |  |

| MAX1075ETC+T | -40°C to +85°C                  | 12 TQFN | Bipolar  |  |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。 T = テープ&リール

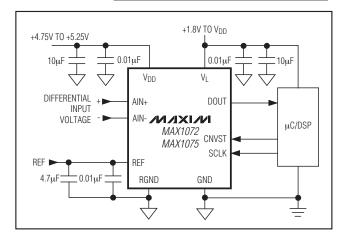

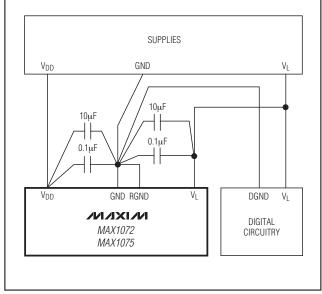

### 標準動作回路

#### MIXIM

Maxim Integrated Products 1

1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +6V<br>V <sub>L</sub> to GND0.3V to the lower of (V <sub>DD</sub> + 0.3V) or +6V | Maximum Current into Any Pin                     |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Digital Inputs                                                                                                 | 12-Pin TQFN (derate 16.9mW/°C above +70°C)1349mW |

| to GND0.3V to the lower of (V <sub>DD</sub> + 0.3V) or +6V                                                     | Operating Temperature Range                      |

| Digital Output                                                                                                 | MAX107_ ETC40°C to +85°C                         |

| to GND0.3V to the lower of $(V_L + 0.3V)$ or +6V                                                               | Junction Temperature+150°C                       |

| Analog Inputs and                                                                                              | Storage Temperature Range60°C to +150°C          |

| REF to GND0.3V to the lower of $(V_{DD} + 0.3V)$ or +6V                                                        | Lead Temperature (soldering, 10s)+300°C          |

| RGND to GND0.3V to +0.3V                                                                                       |                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V \pm 5\%, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, 50\%$  duty cycle,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                               | SYMBOL       | CONDITIONS                                                     | MIN     | TYP | MAX   | UNITS  |

|-----------------------------------------|--------------|----------------------------------------------------------------|---------|-----|-------|--------|

| DC ACCURACY                             | •            |                                                                | •       |     |       |        |

| Resolution                              |              |                                                                | 10      |     |       | Bits   |

| Relative Accuracy                       | INL          | (Note 1)                                                       |         |     | ±0.5  | LSB    |

| Differential Nonlinearity               | DNL          | (Note 2)                                                       |         |     | ±0.5  | LSB    |

| Offset Error                            |              |                                                                |         |     | ±2    | LSB    |

| Offset-Error Temperature<br>Coefficient |              |                                                                |         | ±1  |       | ppm/°C |

| Gain Error                              |              | Offset nulled                                                  |         |     | ±2    | LSB    |

| Gain Temperature Coefficient            |              |                                                                |         | ±2  |       | ppm/°C |

| DYNAMIC SPECIFICATIONS (fin             | = 525kHz sir | ne wave, V <sub>IN</sub> = V <sub>REF</sub> , unless otherwise | noted.) |     |       |        |

| Signal-to-Noise Plus Distortion         | SINAD        |                                                                | 60      | 61  |       | dB     |

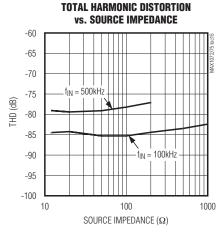

| Total Harmonic Distortion               | THD          |                                                                |         | -80 | -74   | dB     |

| Spurious-Free Dynamic Range             | SFDR         |                                                                |         | -80 | -74   | dB     |

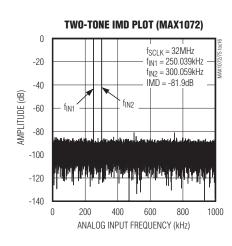

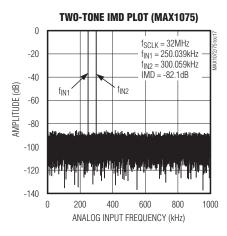

| Intermodulation Distortion              | IMD          | f <sub>IN1</sub> = 250kHz, f <sub>IN2</sub> = 300kHz           |         | -78 |       | dB     |

| Full-Power Bandwidth                    |              | -3dB point, small-signal method                                |         | 20  |       | MHz    |

| Full-Linear Bandwidth                   |              | S/(N + D) > 56dB, single ended                                 |         | 2   |       | MHz    |

| CONVERSION RATE                         |              |                                                                |         |     |       |        |

| Minimum Conversion Time                 | tconv        | (Note 3)                                                       |         |     | 0.556 | μs     |

| Maximum Throughput Rate                 |              |                                                                | 1.8     |     |       | Msps   |

| Minimum Throughput Rate                 |              | (Note 4)                                                       | 10      |     |       | ksps   |

| Track-and-Hold Acquisition Time         | tACQ         | (Note 5)                                                       |         | 104 |       | ns     |

| Aperture Delay                          |              |                                                                |         | 5   |       | ns     |

| Aperture Jitter                         |              | (Note 6)                                                       |         | 30  |       | ps     |

| External Clock Frequency                | fsclk        |                                                                |         |     | 28.8  | MHz    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +5V \pm 5\%, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, 50\%$  duty cycle,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                             | SYMBOL           | CONDITIONS                                     | MIN                   | TYP  | MAX                       | UNITS |

|---------------------------------------|------------------|------------------------------------------------|-----------------------|------|---------------------------|-------|

| ANALOG INPUTS (AIN+, AIN-)            |                  |                                                |                       |      |                           |       |

| Differential Input Voltage Range      | \/               | AIN+ - AIN-, MAX1072                           | 0                     |      | V <sub>REF</sub>          | V     |

|                                       | VIN              | AIN+ - AIN-, MAX1075                           | -V <sub>REF</sub> /2  |      | +V <sub>REF</sub> /2      | V     |

| Absolute Input Voltage Range          |                  |                                                | 0                     |      | $V_{DD}$                  | V     |

| DC Leakage Current                    |                  |                                                |                       |      | ±1                        | μΑ    |

| Input Capacitance                     |                  | Per input pin                                  |                       | 20   |                           | рF    |

| Input Current (Average)               |                  | Time averaged at maximum throughput rate       |                       | 75   |                           | μΑ    |

| REFERENCE INPUT (REF)                 |                  |                                                |                       |      |                           |       |

| REF Input Voltage Range               | V <sub>REF</sub> |                                                | 1.0                   |      | V <sub>DD</sub> +<br>50mV | V     |

| Input Capacitance                     |                  |                                                |                       | 20   |                           | рF    |

| DC Leakage Current                    |                  |                                                |                       |      | ±1                        | μΑ    |

| Input Current (Average)               |                  | Time averaged at maximum throughput rate       |                       | 400  |                           | μΑ    |

| DIGITAL INPUTS (SCLK, CNVST           | )                |                                                |                       |      | •                         |       |

| Input Voltage Low                     | V <sub>IL</sub>  |                                                |                       |      | 0.3 x V <sub>L</sub>      | V     |

| Input Voltage High                    | VIH              |                                                | 0.7 x V <sub>L</sub>  |      |                           | V     |

| Input Leakage Current                 | lıL              |                                                |                       | 0.05 | ±10                       | μΑ    |

| DIGITAL OUTPUT (DOUT)                 | •                |                                                |                       |      | •                         |       |

| Output Load Capacitance               | Соит             | For stated timing performance                  |                       |      | 30                        | рF    |

| Output Voltage Low                    | V <sub>OL</sub>  | I <sub>SINK</sub> = 5mA, V <sub>L</sub> ≥ 1.8V |                       |      | 0.4                       | V     |

| Output Voltage High                   | VoH              | ISOURCE = 1mA, V <sub>L</sub> ≥ 1.8V           | V <sub>L</sub> - 0.5V |      |                           | V     |

| Output Leakage Current                | loL              | Output high impedance                          |                       | ±0.2 | ±10                       | μΑ    |

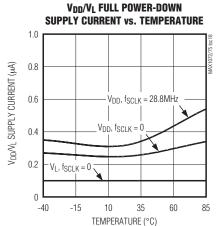

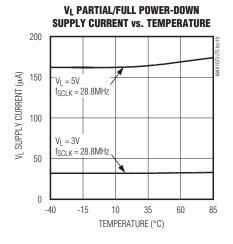

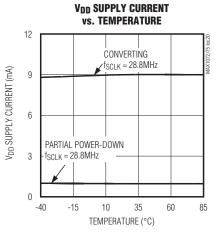

| POWER REQUIREMENTS                    |                  |                                                |                       |      |                           |       |

| Analog Supply Voltage                 | V <sub>DD</sub>  |                                                | 4.75                  |      | 5.25                      | V     |

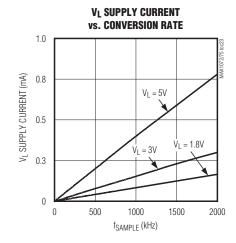

| Digital Supply Voltage                | VL               |                                                | 1.8                   |      | $V_{DD}$                  | V     |

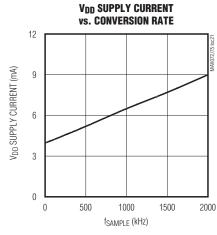

|                                       |                  | Static, fSCLK = 28.8MHz                        |                       | 7    | 9                         |       |

| Analog Supply Current,<br>Normal Mode | I <sub>DD</sub>  | Static, no SCLK                                |                       | 4    | 5                         | mA    |

| Normal Wode                           |                  | Operational, 1.8Msps                           |                       | 9    | 11                        |       |

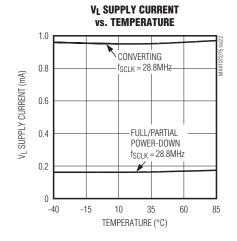

| Analog Supply Current,                | laa              | fSCLK = 28.8MHz                                |                       | 1    |                           | m ^   |

| Partial Power-Down Mode               | IDD              | No SCLK                                        |                       | 1    |                           | mA    |

| Analog Supply Current,                | laa              | f <sub>SCLK</sub> = 28.8MHz                    |                       | 1    |                           |       |

| Full Power-Down Mode                  | IDD              | No SCLK                                        |                       |      | 1                         | μΑ    |

| Digital Supply Current (Note 7)       |                  | Operational, full-scale input at 1.8Msps       |                       | 1    | 2.5                       |       |

|                                       |                  | Static, f <sub>SCLK</sub> = 28.8MHz            |                       | 0.4  | 1                         | m ^   |

|                                       |                  | Partial/full power-down mode, fSCLK = 28.8MHz  |                       | 0.2  | 0.5                       | mA    |

|                                       |                  | Static, no SCLK (all modes)                    |                       | 0.1  | 1                         | μΑ    |

| Positive-Supply Rejection             | PSR              | V <sub>DD</sub> = 5V ±5%, full-scale input     |                       | ±0.2 | ±3.0                      | mV    |

#### **TIMING CHARACTERISTICS**

$(V_{DD} = +5V \pm 5\%, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, 50\%$  duty cycle,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                          | SYMBOL            | CONDITIONS                               | MIN  | TYP | MAX | UNITS  |

|------------------------------------|-------------------|------------------------------------------|------|-----|-----|--------|

| SCLK Pulse-Width High              | tсн               | $V_L = 1.8V$ to $V_{DD}$                 | 15.6 |     |     | ns     |

| SCLK Pulse-Width Low               | tCL               | $V_L = 1.8V$ to $V_{DD}$                 | 15.6 |     |     | ns     |

| SCLK Rise to DOUT Transition       | t <sub>DOUT</sub> | $C_L = 30pF$ , $V_L = 4.75V$ to $V_{DD}$ |      |     | 14  | ns     |

|                                    |                   | $C_L = 30pF$ , $V_L = 2.7V$ to $V_{DD}$  |      |     | 17  |        |

|                                    |                   | $C_L = 30pF$ , $V_L = 1.8V$ to $V_{DD}$  |      |     | 24  |        |

| DOUT Remains Valid After SCLK Rise | tDHOLD            | $V_L = 1.8V$ to $V_{DD}$                 | 4    |     |     | ns     |

| CNVST Fall to SCLK Fall            | tSETUP            | $V_L = 1.8V$ to $V_{DD}$                 | 10   |     |     | ns     |

| CNVST Pulse Width                  | tcsw              | $V_L = 1.8V$ to $V_{DD}$                 | 20   |     |     | ns     |

| Power-Up Time; Full Power-Down     | tpwr-up           |                                          |      | 2   |     | ms     |

| Restart Time; Partial Power-Down   | t <sub>RCV</sub>  |                                          |      | 16  |     | Cycles |

- **Note 1:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the gain error and the offset error have been nulled.

- Note 2: No missing codes over temperature.

- Note 3: Conversion time is defined as the number of clock cycles (16) multiplied by the clock period.

- Note 4: At sample rates below 10ksps, the input full-linear bandwidth is reduced to 5kHz.

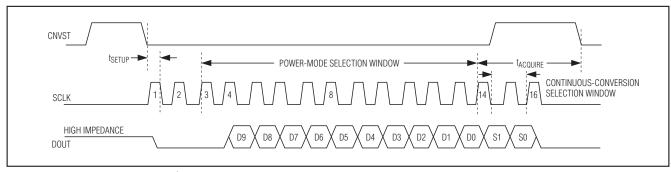

- **Note 5:** The listed value of three SCLK cycles is given for full-speed continuous conversions. Acquisition time begins on the 14th rising edge of SCLK and terminates on the next falling edge of CNVST. The IC idles in acquisition mode between conversions.

- Note 6: Undersampling at the maximum signal bandwidth requires the minimum jitter spec for SINAD performance.

- Note 7: Digital supply current is measured with the VIH level equal to VL, and the VIL level equal to GND.

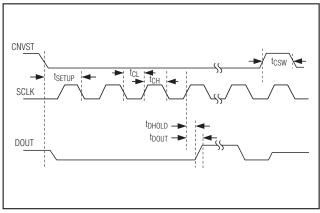

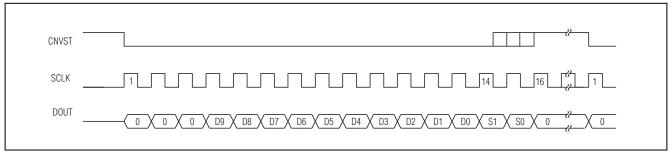

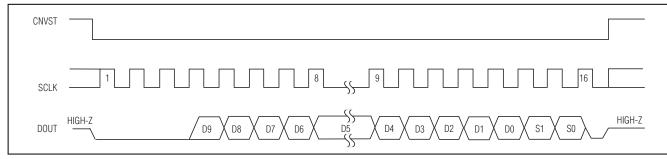

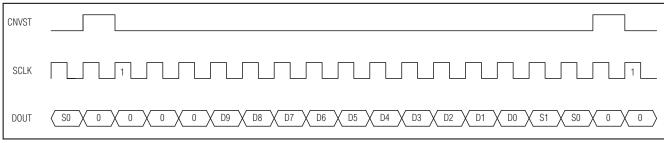

図1. 詳細なシリアルインタフェースのタイミング

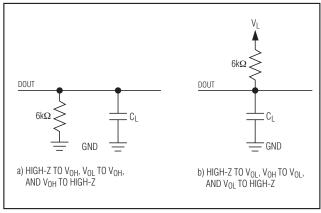

図2. イネーブル/ディセーブル時間測定のための負荷回路

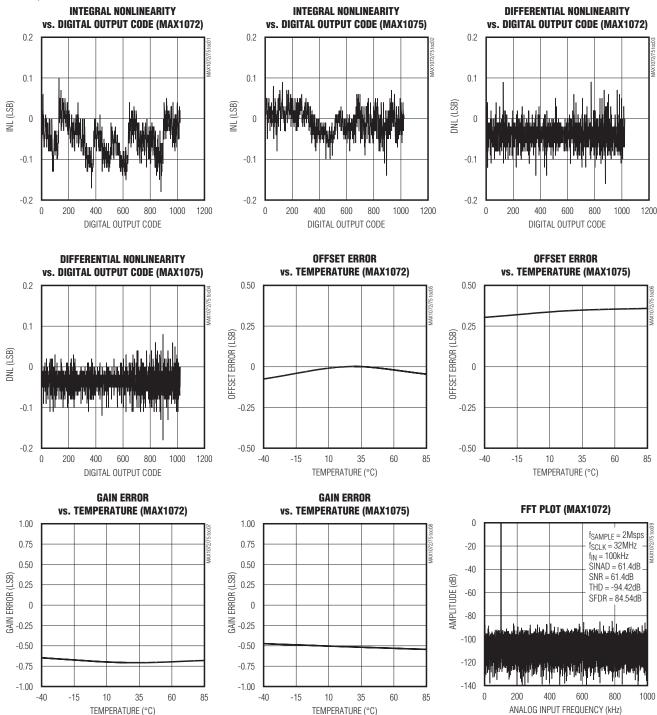

### 標準動作特性

$(V_{DD} = +5V, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

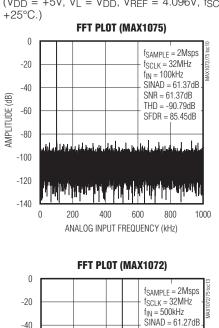

### 標準動作特性(続き)

$(V_{DD} = +5V, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

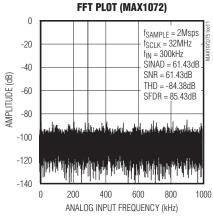

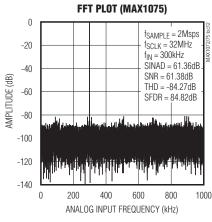

### 標準動作特性(続き)

$(V_{DD} = +5V, V_L = V_{DD}, V_{REF} = 4.096V, f_{SCLK} = 28.8MHz, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

### 端子説明

| 端子    | 名称              | 機能                                                                                                     |

|-------|-----------------|--------------------------------------------------------------------------------------------------------|

| 1     | AIN-            | 負アナログ入力。                                                                                               |

| 2     | REF             | 外部からのリファレンス電圧入力。 $V_{REF}$ は、アナログ入力範囲を設定します。 $0.01\mu$ Fのコンデンサと 4.7 $\mu$ FのコンデンサでREFをRGNDにバイパスしてください。 |

| 3     | RGND            | リファレンスグランド。RGNDをGNDに接続してください。                                                                          |

| 4     | V <sub>DD</sub> | 正アナログ電源電圧(+4.75V~+5.25V)。 $0.01\mu$ Fのコンデンサと $10\mu$ Fのコンデンサで $V_{DD}$ をGNDにバイパスしてください。                |

| 5, 11 | N.C.            | 無接続。                                                                                                   |

| 6     | GND             | グランド。GNDは内部でEPに接続されています。                                                                               |

| 7     | VL              | 正ロジック電源電圧(1.8V $\sim$ V <sub>DD</sub> )。0.01 $\mu$ Fのコンデンサと10 $\mu$ FのコンデンサでV $_{L}$ をGNDにバイパスしてください。  |

| 8     | DOUT            | シリアルデータ出力。データは、SCLKの立上りエッジで同期出力されます。                                                                   |

| 9     | CNVST           | 変換開始入力。CNVSTをハイに強制すると、デバイスが変換の準備をします。変換は、CNVSTの立下りエッジで始まります。サンプリング時点は、CNVSTの立下りエッジで決まります。              |

| 10    | SCLK            | シリアルクロック入力。変換データはシリアルインタフェースからクロック同期出力されます。SCLKによって変換速度も設定されます。                                        |

| 12    | AIN+            | 正アナログ入力。                                                                                               |

| _     | EP              | エクスポーズドパッド。EPは内部でGNDに接続されています。                                                                         |

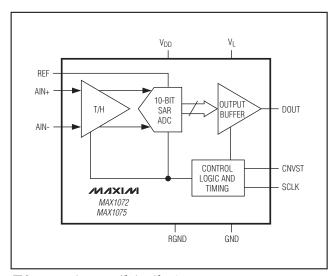

#### 詳細

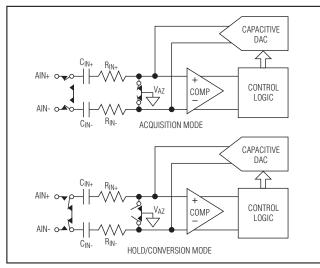

MAX1072/MAX1075では、入力T/Hおよび逐次比較レジスタ(SAR)回路を使用してアナログ入力信号をディジタル10ビット出力に変換します。シリアルインタフェースは、3本のディジタルライン(SCLK、CNVST、およびDOUT)のみを必要とし、マイクロプロセッサ( $\mu$ P)とDSPに容易に接続されます。図3は、MAX1072/MAX1075の内部構成を簡略化して示したものです。

#### 真の差動アナログ入力T/H

図4の等価回路は、T/H、コンパレータ、およびスイッチトキャパシタ方式のディジタル-アナログコンバータ (DAC)で構成されるMAX1072/MAX1075の入力アーキテクチャを示します。T/Hは、前の変換の14番目の SCLKの立上りエッジでトラッキングモードに入ります。電源を投入すると、T/Hは直ちにトラッキングモードに入ります。正入力のコンデンサは、AIN+に接続されます。負入力のコンデンサはAIN-に接続されます。T/Hは、CNVSTの立下りエッジでホールドモードに入り、サンプリングされた正と負の入力電圧間の差が変換されます。T/Hが入力信号を収集するのに要する時間は、その入力容量に充電する時間で決まります。入力信号源のインピーダンスが高い場合は、アクイジション時間が長くなります。アクイジション時間が

に必要な最小時間です。これは次式によって計算され ます。

$t_{ACQ} \ge 8 \times (RS + R_{IN}) \times 16pF$

ここで、 $R_{IN}=200\Omega$ で、RSは入力信号源インピーダンスです。

### 入力帯域幅

ADCの入力トラッキング回路は、小信号帯域幅が20MHzであるため、アンダーサンプリング技術を利用することによって高速の過渡現象をディジタル化し、ADCのサンプリング速度を超える帯域幅の周期信号を測定することができます。高周波信号が所定帯域にエイリアシングとして現れるのを防止するため、アンチエイリアスフィルタの使用をお奨めします。

### アナログ入力保護

アナログ入力を $V_{DD}$ とGNDにクランプする保護ダイオードが内蔵されているため、アナログ入力ピンはGND - 0.3Vから $V_{DD}$  + 0.3Vまで損傷を受けることなくスイングすることができます。変換を正確に行うためには、差動の両入力が $V_{DD}$ 以内であり、GND以上の範囲になければなりません。

図3. ファンクションダイアグラム

図4. 等価入力回路

### シリアルインタフェース

### 電源投入後の初期化および変換の開始

MAX1072/MAX1075は最初の電源投入で内部較正の初期化のために1回の変換サイクルを完了する必要があります。この初期変換が終わると、デバイスは通常動作の準備が完了します。この初期化は、ハードウェアの電源投入シーケンスの後にのみ必要とし、一時的または完全パワーダウンモードから抜け出すときは不要です。

変換を開始するには、CNVSTをロー状態に強制してください。CNVSTの立下りエッジで、T/Hはそのホールドモードに入り変換が始まります。SCLKが変換を実行し、これに続いてデータがDOUT上にシリアルにシフトアウトされます。

#### タイミングと制御

変換開始とデータ読み取り動作は、CNVSTおよびSCLKディジタル入力によって制御されます。図1と5は、シリアルインタフェース動作の概要を示すタイミング図を示します。

変換シーケンスは、CNVSTの立下りエッジで開始されます。すなわち、T/H段が入力電圧をホールドし、ADCが変換を開始し、DOUTがハイインピーダンスからロジックローに変わります。SCLKは、変換プロセスを進めるのに使用され、各変換ビットが確定するとデータをシフトアウトします。

SCLKは、SCLKの4番目の立上りエッジの後にデータのシフトアウトを開始します。DOUTは、各SCLKの立上りエッジ後tDOUTの後に遷移し、次の立上りエッジ後4ns (tDHOLD)の間有効な状態を保ちます。4番目の立上りクロックエッジで変換されたMSBがDOUTに出力

され、MSBは5番目の立上りエッジ後4nsの間有効な 状態を保ちます。10データビット、2サブビット(S1と S0)、および3つの先行ゼロがあるため、これらのビット をシフトアウトするには少なくとも16の立上りクロック エッジが必要です。連続動作とするためには、14番目 と16番目のSCLK立上りエッジの間にCNVSTをハイ状 態に強制してください。16番目のSCLKサイクルの立下 りエッジ後、CNVSTがローのままである場合は、DOUT ラインがCNVSTの立上りエッジまたは次のSCLKの立 上りエッジのいずれかでハイインピーダンス状態にな ります。

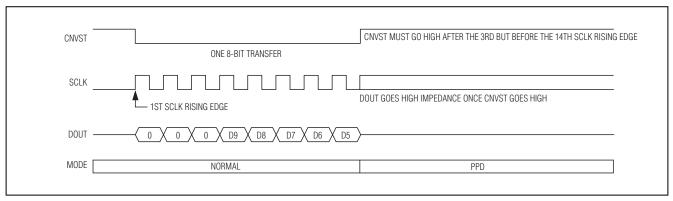

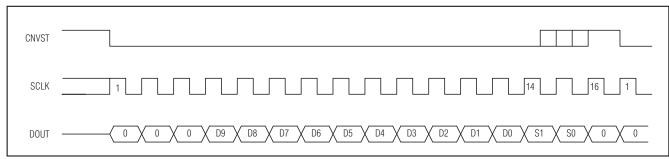

### 一時的パワーダウンおよび 完全パワーダウンモード

消費電力は、MAX1072/MAX1075を一時的、または 完全パワーダウンモードのいずれかとすることによって 著しく低減することができます。一時的パワーダウン モードは、低速のデータサンプリングおよび高速ウェイク アップ時間を必要とするアプリケーションに最適です。 デバイスを一時的パワーダウンモードにしてこのモード を維持するには、3番目のSCLK立上りエッジの後で14 番目のSCLK立上りエッジの前にCNVSTをハイ状態に 強制してください(図6参照)。このことにより、消費電 流が1mAに減少します。一時的パワーダウンモードを 終了するには、CNVSTをローに駆動して少なくとも 14 SCLKサイクルが経過してからCNVSTをハイに駆動 してください。

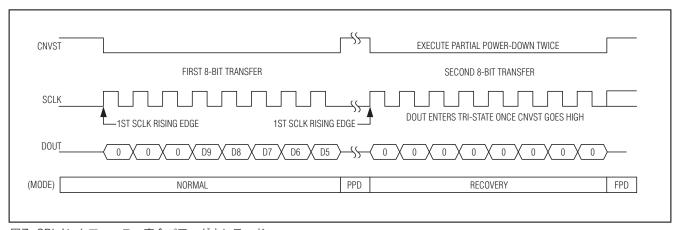

完全パワーダウンモードは、低速のデータサンプリングおよび超低消費電流を必要とするアプリケーションに最適です。MAX1072/MAX1075を完全パワーダウンモードにするには、これらのデバイスが一時的パワーダウンモード状態になければなりません。前記のSCLK/

図5. インタフェース—タイミングシーケンス

図6. SPIインタフェース——時的パワーダウンモード

図7. SPIインタフェース―完全パワーダウンモード

CNVSTシーケンスを実行してデバイスを一時的パワーダウンモードにします。つぎに、同じシーケンスを繰り返して完全パワーダウンモードとします(図7参照)。完全パワーダウンモードを終了するには、CNVSTをロー状態に駆動して少なくとも14 SCLKサイクルが経過してからCNVSTをハイに駆動します。一時的/完全パワーダウンモードでは、消費電力を最小限に抑制するためにSCLKをロジックローまたはロジックハイに保つ必要があります。

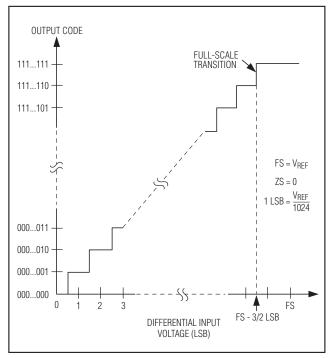

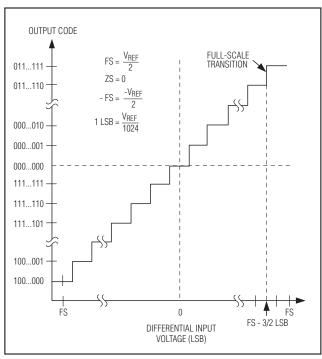

#### 伝達関数

図8は、MAX1072のユニポーラの伝達関数を示します。 図9は、MAX1075のバイポーラの伝達関数を示します。 MAX1072の出力はストレートバイナリですが、 MAX1075の出力は2の補数です。

### アプリケーション情報

#### 外部リファレンス

MAX1072/MAX1075には、外部リファレンスが必要です。最良の性能を得るためには、 $4.7\mu$ Fと $0.01\mu$ FのバイパスコンデンサをREFピンに接続してください。リファレンス入力回路は、 $+1V\sim V_{DD}$ の外部からのリファレンス電圧で動作することができます。

#### 変換の開始方法

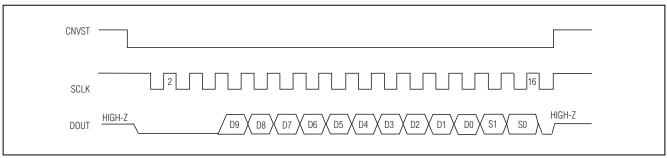

アナログ-ディジタル変換は、CNVSTによって開始さ れて、SCLKのクロックで変換され、得られたデータは SCLKによってDOUT上に同期出力されます。SCLKを ハイまたはローにアイドリングすると、CNVSTの立下 りエッジで変換が始まります。この立下りで、アナログ 入力段がトラックモードからホールドモードに移行し、 DOUTがハイインピーダンス状態からアクティブローに 駆動される状態に移行します。通常の変換を終了する には、合計16 SCLKサイクルが必要です。CNVSTが 16番目の立下りSCLKエッジの間にロー状態であると、 DOUTはCNVSTまたはSCLKの次の立上りエッジでハイ インピーダンスに戻るため、複数のデバイスがシリアル インタフェースを共有することができます。CNVSTが SCLKの14番目立上りエッジの後から16番目の立上り エッジの前の間にハイに戻れば、DOUTはアクティブの ままであるため連続変換を続けることができます。最高 のスループットは、連続変換を行なう場合に得られます。 図10は、標準的なシリアルインタフェースを使用した 変換を示します。

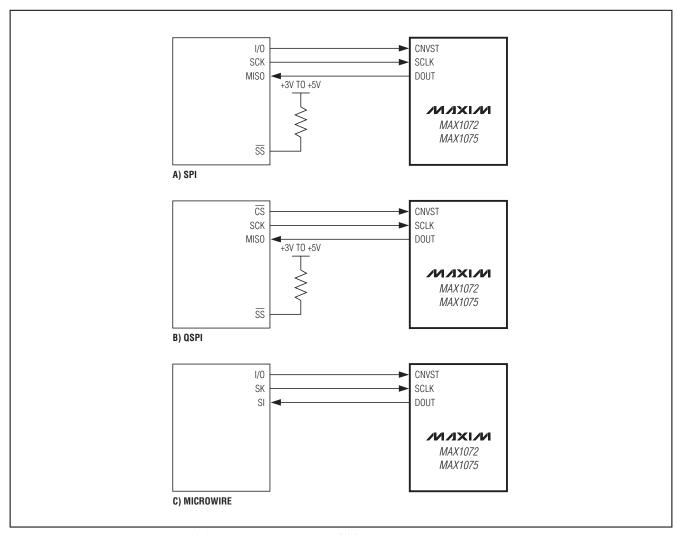

### 標準インタフェースとの接続

MAX1072/MAX1075のシリアルインタフェースは、SPI/QSPI、およびMICROWIREに完全対応しています(図11参照)。シリアルインタフェースが使える場合は、CPUのシリアルインタフェースをマスターモードに設定するとCPUがシリアルクロックを発生します。最高28.8MHzまでのクロック周波数を選定してください。

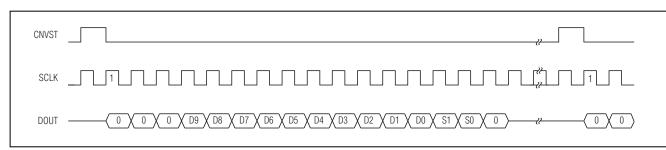

#### **SPIとMICROWIRE**

SPIまたはMICROWIREを使用する場合、MAX1072/MAX1075は、SPIまたはMICROWIRE制御レジスタの CPHAおよびCPOLビットを使用してプログラムする4つのモードすべてに対応します。変換は、CNVSTの立下りエッジで始まります。DOUTがローになり、変換が進行中であることを示します。ADCから完全な10ビットを得るためには、1バイト読み取りを連続して2回行う必要があります。DOUTは、SCLKの立上りエッジで変化します。DOUTは、その $t_{DOUT}$ 後に有効となることが保証されており、次のSCLKの立上りエッジ後の $t_{DHOLD}$ の間有効な状態を保ちます。CPOL = 0およびCPHA = 0またはCPOL = 1およびCPHA = 1またはCPOL = 1およびCPHA = 0を使用する場合、データは次の立

図8. ユニポーラ入力の場合の伝達関数(MAX1072のみ)

図9. バイポーラ入力の場合の伝達関数(MAX1075のみ)

下りエッジのクロックによってµPに取り込まれます。接続については図11を、タイミングについては図12と13を参照してください。最適な利用方法を決定するには、「Timing Characteristics (タイミング特性)」の項を参照してください。

図10. バースト/連続クロックによる連続変換

図11. MAX1072/MAX1075との一般的シリアルインタフェース接続

図12. SPI/MICROWIREシリアルインタフェースのタイミング—単一変換(CPOL = CPHA = 0)、(CPOL = CPHA = 1)

図13. SPI/MICROWIREシリアルインタフェースのタイミング—連続変換(CPOL = CPHA = 0)、(CPOL = CPHA = 1)

図14. QSPIシリアルインタフェースのタイミング—単一変換(CPOL = 1、CPHA = 1)

#### **OSPI**

ADCから10ビットのデータを収集するのに1バイト読み取りを2回行う必要があるSPIとは異なり、QSPIでは最小限のクロックサイクル数でデータをクロックに同期して入力することができます。MAX1072/MAX1075は、10ビットのデータをクロックに同期して出力するのに $\mu$ Pから16クロックサイクルを必要とします。図14は、CPOL = 1およびCPHA = 1を使用した場合の転送を示しています。変換結果は、3個のゼロの後に10データビット、2サブビット、およびその後のゼロからなり、データは先頭がMSBの形式です。

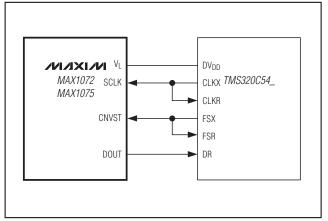

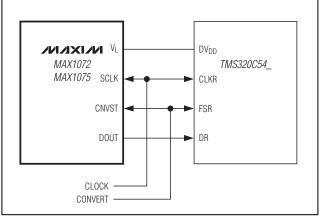

#### TMS320C54 とのDSPインタフェース

MAX1072/MAX1075は、Texas Instruments, Inc.の TMS320C54\_ファミリのDSPに直接接続することができます。それ自身のクロックを発生するかまたは外部クロック信号を使用するようにDSPを設定してください。シリアルポートは標準またはバッファ付きの何れかを選択してください。図15は、MAX1072/MAX1075とTMS320C54\_の最も簡単なインタフェースを示すもので、この場合、送信シリアルクロック(CLKX)が受信シリアルクロック(CLKR)とSCLKを駆動し、送信フレーム同期信号(FSR)とCNVSTを駆動します。

図15. 内部クロックの場合のTMS320C54\_とのインタフェース

連続変換を行うためには、データ伝送を行う前に、クロックを送信するようにシリアルポートを設定し、クロック期間にフレーム同期信号パルスを発生させてください。シリアルポート設定(SPC)レジスタは、内部フレーム同期(TXM = 1)、内蔵クロック信号源によって駆動されるCLKX (MCM = 1)、バーストモード(FSM = 1)、および16ビットワード長(FO = 0)となるように設定しなければなりません。

この設定によって、連続変換が可能になります。ただし、データ送信レジスタ(DXR)とデータ受信レジスタ(DRR)は、次の変換前に使用可能になる必要があります。この代わりに、バッファ付きシリアルポートを使用して変換を行いCPUの介入なしでデータを読み取る場合は、自動バッファリングをイネーブルすることができます。MAX1072/MAX1075がDSP電源電圧よりも高いアナログ電源電圧で動作する場合は、 $V_L$ ピンをTMS320C54\_電源電圧に接続してください。FO=1としてワード長を8ビットに設定すると、パワーダウンモードを実現することが可能です。いずれかのパワーダウン状態に保つには、CNVSTピンをハイの状態にしておく必要があります。

MAX1072/MAX1075をTMS320C54\_に接続するもう 1つの方法は、どちらのデバイスに対しても外部からの クロック信号を供給することです。この接続を図16に 示します。この図では、シリアルクロック(CLOCK)が CLKRとSCLKを駆動し、変換信号(CONVERT)がFSRと CNVSTを駆動しています。

外部受信クロックと外部受信フレーム同期信号を受け入れ可能とするためには、シリアルポートを設定する必要があります。

SPCレジスタには、次のように書き込む必要があります。

TXM = 0、外部フレーム同期

MCM = 0、CLKXをCLKXピンから取り込む

FSM = 1、バーストモード

FO = 0、16ビットワードとしてデータを送受信する

図16. 外部クロックの場合のTMS320C54 とのインタフェース

この設定によって、連続変換が可能になります。ただし、DRRは次の変換前に使用可能になる必要があります。この代わりに、バッファ付きシリアルポートを使用してCPUの介入なしでデータを読み取るために自動バッファリングをイネーブルすることができます。MAX1072/MAX1075がDSP電源電圧よりも高いアナログ電源電圧で動作する場合は、VLピンをTMS320C54\_電源電圧に接続してください。

また、MAX1072/MAX1075は、データ送信(DX)ピンを使用することによってTMS320C54\_に接続して、SCLKを駆動するために内部生成されたCNVSTとCLKXを駆動することができます。DXがハイインピーダンスになるとき、CNVST信号にプルアップ抵抗器を接続してこの信号をハイに保つ必要があり、また連続して変換を行うためには、DXRに連続して0001hexを書き込む必要があります。00FFhexをDXRに書き込むことによってパワーダウンモードに入ることができます(図17と18参照)。

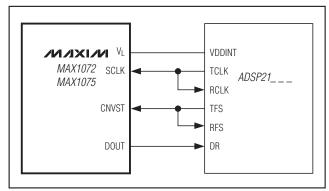

#### ADSP21\_ \_ へのDSPインタフェース

MAX1072/MAX1075は、Analog Devices、Inc.の ADSP21\_\_\_ファミリのDSPに直接接続することができます。図19は、ADSP21\_\_\_へのMAX1072/MAX1075の直接接続を示します。MAX1072/MAX1075とインタフェースするために2つの動作モードをプログラムすることができます。連続変換を行うためには、CNVSTをローの状態から前に送信されるワードのLSBの期間中に1クロックサイクルの間CNVSTをハイパルスとしてください。ADSP21\_\_\_STCTLおよびSRCTLの各レジスタは、初期フレーミング(LAFR = 0)およびアクティブハイフレーム(LTFS = 0、LRFS = 0)信号用に設定する必要があります。このモードでは、データと無関係なフレーム同期ビット(DITFS = 1)を選択して、送信データレジスタへ書き込みが1度で済むようにすることができます。

図17. DSPインタフェース—連続変換

図18. DSPインタフェース—単一変換、連続/バーストクロック

単一変換を行うためには、CNVSTをハイの状態から口ーに変化させてそれを変換期間中維持してください。 ADSP21\_\_\_ STCTLおよびSRCTLの各レジスタは、後期フレーミング(LAFR = 1)およびアクティブローフレーム(LTFS = 1、LRFS = 1)信号用に設定する必要があります。また、この場合、ワード長を8ビットに設定(SLEN = 1001)することはパワーダウンモードに入るための最良の方法です。MAX1072/MAX1075がDSP電源電圧よりも高い電源電圧で動作する場合は、 $V_L$ ピンをADSP21\_\_ 電源電圧に接続してください(図17と図18を参照)。

#### レイアウト、グランド、およびバイパス

最良の性能を得るためには、プリント基板を使用してください。ワイヤラップボードは使用しないようにしてください。プリント基板のレイアウトでは、ディジタルとアナログの信号ラインが互いに分離することを確実に行ってください。アナログとディジタル(特にクロック)の各ラインを互いに平行に走らせたり、ディジタルラインをADCパッケージの下に走らせたりしないでください。

図20は、推奨するシステムグランド接続を示します。アナロググランドは、ロジックグランドから分離してGNDで1点アナロググランド(スターグランドポイント)構成としてください。ノイズをさらに低減するため、すべての他のアナロググランドとDGNDをこのスターグランドポイントに接続してください。このグランドの電源へのグランドリターンは、ノイズに影響されない動作とするために、ローインピーダンスとし、できる限り短くしてください。

$V_{DD}$ 電源の高周波ノイズは、ADCの高速コンパレータに影響を及ぼす可能性があります。この電源は、 $0.01\mu F$ と $10\mu F$ のバイパスコンデンサを使って1点アナロググランドにバイパスしてください。電源ノイズを最大限に排除するために、コンデンサのリード長はできる限り短くしてください。

#### 定義

#### 積分非直線性

積分非直線性(INL)は、実際の伝達関数上の値の直線からのずれです。この直線は、オフセットとゲインエラーをゼロにした後の一次回帰直線または伝達関数の両端点を結んだ直線のいずれかです。MAX1072/MAX1075の静的直線性パラメータは、端点間法を使用して測定します。

#### 微分非直線性

微分非直線性(DNL)は、実際のステップ幅と1 LSBの理想値の差です。1 LSB以下のDNL誤差の仕様は、ミッシングコードのない単調伝達関数を保証するものです。

#### アパーチャジッタ

アパーチャジッタ $(t_{AJ})$ は、各サンプル間の時間間隔の変動です。

#### アパーチャ遅延

アパーチャ遅延 $(t_{AD})$ は、CNVSTの立下りエッジから 実際のサンプリングが行なわれる瞬間までの時間です。

図19. ADSP21\_ \_ \_とのインタフェース

#### 信号対雑音比

ディジタルサンプルから完全に再現される波形の場合、信号対雑音比(SNR)はフルスケールアナログ入力(RMS値)とRMS量子化誤差(残留誤差)の比です。理論的な最小のアナログ-ディジタル変換雑音は、量子化誤差によって生じるもので、ADCの分解能(Nビット)から次式によって直接求められます。

$$SNR = (6.02 \times N + 1.76)dB$$

実際には、量子化雑音以外に、熱雑音、リファレンス雑音、クロックジッタなどの雑音源があります。したがって、SNRは、RMS信号とRMS雑音の比をとることによって求められます。RMS雑音には、全スペクトル成分から基本波を差し引いた成分、最初の5つの高調波成分、およびDCオフセットが含まれます。

#### 信号対雑音比+歪み

信号対雑音比+歪み(SINAD)は、基本入力周波数のRMS 振幅とその他すべてのADC出力信号のRMS振幅との比 です。

SINAD(dB) = 20 x log (Signal<sub>RMS</sub>/Noise<sub>RMS</sub>)

#### 有効ビット数

有効ビット数(ENOB)は、特定の入力周波数とサンプリング速度におけるADCの総合的な精度を表わします。理想的なADCの誤差は、量子化雑音のみから成ります。ADCのフルスケールレンジに等しい入力範囲で、ENOBを次式から計算します。

ENOB =

$$\frac{\text{(SINAD - 1.76)}}{6.02}$$

図20. 電源のグランド接続方法

#### 全高調波歪み

全高調波歪み(THD)は、入力信号に含まれる最初の5つの高調波のRMS合計と基本波そのものとの比です。これは、次式で表わされます。

THD =

$$20 \times log \left( \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2}}{V_1} \right)$$

ここで、 $V_1$ は基本波の振幅で、 $V_2 \sim V_5$ は第2から第5までの高調波の振幅です。

#### スプリアスフリ-ダイナミックレンジ

スプリアスフリ-ダイナミックレンジ(SFDR)は、基本波 (最大信号成分)のRMS振幅と2番目に大きい歪み成分のRMS値との比です。

#### フルパワー帯域幅

フルパワー帯域幅は、入力信号振幅がフルスケール入力に対して3dBだけ減衰する周波数です。

#### フルリニア帯域幅

フルリニア帯域幅は、信号対雑音比+歪み(SINAD)が 56dBに等しい周波数です。

#### 相互変調歪み

非直線性を有するデバイスは、2種類の周波数( $f_1$ と $f_2$ )の2つの正弦波がデバイスに入力されるとき歪み積を発生します。相互変調歪み(IMD)は、2つの入力トーン $f_1$ と $f_2$ の全入力パワーに対するナイキスト周波数までのIM2~IM5の相互変調積の全パワーの比です。各入力トーンレベルは、-7dBFSとします。

チップ情報

TRANSISTOR COUNT: 13,016

PROCESS: BICMOS

相互変調積は、次の通りです。

- 2次の相互変調積(IM2): f<sub>1</sub> + f<sub>2</sub>、f<sub>2</sub> f<sub>1</sub>

- 3次の相互変調積(IM3): 2f<sub>1</sub> f<sub>2</sub>、2f<sub>2</sub> f<sub>1</sub>、2f<sub>1</sub> + f<sub>2</sub>、 2f<sub>2</sub> + f<sub>1</sub>

- 4次の相互変調積(IM4): 3f<sub>1</sub> f<sub>2</sub>、3f<sub>2</sub> f<sub>1</sub>、3f<sub>1</sub> + f<sub>2</sub>、3f<sub>2</sub> + f<sub>1</sub>

- 5次の相互変調積(IM5): 3f<sub>1</sub> 2f<sub>2</sub>、3f<sub>2</sub> 2f<sub>1</sub>、3f<sub>1</sub> + 2f<sub>2</sub>、3f<sub>2</sub> + 2f<sub>1</sub>

### パッケージ

最新のパッケージ情報とランドパターンは、 japan.maxim-ic.com/packagesをご参照ください。

| パッケージタイプ | パッケージコード | ドキュメントNo. |

|----------|----------|-----------|

| 12 TQFN  | T1244+3  | 21-0139   |

### 改訂履歴

| 版数 | 改訂日  | 説明                    | 改訂ページ |

|----|------|-----------------------|-------|

| 0  | 1/04 | 初版                    | _     |

| 1  | 4/09 | データシートから民生用グレード製品を削除。 | 1–7   |

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

18 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600