#

## +5V、**低電力、マルチチャネル** シリアル8ビットADC

概要

MAX1112/MAX1113は、内部トラック/ホールド、電圧 リファレンス、クロック及びシリアルインタフェースを 備えた低電力8ビット、8チャネルアナログディジタル コンバータ(ADC)です。+4.5V~+5.5Vの単一電源で 動作し、最大サンプリングレート50kspsで消費電流は 僅か135µAとなっています。MAX1112の8つのアナログ 入力及びMAX1113の4つのアナログ入力は、ソフトウェア により、ユニポーラ/バイポーラ及びシングルエンド/差動 動作に設定できます。

内部クロック又は外部シリアルインタフェースクロック を使用することによって、逐次比較型のアナログディ ジタル変換を行います。フルスケールアナログ入力範 囲は、4.096V内部リファレンス又は外部から印加され た1V~V<sub>DD</sub>範囲のリファレンスによって決定されます。 4線シリアルインタフェースは、SPI™、QSPI™及び MICROWIRE™シリアルインタフェース規格に適合して います。シリアルストローブ出力により、割込みで駆 動されるプロセサへの変換完了信号が提供されます。

MAX1112/MAX1113は、消費電力を最小限に抑える ためにソフトウェアで設定可能な2µA自動パワーダウン モードを備えています。パワーダウンを使用すると、 消費電流は1kspsで僅か13µA、10kspsで僅か82µAに 低減します。パワーダウンは、SHDN入力ピンを使用し て制御することも可能です。シリアルインタフェース にアクセスすると、自動的にパワーアップします。

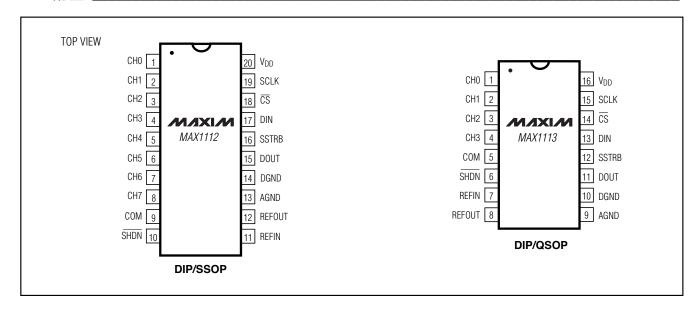

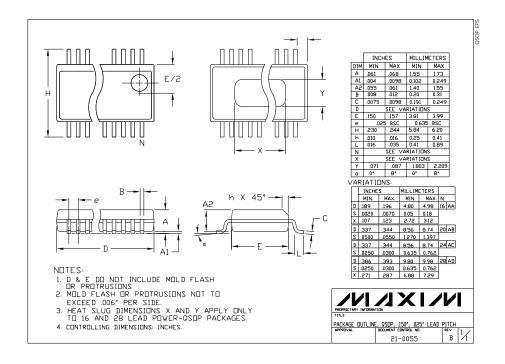

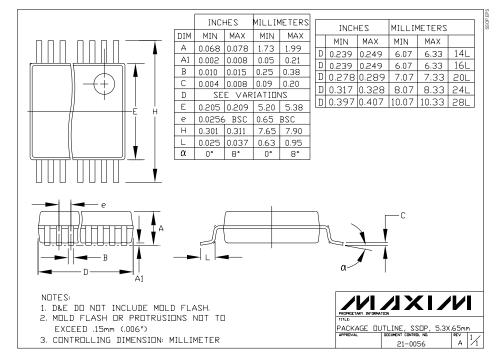

MAX1112は20ピンSSOP及びDIPパッケージ、 MAX1113は小型16ピンQSOP及びDIPパッケージで 提供されています。

### アプリケーション

ポータブルデータロギング

ハンドヘルド測定機器

医療機器

システム診断

太陽電池駆動のリモート機器

4~20mA駆動のリモートデータ収集機器

ピン配置は最後に記載されています。

SPI及びQSPIはMotorola, Inc.の商標です。 MICROWIREはNational Semiconductor Corp.の商標です。

#### 特長

◆ 電源:+4.5V~+5.5V単一

◆ 低電力:50kspsで135µA 1kspsで13µA

◆ 入力:8チャネルシングルエンド又は4チャネル差動

(MAX1112)

4チャネルシングルエンド又は2チャネル差動

(MAX1113)

◆ 内部トラック/ホールドサンプリングレート:50kHz

◆ 内部4.096Vリファレンス

◆ シリアルインタフェース: SPI/QSPI/MICROWIRE コンパチブル

◆ ユニポーラ又はバイポーラ入力: ソフトウェアで設定

◆ 全未調整エラー: ±1LSB(max)

$\pm 0.3LSB(typ)$

#### 型番

| PART       | TEMP. RANGE  | PIN-PACKAGE    |

|------------|--------------|----------------|

| MAX1112CPP | 0°C to +70°C | 20 Plastic DIP |

| MAX1112CAP | 0°C to +70°C | 20 SSOP        |

| MAX1112C/D | 0°C to +70°C | Dice*          |

<sup>\*</sup>Dice are specified at  $T_A = +25$ °C, DC parameters only.

型番はデータシートの最後に続きます。

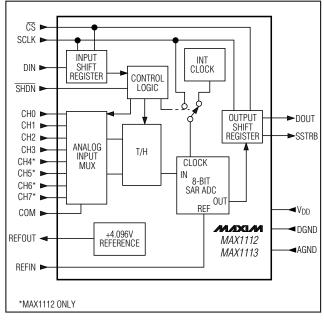

### ファンクションダイアグラム

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to AGND          |                       |

|----------------------------------|-----------------------|

| AGND to DGND                     | 0.3v to 0.3v          |

| REFOUT to AGND                   | -0.3V to (Vpp + 0.3V) |

| Digital Inputs to DGND           |                       |

| Digital Outputs to DGND          |                       |

| Continuous Power Dissipation (TA |                       |

| 16 Plastic DIP (derate 10.53mW/  |                       |

| 16 QSOP (derate 8.30mW/°C ab     |                       |

| 16 CERDIP (derate 10.00mW/°C     | above +70°C)800mW     |

|                                  |                       |

| 00 01 11 010 / 1 1 1 1 1 1 1 1 1 1 1 1 1 | 7000) 000 144  |

|------------------------------------------|----------------|

| 20 Plastic DIP (derate 11.11mW/°C a      |                |

| 20 SSOP (derate 8.00mW/°C above          | +70°C)640mW    |

| 20 CERDIP (derate 11.11mW/°C abo         |                |

| Operating Temperature Ranges             |                |

| MAX1112C_P/MAX1113C_E                    | 0°C to +70°C   |

| MAX1112E_P/MAX1113E_E                    | 40°C to +85°C  |

| MAX1112MJP/MAX1113MJE                    | 55°C to +125°C |

| Storage Temperature Range                | 65°C to +150°C |

| Lead Temperature (soldering, 10sec).     | +300°C         |

|                                          |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VDD = +4.5V to +5.5V; unipolar input mode; COM = 0V; fSCLK = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = TMIN to TMAX; unless otherwise noted.)

| PARAMETER                                          | SYMBOL        | CONDITIONS                                               | MIN          | TYP  | MAX  | UNITS  |

|----------------------------------------------------|---------------|----------------------------------------------------------|--------------|------|------|--------|

| DC ACCURACY                                        | <b>"</b>      |                                                          | _            |      |      | 1      |

| Resolution                                         |               |                                                          | 8            |      |      | Bits   |

| Relative Accuracy (Note 1)                         | INL           |                                                          |              | ±0.1 | ±0.5 | LSB    |

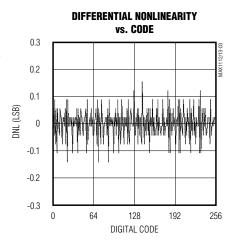

| Differential Nonlinearity                          | DNL           | No missing codes over temperature                        |              |      | ±1   | LSB    |

| Offset Error                                       |               |                                                          |              | ±0.3 | ±1   | LSB    |

| Gain Error (Note 2)                                |               | Internal or external reference                           |              |      | ±1   | LSB    |

| Gain Temperature Coefficient                       |               | External reference, 4.096V                               |              | ±0.8 |      | ppm/°C |

| Total Unadjusted Error                             | TUE           | MAX111_C/E                                               |              | ±0.3 | ±1   | LSB    |

| Channel-to-Channel<br>Offset Matching              |               |                                                          |              | ±0.1 |      | LSB    |

| DYNAMIC SPECIFICATIONS (10.                        | .034kHz sine- | wave input, 4.096Vp-p, 50ksps, 500kHz exte               | ernal clock) |      |      | 1      |

| Signal-to-Noise and Distortion Ratio               | SINAD         |                                                          |              | 49   |      | dB     |

| Total Harmonic Distortion (up to the 5th harmonic) | THD           |                                                          |              | -70  |      | dB     |

| Spurious-Free Dynamic Range                        | SFDR          |                                                          |              | 68   |      | dB     |

| Channel-to-Channel Crosstalk                       |               | V <sub>CH</sub> <sub>_</sub> = 4.096Vp-p, 25kHz (Note 3) |              | -75  |      | dB     |

| Small-Signal Bandwidth                             |               | -3dB rolloff                                             |              | 1.5  |      | MHz    |

| Full-Power Bandwidth                               |               |                                                          |              | 800  |      | kHz    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +4.5V \text{ to } +5.5V; \text{ unipolar input mode; COM} = 0V; f_{SCLK} = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = T_{MIN} to T_{MAX}; unless otherwise noted.)$

| PARAMETER                                                       | SYMBOL          | CON                                                      | DITIONS                                      | MIN   | TYP   | MAX                    | UNITS  |  |

|-----------------------------------------------------------------|-----------------|----------------------------------------------------------|----------------------------------------------|-------|-------|------------------------|--------|--|

| CONVERSION RATE                                                 | L               | I                                                        |                                              |       |       |                        |        |  |

| Conversion Times (Nate 4)                                       | toosus          | Internal clock                                           |                                              |       | 25    | 55                     |        |  |

| Conversion Time (Note 4)                                        | tconv           | External clock, 500kl                                    | Hz, 10 clocks/conversion                     | 20    |       |                        | μs     |  |

| Track/Hold Acquisition Time                                     | tACQ            | External clock, 2MH                                      | łz                                           | 1     |       |                        | μs     |  |

| Aperture Delay                                                  |                 |                                                          |                                              |       | 10    |                        | ns     |  |

| Aperture Jitter                                                 |                 |                                                          |                                              |       | <50   |                        | ps     |  |

| Internal Clock Frequency                                        |                 |                                                          |                                              |       | 400   |                        | kHz    |  |

| Fishers of Olevely Francisco Decree                             |                 | (Note 5)                                                 |                                              | 50    |       | 500                    | kHz    |  |

| External Clock-Frequency Range                                  |                 | Used for data transf                                     | fer only                                     |       |       | 2                      | MHz    |  |

| ANALOG INPUT                                                    | 1               | 1                                                        |                                              |       |       |                        |        |  |

|                                                                 |                 | Unipolar input, CON                                      | M = 0V                                       | 0     |       | V <sub>REFIN</sub>     |        |  |

| Input Voltage Range, Single-<br>Ended and Differential (Note 6) |                 | Discolon insent COM                                      | V / 0                                        |       | (     | COM ±                  | V      |  |

| Ended and Differential (Note 0)                                 |                 | Bipolar input, COM                                       | = VREFIN / 2                                 |       | V     | REFIN / 2              |        |  |

| Multiplexer Leakage Current                                     |                 | On/off leakage curre                                     | ent, V <sub>CH</sub> = 0V or V <sub>DD</sub> |       | ±0.01 | ±1                     | μA     |  |

| Input Capacitance                                               |                 |                                                          |                                              |       | 18    |                        | pF     |  |

| INTERNAL REFERENCE                                              |                 | I                                                        |                                              |       |       |                        |        |  |

| REFOUT Voltage                                                  |                 |                                                          |                                              | 3.936 | 4.096 | 4.256                  | V      |  |

| REFOUT Short-Circuit Current                                    |                 |                                                          |                                              |       | 6     |                        | mA     |  |

| REFOUT Temperature Coefficient                                  |                 |                                                          |                                              |       | ±50   |                        | ppm/°C |  |

| Load Regulation (Note 7)                                        |                 | 0mA to 0.5mA outpu                                       | ut load                                      |       | 4.5   |                        | mV     |  |

| Capacitive Bypass at REFOUT                                     |                 |                                                          |                                              | 1     |       |                        | μF     |  |

| EXTERNAL REFERENCE AT REF                                       | IN              | 1                                                        |                                              |       |       |                        |        |  |

| Input Voltage Range                                             |                 |                                                          |                                              | 1     |       | V <sub>DD</sub> + 50mV | V      |  |

| Input Current                                                   |                 | (Note 8)                                                 |                                              |       | 1     | 20                     | μΑ     |  |

| POWER REQUIREMENTS                                              |                 | ı                                                        |                                              | 1     |       |                        |        |  |

| Supply Voltage                                                  | V <sub>DD</sub> |                                                          |                                              | 4.5   |       | 5.5                    | V      |  |

|                                                                 |                 | Full-scale input                                         | Operating mode                               |       | 135   | 250                    |        |  |

| Cupply Current                                                  | I <sub>DD</sub> | C <sub>LOAD</sub> = 10pF                                 | Reference disabled                           |       | 95    |                        | 1      |  |

| Supply Current                                                  |                 | Power-down                                               | Software                                     |       | 2     |                        | μA     |  |

|                                                                 | SHDN at DGND    |                                                          |                                              | 3.2   | 10    | <u> </u>               |        |  |

| Power-Supply Rejection<br>(Note 9)                              | PSR             | V <sub>DD</sub> = 4.5V to 5.5V;<br>4.096V; full-scale in |                                              |       | ±0.4  | ±4                     | mV     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +4.5V \text{ to } +5.5V; \text{ unipolar input mode}; COM = 0V; f_{SCLK} = 500kHz, external clock (50% duty cycle); 10 clocks/conversion cycle (50ksps); 1µF capacitor at REFOUT; TA = T_{MIN} to T_{MAX}; unless otherwise noted.)$

| PARAMETER                                           | SYMBOL            | CONDITIONS                             | MIN                   | TYP                 | MAX                 | UNITS |

|-----------------------------------------------------|-------------------|----------------------------------------|-----------------------|---------------------|---------------------|-------|

| DIGITAL INPUTS: DIN, SCLK, $\overline{\mathbb{CS}}$ |                   |                                        |                       |                     |                     |       |

| DIN, SCLK, CS Input High Voltage                    | VIH               |                                        | 3                     |                     |                     | V     |

| DIN, SCLK, CS Input Low Voltage                     | VIL               |                                        |                       |                     | 0.8                 | V     |

| DIN, SCLK, CS Input Hysteresis                      | VHYST             |                                        |                       | 0.2                 |                     | V     |

| DIN, SCLK, CS Input Leakage                         | I <sub>IN</sub>   | Digital inputs = 0V or V <sub>DD</sub> |                       |                     | ±1                  | μΑ    |

| DIN, SCLK, CS Input Capacitance                     | CIN               | (Note 5)                               |                       |                     | 15                  | рF    |

| SHDN INPUT                                          |                   |                                        |                       |                     |                     |       |

| SHDN Input High Voltage                             | VsH               |                                        | V <sub>DD</sub> - 0.4 |                     |                     | V     |

| SHDN Input Mid-Voltage                              | V <sub>SM</sub>   |                                        | 1.1                   | \                   | <sub>DD</sub> - 1.1 | V     |

| SHDN Voltage, Floating                              | V <sub>FL</sub> T | SHDN = open                            | \                     | V <sub>DD</sub> / 2 |                     | V     |

| SHDN Input Low Voltage                              | V <sub>SL</sub>   |                                        |                       |                     | 0.4                 | V     |

| SHDN Input Current                                  |                   | SHDN = 0V or V <sub>DD</sub>           |                       |                     | ±4                  | μΑ    |

| SHDN Maximum Allowed Leakage for Mid-Input          |                   | SHDN = open                            |                       |                     | ±100                | nA    |

| DIGITAL OUTPUTS: DOUT, SSTRI                        | В                 |                                        | ,                     |                     |                     |       |

| Output Low Voltage                                  | VoL               | ISINK = 5mA                            |                       |                     | 0.4                 | V     |

| Output Low Voltage                                  | VOL               | I <sub>SINK</sub> = 16mA               |                       |                     | 0.8                 | V     |

| Output High Voltage                                 | Vон               | ISOURCE = 0.5mA                        | V <sub>DD</sub> - 0.5 |                     |                     | V     |

| Three-State Leakage Current                         | ΙL                | CS = V <sub>DD</sub>                   |                       | ±0.01               | ±10                 | μΑ    |

| Three-State Output Capacitance                      | Cout              | CS = V <sub>DD</sub> (Note 5)          |                       |                     | 15                  | pF    |

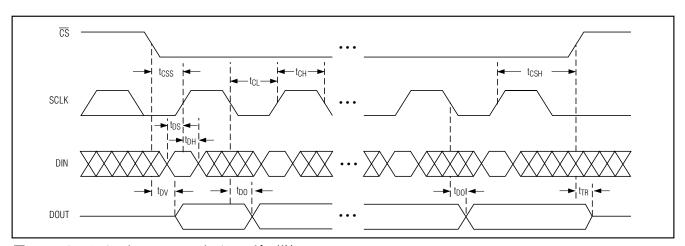

### TIMING CHARACTERISTICS (Figures 8 and 9)

$(V_{DD} = +4.5V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$

| PARAMETER                                   | SYMBOL          | CON                                               | CONDITIONS                                        |     | TYP | MAX | UNITS |

|---------------------------------------------|-----------------|---------------------------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| Track/Hold Acquisition Time                 | tACQ            |                                                   |                                                   | 1   |     |     | μs    |

| DIN to SCLK Setup                           | t <sub>DS</sub> |                                                   |                                                   | 100 |     |     | ns    |

| DIN to SCLK Hold                            | tDH             |                                                   |                                                   | 0   |     |     | ns    |

| SCLK Fall to Output Data Valid              | tno             | Figure 1,                                         | MAX111_C/E                                        | 20  |     | 200 | ns    |

| SOLN Faii to Output Data Vaiiu              | tDO             | CLOAD = 100pF                                     | MAX111_M                                          | 20  |     | 240 | 115   |

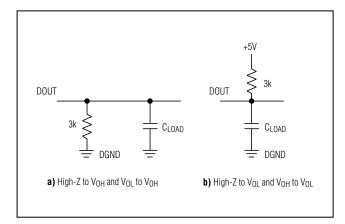

| CS Fall to Output Enable                    | tDV             | Figure 1, CLOAD =                                 | 100pF                                             |     |     | 240 | ns    |

| CS Rise to Output Disable                   | t <sub>TR</sub> | Figure 2, C <sub>LOAD</sub> =                     | 100pF                                             |     |     | 240 | ns    |

| CS to SCLK Rise Setup                       | tcss            |                                                   |                                                   | 100 |     |     | ns    |

| CS to SCLK Rise Hold                        | tcsh            |                                                   |                                                   | 0   |     |     | ns    |

| SCLK Pulse Width High                       | tch             |                                                   |                                                   | 200 |     |     | ns    |

| SCLK Pulse Width Low                        | t <sub>CL</sub> |                                                   |                                                   | 200 |     |     | ns    |

| SCLK Fall to SSTRB                          | tsstrb          | CLOAD = 100pF                                     |                                                   |     |     | 240 | ns    |

| CS Fall to SSTRB Output Enable (Note 5)     | tsdv            | Figure 1, external c<br>CLOAD = 100pF             | lock mode only,                                   |     |     | 240 | ns    |

| CS Rise to SSTRB Output<br>Disable (Note 5) | tstr            | Figure 2, external c<br>C <sub>LOAD</sub> = 100pF | Figure 2, external clock mode only, CLOAD = 100pF |     |     | 240 | ns    |

| SSTRB Rise to SCLK Rise (Note 5)            | tsck            | Figure 11, internal of                            | clock mode only                                   | 0   |     |     | ns    |

| Wakaun Tima                                 | torrace         | External reference                                |                                                   |     | 20  |     | μs    |

| Wakeup Time                                 | twake           | Internal reference (                              | ernal reference (Note 10)                         |     | 24  |     | ms    |

- Note 1: Relative accuracy is the analog value's deviation (at any code) from its theoretical value after the full-scale range is calibrated.

- **Note 2:** V<sub>REFIN</sub> = 4.096V, offset nulled.

- Note 3: On-channel grounded; sine wave applied to all off-channels.

- Note 4: Conversion time is defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

- Note 5: Guaranteed by design. Not subject to production testing.

- **Note 6:** Common-mode range for the analog inputs is from AGND to V<sub>DD</sub>.

- Note 7: External load should not change during the conversion for specified accuracy.

- Note 8: External reference at 4.096V, full-scale input, 500kHz external clock.

- **Note 9:** Measured as | V<sub>FS</sub> (4.5V) V<sub>FS</sub> (5.5V) |.

- **Note 10:** 1µF at REFOUT; internal reference settling to 0.5LSB.

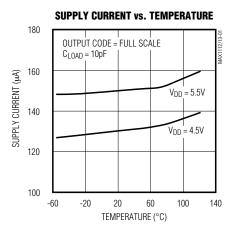

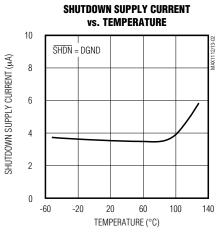

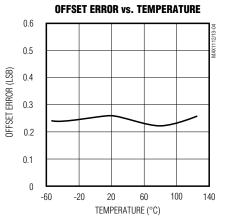

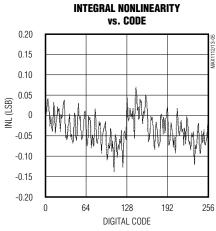

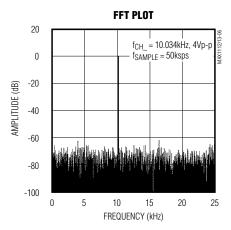

標準動作特性 \_

$(V_{DD} = +5.0V; f_{SCLK} = 500kHz; external clock (50% duty cycle); R_L = \infty; T_A = +25°C, unless otherwise noted.)$

## 端子説明

| 端       | i子      | 67.1h   | 144 - 44-                                                                                                                                                             |

|---------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1112 | MAX1113 | 名称      | 機能                                                                                                                                                                    |

| 1–4     | 1–4     | CH0-CH3 | サンプリングアナログ入力                                                                                                                                                          |

| 5–8     | _       | CH4-CH7 | サンプリングアナログ入力                                                                                                                                                          |

| 9       | 5       | COM     | アナログ入力のグランドリファレンス。シングルエンドモードにおけるゼロコード電圧を設定します。 ± 0.5LSBの安定性が必要です。                                                                                                     |

| 10      | 6       | SHDN    | 3レベルシャットダウン入力。通常はフローティングです。MAX1112/MAX1113はSHDNをローにするとシャットダウンし、消費電流が10μA(max)に低減されます。それ以外の場合は、完全動作状態です。SHDNをハイにすると、内部リファレンスがシャットダウンされます。                              |

| 11      | 7       | REFIN   | アナログディジタル変換用のリファレンス電圧入力。内部リファレンスを使用する場合は、REFOUTに接続してください。                                                                                                             |

| 12      | 8       | REFOUT  | 内部リファレンスジェネレータ出力。1µFコンデンサでAGNDにバイパスしてください。                                                                                                                            |

| 13      | 9       | AGND    | アナロググランド                                                                                                                                                              |

| 14      | 10      | DGND    | ディジタルグランド                                                                                                                                                             |

| 15      | 11      | DOUT    | シリアルデータ出力。データは、SCLKの立下がりエッジでクロック出力されます。 CS がハイの時は、ハイインピーダンスになります。                                                                                                     |

| 16      | 12      | SSTRB   | シリアルストローブ出力。内部クロックモードのSSTRBは、MAX1112/MAX1113がA/D変換を開始した時にローになり、変換終了時にハイになります。外部クロックモードでは、MSBがシフトアウトされる前に2クロックサイクルだけパルス的にハイになります。CSがハイの時は、ハイインピーダンスになります(外部クロックモードのみ)。 |

| 17      | 13      | DIN     | シリアルデータ入力。データはSCLKの立上がりエッジでクロック入力されます。                                                                                                                                |

| 18      | 14      | CS      | アクティブローのチップセレクト。 $\overline{\text{CS}}$ がローでない限り、データはDINにクロック入力されません。 $\overline{\text{CS}}$ がハイの時、DOUTはハイインピーダンスになります。                                               |

| 19      | 15      | SCLK    | シリアルクロック入力。シリアルインタフェースのデータをクロック入力及び出力します。SCLKは、外部クロックモードの時に変換速度も設定します(デューティサイクルは45%~55%であることが必要です)。                                                                   |

| 20      | 16      | VDD     | 正電源電圧(+4.5V~+5.5V)                                                                                                                                                    |

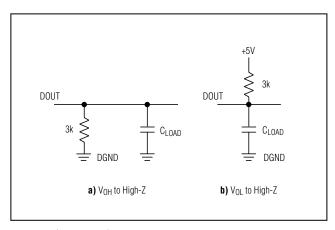

図1. イネーブル時間用の負荷回路

図2. ディセーブル時間用の負荷回路

詳細

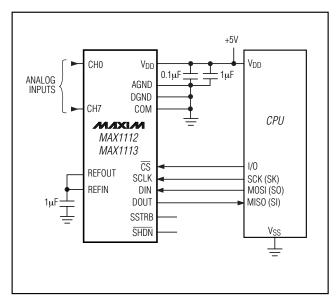

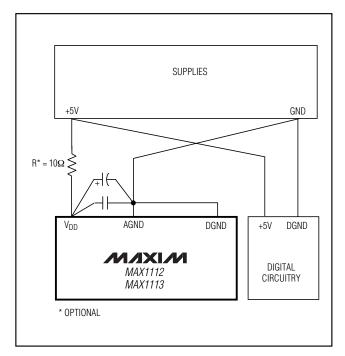

MAX1112/MAX1113アナログディジタルコンバータ (ADC)は、逐次比較型の変換技法及び入力トラック/ホールド(T/H)回路を使用することによって、アナログ信号を8ビットのディジタル出力に変換します。フレキシブルなシリアルインタフェースにより、マイクロプロセッサ(μP)とのインタフェースを容易にしています。図3に標準動作回路を示します。

#### 疑似差動入力

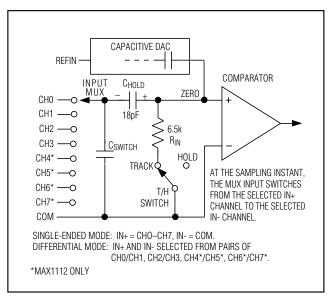

図4は、このADCのアナログコンパレータのサンプリング構成を示す等価入力回路です。シングルエンドモードでは、IN+が選択された入力チャネルCH\_に内部でスイッチングされ、IN-はCOMにスイッチングされます。差動モードの場合のIN+及びIN-は、CH0/CH1、CH2/CH3、CH4/CH5、及びCH6/CH7の組み合わせの中から選択します。MAX1112及びMAX1113のチャネルの設定は、それぞれ表1及び表2を参考に行ってください。

差動モードでは、IN-及びIN+が内部でアナログ入力のどちらかにスイッチングされます。この構成ではIN+のところの信号だけがサンプリングされるため、疑似差動と呼ばれています。リターン側(IN-)は、変換中、AGNDに対して±0.5LSB(最良の結果を得るには±0.1LSB)以内で安定している必要があります。これを実現するには、必要に応じて(選択したアナログ入力の)IN-とAGNDの間に0.1µFのコンデンサを接続してください。

アクイジション期間中は、正入力(IN+)として選択されたチャネルにより、コンデンサ $C_{HOLD}$ が充電されます。アクイジション期間は2 SCLKサイクル間続き、入力制御ワードの最後のビットが入力された後のSCLKの立下がリエッジで完了します。アクイジション期間の終了時にT/Hスイッチが開き、 $C_{HOLD}$ の電荷をIN+の信号のサンプルとして保持します。

変換期間は、入力マルチプレクサがC<sub>HOLD</sub>を正入力 (IN+)から負入力(IN-)にスイッチングした時から始まります。シングルエンドモードにおけるIN-は、COMです。このため、コンパレータの入力におけるノードZEROが不平衡になります。変換サイクルの残りの時間で、容量性DACがノードZEROを8ビット分解能の制限範囲で 0Vに調節します。この動作は、18pF x [(V<sub>IN+</sub>) - (V<sub>IN-</sub>)] の電荷をC<sub>HOLD</sub>からバイナリ重み付の容量性DACに移すことと等価です。この結果、アナログ入力信号のディジタル表示が生成されます。

#### トラック/ホールド

T/Hは、8ビット制御ワードの6番目のビットがシフトインされた後の立下がリクロックエッジでトラッキングモードに入り、制御ワードの8番目のビットがシフトインされた後の立下がリクロックエッジでホールドモードに入ります。コンバータがシングルエンド入力用に設定されている場合は、IN-がCOMに接続され、コンバータは「+」入力をサンプリングします。コンバータが差動入力用に設定されている場合は、IN-が「-」入力に接続され、差(IN+-IN-)がサンプリングされます。変換完了時に正入力が再びIN+に接続され、CHOLDは入力信号電圧まで充電されます。

図3. 標準動作回路

図4. 等価入力回路

## 表1a. MAX1112のシングルエンドモードにおけるチャネル選択(SGL/ $\overline{DIF}$ = 1)

| SEL2 | SEL1 | SEL0 | СН0 | CH1 | CH2 | СНЗ | CH4 | CH5 | СН6 | CH7 | СОМ |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   |     |     |     |     |     |     |     | _   |

| 1    | 0    | 0    |     | +   |     |     |     |     |     |     | -   |

| 0    | 0    | 1    |     |     | +   |     |     |     |     |     | -   |

| 1    | 0    | 1    |     |     |     | +   |     |     |     |     | -   |

| 0    | 1    | 0    |     |     |     |     | +   |     |     |     | -   |

| 1    | 1    | 0    |     |     |     |     |     | +   |     |     | _   |

| 0    | 1    | 1    |     |     |     |     |     |     | +   |     | -   |

| 1    | 1    | 1    |     |     |     |     |     |     |     | +   | ı   |

## 表1b. MAX1112の差動モードにおけるチャネル選択(SGL/DIF = 0)

| SEL2 | SEL1 | SEL0 | СН0 | CH1 | CH2 | СНЗ | CH4 | CH5 | СН6 | CH7 |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   | -   |     |     |     |     |     |     |

| 0    | 0    | 1    |     |     | +   | -   |     |     |     |     |

| 0    | 1    | 0    |     |     |     |     | +   | -   |     |     |

| 0    | 1    | 1    |     |     |     |     |     |     | +   | _   |

| 1    | 0    | 0    | -   | +   |     |     |     |     |     |     |

| 1    | 0    | 1    |     |     | -   | +   |     |     |     |     |

| 1    | 1    | 0    |     |     |     |     | -   | +   |     |     |

| 1    | 1    | 1    |     |     |     |     |     |     | _   | +   |

## 表2a. MAX1113のシングルエンドモードにおけるチャネル選択(SGL/ $\overline{DIF}$ = 1)

| SEL2 | SEL1 | SEL0 | CH0 | CH1 | CH2 | СНЗ | СОМ |

|------|------|------|-----|-----|-----|-----|-----|

| 0    | 0    | Х    | +   |     |     |     | _   |

| 1    | 0    | Х    |     | +   |     |     | _   |

| 0    | 1    | Х    |     |     | +   |     | _   |

| 1    | 1    | Х    |     |     |     | +   | -   |

## 表2b. MAX1113の差動モードにおけるチャネル選択(SGL/DIF = 0)

| SEL2 | SEL1 | SEL0 | СН0 | CH1 | CH2 | СНЗ |

|------|------|------|-----|-----|-----|-----|

| 0    | 0    | Х    | +   | _   |     |     |

| 0    | 1    | Х    |     |     | +   | _   |

| 1    | 0    | Х    | -   | +   |     |     |

| 1    | 1    | Х    |     |     | _   | +   |

T/Hが入力信号を取込むために要する時間は、入力容量が充電される速さの関数になっています。入力信号のソースインピーダンスが高いとアクイジション時間は長くなるため、変換と変換の間の時間を長くする必要があります。アクイジション時間t<sub>ACQ</sub>は信号の取込みに必要な最低時間です。t<sub>ACQ</sub>は、次式で計算されます。

$t_{ACQ} = 6 \times (R_S + R_{IN}) \times 18pF$

ここで、 $R_{IN}$  = 6.5k 、 $R_S$  = 入力信号のソースインピーダンス、そして $t_{ACQ}$  は必ず $1\mu s$  以上です。ソースインピーダンスが2.4k 以下であれば、ADCのAC性能に大きな影響はありません。

#### 入力帯域幅

ADCの入力トラッキング回路の小信号帯域幅は1.5MHzであるため、高速の過渡現象の数値化、及びアンダーサンプリング技法を使用することにより帯域幅がADCのサンプリングレート以上の帯域の周期信号を測定できます。高周波信号が計測する周波数帯域にエイリアシングしてくるのを防ぐために、アンチエイリアシングフィルタリングをお勧めします。

#### アナログ入力

内部保護ダイオードによってアナログ入力が $V_{DD}$ と AGNDにクランプされているため、チャネル入力ピンは (AGND - 0.3V)  $\sim$  ( $V_{DD}$  + 0.3V) の範囲で損傷を起

こすことなくスイングできます。しかし、フルスケール付近で正確な変換を行うには、入力がV<sub>DD</sub>を50mV以上超えたり、AGNDを50mV以上下回ることがないようにします。

アナログ入力が電源を50mV以上超えた場合、オフチャネルの保護ダイオードに2mA以上の順方向バイアスをかけないでください。

MAX1112/MAX1113は、制御バイトのビット2及びビット3によって差動又はシングルエンド入力用に設定できます(表3)。シングルエンドモードでは、アナログ入力は内部でCOMを基準としており、フルスケール入力範囲はCOM  $\sim$  V<sub>REFIN</sub> + COMとなります。バイポーラ動作の場合は、COMをV<sub>RFFIN</sub>/2に設定してください。

差動モードの場合、ユニポーラモードを選択すると、差動入力範囲が0V~VREFINになります。ユニポーラモードでは、負の差動入力電圧が印加されると出力コードは無効(コードゼロ)になります。バイポーラモードでは差動入力範囲は±VREFIN/2に設定されます。このモードでは、入力同相範囲が両電源電圧を含んでいます。入力電圧範囲については、表4を参照してください。

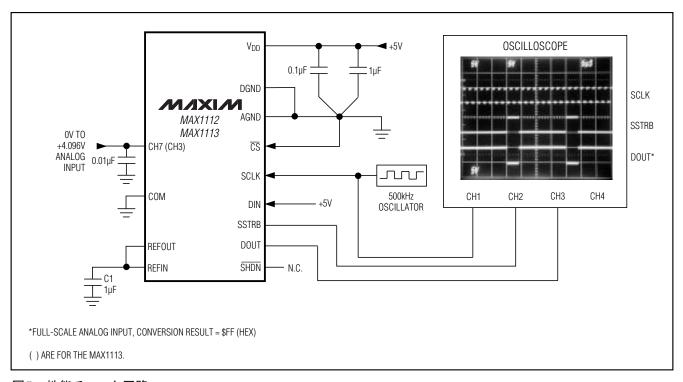

#### 性能チェック回路

MAX1112/MAX1113のアナログ性能を迅速に評価するには、図5の回路を使用してください。MAX1112/MAX1113では、各変換の前に制御バイトがDINに書き

#### 表3. 制御バイトフォーマット

| ビット7<br>( <b>MSB)</b> | ビット6 | ビット5 | ビット4 | ビット3    | ビット2    | ビット1 | ビット0<br>( <b>LSB)</b> |

|-----------------------|------|------|------|---------|---------|------|-----------------------|

| START                 | SEL2 | SEL1 | SEL0 | UNI/BIP | SGL/DIF | PD1  | PD0                   |

| ビット         | 名称                   | 内 容                                                                                                              |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------|

| 7 (MSB)     | START                | CSがローになった後の最初のロジック「1」が制御バイトの開始になります。                                                                             |

| 6<br>5<br>4 | SEL2<br>SEL1<br>SEL0 | 8つのチャネルのうちのどれを変換に使用するかを選択します(表1及び表2)。                                                                            |

| 3           | UNI/BIP              | 1 = ユニポーラ、0 = バイポーラ。ユニポーラ変換モードかバイポーラ変換モードかを選択します(表4)。                                                            |

| 2           | SGL/DIF              | 1 = シングルエンド、0 = 差動。シングルエンド変換か差動の変換かを選択します。シングルエンドモードの入力信号電圧は、COMを基準としています。差動モードでは2つのチャネルの間の電圧差が測定されます。表1及び表2を参照。 |

| 1           | PD1                  | 1 = 完全動作、0 = パワーダウン<br>完全動作モードかパワーダウンモードかを選択します。                                                                 |

| 0 (LSB)     | PD0                  | 1 = 外部クロックモード、0 = 内部クロックモード<br>外部クロックモードか内部クロックモードかを選択します。                                                       |

#### 表4. フルスケール及びゼロスケール電圧

| ユニポーラモード                 |        | バイポーラモード                         |        |                                  |  |

|--------------------------|--------|----------------------------------|--------|----------------------------------|--|

| フルスケール                   | ゼロスケール | 正のフルスケール                         | ゼロスケール | 負のフルスケール                         |  |

| V <sub>REFIN</sub> + COM | COM    | +V <sub>REFIN</sub> / 2<br>+ COM | COM    | -V <sub>REFIN</sub> / 2<br>+ COM |  |

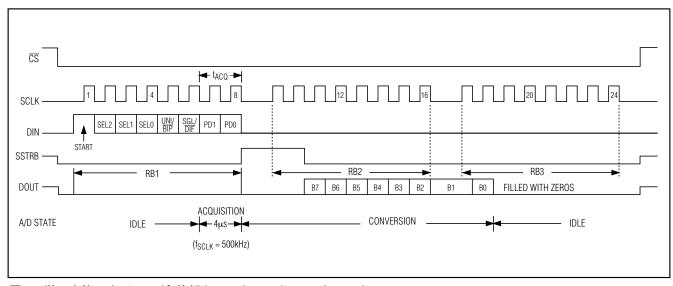

込まれる必要があります。DINを+5Vにすると、\$FF (HEX)の制御バイトが書き込まれます。これは、変換と変換の間にパワーダウンのない外部クロックモードのCH7(MAX1112)又はCH3(MAX1113)のシングルエンドユニポーラ変換をトリガします。外部クロックモードでは、8ビット変換結果の最上位ビットがDOUTからシフトアウトされる前に、SSTRB出力が2クロック周期分がパルス的にハイになります。アナログ入力を変化させると出力コードが変わります。1変換当たり合計10クロックサイクルが必要です。SSTRB及びDOUT出力の遷移は、SCLKの立下がりエッジで起こります。

#### 变換開始方法

変換は、制御バイトをDINにクロックインすることによって開始されます。 CS がローの場合、SCLKクロックの各立上がリエッジ毎にDINからMAX1112/MAX1113 の内部シフトレジスタへと1ビットずつクロック入力さ

れます。CSが下がった後で最初に来たロジック「1」の ビットが制御バイトのMSBを定義します。この最初の 「スタート」ビットが来るまでは、ロジック「0」のビット がいくつDINにクロック入力されても一切影響はありま せん。表3に、制御バイトのフォーマットを示します。

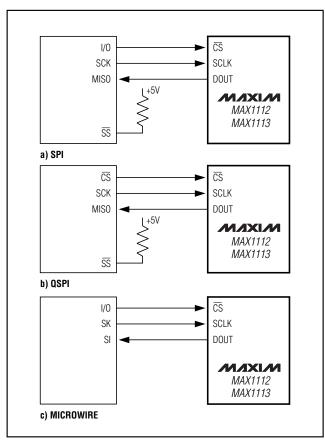

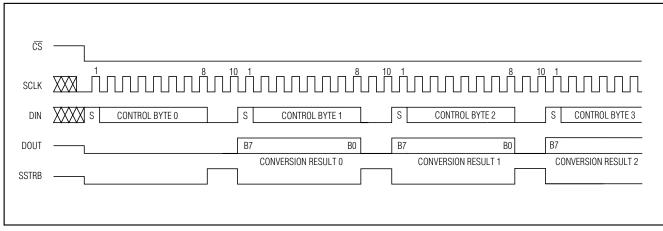

MAX1112/MAX1113は、MICROWIRE、SPI及びQSPI機器とコンパチブルです。SPIの場合は、SPI制御レジスタで正しいクロック極性及びサンプリングエッジを選択してください(CPOL = 0 及びCPHA = 0に設定してください)。MICROWIRE、SPI及びQSPIはいずれもバイトの送信とバイトの受信を同時に行います。標準動作回路(図3)を使用した場合、最もシンプルなソフトウェアインタフェースでは8ビット転送を3回行うことにより変換できます(1回の8ビット転送ではADCを設定し、残り後2回の8ビット転送では8ビット変換結果をクロック出力します)。図6に、MAX1112とMAX1113に共通なシリアルインタフェースの接続を示します。

図5. 性能チェック回路

図6. MAX1112とMAX1113に共通なシリアルインタ フェースの接続

シンプルなソフトウェアインタフェース

CPUがシリアルクロックを発生するように、CPUのシリアルインタフェースがマスターモードで動作していることを確認してください。クロック周波数は、50kHz~500kHzの範囲で選択してください。

- 1) 制御バイトを外部クロックモードに設定し、これを TB1と呼びます。TB1のフォーマットは、バイナリ の1XXXXX11になります。ここで、Xは選択された 特定のチャネル及び変換モードを意味します。

- 2) CPUの汎用I/Oラインを使用して、MAX1112/ MAX1113のCSCSをローにします。

- 3) TB1を送信し、同時に1バイトを受信します。受信した1バイトをRB1と呼びます。RB1を無視します。

- 4) 全てゼロで構成される1バイト(\$00 HEX)を送信し、 同時にバイトRB2を受信します。

- 5) 全てゼロで構成される1バイト(\$00 HEX)を送信し、 同時にバイトRB3を受信します。

- 6) CSをハイにします。

図7に、このシーケンスのタイミングを示します。バイトRB2とRB3は、先行のゼロ2個及び後続ビットである6つのゼロに挟まれた変換結果を含んでいます。合計変換時間は、シリアルクロック周波数及び8ビット転送間のアイドル時間の関数です。T/Hが過剰にドループするのを防ぐために、合計変換時間が1msを超えないようにしてください。

図7. 単一変換のタイミング(外部クロックモード、24クロック)

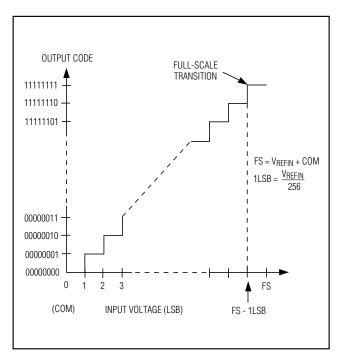

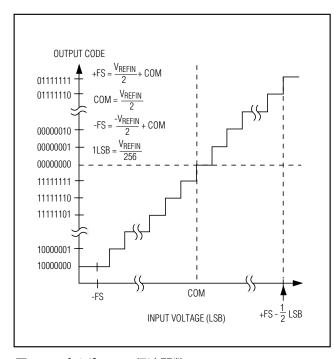

#### ディジタル出力

ユニポーラ入力モードにおける出力は、ストレートなバイナリです(図15)。バイポーラ入力の場合、出力は2の補数形式になります(図16)。データは、SCLKの立下がリエッジで、MSBを先頭にクロックアウトされます。

#### クロックモード

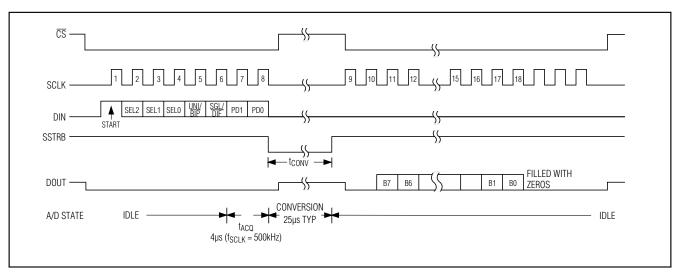

MAX1112/MAX1113では、外部シリアルクロック又は内部クロックのいずれかを使用することにより、逐次比較型変換を行うことができます。どちらのクロックモードの場合も、外部クロックによってMAX1112/MAX1113からデータをシフトイン/アウトします。制御バイトのビットPD0により、クロックモードがプログラムされます。図8~図11に、両方のモードに共通するタイミングの特性を示します。

#### 外部クロック

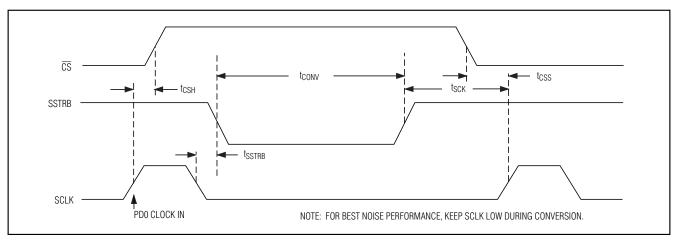

外部クロックモードにおける外部クロックは、データを シフトイン/アウトするだけでなく、A/D変換のステップ の駆動も行います。SSTRBは制御バイトの最後のビットの後で、2クロック周期分がパルス的にハイになります。逐次比較用のビット決定はそれに続くSCLKの立下がリエッジ8個でそれぞれ行われ、DOUTに出力されます(図7)。8個のデータビットがクロックアウトされた後のクロックパルスはDOUTピンからゼロをクロックアウトすることになります。

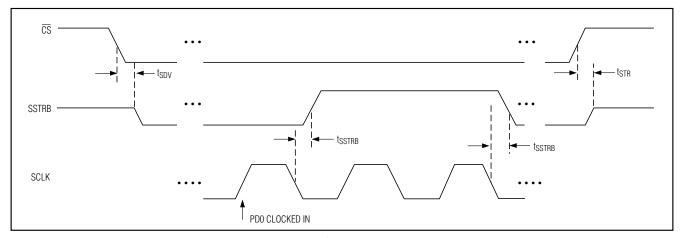

CSがハイになると、SSTRB及びDOUTはハイインピーダンス状態になります。そして、その次のCSの立下がリエッジでSSTRBはロジックローを出力します。図9に、外部クロックモードにおけるSSTRBのタイミングを示します。

変換は、1ms以内に完了する必要があります。完了しない場合は、サンプルアンドホールドコンデンサのドループによって変換結果が劣化することがあります。シリアルクロック周波数が50kHz以下の場合やシリアルクロックの割込みによって変換周期が1msを超える可能性がある場合は、内部クロックモードを使用してください。

図8. シリアルインタフェースのタイミングの詳細

図9. 外部クロックモードにおけるSSTRBのタイミングの詳細

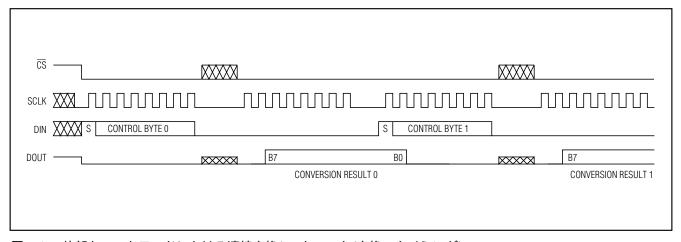

図10. 内部クロックモードのタイミング

図11. 内部クロックモードにおけるSSTRBのタイミングの詳細

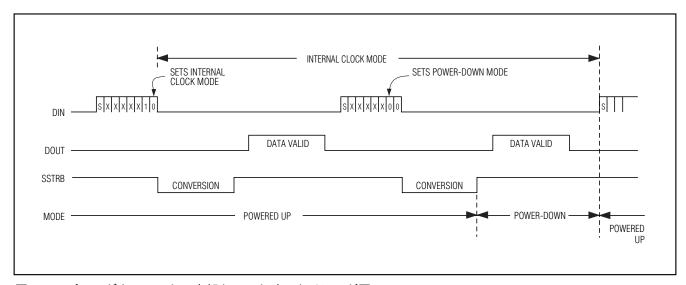

#### 内部クロック

内部クロックモードでは、µPがSAR変換クロックを動作させる役割から解放され、変換結果はプロセッサの都合のよいときに、2MHzまでの任意のクロックレートで読取ることができます。SSTRBは変換開始時にローになり、変換が完了するとハイになります。SSTRBは25µs(typ)間ローに留まりますが、最高のノイズ性能を得るには、その間SCLKをローに保つようにします。

変換中は、内部レジスタにデータが保管されます。 変換の完了後任意の時点で、SCLKがこのレジスタから データをクロックアウトします。SSTRBがハイになっ た後、2番目の立下がリクロックエッジでDOUTに変換 結果のMSBが出力され、続いて残りのビットがMSBを 先頭にしたフォーマットで出力されます(図10)。一旦 変換が開始された後は、CSをローに保持する必要はありません。CSをハイにするとデータがMAX1112/MAX1113にクロックインされなくなり、DOUTがスリーステートになりますが、すでに進行中の内部クロックモードの変換に悪影響を与えることはありません。内部クロックモードが選択されている場合は、CSがハイになってもSSTRBがハイインピーダンス状態にはなりません。

図11に、内部クロックモードにおけるSSTRBのタイミングを示します。このモードでは、最小アクイジションタイム $(t_{ACQ})$ が $1\mu$ S以上に保持されている限り2.0MHzまでのクロックレートでデータをMAX1112/MAX1113にシフトインできると共に、シフトアウトすることもできます。

図12a. 外部クロックモードにおける連続変換(10クロック/変換のタイミング)

図12b. 外部クロックモードにおける連続変換(16クロック/変換のタイミング)

#### データフレーミング

変換は、CSの立下がりエッジでは開始されません。DINにクロックインされる最初のロジックハイはスタートビットとして解釈され、これが制御バイトの最初のビットとなります。変換は8番目の制御ビット(PD0ビット)がDINにクロックインされた後のSCLKの立下がりエッジで開始されます。スタートビットの定義は、以下のとおりです。

コンバータがアイドル状態である任意の時間(例えば V<sub>DD</sub>が印加された後)に、CSがローの状態でDINに クロックインされてきた最初のハイビット。

#### 又は

進行中の変換のMSBがDOUTピンに出てきた後に、 DINにクロックインされてきた最初のハイビット。 現在の変換が完了する前にCSがトグルされると、その後に初めてDINにクロックインされてきたハイビットがスタートビットとして認識されます。現在の変換は中止され、新しい変換が開始されます。

MAX1112/MAX1113が動作できる最高速度は、10 クロック/変換です。図12aに、外部クロックモードで10SCLKサイクル毎に変換を実行するために必要なシリアルインタフェースタイミングを示します。

殆どのマイクロコントローラの場合、変換は8 SCLK クロックの倍数で発生させる必要があります。従って、マイクロコントローラによってMAX1112/MAX1113 を動作させる最高速度は、通常16クロック/変換ということになります。図12bに、外部クロックモードで16 SCLKサイクル毎に変換を実行するために必要なシリアルインタフェースタイミングを示します。

アプリケーション情報 \_\_\_\_\_

#### パワーオンリセット

MAX1112/MAX1113は、最初に電源が入った時に SHDNがローでない場合、内部パワーオンリセット回路 により内部クロックモードで起動されます。SSTRBは パワーアップ時にはハイで、CSがローの場合は、DIN の最初のロジック1がスタートビットと見なされます。DOUTは、変換が行われるまではゼロをシフトアウトします。リファレンス電圧が安定するまでは変換を行わないでください(「タイミング特性」の中のウェイクアップ時間の仕様を参照)。

#### パワーダウン

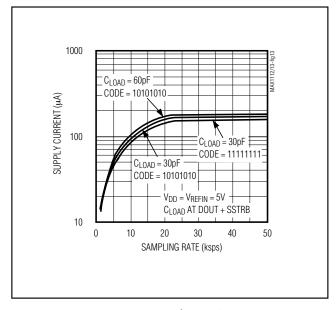

最大サンプリングレートよりも遅いスピードで動作している場合、MAX1112/MAX1113の自動パワーダウンモードによって変換と変換の間でコンバータが低電流のシャットダウン状態になるため、電力が節約されます。図13に、平均消費電流をサンプリングレートの関数として示します。

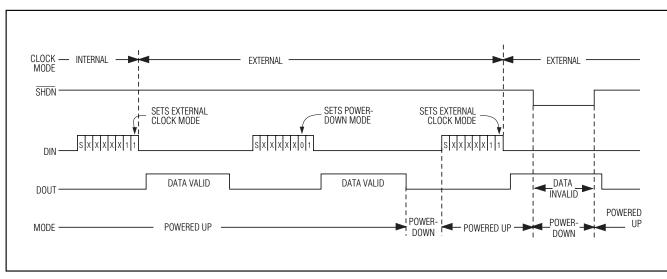

パワーダウンを選択するには、SHDNがハイ又はフローティングの状態でDIN制御バイトのPD1を使用します (表3)。SHDNをローにすることにより、適宜コンバータを完全にシャットダウンできます。SHDNは、制御バイトのPD1をオーバーライドします。図14a及び図14bに、外部及び内部クロックモード時の様々なパワーダウンシーケンスを示します。

#### ソフトウェアのパワーダウン

制御バイトのビットPD1を使用することにより、ソフトウェアのパワーダウンを起動できます。ソフトウェアのパワーダウンが発生すると、変換が完了するまでADCは最後に指定されたクロックモードで動作し続けます。その後、ADCはパワーダウンし、低自己消費電流状態になります。内部クロックモードにおけるインタフェースは、MAX1112/MAX1113がソフトウェアのパワーダウンに入った後でもアクティブ状態を保ち、変換結果をクロックアウトできます。

DINの最初のロジック「1」がスタートビットと見なされ、これによってMAX1112/MAX1113はパワーアップし

表5. ハード配線によるパワーダウンと 内部リファレンス状態

| SHDN状態  | 素子のモード | 内部リファレンス |  |

|---------|--------|----------|--|

| 1       | イネーブル  | ディセーブル   |  |

| フローティング | イネーブル  | イネーブル    |  |

| 0       | パワーダウン | ディセーブル   |  |

ます。DINワードがPD1 = 1を含んでいると、チップは パワーアップ状態に留まります。PD1 = 0の時は1回 だけ変換を行い、その後再びパワーダウンします。

#### ハードウェアのパワーダウン

$\overline{SHDN}$ ピンをローにすると、コンバータはハード配線のパワーダウン状態に入ります。ソフトウェアのパワーダウンモードとは異なり、変換は完了せずに、 $\overline{SHDN}$ がローになると同時に停止します。 $\overline{SHDN}$ は、内部リファレンスの状態も制御します(表5)。 $\overline{SHDN}$ をフローティング状態にすると、4.096V電圧リファレンスがイネーブルされます。 $\overline{SHDN}$ がフローティングの状態で通常動作に戻る時は、約1M ×  $C_{LOAD}$ の $t_{RC}$ ディレーがあります( $C_{LOAD}$ は $\overline{SHDN}$ ピンでの容量性負荷です)。 $\overline{SHDN}$ をハイにすると内部リファレンスがディセーブルされるため、外部リファレンスを使用して電力を節約できます。

#### 外部リファレンス

1V~V<sub>DD</sub>の外部リファレンスをREFIN端子に直接接続してください。REFINでのDC入力インピーダンスは非常に大きく、リーク電流(10nA typ)のみに起因します。変換中、リファレンスは最大平均負荷電流20µAを供給することを要求され、また変換クロック周波数における出力インピーダンスが1k 以下であることが必要です。リファレンスの出力インピーダンスがこれより大きかったり、ノイズが大きい場合は、0.1µFコンデンサを使用してREFINの近くでバイパスしてください。

MAX1112/MAX1113で外部リファレンスを使用する場合は、SHDNをV<sub>DD</sub>に接続して内部リファレンスをディセーブルすることにより、消費電力を節減してください。

図13. 平均消費電流対サンプリングレート

図14a. パワーダウンモード、外部クロック時のタイミング図

図14b. パワーダウンモード、内部クロック時のタイミング図

#### 内部リファレンス

MAX1112/MAX1113を内部リファレンスで使用するには、REFINをREFOUTに接続してください。内部リファレンスにおけるMAX1112/MAX1113のフルスケール範囲は、ユニポーラ入力で4.096V(typ)、バイポーラ入力で $\pm 2.048V$ です。内部リファレンスは、REFINピンのできるだけ近くに取り付けた $1\mu$ FコンデンサでAGNDにバイパスしてください。

#### 伝達関数

表4に、ユニポーラ及びバイポーラモードでのフルスケール電圧範囲を示します。図15は公称ユニポーラI/O 伝達関数、図16はバイポーラI/O伝達関数を示しています(4.096Vリファレンス使用時)。コード遷移は、整数のLSB値の位置で起こります。出力コーディングはバイナリで、ユニポーラ動作では1LSB = 16mV(4.096V/256)、バイポーラ動作では1LSB = 16mV[(4.096V/256)]となります。

図15. ユニポーラの伝達関数

図16. バイポーラの伝達関数

図17. 電源グランド接続図

### レイアウト、グランド、及びバイパス

最高の性能を得るには、プリント回路基板を使用してください。ワイヤラップボードはお勧めできません。ボードレイアウトについては、ディジタル信号ラインとアナログ信号ラインが分離されるようにしてください。アナログとディジタル(特にクロック)ラインを互いに平行に走らせないでください。又、ディジタルラインがADCパッケージの下に配置されないようにしてください。

図17に、推奨されるシステムグランド接続法を示します。ロジックグランドとは別に、シングルポイントアナロググランド(スターグランドポイント)をAGNDのところで設定し、その他のアナロググランド及びDGNDは全てこのグランドに接続してください。このグランドには、その他のディジタルシステムグランドを接続しないでください。ノイズを排除するために、スターグランドから電源へのグランドリターンはできるだけ短くすると共に、低インピーダンスにしてください。

V<sub>DD</sub>電源内の高周波ノイズが、ADCのコンパレータに影響を与える可能性があります。この電源はMAX1112/MAX1113のV<sub>DD</sub>ピンに近いところで、0.1µF及び1µFコンデンサを使用してスターグランドにバイパスしてください。最高の電源ノイズ除去比を得るために、コンデンサのリード線をできるだけ短くしてください。+5V電源のノイズが特に大きい場合は、10 抵抗を接続してローパスフィルタを形成することができます。

### ピン配置 \_\_\_\_

### 型番(続き) \_\_\_\_\_

| PART       | TEMP. RANGE     | PIN-PACKAGE    |

|------------|-----------------|----------------|

| MAX1112EPP | -40°C to +85°C  | 20 Plastic DIP |

| MAX1112EAP | -40°C to +85°C  | 20 SSOP        |

| MAX1112MJP | -55°C to +125°C | 20 CERDIP**    |

| MAX1113CPE | 0°C to +70°C    | 16 Plastic DIP |

| MAX1113CEE | 0°C to +70°C    | 16 QSOP        |

| MAX1113EPE | -40°C to +85°C  | 16 Plastic DIP |

| MAX1113EEE | -40°C to +85°C  | 16 QSOP        |

| MAX1113MJE | -55°C to +125°C | 16 CERDIP**    |

<sup>\*\*</sup>Contact factory for availability.

### チップ情報

TRANSISTOR COUNT: 1996

SUBSTRATE CONNECTED TO DGND

パッケージ

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。 マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

20 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600