#### 概要

MAX12553は、完全差動型広帯域トラックホールド(T/H) 入力アンプを備え、内蔵の低ノイズ量子化器を駆動する 3.3V、14ビット、65Mspsのアナログ-ディジタルコン バータ(ADC)です。アナログ入力段は、シングルエンド または差動信号で動作します。MAX12553は、低電力、 小型、及び高ダイナミック性能に最適化されています。 MAX12553は、ベースバンドから175MHz以上の入力 周波数に至るまで卓越したダイナミック性能を維持する ため、中間周波数(IF)のサンプリングアプリケーション に最適です。

MAX12553は、3.15V~3.60Vの単一電源で動作し、 消費電力がわずか363mWで、175MHzの入力周波数 における信号対雑音比(SNR)の標準値は71dBです。 MAX12553は、動作電力が低いことに加えて、アイドル 期間の電力を節約するために150µWのパワーダウン モードを備えています。

MAX12553は、フレキシブルなリファレンス構成と なっており、内部の2.048Vバンドギャップリファレンス を使用することも外部からリファレンスを印加することも 可能です。このリファレンス構成により、フルスケール のアナログ入力を±0.35V~±1.10Vの範囲で調整する ことが可能です。MAX12553は、差動アナログ入力 回路の設計を簡素化し、外付け部品点数を少なくする ために、コモンモードリファレンスを備えています。

MAX12553は、シングルエンド及び差動入力クロック 駆動の両方をサポートしています。ADC内部のデュー ティサイクルイコライザ(DCE)がクロックデューティ サイクルの大幅な変動を補償します。

ADCの変換結果は、14ビットパラレルCMOS対応出力 バスから得ることができます。ディジタル出力形式は、 2の補数またはグレイコードのいずれかを端子設定に よって選択することができます。データバリッドイン ジケータによって、信頼性の高いディジタルインタ フェースに一般的に必要とされる外付け部品が不要と なります。ディジタル電源入力は独立した1.7V~3.6V の広範な電圧で動作するため、MAX12553は様々な ロジックレベルとインタフェースすることができます。

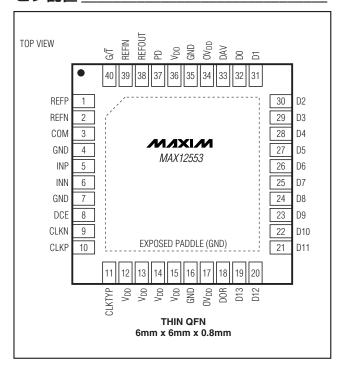

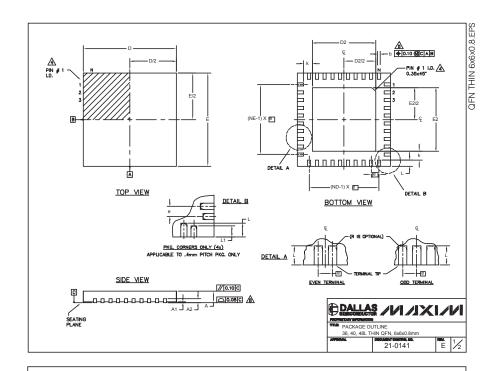

MAX12553は、6mm×6mm×0.8mmの40ピン、エク スポーズドパッド(EP)付き薄型OFNパッケージで提供 され、拡張温度範囲(-40℃~+85℃)で動作が保証され ています。

14ビット及び12ビットの高速ADCの全ファミリについ ては、「ピンコンパチブルバージョン」表をご覧ください。

#### アプリケーション\_

IF及びベースバンド通信レシーバ、セルラ、 ポイント間マイクロ波、HFC、WLAN 超音波及び医療用画像化

ポータブル計測機器

低電力データ収集

#### 特長

- ◆ 最高400MHzのダイレクトIFサンプリング

- ◆ 卓越したダイナミック性能 74.0dB/71dB SNR  $(f_{IN} = 3MHz/175MHzにおいて)$ 90.6dBc/80.7dBc SFDR  $(f_{IN} = 3MHz/175MHzにおいて)$

- ◆ 低ノイズフロア: -76dBFS

- ◆ 3.3V低電力動作 337mW(シングルエンドクロックモード) 363mW(差動クロックモード) 150µW(パワーダウンモード)

- ◆ 完全差動またはシングルエンドアナログ入力

- ◆ 調整可能なフルスケールアナログ入力レンジ: ±0.35V~±1.10V

- ◆ コモンモードリファレンス内蔵

- ◆ 2の補数またはグレイコードのCMOS対応出力

- ◆ データバリッドインジケータによってディジタル インタフェースが簡素化

- ◆ データアウトオブレンジインジケータ

- ◆ 小型、40ピン、エクスポーズドパッド付き薄型QFN パッケージ

- ◆ 評価キット(型番MAX12555 EVKIT)あり

| PART        | TEMP<br>RANGE     | PIN-PACKAGE                        | PKG<br>CODE |

|-------------|-------------------|------------------------------------|-------------|

| MAX12553ETL | -40°C to<br>+85°C | 40 Thin QFN<br>(6mm x 6mm x 0.8mm) | T4066-3     |

#### ピンコンパチブルバージョン

| PART     | SAMPLING<br>RATE (Msps) | RESOLUTION<br>(BITS) | TARGET APPLICATION |

|----------|-------------------------|----------------------|--------------------|

| MAX12553 | 65                      | 14                   | IF/Baseband        |

| MAX1209  | 80                      | 12                   | IF                 |

| MAX1211  | 65                      | 12                   | IF                 |

| MAX1208  | 80                      | 12                   | Baseband           |

| MAX1207  | 65                      | 12                   | Baseband           |

| MAX1206  | 40                      | 12                   | Baseband           |

ピン配置はデータシートの最後に記載されています。

\_ Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +3.6V                                            | Continuous Power Dissipation ( $T_A = +70$ °C) |        |

|--------------------------------------------------------------------------------|------------------------------------------------|--------|

| OV <sub>DD</sub> to GND0.3V to the lower of (V <sub>DD</sub> + 0.3V) and +3.6V | 40-Pin Thin QFN 6mm x 6mm x 0.8mm              |        |

| INP, INN to GND0.3V to the lower of $(V_{DD} + 0.3V)$ and +3.6V                | (derated 26.3mW/°C above +70°C)210             | 5.3mW  |

| REFIN, REFOUT, REFP, REFN, COM                                                 | Operating Temperature Range40°C to             | +85°C  |

| to GND0.3V to the lower of (VDD + 0.3V) and +3.6V                              | Junction Temperature                           | -150°C |

| CLKP, CLKN, CLKTYP, G/T, DCE,                                                  | Storage Temperature Range65°C to 4             | -150°C |

| PD to GND0.3V to the lower of (V <sub>DD</sub> + 0.3V) and +3.6V               | Lead Temperature (soldering 10s)               | -300°C |

| D13–D0, DAV, DOR to GND0.3V to (OV <sub>DD</sub> + 0.3V)                       |                                                |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, fCLK = 65MHz (50% duty cycle), TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)$

| PARAMETER                        | SYMBOL            | CONDITIONS                                                         | MIN  | TYP                | MAX   | UNITS           |

|----------------------------------|-------------------|--------------------------------------------------------------------|------|--------------------|-------|-----------------|

| DC ACCURACY (Note 2)             |                   |                                                                    | •    |                    |       | •               |

| Resolution                       |                   |                                                                    | 14   |                    |       | Bits            |

| Integral Nonlinearity            | INL               | f <sub>IN</sub> = 3MHz (Note 5)                                    |      | ±1.4               | ±4.2  | LSB             |

| Differential Nonlinearity        | DNL               | f <sub>IN</sub> = 3MHz, no missing codes over temperature (Note 3) |      | ±0.5               | ±1.0  | LSB             |

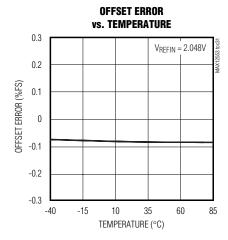

| Offset Error                     |                   | V <sub>REFIN</sub> = 2.048V                                        |      | ±0.1               | ±0.55 | %FS             |

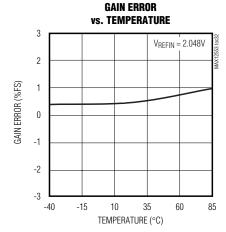

| Gain Error                       |                   | V <sub>REFIN</sub> = 2.048V                                        |      | ±0.5               | ±4.9  | %FS             |

| ANALOG INPUT (INP, INN)          |                   |                                                                    |      |                    |       |                 |

| Differential Input Voltage Range | V <sub>DIFF</sub> | Differential or single-ended inputs                                |      | ±1.024             |       | V               |

| Common-Mode Input Voltage        |                   |                                                                    |      | V <sub>DD</sub> /2 |       | V               |

| Input Capacitance                | CPAR              | Fixed capacitance to ground                                        |      | 2                  |       | ۵۲              |

| (Figure 3)                       | CSAMPLE           | Switched capacitance                                               |      | 4.5                |       | pF              |

| CONVERSION RATE                  |                   |                                                                    |      |                    |       |                 |

| Maximum Clock Frequency          | fCLK              |                                                                    | 65   |                    |       | MHz             |

| Minimum Clock Frequency          |                   |                                                                    |      |                    | 5     | MHz             |

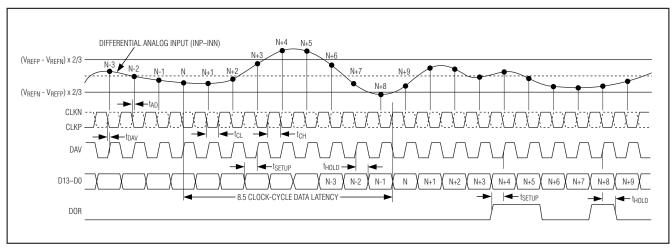

| Data Latency                     |                   | Figure 6                                                           |      | 8.5                |       | Clock<br>cycles |

| DYNAMIC CHARACTERISTICS (c       | lifferential in   | puts, Note 2)                                                      | ,    |                    |       |                 |

| Small-Signal Noise Floor         | SSNF              | Input at less than -35dBFS                                         |      | -76.0              |       | dBFS            |

|                                  |                   | f <sub>IN</sub> = 3MHz at -0.5dBFS (Note 8)                        | 69.3 | 74.0               |       |                 |

| Cinnal ta Naisa Datia            | OND               | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                              |      | 73.9               |       | -ID             |

| Signal-to-Noise Ratio            | SNR               | f <sub>IN</sub> = 70MHz at -0.5dBFS                                |      | 73.4               |       | dB              |

|                                  |                   | f <sub>IN</sub> = 175MHz at -0.5dBFS (Notes 7, 8)                  | 68.0 | 71.0               |       |                 |

|                                  |                   | f <sub>IN</sub> = 3MHz at -0.5dBFS (Note 8)                        | 69.2 | 73.9               |       |                 |

| Cional ta Naisa and Distortion   | CINIAD            | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                              |      | 73.1               |       | ٩D              |

| Signal-to-Noise and Distortion   | SINAD             | f <sub>IN</sub> = 70MHz at -0.5dBFS                                |      | 73.1               |       | dB              |

|                                  | i                 | f <sub>IN</sub> = 175MHz at -0.5dBFS (Notes 7, 8)                  |      |                    |       | 1               |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3.3V,\ OV_{DD}=2.0V,\ GND=0,\ REFIN=REFOUT\ (internal\ reference),\ V_{IN}=-0.5dBFS,\ CLKTYP=high,\ DCE=high,\ PD=low,\ G/\overline{T}=low,\ f_{CLK}=65MHz\ (50\%\ duty\ cycle),\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.$ ) (Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS                                                                                                     | MIN  | TYP   | MAX   | UNITS              |

|------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------|------|-------|-------|--------------------|

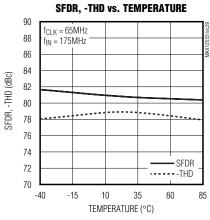

|                              |                 | f <sub>IN</sub> = 3MHz at -0.5dBFS                                                                             | 79.8 | 90.6  |       |                    |

| Caurious Free Dunamie Bance  | CEDD            | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                                                                          |      | 84.0  |       | alD a              |

| Spurious-Free Dynamic Range  | SFDR            | f <sub>IN</sub> = 70MHz at -0.5dBFS                                                                            |      | 87.8  |       | dBc                |

|                              |                 | f <sub>IN</sub> = 175MHz at -0.5dBFS (Note 7)                                                                  | 75.9 | 80.7  |       |                    |

|                              |                 | f <sub>IN</sub> = 3MHz at -0.5dBFS                                                                             |      | -90.6 | -80.2 |                    |

| T                            | TUD             | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                                                                          |      | -81.0 |       | ID.                |

| Total Harmonic Distortion    | THD             | f <sub>IN</sub> = 70MHz at -0.5dBFS                                                                            |      | -85.4 |       | dBc                |

|                              |                 | f <sub>IN</sub> = 175MHz at -0.5dBFS                                                                           |      | -78.9 | -71.3 |                    |

|                              |                 | f <sub>IN</sub> = 3MHz at -0.5dBFS                                                                             |      | -99   |       |                    |

|                              |                 | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                                                                          |      | -91   |       |                    |

| Second Harmonic              | HD2             | f <sub>IN</sub> = 70MHz at -0.5dBFS                                                                            |      | -92   |       | dBc                |

|                              |                 | f <sub>IN</sub> = 175MHz at -0.5dBFS                                                                           |      | -81   |       |                    |

|                              |                 | f <sub>IN</sub> = 3MHz at -0.5dBFS                                                                             |      | -94   |       |                    |

|                              | İ               | f <sub>IN</sub> = 32.5MHz at -0.5dBFS                                                                          |      | -84   |       | i                  |

| Third Harmonic               | HD3             | f <sub>IN</sub> = 70MHz at -0.5dBFS                                                                            |      | -88   |       | dBc                |

|                              |                 | f <sub>IN</sub> = 175MHz at -0.5dBFS                                                                           |      | -86   |       |                    |

|                              |                 | $f_{IN1} = 68.5MHz \text{ at -7dBFS}$<br>$f_{IN2} = 71.5MHz \text{ at -7dBFS}$                                 |      | -87   |       |                    |

| Intermodulation Distortion   | IMD             | $f_{\text{IN1}} = 172.5 \text{MHz} \text{ at -7dBFS}$<br>$f_{\text{IN2}} = 177.5 \text{MHz} \text{ at -7dBFS}$ |      | -80   |       | - dBc              |

| Third Order Interned Justice | IMO             | $f_{IN1} = 68.5MHz \text{ at -7dBFS}$<br>$f_{IN2} = 71.5MHz \text{ at -7dBFS}$                                 |      | -91   |       | dD o               |

| Third-Order Intermodulation  | IM3             | $f_{\text{IN1}}$ = 172.5MHz at -7dBFS<br>$f_{\text{IN2}}$ = 177.5MHz at -7dBFS                                 |      | -83   |       | - dBc              |

| Two-Tone Spurious-Free       | SFDRTT          | $f_{\text{IN1}} = 68.5 \text{MHz}$ at -7dBFS<br>$f_{\text{IN2}} = 71.5 \text{MHz}$ at -7dBFS                   |      | 90    |       | dDo                |

| Dynamic Range                | SFURI           | $f_{\text{IN1}}$ = 172.5MHz at -7dBFS<br>$f_{\text{IN2}}$ = 177.5MHz at -7dBFS                                 |      | 81    |       | - dBc              |

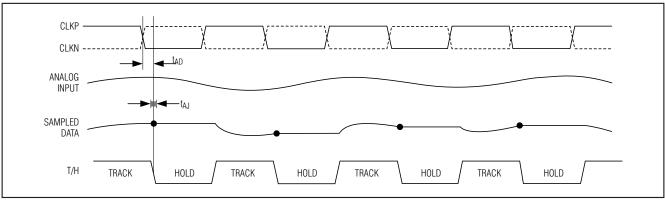

| Aperture Delay               | t <sub>AD</sub> | Figure 4                                                                                                       |      | 1.2   |       | ns                 |

| Aperture Jitter              | taj             | Figure 4                                                                                                       |      | <0.2  |       | psrms              |

| Output Noise                 | nout            | INP = INN = COM                                                                                                |      | 0.95  |       | LSB <sub>RMS</sub> |

| Overdrive Recovery Time      |                 | ±10% beyond full scale                                                                                         |      | 1     |       | Clock<br>cycles    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3.3V,\ OV_{DD}=2.0V,\ GND=0,\ REFIN=REFOUT\ (internal\ reference),\ V_{IN}=-0.5dBFS,\ CLKTYP=high,\ DCE=high,\ PD=low,\ G/\overline{T}=low,\ f_{CLK}=65MHz\ (50\%\ duty\ cycle),\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ T_A=+25^{\circ}C.)\ (Note\ 1)$

| PARAMETER                                         | SYMBOL            | CONDITIONS                                                                           | MIN                      | TYP                   | MAX                      | UNITS            |

|---------------------------------------------------|-------------------|--------------------------------------------------------------------------------------|--------------------------|-----------------------|--------------------------|------------------|

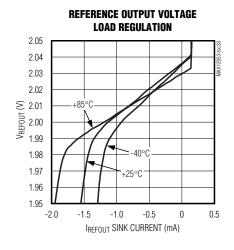

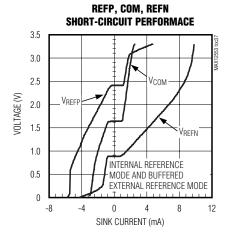

| INTERNAL REFERENCE (REFIN                         | = REFOUT; \       | V <sub>REFP</sub> , V <sub>REFN</sub> , and V <sub>COM</sub> are generated in        | ternally)                |                       |                          |                  |

| REFOUT Output Voltage                             | VREFOUT           |                                                                                      | 2.002                    | 2.048                 | 2.066                    | V                |

| COM Output Voltage                                | V <sub>COM</sub>  | V <sub>DD</sub> /2                                                                   |                          | 1.65                  |                          | V                |

| Differential Reference Output<br>Voltage          | V <sub>REF</sub>  | VREF = VREFP - VREFN = VREFIN x 3/4                                                  |                          | 1.536                 |                          | V                |

| REFOUT Load Regulation                            |                   |                                                                                      |                          | 35                    |                          | mV/mA            |

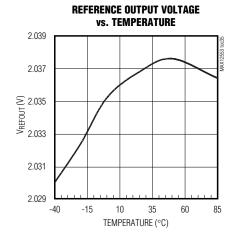

| REFOUT Temperature Coefficient                    | TCREF             |                                                                                      |                          | +50                   |                          | ppm/°C           |

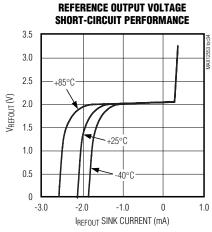

| DEFOLIT Chart Circuit Current                     |                   | Short to V <sub>DD</sub> —sinking                                                    |                          | 0.24                  |                          | A                |

| REFOUT Short-Circuit Current                      |                   | Short to GND—sourcing                                                                |                          | 2.1                   |                          | mA mA            |

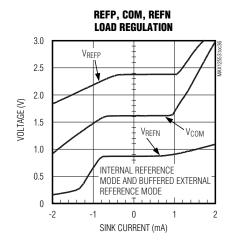

| <b>BUFFERED EXTERNAL REFEREN</b>                  | CE (REFIN di      | riven externally; V <sub>REFIN</sub> = 2.048V, V <sub>REFP</sub> , V <sub>REFP</sub> | FN, and V <sub>C</sub>   | <sub>OM</sub> are ger | nerated in               | ternally)        |

| REFIN Input Voltage                               | VREFIN            |                                                                                      |                          | 2.048                 |                          | V                |

| REFP Output Voltage                               | VREFP             | (V <sub>DD</sub> /2) + (V <sub>REFIN</sub> × 3/8)                                    |                          | 2.418                 |                          | V                |

| REFN Output Voltage                               | V <sub>REFN</sub> | (V <sub>DD</sub> /2) - (V <sub>REFIN</sub> x 3/8)                                    |                          | 0.882                 |                          | V                |

| COM Output Voltage                                | V <sub>COM</sub>  | V <sub>DD</sub> /2                                                                   | 1.60                     | 1.65                  | 1.70                     | V                |

| Differential Reference Output<br>Voltage          | V <sub>REF</sub>  | V <sub>REF</sub> = V <sub>REFP</sub> - V <sub>REFN</sub> = V <sub>REFIN</sub> x 3/4  | 1.463                    | 1.536                 | 1.601                    | V                |

| Differential Reference<br>Temperature Coefficient |                   |                                                                                      |                          | ±25                   |                          | ppm/°C           |

| REFIN Input Resistance                            |                   |                                                                                      |                          | >50                   |                          | МΩ               |

| UNBUFFERED EXTERNAL REFE                          | RENCE (REI        | FIN = GND; V <sub>REFP</sub> , V <sub>REFN</sub> , and V <sub>COM</sub> are a        | pplied exte              | rnally)               |                          | •                |

| COM Input Voltage                                 | V <sub>COM</sub>  | V <sub>DD</sub> /2                                                                   |                          | 1.65                  |                          | V                |

| REFP Input Voltage                                |                   | V <sub>REFP</sub> - V <sub>COM</sub>                                                 |                          | 0.768                 |                          | V                |

| REFN Input Voltage                                |                   | V <sub>REFN</sub> - V <sub>COM</sub>                                                 |                          | -0.768                |                          | V                |

| Differential Reference Input<br>Voltage           | V <sub>REF</sub>  | VREF = VREFP - VREFN = VREFIN x 3/4                                                  |                          | 1.536                 |                          | V                |

| REFP Sink Current                                 | IREFP             | V <sub>REFP</sub> = 2.418V                                                           |                          | 1                     |                          | mA               |

| REFN Source Current                               | I <sub>REFN</sub> | V <sub>REFN</sub> = 0.882V                                                           |                          | 0.7                   |                          | mA               |

| COM Sink Current                                  | Ісом              |                                                                                      |                          | 0.7                   |                          | mA               |

| REFP, REFN Capacitance                            |                   |                                                                                      |                          | 13                    |                          | рF               |

| COM Capacitance                                   |                   |                                                                                      |                          | 6                     |                          | рF               |

| CLOCK INPUTS (CLKP, CLKN)                         |                   |                                                                                      |                          |                       |                          |                  |

| Single-Ended Input High<br>Threshold              | VIH               | CLKTYP = GND, CLKN = GND                                                             | 0.8 x<br>V <sub>DD</sub> |                       |                          | V                |

| Single-Ended Input Low<br>Threshold               | VIL               | CLKTYP = GND, CLKN = GND                                                             |                          |                       | 0.2 x<br>V <sub>DD</sub> | V                |

| Differential Input Voltage Swing                  |                   | CLKTYP = high                                                                        |                          | 1.4                   |                          | V <sub>P-P</sub> |

| Differential Input Common-Mode<br>Voltage         |                   | CLKTYP = high                                                                        |                          | V <sub>DD</sub> /2    |                          | V                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=3.3V,\ OV_{DD}=2.0V,\ GND=0,\ REFIN=REFOUT$  (internal reference),  $V_{IN}=-0.5dBFS$ , CLKTYP = high, DCE = high, PD = low, G/T = low, f<sub>CLK</sub> = 65MHz (50% duty cycle), T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                                                                        | MIN                       | TYP   | MAX                       | UNITS |

|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|-------|

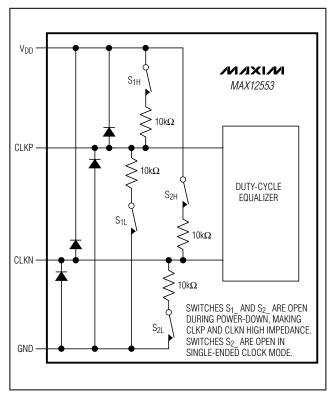

| Input Resistance                            | RCLK             | Figure 5                                                                                                          |                           | 5     |                           | kΩ    |

| Input Capacitance                           | Cclk             |                                                                                                                   |                           | 2     |                           | рF    |

| DIGITAL INPUTS (CLKTYP, G/T,                | PD)              |                                                                                                                   |                           |       |                           |       |

| Input High Threshold                        | V <sub>IH</sub>  |                                                                                                                   | 0.8 x<br>OV <sub>DD</sub> |       |                           | V     |

| Input Low Threshold                         | VIL              |                                                                                                                   |                           |       | 0.2 x<br>OV <sub>DD</sub> | V     |

| Input Lookaga Current                       |                  | $V_{IH} = OV_{DD}$                                                                                                |                           |       | ±5                        |       |

| Input Leakage Current                       |                  | $V_{IL} = 0$                                                                                                      |                           |       | ±5                        | μΑ    |

| Input Capacitance                           | C <sub>DIN</sub> |                                                                                                                   |                           | 5     |                           | рF    |

| DIGITAL OUTPUTS (D13-D0, DA                 | V, DOR)          |                                                                                                                   |                           |       |                           |       |

| Output Voltage Low                          | VoL              | D13-D0, DOR, I <sub>SINK</sub> = 200µA                                                                            |                           |       | 0.2                       | V     |

| Output voltage Low                          | VOL              | DAV, ISINK = 600µA                                                                                                |                           |       | 0.2                       | V     |

| Output Voltage High                         | VOH              | D13-D0, DOR, I <sub>SOURCE</sub> = 200μA                                                                          | OV <sub>DD</sub> - 0.2    |       |                           | V     |

| Output Voltage Filgri                       | VOH              | DAV, ISOURCE = 600µA                                                                                              | OV <sub>DD</sub> - 0.2    |       |                           | V     |

| Tri-State Leakage Current                   | ILEAK            | (Note 4)                                                                                                          |                           |       | ±5                        | μΑ    |

| D13-D0, DOR Tri-State Output<br>Capacitance | Cout             | (Note 4)                                                                                                          |                           | 3     |                           | pF    |

| DAV Tri-State Output<br>Capacitance         | C <sub>DAV</sub> | (Note 4)                                                                                                          |                           | 6     |                           | pF    |

| POWER REQUIREMENTS                          | •                |                                                                                                                   |                           |       |                           |       |

| Analog Supply Voltage                       | $V_{DD}$         |                                                                                                                   | 3.15                      | 3.3   | 3.60                      | V     |

| Digital Output Supply Voltage               | OV <sub>DD</sub> |                                                                                                                   | 1.7                       | 2.0   | V <sub>DD</sub> + 0.3V    | V     |

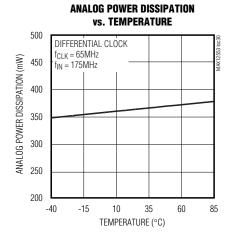

|                                             |                  | Normal operating mode,<br>f <sub>IN</sub> = 175MHz at -0.5dBFS, CLKTYP = GND,<br>single-ended clock               |                           | 102   |                           |       |

| Analog Supply Current                       | I <sub>VDD</sub> | Normal operating mode,<br>f <sub>IN</sub> = 175MHz at -0.5dBFS,<br>CLKTYP = OV <sub>DD</sub> , differential clock |                           | 110   | 123                       | mA    |

|                                             |                  | Power-down mode clock idle, PD = OV <sub>DD</sub>                                                                 |                           | 0.045 |                           |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f_{CLK} = 65MHz (50% duty cycle), T_A = -40°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 1)$

| PARAMETER                                 | SYMBOL            | CONDITIONS                                                                                                        | MIN | TYP  | MAX | UNITS |

|-------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                                           |                   | Normal operating mode,<br>f <sub>IN</sub> = 175MHz at -0.5dBFS, CLKTYP = GND,<br>single-ended clock               |     | 337  |     |       |

| Analog Power Dissipation                  | P <sub>DISS</sub> | Normal operating mode,<br>f <sub>IN</sub> = 175MHz at -0.5dBFS,<br>CLKTYP = OV <sub>DD</sub> , differential clock |     | 363  | 406 | mW    |

|                                           |                   | Power-down mode clock idle, PD = OV <sub>DD</sub>                                                                 |     | 0.15 |     |       |

| Digital Output Supply Current             | lovdd             | Normal operating mode, $f_{IN}$ = 175MHz at -0.5dBFS, $OV_{DD}$ = 2.0V, $C_L \approx 5pF$                         |     | 8.2  |     | mA    |

|                                           |                   | Power-down mode clock idle, PD = OV <sub>DD</sub>                                                                 |     | 20   |     | μΑ    |

| TIMING CHARACTERISTICS (Figure 1)         | ure 6)            |                                                                                                                   |     |      |     |       |

| Clock Pulse-Width High                    | tch               |                                                                                                                   |     | 7.7  |     | ns    |

| Clock Pulse-Width Low                     | t <sub>CL</sub>   |                                                                                                                   |     | 7.7  |     | ns    |

| Data-Valid Delay                          | t <sub>DAV</sub>  | C <sub>L</sub> = 5pF (Note 6)                                                                                     |     | 6.9  |     | ns    |

| Data Setup Time Before Rising Edge of DAV | tsetup            | C <sub>L</sub> = 5pF (Notes 5, 6)                                                                                 | 8.5 |      |     | ns    |

| Data Hold Time After Rising Edge of DAV   | <sup>†</sup> HOLD | C <sub>L</sub> = 5pF (Notes 5, 6)                                                                                 | 6.3 |      |     | ns    |

| Wake-Up Time from Power-Down              | twake             | V <sub>REFIN</sub> = 2.048V                                                                                       |     | 10   |     | ms    |

- **Note 1:** Specifications ≥+25°C guaranteed by production test; <+25°C guaranteed by design and characterization.

- Note 2: See definitions in the Parameter Definitions section at the end of this data sheet.

- Note 3: Specifications guaranteed by design and characterization. Devices tested for performance during production test.

- Note 4: During power-down, D13–D0, DOR, and DAV are high impedance.

- **Note 5:** Guaranteed by design and characterization.

- Note 6: Digital outputs settle to VIH or VIL.

- **Note 7:** Due to test-equipment-jitter limitations at 175MHz, 0.15% of the spectrum on each side of the fundamental is excluded from the spectral analysis.

- **Note 8:** Limit specifications include performance degradations due to a production test socket. Performance is improved when the MAX12553 is soldered directly to the PC board.

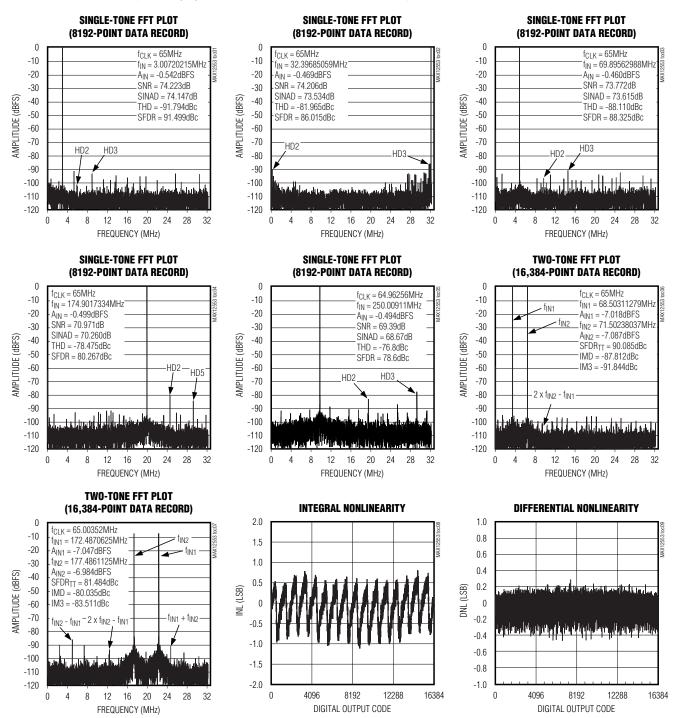

#### 標準動作特性

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f_{CLK} ≈ 65MHz (50% duty cycle), T_A = +25°C, unless otherwise noted.)$

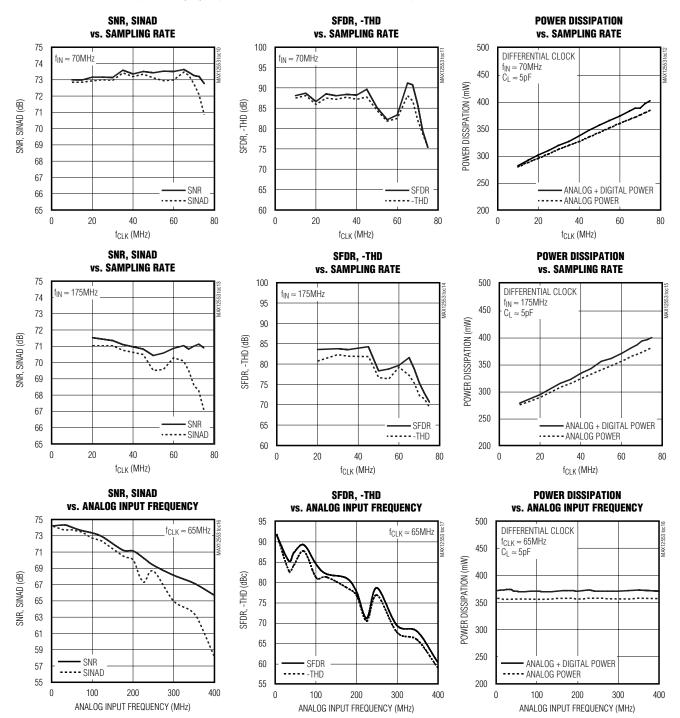

#### 標準動作特性(続き)

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f<sub>CLK</sub> <math>\approx$  65MHz (50% duty cycle), T<sub>A</sub> = +25°C, unless otherwise noted.)

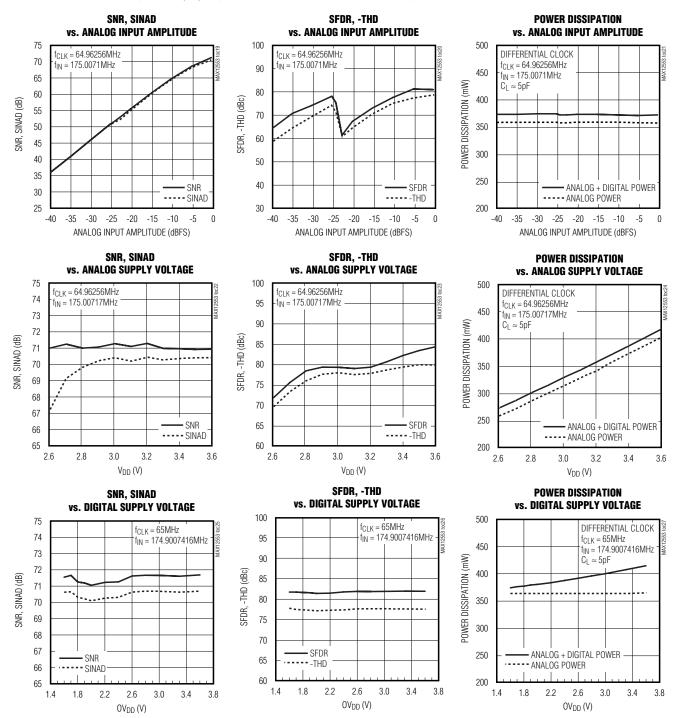

#### 標準動作特性(続き)

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f_{CLK} ≈ 65MHz (50% duty cycle), T_A = +25°C, unless otherwise noted.)$

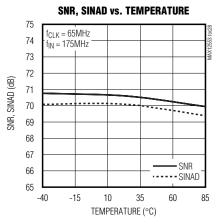

#### 標準動作特性(続き)

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f_{CLK} ≈ 65MHz (50% duty cycle), T_A = +25°C, unless otherwise noted.)$

#### 標準動作特性(続き)

$(V_{DD} = 3.3V, OV_{DD} = 2.0V, GND = 0, REFIN = REFOUT (internal reference), V_{IN} = -0.5dBFS, CLKTYP = high, DCE = high, PD = low, G/T = low, f_{CLK} \approx 65MHz (50% duty cycle), T_A = +25°C, unless otherwise noted.)$

### 端子説明\_\_\_\_\_

| 端子              | 名称               | 機 能                                                                                                                                                                                                                                               |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

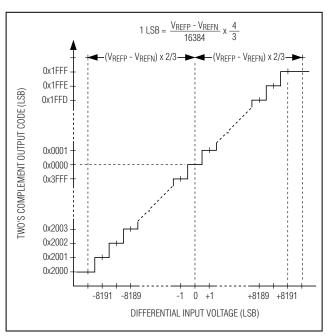

| 1               | REFP             | 正リファレンス $I/O$ 。フルスケールのアナログ入力範囲は、 $\pm (V_{REFP} - V_{REFN})$ x $2/3$ です。REFPを $0.1\mu$ FのコンデンサでGNDにバイパスしてください。REFPとREFNの間に $1\mu$ Fのコンデンサと $10\mu$ Fの コンデンサを並列にして接続してください。 $1\mu$ FのREFPとREFN間に接続するコンデンサは、プリント 基板のデバイスと同じ側でデバイスのできる限り近くに配置してください。 |

| 2               | REFN             | 負リファレンスI/O。フルスケールのアナログ入力範囲は $\pm$ ( $V_{REFP}$ - $V_{REFN}$ ) x 2/3です。REFNを $0.1\mu$ FのコンデンサでGNDにバイパスしてください。REFPとREFNの間に $1\mu$ Fのコンデンサと $10\mu$ Fのコンデンサを並列にして接続してください。 $1\mu$ FのREFPとREFN間に接続するコンデンサは、プリント 基板のデバイスと同じ側でデバイスのできる限り近くに配置してください。    |

| 3               | COM              | コモンモード電圧I/O。COMを2.2µFのコンデンサでGNDにバイパスしてください。 <b>2.2µFのCOMとGND間のコンデンサは、デバイスのできる限り近くに配置してください。</b> この2.2µFのコンデンサは、プリント基板のデバイスとは反対側に配置し、ビアを通してMAX12553に接続することができます。                                                                                   |

| 4, 7, 16,<br>35 | GND              | グランド。すべてのグランド端子とEPを互いに接続してください。                                                                                                                                                                                                                   |

| 5               | INP              | 正アナログ入力。                                                                                                                                                                                                                                          |

| 6               | INN              | 負アナログ入力。                                                                                                                                                                                                                                          |

| 8               | DCE              | デューティサイクルイコライザ入力。内蔵のデューティサイクルイコライザをディセーブルするためには、DCEをロー(GND)に接続してください。内蔵のデューティサイクルイコライザをイネーブルするためには、DCEをハイ(OV <sub>DD</sub> またはV <sub>DD</sub> )に接続してください。                                                                                         |

| 9               | CLKN             | 負クロック入力。差動クロック入力モード(CLKTYP = $OV_{DD}$ または $V_{DD}$ とする)では、差動クロック信号をCLKPとCLKNの間に接続してください。シングルエンドクロックモード(CLKTYP = GNDとする)では、シングルエンドクロック信号をCLKPに印加し、CLKNをGNDに接続してください。                                                                              |

| 10              | CLKP             | 正クロック入力。差動クロック入力モード(CLKTYP = $OV_{DD}$ または $V_{DD}$ とする)では、差動クロック信号をCLKPとCLKNの間に接続してください。シングルエンドクロックモード(CLKTYP = $GND$ とする)では、シングルエンドクロック信号をCLKPに印加し、CLKNをGNDに接続してください。                                                                           |

| 11              | CLKTYP           | クロックタイプ決定入力。シングルエンドクロック入力に決定するためには、 $CLKTYP$ を $GND$ に接続してください。差動クロック入力に決定するためには、 $CLKTYP$ を $OV_{DD}$ または $V_{DD}$ に接続してください。                                                                                                                    |

| 12–15, 36       | V <sub>DD</sub>  | アナログ電源入力。 $V_{DD}$ を3.15V $\sim$ 3.60V電源に接続してください。2.2 $\mu$ F以上と0.1 $\mu$ Fの並列接続コンデンサで $V_{DD}$ をGNDにバイパスしてください。すべての $V_{DD}$ 端子を同じ電位に接続してください。                                                                                                   |

| 17, 34          | OV <sub>DD</sub> | 出力ドライバ電源入力。 $OV_{DD}$ を $1.7V\sim V_{DD}$ の電源に接続してください。 $2.2\mu$ F以上と $0.1\mu$ Fの並列接続コンデンサで $OV_{DD}$ をGNDにバイパスしてください。                                                                                                                            |

| 18              | DOR              | データアウトオブレンジインジケータ。DORディジタル出力は、アナログ入力電圧が正常範囲から外れていることを示します。DORがハイのとき、アナログ入力はそのフルスケール範囲を超えています。DORがローのとき、アナログ入力はそのフルスケール範囲内にあります(図6)。                                                                                                               |

| 19              | D13              | CMOSディジタル出力、ビット13(MSB)                                                                                                                                                                                                                            |

| 20              | D12              | CMOSディジタル出力、ビット12                                                                                                                                                                                                                                 |

| 21              | D11              | CMOSディジタル出力、ビット11                                                                                                                                                                                                                                 |

| 22              | D10              | CMOSディジタル出力、ビット10                                                                                                                                                                                                                                 |

| 23              | D9               | CMOSディジタル出力、ビット9                                                                                                                                                                                                                                  |

| 24              | D8               | CMOSディジタル出力、ビット8                                                                                                                                                                                                                                  |

| 25              | D7               | CMOSディジタル出力、ビット7                                                                                                                                                                                                                                  |

| 26              | D6               | CMOSディジタル出力、ビット6                                                                                                                                                                                                                                  |

| 27              | D5               | CMOSディジタル出力、ビット5                                                                                                                                                                                                                                  |

#### 端子説明(続き)\_\_\_\_\_

| 端子 | 名称     | 機能                                                                                                                                                                                       |

|----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 | D4     | CMOSディジタル出力、ビット4                                                                                                                                                                         |

| 29 | D3     | CMOSディジタル出力、ビット3                                                                                                                                                                         |

| 30 | D2     | CMOSディジタル出力、ビット2                                                                                                                                                                         |

| 31 | D1     | CMOSディジタル出力、ビット1                                                                                                                                                                         |

| 32 | D0     | CMOSディジタル出力、ビットO(LSB)                                                                                                                                                                    |

| 33 | DAV    | データバリッド出力。DAVは入力クロックのデューティサイクル変動が補償されたクロックとしてシングルエンド出力するものです。DAVは、標準的には、MAX12553の出力データを外部の後続するディジタル回路にラッチするために使用されます。                                                                    |

| 37 | PD     | パワーダウン入力。パワーダウンモードにするためには、PDをハイに強制してください。通常動作にする場合はPDをローに強制してください。                                                                                                                       |

| 38 | REFOUT | 内部リファレンス電圧出力。内部リファレンスを使用する場合は、REFOUTを直接REFINに接続するか、またはREFOUTに抵抗分圧器を使用してREFINの電圧を設定してください。REFOUTを0.1µF以上のコンデンサでGNDにバイパスしてください。                                                            |

| 39 | REFIN  | リファレンス入力。内部リファレンスモード及びバッファ付き外部リファレンスモードでは、REFINを $0.1\mu$ F以上のコンデンサでGNDにバイパスしてください。これらのモードでは、 $V_{REFP}$ - $V_{REFN}$ = $V_{REFIN}$ × 3/4となります。バッファなし外部リファレンスモード動作では、REFINをGNDに接続してください。 |

| 40 | G/T    | 出力形式選択入力。 $2$ の補数ディジタル出力形式では、 $G/T$ を $GND$ に接続してください。グレイコードディジタル出力形式では、 $G/T$ を $OV_{DD}$ または $V_{DD}$ に接続してください。                                                                       |

| _  | EP     | エクスポーズドパッド。MAX12553では、エクスポーズドパッドを使用して低インダクタンスのグランド接続を実現します。保証性能を実現するために、EPをGNDに接続してください。複数のビアを使用してプリント基板の上側のグランドプレーンをプリント基板の下側のグランドプレーンに接続してください。                                        |

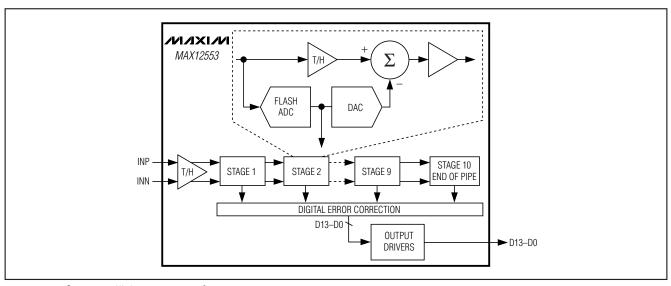

図1. パイプラインの構成 — ステージブロック

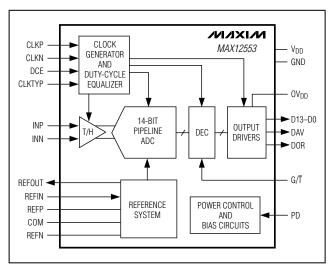

図2. 簡略化ファンクションダイアグラム

#### 詳細

MAX12553には、高速変換とともに、消費電力の最小化が可能な10段の完全差動パイプライン構成(図1)が採用されています。入力で取り込まれたサンプルは、1/2クロックサイクルごとにパイプラインの複数段を順次移動します。入力から出力までの全クロックサイクル待ち時間は8.5クロックサイクルです。

パイプラインの各コンバータ段は、その入力電圧をディジタル出力コードに変換します。最終段を除くすべての段で、入力電圧とディジタル出力コード間の誤差が増幅されて次のパイプライン段に入ります。ディジタル誤差補正は、各パイプライン段においてADCコンパレータのオフセットを補償し、ミッシングコードがないことを保証します。図2は、MAX12553のファンクションダイアグラムを示します。

#### 入力トラックホールド(T/H)回路

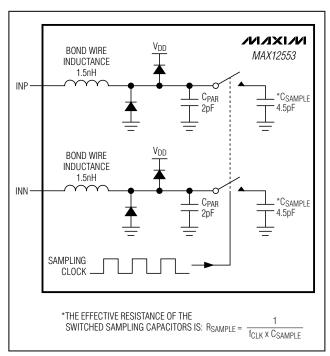

図3は、入力T/H回路の簡略化ファンクションダイアグラムを示しています。この入力T/H回路は、175MHz以上の高いアナログ入力周波数による動作が可能で、 $V_{DD}/2\pm0.5V$ のコモンモード入力電圧で動作します。

MAX12553のサンプリングクロックは、ADCのスイッチトキャパシタT/H構成(図3)を制御し、アナログ入力信号をサンプリングコンデンサに電荷として蓄えることができます。これらのスイッチは、サンプリングクロックがハイのとき閉じ(トラック)、サンプリングクロックがローのとき開きます(ホールド)(図4)。アナログ入力信号源は、サンプリングコンデンサの充放電に必要なダイナミック電流を流すことができなければなりません。信号の劣化を防ぐために、これらのコンデンサは1/2クロックサイクル以内に1/2LSBの精度まで充電される必要があります。

図3. 簡略化入力T/H回路

MAX12553のアナログ入力は、差動またはシングルエンド入力駆動を可能とします。差動入力によって最適な性能を得るために、INPとINNの入力インピーダンスをバランスさせてコモンモード電圧を中間の電源電圧(V<sub>DD</sub>/2)に設定してください。MAX12553は、内部リファレンスモード及びバッファ付き外部リファレンスモードで動作するとき、COM出力からV<sub>DD</sub>/2の最適なコモンモード電圧を出力します。このCOM出力電圧は、図10、11、及び12に示すように、入力回路網のバイアスに使用することができます。

#### リファレンス出力(REFOUT)

内部のバンドギャップリファレンスは、MAX12553で使用されるすべての内部電圧とバイアス電流の基準となります。パワーダウンロジック入力(PD)は、リファレンス回路をイネーブル/ディセーブルします。電源がMAX12553に印加されたときやPDがハイからローに遷移するときは、リファレンス回路が起動して整定するまでに10msを要します。MAX12553がパワーダウンとなっているとき、REFOUTはGNDに対して約17k $\Omega$ で接続されます。

内部バンドギャップリファレンスとそのバッファは、 $V_{REFOUT}$ に2.048Vを発生します。リファレンスの温度係数は、標準値で+50ppm/Cです。安定化のために、0.1 $\mu$ F以上の外付けバイパスコンデンサをREFOUTとGNDの間に接続してください。

図4. T/Hアパーチャタイミング

REFOUTは、外部回路に対して最大ソース電流が1.0mA、最大シンク電流が0.1mAで、負荷レギュレーションが35mV/mAです。REFOUTがGNDに短絡されたとき、 $I_{REFOUT}$ はソース電流を2.1mAに、また $V_{DD}$ に短絡されたときはシンク電流を0.24mAに制限して短絡保護されます。

#### アナログ入力とリファレンスの設定

MAX12553のフルスケールアナログ入力範囲は、コモンモード入力範囲が $V_{DD}/2\pm0.5V$ の場合、 $\pm0.35V\sim\pm1.10V$ の範囲で調整することができます。MAX12553には、3つのリファレンス動作モードがあります。REFINの電圧( $V_{REFIN}$ )によってリファレンス動作モードが設定されます(表1)。

MAX12553を内部リファレンスで動作させるためには、REFOUTをREFINに直接または抵抗分圧器を介して接続してください。このモードでは、 $V_{COM} = V_{DD}/2$ 、 $V_{REFP} = V_{DD}/2 + V_{REFIN} \times 3/8$ 、及び $V_{REFN} = V_{DD}/2 - V_{REFIN} \times 3/8$ であり、COM、REFP、及びREFNはローインピーダンス出力となります。REFIN入力インピーダンスは、非常に大きい値です(50M $\Omega$ を超える)。抵抗分圧器を

介してREFINを駆動する場合は、 $10k\Omega$ 以上の抵抗を使用してREFOUTの負荷が重くなることを避けてください。 バッファ付き外部リファレンスモードは、リファレンス源が外部リファレンスから与えられ、MAX125530 REFOUTからではない点を除くと、内部リファレンスモードと事実上は同じです。 バッファ付き外部リファレンスモードでは、REFINに安定した $0.7V\sim2.2V$ 電源を印加してください。このモードでは、 $V_{COM}=V_{DD}/2$ 、 $VREFP=V_{DD}/2+V_{REFIN}\times3/8$ 、及び $V_{REFN}=V_{DD}/2-V_{DD}/2$

V<sub>REFIN</sub> x 3/8であり、COM、REFP、及びREFNはロー

インピーダンス出力となります。

MAX12553をバッファなし外部リファレンスモードで動作させるためには、REFINをGNDに接続してください。REFINをGNDに接続すると、COM、REFP、及びREFN用の内蔵リファレンスバッファが不活性になりまま。各バッファが不活性になると、COM、REFP、及びREFNはハイインピーダンス入力になり、独立の外部リファレンス源による駆動を必要とします。 $V_{COM}$ を $V_{DD}/2\pm5\%$ に駆動し、 $V_{COM}=(V_{REFP}+V_{REFN})/2$ となるようにREFPとREFNを駆動してください。その場合フルスケールアナログ入力範囲は、 $\pm(V_{REFP}-V_{REFN})$  x 2/3となります。

表1. リファレンスモード

| V <sub>REFIN</sub>                                     | REFERENCE MODE                                                                                                                                                                                                                                 |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35% V <sub>REFOUT</sub> to 100%<br>V <sub>REFOUT</sub> | Internal Reference Mode. Drive REFIN with REFOUT either through a direct short or a resistive divider.  The full-scale analog input range is ±V <sub>REFIN</sub> /2:  VCOM = VDD/2  VREFP = VDD/2 + VREFIN × 3/8  VREFN = VDD/2 - VREFIN × 3/8 |

| 0.7V to 2.2V                                           | Buffered External Reference Mode. Apply an external 0.7V to 2.2V reference voltage to REFIN. The full-scale analog input range is ±V <sub>REFIN</sub> /2: VCOM = VDD/2 VREFP = VDD/2 + VREFIN × 3/8 VREFN = VDD/2 - VREFIN × 3/8               |

| <0.4V                                                  | Unbuffered External Reference Mode. Drive REFP, REFN, and COM with external reference sources. The full-scale analog input range is ±(V <sub>REFP</sub> - V <sub>REFN</sub> ) x 2/3.                                                           |

リファレンスの3つの動作モードはすべて、次のように同じ組合せのバイパスコンデンサを必要とします。COMを2.2 $\mu$ FのコンデンサでGNDにバイパスしてください。REFPとREFNを各々0.1 $\mu$ FのコンデンサでGNDにバイパスしてください。並列接続した1 $\mu$ Fと10 $\mu$ FのコンデンサでREFPをREFNにバイパスしてください。 $1\mu$ Fのコンデンサは、プリント基板の同じ側でデバイスのできる限り近くに配置してください。REFINとREFOUTを0.1 $\mu$ FのコンデンサでGNDにバイパスしてください。

詳細な回路例については、図13と14を参照してください。

#### クロック入力とクロック制御ライン (CLKP、CLKN、CLKTYP)

MAX12553は、差動とシングルエンドの両方のクロック入力で動作します。シングルエンドクロック入力動作では、CLKTYPをGNDに、CLKNをGNDに接続し、CLKPを外部のシングルエンドクロック信号で駆動してください。差動クロック入力動作では、CLKTYPをOV<sub>DD</sub>またはV<sub>DD</sub>に接続し、CLKPとCLKNを外部の差動クロック信号で駆動してください。クロックのジッタを低減するために、外部のシングルエンドクロックは立下りエッジを急峻にする必要があります。クロック入力はアナログ入力と考えて、配線ルートを他のアナログ入力及びディジタル信号ラインから離してください。

MAX12553がパワーダウンとなっているとき、CLKPとCLKNはハイインピーダンスになります(図5)。

MAX12553の規定されたSNR性能を得るためには、低クロックジッタが求められます。アナログ入力はクロック信号の立下りエッジでサンプリングされるため、このエッジのジッタは可能な限り小さくする必要があります。ジッタは、次の関係に従ってADCの最大SNR性能を制限します。

$$SNR = 20 \times log \left( \frac{1}{2 \times \pi f_{IN} \times t_{J}} \right)$$

ここで、f<sub>IN</sub>はアナログ入力周波数を表わし、t<sub>J</sub>はシステムの全クロックジッタを表わします。クロックジッタは、アンダサンプリングアプリケーションにおいて特に重要です。たとえば、クロックジッタが唯一のノイズ源であるとすると、175MHzの入力周波数で71dBの規定

図5. 簡略化クロック入力回路

SNRを実現するためには、クロックジッタを0.25ps 以下にしなければなりません。実際には、熱雑音や量子化雑音など、システムノイズに影響するノイズ源が他にもあるため、175MHzで規定された71dBのSNRを得るためにはクロックジッタを0.2ps以下にする必要があります。

#### クロックデューティサイクルイコライザ(DCE)

クロックデューティサイクルイコライザでは、デューティサイクルとは無関係の内部タイミング信号を生成するために遅延ロックループ(DLL)が使用されます。このDLLでは、MAX12553が新たなクロック周波数を獲得してロックするまでに約100クロックサイクルを必要とします。

クロックデューティサイクルイコライザをディセーブルすると、アナログ消費電流が1.5mA減少します。

図6. システムのタイミング図

#### システムのタイミング要件

図6は、クロック、アナログ入力、DAVインジケータ、DORインジケータ、及び変換出力データの関係を示しています。アナログ入力はクロック信号の立下りエッジでサンプリングされ、変換されたデータは8.5クロックサイクル後にディジタル出力に現れます。

DAVインジケータは、ディジタル出力に同期しており、データを後続のディジタル回路にラッチする用途に最適化されています。また、別の方法として、後続のディジタル回路を、変換クロック(CLKP-CLKN)の立上りエッジでラッチすることができます。

#### データバリッド出力(DAV)

DAVは、入力クロック(CLKP)をシングルエンドとして 出力するものです。出力データはDAVの立下りエッジで 変化し、DAVは出力データが有効になると立上ります (図6)。

デューティサイクルイコライザ入力(DCE)の状態によって、DAVの波形が変化します。デューティサイクルイコライザをディセーブルする(DCE = ロー)と、DAV信号はCLKPが6.8ns(t<sub>DAV</sub>)遅れた反転信号として現れ

ます。デューティサイクルイコライザをイネーブルする (DCE = ハイ)と、DAV信号はパルス幅がCLKPと関係 なく一定になります。DCEがハイまたはローのいずれの 場合も、D13~D0及びDORの出力データはDAVの立上りエッジの8.5ns前からDAVの立上りエッジの6.3ns後まで 有効で、DAVの立上りエッジはCLKPの立下りエッジから 6.9ns(t<sub>DAV</sub>)遅れて同期しています。

MAX12553がパワーダウン状態(PD=ハイ)にあるとき、DAVはハイインピーダンスです。DAVは600μAのシンク電流とソース電流を流すことができ、駆動能力がD13~D0及びDORの3倍です。DAVは、通常、MAX12553の出力データを外部の後続ディジタル回路にラッチするために使用されます。

大きなディジタル電流がMAX12553のアナログ部にフィードバックされてそのダイナミック性能が低下することを防止するために、DAVの容量性負荷をできる限り小さく(25pF未満)抑えてください。DAVの外部にバッファを設けると、DAVは容量性の重負荷から分離されます。外部バッファを介して後続のディジタル回路を駆動するDAVの例については、MAX12555の評価キットの回路図を参照してください。

#### データアウトオブレンジインジケータ(DOR)

DORディジタル出力は、アナログ入力電圧がレンジから外れているか否かを示します。DORがハイのとき、アナログ入力はレンジから外れています。DORがローのとき、アナログ入力はレンジ内にあります。有効な差動入力範囲は、 $(V_{REFP} - V_{REFN}) \times 3/4 \sim (V_{REFN} - V_{REFP}) \times 3/4$ です。信号がこの有効差動範囲外にある場合は、表2と図6に示すように、DORがハイになります。

DORは、DAVと同期しており、出力データD13~D0とともに遷移します。出力データの場合と同様に、DORの動作には8.5クロックサイクルの待ち時間があります(図6)。

MAX12553がパワーダウン状態(PD = ハイ)にあるとき、DORはハイインピーダンスです。DORは、PDの立上りエッジ後の10ns以内にハイインピーダンス状態になり、PDの立下りエッジの10ns後にアクティブになります。

#### ディジタル出力データ(D13~D0)、出力形式(G/T)

MAX12553は、14ビット、パラレル、トライステート 出力バスを備えています。D13~D0及びDORは、DAV の立下りエッジで更新され、DAVの立上りエッジで有効 になります。

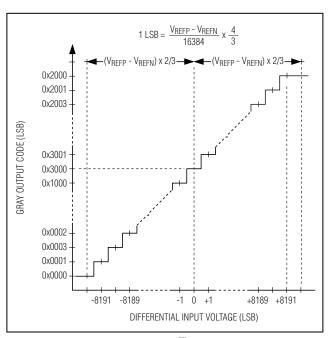

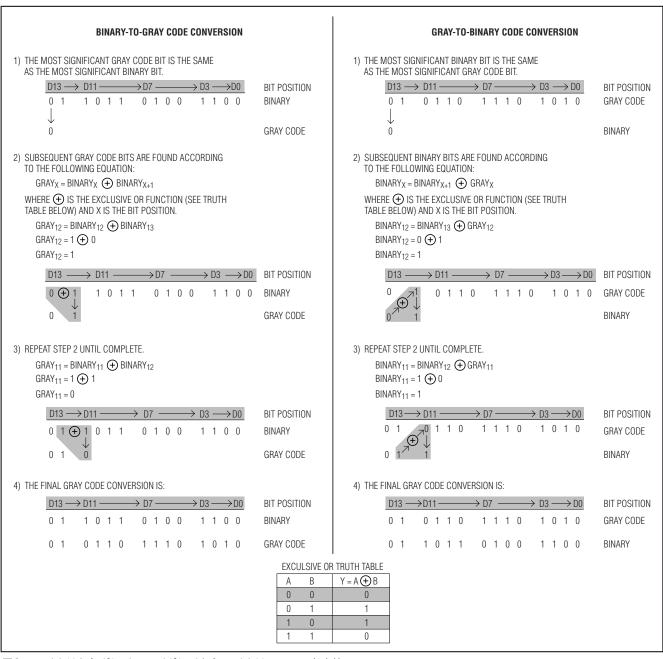

MAX12553の出力データ形式は、ロジック入力G/Tに応じてグレイコードまたは2の補数のいずれかとなります。G/Tがハイの場合は、出力データ形式はグレイコードです。G/Tがローの場合は、出力データ形式は2の補数です。バイナリからグレイ、及びグレイからバイナリへのコード変換例については、図8を参照してください。次式、表2、図7、及び図8によって、ディジタル出力とアナログ入力の関係が定まります。

$$V_{INP} - V_{INN} = (V_{REFP} - V_{REFN}) \times \frac{4}{3} \times \frac{CODE_{10} - 8192}{16384}$$

グレイコード(G/T=1)の場合は、

$$V_{INP} - V_{INN} = (V_{REFP} - V_{REFN}) \times \frac{4}{3} \times \frac{CODE_{10}}{16384}$$

2の補数(G/T=0)の場合は、

ここで、 $CODE_{10}$ は、表2に示すディジタル出力コード と等価な10進値です。

MAX12553がパワーダウン状態(PD=ハイ)にあるとき、ディジタル出力D13~D0はハイインピーダンスです。D13~D0は、PDの立上りエッジの10ns後にハイに 遷移し、PDの立下りエッジの10ns後にアクティブになります。

大きなディジタル電流がMAX12553のアナログ部にフィードバックされてそのダイナミック性能が低下することを防止するために、MAX12553のディジタル出力D13~D0の容量性負荷をできる限り小さく(15pF未満)抑えてください。ディジタル出力にディジタルバッファを外付けすると、MAX12553が容量性の重負荷から分離されます。MAX12553のダイナミック性能を向上させるために、MAX12553の近くで220 $\Omega$ の抵抗器をディジタル出力に直列に接続してください。220 $\Omega$ の直列抵抗器を介してディジタルバッファを駆動するディジタル出力の例については、MAX12555の評価キットの回路図を参照してください。

#### パワーダウン入力(PD)

MAX12553は、パワーダウンディジタル入力(PD)によって制御される2つの電力モードを備えています。

表2. 出力コードと入力電圧

|                    | GRAY C<br>OUTPUT<br>(G/T = | GRAY CODE<br>•UTPUT CODE<br>(G∏ = 1)        |                                                     | E                    | MO'S-C<br>OUTP<br>(G | TWO'S-COMPLEMENT OUTPUT CODE $(G/\overline{\Gamma} = 0)$ |                                                     | :                                               |

|--------------------|----------------------------|---------------------------------------------|-----------------------------------------------------|----------------------|----------------------|----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|

| BINARY<br>D13 → D0 | DOR                        | HEXADECIMAL<br>EQUIVALENT<br>OF<br>D13 → D0 | DECIMAL<br>EQUIVALENT<br>OF<br>D13 → D0<br>(CODE₁0) | BINARY<br>D13 → D0   | DOR                  | HEXADECIMAL<br>EQUIVALENT<br>OF<br>D13→ D0               | DECIMAL<br>EQUIVALENT<br>OF<br>D13 → D0<br>(CODE₁0) | VINP - VINN  (VREFP = 2.418V)  (VREFN = 0.882V) |

| 10 0000 0000 0000  | -                          | 0×2000                                      | +16383                                              | 01 1111 1111 1111    | -                    | 0×1FFF                                                   | +8191                                               | >+1.023875V<br>(DATA OUT OF<br>RANGE)           |

| 10 0000 0000 0000  | 0                          | 0x2000                                      | +16383                                              | 01 1111 1111 1111    | 0                    | 0x1FFF                                                   | +8191                                               | +1.023875V                                      |

| 10 0000 0000 0001  | 0                          | 0x2001                                      | +16382                                              | 01 1111 1111 1110    | 0                    | 0x1FFE                                                   | +8190                                               | +1.023750V                                      |

|                    |                            |                                             |                                                     |                      |                      |                                                          |                                                     |                                                 |

| 11 0000 0000 0011  | 0                          | 0×3003                                      | +8194                                               | 00 0000 0000 0010    | 0                    | 0×0002                                                   | +2                                                  | +0.000250V                                      |

| 11 0000 0000 0001  | 0                          | 0×3001                                      | +8193                                               | 00 0000 0000 0001    | 0                    | 0×0001                                                   | +                                                   | +0.000125V                                      |

| 11 0000 0000 0000  | 0                          | 000£×0                                      | +8192                                               | 00 0000 0000 0000    | 0                    | 0000×0                                                   | 0                                                   | +0.000000V                                      |

| 01 0000 0000 0000  | 0                          | 0×1000                                      | +8191                                               | 11 1111 1111 1111    | 0                    | 0×3FFF                                                   | -1                                                  | -0.000125V                                      |

| 01 0000 0000 0001  | 0                          | 0×1001                                      | +8190                                               | 11 1111 1111 1110    | 0                    | 0x3FFE                                                   | -2                                                  | -0.000250V                                      |

|                    |                            |                                             |                                                     |                      |                      |                                                          |                                                     |                                                 |

| 00 0000 0000 1     | 0                          | 0x0001                                      | +                                                   | 10 0000 0000 0001    | 0                    | 0x2001                                                   | -8191                                               | -1.023875V                                      |

| 0000 0000 0000 00  | 0                          | 0000×0                                      | 0                                                   | 10 0000 0000 0000 01 | 0                    | 0×2000                                                   | -8192                                               | -1.024000V                                      |

| 0000 0000 0000 00  | -                          | 0000×0                                      | 0                                                   | 10 0000 0000 0000    | -                    | 0×2000                                                   | -8192                                               | <-1.024000V<br>(DATA OUT OF<br>RANGE)           |

図7. 2の補数の伝達関数(G/T = 0)

PDがローの場合、MAX12553は通常動作モードにあります。PDがハイの場合、MAX12553はパワーダウンモードにあります。

パワーダウンモードでは、MAX12553は、変換が必要でないとき低電力状態に遷移することによって電力を効率的に利用することができます。さらに、パワーダウンモードではMAX12553のパラレル出力バスがハイインピーダンスであるため、バス上の他のデバイスがアクセスされることが可能となります。

パワーダウンモードでは、すべての内部回路がオフ状態にあり、アナログ消費電流が0.045mAに減少し、ディジタル消費電流が0.02mAに減少します。下記のリストは、パワーダウンモードにおけるアナログ入力とディジタル出力の状態を示します。

- INP、INNアナログ入力は、内蔵入力アンプから切断 される(図3)。

- REFOUTは、GNDに対して約17kΩとなる。

- REFP、COM、及びREFNは、 $V_{DD}$ とGNDに対して ハイインピーダンスになるが、REFPとCOMの間に  $4k\Omega$ の内部抵抗器があり、REFNとCOMの間にも $4k\Omega$  の内部抵抗器がある。

- D13~D0、DOR、及びDAVがハイインピーダンス になる。

- CLKPとCLKNがハイインピーダンスになる(図5)。 パワーダウンモードからのウェイクアップ時間は、REFP、 REFN、及びCOMにおけるコンデンサの充電に必要な

図8. グレイコードの伝達関数(G/T = 1)

時間によって支配されます。内部リファレンスモード及びバッファ付き外部リファレンスモードでは、推奨コンデンサアレイを接続した場合のウェイクアップ時間は標準値で10msです(図13)。バッファなし外部リファレンスモードで動作させる場合、ウェイクアップ時間は外付けのリファレンスドライバによって異なります。

#### アプリケーション情報

#### トランス結合の利用

一般に、MAX12553は、シングルエンド入力駆動の場合よりも、完全差動入力信号の場合のSFDRとTHD性能が優れています。差動入力モードでは、両入力が平衡しており、かつADC入力の各々がシングルエンド入力モードに比べて1/2の信号振幅で済むため、偶数次の高調波が少なくなります。

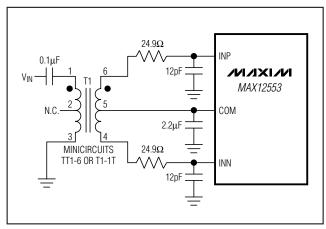

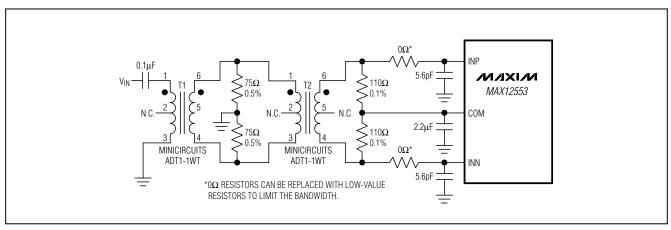

RFトランス(図10)は、シングルエンド入力源信号を完全差動信号(最適性能を得るためにMAX12553が必要とする)に変換するための優れたソリューションを提供します。このトランスのセンタタップをCOMに接続すると、入力に対して $V_{DD}/2$ だけDCレベルがシフトします。1:1のトランスが記載されていますが、ステップアップトランスを選択して駆動要件を緩和することもできます。オペアンプなどの入力ドライバの信号振幅を小さくすることによって、総合歪みを改善することもできます。図10の構成は、ナイキスト( $f_{CLK}/2$ )までの周波数に適しています。

図9. バイナリからグレイ、及びグレイからバイナリへのコード変換

図10. ナイキストまでの入力周波数に対するトランス結合 入力駆動

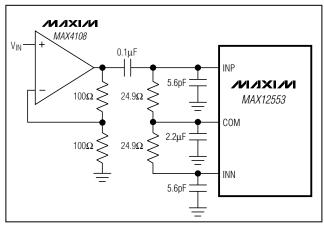

図12. シングルエンド、AC結合入力駆動

図11. ナイキストを超える入力周波数に対するトランス結合入力駆動

図11の回路は、シングルエンド入力信号を図10のような完全差動に変換するだけでなくコモンモード除去比を改善するために補助トランスを利用しているため、ナイキスト周波数を超える高周波信号を処理することができます。2組の終端抵抗器を使用して、信号源に対し75 $\Omega$ に等しい終端が行われています。2番目の組の終端抵抗器を接続することによって、COMに適切な入力コモンモード電圧を供給しています。アナログ入力に2個の $\Omega$ Ω抵抗器を直列接続すると、IF入力周波数を

高くすることができます。これらの $0\Omega$ 抵抗器を値の小さい抵抗器に置き換えると入力帯域幅を制限することができます。

#### シングルエンドAC結合入力信号

図12は、AC結合、シングルエンド入力のアプリケーションを示します。MAX4108は、高速、広帯域幅、低ノイズ、及び低歪みの特長を備えおり、入力信号の完全性を保ちます。

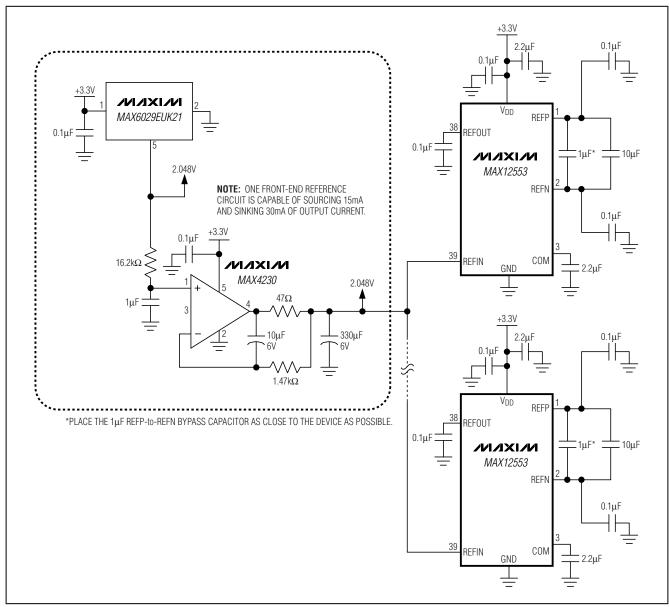

図13. 複数のADCを駆動するバッファ付き外部リファレンス

#### バッファ付き外部リファレンスが複数のADCを駆動

バッファ付き外部リファレンスモードを使用すると、MAX12553内蔵のリファレンス電圧に優る、より多くの制御が可能になり、複数のコンバータが共通リファレンスを使用することができます。REFINの入力インピーダンスは 50MΩを超えています。

図13では、複数のコンバータに対する共通リファレンス として高精度2.048VリファレンスのMAX6029EUK21 を使用しています。MAX6029の2.048V出力は、1次、 10Hzのローパスフィルタを介してMAX4230に接続 されています。MAX4230は2.048Vリファレンスの バッファとして働き、その出力がMAX12553のREFIN 入力に加えられる前にさらに10Hzのローパスフィルタ 処理を行っています。

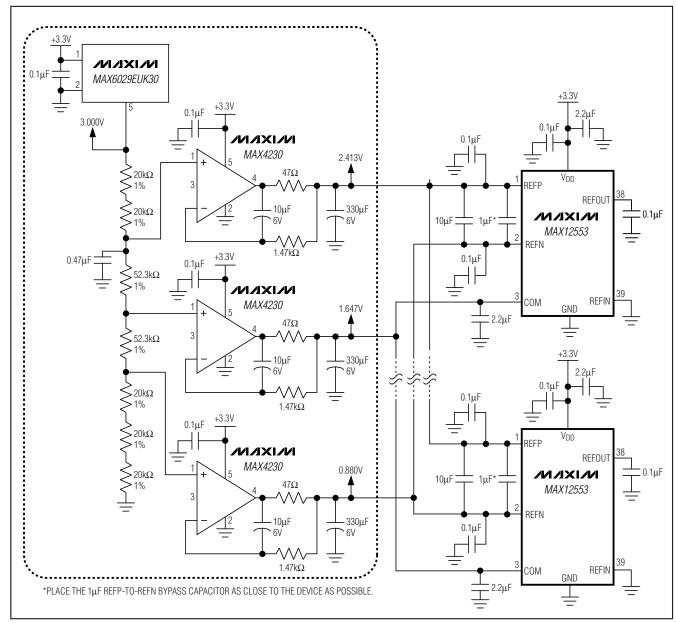

#### バッファなし外部リファレンスが 複数のADCを駆動

バッファなし外部リファレンスモードを使用すると、MAX12553内蔵リファレンスに優る高精度の制御が可能になり、複数のコンバータに共通リファレンスを使用することができます。REFINをGNDに接続すると、

図14. 複数のADCを駆動するバッファなし外部リファレンス

内部リファレンスがディセーブルされて、REFP、REFN、及びCOMを1組の外部リファレンスソースによって直接駆動することができます。

図14では、複数のコンバータに対する共通リファレンスとして高精度3.000VリファレンスのMAX6029EUK30を使用しています。7個の部品から成る抵抗分圧器チェーンが電圧リファレンスのMAX6029の後に接続されています。 $0.47\mu F$ のコンデンサがこのチェーンとともに10Hzのローパスフィルタを形成しています。3個のオペアンプMAX4230が、この抵抗器チェーンに

沿ったタップにバッファとして接続され、MAX12553 のREFP、COM、及びREFNの各リファレンス入力にそれぞれ2.413V、1.647V、及び0.880Vを供給しています。オペアンプのMAX4230にフィードバックを施すことによって、10Hzのローパスフィルタが新たに加わります。2.413Vと0.880Vのリファレンス電圧によって、フルスケールのアナログ入力範囲が $\pm 1.022V = \pm (V_{REFP} - V_{REFN}) \times 2/3$ に設定されます。全能動部品の電源を共通にすることによって、パワーアップまたはパワーダウンの際の電源シーケンスに関する問題が解消します。

#### グランド、バイパス、及び 基板のレイアウト

MAX12553には、高速の基板レイアウト設計法を適用する必要があります。基板のレイアウト基準については、MAX12555の評価キットのデータシートを参照してください。すべてのバイパスコンデンサは、インダクタンスを最小とする表面実装型デバイスを使用し、できればADCと基板の同じ側でデバイスにできる限り近づけて配置してください。 $0.1\mu F$ のセラミックコンデンサと並列の $2.2\mu F$ のセラミックコンデンサで $V_{DD}$ をGNDにバイパスしてください。 $0.1\mu F$ のセラミックコンデンサで $V_{DD}$ をGNDにバイパスしてください。 $0.1\mu F$ のセラミックコンデンサで $V_{DD}$ をGNDにバイパスしてください。

十分に広いグランドプレーンと電源プレーンを備えた 多層基板を使用すると、最高レベルの信号の完全性が 実現します。MAX12553のすべてのGNDと裏側のエク スポーズドパッドは、同じグランドプレーンに接続する 必要があります。MAX12553は低インダクタンスの グランド接続を裏側のエクスポーズドパッドに依存し ます。複数のビアを使用して上側のグランドを下側の グランドに接続してください。グランドプレーンは、 DSPや出力バッファグランドなど、ノイズの多いディ ジタルシステムグランドプレーンから分離してください。 高速ディジタル信号トレースは、ノイズに敏感なアナ ログトレースから離して配置してください。すべての 信号ラインを短くして90°の方向転換を避けてください。 差動アナログ入力回路網のレイアウトが対称になるよう にし、すべての寄生成分が等しくバランスされるように してください。対称な入力レイアウトの例については、 MAX12555の評価キットのデータシートを参照して ください。

#### パラメータの定義 \_

#### Integral Nonlinearity(積分非直線性)(INL)

積分非直線性は、実際の伝達関数上の値に対する直線からのずれです。MAX12553の場合、この直線は、オフセットと利得誤差をゼロにした後の伝達関数の両端点を結んだ直線です。INLのずれは、伝達関数の全ステップにおいて測定され、ワーストケースのずれが「Electrical Characteristics(電気的特性)」の表に記載されています。

#### Differential Nonlinearity(微分非直線性)(DNL)

微分非直線性は、実際のステップ幅と1LSBの理想値の 差です。1LSBより小さいDNL誤差の仕様は、ミッシング コードのない単調伝達関数を保証します。MAX12553 の場合、DNLのずれは、伝達関数の全ステップにおいて 測定され、ワーストケースのずれが「Electrical Characteristics(電気的特性)」の表に記載されています。

#### Offset Error(オフセット誤差)

オフセット誤差は、実際の伝達関数が1点において理想的な伝達関数とどの程度一致しているかを示す性能指数です。理想的には、ミッドスケールのMAX12553の遷移がミッドスケールよりも0.5LSBだけ上で起ります。オフセット誤差は、測定されたミッドスケール遷移点と理想的なミッドスケール遷移点のずれの大きさです。

#### Gain Error(利得誤差)

利得誤差は、実際の伝達関数の傾斜が理想的な伝達関数の傾斜とどの程度一致しているかを示す性能指数です。実際の伝達関数の傾斜は、2つのデータポイントの間、すなわち正のフルスケールと負のフルスケールの間で測定されます。理想的には、正のフルスケールのMAX12553の遷移が正のフルスケールよりも1.5LSBだけ下で起こり、負のフルスケールの遷移が負のフルスケールよりも0.5LSBだけ上で起ります。利得誤差は、測定された遷移点の差から理想的な遷移点の差を差し引いた値です。

#### Small-Signal Noise Floor (小信号ノイズフロア)(SSNF)

小信号ノイズフロアは、小信号入力の場合のナイキスト帯域のノイズと歪みのパワーの総合値です。DCオフセットはこのノイズの計算から除外されます。このコンバータの場合、小信号は、-35dBFS以下の振幅を有するシングルトーンとして定義されます。このパラメータは、コンバータの熱雑音及び量子化雑音特性を取り入れて受信チャネルの総合雑音指数の計算に役立てることができます。熱雑音及び量子化雑音フロアに関するアプリケーションノートについては、japan.maxim-ic.comをご覧ください。

#### Signal-to-Noise Ratio(信号対雑音比)(SNR)

ディジタルサンプルから完全に再現される波形の場合、理論的な最大SNRはフルスケールアナログ入力(RMS値)とRMS量子化誤差(残留誤差)との比です。理想的で理論的な最小のアナログ - ディジタル変換雑音は、量子化誤差のみによって生じるもので、ADCの分解能(Nビット)から次式によって直接求められます。

$SNR[max] = 6.02 \times N + 1.76$

実際には、量子化雑音以外に、熱雑音、リファレンス 雑音、クロックジッタなどのノイズ源があります。 SNRは、RMS信号とRMS雑音の比をとることによって 求められます。RMS雑音には、基本波成分、最初の6つの高調波成分(HD2~HD7)、及びDCオフセットを除く、ナイキスト周波数までの全スペクトル成分が含まれます。

#### Signal-to-Noise Plus Distortion (信号 対 ノイズ + 歪み)(SINAD)

SINADは、RMS信号とRMS雑音+歪みとの比をとることによって求められます。RMS雑音+歪みには、基本波とDCオフセットを除く、ナイキスト周波数までの全スペクトル成分が含まれます。

#### Effective Number of Bits(有効ビット数)(ENOB)

ENOBは、特定の入力周波数とサンプリングレートにおけるADCのダイナミック性能を規定します。理想的なADCの誤差は、量子化雑音のみから成ります。フルスケールの正弦波入力信号波形に対するENOBは次式から計算されます:

$$ENOB = \left(\frac{SINAD - 1.76}{6.02}\right)$$

# Single-Tone Spurious-Free Dynamic Range (シングルトーンスプリアスフリーダイナミックレンジ)(SFDR)

SFDRは、基本波(最大信号成分)のRMS振幅と次に大きいスプリアス成分(DCオフセットを除く)のRMS振幅との比をデシベル単位で表わした値です。

#### Total Harmonic Distortion(全高調波歪み)(THD)

THDは、入力信号に含まれる最初の6つの高調波のRMS和と基本波そのものとの比です。これは、次式で表わされます:

THD =

$$20 \times log \left( \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2 + V_7^2}}{V_1} \right)$$

ここで、 $V_1$ は基本波の振幅で、 $V_2 \sim V_7$ は第2から第7までの高調波(HD2 $\sim$ HD7)の振幅です。

#### Intermodulation Distortion(相互変調歪み)(IMD)

IMDは、相互変調積のRMS和と2つの基本波入力トーンのRMS和との比です。これは、次式で表わされます:

$$IMD = 20 \times log \left( \frac{\sqrt{V_{IM1}^2 + V_{IM2}^2 + \dots + V_{IM13}^2 + V_{IM14}^2}}{\sqrt{V_1^2 + V_2^2}} \right)$$

基本波入力トーンの振幅( $V_1 \& V_2$ )は、-7 dBFSにおける値です。MAX12553 のIMDの計算では、 $14 の相互変調積(V_{IM\_})$ が使用されます。相互変調積は下記の周波数における出力スペクトルの振幅で、 $f_{IN1} \& f_{IN2}$ は基本波入力トーン周波数です。

- 2次の相互変調積: f<sub>IN1</sub> + f<sub>IN2</sub>、f<sub>IN2</sub> f<sub>IN1</sub>

- 3次の相互変調積:2xf<sub>IN1</sub>-f<sub>IN2</sub>、2xf<sub>IN2</sub>-f<sub>IN1</sub>、2x f<sub>IN1</sub>+f<sub>IN2</sub>、2xf<sub>IN2</sub>+f<sub>IN1</sub>

- 4次の相互変調積:3xf<sub>IN1</sub>-f<sub>IN2</sub>、3xf<sub>IN2</sub>-f<sub>IN1</sub>、3x f<sub>IN1</sub>+f<sub>IN2</sub>、3xf<sub>IN2</sub>+f<sub>IN1</sub>

- 5次の相互変調積:3xf<sub>IN1</sub>-2xf<sub>IN2</sub>、3xf<sub>IN2</sub>-2xf<sub>IN1</sub>、 3xf<sub>IN1</sub>+2xf<sub>IN2</sub>、3xf<sub>IN2</sub>+2xf<sub>IN1</sub>

## Third-Order Intermodulation (3次相互変調)(IM3)

IM3は、2つの入力トーン $f_{\text{IN1}}$ と $f_{\text{IN2}}$ の全入力パワーを基準とするナイキスト周波数までの3次相互変調積の全パワーです。各入力トーンのレベルは、-7dBFSにおける値です。3次相互変調積は、 $2 \times f_{\text{IN1}} - f_{\text{IN2}}$ 、 $2 \times f_{\text{IN2}} - f_{\text{IN1}}$ 、 $2 \times f_{\text{IN1}} + f_{\text{IN2}}$ 、 $2 \times f_{\text{IN2}} + f_{\text{IN1}}$ です。

## Two-Tone Spurious-Free Dynamic Range (2トーンスプリアスフリーダイナミックレンジ) (SFDR<sub>TT</sub>)

SFDR<sub>TT</sub>は、どちらかの入力トーンのRMS振幅とスペクトルにおける次に大きいスプリアス成分(DCオフセットを除く)のRMS振幅との比をデシベル単位で表わした値です。このスプリアス成分は、ナイキスト周波数までのスペクトルのどこでも発生する可能性があり、通常は相互変調積または高調波です。

#### Aperture Delay(アパーチャ遅延)

MAX12553は、そのサンプリングクロックの立下りエッジでデータがサンプリングされます。実際には、サンプリングクロック立下りエッジと実際のサンプリング時点の間にわずかな遅延があります。アパーチャ遅延(t<sub>AD</sub>)は、サンプリングクロックの立下りエッジと実際のサンプルが取り込まれた時点の間の時間として定義されます(図4)。

#### Aperture Jitter(アパーチャジッタ)

図4はアパーチャジッタ(t<sub>AJ</sub>)を示します。これは、アパーチャ遅延における各サンプル間の変動です。

#### Output Noise(出力ノイズ)(n<sub>OUT</sub>)

出力ノイズ(n<sub>OUT</sub>)パラメータは、熱雑音+量子化雑音 パラメータに似ており、ADCの総合ノイズ性能を表わ します。

n<sub>OUT</sub>の試験には、基本波入力トーンは使用されません。INP、INN、及びCOMを相互に接続して、1024kのデータポイントが収集されます。n<sub>OUT</sub>は、収集されたデータポイントのRMS値を求めることによって計算されます。

## Overdrive Recovery Time (オーバドライブ回復時間)

オーバドライブ回復時間は、ADCがフルスケールの限界値を超える過渡入力から回復するのに要する時間です。MAX12553では、フルスケールの限界値を±10%だけ超える過渡入力を使用してオーバドライブ回復時間を規定します。

#### ピン配置

パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packagesをご参照下さい。)

|        |           |      | CC   | NOMIN     | DIMENS | IONS |           |      |      |

|--------|-----------|------|------|-----------|--------|------|-----------|------|------|

| PKG.   | 36L 6x6   |      |      | 40L 6x6   |        |      | 48L 6x6   |      |      |

| SYMBOL | MIN.      | NOM. | MAX. | MIN.      | NOM.   | MAX. | MIN       | NOM. | MAX  |

| A      | 0.70      | 0.75 | 0.80 | 0.70      | 0.75   | 0.80 | 0.70      | 0.75 | 0.80 |

| A1     | 0         | 0.02 | 0.05 | 0         | 0.02   | 0.05 | 0         | -    | 0.05 |

| A2     | 0.20 REF. |      |      | 0.20 REF. |        |      | 0.20 REF. |      |      |

| b      | 0.20      | 0.25 | D.3D | 0.20      | 0.25   | 0.30 | 0.15      | 0.20 | 0.25 |

| D      | 5.90      | 6.00 | 6.10 | 5,90      | 6.00   | 6.10 | 5.90      | 6,00 | 6.10 |

| E      | 5.90      | 6.00 | 6.10 | 5,90      | 6.00   | 6.10 | 5,90      | 5.00 | 6.10 |

| e      | 0.50 BSC. |      |      | 0.50 BSC. |        |      | 0.40 BSC. |      |      |

| k      | 0.25      | -    | -    | 0.25      | -      | -    | 0.25      | 0.35 | 0.4  |

| L      | 0.45      | 0.55 | D.65 | 0.30      | 0.40   | 0.50 | 0.40      | 0.50 | 0.6  |

| LI     | -         | -    | -    | -         | -      | -    | 0.30      | 0.40 | 0.5  |

| N      | 36        |      |      | 40        |        |      | 48        |      |      |

| ND     | 9         |      |      | 10        |        |      | 12        |      |      |

| NE     | 9         |      |      | 10        |        |      | 12        |      |      |

| JEDEC  | WJJD-1    |      |      | WJJD-2    |        |      | -         |      |      |

|               | DOWN |      |      |      |       |      |     |

|---------------|------|------|------|------|-------|------|-----|

| PKG.<br>CODES |      | D2   |      |      | BONDS |      |     |

|               | MIN. | NOM. | MAX. | MIN. | NOM.  | MAX. |     |

| T3666-1       | 3,60 | 3.70 | 3.80 | 3,60 | 3.70  | 3.80 | NO  |

| T3666-2       | 3,60 | 3.70 | 3.80 | 3,60 | 3,70  | 3.80 | YES |

| T3666-3       | 3.60 | 3.70 | 3.80 | 3,60 | 3.70  | 3.80 | NO  |

| T4066-1       | 4.00 | 4.10 | 4.20 | 4.00 | 4.10  | 4.20 | NO  |

| T4066-2       | 4.00 | 4.10 | 4.20 | 4.00 | 4.10  | 4.20 | YES |

| T4066-3       | 4.00 | 4.10 | 4.20 | 4.00 | 4.10  | 4.20 | YES |

| T4066-4       | 4.00 | 4.10 | 4.20 | 4.00 | 4.10  | 4.20 | NO  |

| T4066-5       | 4.00 | 4.10 | 4.20 | 4.00 | 4.10  | 4.20 | NO  |

| T4866-1       | 4.20 | 4.30 | 4.40 | 4.20 | 4.30  | 4.40 | YES |

#### NOTES:

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

⚠ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ANS EOPTIONAL. BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

#### ⚠DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6. NO AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- $\underline{\&}$  COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS

- 9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR 0.4mm LEAD PITCH PACKAGE T4866-1

- 10. WARPAGE SHALL NOT EXCEED 0.10 mm.

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

28 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600