EVALUATION KIT

#

# **AVAILABLE** 250ksps、+3V、8/4チャネル、12ビットADC +2.5Vリファレンス及びパラレルインタフェース付

## 概要

MAX1291/MAX1293は、逐次比較ADC、自動パワー ダウン、高速ウェイクアップ(2μs)、内蔵クロック、 +2.5V内部リファレンス及び高速バイト幅パラレルイ タフェースを備えた低電力、12ビットアナログディジ タルコンバータ(ADC)です。これらの製品は、単一+3V アナログ電源で動作し、+1.8V~+5.5Vディジタル電源 と直接インタフェースするためのV<sub>LOGIC</sub>ピンを備えて います。

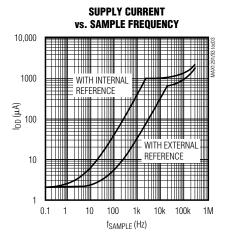

最大サンプリング速度250kspsにおける消費電力は、 僅か5.7 $mW(V_{DD} = V_{LOGIC})$ です。2つのソフトウェア 選択可能なパワーダウンモードにより、MAX1291/ MAX1293は変換の合間にシャットダウンすることが できます。パラレルインタフェースにアクセスすると、 通常動作に戻ります。変換の合間にパワーダウンする ことにより、低サンプリング速度における消費電流を 10µA以下に削減できます。

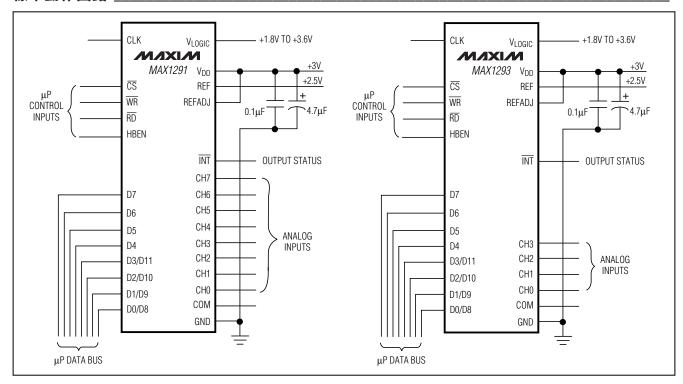

いずれの素子も、アナログ入力はユニポーラ/バイポーラ 及びシングルエンド/疑似差動動作をソフトウェアで 設定できるようになっています。シングルエンドモード において、MAX1291は8つの入力チャネル、MAX1293 は4つの入力チャネルを持っています(疑似差動モード においてはそれぞれ4つ及び2つの入力チャネル)。

本製品は優れた動的性能及び低電力特性に加え、 パッケージが小型で使いやすいため、バッテリ駆動 及びデータ収集アプリケーション、あるいはその他の 省電力、小型化が必要な回路に最適です。

MAX1291/MAX1293は、CSがハイになると、INTを トライステートにします。<del>INT</del>のトライステートが好ま しくない場合、MAX1261/MAX1263を参照してくだ さい。

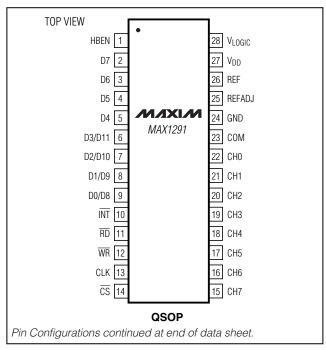

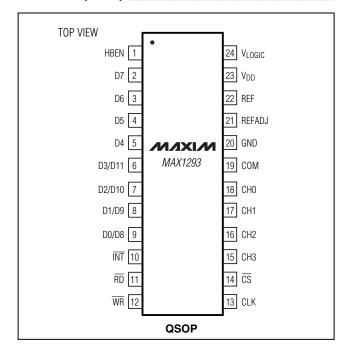

MAX1291は28ピンOSOPパッケージで提供されて います。MAX1293は24ピンQSOPです。ピンコン パチブルな+5V、12ビットバージョンについては、 MAX1290/MAX1292データシートを参照して下さい。

## アプリケーション

| 工業用制御機器 | データロギング  |

|---------|----------|

| エネルギー管理 | 患者の監視    |

| データ収集機器 | タッチスクリーン |

### 型番

| PART        | TEMP RANGE     | PIN-PACKAGE | INL<br>(LSB) |

|-------------|----------------|-------------|--------------|

| MAX1291ACEI | 0°C to +70°C   | 28 QSOP     | ±0.5         |

| MAX1291BCEI | 0°C to +70°C   | 28 QSOP     | ±1           |

| MAX1291AEEI | -40°C to +85°C | 28 QSOP     | ±0.5         |

| MAX1291BEEI | -40°C to +85°C | 28 QSOP     | ±1           |

型番の続きはデータシートの最後に記載されています。

### 特長

- ◆ 分解能: 12ビット、直線性:±0.5LSB

- ◆ 電源:+3V単一

- ◆ ユーザがロジックレベルを調節可能:+1.8V~+3.6V

- ◆ 内部+2.5Vリファレンス

- ◆ ソフトウェア設定可能なアナログ入力マルチプレクサ 8チャネルシングルエンド/

4チャネル疑似差動(MAX1291)

4チャネルシングルエンド/

2チャネル疑似差動(MAX1293)

- ◆ ユニポーラ/バイポーラ入力をソフトウェア設定可能

- ◆ 低電力: 1.9mA(250ksps) 1.0mA(100ksps) 400μA(10ksps) 2μA(シャットダウン)

- ◆ フルパワー帯域幅が3MHzの内部トラック/ホールド

- ◆ バイト幅パラレル(8+4)インタフェース

- ◆ 小面積:28ピンQSOP(MAX1291) 24ピンQSOP(MAX1293)

## ピン配置

標準動作回路はデータシートの最後に記載されています。

MIXIM

Maxim Integrated Products 1

本データシートに記載された内容はMaxim Integrated Productsの公式な英語版データシートを翻訳したものです。翻訳により生じる相違及び 誤りについては責任を負いかねます。正確な内容の把握には英語版データシートをご参照ください。

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND              | 0.3V to +6V                      |

|-------------------------------------|----------------------------------|

| VLOGIC to GND                       | 0.3V to +6V                      |

| CH0-CH7, COM to GND                 | 0.3V to $(V_{DD} + 0.3V)$        |

| REF, REFADJ to GND                  | 0.3V to (V <sub>DD</sub> + 0.3V) |

| Digital Inputs to GND               |                                  |

| Digital Outputs (D0-D11, INT) to GN | D0.3V to (VI OGIC + 0.3V)        |

|                                                  | (T <sub>A</sub> = +70°C)<br>//°C above +70°C)762mW<br>W/°C above +70°C)667mW |

|--------------------------------------------------|------------------------------------------------------------------------------|

| Operating Temperature Range MAX1291_C/MAX1293_C_ |                                                                              |

|                                                  | 65°C to +150°C<br>10s)+300°C                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{LOGIC} = +2.7V \text{ to } +3.6V, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu\text{F}$  capacitor at REF pin,  $f_{CLK} = 4.8\text{MHz}$  (50% duty cycle); Ta = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at Ta = +25°C.)

| PARAMETER                                                | SYMBOL         | CONDITIONS                                                               | MIN       | TYP         | MAX      | UNITS  |

|----------------------------------------------------------|----------------|--------------------------------------------------------------------------|-----------|-------------|----------|--------|

| DC ACCURACY (Note 1)                                     |                |                                                                          | '         |             |          |        |

| Resolution                                               | RES            |                                                                          | 12        |             |          | Bits   |

| Deletive Assurance (Nets O)                              | INL            | MAX129_A                                                                 |           |             | ±0.5     | LSB    |

| Relative Accuracy (Note 2)                               | IINL           | MAX129_B                                                                 |           |             | ±1       | LSB    |

| Differential Nonlinearity                                | DNL            | No missing codes over temperature                                        |           |             | ±1       | LSB    |

| Offset Error                                             |                |                                                                          |           |             | ±4       | LSB    |

| Gain Error (Note 3)                                      |                |                                                                          |           |             | ±4       | LSB    |

| Gain Temperature Coefficient                             |                |                                                                          |           | ±2.0        |          | ppm/°C |

| Channel-to-Channel Offset<br>Matching                    |                |                                                                          |           | ±0.2        |          | LSB    |

| DYNAMIC SPECIFICATIONS (file                             | N(sine wave) = | = 50kHz, $V_{IN}$ = 2.5 $V_{P-P}$ , 250ksps, external $f_{CLK}$ =        | = 4.8MHz, | bipolar inp | ut mode) | )      |

| Signal-to-Noise Plus Distortion                          | SINAD          |                                                                          | 67        | 70          |          | dB     |

| Total Harmonic Distortion (including 5th-order harmonic) | THD            |                                                                          |           |             | -78      | dB     |

| Spurious-Free Dynamic Range                              | SFDR           |                                                                          | 80        |             |          | dB     |

| Intermodulation Distortion                               | IMD            | $f_{IN1} = 49kHz$ , $f_{IN2} = 52kHz$                                    |           | 76          |          | dB     |

| Channel-to-Channel Crosstalk                             |                | f <sub>IN</sub> = 125kHz, V <sub>IN</sub> = 2.5V <sub>P-P</sub> (Note 4) |           | -78         |          | dB     |

| Full-Linear Bandwidth                                    |                | SINAD > 68dB                                                             |           | 250         |          | kHz    |

| Full-Power Bandwidth                                     |                | -3dB rolloff                                                             |           | 3           |          | MHz    |

| CONVERSION RATE                                          | •              |                                                                          |           |             |          |        |

|                                                          |                | External clock mode                                                      | 3.3       |             |          |        |

| Conversion Time (Note 5)                                 | tconv          | External acquisition/internal clock mode                                 | 2.5       | 3.0         | 3.5      | μs     |

|                                                          |                | Internal acquisition/internal clock mode                                 | 3.2       | 3.6         | 4.1      |        |

| Track/Hold Acquisition Time                              | tACQ           |                                                                          |           |             | 625      | ns     |

| Aperture Delay                                           |                | External acquisition or external clock mode                              |           | 50          |          | ns     |

| Aperture Jitter                                          |                | External acquisition or external clock mode                              |           | <50         |          | ps     |

| ·                                                        |                | Internal acquisition/internal clock mode                                 |           | <200        |          | '      |

| External Clock Frequency                                 | fCLK           |                                                                          | 0.1       |             | 4.8      | MHz    |

| Duty Cycle                                               |                |                                                                          | 30        |             | 70       | %      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +2.7V \text{ to } +3.6V, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu\text{F}$  capacitor at REF pin,  $f_{CLK} = 4.8\text{MHz}$  (50% duty cycle);  $T_{A} = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}\text{C}$ .)

| PARAMETER                                                   | SYMBOL            | CONDITIONS                                                     | MIN                   | TYP   | MAX                       | UNITS  |  |

|-------------------------------------------------------------|-------------------|----------------------------------------------------------------|-----------------------|-------|---------------------------|--------|--|

| ANALOG INPUTS                                               |                   |                                                                |                       |       |                           |        |  |

| Analog Input Voltage Range<br>Single-Ended and Differential | V <sub>IN</sub>   | Unipolar, V <sub>COM</sub> = 0                                 | 0                     |       | $V_{REF}$                 | V      |  |

| (Note 6)                                                    |                   | Bipolar, V <sub>COM</sub> = V <sub>REF</sub> / 2               | -V <sub>REF</sub> /2  |       | +V <sub>REF</sub> /2      |        |  |

| Multiplexer Leakage Current                                 |                   | On/off-leakage current, V <sub>IN</sub> = 0 or V <sub>DD</sub> |                       | ±0.01 | ±1                        | μΑ     |  |

| Input Capacitance                                           | CIN               |                                                                |                       | 12    |                           | рF     |  |

| INTERNAL REFERENCE                                          |                   |                                                                | '                     |       |                           |        |  |

| REF Output Voltage                                          |                   |                                                                | 2.49                  | 2.5   | 2.51                      | V      |  |

| REF Short-Circuit Current                                   |                   |                                                                |                       | 15    |                           | mA     |  |

| REF Temperature Coefficient                                 | TC <sub>REF</sub> | $T_A = 0$ °C to +70°C                                          |                       | ±20   |                           | ppm/°C |  |

| REFADJ Input Range                                          |                   | For small adjustments                                          |                       | ±100  |                           | mV     |  |

| REFADJ High Threshold                                       |                   | To power down the internal reference                           | V <sub>DD</sub> - 1.0 |       |                           | V      |  |

| Load Regulation (Note 7)                                    |                   | 0 to 0.5mA output load                                         |                       | 0.2   |                           | mV/mA  |  |

| Capacitive Bypass at REFADJ                                 |                   |                                                                |                       | 0.01  | 1                         | μF     |  |

| Capacitive Bypass at REF                                    |                   |                                                                | 4.7                   |       | 10                        | μF     |  |

| EXTERNAL REFERENCE AT R                                     | EF                |                                                                |                       |       |                           |        |  |

| REF Input Voltage Range                                     | VREF              |                                                                | 1.0                   |       | V <sub>DD</sub> +<br>50mV | V      |  |

| DEE Input Current                                           | lass              | V <sub>REF</sub> = 2.5V, f <sub>SAMPLE</sub> = 250ksps         |                       | 200   | 300                       | — н    |  |

| REF Input Current                                           | IREF              | Shutdown mode                                                  |                       |       | 2                         |        |  |

| DIGITAL INPUTS AND OUTPUT                                   | rs                |                                                                | •                     |       |                           |        |  |

| Input High Voltage                                          | VIH               | V <sub>LOGIC</sub> = 2.7V                                      | 2.0                   |       |                           | V      |  |

| input riigii voitage                                        | VIH               | V <sub>LOGIC</sub> = 1.8V                                      | 1.5                   |       |                           | V      |  |

| Input Low Voltage                                           | VIL               | V <sub>LOGIC</sub> = 2.7V                                      |                       |       | 0.8                       | V      |  |

| input Low Voltage                                           | V IL              | V <sub>LOGIC</sub> = 1.8V                                      |                       |       | 0.5                       | ٧      |  |

| Input Hysteresis                                            | V <sub>H</sub> YS |                                                                |                       | 200   |                           | mV     |  |

| Input Leakage Current                                       | I <sub>IN</sub>   | $V_{IN} = 0$ or $V_{DD}$                                       |                       | ±0.1  | ±1                        | μΑ     |  |

| Input Capacitance                                           | C <sub>IN</sub>   |                                                                |                       | 15    |                           | рF     |  |

| Output Low Voltage                                          | VoL               | I <sub>SINK</sub> = 1.6mA                                      |                       |       | 0.4                       | V      |  |

| Output High Voltage                                         | VoH               | ISOURCE = 1mA                                                  | VLOGIC -              | 0.5   | <u> </u>                  | V      |  |

| Three-State Leakage Current                                 | ILEAKAGE          | CS = V <sub>DD</sub>                                           |                       | ±0.1  | ±1                        | μΑ     |  |

| Three-State Output Capacitance                              | Cout              | $\overline{\text{CS}} = V_{\text{DD}}$                         |                       | 15    |                           | рF     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +2.7V \text{ to } +3.6V, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu\text{F}$  capacitor at REF pin,  $f_{CLK} = 4.8\text{MHz}$  (50% duty cycle); Ta = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted. Typical values are at Ta = +25°C.)

| PARAMETER               | SYMBOL          | CONE                                 | MIN                | TYP | MAX  | UNITS                 |    |

|-------------------------|-----------------|--------------------------------------|--------------------|-----|------|-----------------------|----|

| POWER REQUIREMENTS      |                 |                                      |                    |     |      |                       |    |

| Analog Supply Voltage   | V <sub>DD</sub> |                                      |                    | 2.7 |      | 3.6                   | V  |

| Digital Supply Voltage  | VLOGIC          |                                      |                    | 1.8 |      | V <sub>DD</sub> + 0.3 | V  |

|                         |                 | Operating mode,<br>fSAMPLE = 250ksps | Internal reference |     | 2.3  | 2.6                   | mA |

|                         |                 |                                      | External reference |     | 1.9  | 2.3                   |    |

| Positive Supply Current | IDD             | Ct a malla v ma a al a               | Internal reference |     | 0.9  | 1.2                   |    |

| 117                     |                 | Standby mode                         | External reference |     | 0.5  | 0.8                   |    |

|                         |                 | Shutdown mode                        |                    |     | 2    | 10                    | μΑ |

| Vi acia Current         | li oolo         | 0 00 5                               | fsample = 250ksps  |     |      | 150                   | μА |

| VLOGIC Current          | ILOGIC          | C <sub>L</sub> = 20pF                | Not converting     |     | 2    | 10                    |    |

| Power-Supply Rejection  | PSR             | $V_{DD} = 3V \pm 10\%$ , full-s      | scale input        |     | ±0.4 | ±0.9                  | mV |

## **TIMING CHARACTERISTICS**

$(V_{DD} = V_{LOGIC} = +2.7V \text{ to } +3.6V, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu\text{F}$  capacitor at REF pin,  $f_{CLK} = 4.8\text{MHz}$  (50% duty cycle);  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                       | SYMBOL            | CONDITIONS                          | MIN | TYP | MAX | UNITS |

|---------------------------------|-------------------|-------------------------------------|-----|-----|-----|-------|

| CLK Period                      | t <sub>CP</sub>   |                                     | 208 |     |     | ns    |

| CLK Pulse Width High            | tcH               |                                     | 40  |     |     | ns    |

| CLK Pulse Width Low             | t <sub>CL</sub>   |                                     | 40  |     |     | ns    |

| Data Valid to WR Rise Time      | t <sub>DS</sub>   |                                     | 40  |     |     | ns    |

| WR Rise to Data Valid Hold Time | tDH               |                                     | 0   |     |     | ns    |

| WR to CLK Fall Setup Time       | tcws              |                                     | 40  |     |     | ns    |

| CLK Fall to WR Hold Time        | tcwH              |                                     | 40  |     |     | ns    |

| CS to CLK or WR<br>Setup Time   | t <sub>CSWS</sub> |                                     | 60  |     |     | ns    |

| CLK or WR to CS<br>Hold Time    | tcswh             |                                     | 0   |     |     | ns    |

| CS Pulse Width                  | tcs               |                                     | 100 |     |     | ns    |

| WR Pulse Width (Note 8)         | twR               |                                     | 60  |     |     | ns    |

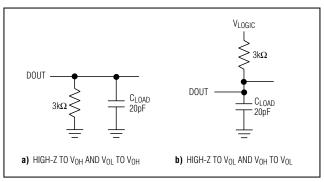

| CS Rise to Output Disable       | tTC               | C <sub>LOAD</sub> = 20pF (Figure 1) | 20  |     | 100 | ns    |

## **TIMING CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +2.7V \text{ to } +3.6V, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu\text{F} \text{ capacitor at REF pin, } f_{CLK} = 4.8\text{MHz} (50\% \text{ duty cycle}); T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C.})$

| PARAMETER                    | SYMBOL            | CONDITIONS                         | MIN | TYP | MAX | UNITS |

|------------------------------|-------------------|------------------------------------|-----|-----|-----|-------|

| RD Rise to Output Disable    | t <sub>TR</sub>   | C <sub>LOAD</sub> = 20pF, Figure 1 | 20  |     | 70  | ns    |

| RD Fall to Output Data Valid | t <sub>DO</sub>   | C <sub>LOAD</sub> = 20pF, Figure 1 | 20  |     | 70  | ns    |

| HBEN to Output Data Valid    | t <sub>DO1</sub>  | C <sub>LOAD</sub> = 20pF, Figure 1 | 20  |     | 110 | ns    |

| RD Fall to INT High Delay    | t <sub>INT1</sub> | C <sub>LOAD</sub> = 20pF, Figure 1 |     |     | 100 | ns    |

| CS Fall to Output Data Valid | t <sub>DO2</sub>  | C <sub>LOAD</sub> = 20pF, Figure 1 |     |     | 110 | ns    |

- **Note 1:** Tested at V<sub>DD</sub> = +3V, COM = GND, unipolar single-ended input mode.

- **Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after offset and gain errors have been removed.

- Note 3: Offset nulled.

- **Note 4:** On channel is grounded; sine wave applied to off channels.

- Note 5: Conversion time is defined as the number of clock cycles times the clock period; clock has 50% duty cycle.

- Note 6: Input voltage range referenced to negative input. The absolute range for the analog inputs is from GND to VDD.

- Note 7: External load should not change during conversion for specified accuracy.

- Note 8: When bit 5 is set low for internal acquisition, WR must not return low until after the first falling clock edge of the conversion.

図1. イネーブル/ディセーブル時間の負荷回路

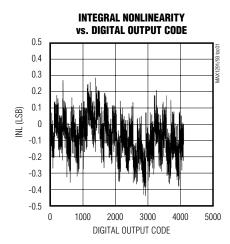

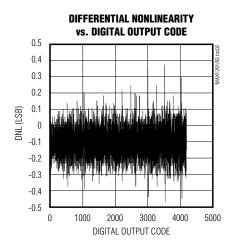

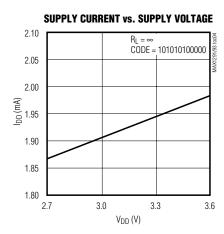

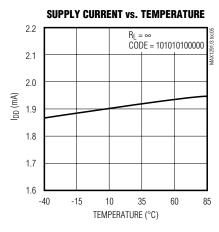

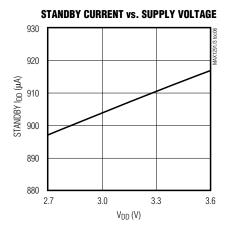

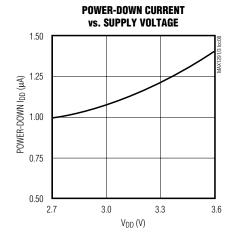

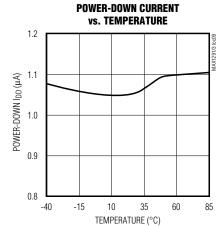

### 標準動作特性

((VDD = VLOGIC = +3V, VREF = +2.500V, fCLK = 4.8MHz, CL = 20pF, TA = +25°C, unless otherwise noted.)

## 標準動作特性(続き)

$(V_{DD} = V_{LOGIC} = +3V, V_{REF} = +2.500V, f_{CLK} = 4.8MHz, C_{L} = 20pF, T_{A} = +25^{\circ}C, unless otherwise noted.)$

# 端子説明\_\_\_\_\_

| 端子      |         |                 |                                                                                                                                                   |

|---------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1291 | MAX1293 | - 名称            | 機能                                                                                                                                                |

| 1       | 1       | HBEN            | ハイバイトイネーブル。12ビット変換結果を多重化するために使用されます。<br>1:4つのMSBがデータバス上で多重化されます。<br>0:8つのLSBがデータバス上で提供されます。                                                       |

| 2       | 2       | D7              | スリーステートディジタルI/Oライン(D7)                                                                                                                            |

| 3       | 3       | D6              | スリーステートディジタルI/Oライン(D6)                                                                                                                            |

| 4       | 4       | D5              | スリーステートディジタルI/Oライン(D5)                                                                                                                            |

| 5       | 5       | D4              | スリーステートディジタルI/Oライン(D4)                                                                                                                            |

| 6       | 6       | D3/D11          | スリーステートディジタルI/Oライン(D3、HBEN = 0; D11、HBEN = 1)                                                                                                     |

| 7       | 7       | D2/D10          | スリーステートディジタルI/Oライン(D2、HBEN = 0; D10、HBEN = 1)                                                                                                     |

| 8       | 8       | D1/D9           | スリーステートディジタルI/Oライン(D1、HBEN = 0; D9、HBEN = 1)                                                                                                      |

| 9       | 9       | D0/D8           | スリーステートディジタルI/Oライン(D0、HBEN = 0; D8、HBEN = 1)                                                                                                      |

| 10      | 10      | ĪNT             | INTは変換が完了して出力データが準備できた時にローになります。                                                                                                                  |

| 11      | 11      | RD              | アクティブロー読取り選択。CSがローの場合、RDの立下がりエッジがデータバス上の<br>読取り動作をイネーブルします。                                                                                       |

| 12      | 12      | WR              | アクティブロー書込み選択。内部アクイジションモードにおいてCSがローの場合、WRの立上がりエッジで構成データがラッチインされ、アクイジション及び変換サイクルが始まります。外部アクイジションモードにおいてCSがローの場合、WRの最初の立上がりエッジでアクイジションが終了し、変換が始まります。 |

| 13      | 13      | CLK             | クロック入力。外部クロックモードの場合、TTL/CMOSコンパチブルクロックでCLKを<br>駆動して下さい。内部クロックモードの場合、このピンをV <sub>DD</sub> 又はGNDに接続して下さい。                                           |

| 14      | 14      | CS              | アクティブローチップセレクト。 $\overline{\text{CS}}$ がハイの時に、ディジタル出力( $\overline{\text{INT}}$ 、D7 $\sim$ D0)がハイインピーダンスになります。                                     |

| 15      | _       | CH7             | アナログ入力チャネル7                                                                                                                                       |

| 16      | _       | CH6             | アナログ入力チャネル6                                                                                                                                       |

| 17      | _       | CH5             | アナログ入力チャネル5                                                                                                                                       |

| 18      | _       | CH4             | アナログ入力チャネル4                                                                                                                                       |

| 19      | 15      | CH3             | アナログ入力チャネル3                                                                                                                                       |

| 20      | 16      | CH2             | アナログ入力チャネル2                                                                                                                                       |

| 21      | 17      | CH1             | アナログ入力チャネル1                                                                                                                                       |

| 22      | 18      | CH0             | アナログ入力チャネル0                                                                                                                                       |

| 23      | 19      | COM             | アナログ入力のグランドリファレンス。シングルエンドモードにおけるゼロコード電圧を<br>設定します。変換中は±0.5LSBまで安定している必要があります。                                                                     |

| 24      | 20      | GND             | アナログ及びディジタルグランド                                                                                                                                   |

| 25      | 21      | REFADJ          | バンドギャップリファレンス出力/バンドギャップリファレンスバッファ入力。 $0.01\mu F$ コンデンサでGNDにバイパスして下さい。外部リファレンスを使用する場合は、REFADJを $V_{DD}$ に接続して内部バンドギャップリファレンスをディセーブルして下さい。          |

| 26      | 22      | REF             | バンドギャップリファレンスバッファ出力/外部リファレンス入力。内部リファレンスを<br>使用する場合は、4.7μFコンデンサを追加して下さい。                                                                           |

| 27      | 23      | V <sub>DD</sub> | アナログ+5V電源。0.1µFコンデンサでGNDにバイパスして下さい。                                                                                                               |

| 28      | 24      | VLOGIC          | ディジタル電源。 $V_{LOGIC}$ によりデータコンバータのディジタル出力が駆動されます。<br>許容範囲は $+1.8V\sim V_{DD}+300~mV$ です。                                                           |

詳細 \_\_\_\_\_

### コンバータの動作

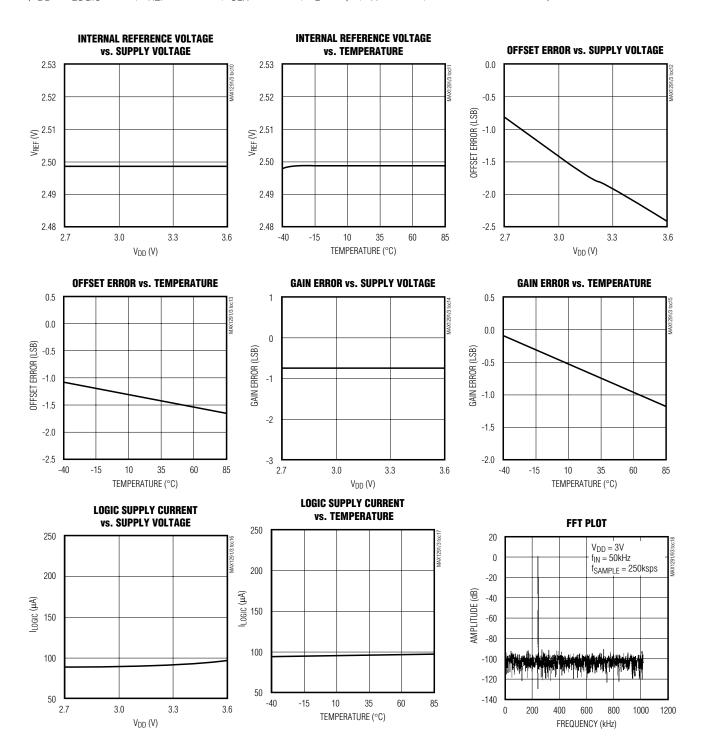

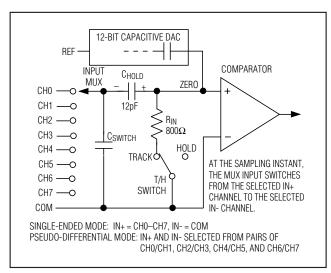

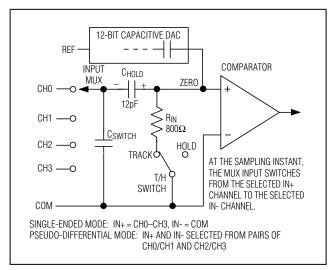

MAX1291/MAX1293 ADCは、逐次比較(SAR)変換技法及び入力トラック/ホールド(T/H)段を使用することにより、アナログ入力信号を12ビットディジタル出力に変換します。パラレル8+4出力フォーマットにより、標準 $\mu$ Pへのインタフェースが容易になっています。図2に、MAX1291/MAX1293の内部構造の略図を示します。

## シングルエンド及び疑似差動動作

図3に、このADCのアナログコンパレータのサンプリング 構成を等価回路で示します。シングルエンドモードでは、IN+が内部で $CH0\sim CH7(MAX12910$ 場合、図3a)及び $CH0\sim CH3(MAX12930$ 場合、図3b)にスイッチングされ、IN-はCOMにスイッチングされます(表3)。

差動モードの場合のIN+及びIN-は、アナログ入力ペアの中から選択され(表4)、内部でそれらのアナログ入力のどちらかにスイッチングされます。この構成ではIN+

のところの信号だけがサンプリングされるため、疑似 差動と呼ばれます。リターン側(IN-)は、変換中GNDに 対して $\pm 0.5$ LSB(最良の結果を得るには $\pm 0.1$ LSB)以内 で安定していることが必要です。これを実現するには、(選択したアナログ入力の)IN-とGNDの間に $0.1\mu$ Fのコンデンサを接続して下さい。

アクイジション期間中は、正入力(IN+)として選択されたチャネルにより、コンデンサ $C_{HOLD}$ が充電されます。アクイジション期間の終了時にT/Hスイッチが開き、 $C_{HOLD}$ の電荷をIN+の信号のサンプルとして保持します。変換期間は、入力マルチプレクサが $C_{HOLD}$ を正入力(IN+)から負入力(IN-)にスイッチングした時点から始まります。このため、コンパレータの入力におけるノードZEROが不平衡になります。変換サイクルの残りの時間で、容量性DACがノードZEROを12ビット分解能の制限範囲でOVに調節します。この動作は、12pFx[(VIN+)-(VIN-)]の電荷を $C_{HOLD}$ からバイナリ重み付の容量性DACに移すことと等価です。この結果、アナログ入力信号のディジタル表示が生成されます。

図2. 8/4チャネルMAX1291/MAX1293の内部構造の略図

図3a. MAX1291の入力構造の略図

図3b. MAX1293の入力構造の略図

### アナログ入力保護

内部保護ダイオードによりアナログ入力が $V_{DD}$ とGNDにクランプされているため、チャネル入力ピンは(GND-300mV)~( $V_{DD}$ +300mV)の範囲で損傷を起こすことなくスイングできます。しかし、フルスケール付近で正確な変換を行うには、入力が( $V_{DD}$ +50mV)を超えず、また(GND-50mV)を下回らないようにして下さい。

オフチャネルのアナログ入力電圧が50mV以上超えた場合は、順方向バイアス入力電流を4mAまでに制限して下さい。

### トラック/ホールド

MAX1291/MAX1293 T/H段は、WRの立上がりエッジでトラッキングモードに入ります。外部アクイジションモードにおいては、本素子は次のWRの立上がりエッジで

ホールドモードに入ります。内部アクイジションモードにおいては、制御バイトを書き込んでから、4つ目のクロックの立下がりエッジでホールドモードに入ります。内部クロックモードにおいては、これが制御バイトへの書込みから約1 $\mu$ s後に起こることに注意して下さい。シングルエンド動作の場合は、IN-がCOMに接続され、コンバータは"+"入力をサンプリングします。疑似差動動作の場合は、IN-が"-"入力に接続され、|(IN+)-(IN-)|の差がサンプリングされます。次の変換の開始時に正入力が再びIN+に接続され、 $C_{HOLD}$ は入力信号電圧まで充電されます。

T/H段が入力信号を取込むために要する時間は、入力容量が充電される速さの関数になっています。入力信号のソースインピーダンスが高いとアクイジション時間は長くなるため、変換と変換の間の時間を長くする必要があります。アクイジション時間tACQは素子が信号を取込むために要する最大時間であると共に、信号の取込みに必要な最低時間にもなっています。tACQは、次式で計算されます。

$$t_{ACO} = 9(R_S + R_{IN})C_{IN}$$

ここで、 $R_S$ =入力信号のソースインピーダンス、 $R_{IN}$  (800 $\Omega$ )は入力抵抗、そして $C_{IN}$ (12pF)はADCの入力容量です。ソースインピーダンスが $3k\Omega$ 以下であれば、MAX1291/MAX1293のAC性能に大きな影響はありません。

0.01µFコンデンサが個々のアナログ入力に接続されている場合は、これ以上のソースインピーダンスの使用も可能です。入力コンデンサ及び入力ソースインピーダンスによってRCフィルタが形成され、ADCの信号帯域幅が制限されることに注意して下さい。

#### 入力帯域幅

MAX1291/MAX1293のT/H段は、フルリニア帯域幅が250kHz、フルパワー帯域幅が3MHzであるため、高速のトランジェントの数値化及びアンダーサンプリング技法を使用することにより、帯域幅がADCのサンプリング速度以上の帯域の周期信号を測定できます。高周波信号が計測する周波数帯域にエイリアシングしてくるのを防ぐために、アンチエイリアシングフィルタリングを推奨します。

#### 变換開始方法

変換は、制御バイトを書き込むことによって開始して下さい。制御バイトはマルチプレクサチャネルを選択し、MAX1291/MAX1293をユニポーラ又はバイポーラ動作に設定します。書込みパルス $(\overline{WR}+\overline{CS})$ は、アクイジション期間又は複合アクイジション+変換を開始できます。サンプリング期間はアクイジション期間の最後

に始まります。入力制御バイト(表1)のACQMOD(アクイジションモード)ビットは、信号の取り込み方として内部アクイジション及び外部アクイジションの2つのオプションを提供しています。クロック又はアクイジションモードが内部又は外部のいずれの場合も、変換期間は13クロックサイクルだけ持続します。変換中に新しい制御バイトを書き込むと、その変換が中止されて新しいアクイジション期間が始まります。

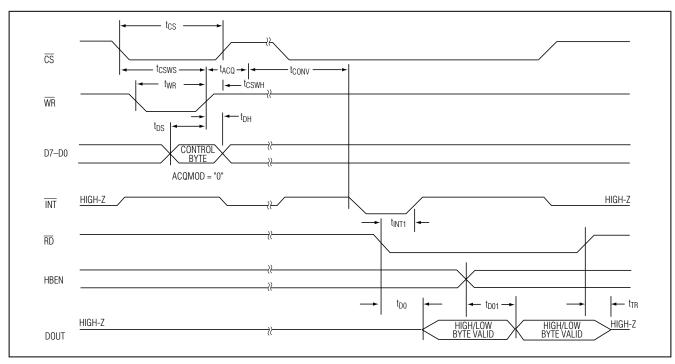

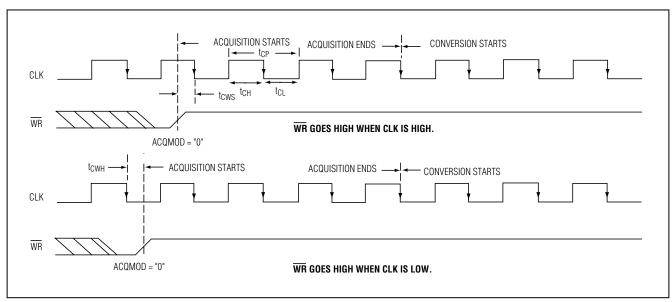

### 内部アクイジション

制御バイトを書き込む時にACQMODをクリアしておくと (ACQMOD = 0)、内部アクイジションが選択されます。この場合、持続時間が内部で設定されたアクイジション 期間が書込みパルスによって始まります。変換はこの アクイジション期間が終わった時点で始まります(3外部 サイクル、あるいは内部クロックモードの場合は約1µs) (図4)。内部アクイジションと内部クロックの組み合わせ の場合、アパーチャジッタが200psに達することがあることに注意して下さい。内部クロックでジッタ仕様50ps を実現する場合は、常に外部アクイジションモードを 使用して下さい。

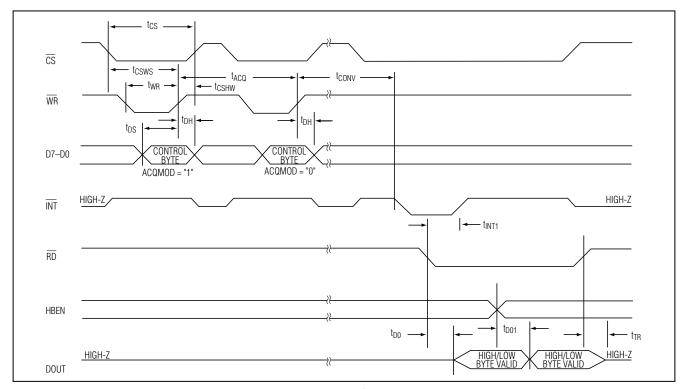

#### 外部アクイジション

サンプリングアパーチャを正確に制御する場合やアクイジションと変換時間を連携して制御する場合は、外部アクイジションモードを使用して下さい。2つの個別の書込みパルスを使用することによって、アクイジション及び変換開始を制御します。第1のパルスはACQMOD=1で書き込まれ、長さ不定のアクイジション期間を開始します。第2の書込みパルスはACQMOD=0で書き込まれ、 $\overline{\text{WR}}$ の立上がりエッジでアクイジションを終了して変換を開始します(図5)。

入力マルチプレクサのアドレスビットは、第1及び第2の書込みパルスで同じ値を持っていることが必要です。パワーダウンモードビット(PDO、PD1)は、第2の書込みパルスで新しい値にすることができます(「パワーダウンモード」を参照)。制御バイトのその他のビットを変更すると、変換が破壊されます。

### 変換の読取り

MAX1291/MAX1293では、変換が終了して有効な結果が読み取れる状態になったことをマイクロプロセッサに知らせるフラグを出すための標準割込み信号INTが提供されています。INTは、変換が完了して出力データが準備できた時点でローになります(図4、5)。そして、最初の読取りサイクルが始まった時又は新しい制御バイトが書き込まれた時にハイに戻ります。

## 表1. 制御バイトの機能の説明

| BIT        | NAME       | FUNCTION         |                                                                                                                                                                                                                                                                                                                              |                                                      |  |  |  |

|------------|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

|            |            | PD1 an           | d <b>PD0</b> s                                                                                                                                                                                                                                                                                                               | elect the various clock and power-down modes.        |  |  |  |

|            |            | 0                | 0                                                                                                                                                                                                                                                                                                                            | Full Power-Down Mode. Clock mode is unaffected.      |  |  |  |

| D7, D6     | PD1, PD0   | 0                | 1                                                                                                                                                                                                                                                                                                                            | Standby Power-Down Mode. Clock mode is unaffected.   |  |  |  |

|            |            | 1 0              |                                                                                                                                                                                                                                                                                                                              | Normal Operation Mode. Internal clock mode selected. |  |  |  |

|            |            | 1                | Normal Operation Mode. External clock mode selected.                                                                                                                                                                                                                                                                         |                                                      |  |  |  |

| D5         | ACQMOD     |                  | ACQMOD = 0: Internal Acquisition Mode ACQMOD = 1: External Acquisition Mode                                                                                                                                                                                                                                                  |                                                      |  |  |  |

| D4         | SGL/DIF    | SGL/D<br>In sing | SGL/DIF = 0: Pseudo-Differential Analog Input Mode SGL/DIF = 1: Single-Ended Analog Input Mode In single-ended mode, input signals are referred to COM. In pseudo-differential mode, the voltage difference between two channels is measured (see Tables 2, 3).                                                              |                                                      |  |  |  |

| D3         | UNI/BIP    | UNI/B<br>In unip | $ \begin{array}{l} UNI/\overline{BIP} = 0: \ Bipolar \ Mode \\ UNI/\overline{BIP} = 1: \ Unipolar \ Mode \\ In \ unipolar \ mode, \ an \ analog \ input \ signal \ from 0 \ to \ V_{REF} \ can \ be \ converted; \ in \ bipolar \ mode, \ the \ signal \ can \ range \ from \ -V_{REF}/2 \ to \ +V_{REF}/2. \\ \end{array} $ |                                                      |  |  |  |

| D2, D1, D0 | A2, A1, A0 |                  | Address bits A2, A1, A0 select which of the 8/4 (MAX1291/MAX1293) channels are to be converted (see Tables 3, 4).                                                                                                                                                                                                            |                                                      |  |  |  |

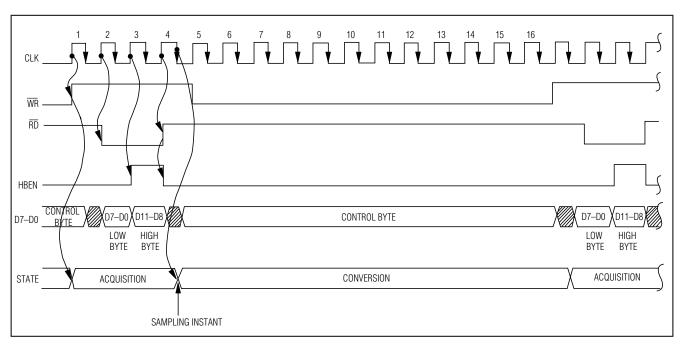

図4. 内部アクイジションモードを使用した変換のタイミング

図5. 外部アクイジションモードを使用した変換のタイミング

### クロックモードの選択

MAX1291/MAX1293は、内部又は外部クロックのいずれでも動作します。制御ビットD6及びD7によって、内部又は外部クロックモードを選択します。その時の入力ワードでパワーダウンモードが選択されると、素子は最後にリクエストされたクロックモードを保持します。内部及び外部クロックモードのいずれの場合も、内部又は外部アクイジションのどちらでも使用できます。パワーアップ時には、MAX1291/MAX1293はデフォルトの外部クロックモードになります。

### 内部クロックモード

内部クロックモードにすると、µPはSAR変換クロックを動作させる役割から解放されます。このモードを選択するには、制御バイトのビットD7を1に、ビットD6を0に設定する必要があります。これにより内部クロック周波数が選択され、変換時間が3.6µsとなります。内部クロックモードを使用する場合は、CLKピンがフローティングにならないようにハイ又はローに接続して下さい。

### 外部クロックモード

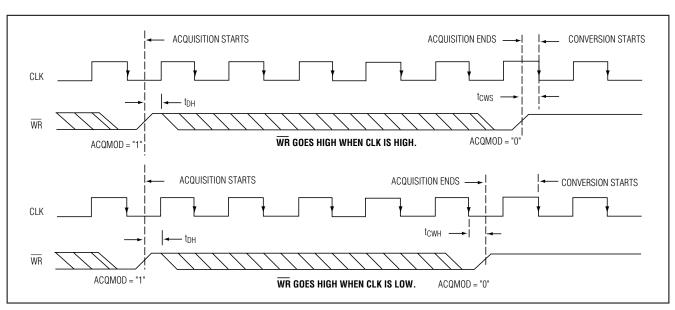

外部クロックモードを選択するには、制御バイトのD6 及びD7をゼロに設定する必要があります。図6に、外部クロックによる内部(図6a)及び外部(図6b)アクイジションモードのクロック及びWRタイミングの関係を示します。適正な動作には、デューティサイクルが30%~70%で周波数が100kHz~4.8MHzのクロックを推奨します。100kHz以下のクロック周波数でMAX1291/MAX1293を動作させることは推奨しません。

これは、T/H段のホールドコンデンサの両端の電圧が低下して性能が劣化するためです。

### ディジタルインタフェース

入力(制御バイト)及び出力データは、スリーステートパラレルインタフェース上で多重化されます。このパラレルインタフェース(I/O)は、標準 $\mu$ Pと簡単にインタフェースすることができます。信号 $\overline{CS}$ 、 $\overline{WR}$ 及び $\overline{RD}$ が書込み及び読取り動作を制御します。 $\overline{CS}$ はチップ選択信号です。この信号によって $\mu$ PはMAX1291/MAX1293をI/Oポートとしてアドレス指定できます。 $\overline{CS}$ がハイの時にはCLK  $\overline{WR}$ 及び $\overline{RD}$ 入力がディセーブルされ、インタフェースは強制的にハイインピーダンス状態(ハイZ)になります。

### 入力フォーマット

制御バイトは、書き込みコマンド中にピンD7~D0にラッチされます。表2に制御バイトフォーマットを示します。

### 出力フォーマット

MAX1291/MAX1293の出力フォーマットはユニポーラモードにおいてはバイナリ、バイポーラモードにおいては2の補数形式です。出力データを読み取る時には $\overline{CS}$ 及び $\overline{RD}$ がローであることが必要です。HBEN = 1の時は下位8ビットが読まれます。HBEN = 1の時は上位4ビットが読取り可能で、出力データビットD7~D4はユニポーラモードでローに設定され、バイポーラモードにおいてはMSBの値に設定されます(表5)。

図6a. 外部クロック及びWRタイミング(内部アクイジションモード)

図6b. 外部クロック及びWRタイミング(外部アクイジションモード)

## 表2. 制御バイトフォーマット

| D7 (MSB) | D6  | D5     | D4      | D3      | D2 | D1 | D0 (LSB) |

|----------|-----|--------|---------|---------|----|----|----------|

| PD1      | PD0 | ACQMOD | SGL/DIF | UNI/BIP | A2 | A1 | A0       |

# 表3. シングルエンド動作のチャネル選択(SGL/DIF = 1)

| A2 | A1 | A0 | CH0 | CH1 | CH2 | СНЗ | CH4* | CH5* | CH6* | CH7* | СОМ |

|----|----|----|-----|-----|-----|-----|------|------|------|------|-----|

| 0  | 0  | 0  | +   |     |     |     |      |      |      |      | -   |

| 0  | 0  | 1  |     | +   |     |     |      |      |      |      | -   |

| 0  | 1  | 0  |     |     | +   |     |      |      |      |      | -   |

| 0  | 1  | 1  |     |     |     | +   |      |      |      |      | -   |

| 1  | 0  | 0  |     |     |     |     | +    |      |      |      | -   |

| 1  | 0  | 1  |     |     |     |     |      | +    |      |      | -   |

| 1  | 1  | 0  |     |     |     |     |      |      | +    |      | -   |

| 1  | 1  | 1  |     |     |     |     |      |      |      | +    | -   |

<sup>\*</sup>チャネルCH4~CH7は、MAX1291のみに適用します。

## 表4. 疑似差動動作のチャネル選択(SGL/ $\overline{DIF} = 0$ )

| A2 | A1 | A0 | CH0 | CH1 | CH2 | СНЗ | CH4* | CH5* | CH6* | CH7* |

|----|----|----|-----|-----|-----|-----|------|------|------|------|

| 0  | 0  | 0  | +   | -   |     |     |      |      |      |      |

| 0  | 0  | 1  | -   | +   |     |     |      |      |      |      |

| 0  | 1  | 0  |     |     | +   | -   |      |      |      |      |

| 0  | 1  | 1  |     |     | -   | +   |      |      |      |      |

| 1  | 0  | 0  |     |     |     |     | +    | -    |      |      |

| 1  | 0  | 1  |     |     |     |     | -    | +    |      |      |

| 1  | 1  | 0  |     |     |     |     |      |      | +    | -    |

| 1  | 1  | 1  |     |     |     |     |      |      | -    | +    |

<sup>\*</sup>チャネルCH4~CH7は、MAX1291のみに適用します。

## アプリケーション情報

### パワーオンリセット

最初に電源が投入された時、内部パワーオンリセット 回路がMAX1291/MAX1293を外部クロックモードで 状態で起動し、 $\overline{\text{INT}}$ をハイに設定します。電源が安定化 した後の内部リセット時間は $10\mu \text{s}$ です。この時変換を 行わないで下さい。内部リファレンスを使用する場合 は、 $V_{\text{RFF}}$ が安定するのに $500\mu \text{s}$ を要します。

## 内部及び外部リファレンス

MAX1291/MAX1293は、内部又は外部リファレンス 電圧を使用できます。外部リファレンス電圧は、直接 REF又はREFADJに接続できます。

MAX1291及びMAX1293のいずれの場合も、内部バッファはREFで+2.5Vを供給するように設計されています。内部でトリミングされた+1.22Vリファレンスが利得+2.05V/Vでバッファされています。

# 表5. データバス出力(8+4パラレルインタフェース)

|     | 1 - 2 - 2 - 2 - 2 |                          |                           |  |  |  |  |  |

|-----|-------------------|--------------------------|---------------------------|--|--|--|--|--|

| PIN | HBEN = 0          | HBEN = 1                 |                           |  |  |  |  |  |

| D0  | BIT 0 (LSB)       | BIT 8                    |                           |  |  |  |  |  |

| D1  | BIT 1             | BI <sup>-</sup>          | Г9                        |  |  |  |  |  |

| D2  | BIT 2             | BIT                      | 10                        |  |  |  |  |  |

| D3  | BIT 3             | BIT 11 (MSB)             |                           |  |  |  |  |  |

| D4  | BIT 4             | BIPOLAR<br>(UNI/BIP = 0) | UNIPOLAR<br>(UNI/BIP = 1) |  |  |  |  |  |

|     |                   | BIT 11                   | 0                         |  |  |  |  |  |

| D5  | BIT 5             | BIT 11                   | 0                         |  |  |  |  |  |

| D6  | BIT 6             | BIT 11 0                 |                           |  |  |  |  |  |

| D7  | BIT 7             | BIT 11 0                 |                           |  |  |  |  |  |

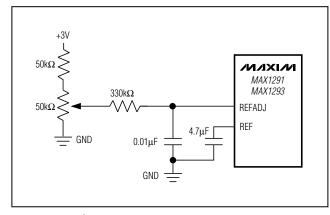

## 内部リファレンス

内部リファレンスの場合、フルスケール範囲はユニポーラ 入力の場合+2.5V、バイポーラ入力の場合±1.25Vです。 内部リファレンスバッファは、リファレンス電圧の 微調整(±100mV)が可能になっています。図7を参照 して下さい。

リファレンスバッファは、REFとGNDの間の外部コンデンサ( $4.7\mu F$  min)で補償される必要があることに注意して下さい。これは、リファレンスノイズとADCからのスイッチングスパイクを低減するためです。リファレンスのノイズをさらに小さくするには、REFADJとGNDの間に $0.01\mu F$ コンデンサを接続して下さい。

### 外部リファレンス

MAX1291とMAX1293は、いずれも内部リファレンス バッファアンプの入力(REFADJ)又は出力(REF)において 外部リファレンスに接続できます。

REFADJ入力を使用すると外部リファレンスをバッファする必要がなくなります。REFADJの入力インピーダンスは17k $\Omega$ (typ)です。

図7. 外部ポテンショメータを使用したリファレンス 電圧調節

外部リファレンスをREFに印加する場合は、REFADJを $V_{DD}$ に接続することによって内部リファレンスバッファをディセーブルして下さい。REFにおけるDC入力抵抗は25k $\Omega$ であるため、REFにおける外部リファレンスが変換中に最大200 $\mu$ AのDC負荷電流を供給し、出力インピーダンスが10 $\Omega$ 以下であることが必要です。リファレンスの出力インピーダンスがこれよりも大きかったり、ノイズが大きい場合には、REFピンの近くで4.7 $\mu$ Fコンデンサを使用してバイパスして下さい。

### パワーダウンモード

変換の合間にコンバータを低電流シャットダウン状態にすることによって、電力を節約することができます。制御バイトのD6及びD7を使用して、スタンバイモード又はシャットダウンモードを選択して下さい(表1及び2)。いずれのソフトウェアパワーダウンモードにおいてもパラレルインタフェースはアクティブのままですが、AD変換を行いません。

### スタンバイモード

スタンバイモードにおいては、消費電流が850μA(typ)です。素子は、次のWRの立上がりエッジでパワーアップし、変換可能な状態になります。このようにターンオンが速いため、250ksps以下の変換速度において大幅な省電力が可能です。

#### シャットダウンモード

シャットダウンモードにおいては、自己消費電流を 費やす全てのチップ機能がターンオフされて、その時

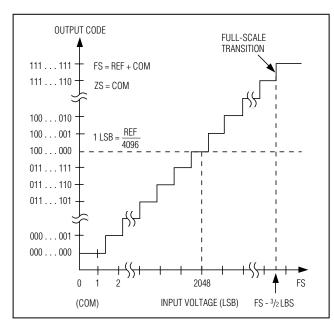

図8. ユニポーラ伝達関数

の変換が完了した直後に標準消費電流が $2\mu$ Aに低下します。 $\overline{WR}$ の立上がりエッジでMAX1291/MAX1293はシャットダウンモードを終了し、通常動作に戻ります。 4.7 $\mu$ Fのリファレンスバイパスコンデンサを使用してフル12ビット精度を実現するには、パワーアップ後に500 $\mu$ Sが必要です。この500 $\mu$ Sをフルパワーモードではなくスタンバイモードで待つと、消費電力を3分の1以下に減らすことができます。外部リファレンスを使用する場合、パワーアップ後の待ち時間は僅か50 $\mu$ Sで済みます。スタンバイモードに入るには、制御バイトでスタンバイモードを指定してダミーの変換を行って下さい。

注記: REFとGNDの間のバイパスコンデンサが4.7μF よりも大きいと、パワーアップ遅延が長くなります。

### 伝達関数

表6に、ユニポーラ及びバイポーラモードのフルスケール電圧範囲を示します。

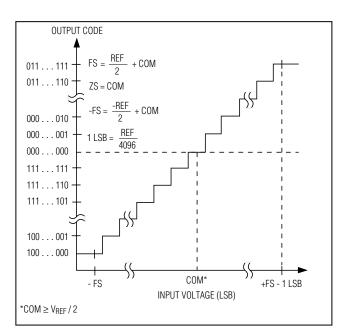

図8に公称ユニポーラ入力/出力(I/O)伝達関数を、図9 にバイポーラ(I/O)伝達関数を示します。コード遷移は、連続する整数のLSB値同士の中間で起こります。出力コードはバイナリで、 $1LSB = (V_{RFF}/4096)$ です。

## 最大サンプリング速度/300kspsを実現する方法

最大クロック周波数4.8MHzで動作している時、19 クロックサイクル毎に変換を完了することにより仕様 のスループット250kspsを実現できます。19サイクル のうちわけは、1書込みサイクル、3アクイジション

図9. バイポーラ伝達関数

## 表6. ユニポーラ及びバイポーラ動作のフルスケール及びゼロスケール

| UNIPOLA    | AR MODE                | BIPOLAR MODE        |                            |  |

|------------|------------------------|---------------------|----------------------------|--|

| Full Scale | V <sub>REF</sub> + COM | Positive Full Scale | V <sub>REF</sub> /2 + COM  |  |

| Zero Scale | COM                    | Zero Scale          | COM                        |  |

| _          | _                      | Negative Full Scale | -V <sub>REF</sub> /2 + COM |  |

サイクル、13変換サイクル、及び2読取りサイクルです。これは、次の制御バイトが書き込まれる前に最後の変換結果が読み取られると仮定しています。さらに速くするために、次の変換のアクイジションサイクルを開始するための制御ワードを先に書き込んで、その後バスから前の変換を結果を読み取るようにすると、最大300kspsのスループットを実現できます(図10)。この技法を使用すると、16クロックサイクル毎に変換を完了できます。アクイジション中又は変換中にデータバスでスイッチングが起こると電源ノイズの原因となり、真の12ビット性能を実現することが難しくなることに注意して下さい。

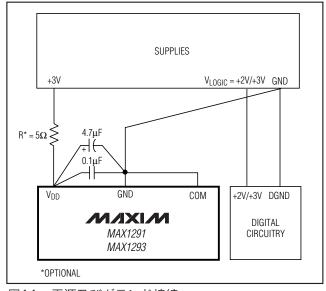

## レイアウト、グランド、及びバイパス

最高の性能を得るために、プリント回路(PC)基板を使用して下さい。ディジタル信号ラインとアナログ信号ラインを分離するレイアウトを必要とするため、ワイヤラップ構成は推奨できません。アナログとディジタルラインを互いに並行に走らせないで下さい。又、ディジタル信号経路がADCパッケージの下に配置されないようにして下さい。アナログとディジタルのプランド部分は別々にして、2つのグランドされるようにして下さい。ノイズを排除するために、このスターグランドから電源へのグランドリターンはでさい。スターグランドから電源へのグランドリターンはでさい。ディジタル信号は、敏感なアナログ及びリファレンス入力から離して配線して下さい。

電源(VDD)内の高周波ノイズが、ADCの高速コンパレータに影響を与える可能性があります。 $V_{DD}$ は、MAX1291/MAX1293にできるだけ近いところで並列の  $0.1\mu$ F及び $4.7\mu$ Fコンデンサを使用してスターグランドにバイパスして下さい。最高の電源ノイズ除去比を得るために、コンデンサのリード線をできるだけ短くして下さい。電源のノイズが特に大きい場合は、減衰抵抗  $(5\Omega)$ を接続して下さい。

## 用語の定義

### 積分非直線性

積分非直線性(INL)は、実際の伝達関数値の直線からの偏差です。この直線は、ベストストレートラインフィットあるいはオフセット及び利得誤差をヌル(ゼロ)にした後に、伝達関数のエンドポイント間を結んだ線です。MAX1291/MAX1293の静的直線性パラメータは、エンドポイント法を使用して測定されます。

### 微分非直線性

微分非直線性(DNL)は、実際のステップの高さと1LSB の理想値の間の差です。DNL誤差の仕様が1LSB未満であれば、ミッシングコードがないこと及びコードは単調性であることが保証されます。

### アパーチャの定義

アパーチャジッタ $(t_{AJ})$ は、サンプルとサンプル間の時間 のばらつきです。アパーチャディレー $(t_{AD})$ は、サンプリングクロックの立上がりエッジと実際にサンプルが取られる瞬間の間の時間です。

### 信号対雑音比

ディジタルサンプルから完ぺきに再構築された波形の場合、信号対雑音比SNRは、フルスケールアナログ入力 (RMS値)のRMS量子化エラー(残留エラー)に対する比です。理想的な最小アナログディジタルノイズは量子化エラーのみに起因し、ADCの分解能(Nビット)によって直接決まります。

$SNR = (6.02 \times N + 1.76)dB$

現実には、量子化ノイズの他にもサーマルノイズ、リファレンスノイズ、クロックジッタ等のノイズソースがあります。このため、SNRを計算する時はRMS信号とRMSノイズの比をとります。RMSノイズは基本波以外の全てのスペクトラル成分、最初の5つの高調波及びDCオフセットを含みます。

### 信号対雑音+歪み(SINAD)

信号対雑音+歪み(SINAD)は、基本入力周波数のRMS 振幅とその他全てのADC出力信号のRMS等価値の比です。

$SINAD(dB) = 20 \times log(信号_{RMS}// イズ_{RMS})$

図10. 最も速い変換のタイミング図

### 有効ビット数

有効ビット数(ENOB)は、特定の入力周波数及びサンプリングレートにおけるADCの包括的な精度です。理想的なADCの誤差は、量子化ノイズのみからなっています。入力範囲がADCのフルスケール範囲に等しい場合、有効ビット数は次式で計算できます。

ENOB = (SINAD - 1.76)/6.02

### 全高調波歪み

全高調波歪み(THD)は、入力信号の最初の5つの高調波 RMS和と基本波そのものの比です。これは次式で表され ます。

THD =

$$20 \times \log \left( \sqrt{(V_2^2 + V_3^2 + V_4^2 + V_5^2)} / V_1 \right)$$

ここで、 $V_1$ は基本波の振幅、 $V_2 \sim V_5$ は2次 $\sim$ 5次高調波の振幅です。

### スプリアスフリーダイナミックレンジ

スプリアスフリーダイナミックレンジ(SFDR)は、基本波 (最大信号成分)のRMS振幅と次に大きな歪み成分のRMS値の比です。

図11. 電源及びグランド接続

# チップ情報 \_\_\_\_\_

TRANSISTOR COUNT: 5781 SUBSTRATE CONNECTED TO GND

## 標準動作回路

## ピン配置(続き)

# 型番(続き)

| PART        | TEMP RANGE     | PIN-PACKAGE | INL<br>(LSB) |

|-------------|----------------|-------------|--------------|

| MAX1293ACEG | 0°C to +70°C   | 24 QSOP     | ±0.5         |

| MAX1293BCEG | 0°C to +70°C   | 24 QSOP     | ±1           |

| MAX1293AEEG | -40°C to +85°C | 24 QSOP     | ±0.5         |

| MAX1293BEEG | -40°C to +85°C | 24 QSOP     | ±1           |

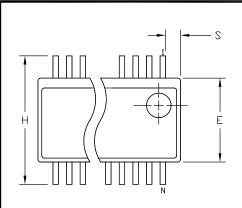

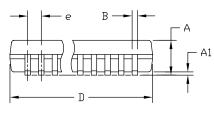

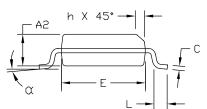

パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packagesをご参照下さい。)

|     | INCH  | ES     | MILLIM    | ETERS |  |

|-----|-------|--------|-----------|-------|--|

| DIM | MIN   | MAX    | MIN       | MAX   |  |

| Α   | .061  | .068   | 1.55      | 1.73  |  |

| A1  | .004  | .0098  | 0.102     | 0.249 |  |

| A2  | .055  | .061   | 1.40      | 1.55  |  |

| В   | .008  | .012   | 0.20      | 0.30  |  |

| С   | .0075 | .0098  | 0.191     | 0.249 |  |

| D   |       | SEE VA | RIATIONS  |       |  |

| Ε   | .150  | .157   | 3.81      | 3.99  |  |

| е   | .025  | 5 BSC  | 0.635 BSC |       |  |

| Н   | .230  | .244   | 5.84      | 6.20  |  |

| h   | .010  | .016   | 0.25      | 0.41  |  |

| L   | .016  | .035   | 0.41      | 0.89  |  |

| N   |       | SEE VA | RIATION   | 2     |  |

| α   | 0, 8, |        | 0°        | 8°    |  |

#### VARIATIONS:

|   | INCHE | S     | MILLIM |       |       |

|---|-------|-------|--------|-------|-------|

|   | MIN.  | MAX.  | MIN.   | MAX.  | N     |

| D | .189  | .196  | 4.80   | 4.98  | 16 AB |

| S | .0020 | .0070 | 0.05   | 0.18  |       |

| D | .337  | .344  | 8.56   | 8.74  | 20 AD |

| S | .0500 | .0550 | 1.270  | 1.397 |       |

| D | .337  | .344  | 8.56   | 8.74  | 24 AE |

| S | .0250 | .0300 | 0.635  | 0.762 |       |

| D | .386  | .393  | 9.80   | 9.98  | 28 AF |

| S | .0250 | .0300 | 0.635  | 0.762 |       |

#### NOTES:

- 1). D & E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

- 2). MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .006" PER SIDE.

- 3). CONTROLLING DIMENSIONS: INCHES.

- 4). MEETS JEDEC MO137.

# DALLAS /// JX //

PROPRIETARY INFORMATION

PACKAGE OUTLINE, QSOP .150", .025" LEAD PITCH

21-0055

E 1

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。 マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

20 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600