# MIXIM

### +3V、18ビット、低電力マルチチャネル オーバサンプリング(シグマ-デルタ)ADC

#### 概要

MAX1403は、センサ励起用にマッチングされた200µA の電流ソースを備えた18ビット低電力マルチチャネル、 シリアル出力アナログディジタルコンバータ(ADC) です。本ADCは16ビット精度を実現するために、ディジ タルデシメーションフィルタ付のシグマ-デルタ変調器 を使用しています。ディジタルフィルタのデシメーション 係数を選択できるため、変換分解能を落として出力 データ速度を速くすることができます。出力データ速度 480spsまで、真の16ビット性能を実現します。さら に、変調器のサンプリング周波数の最適化により、電力 消費を最小にするか、あるいはスループット速度を 最大にすることができます。MAX1403は+3V電源で 動作します。

本デバイスは、利得を+1V/V~+128V/Vに個別設定 できる3つの完全差動入力チャネルを備えています。 さらに、選択されたフルスケール範囲の117%まで入力 を基準としたDCオフセット(システムオフセット等)を 補償できます。これら3つの差動チャネルは、5つの 疑似差動入力チャネルとして設定することも可能です。 利得及びオフセット誤差補正用に、2つの差動システム キャリブレーションチャネルが追加されています。

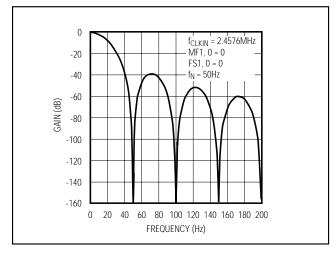

MAX1403は、全ての信号チャネルを順番にスキャンし、 シリアルインタフェースを通じて結果を出力するように 設定することもできます。この場合の通信オーバヘッド は最小限で済みます。2.4576MHz又は1.024MHzの マスタークロックと共に使用した場合、ライン周波数 及び関連する高調波におけるディジタルデシメーション フィルタの周波数応答をゼロにすることにより、ポスト フィルタリングなしで優れたライン除去比を保証でき ます。

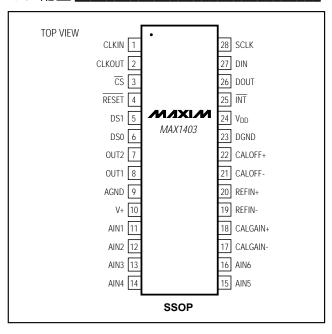

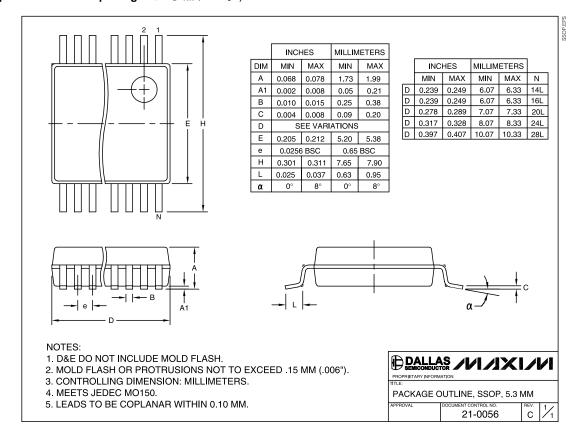

MAX1403は28ピンSSOPパッケージで提供されて います。

#### アプリケーション

ポータブル工業用計器

ポータブル重量計

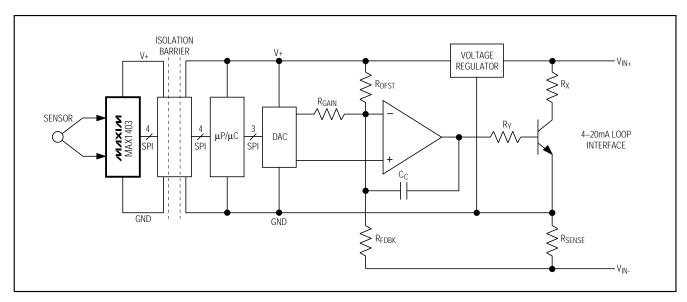

ループ電力機器

圧力トランスデューサ

#### 型番

| Ì | PART       | TEMP RANGE     | PIN-PACKAGE |

|---|------------|----------------|-------------|

|   | MAX1403CAI | 0°C to +70°C   | 28 SSOP     |

|   | MAX1403EAI | -40°C to +85°C | 28 SSOP     |

SPI及びQSPIはMotorola, Inc.の商標です。

#### 特長

- ◆ 分解能18ビットのシグマ・デルタADC

- ◆ 480spsまで分解能16ビットを保持 (ミッシングコードなし)

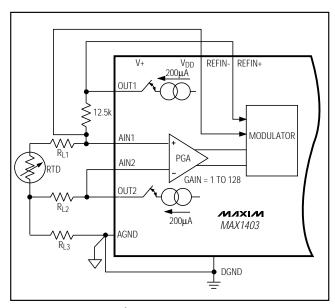

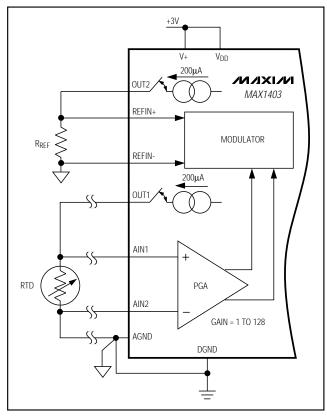

- ◆ センサ励起用のマッチングされた内蔵電流ソース  $(200 \mu A)$

- ◆ 低自己消費電流 250µA(動作モード) 2μA(パワーダウンモード)

- ◆ 3つの完全差動又は5つの疑似差動信号入力チャネル

- ◆ 2つの完全差動キャリブレーションチャネル/ 補助入力チャネルを追加

- ◆ 利得及びオフセットは設定可能

- ◆ 完全差動リファレンス入力

- ◆ 連続又はオンコマンドで変換

- ◆ 自動チャネルスキャン及び連続データ出力モード

- ◆ アナログ及びディジタル電源:+2.7V~+3.6V

- ◆ 3線シリアルインタフェース: SPI™/QSPI™コンパチブル

- ◆ パッケージ: 28ピンSSOP

#### ピン配置

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to AGND, DGNDVDD to AGND, DGND |                                  |

|-----------------------------------|----------------------------------|

| AGND to DGND                      |                                  |

| Analog Inputs to AGND             | 0.3V to (V+ + 0.3V)              |

| Analog Outputs to AGND            | 0.3V to $(V + + 0.3V)$           |

| Reference Inputs to AGND          | 0.3V to (V+ + 0.3V)              |

| CLKIN and CLKOUT to DGND          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| All Other Digital Inputs to DGND  | 0.3V to +6V                      |

| All Digital Outputs to DGND       | 0.3V to (V <sub>DD</sub> + 0.3V) |

| 50mA       |

|------------|

|            |

| 524mW      |

|            |

| C to +70°C |

| C to +85°C |

| to +150°C  |

| +300°C     |

|            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+=+2.7V \text{ to } +3.6V, V_{DD}=+2.7V \text{ to } +3.6V, V_{REFIN+}=+1.25V, REFIN-=AGND, f_{CLKIN}=2.4576MHz, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER                         | SYMBOL | CONDITIONS                                                              | MIN     | TYP      | MAX    | UNITS      |

|-----------------------------------|--------|-------------------------------------------------------------------------|---------|----------|--------|------------|

| STATIC PERFORMANCE                |        |                                                                         |         |          |        |            |

| Noise-Free Resolution             |        | No missing codes guaranteed by design; for filter settings with FS1 = 0 | 16      |          |        | Bits       |

| Output Noise                      |        | Depends on filter setting and selected gain                             | (Tab    | les 16a, | 16b)   |            |

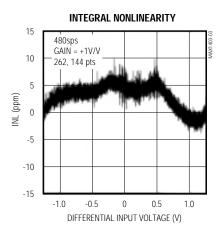

| Integral Nonlinearity             | INII   | Bipolar mode; FS1 = 0; MF1, MF0 = 0                                     | -0.0015 |          | 0.0015 | 0/ ECD     |

| (Note 1)                          | INL    | FS1 = 0; MF1, MF0 = 1, 2, 3                                             |         | ±0.001   |        | %FSR       |

| Nominal Gain (Note 2)             |        |                                                                         |         | 0.98     |        |            |

| Unipolar Offset Error             |        | Relative to nominal of 1% FSR                                           | -1      |          | 2      | %FSR       |

| Unipolar Offset Drift             |        | For gains of 1, 2, 4                                                    |         | 0.5      |        | 11/1°C     |

| Onipolal Oliset Driit             |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μV/°C      |

| Bipolar Zero Error                |        |                                                                         | -2.0    |          | 2.0    | %FSR       |

| Dipolar Zara Drift                |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | μV/°C      |

| Bipolar Zero Drift                |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | ] μν/ C    |

| Positive Full-Scale Error         |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2.5    |          | 2.5    | %FSR       |

| (Note 3)                          |        | For gain of 128                                                         | -3.5    |          | 3.5    | %FSR       |

| Full Scale Drift (Note 4)         |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | 11/1/°C    |

| Full-Scale Drift (Note 4)         |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μV/°C      |

| Cain Error (Note E)               |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2      |          | 2      | %FSR       |

| Gain Error (Note 5)               |        | For gain of 128                                                         | -3      |          | 3      | %FSR       |

| Cain From Drift (Note ()          |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | 1       |          |        | 10 to 10 C |

| Gain-Error Drift (Note 6)         |        | For gain of 128                                                         |         | 5        |        | ppm/°C     |

| Dinalar Magativa Full Coals From  |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2.5    |          | 2.5    | %FSR       |

| Bipolar Negative Full-Scale Error |        | For gain of 128                                                         | -3.5    |          | 3.5    | %FSR       |

| Dinalar Nagativa Full Coals Drift |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | \//°C      |

| Bipolar Negative Full-Scale Drift |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μV/°C      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+2.7V\ to\ +3.6V,\ V_{DD}=+2.7V\ to\ +3.6V,\ V_{REFIN+}=+1.25V,\ REFIN-=AGND,\ f_{CLKIN}=2.4576MHz,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.)$

| PARAMETER                                     | SYMBOL    |                     | CONDITIONS                                                                      | MIN                         | TYP                  | MAX          | UNITS  |

|-----------------------------------------------|-----------|---------------------|---------------------------------------------------------------------------------|-----------------------------|----------------------|--------------|--------|

| OFFSET DAC                                    |           |                     |                                                                                 |                             |                      |              |        |

| O"   DAO D                                    |           | Unipolar mode       |                                                                                 | -116.7                      |                      | 116.7        | 0/ 500 |

| Offset DAC Range (Note 7)                     |           | Bipolar mode        |                                                                                 | -58.35                      |                      | 58.35        | %FSR   |

| Off + DAO D   - +                             |           | Unipolar mode       |                                                                                 |                             | 16.7                 |              | 0/ ECD |

| Offset DAC Resolution                         |           | Bipolar mode        |                                                                                 |                             | 8.35                 |              | %FSR   |

| Official DAC Full Scale Error                 |           | Input referred      | Gain = 1, 2, 4, 8, 16, 32, 64                                                   | -2.5                        |                      | +2.5         | %FSR   |

| Offset DAC Full-Scale Error                   |           | Inputreierred       | Gain = 128                                                                      | -3.5                        |                      | +3.5         | %F3R   |

| Offset DAC Zero-Scale Error                   |           |                     |                                                                                 |                             | 0                    |              | %FSR   |

| Additional Noise from Offset DAC (Note 8)     |           | DAC code = 000      | 00                                                                              |                             | 0                    |              | μVRMS  |

| ANALOG INPUTS/REFERENCE                       | INPUTS (S | pecifications for A | IN and REFIN, unless otherwis                                                   | e noted.)                   |                      |              |        |

|                                               |           | At DC               |                                                                                 | 90                          |                      |              |        |

| Common-Mode Rejection                         | CMR       |                     | 0Hz, ±0.02 • fNOTCH,<br>0, f <sub>CLKIN</sub> = 2.4576MHz (Note 9)              | 150                         |                      |              | dB     |

|                                               |           |                     | DHz, ±0.02 • f <sub>NOTCH</sub> ,<br>0, f <sub>CLKIN</sub> = 2.4576MHz (Note 9) | 150                         |                      |              |        |

| Normal Mode 50Hz Rejection (Note 9)           | NMR       |                     | 0Hz, ±0.02 • f <sub>NOTCH</sub> ,<br>0, f <sub>CLKIN</sub> = 2.4576MHz          | 100                         |                      |              | dB     |

| Normal Mode 60Hz Rejection (Note 9)           | NMR       |                     | 0Hz, ±0.02 • fnotch,<br>0, f <sub>CLKIN</sub> = 2.4576MHz                       | 100                         |                      |              | dB     |

| Common-Mode Voltage Range (Note 10)           |           | REFIN and AIN f     | or BUFF = 0                                                                     | V <sub>AGND</sub>           |                      | V+           | V      |

| Absolute Input Voltage Range                  |           | REFIN and AIN f     | or BUFF = 0                                                                     | V <sub>AGND</sub><br>- 30mV |                      | V+<br>+ 30mV | V      |

| Absolute and Common-Mode<br>AIN Voltage Range |           | BUFF = 1            |                                                                                 | VAGND<br>+ 200mV            |                      | V+<br>- 1.5  | V      |

| DC Input Leakage Current                      |           | REFIN and AIN f     | $T_A = +25^{\circ}C$                                                            |                             | 40                   |              | рА     |

| (Note 11)                                     |           | BUFF = 0            | TA = TMIN to TMAX                                                               |                             |                      | 10           | nA     |

| AIN Input Current (Note 11)                   |           | BUFF = 1            |                                                                                 |                             |                      | 10           | nA     |

|                                               |           |                     | Gain = 1                                                                        |                             | 34                   |              |        |

| AIN Input Capacitance (Notes 12)              |           | BUFF = 0            | Gain = 2                                                                        |                             | 38                   |              |        |

|                                               |           | 5011 - 0            | Gain = 4                                                                        |                             | 45                   |              | pF     |

| · · · · · · · · · · · · · · · · · · ·         |           |                     | Gain = 8, 16, 32, 64, 128                                                       |                             | 60                   |              |        |

|                                               |           | BUFF = 1, all ga    |                                                                                 |                             | 30                   |              |        |

| AIN Differential Voltage Range                |           |                     | inge (U/B bit = 1)                                                              |                             | V <sub>REF</sub> / g |              | V      |

| (Note 13)                                     |           | Bipolar input ran   | $ge (U/\overline{B} bit = 0)$                                                   | ± V                         | 'REF / ga            | in           |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+2.7V \text{ to } +3.6V, V_{DD}=+2.7V \text{ to } +3.6V, V_{REFIN+}=+1.25V, REFIN-=AGND, f_{CLKIN}=2.4576MHz, T_{A}=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_{A}=+25^{\circ}C.)$

| PARAMETER                              | SYMBOL                                | CONDITIONS                                                            | MIN                   | TYP      | MAX      | UNITS  |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------------|-----------------------|----------|----------|--------|

| AIN and REFIN Input Sampling Frequency | fs                                    |                                                                       | Т)                    | able 15) | ı        | Hz     |

| REFIN+ - REFIN- Voltage<br>(Note 14)   |                                       | ±5% for specified performance; functional with lower V <sub>REF</sub> |                       |          | 1.25     | V      |

| LOGIC INPUTS                           |                                       |                                                                       |                       |          |          |        |

| Input Current                          | liN                                   |                                                                       | -10                   |          | +10      | μΑ     |

| Input Law Voltage                      | \/                                    | All inputs except CLKIN                                               |                       |          | 0.4      | V      |

| Input Low Voltage                      | VIL                                   | CLKIN only                                                            |                       |          | 0.4      | V      |

| Lance of Library Market and            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | All inputs except CLKIN                                               | 2                     |          |          | \/     |

| Input High Voltage                     | VIH                                   | CLKIN only                                                            | 2.4                   |          |          | V      |

| Input Hysteresis                       | V <sub>H</sub> YS                     | All inputs except CLKIN                                               |                       | 200      |          | mV     |

| LOGIC OUTPUTS                          |                                       |                                                                       |                       |          |          |        |

| 0   1   1   1   1   1   1   1   1   1  | .,                                    | DOUT and INT, ISINK = 100µA                                           |                       |          | 0.4      |        |

| Output Low Voltage (Note 15)           | Vol                                   | CLKOUT, ISINK = 10µA                                                  |                       |          | 0.4      | V      |

| 0                                      |                                       | DOUT and INT, I <sub>SOURCE</sub> = 100μA                             | V <sub>DD</sub> - 0.3 |          |          |        |

| Output High Voltage (Note 15)          | Voн                                   | CLKOUT, ISOURCE = 10µA                                                | V <sub>DD</sub> - 0.3 |          |          | V      |

| Floating-State Leakage Current         | IL                                    |                                                                       | -10                   |          | 10       | μΑ     |

| Floating-State Output<br>Capacitance   | Co                                    |                                                                       |                       | 9        |          | pF     |

| TRANSDUCER BURN-OUT (No                | te 16)                                | I                                                                     |                       |          |          |        |

| Current                                | IBO                                   |                                                                       |                       | 0.1      |          | μΑ     |

| Initial Tolerance                      |                                       |                                                                       |                       | ±10      |          | %      |

| Drift                                  |                                       |                                                                       |                       | ±0.05    |          | %/°C   |

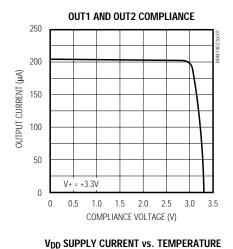

| TRANSDUCER EXCITATION CO               | JRRENTS                               |                                                                       |                       |          |          |        |

| Current                                | I <sub>EXC</sub>                      |                                                                       |                       | 200      |          | uA     |

| Initial Tolerance                      |                                       |                                                                       |                       |          | 15       | %      |

| Drift                                  |                                       |                                                                       |                       | 100      |          | ppm/°C |

| Match                                  |                                       | OUT1 to OUT2                                                          |                       |          | ±1       | %      |

| Drift Match                            |                                       |                                                                       |                       | 5        |          | ppm/°C |

| Compliance Voltage Range               |                                       |                                                                       | Vagnd                 |          | V+ - 1.0 | V      |

| POWER REQUIREMENTS                     | 1                                     | ı                                                                     |                       |          |          | 1      |

| V+ Voltage                             | V+                                    | For specified performance                                             | 2.7                   |          | 3.6      | V      |

| V <sub>DD</sub> Voltage                | V <sub>DD</sub>                       |                                                                       | 2.7                   |          | 3.6      | V      |

| Power-Supply Rejection V+ (Note 17)    | PSR                                   |                                                                       | 1)                    | Note 18) |          | dB     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+2.7V\ to\ +3.6V,\ V_{DD}=+2.7V\ to\ +3.6V,\ V_{REFIN+}=+1.25V,\ REFIN-=AGND,\ f_{CLKIN}=2.4576MHz,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.)$

| PARAMETER                                                    | SYMBOL          |                                 | CONDITIONS     | i           | MIN         | TYP         | MAX         | UNITS |     |     |

|--------------------------------------------------------------|-----------------|---------------------------------|----------------|-------------|-------------|-------------|-------------|-------|-----|-----|

| ANALOG POWER-SUPPLY CU transducer excitation currents d      |                 |                                 |                |             |             | CLKIN, bu   | ırn-out an  | d     |     |     |

| V+ Standby Current (Note 19)                                 |                 | PD bit = 1, exter               | nal clock stop | ped         |             | 1           | 10          | μA    |     |     |

|                                                              |                 |                                 | 1 00414117     | Buffers off |             | 175         | 210         |       |     |     |

|                                                              |                 | Normal mode,<br>MF1 = 0.        | 1.024MHz       | Buffers on  |             | 370         | 420         | 1     |     |     |

|                                                              |                 | MF0 = 0                         | 2.4576MHz      | Buffers off |             | 250         | 300         |       |     |     |

|                                                              |                 |                                 | 2.43/01/17/2   | Buffers on  |             | 610         | 700         | μA    |     |     |

|                                                              |                 |                                 | 1.024MHz       | Buffers off |             | 245         |             |       |     |     |

|                                                              |                 | 2X mode,<br>MF1 = 0.            | 1.024101⊓2     | Buffers on  |             | 610         |             |       |     |     |

|                                                              |                 | MF0 = 1                         | 2.4576MHz      | Buffers off |             | 0.42        | 0.55        |       |     |     |

| V. Current                                                   | l.              |                                 | 2.45/0IVIHZ    | Buffers on  |             | 1.2         | 1.5         |       |     |     |

| V+ Current                                                   |                 | 4X mode,<br>MF1 = 1,<br>MF0 = 0 | 1 00 41 41 1-  | Buffers off |             | 0.42        |             |       |     |     |

|                                                              |                 |                                 | 1.024MHz       | Buffers on  |             | 1.2         |             |       |     |     |

|                                                              |                 |                                 |                |             | 0.457/1411  | Buffers off |             | 1.8   | 2.2 |     |

|                                                              |                 |                                 |                | Buffers on  |             | 4.8         | 6           | mA    |     |     |

|                                                              |                 | 8X mode,<br>MF1 = 1,<br>MF0 = 1 | MF1 = 1,       | 1.0041411-  | Buffers off |             | 1.8         |       | 1   |     |

|                                                              |                 |                                 |                | MF1 = 1,    | 1.024MHz    | Buffers on  |             | 4.8   |     |     |

|                                                              |                 |                                 |                |             |             | 0.457/\\    | Buffers off |       | 1.8 | 2.2 |

|                                                              |                 |                                 |                | 2.4576MHz   | Buffers on  |             | 4.8         | 6     |     |     |

| DIGITAL POWER-SUPPLY CUI<br>ransducer excitation currents di |                 |                                 |                |             |             |             |             | İ     |     |     |

| V <sub>DD</sub> Standby Current (Note 19)                    |                 | PD bit = 1, exter               | nal clock stop | ped         |             | 1           | 10          | μΑ    |     |     |

|                                                              |                 | Normal mode,                    | 1.024          |             |             | 70          | 200         | μΑ    |     |     |

|                                                              |                 | MF1 = 0, MF0 =                  | 0 2.457        | 6MHz        |             | 150         | 300         | μ, ,  |     |     |

| Digital Supply Current                                       |                 | 2X mode,                        | 1.024          | MHz         |             | 0.08        |             |       |     |     |

|                                                              | I <sub>DD</sub> | MF1 = 0, MF0 =                  | 1 2.457        | 6MHz        |             | 0.17        | 0.35        |       |     |     |

| Digital Jupply Current                                       | טטי             | 4X mode,                        | 1.024          | MHz         |             | 0.11        |             | mA    |     |     |

|                                                              |                 | MF1 = 1, MF0 =                  | 0 2.457        | 6MHz        |             | 0.22        | 0.40        | '''^  |     |     |

|                                                              |                 | 8X mode,                        | 1.024          | MHz         |             | 0.15        |             |       |     |     |

|                                                              |                 | MF1 = 1, MF0 =                  | 1 2.457        | 6MHz        |             | 0.32        | 0.50        | ]     |     |     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+2.7V \text{ to } +3.6V, V_{DD}=+2.7V \text{ to } +3.6V, V_{REFIN+}=+1.25V, REFIN-=AGND, f_{CLKIN}=2.4576MHz, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A=+25^{\circ}C.)$

| PARAMETER                                                      | SYMBOL           |                                 | CONDITIONS    |                   | MIN         | TYP         | MAX         | UNITS    |     |          |            |  |      |  |   |

|----------------------------------------------------------------|------------------|---------------------------------|---------------|-------------------|-------------|-------------|-------------|----------|-----|----------|------------|--|------|--|---|

| <b>POWER DISSIPATION</b> (V+ = V) disabled, X2CLK = 0, CLK = 0 |                  | •                               |               | al CLKIN, burn-ou | ut and tran | sducer e    | xcitation o | currents |     |          |            |  |      |  |   |

|                                                                |                  |                                 | 1.024MHz      | Buffers off       |             | 0.81        | 1.36        |          |     |          |            |  |      |  |   |

|                                                                |                  | Normal mode,<br>MF1 = 0,        | 1.024101112   | Buffers on        |             | 1.45        | 2.05        |          |     |          |            |  |      |  |   |

|                                                                |                  | MF0 = 0                         | 2.4576MHz     | Buffers off       |             | 1.32        | 1.98        |          |     |          |            |  |      |  |   |

|                                                                |                  |                                 | 2.43/01/17/2  | Buffers on        |             | 2.51        | 3.30        |          |     |          |            |  |      |  |   |

|                                                                | 2V mode 1.024MHz | 1.08                            |               |                   |             |             |             |          |     |          |            |  |      |  |   |

|                                                                |                  | 2.28                            |               |                   |             |             |             |          |     |          |            |  |      |  |   |

|                                                                |                  | MFO = 1                         | 2.4576MHz     | Buffers off       |             | 1.95        | 2.97        | mW       |     |          |            |  |      |  |   |

| Dawar Dissipation                                              | PD               |                                 |               | Buffers on        |             | 4.53        | 6.11        |          |     |          |            |  |      |  |   |

| Power Dissipation                                              | PD               | 4X mode,<br>MF1 = 1,<br>MF0 = 0 | 1.024MHz      | Buffers off       |             | 1.75        |             |          |     |          |            |  |      |  |   |

|                                                                |                  |                                 |               | Buffers on        |             | 4.32        |             |          |     |          |            |  |      |  |   |

|                                                                |                  |                                 | 2.457/1415    | Buffers off       |             | 6.67        | 8.58        |          |     |          |            |  |      |  |   |

|                                                                |                  |                                 | 2.4576MHz     | Buffers on        |             | 16.6        | 21.2        |          |     |          |            |  |      |  |   |

|                                                                |                  |                                 | 1 00 41 41 1- | Buffers off       |             | 6.44        |             |          |     |          |            |  |      |  |   |

|                                                                |                  | 8X mode,                        | MF1 = 1,      | MF1 = 1,          | MF1 = 1,    |             | ,           | · ·      | · · | 1.024MHz | Buffers on |  | 16.4 |  | 1 |

|                                                                |                  | MFO = 1                         |               |                   |             | 2 457/1411- | Buffers off |          | 7.0 | 8.91     |            |  |      |  |   |

|                                                                |                  | MFU = 1  2.4576MHz              |               | Buffers on        |             | 16.9        | 21.45       |          |     |          |            |  |      |  |   |

| Standby Power Dissipation                                      |                  | (Note 19)                       | 1             |                   |             | 7           | 70          | μW       |     |          |            |  |      |  |   |

- Note 1: Contact factory for INL limits applicable with FS1 = 0 and MF1, MF0 = 1, 2, or 3.

- **Note 2:** Nominal gain is 0.98. This ensures a full-scale input voltage may be applied to the part under all conditions without causing saturation of the digital output data.

- **Note 3:** Positive Full-Scale Error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar and bipolar input ranges. This error does not include the nominal gain of 0.98.

- Note 4: Full-Scale Drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and applies to both unipolar and bipolar input ranges.

- **Note 5:** Gain Error does not include zero-scale errors. It is calculated as (full-scale error unipolar offset error) for unipolar ranges and as (full-scale error bipolar zero error) for bipolar ranges. This error does not include the nominal gain of 0.98.

- **Note 6:** Gain-Error Drift does not include unipolar offset drift or bipolar zero drift. It is effectively the drift of the part if zero-scale error is removed.

- Note 7: Use of the offset DAC does not imply that any input may be taken below AGND.

- **Note 8:** Additional noise added by the offset DAC is dependent on the filter cutoff, gain, and DAC setting. No noise is added for a DAC code of 0000.

- **Note 9:** Guaranteed by design or characterization; not production tested.

- Note 10: The absolute input voltage must be within the input voltage range specification.

- Note 11: All AlN and REFIN pins have identical input structures. Leakage is production tested only for the AlN3, AlN4, AlN5, CALGAIN, and CALOFF inputs.

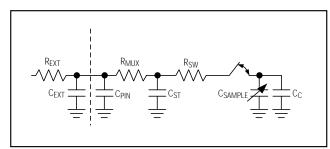

- **Note 12:** The dynamic load presented by the MAX1403 analog inputs for each gain setting is discussed in detail in the *Switching Network* section. Values are provided for the maximum allowable external series resistance.

- **Note 13:** The input voltage range for the analog inputs is with respect to the voltage on the negative input of its respective differential or pseudo-differential pair. Table 5 shows which inputs form differential pairs.

- Note 14: VRFF = VRFFIN+ VRFFIN-.

- **Note 15:** These specifications apply to CLKOUT only when driving a single CMOS load.

- **Note 16:** The burn-out currents require a 500mV overhead between the analog input voltage and both V+ and AGND to operate correctly.

- Note 17: Measured at DC in the selected passband. PSR at 50Hz will exceed 120dB with filter notches of 25Hz or 50Hz and FAST bit = 0. PSR at 60Hz will exceed 120dB with filter notches of 20Hz or 60Hz and FAST bit = 0.

- **Note 18:** PSR depends on gain. For a gain of +1V/V, PSR is 70dB typical. For a gain of +2V/V, PSR is 75dB typical. For a gain of +4V/V, PSR is 80dB typical. For gains of +8V/V to +128V/V, PSR is 85dB typical.

- **Note 19:** Standby power-dissipation and current specifications are valid only with CLKIN driven by an external clock and with the external clock stopped. If the clock continues to run in standby mode, the power dissipation will be considerably higher. When used with a resonator or crystal between CLKIN and CLKOUT, the actual power dissipation and I<sub>DD</sub> in standby mode will depend on the resonator or crystal type.

### **TIMING CHARACTERISTICS**

$(V+=+2.7V \text{ to } +3.6V, V_{DD}=+2.7V \text{ to } +3.6V, AGND=DGND, f_{CLKIN}=2.4576MHz, input logic 0=0V, logic 1=V_{DD}, T_A=T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted.) (Notes 20, 21, 22)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                                 |           | MIN          | TYP | MAX | UNITS  |

|---------------------------------------------------------|-----------------|----------------------------------------------------------------------------|-----------|--------------|-----|-----|--------|

| Master Clock Frequency                                  | fCLKIN          | Crystal oscillator or clock exter-<br>nally supplied for specified perfor- | X2CLK = 0 | 0.4          |     | 2.5 | MHz    |

| Master Clock Frequency                                  | ICLKIN          | mance (Notes 23, 24)                                                       | X2CLK = 1 | 0.8          |     | 5.0 | IVIIIZ |

| Master Clock Input Low Time                             | fCLKIN LO       | t <sub>CLKIN</sub> = 1 / f <sub>CLKIN</sub> , X2CLK = 0                    |           | 0.4 • tclkin |     |     | ns     |

|                                                         |                 |                                                                            |           | 0.4 •        |     |     |        |

| Master Clock Input High Time                            | fCLKIN HI       | $t_{CLKIN} = 1 / f_{CLKIN}, X2CLK = 0$                                     |           | tCLKIN       |     |     | ns     |

|                                                         |                 | X2CLK = 0, N = 2 <sup>(2 • MF1 + MF0)</sup>                                |           | 280 / N      |     |     |        |

| INT High Time                                           | tīnt            | ·                                                                          |           | • tCLKIN     |     |     | ns     |

| 3                                                       |                 | $X2CLK = 1, N = 2(2 \cdot MF1 + MF0)$                                      |           | 560 / N      |     |     | -      |

|                                                         |                 | ,                                                                          |           | • tCLKIN     |     |     |        |

| RESET Pulse Width Low                                   | t <sub>2</sub>  |                                                                            |           | 100          |     |     | ns     |

| SERIAL-INTERFACE READ OPE                               | RATION          |                                                                            |           |              |     |     |        |

| INT to CS Setup Time (Note 9)                           | t <sub>3</sub>  |                                                                            |           | 0            |     |     | ns     |

| SCLK Setup to Falling Edge CS                           | t <sub>4</sub>  |                                                                            |           | 30           |     |     | ns     |

| CS Falling Edge to SCLK Falling Edge Setup Time         | t <sub>5</sub>  |                                                                            |           | 30           |     |     | ns     |

| SCLK Falling Edge to Data Valid<br>Delay (Notes 25, 26) | t <sub>6</sub>  |                                                                            |           | 0            |     | 100 | ns     |

| SCLK High Pulse Width                                   | t <sub>7</sub>  |                                                                            |           | 100          |     |     | ns     |

| SCLK Low Pulse Width                                    | t <sub>8</sub>  |                                                                            |           | 100          |     |     | ns     |

| CS Rising Edge to SCLK Rising Edge Hold Time (Note 22)  | t9              |                                                                            |           | 0            |     |     | ns     |

| Bus Relinquish Time After SCLK<br>Rising Edge (Note 27) | t <sub>10</sub> |                                                                            |           | 10           |     | 100 | ns     |

| SCLK Rising Edge to INT High (Note 28)                  | t <sub>11</sub> |                                                                            |           |              |     | 200 | ns     |

| SERIAL-INTERFACE WRITE OF                               | ERATION         |                                                                            |           | I            |     |     | ı      |

| SCLK Setup to Falling Edge CS                           | t <sub>12</sub> |                                                                            |           | 30           |     |     | ns     |

|                                                         |                 |                                                                            |           |              |     |     |        |

### **TIMING CHARACTERISTICS (continued)**

$(V+=+2.7V \text{ to } +3.6V, V_{DD}=+2.7V \text{ to } +3.6V, AGND=DGND, f_{CLKIN}=2.4576MHz, input logic 0=0V, logic 1=V_{DD}, T_{A}=T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted.) (Notes 20, 21, 22)

| PARAMETER                                                 | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------|-----------------|------------|-----|-----|-----|-------|

| CS Falling Edge to SCLK Falling Edge Setup Time           | t <sub>13</sub> |            | 30  |     |     | ns    |

| Data Valid to SCLK Rising Edge<br>Setup Time              | t <sub>14</sub> |            | 30  |     |     | ns    |

| Data Valid to SCLK Rising Edge<br>Hold Time               | t <sub>15</sub> |            | 0   |     |     | ns    |

| SCLK High Pulse Width                                     | t <sub>16</sub> |            | 100 |     |     | ns    |

| SCLK Low Pulse Width                                      | t <sub>17</sub> |            | 100 |     |     | ns    |

| CS Rising Edge to SCLK Rising Edge Hold Time              | t <sub>18</sub> |            | 0   |     |     | ns    |

| AUXILIARY DIGITAL INPUTS (D                               | S0 and DS       | 1)         |     |     |     |       |

| DS0/DS1 to SCLK Falling Edge<br>Setup Time (Notes 21, 29) | t <sub>19</sub> |            | 40  |     |     | ns    |

| DS0/DS1 to SCLK Falling Edge<br>Hold Time (Notes 21, 29)  | t <sub>20</sub> |            | 0   |     |     | ns    |

- **Note 20:** All input signals are specified with  $t_f = t_f = 5$ ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6V.

- Note 21: See Figure 4.

- Note 22: Timings shown in tables are for the case where SCLK idles high between accesses. The part may also be used with SCLK idling low between accesses, provided  $\overline{CS}$  is toggled. In this case SCLK in the timing diagrams should be inverted and the terms "SCLK Falling Edge" and "SCLK Rising Edge" exchanged in the specification tables. If  $\overline{CS}$  is permanently tied low, the part should only be operated with SCLK idling high between accesses.

- **Note 23:** CLKIN duty cycle range is 45% to 55%. CLKIN must be supplied whenever the MAX1403 is not in standby mode. If no clock is present, the device can draw higher current than specified.

- Note 24: The MAX1403 is production tested with fCLKIN at 2.5MHz (1MHz for some IDD tests).

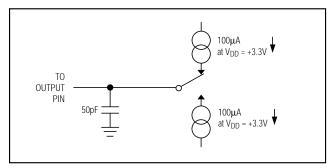

- Note 25: Measured with the load circuit of Figure 1 and defined as the time required for the output to cross the V<sub>OL</sub> or V<sub>OH</sub> limits.

- Note 26: For read operations, SCLK active edge is falling edge of SCLK.

- **Note 27:** Derived from the time taken by the data output to change 0.5V when loaded with the circuit of Figure 1. The number is then extrapolated back to remove effects of charging or discharging the 50pF capacitor. This ensures that the times quoted in the timing characteristics are true bus-relinquish times and are independent of external bus loading capacitances.

- Note 28:  $\overline{\text{INT}}$  returns high after the first read after an output update. The same data can be read again while  $\overline{\text{INT}}$  is high, but be careful not to allow subsequent reads to occur close to the next output update.

- Note 29: Auxiliary inputs DS0 and DS1 are latched on the first falling edge of SCLK during a data-read cycle.

図1. バス放棄時間及びV<sub>OL</sub>とV<sub>OH</sub>レベルのための負荷 回路

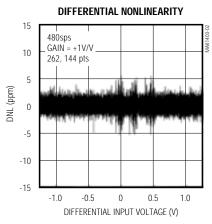

#### 標準動作特性

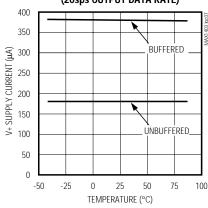

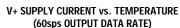

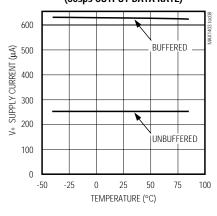

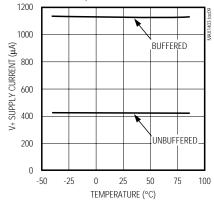

(V+ = +3V, V<sub>DD</sub> = +3V, V<sub>REFIN+</sub> = +1.25V, REFIN- = AGND, f<sub>CLKIN</sub> = 2.4576MHz, transducer excitation currents disabled, T<sub>A</sub> = +25°C, unless otherwise noted.)

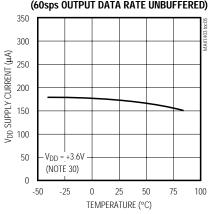

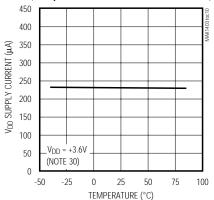

(20sps output data rate unbuffered)

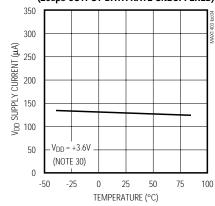

**VDD SUPPLY CURRENT vs. TEMPERATURE** (60sps OUTPUT DATA RATE UNBUFFERED)

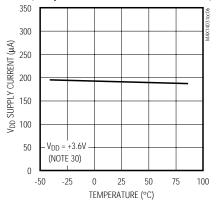

**VDD SUPPLY CURRENT vs. TEMPERATURE** (120sps OUTPUT DATA RATE UNBUFFERED)

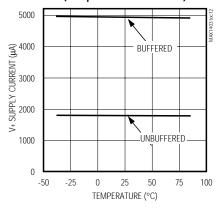

V+ SUPPLY CURRENT vs. TEMPERATURE (20sps OUTPUT DATA RATE)

#### V+ SUPPLY CURRENT vs. TEMPERATURE (120sps OUTPUT DATA RATE)

### 標準動作特性(続き)

$(V_+ = +3V, V_{DD} = +3V, V_{REFIN_+} = +1.25V, REFIN_- = AGND, f_{CLKIN} = 2.4576MHz, transducer excitation currents disabled, T_A = +25°C, unless otherwise noted.)$

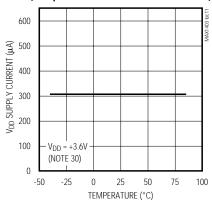

### V<sub>DD</sub> SUPPLY CURRENT vs. TEMPERATURE (240sps Output data rate unbuffered)

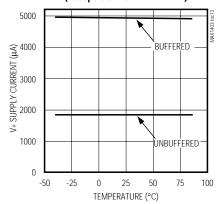

### V+ SUPPLY CURRENT vs. TEMPERATURE (240sps OUTPUT DATA RATE)

### V<sub>DD</sub> SUPPLY CURRENT vs. TEMPERATURE (480sps Output Data rate unbuffered)

### V+ SUPPLY CURRENT vs. TEMPERATURE (480sps OUTPUT DATA RATE)

**Note 30:** Minimize capacitive loading at CLKOUT for lowest V<sub>DD</sub> supply current. *Typical Operating Characteristics* show V<sub>DD</sub> supply current with CLKOUT loaded by 120pF.

### 端子説明 \_\_\_\_\_

| 端子 | 名称       | 機能                                                                                                                                                                                                                                                                          |

|----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CLKIN    | クロック入力。CLKINとCLKOUTの間にクリスタルを接続できます。別方法として、公称周波数2.4576MHz<br>又は1.024MHzのCMOSコンパチブルクロックでCLKINを駆動し、CLKOUTは未接続にしておくこともできます。<br>X2CLK制御ビットが1に設定されている場合は、周波数として4.9152MHz及び2.048MHzを使用できます。                                                                                        |

| 2  | CLKOUT   | クロック出力。マスタークロックをクリスタルから得る場合は、CLKINとCLKOUTの間にクリスタルを<br>接続してください。このモードにおいては、内蔵クロック信号をCLKOUTで得ることはできません。<br>CLKINを外部クロックで駆動する場合は、CLKOUTを未接続のままにしてください。                                                                                                                         |

| 3  | CS       | チップセレクト入力。ディジタルインタフェースをイネーブルするために使用されるアクティブローロジック入力。 $\overline{	ext{CS}}$ がハード配線でローに接続されている場合、MAX1403は3線インタフェースモードで動作し、SCLK、DIN及びDOUTがインタフェースに使用されます。 $\overline{	ext{CS}}$ は、シリアルバスに2つ以上のデバイスが使用されているシステムにおいてデバイスを選択するために、あるいは連続SCLKが使用されている場合にMAX1403のフレーム同期信号として使用されます。 |

| 4  | RESET    | アクティブローリセット入力。これをローにすると、制御ロジック、インタフェースロジック、ディジタルフィルタ及びアナログ変調器がパワーオン状態にリセットされます。リセットが解除されるには、RESETがハイとなり、CLKINがトグルしている必要があります。                                                                                                                                               |

| 5  | DS1      | 補助データ入力ビット1のディジタル入力。このビットの状態は、出力データのビットD4に反映されます。これは、DS1の状態をシリアルインタフェースを通じて通信するために使用されます。                                                                                                                                                                                   |

| 6  | DS0      | 補助データ入力ビット0のディジタル入力。このビットの状態は、出力データのビットD3に反映されます。これは、DS0の状態をシリアルインタフェースを通じて通信するために使用されます。                                                                                                                                                                                   |

| 7  | OUT2     | トランスデューサ励起電流ソース2                                                                                                                                                                                                                                                            |

| 8  | OUT1     | トランスデューサ励起電流ソース1                                                                                                                                                                                                                                                            |

| 9  | AGND     | アナロググランド。アナログ回路の基準点。AGNDはICサブストレートに接続されています。                                                                                                                                                                                                                                |

| 10 | V+       | アナログ正電源電圧(+2.7 ~ +3.6V)                                                                                                                                                                                                                                                     |

| 11 | AIN1     | アナログ入力チャネル1。AIN6をコモン端子とする疑似差動入力、あるいはAIN1/AIN2差動アナログ入力<br>ペアの正入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                                      |

| 12 | AIN2     | アナログ入力チャネル2。AIN6をコモン端子とする疑似差動入力、あるいはAIN1/AIN2差動アナログ入力ペアの負入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                                          |

| 13 | AIN3     | アナログ入力チャネル3。AIN6をコモン端子とする疑似差動入力、あるいはAIN3/AIN4差動アナログ入力ペアの正入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                                          |

| 14 | AIN4     | アナログ入力チャネル4。AIN6をコモン端子とする疑似差動入力、あるいはAIN3/AIN4差動アナログ入力ペアの負入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                                          |

| 15 | AIN5     | アナログ入力チャネル5。AIN6と共に差動又は疑似差動入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                                                                        |

| 16 | AIN6     | アナログ入力チャネル6。疑似差動入力モードにおけるAIN1~AIN5のコモン端子、あるいはAIN5/AIN6<br>差動アナログ入力ペアの負入力として使用できます(「内蔵レジスタ」を参照)。                                                                                                                                                                             |

| 17 | CALGAIN- | 負利得キャリブレーション入力。システム利得キャリブレーションに使用されます。完全差動入力ペア (CALGAIN+との組み合わせ)の負入力です。通常、これらの入力はシステム内のリファレンス電圧に接続されています。システム利得キャリブレーションが不要で、自動シーケンスモードが使用されている場合、CALGAIN+/CALGAIN-入力ペアは付加的な完全差動入力チャネルとして使用できます。                                                                            |

| 18 | CALGAIN+ | 正利得キャリブレーション入力。システム利得キャリブレーションに使用されます。完全差動入力ペア (CALGAIN-との組み合わせ)の正入力です。通常、これらの入力はシステム内のリファレンス電圧に接続されています。システム利得キャリブレーションが不要で、自動シーケンスモードが使用されている場合、CALGAIN+/CALGAIN-入力ペアは付加的な完全差動入力チャネルとして使用できます。                                                                            |

### 端子説明(続き)\_\_\_\_\_

| 端子 | 名称              | 機能                                                                                                                                                                                                                                                               |

|----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | REFIN-          | 負差動リファレンス入力。REFIN-はV+とAGNDの間にバイアスしてください(REFIN+がREFIN-よりも高いことが条件です)。                                                                                                                                                                                              |

| 20 | REFIN+          | 正差動リファレンス入力。REFIN+はV+とAGNDの間にバイアスしてください(REFIN+がREFIN-よりも高いことが条件です)。                                                                                                                                                                                              |

| 21 | CALOFF-         | 負オフセットキャリブレーション入力。システムオフセットキャリブレーションに使用されます。完全差動入力ペア(CALOFF+との組み合わせ)の負入力です。通常、これらの入力はシステム内のゼロリファレンス電圧に接続されています。システムオフセットキャリブレーションが不要で、自動シーケンスモードが使用されている場合、CALOFF+/CALOFF-入力ペアは付加的な完全差動入力チャネルとして使用できます。                                                          |

| 22 | CALOFF+         | 正オフセットキャリブレーション入力。システムオフセットキャリブレーションに使用されます。完全差動入力ペア(CALOFF-との組み合わせ)の正入力です。通常、これらの入力はシステム内のゼロリファレンス電圧に接続されています。システムオフセットキャリブレーションが不要で、自動シーケンスモードが使用されている場合、CALOFF+/CALOFF-入力ペアは付加的な完全差動入力チャネルとして使用できます。                                                          |

| 23 | DGND            | ディジタルグランド。ディジタル回路の基準点。                                                                                                                                                                                                                                           |

| 24 | V <sub>DD</sub> | ディジタル電源電圧(+2.7V~+3.6V)。                                                                                                                                                                                                                                          |

| 25 | ĪNT             | 割込み出力。ロジックローの時は、データレジスタから新しい出力ワードを読み取れることを意味します。<br>出力ワード読取り動作が完了するとINTはハイに戻ります。INTは、データ読取りが行われなくても短時間<br>(長さはフィルタ及びクロック制御ビットで決定)だけハイに戻ります。ロジックハイの時は、内部でアク<br>ティビティがあることを意味するため、ハイの時は読取り動作を行わないようにしてください。また、INT<br>はDOUTに有効なデータが出ていることを示すストローブを提供します(MDOUT = 1)。 |

| 26 | DOUT            | シリアルデータ出力。DOUTは、通信レジスタ、グローバルセットアップレジスタ、伝達関数レジスタ又は<br>データレジスタからの情報を含む内部シフトレジスタからデータを出力します。DOUTは、 $\Sigma$ - $\Delta$ 変調器の<br>ディジタルビットストリームを直接供給することもできます(MDOUT = 1)。                                                                                              |

| 27 | DIN             | シリアルデータ入力。DINのデータは入力シフトレジスタに書き込まれ、後で通信レジスタ、グローバルセットアップレジスタ、特殊関数レジスタ又は伝達関数レジスタに転送されます(どのレジスタかは通信レジスタのレジスタ選択ビットに依存します)。                                                                                                                                            |

| 28 | SCLK            | シリアルクロック入力。MAX1403とのデータ転送を行うには、ここに外部シリアルクロックを印加してください。このシリアルクロックは、連続的(データはパルストレインとして送信)でも間欠的でもかまいません。CSを使用してデータ転送のフレーミングを行う場合は、変換の合間のSCLKはハイ、ローいずれも可能で、CSが希望のアクティブクロックエッジを決定します(「クロック極性の選択」を参照)。CSが恒久的にローに接続されている場合は、データ転送の合間でSCLKをハイにアイドリングする必要があります。           |

詳細 \_\_\_\_\_\_

#### 回路の説明

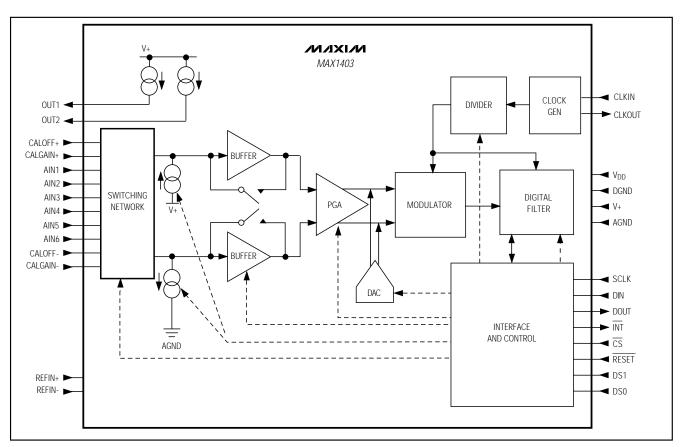

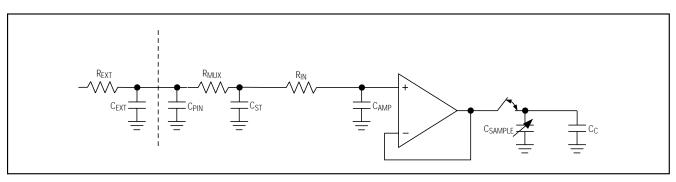

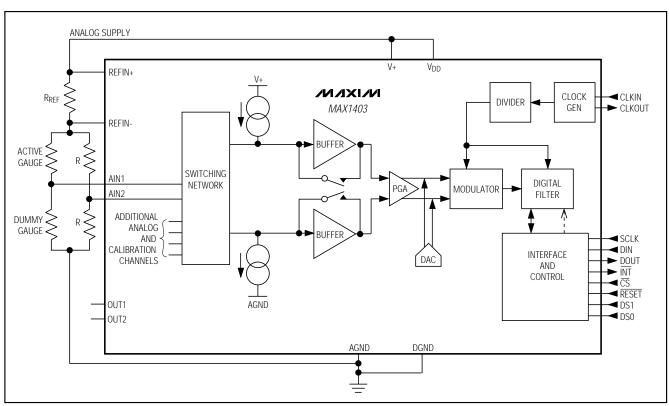

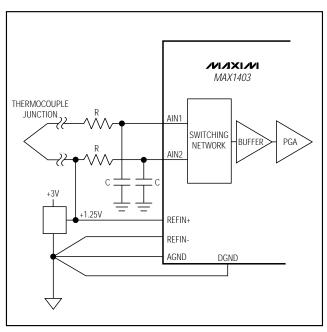

MAX1403は、重量計や圧力トランスデューサ等のダイナミックレンジの広いアプリケーション用に設計された低電力マルチチャネル、シリアル出力シグマ-デルタADCです。図2のファンクションダイアグラムは、スイッチングネットワーク、変調器、PGA、2つのバッファ、発振器、内蔵ディジタルフィルタ、2つのマッチングされた励起電流ソース及び双方向性シリアル通信ポートを含んでいます。

3つの完全差動入力チャネルがスイッチングネットワークに接続されています。各チャネルは、利得を+1V/V~+128V/Vの範囲で個別に設定できるようになっています。これら3つの差動チャネルは、5つの疑似差動入力チャネルとして動作するように設定することもできます。2つの付加的な完全差動システムキャリブレーションチャネルにより、システム利得誤差及びオフセット誤差を測定できるようになっています。専用の利得及びオフセット誤差補正チャネルを必要としない場合、これらのシステムキャリブレーションチャネルは付加的な差動信号チャネルとして使用できます。

選択された入力をPGAと変調器の容量性負荷から分離するために、2つのチョッパ安定化バッファが提供されています。3つの独立したDACが、各差動入力チャネルの入力信号のDC成分を補償します。

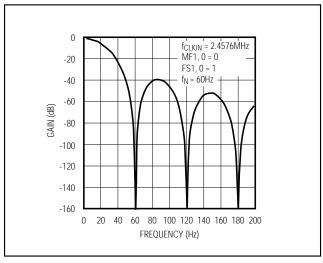

シグマ-デルタ変調器は、入力信号をディジタルパルストレインに変換します(平均デューティサイクルが数値化信号情報を表現します)。次に、このパルストレインがディジタルデシメーションフィルタによって処理され、16ビット以上の変換精度を実現します。ディジタルフィルタのデシメーション係数をユーザが選択できます。ため、変換結果の分解能を低減して出力データ速度を高くすることができます。2.4576MHz又は1.024MHzのマスタークロックと共に使用した場合、ライン周波数スタークロックと共に使用した場合、ライン周波数フィルタの周波数応答をゼロに設定することができます。これにより、ポストフィルタリングなしで優れたラインクにより、ポストフィルタリングなしで優れたラインにより、ポストフィルタリングなして優れたライングは大いできます。さらに、変調器のサンプリングは大いで表出を保証できます。さらに、変調器のサンプリングラット速度を最大にするように最適化できます。

MAX1403は、全ての信号チャネルを順番にスキャンし、シリアルインタフェースを通じて結果を出力するように設定することもできます。このようにすると、

図2. ファンクションダイアグラム

通信オーバヘッドが最小限で済みます。出力ワードは、 各変換結果のソースを示す結果識別タグを含んで います。

#### シリアルディジタルインタフェース

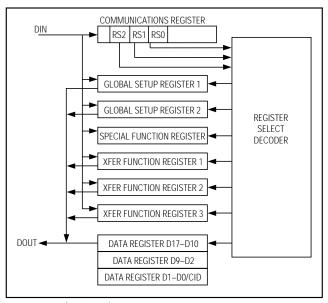

シリアルディジタルインタフェースを通じて、8つの内蔵レジスタにアクセスできます(図3)。全てのシリアルインタフェースコマンドは、通信レジスタ(COMM)への書込みで始まります。パワーアップ、システムリセット又はインタフェースリセット時に、本デバイスは通信レジスタへの書込みを予期します。COMMレジスタへのアクセスは0スタートビットで始まります。COMMレジスタのR/Wビットは読取り又は書込み動作を選択し、レジスタ選択ビット(RS2、RS1、RS0)がアドレス指定されるべきレジスタを選択します。COMM又は他のレジスタに書き込んでいない時は、DINをハイに保持してください(表1)。

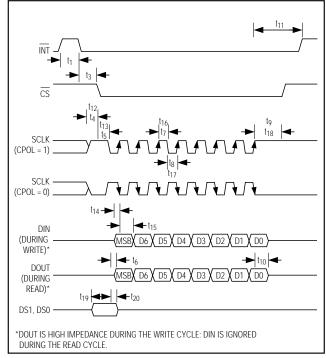

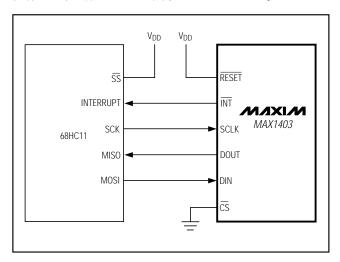

シリアルインタフェースはCS、SCLK、DIN、DOUT及びINTの5つの信号からなっています。SCLKのクロックパルスがビットをDINにシフトインし、DOUTからシフトアウトします。INTはデータの準備ができたことを知らせます。CSはデバイスのチップセレクト入力であると同時に、クロック極性選択入力です(図4)。

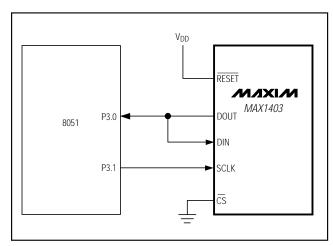

でSを使用すると、いくつかのSPIコンパチブルデバイス間でSCLK、DIN及びDOUT信号を共有できます。I/Oピンが足りない場合は、でSをローに接続し、SCLK、DIN及びDOUTを使って、シリアルディジタルインタフェースをCPOL=1、CPHA=1モードで動作させてください。この3線インタフェースモードは光絶縁アプリケーションに最適です。さらに、MAX1403は読取りサイクル中にのみDOUTを駆動するため、マイクロコントローラ(PIC16C54又は80C51等)は単一の双方向性I/Oピンを使用することによって、DINへの送信とDOUTからの受信の両方(「アプリケーション情報」を参照)を行うことができます。

表1. 制御レジスタのアドレス指定

| RS2 | RS1 | RS0 | TARGET REGISTER              |  |

|-----|-----|-----|------------------------------|--|

| 0   | 0   | 0   | Communications Register      |  |

| 0   | 0   | 1   | Global Setup Register 1      |  |

| 0   | 1   | 0   | Global Setup Register 2      |  |

| 0   | 1   | 1   | Special Function Register    |  |

| 1   | 0   | 0   | Transfer Function Register 1 |  |

| 1   | 0   | 1   | Transfer Function Register 2 |  |

| 1   | 1   | 0   | Transfer Function Register 3 |  |

| 1   | 1   | 1   | Data Register                |  |

さらに、INT信号をハードウェア割込みに接続すると、 高速スループットが可能になると共に、信頼性が高く、 衝突のないデータフローが可能になります。

MAX1403は、生の変調器データ出力にアクセスできる モードを備えています。このモードにおいては、DOUT とINTの機能が変更されます(「変調器データ出力」を参照)。

図3. レジスタの概要

図4. シリアルインタフェースのタイミング

#### クロック極性の選択

シリアルインタフェースは、クロックがハイ又はローにアイドリングしている状態で動作できます。これは、モトローラ社のSPIインタフェースをCPOL=1、CPHA=1又はCPOL=0及びCPHA=1モードで動作させた場合とコンパチブルです。クロック極性は、 $\overline{CS}$ の立下がリエッジにおけるSCLKの状態をサンプリングすることにより求めてください。セットアップ時間 $t_4/t_{12}$ 及び $t_5/t_{13}$ に違反しないように気をつけてください。 $\overline{CS}$ に対方ンドに接続されていると、 $\overline{CS}$ に立下がリエッジがないため、SCLKをハイでアイドリングする必要があります(CPOL=1、CPHA=1)。

データレディ信号(DRDYビットが真、又はINT = ロー) データレディ信号は、24ビットデータレジスタから 新しいデータを読取ることができることを知らせます。 データレジスタの読取りに成功すると、データレディ 信号は偽になります。データが読まれる前に新しい測定 が完了すると、データレディ信号は偽になります。 データレジスタに新しいデータが用意されると、データ レディ信号は再び真になります。

MAX1403は、データレディ信号を監視する方法を2つ 提供しています。INTはハードウェア解決法(データが アクセス可能になったときにアクティブロー)を提供し、 COMMレジスタのDRDYビットはソフトウェア解決法 (アクティブハイ)を提供します。

データレディが真になったら、できるだけ早くデータを 読取ってください。これは、測定速度が速いほど重要 になります。データ読取りが大幅に遅れると、衝突が 起こることがあります。データレジスタの読取り動作中 に新しい測定が完了すると、衝突が起こります。衝突が 起こると、データレジスタ内の情報は無効になります。 データは無効になりますが、それでもこの無効な読取り 動作を完了する必要があります。

#### インタフェースのリセット

32個の1を同期入力するとシリアルインタフェースが リセットされます。インタフェースをリセットしても 内部レジスタは影響されません。

連続データ出力モードを使用している場合は、8個の0を入力してから32個の1を入力してください。先頭の0が全ての動作のスタートビットとして使用されるため、32個を超える1を同期入力してもかまいません。

#### 連続データ出力モード

入力チャネルをスキャンしている場合(SCAN=1)、 シリアルインタフェースによって、COMMレジスタ への書込みを必要とせずにデータレジスタを繰り返し 読取ることができます。最初のCOMM書込み (01111000)の後に24ビットのデータレジスタを読取るための24クロック(DIN=ハイ)が続きます。データレジスタが読み取られた後、次の変換の後でもう一度 24クロック(DIN=ハイ)を書き込むことにより、再び読取りが可能になります。COMMレジスタに任意の有効なアクセスを書き込むことにより、連続データ出力モードを終了させることができます。

#### 変調器データ出力(MDOUT = 1)

MDOUT = 1の場合、カスタムフィルタリング用にシングルビットの生の変調器データをDOUTから得ることができます。INTはデータ同期用の変調器クロックを提供します。データはINTの立下がリエッジで有効になります。それでも書込み動作は実行できますが、読取り動作はディセーブルされます。MDOUTが0に戻った後は、通常のシリアルインタフェース読取り動作で有効データにアクセスできます。

#### 内蔵レジスタ

#### 通信レジスタ

O/DRDY:(デフォルト=0)データレディビット。書込みのときは、このビットを0にリセットして通信レジスタデータワードの開始を知らせる必要があります。読取りのときは、ここ(0/DRDY)に1があると、データレジスタに有効なデータが用意されていることを意味します。このビットはデータレジスタが読取られた後にリセットされます。データが読み取られなかった場合、0/DRDYは次の測定の最後でローになります。

RS2、RS1、RS0: (デフォルト = 0、0、0) レジスタ 選択ビット。これらのビットで、アクセスされるレジ スタを選択します(表1)。

$R/\overline{W}$ : (デフォルト = 0)読取り/書込みビット。ハイに設定されると、選択されたレジスタが読取られます。  $R/\overline{W}$  = 0の場合は、選択されたレジスタに書き込まれます。

RESET: (デフォルト = 0)ソフトウェアリセットビット。このビットをハイに設定すると、デバイスはデフォルトのパワーアップ状態にリセットされます(RESET = 0)。

STDBY: (デフォルト = 0)スタンバイパワーダウン ビット。STDBYビットをセットすると、デバイスは スタンバイ状態になり、シリアルインタフェース及び CLK発振器以外の全てがシャットダウンします。

FSYNC: (デフォルト=0)フィルタ同期ビット。 FSYNC=0の時、変換はCLK、FS1、FS0、MF1及び

#### 通信レジスタ

最初のビット(MSB)

(LSB)

| FUNCTION | DATA<br>RDY | REGISTER SELECT BITS |     |     |     |       |       |       |

|----------|-------------|----------------------|-----|-----|-----|-------|-------|-------|

| Name     | 0/DRDY      | RS2                  | RS1 | RS0 | R/W | RESET | STDBY | FSYNC |

| Defaults | 0           | 0                    | 0   | 0   | 0   | 0     | 0     | 0     |

MF0ビットによって決まるデータレートで自動的に 実行されます。FSYNC=1の場合は、ディジタルフィルタ及びアナログ変調器がリセット状態に保持され、 通常の自己タイミング動作が禁止されます。この ビットは、オンコマンドで変換して有効な出力データ へのセトリング時間を最小限に抑えるため、あるいは いくつかのMAX1403の動作を同期させるために使用 できます。FSYNCは、シリアルインタフェースや 0/DRDYフラグをリセットしません。FSYNCがアク ティブの時に0/DRDYをクリアするには、データレジ スタの読取りを実行してください。

#### グローバルセットアップレジスタ1

A1、A0: (デフォルト = 0、0)チャネル選択制御ビット。 表8、9及び10に従って、これらのビット(及びDIFF、M1 及びM0ビットの状態)が変換のために選択されるチャネルを決定します。 SCANビットがセットされていると、これらのビットは無視されます。

MF1、MF0: (デフォルト = 0、0) 変調器周波数ビット。 MF1及びMF0はCLKIN発振器周波数の変調器動作周波数 に対する比を決定します。これらは出力データレート、ディジタルフィルタノッチ周波数の位置及びデバイス の電力消費に影響を与えます。 MF1 = 0及びMF0 = 0の場合は、電力消費が最小になります。これらのビットが1、1に設定されると、電力消費が最大になり、出力データレートが最高速になります(表 2)。

CLK: (デフォルト = 1)CLKビット。CLKビットは X2CLKとの組み合わせで、MAX1403にCLKIN入力 信号の周波数を知らせます。CLK = 0の場合、CLKIN 入力周波数として1.024MHz(X2CLK = 1の場合は 2.048MHz)が予期されます。CLK = 1の場合、CLKIN 入力周波数として2.4576MHz(X2CLK = 1の場合は 4.9152MHz)が予期されます。このビットはディジタルフィルタのデシメーション係数に影響し、最終的に 出力データレートに影響します(表2)。

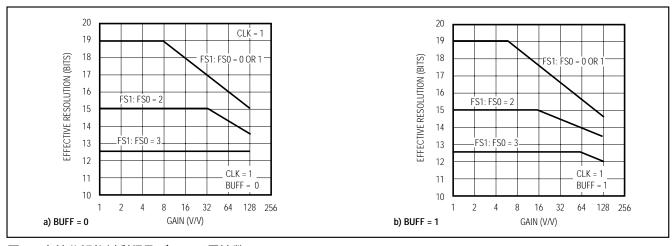

FS1、FS0:(デフォルト=0、1)フィルタ選択ビット。 これらのビット(及びCLKビット)がディジタルフィルタ のデシメーション比を制御します。出力データレート、 ディジタルフィルタ周波数応答ノッチの位置及び出力 結果に存在するノイズがこれらのビットによって決ま ります(表2)。

FAST: (デフォルト0)高速ビット。FAST = 0の場合、 ディジタルフィルタは変調器のデータストリームに 対してSINC<sup>3</sup>フィルタ機能を果たします。出力データ レートは、CLK、FS1、FS0、MF1及びMF0ビットの 値によって決まります(表2)。SINC3機能のセトリング 時間は $3\cdot[1/(出力データレート)]$ です。SINC $^3$ モード においては、MAX1403は(有為な設定変更の後)セト リングしたデータが準備できるまで、自動的にDRDY 信号を偽に保持します。FAST=1の場合、ディジタル フィルタは変調器のデータストリームに対してSINC1 フィルタ機能を果たします。このフィルタ機能によって 達成される信号雑音比はSINC3の場合よりも小さくなり ますが、SINC3はセトリングに少なくとも3出力サンプル 周期を要するのに対して、SINC<sup>1</sup>は単一の出力サンプル 周期内にセトリングします。SINC<sup>1</sup>モードからSINC<sup>3</sup> モードに切り換えると、フィルタが完全にセトリング した後でDRDYフラグの発生が止まり、再び発生します。 このモード変更には少なくとも3サンプルを要します。

#### グローバルセットアップレジスタ2

SCAN: (デフォルト0)スキャンビット。このビットを1に設定すると、DIFF、M1及びM0の設定に従って入力チャネルの順次スキャンが行われます(「スキャン(スキャンモード)」を参照)。SCAN=0の時、MAX1403はA1、A0、DIFF、M1及びM0で選択された特定のチャネルを繰り返し測定します(表4)。

M1、M0: (デフォルト = 0、0)モード制御ビット。これらのビットは、キャリブレーションチャネル CALOFF及びCALGAINへのアクセスを制御します。 SCAN = 0の時、M1 = 0及びM0 = 1に設定すると CALOFF入力が選択され、M1 = 1及びM0 = 0に設定すると CALGAIN入力が選択されます(表3)。 SCAN = 1で M1 M0の場合、スキャンシーケンスにはCALOFFと CALGAIN入力の両方が含まれます(表4)。 SCANが 1に設定され、デバイスが使用可能な入力チャネルを

#### グローバルセットアップレジスタ1

### 最初のビット(MSB)

(LSB)

| FUNCTION | CHANNEL | SELECTION | MODU<br>FREQU | LATOR<br>JENCY |     | FILTER SI | ELECTION |      |

|----------|---------|-----------|---------------|----------------|-----|-----------|----------|------|

| Name     | A1      | A0        | MF1           | MF0            | CLK | FS1       | FS0      | FAST |

| Defaults | 0       | 0         | 0             | 0              | 1   | 0         | 1        | 0    |

#### グローバルセットアップレジスタ2

#### 最初のビット(MSB)

(LSB)

| FUNCTION |      | MODE C | ONTROL |      |      |      |      |       |

|----------|------|--------|--------|------|------|------|------|-------|

| Name     | SCAN | M1     | MO     | BUFF | DIFF | BOUT | IOUT | X2CLK |

| Defaults | 0    | 0      | 0      | 0    | 0    | 0    | 0    | 0     |

スキャンしているときにどちらかのキャリブレーション モード(01又は10)が選択されると、スキャンシーケンス が拡張されてCALGAIN+/CALGAIN-入力ペア及び CALOFF+/CALOFF-入力ペアの両方の変換を含むよう になります。正確なシーケンスは、DIFFビットの状態 に依存します(表4)。スキャン中、キャリブレーション チャネルは伝達関数レジスタ3の内容によって定義され るPGA利得、フォーマット及びDAC設定を使用します。

BUFF: (デフォルト = 0)BUFFビットは、入力バッファアンプの動作を制御します。このビットが0の場合、入力バッファはバイパスされ、パワーダウンします。このビットがハイに設定されると、バッファが入力サンプリングコンデンサを駆動して、動的入力負荷を最小限に抑えます。

DIFF: (デフォルト = 0)差動/疑似差動ビット。DIFF = 0 の時、デバイスは疑似差動モードになり、AIN1 ~ AIN5 はアナログコモン端子AIN6を基準として測定されます。DIFF = 1の時、デバイスは差動モードになり、アナログ入力はAIN1/AIN2、AIN3/AIN4及びAIN5/AIN6として定義されます。各モードで使用可能な入力チャネルは、表5に記載されています。DIFFは、デバイスがスキャンモードになっている時のスキャンシーケンスにも影響することに注意してください(表4)。

BOUT:(デフォルト=0)バーンアウト電流ビット。BOUT=1に設定すると、選択されたアナログ入力チャネルに100nAの電流ソースが接続されます。このモードは、トランスジューサが焼き切れたり、開回路になっていないかどうかをチェックするために使用されます。最高の直線性を保証するために、測定の前にバーンアウト電流ソースをターンオフ(BOUT=0)する必要があります。

IOUT: (デフォルト = 0)IOUTビットは、トランスデューサ励起電流を制御します。このビットが0に設定されていると、OUT1及びOUT2がディセーブルされ、これらのピンは実効的にハイインピーダンスになります。これが1になると、IOUT1及びIOUT2の両方が起動され、各ピンが200μAの電流ソースとなります。

X2CLK: (デフォルト=0)2倍クロックビット。このビットを1に設定すると、クロック信号経路内の2分周プリスケーラが選択されます。これにより、周波数の高いクリスタル又はクロックソースを使用でき、非対称クロックソースへの耐性が改善されます。

#### 特殊関数レジスタ(書込み専用)

MDOUT: (デフォルト = 0) 変調器出力ビット。 MDOUT = 0の時、DOUTピンにおけるデータ読み出し

表2. データ出力レート対CLK、フィルタ選択及び変調器周波数ビット

| CLKIN FREQUENCY,<br>f <sub>CLKIN</sub> (MHz) |           | CLK | MF1   | MFO     | AVAILABLE OUTPUT DATA RATES (sps) |                     |                    |                    |  |

|----------------------------------------------|-----------|-----|-------|---------|-----------------------------------|---------------------|--------------------|--------------------|--|

| X2CLK = 0                                    | X2CLK = 1 | CLK | IVIFI | MF1 MF0 | FS1, FS0*<br>(0, 0)               | FS1, FS0*<br>(0, 1) | FS1, FS0<br>(1, 0) | FS1, FS0<br>(1, 1) |  |

| 1.024                                        | 2.048     | 0   | 0     | 0       | 20                                | 25                  | 100                | 200                |  |

| 1.024                                        | 2.048     | 0   | 0     | 1       | 40                                | 50                  | 200                | 400                |  |

| 1.024                                        | 2.048     | 0   | 1     | 0       | 80                                | 100                 | 400                | 800                |  |

| 1.024                                        | 2.048     | 0   | 1     | 1       | 160                               | 200                 | 800                | 1600               |  |

| 2.4576                                       | 4.9152    | 1   | 0     | 0       | 50                                | 60                  | 300                | 600                |  |

| 2.4576                                       | 4.9152    | 1   | 0     | 1       | 100                               | 120                 | 600                | 1200               |  |

| 2.4576                                       | 4.9152    | 1   | 1     | 0       | 200                               | 240                 | 1200               | 2400               |  |

| 2.4576                                       | 4.9152    | 1   | 1     | 1       | 400                               | 480                 | 2400               | 4800               |  |

<sup>\*</sup> Data rates offering noise-free 16-bit resolution.

**Note:** When FAST = 0,  $f_{-3dB} = 0.262 \cdot Data Rate$ . When FAST = 1,  $f_{-3dB} = 0.443 \cdot Data Rate$ .

Note: Default condition is in bold print.

表3. M1、M0によって制御される特殊モード(SCAN = 0)

| M1 | MO | DESCRIPTION                                                                                                                                                                                                  |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Normal Mode: The device operates normally.                                                                                                                                                                   |

| 0  | 1  | <b>Calibrate Offset:</b> In this mode, the MAX1403 converts the voltage applied across CALOFF+ and CALOFF The PGA gain, DAC, and format settings of the selected channel (defined by DIFF, A1, A0) are used. |

| 1  | 0  | <b>Calibrate Gain:</b> In this mode, the MAX1403 converts the voltage applied across CALGAIN+ and CALGAIN The PGA gain, DAC, and format settings of the selected channel (defined by DIFF, A1, A0) are used. |

| 1  | 1  | Reserved: Do not use.                                                                                                                                                                                        |

# 表4. SCANモードのスキャンシーケンス (SCAN = 1)

| DIFF | M1 | MO | SEQUENCE                                                                     |

|------|----|----|------------------------------------------------------------------------------|

| 0    | 0  | 0  | AIN1–AIN6, AIN2–AIN6, AIN3–AIN6,<br>AIN4–AIN6, AIN5–AIN6                     |

| 0    | 0  | 1  | AIN1-AIN6, AIN2-AIN6, AIN3-AIN6,<br>AIN4-AIN6, AIN5-AIN6, CALOFF,<br>CALGAIN |

| 0    | 1  | 0  | AIN1-AIN6, AIN2-AIN6, AIN3-AIN6,<br>AIN4-AIN6, AIN5-AIN6, CALOFF,<br>CALGAIN |

| 1    | 0  | 0  | AIN1-AIN2, AIN3-AIN4, AIN5-AIN6                                              |

| 1    | 0  | 1  | AIN1-AIN2, AIN3-AIN4, AIN5-AIN6,<br>CALOFF, CALGAIN                          |

| 1    | 1  | 0  | AIN1-AIN2, AIN3-AIN4, AIN5-AIN6,<br>CALOFF, CALGAIN                          |

**Note:** All other combinations reserved.

### 表5. 使用可能な入力チャネル(SCAN = 0)

| DIFF | M1 | MO | AVAILABLE CHANNELS                            |

|------|----|----|-----------------------------------------------|

| 0    | 0  | 0  | AIN1–AIN6, AIN2–AIN6, AIN3–AIN6,<br>AIN4–AIN6 |

| 0    | 0  | 1  | CALOFF                                        |

| 0    | 1  | 0  | CALGAIN                                       |

| 1    | 0  | 0  | AIN1-AIN2, AIN3-AIN4, AIN5-AIN6               |

| 1    | 0  | 1  | CALOFF                                        |

| 1    | 1  | 0  | CALGAIN                                       |

がイネーブルされます。これはシリアルインタフェースの通常状態です。MDOUT = 1に設定されると、DOUT 及びINTピンの機能が変更され、通常のシリアルデータインタフェース出力の代わりに生のシングルビット変調器出力が提供されます。これにより、内蔵ディジタルフィルタを経由せずに、変調器出力に直接カスタムフィルタリングを施すことができます。INTピンはDOUTにおける変調器データをいつサンプリングするべきか(INTの立下がリエッジ)を知らせるクロックを提供します。このモードにおいても内蔵ディジタルフィルタは通常通り動作することに注意してください。MDOUTが0に戻ると、通常のシリアルインタフェース読取り動作によって有効なデータにアクセスできるようになります。

FULLPD: (デフォルト = 0)完全パワーダウンビット。 FULLPD = 1の時、デバイスはクロック発振器も含めて 強制的に完全パワーダウン状態になります。シリアル インタフェースは引き続き動作します。この状態から 適正に回復するには、ハードウェアリセットを必要と します。

注記:特殊関数レジスタの予備ビットを全て0のデフォルト状態から変更すると、予備モードの1つが選択され、デバイスは予期通りの動作をしなくなります。このレジスタは書込み専用レジスタです。しかし、間違ってこのレジスタを読んでしまった場合は、デバイスから24ビットのデータを同期出力することにより、通常のインタフェースアイドル状態に回復させてください。

#### 伝達関数レジスタ

3つの伝達関数レジスタが、入力電圧を出力コードにマッピングするために使用される方法を制御します。これらのレジスタは全て同じフォーマットを持っています。制御レジスタが関連するチャネルにどのようにマッピングされるかは、動作モードに依存し、M1、M0、DIFF及びSCANの状態に影響されます(表8、9及び10)。

#### 特殊関数レジスタ(書込み専用)

最初のビット(MSB)

(LSB)

| FUNCTION | RESERVED BITS |   |       |   | RESERV | ED BITS |   |        |

|----------|---------------|---|-------|---|--------|---------|---|--------|

| Name     | 0             | 0 | MDOUT | 0 | 0      | 0       | 0 | FULLPD |

| Defaults | 0             | 0 | 0     | 0 | 0      | 0       | 0 | 0      |

#### 伝達関数レジスタ

最初のビット(MSB)

(LSB)

|          |    | 1 (IVIOD) |         |     |    | (200)     |          |    |

|----------|----|-----------|---------|-----|----|-----------|----------|----|

| FUNCTION |    | PGA GAIN  | CONTROL |     |    | OFFSET CO | RRECTION |    |

| Name     | G2 | G1        | G0      | U/B | D3 | D2        | D1       | D0 |

| Defaults | 0  | 0         | 0       | 0   | 0  | 0         | 0        | 0  |

#### アナログ入力AIN1~AIN6

入力AIN1及びAIN2は、スキャンモード(SCAN=1)やシングルエンドと差動(DIFF)モードの別にかかわりなく、伝達関数レジスタ1にマッピングします。同様に、AIN3及びAIN4入力は常に伝達関数レジスタ2にマッピングします。最後に、AIN5は常に伝達関数レジスタ3にマッピングします(AIN6はアナログコモン端子です)。

#### CALGAIN及びCALOFF

スキャンモードでない時(SCAN = 0)、A1とA0はいずれの 伝達関数がCALGAIN及びCALOFFに適用されるかを 選択します。スキャンモード(SCAN = 1)においては、CALGAIN及びCALOFFは常に伝達関数レジスタ3に マッピングされます。M1 M0の状態でスキャンしている時、CALGAIN及びCALOFFの両チャネルがスキャンシーケンスに含まれることに注意してください(表4)。両方のチャネルが同じチャネルIDタグを共有しますが、CALOFFが常にCALGAINよりも先になります(表11)。

任意のアクティブなチャネル制御ビットの状態を変更すると、INTが直ちにハイに遷移して変調器/フィルタがリセットされることに注意してください。INTは適切なディジタルフィルタセトリング時間が経過した後に再び発生します。インアクティブなチャネルの制御設定を自由に変更しても、INTの状態に影響せず、フィルタ/変調器がリセットすることもありません。

#### PGAの利得

ビットG2~G0は、表6に従ってPGAの利得を制御します。

#### ユニポーラ/バイポーラモード

U/Bビットは、チャネルをバイポーラ又はユニポーラモードに設定します。0の場合はバイポーラモードが選択され、1の場合はユニポーラモードが選択されます。このビットはアナログ信号調節には影響しません。変調器は常にバイポーラ入力を受け付け、選択された入力が同じ電位の時に1の密度が50%であるビットストリームを生成します。このビットは、使用可能な

表6. PGA利得コード

| G2 | G1 | G0 | PGA GAIN |

|----|----|----|----------|

| 0  | 0  | 0  | x1       |

| 0  | 0  | 1  | x2       |

| 0  | 1  | 0  | x4       |

| 0  | 1  | 1  | x8       |

| 1  | 0  | 0  | x16      |

| 1  | 0  | 1  | x32      |

| 1  | 1  | 0  | x64      |

| 1  | 1  | 1  | x128     |

出力ビットが適正な出力範囲にマッピングされるようにディジタルフィルタ出力の処理を制御します。変換する前にU/Bを設定する必要があることに注意してください(出力レジスタに既に保持されているデータには影響を与えません)。

バイポーラモードを選択しても、AGNDより低い入力が許容されるわけではありません。デバイスの利得とオフセットが変わるだけです。全ての入力は仕様動作電圧範囲内に収まっていなければなりません。

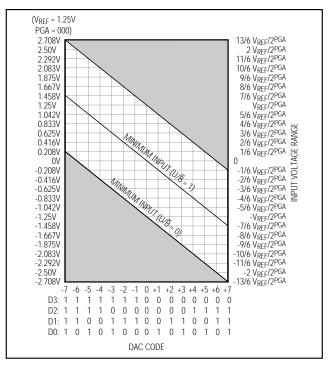

#### オフセット補正DAC

ビットD3~D0はオフセット補正DACを制御します。 DACの範囲はPGAの利得設定に依存し、使用可能なフルスケール入力範囲に対するパーセント比率として表現されます(表7)。

D3は符号ビット、D2~D0はDAC値の大きさを表します。DAC値として0000(デフォルト)が設定されると、DACは変調器入力から切り離されることに注意してください。これにより、オフセット補正が必要ないときにDACによってノイズ性能が劣化するのを防ぐことができます。

#### 伝達関数レジスタのマッピング

表8、9及び10に、様々な動作モードにおけるチャネル 制御レジスタのマッピングを示します。

表7. DACコード対DAC値

| D3 | D2 | D1 | D0 | BIPOLAR<br>DAC VALUE<br>(% of FSR) | UNIPOLAR<br>DAC VALUE<br>(% of FSR) |  |  |

|----|----|----|----|------------------------------------|-------------------------------------|--|--|

| 0  | 0  | 0  | 0  | DAC not connected                  |                                     |  |  |

| 0  | 0  | 0  | 1  | +8.3                               | +16.7                               |  |  |

| 0  | 0  | 1  | 0  | +16.7                              | +33.3                               |  |  |

| 0  | 0  | 1  | 1  | +25                                | +50                                 |  |  |

| 0  | 1  | 0  | 0  | +33.3                              | +66.7                               |  |  |

| 0  | 1  | 0  | 1  | +41.6                              | +83.3                               |  |  |

| 0  | 1  | 1  | 0  | +50                                | +100                                |  |  |

| 0  | 1  | 1  | 1  | +58.3                              | +116.7                              |  |  |

| 1  | 0  | 0  | 0  | DAC not cor                        | nnected                             |  |  |

| 1  | 0  | 0  | 1  | -8.3                               | -16.7                               |  |  |

| 1  | 0  | 1  | 0  | -16.7                              | -33.3                               |  |  |

| 1  | 0  | 1  | 1  | -25                                | -50                                 |  |  |

| 1  | 1  | 0  | 0  | -33.3                              | -66.7                               |  |  |

| 1  | 1  | 0  | 1  | -41.6                              | -83.3                               |  |  |

| 1  | 1  | 1  | 0  | -50                                | -100                                |  |  |

| 1  | 1  | 1  | 1  | -58.3                              | -116.7                              |  |  |

表8. 伝達関数レジスタのマッピング --- 通常モード(M1 = 0、M0 = 0)

| SCAN | DIFF | A1 | A0 | CHANNEL    | TRANSFER-<br>FUNCTION REGISTER |  |  |

|------|------|----|----|------------|--------------------------------|--|--|

| 0    | 0    | 0  | 0  | AIN1-AIN6  | 1                              |  |  |

| 0    | 0    | 0  | 1  | AIN2-AIN6  | 1                              |  |  |

| 0    | 0    | 1  | 0  | AIN3-AIN6  | 2                              |  |  |

| 0    | 0    | 1  | 1  | AIN4-AIN6  | 2                              |  |  |

| 0    | 1    | 0  | 0  | AIN1-AIN2  | 1                              |  |  |

| 0    | 1    | 0  | 1  | AIN3-AIN4  | 2                              |  |  |

| 0    | 1    | 1  | 0  | AIN5-AIN6  | 3                              |  |  |

| 0    | 1    | 1  | 1  | Do Not Use |                                |  |  |