### 概要

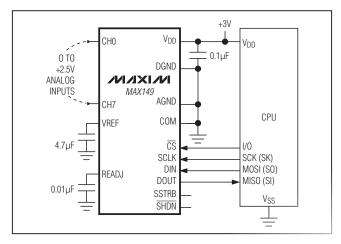

MAX148/MAX149は、8チャネルマルチプレクサ、高帯 域幅トラック/ホールドおよびシリアルインタフェースを備 えた、低消費電力で高速変換の10ビットデータ収集シス テムです。+2.7V~+5.25Vの単一電源で動作し、サンプ リングレートは最大133kspsです。両製品のアナログ入力 はソフトウェアにより、ユニポーラ/バイポーラおよびシン グルエンド/差動動作に設定することができます。

4線シリアルインタフェースは外部ロジック無しで直接SPI™/ QSPI™およびMICROWIRE™デバイスに接続可能です。 シリアルストローブ出力により、TMS320ファミリのディ ジタル信号プロセッサに直接接続することができます。 MAX148/MAX149は、内部クロックまたは外部シリアル インタフェースクロックを用いることで、逐次比較のアナ ログディジタル変換を行います。

MAX149は2.5Vリファレンスを内蔵し、MAX148は外部 リファレンスを必要とします。どちらの製品も電圧調整範囲 ±1.5%のリファレンスバッファアンプを備えています。

これらの製品はハードによるSHDNピンおよびソフトウェア 選択によるパワーダウン機能を備えており、変換の最後で 自動的にシャットダウンするようにプログラムすることが 可能です。MAX148/MAX149はシリアルインタフェース にアクセスすると自動的にパワーアップし、ターンオン時 間が速いため全ての変換と変換の間をシャットダウンする ことができます。この機能によって、サンプリングレート が低い場合には消費電流を60µA以下に抑えることができ ます。

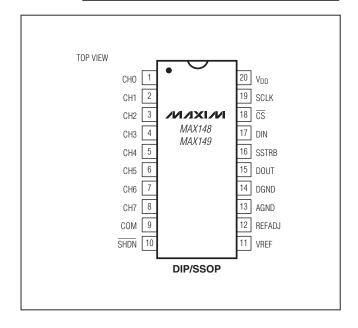

MAX148/MAX149は、20ピンDIPおよび20ピンSSOP パッケージで提供されています。

これらの製品の4チャネルバージョンはMAX1248/ MAX1249のデータシートを参照して下さい。

### アプリケーション

ポータブルデータロギング

データ収集

医療機器

バッテリ駆動機器

ペンディジタイザ

プロセス制御

ピン配置はデータシートの最後に記載されています。

### 特長

◆ 入力:8チャネルシングルエンドまたは4チャネル差動

◆ 単一電源:+2.7V~+5.25V

◆ 2.5Vリファレンス内蔵(MAX149)

◆ 低電力: 1.2mA (133ksps、3V電源) 54µA (1ksps、3V電源) 1µA (パワーダウンモード)

◆ 4線シリアルインタフェース: SPI/QSPI/ MICROWIRE/TMS320コンパチブル

◆ ユニポーラまたはバイポーラ入力:ソフトウェアで設定

♦ パッケージ: 20ピンDIP/SSOP

### 型番

| PART†      | TEMP RANGE   | PIN-<br>PACKAGE | INL<br>(LSB) |

|------------|--------------|-----------------|--------------|

| MAX148ACPP | 0°C to +70°C | 20 Plastic DIP  | ±1/2         |

| MAX148BCPP | 0°C to +70°C | 20 Plastic DIP  | ±1           |

| MAX148ACAP | 0°C to +70°C | 20 SSOP         | ±1/2         |

| MAX148BCAP | 0°C to +70°C | 20 SSOP         | ±1           |

#### 型番はデータシートの最後に続いています。

†代替の表面実装パッケージの供給性についてはお問い合わせ 下さい。鉛フリー対応品は、オーダー時に型番末尾に[+]を 付加して下さい。

\*CERDIPパッケージ、MIL-STD-883B製品の供給性については お問い合わせ下さい。鉛フリー対応品は提供されていません。

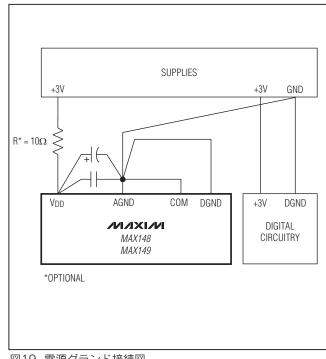

### 標準動作回路

SPIおよびQSPIはMotorola, Inc.の商標、MICROWIREはNational Semiconductor Corp.の商標です。

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| VDD to AGND, DGND                                     | 0.3V to +6V         |

|-------------------------------------------------------|---------------------|

| AGND to DGND                                          | 0.3V to +0.3V       |

| CH0-CH7, COM to AGND, DGND0.3V t                      | $0 (V_{DD} + 0.3V)$ |

| VREF, REFADJ to AGND0.3V t                            | $(V_{DD} + 0.3V)$   |

| Digital Inputs to DGND                                | 0.3V to +6V         |

| Digital Outputs to DGND0.3V t                         | o(VDD + 0.3V)       |

| Digital Output Sink Current                           | 25mA                |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                     |

| Plastic DIP (derate 11 11mW/°C above +70°C            | ) 889mW             |

| SSOP (derate 8.00mW/°C above 4     | +70°C)640mW    |

|------------------------------------|----------------|

| CERDIP (derate 11.11mW/°C above    | ve +70°C)889mW |

| Operating Temperature Ranges       |                |

| MAX148_C_P/MAX149_C_P              | 0°C to +70°C   |

| MAX148_E_P/MAX149_E_P              | 40°C to +85°C  |

| MAX148_MJP/MAX149_MJP              | 55°C to +125°C |

| MAX149BMAP                         | 55°C to +125°C |

| Storage Temperature Range          | 60°C to +150°C |

| Lead Temperature (soldering, 10s). | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VDD = +2.7V \text{ to } +5.25V; COM = 0; fSCLK = 2.0MHz; external clock (50% duty cycle); 15 clocks/conversion cycle (133ksps); MAX149—4.7<math>\mu$ F capacitor at VREF pin; MAX148—external reference, VREF = 2.500V applied to VREF pin; TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                             | SYMBOL      | CONDITIONS                                             | MIN        | TYP       | MAX       | UNITS   |

|---------------------------------------|-------------|--------------------------------------------------------|------------|-----------|-----------|---------|

| DC ACCURACY (Note 1)                  |             |                                                        |            |           |           |         |

| Resolution                            |             |                                                        | 10         |           |           | Bits    |

| Polativa Aggurgay (Note 2)            | INL         | MAX14_A                                                |            |           | ±0.5      | LSB     |

| Relative Accuracy (Note 2)            | IINL        | MAX14_B                                                |            |           | ±1.0      | LSD     |

| Differential Nonlinearity             | DNL         | No missing codes over temperature                      |            |           | ±1        | LSB     |

| Offset Error                          |             | MAX14_A                                                |            | ±0.15     | ±1        | LSB     |

| Oliset Elloi                          |             | MAX14_B                                                |            | ±0.15     | ±2        | LSB     |

| Gain Error (Note 3)                   |             | MAX14_A                                                |            |           | ±1        | LSB     |

| Gaill Ellor (Note 3)                  |             | MAX14_B                                                |            |           | ±2        | LSD     |

| Gain Temperature Coefficient          |             |                                                        |            | ±0.25     |           | ppm/°C  |

| Channel-to-Channel Offset<br>Matching |             |                                                        |            | ±0.05     |           | LSB     |

| DYNAMIC SPECIFICATIONS (10            | kHz Sine-Wa | ve Input, 0 to 2.500V <sub>P-P</sub> , 133ksps, 2.0MHz | External C | lock, Bip | olar Inpu | t Mode) |

| Signal-to-Noise + Distortion<br>Noise | SINAD       |                                                        |            | 66        |           | dB      |

| Total Harmonic Distortion             | THD         | Up to the 5th harmonic                                 |            | -70       |           | dB      |

| Spurious-Free Dynamic Range           | SFDR        |                                                        |            | 70        |           | dB      |

| Channel-to-Channel Crosstalk          |             | 65kHz, 2.500V <sub>P-P</sub> (Note 4)                  |            | -75       |           | dB      |

| Small-Signal Bandwidth                |             | -3dB rolloff                                           |            | 2.25      |           | MHz     |

| Full-Power Bandwidth                  |             |                                                        |            | 1.0       |           | MHz     |

| CONVERSION RATE                       |             |                                                        |            |           |           |         |

|                                       |             | Internal clock, SHDN = unconnected                     | 5.5        |           | 7.5       |         |

| Conversion Time (Note 5)              | tCONV       | Internal clock, SHDN = VDD                             | 35         |           | 65        |         |

| Conversion time (Note 3)              | ICONV       | External clock = 2MHz, 12 clocks/ conversion           | 6          |           |           | - µs    |

| Track/Hold Acquisition Time           | tACQ        |                                                        |            |           | 1.5       | μs      |

| Aperture Delay                        |             |                                                        |            | 30        |           | ns      |

| Aperture Jitter                       |             |                                                        |            | < 50      |           | ps      |

|                                       |             |                                                        |            |           |           |         |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V \text{ to } +5.25V; COM = 0; f_{SCLK} = 2.0MHz; external clock (50% duty cycle); 15 clocks/conversion cycle (133ksps); MAX149—4.7<math>\mu$ F capacitor at VREF pin; MAX148—external reference, VREF = 2.500V applied to VREF pin;  $T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                            | SYMBOL       | CONDITIONS                                                     | MIN                   | TYP   | MAX                       | UNITS  |  |  |

|--------------------------------------|--------------|----------------------------------------------------------------|-----------------------|-------|---------------------------|--------|--|--|

| CONVERSION RATE (continued)          |              |                                                                |                       |       |                           |        |  |  |

|                                      |              | SHDN = unconnected                                             |                       | 1.8   |                           | NAL I  |  |  |

| Internal Clock Frequency             |              | SHDN = V <sub>DD</sub>                                         |                       | 0.225 |                           | MHz    |  |  |

| F                                    |              |                                                                | 0.1                   |       | 2.0                       |        |  |  |

| External Clock Frequency             |              | Data transfer only                                             | 1                     | 1 2.  |                           | MHz    |  |  |

| ANALOG/COM INPUTS                    |              |                                                                |                       |       |                           |        |  |  |

| Input Voltage Range, Single-         |              | Unipolar, COM = 0                                              |                       | (     | to VREF                   | V      |  |  |

| Ended and Differential (Note 6)      |              | Bipolar, COM = VREF/2                                          | ±VREF/2               |       |                           | V      |  |  |

| Multiplexer Leakage Current          |              | On/off leakage current, V <sub>CH</sub> = 0 or V <sub>DD</sub> |                       | ±0.01 | ±1                        | μΑ     |  |  |

| Input Capacitance                    |              |                                                                |                       | 16    |                           | pF     |  |  |

| INTERNAL REFERENCE (MAX14            | 9 Only, Refe | rence Buffer Enabled)                                          | •                     |       |                           | ,      |  |  |

| VREF Output Voltage                  |              | $T_A = +25$ °C (Note 7)                                        | 2.470                 | 2.500 | 2.530                     | V      |  |  |

| VREF Short-Circuit Current           |              |                                                                |                       |       | 30                        | mA     |  |  |

| VREF Temperature Coefficient         |              | MAX149                                                         |                       | ±30   |                           | ppm/°C |  |  |

| Load Regulation (Note 8)             |              | 0 to 0.2mA output load                                         |                       | 0.35  |                           | mV     |  |  |

| Consolitive Dynama at VDEE           |              | Internal compensation mode                                     | 0                     |       |                           |        |  |  |

| Capacitive Bypass at VREF            |              | External compensation mode                                     | 4.7                   |       |                           | μF     |  |  |

| Capacitive Bypass at REFADJ          |              |                                                                | 0.01                  |       |                           | μF     |  |  |

| REFADJ Adjustment Range              |              |                                                                |                       | ±1.5  |                           | %      |  |  |

| EXTERNAL REFERENCE AT VRE            | F (Buffer Di | sabled)                                                        |                       |       |                           |        |  |  |

| VREF Input Voltage Range<br>(Note 9) |              |                                                                | 1.0                   |       | V <sub>DD</sub> +<br>50mV | V      |  |  |

| VREF Input Current                   |              | VREF = 2.500V                                                  |                       | 100   | 150                       | μΑ     |  |  |

| VREF Input Resistance                |              |                                                                | 18                    | 25    |                           | kΩ     |  |  |

| Shutdown VREF Input Current          |              |                                                                |                       | 0.01  | 10                        | μΑ     |  |  |

| REFADJ Buffer-Disable Threshold      |              |                                                                | V <sub>DD</sub> - 0.5 |       |                           | V      |  |  |

| EXTERNAL REFERENCE AT REF            | ADJ          |                                                                |                       |       |                           | 1      |  |  |

|                                      |              | Internal compensation mode                                     | 0                     |       |                           |        |  |  |

| Capacitive Bypass at VREF            |              | External compensation mode                                     | 4.7                   | -     |                           | μF     |  |  |

| D. (                                 |              | MAX149                                                         |                       | 2.06  |                           |        |  |  |

| Reference Buffer Gain                |              | MAX148                                                         |                       | 2.00  |                           | V/V    |  |  |

| DEEAD II O                           |              | MAX149                                                         |                       |       | ±50                       |        |  |  |

| REFADJ Input Current                 |              | MAX148                                                         |                       | -     | ±10                       | μΑ     |  |  |

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{DD} = +2.7 V \text{ to } +5.25 V; COM = 0; f_{SCLK} = 2.0 MHz; external clock (50% duty cycle); 15 clocks/conversion cycle (133ksps); MAX149—4.7 µF capacitor at VREF pin; MAX148—external reference, VREF = 2.500 V applied to VREF pin; TA = T_{MIN} to T_{MAX}, unless otherwise noted.)$

| PARAMETER                                  | SYMBOL          | CONDITION                                                          | IS               | MIN                   | TYP                      | MAX  | UNITS |

|--------------------------------------------|-----------------|--------------------------------------------------------------------|------------------|-----------------------|--------------------------|------|-------|

| DIGITAL INPUTS (DIN, SCLK, CS              | SHDN)           |                                                                    |                  |                       |                          |      |       |

|                                            | \/              | V <sub>DD</sub> ≤ 3.6V                                             |                  | 2.0                   |                          |      | V     |

| DIN, SCLK, CS Input High Voltage           | VIH             | V <sub>DD</sub> > 3.6V                                             |                  | 3.0                   |                          |      | ] V   |

| DIN, SCLK, CS Input Low Voltage            | VIL             |                                                                    |                  |                       |                          | 0.8  | V     |

| DIN, SCLK, CS Input Hysteresis             | VHYST           |                                                                    |                  | 0.2                   |                          | V    |       |

| DIN, SCLK, CS Input Leakage                | IIN             | $V_{IN} = 0$ or $V_{DD}$                                           |                  |                       | ±0.01                    | ±1   | μΑ    |

| DIN, SCLK, CS Input Capacitance            | CIN             | (Note 10)                                                          |                  |                       |                          | 15   | pF    |

| SHDN Input High Voltage                    | VsH             |                                                                    |                  | V <sub>DD</sub> - 0.4 |                          |      | V     |

| SHDN Input Mid Voltage                     | V <sub>SM</sub> |                                                                    | 1.1              |                       | V <sub>DD</sub> -<br>1.1 | V    |       |

| SHDN Input Low Voltage                     | V <sub>SL</sub> |                                                                    |                  |                       |                          | 0.4  | V     |

| SHDN Input Current                         | Is              | SHDN = 0 or V <sub>DD</sub>                                        |                  |                       |                          | ±4.0 | μΑ    |

| SHDN Voltage, Unconnected                  | VFLT            | SHDN = unconnected                                                 |                  | V <sub>DD</sub> /2    |                          | V    |       |

| SHDN Maximum Allowed<br>Leakage, Mid Input |                 | SHDN = unconnected                                                 |                  |                       | ±100                     | nA   |       |

| DIGITAL OUTPUTS (DOUT, SSTR                | B)              |                                                                    |                  |                       |                          |      |       |

| Output Valtaga Laur                        | 1/01            | ISINK = 5mA                                                        |                  |                       | 0.4                      | V    |       |

| Output-Voltage Low                         | Vol             | ISINK = 16mA                                                       |                  |                       | 0.8                      | ] V  |       |

| Output-Voltage High                        | Voн             | ISOURCE = 0.5mA                                                    |                  | V <sub>DD</sub> - 0.5 |                          |      | V     |

| Three-State Leakage Current                | IL              | CS = V <sub>DD</sub>                                               |                  |                       | ±0.01                    | ±10  | μΑ    |

| Three-State Output Capacitance             | Cout            | CS = V <sub>DD</sub> (Note 10)                                     |                  |                       |                          | 15   | pF    |

| POWER REQUIREMENTS                         |                 |                                                                    |                  |                       |                          |      |       |

| Positive Supply Voltage                    | V <sub>DD</sub> |                                                                    | _                | 2.70                  |                          | 5.25 | V     |

|                                            |                 | Operating mode, full-scale                                         | $V_{DD} = 5.25V$ |                       | 1.6                      | 3.0  | mA    |

|                                            |                 | input (Note 11)                                                    | $V_{DD} = 3.6V$  |                       | 1.2                      | 2.0  | 111/4 |

| Positive Supply Current                    | IDD             | Full power-down                                                    | $V_{DD} = 5.25V$ |                       | 3.5                      | 15   | μА    |

|                                            |                 | ruii power-down                                                    | $V_{DD} = 3.6V$  |                       | 1.2                      | 10   |       |

|                                            |                 | Fast power-down (MAX149                                            | )                |                       | 30                       | 70   |       |

| Supply Rejection (Note 12)                 | PSR             | Full-scale input, external reference = 2.500V, VDD = 2.7V to 5.25V |                  |                       | ±0.3                     |      | mV    |

### TIMING CHARACTERISTICS

$(V_{DD} = +2.7V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$

| PARAMETER                       | SYMBOL | CON                                | IDITIONS      | MIN | TYP | MAX | UNITS |

|---------------------------------|--------|------------------------------------|---------------|-----|-----|-----|-------|

| Acquisition Time                | tACQ   |                                    |               | 1.5 |     |     | μs    |

| DIN to SCLK Setup               | tDS    |                                    |               | 100 |     |     | ns    |

| DIN to SCLK Hold                | tDH    |                                    |               | 0   |     |     | ns    |

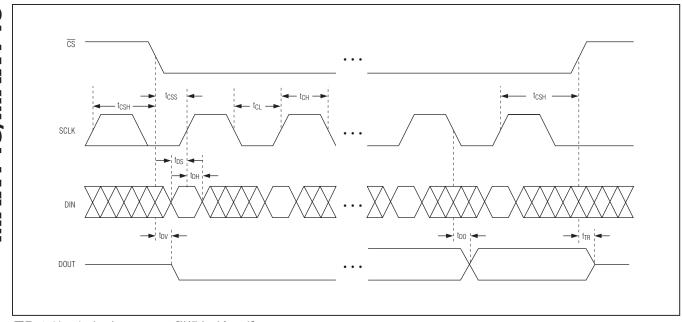

| COLK Fall to Output Data Valid  | +0.0   | Figure 1                           | MAX14C/E      | 20  |     | 200 |       |

| SCLK Fall to Output Data Valid  | tDO    | Figure 1                           | MAX14M        | 20  |     | 240 | ns    |

| CS Fall to Output Enable        | tDV    | Figure 1                           |               |     |     | 240 | ns    |

| CS Rise to Output Disable       | tTR    | Figure 2                           |               |     |     | 240 | ns    |

| CS to SCLK Rise Setup           | tcss   |                                    |               | 100 |     |     | ns    |

| CS to SCLK Rise Hold            | tcsh   |                                    |               | 0   |     |     | ns    |

| SCLK Pulse Width High           | tCH    |                                    |               | 200 |     |     | ns    |

| SCLK Pulse Width Low            | tCL    |                                    |               | 200 |     |     | ns    |

| SCLK Fall to SSTRB              | tsstrb | Figure 1                           |               |     |     | 240 | ns    |

| CS Fall to SSTRB Output Enable  | tsdv   | External clock mode only, Figure 1 |               |     |     | 240 | ns    |

| CS Rise to SSTRB Output Disable | tstr   | External clock mode only, Figure 2 |               |     |     | 240 | ns    |

| SSTRB Rise to SCLK Rise         | tsck   | Internal clock mode                | only (Note 7) | 0   |     |     | ns    |

- **Note 1:** Tested at V<sub>DD</sub> = 2.7V; COM = 0; unipolar single-ended input mode.

- Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated.

- Note 3: MAX149—internal reference, offset nulled; MAX148—external reference (VREF = +2.500V), offset nulled.

- Note 4: Ground "on" channel; sine wave applied to all "off" channels.

- Note 5: Conversion time defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

- Note 6: The common-mode range for the analog inputs is from AGND to VDD.

- Note 7: Sample tested to 0.1% AQL.

- Note 8: External load should not change during conversion for specified accuracy.

- Note 9: ADC performance is limited by the converter's noise floor, typically  $300\mu V_{P-P}$ .

- Note 10: Guaranteed by design. Not subject to production testing.

- **Note 11:** The MAX148 typically draws 400µA less than the values shown.

- Note 12: Measured as IVFS(2.7V) VFS(5.25V)I.

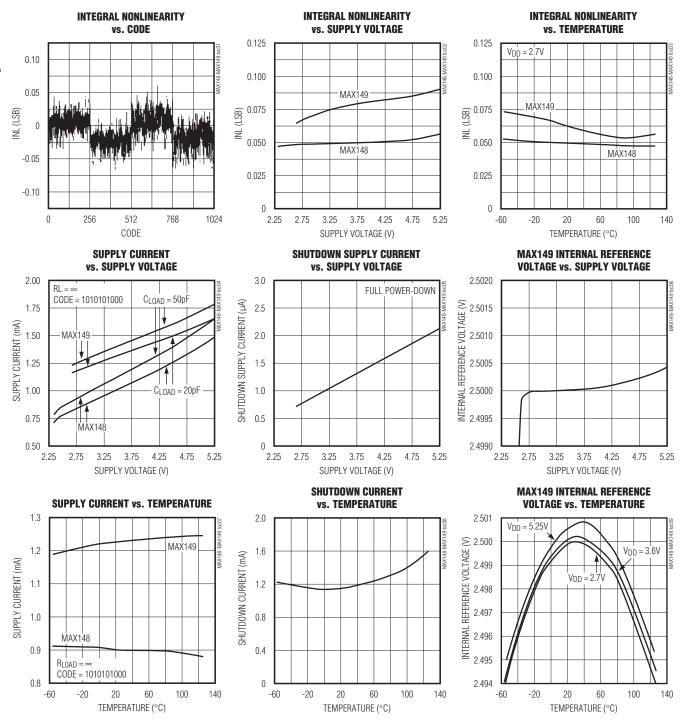

### 標準動作特性

(VDD = 3.0V, VREF = 2.500V, fSCLK = 2.0MHz, CLOAD = 20pF, TA = +25°C, unless otherwise noted.)

### 端子説明

| 端子  | 名称              | 機能                                                                                                                                                               |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–8 | CH0-CH7         | サンプリングアナログ入力                                                                                                                                                     |

| 9   | COM             | アナログ入力のグランド基準。シングルエンドモードでのCOMはゼロコード電圧を設定します。<br>±0.5 LSB以内の安定性が必要です。                                                                                             |

| 10  | SHDN            | 3レベルシャットダウン入力。SHDNをローにするとMAX148/MAX149はシャットダウンし、それ以外の場合は、完全動作状態です。SHDNをハイにするとリファレンスバッファアンプは内部補償モードになります。SHDNをオープンにするとリファレンスバッファアンプは外部補償モードになります。                 |

| 11  | VREF            | リファレンスバッファ出力/ADCリファレンス入力。A/D変換用のリファレンス電圧。内部リファレンスモード(MAX149のみ)では、リファレンスバッファは公称2.500V出力を提供し、REFADJで外部的に調整可能です。外部リファレンスモードでは、REFADJをVDDに接続することで内部バッファをディセーブルします。   |

| 12  | REFADJ          | リファレンスバッファアンプ入力。リファレンスバッファアンプをディセーブルするにはREFADJをV <sub>DD</sub> に接続して下さい。                                                                                         |

| 13  | AGND            | アナロググランド                                                                                                                                                         |

| 14  | DGND            | ディジタルグランド                                                                                                                                                        |

| 15  | DOUT            | シリアルデータ出力。データはSCLKの立下がりエッジでクロック出力されます。CSがハイの時は、<br>ハイインピーダンスになります。                                                                                               |

| 16  | SSTRB           | シリアルストローブ出力。内部クロックモードでは、SSTRBはMAX148/MAX149がA/D変換を開始した時にローになり、変換終了時にハイになります。外部クロックモードでは、SSTRBはMSBの決定前に1クロックサイクルだけパルス的にハイになります。CSがハイ(外部クロックモード)の時はハイインピーダンスになります。 |

| 17  | DIN             | シリアルデータ入力。データはSCLKの立上がりエッジでクロック入力されます。                                                                                                                           |

| 18  | CS              | アクティブローのチップセレクト。CSがローでない限り、データはDINにクロック入力されません。CSがハイの時、DOUTはハイインピーダンスになります。                                                                                      |

| 19  | SCLK            | シリアルクロック入力。シリアルインタフェースのデータをクロック入力および出力します。外部クロック<br>モードではSCLKは変換速度も設定します(デューティサイクルは40%~60%にして下さい)。                                                               |

| 20  | V <sub>DD</sub> | 正電源電圧                                                                                                                                                            |

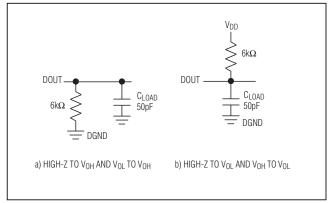

図1. イネーブル時間測定用の負荷回路

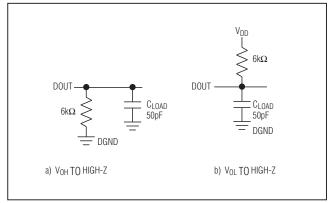

図2. ディセーブル時間測定用の負荷回路

### の 詳細

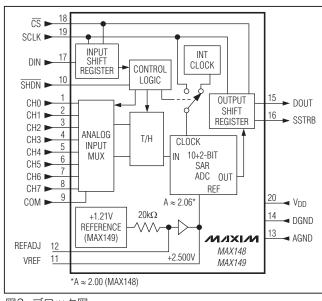

MAX148/MAX149、逐次比較型の変換技法と入力トラック/ホールド(T/H)回路を用いることで、アナログ信号を10ビットのディジタル出力に変換するアナログ-ディジタルコンバータ(ADC)です。フレキシブルなシリアルインタフェースがマイクロプロセッサ(µP)とのインタフェースを容易にします。図3にMAX148/MAX149のブロック図を示します。

#### 疑似差動入力

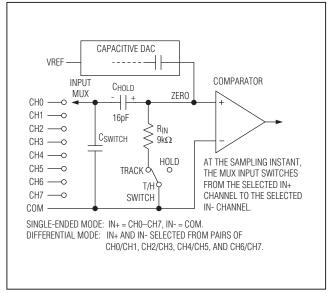

ADCのアナログコンパレータのサンプリング構造は入力等価回路(図4)に図解されています。シングルエンドモードでは、IN+は内部でCH0~CH7にスイッチされ、IN-はCOMにスイッチされます。差動モードでは、IN+およびIN-はCH0/CH1、CH2/CH3、CH4/CH5およびCH6/CH7の組合せから選択されます。チャネルの設定は表2および表3を参考に行って下さい。

差動モードでは、IN-およびIN+は内部でアナログ入力の どちらかにスイッチされます。この構成はIN+の信号だけが サンプリングされるため、疑似差動になります。リターン側 (IN-)は変換中、AGNDに対して±0.5 LSB (ベストの結果を 得るためには±0.1 LSB)以内で安定していなければなりません。これを実現するために、IN- (選択されたアナログ 入力)とAGNDの間に0.1μFのコンデンサを接続して下さい。

アクイジション期間中は正入力(IN+)として選択されたチャネルがコンデンサCHOLDを充電します。アクイジション期間は3 SCLKサイクル間だけ続き、入力制御ワードの最後のビットが入力された後のSCLKの立下がりエッジで完了

します。アクイジション期間の終了時にT/Hスイッチが開き、 CHOLDの電荷をIN+の信号のサンプルとして保持します。

変換期間は、入力マルチプレクサが $C_{HOLD}$ を正入力(IN+) から負入力(IN-)にスイッチした時から始まります。シングルエンドモードではIN-はCOMです。このため、コンパレータの入力でのノードZEROが不平衡になります。変換サイクルの残りの時間で、容量性DACがノードZEROを10ビット分解能の制限範囲でOに調節します。この動作は16pFx[ $(V_{IN+}) - (V_{IN-})$ ]の電荷を $C_{HOLD}$ からバイナリ重み付の容量性DACに移すのと等価です。この結果、アナログ入力信号のディジタル表現が生成されます。

### トラック/ホールド

T/Hは、8ビット制御ワードの5番目のビットがシフトインされた後の立下がりクロックエッジでトラッキングモードに入り、制御ワードの8番目のビットがシフトインされた後の立下がりクロックエッジでホールドモードに入ります。コンバータがシングルエンド入力用に設定されている場合はIN-がCOMに接続され、コンバータは[+]入力をサンプリングします。コンバータが差動入力用に設定されている場合はIN-が[-]入力に接続され、|IN+ - IN- | の差がサンプリングされます。変換完了時に正入力が再びIN+に接続され、CHOLDは入力信号電圧まで充電されます。

T/Hが入力信号を取込むのに要する時間は、入力容量が充電される速さとの関数になります。入力信号のソースインピーダンスが高いとアクイジション時間は長くなるため、変換と変換の間の時間を長くする必要があります。アクイジション時間tacoはデバイスが信号を取込むのに要する

図3. ブロック図

図4. 入力等価回路

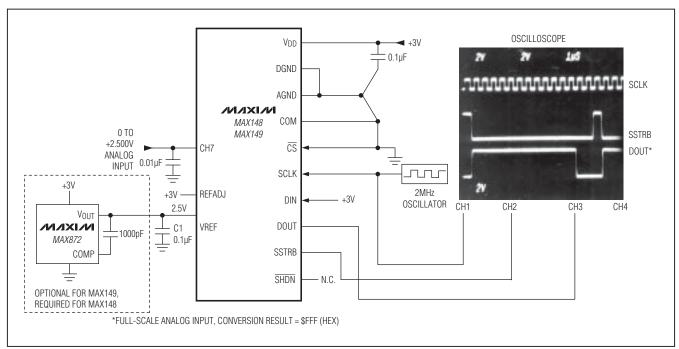

図5. 性能チェック回路

最大時間であり、信号の取込みに必要な最低時間です。 アクイジション時間は、次式で計算されます。

$$t_{ACO} = 7 \times (R_S + R_{IN}) \times 16 pF$$

ここで、 $R_{\text{IN}}=9k\Omega$ 、 $R_{\text{S}}=$  入力信号のソースインピーダンス、そして $t_{\text{ACQ}}$ は必ず $1.5\mu$ s以上とします。ソースインピーダンスが $4k\Omega$ 以下であれば、ADCのAC性能に大きな影響はありません。

各アナログ入力に0.01µFのコンデンサを接続することで、より高いソースインピーダンスも使用可能になります。入力コンデンサは入力ソースインピーダンスと共にRCフィルタを構成し、ADCの信号帯域幅が制限されることに注意して下さい。

#### 入力帯域幅

ADCの入力トラッキング回路の小信号帯域幅は2.25MHzであるため、アンダーサンプリング技法を用いることによって帯域幅がADCのサンプリングレートを超える周期信号を測定し、高速トランジェント現象を数値化することが可能です。高周波信号が計測したい周波数帯域にエイリアシングするのを防ぐために、アンチエイリアシングフィルタリングをお勧めします。

### アナログ入力保護

内部保護ダイオードがアナログ入力をV<sub>DD</sub>および AGNDにクランプしているため、チャネル入力ピンは (AGND - 0.3V)~( $V_{DD}$  + 0.3V)の範囲で、損傷を起こすことなくスイングすることができます。しかし、フルスケール付近で正確な変換を行うためには、入力が $V_{DD}$ を50mV以上超えないように、またAGNDを50mV以上下回らないようにして下さい。

アナログ入力が電源を50mV以上超える場合には、オフチャネルの保護ダイオードに2mA以上の順方向バイアスをかけないで下さい。

#### 性能チェック回路

MAX148/MAX149のアナログ性能を簡便に評価するには、図5の回路を使用して下さい。MAX148/MAX149では各変換の前に制御バイトがDINに書き込まれる必要があります。DINを+3Vに接続すると、\$FF (HEX)という制御バイトが書き込まれ、これは変換と変換の間にパワーダウンのない外部クロックモードでのCH7のシングルエンドユニポーラ変換を設定します。外部クロックモードでは、変換結果の最上位ビットがDOUTからシフトアウトされる前に、SSTRB出力が1クロック周期だけパルス的にハイになります。CH7へのアナログ入力を変化させると、DOUTからのビットのシーケンスが変わります。1変換当たり合計15クロックサイクルが必要です。SSTRBおよびDOUTの遷移は全てSCLKの立下がりエッジで起こります。

| BIT 7<br>(MSB) | BIT 6 | BIT 5 | BIT 4 | BIT 3   | BIT 2    | BIT 1 | BIT 0<br>(LSB) |

|----------------|-------|-------|-------|---------|----------|-------|----------------|

| START          | SEL2  | SEL1  | SEL0  | UNI/BIP | SGL//DIF | PD1   | PD0            |

| BIT 7<br>(MSB) | BIT 6                | BIT 5               | BIT 4                                                                                            | BIT 3                                                            | BIT 2              | BIT 1           | BIT 0<br>(LSB) |  |  |

|----------------|----------------------|---------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|-----------------|----------------|--|--|

| START          | SEL2                 | SEL1                | SEL0                                                                                             | UNI/BIP                                                          | SGL//DIF           | PD1             | PD0            |  |  |

| BIT            | NAME                 |                     |                                                                                                  | DESCRI                                                           | PTION              |                 |                |  |  |

| 7(MSB)         | START                | The first logic "1" | bit after CS c                                                                                   | joes low defines the                                             | e beginning of the | e control byte. |                |  |  |

| 6<br>5<br>4    | SEL2<br>SEL1<br>SEL0 | These three bits    | These three bits select which of the eight channels are used for the conversion (Tables 2 and 3) |                                                                  |                    |                 |                |  |  |

| 3              | UNI/BIP              | · ·                 | nal from 0 to V                                                                                  | cts unipolar or bipo<br>REF can be conver                        |                    |                 |                |  |  |

| 2              | SGL/ <del>DIF</del>  | ended mode, inp     | out signal volta                                                                                 | ial. Selects single-eages are referred to<br>els is measured (Ta | COM. In differer   |                 |                |  |  |

| 1              | PD1                  | Selects clock and   | d power-dowr                                                                                     | modes.                                                           |                    |                 |                |  |  |

|                |                      | PD1                 | PD0                                                                                              | Mode                                                             |                    |                 |                |  |  |

|                |                      | 0                   | 0                                                                                                | Full power-down                                                  | _                  |                 |                |  |  |

| 0(LSB)         | PD0                  | 0                   | 1                                                                                                | Fast power-down (                                                |                    |                 |                |  |  |

|                |                      | 1                   | 0                                                                                                | Internal clock mod                                               |                    |                 |                |  |  |

|                |                      | 1                   | 1                                                                                                | External clock mod                                               | de                 |                 |                |  |  |

### 表2. シングルエンドモードでのチャネル選択(SGL/ $\overline{\text{DIF}}$ = 1)

| SEL2 | SEL1 | SEL0 | CH0 | CH1 | CH2 | CH3 | CH4 | CH5 | CH6 | CH7 | COM |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   |     |     |     |     |     |     |     | -   |

| 1    | 0    | 0    |     | +   |     |     |     |     |     |     | -   |

| 0    | 0    | 1    |     |     | +   |     |     |     |     |     | -   |

| 1    | 0    | 1    |     |     |     | +   |     |     |     |     | -   |

| 0    | 1    | 0    |     |     |     |     | +   |     |     |     | -   |

| 1    | 1    | 0    |     |     |     |     |     | +   |     |     | -   |

| 0    | 1    | 1    |     |     |     |     |     |     | +   |     | -   |

| 1    | 1    | 1    |     |     |     |     |     |     |     | +   | -   |

#### 変換開始方法

変換は制御バイトをDINにクロックインすることで始まり ます。 CSがローの場合、SCLKクロックの各立上りエッジ で、DINからMAX148/MAX149の内部シフトレジスタへ 1ビットずつクロック入力されます。 CSが下がった後で最 初に来たロジック[1]のビットが、制御バイトのMSBを定 義します。この最初の「スタート」ビットが来るまでは、ロジッ ク[0]のビットがいくつDINにクロック入力されたとしても 影響はありません。表1に制御バイトのフォーマットを示し

MAX148/MAX149はSPI/QSPIおよびMICROWIRE デバイスとコンパチブルです。SPIの場合は、SPI制御レジ

スタで正しいクロック極性とサンプリングエッジを選択し て下さい(CPOL = OおよびCPHA = Oに設定して下さい)。 MICROWIRE、SPIおよびQSPIはいずれもバイトの送信 とバイトの受信を同時に行います。「標準動作回路」を用い た場合、最もシンプルなソフトウェアインタフェースでは 8ビット転送を僅か3回行うだけで変換が行えます(1回の 8ビット転送ではADCを設定し、残り2回の8ビット転送で は変換結果をクロック出力します)。MAX148/MAX149 のQSPI接続法については図20を参照して下さい。

### 表3. 差動モードでのチャネル選択(SGL/ $\overline{DIF}$ = 0)

| SEL2 | SEL1 | SEL0 | CH0 | CH1 | CH2 | СНЗ | CH4 | CH5 | CH6 | CH7 |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0    | 0    | +   | -   |     |     |     |     |     |     |

| 0    | 0    | 1    |     |     | +   | -   |     |     |     |     |

| 0    | 1    | 0    |     |     |     |     | +   | -   |     |     |

| 0    | 1    | 1    |     |     |     |     |     |     | +   | -   |

| 1    | 0    | 0    | -   | +   |     |     |     |     |     |     |

| 1    | 0    | 1    |     |     | -   | +   |     |     |     |     |

| 1    | 1    | 0    |     |     |     |     | -   | +   |     |     |

| 1    | 1    | 1    |     |     |     |     |     |     | -   | +   |

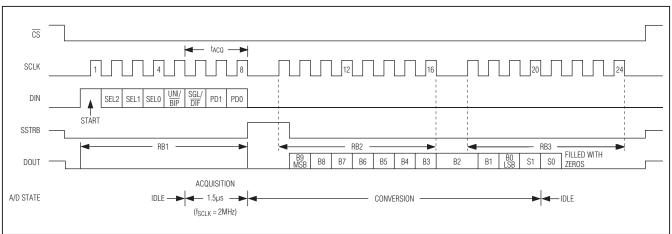

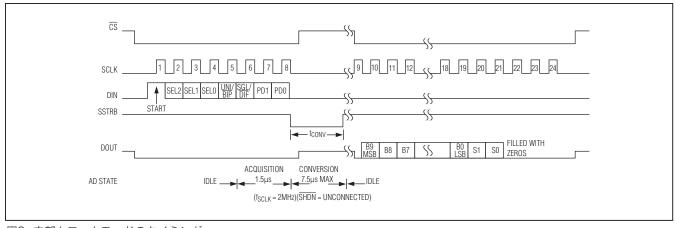

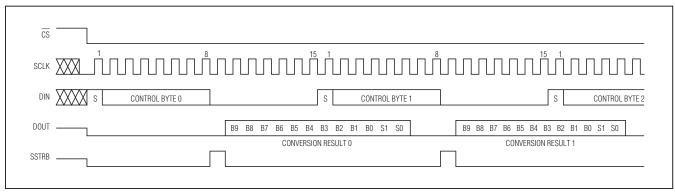

図6. 24クロック外部クロックモードの変換タイミング(MICROWIREおよびSPIコンパチブル、f<sub>SCLK</sub> ≤ 2MHzでQSPIコンパチブル)

#### シンプルなソフトウェアインタフェース

CPUがシリアルクロックを発生するために、CPUのシリアルインタフェースがマスターモードで動作していることを確認して下さい。クロック周波数は100kHz~2MHzの範囲から選択して下さい。

- 1) 制御バイトを外部クロックモードに設定し、これを TB1と呼びます。TB1はバイナリの1XXXXX11という フォーマットになるはずです。ここで、Xは選択された 特定のチャネルおよび変換モードを意味します。

- 2) CPUの汎用I/Oラインを用いて $\overline{CS}$ をローにします。

- 3) TB1を送信し、同時にバイトを受信します。受信した バイトをRB1と呼びます。RB1は無視します。

- 4) 全てゼロで構成されるバイト(\$00 HEX)を送信し、 同時にバイトRB2を受信します。

- 5) 全てゼロで構成されるバイト(\$00 HEX)を送信し、 同時にバイトRB3を受信します。

- 6) CSをハイにします。

図6にこのシーケンスのタイミングを示します。バイトRB2とRB3は、先頭のゼロ1個、2つのサブLSBビットおよび最後の3つのゼロにはさまれた変換結果を含んでいます。総変換時間はシリアルクロック周波数と8ビット転送間のアイドル時間の関数です。T/Hが過剰にドループするのを防ぐために、総変換時間が120µsを超えないようにして下さい。

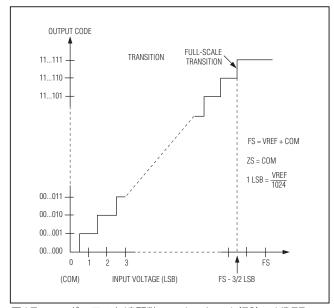

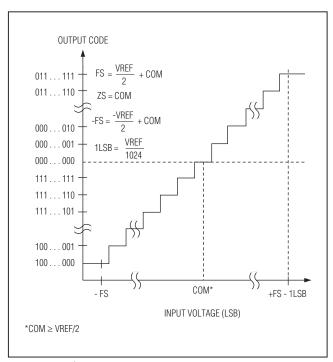

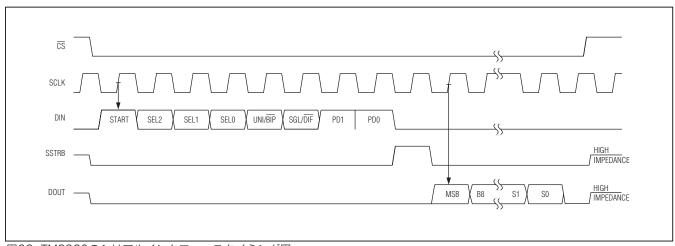

#### ディジタル出力

ユニポーラ入力モードでは、出力はストレートバイナリです (図17)。バイポーラ入力モードでは、出力は2の補数形式になります(図18)。データはSCLKの立下がりエッジで、MSBを先頭にクロック出力されます。

### クロックモード

MAX148/MAX149は外部シリアルクロックまたは内部クロックを用いることで、逐次比較型変換を行うことができます。どちらのクロックモードの場合も、外部クロックがMAX148/MAX149からデータをシフトイン/アウトします。T/Hは制御バイトの最後の3ビットがDINにクロック入力

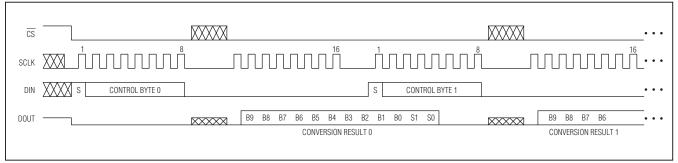

図7. シリアルインタフェースの詳細タイミング

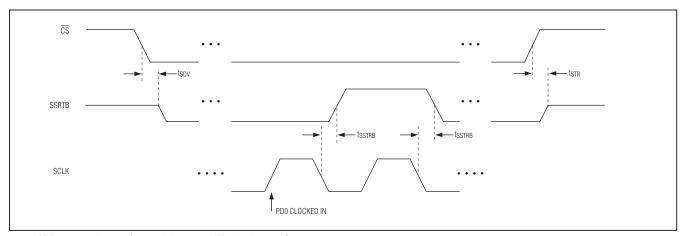

図8. 外部クロックモードでのSSTRBの詳細タイミング

される時に入力信号を取込みます。制御バイトのビットPD1およびPD0がクロックモードをプログラムします。図7~10に両方のモードに共通するタイミング特性を示します。

### 外部クロック

外部クロックモードでは、外部クロックはデータをシフトイン/アウトするだけでなく、アナログディジタル変換ステップの駆動も行います。SSTRBは制御バイトの最後のビットの後で、1クロック周期だけパルス的にハイになります。逐次比較用のビット決定はそれに続くSCLKの立下がりエッジ12個でそれぞれ行われ、DOUTに出力されます

(図6)。 CSがハイになると、SSTRBおよびDOUTはハイインピーダンス状態になります。そして、その次のCSの立下がりエッジでSSTRBはロジックローを出力します。 図8 に外部クロックモードでのSSTRBのタイミングを示します。

変換は一定した最小時間内に完了しなければなりません。 完了しない場合は、サンプルアンドホールドコンデンサの ドループが変換結果を劣化させます。シリアルクロック周 波数が100kHz以下の場合、あるいはシリアルクロックの 中断が原因で変換期間が120µsを超える可能性がある 場合は、内部クロックモードを使用して下さい。

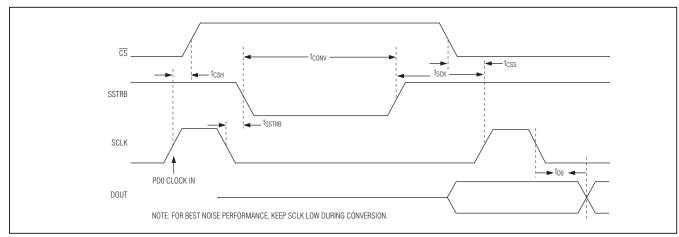

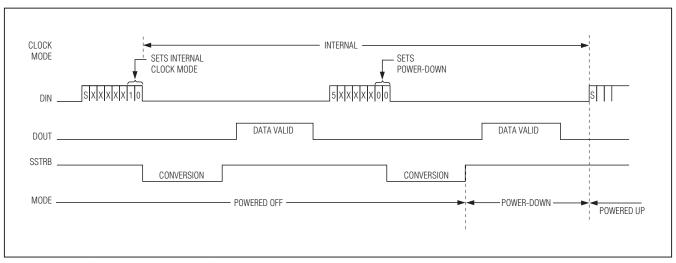

図9. 内部クロックモードのタイミング

図10. 内部クロックモードでのSSTRBの詳細タイミング

### 内部クロック

内部クロックモードでは、MAX148/MAX149自体が変換クロックを内部で発生します。この結果、μPはSAR変換クロックを動作させる役目から解放され、変換結果はプロセッサの都合の良い時に、0~2MHzの任意のクロックレートで読取ることができます。SSTRBは変換開始時にローになり、変換が完了するとハイになります。SSTRBは最大7.5μsの間ローに留まりますが(SHDN = オープン)、最高のノイズ性能を得るためには、その間SCLKをローに保つようにして下さい。

変換が行われている間は内部レジスタがデータを保管します。変換の完了後、任意の時点で、SCLKがこのレジスタからデータをクロック出力します。SSTRBがハイになった後、次の立下がリクロックエッジでDOUTに変換のMSBが出力され、続いて残りのビットがMSBを先頭にしたフォーマットで出力されます(図9)。一旦変換が開始されれば、CSをローに保持する必要はありません。CSをハイにするとデータがMAX148/MAX149にクロック入力さ

れる事を防ぎ、DOUTがスリーステートになりますが、既に 進行中の内部クロックモードの変換に悪影響を与えること はありません。内部クロックモードが選択されている場合、 CSがハイになってもSSTRBはハイインピーダンス状態に はなりません。

図10に内部クロックモードでのSSTRBのタイミングを示します。このモードでは、最小アクイジションタイム(t<sub>ACQ</sub>)が1.5µs以上に保持されている限り、2.0MHz以上のクロックレートでデータをMAX148/MAX149にシフトイン、またはシフトアウトすることができます。

#### データフレーミング

CSの立下がりエッジでは変換は開始されません。DINにクロック入力される最初のロジックハイはスタートビットとして解釈され、これが制御バイトの最初のビットの定義付けを行います。変換は、制御バイトの8番目のビット(PD0ビット)がDINにクロック入力された後のSCLKの立下がりエッジで開始されます。スタートビットの定義は次のとおりです。

| REFERENCE<br>BUFFER | REFERENCE-<br>BUFFER<br>COMPENSATION<br>MODE | VREF<br>CAPACITOR<br>(µF) | POWER-DOWN<br>MODE | POWER-UP DELAY<br>(µs) | MAXIMUM<br>SAMPLING RA <sup>-</sup><br>(ksps) |

|---------------------|----------------------------------------------|---------------------------|--------------------|------------------------|-----------------------------------------------|

| Enabled             | Internal                                     | _                         | Fast               | 5                      | 26                                            |

| Enabled             | Internal                                     | _                         | Full               | 300                    | 26                                            |

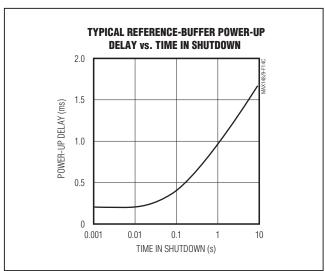

| Enabled             | External                                     | 4.7                       | Fast               | See Figure 14c         | 133                                           |

| Enabled             | External                                     | 4.7                       | Full               | See Figure 14c         | 133                                           |

| Disabled            | _                                            | _                         | Fast               | 2                      | 133                                           |

| Disabled            | _                                            | _                         | Full               | 2                      | 133                                           |

コンバータがアイドル状態である任意の時間(例えば V<sub>DD</sub>が印加された後)にCSがローの状態でDINにクロッ ク入力された最初のハイビット。

#### または

進行中の変換のビット3がDOUTピンにクロック出力 された後にDINにクロックインされた最初のハイビット。

現在の変換が完了する前にCSがトグルされると、その次 にDINにクロック入力されるハイビットがスタートビットと 見なされ、現在の変換は中止され、新しい変換が開始さ れます。

MAX148/MAX149の最高動作速度は、変換中CSがローに 維持されている場合15クロック/変換になります。図11aに、 外部クロックモードで15 SCLKサイクル毎に変換を実行 するために必要なシリアルインタフェースタイミングを示し ます。CSがローに固定され、SCLKが連続的である場合、 スタートビットは最初に16個のゼロをクロック入力するこ とで保証されます。

多くのマイクロコントローラ(µC)の場合、変換は8 SCLK クロックの倍数で起動することが要求されます。従って、 マイクロコントローラによるMAX148/MAX149の最高動作 速度は通常16クロック/変換という事になります。図11bに、 外部クロックモードで16 SCLKサイクル毎に変換を実行する ために必要なシリアルインタフェースタイミングを示します。

### アプリケーション情報

#### パワーオンリセット

最初に電源が入った時にSHDNがローでなければ、パワー オンリセット回路がMAX148/MAX149を内部クロック モードで起動し、SSTRB = ハイの状態で変換を開始できる 準備が整っています。電源が安定した後、内部リセット時間 が10µs必要なため、この間は変換を実行しないで下さい。 SSTRBはパワーアップ時にはハイで、CSがローの場合は、 DINの最初のロジック1がスタートビットと見なされます。 変換が行われるまではDOUTはゼロをシフトアウトします。 表4を参照して下さい。

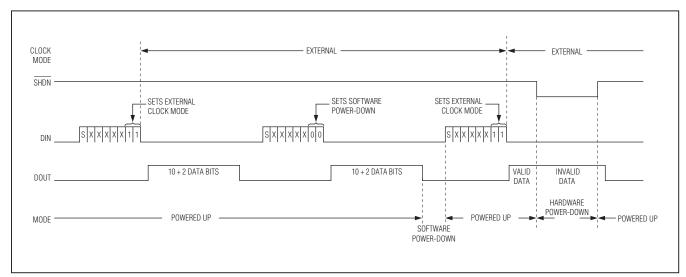

### リファレンスバッファの補償

SHDNは、シャットダウン機能の他に、内部または外部補償 の選択に使用します。この補償は、パワーアップ時間および 最大変換速度の両方に影響します。最小クロックレートは、 補償の状態に関らず、サンプルアンドホールドのドループ のために100kHzに制限されます。

SHDNをオープンにすると、外部補償になります。「標準 動作回路」では、VREFにおいて4.7µFのコンデンサを使 用しています。4.7µFの容量によりリファレンスバッファ の安定性が保証され、2MHzのフルクロック速度の変換 動作が可能になります。外部補償の場合は、パワーアップ 時間が増加します(「パワーダウンモードの選択」の項およ び表4を参照)。

SHDNをハイにすると、内部補償になります。内部補償では VREFの外部コンデンサを必要としないため、パワーアップ 時間を最も短くすることができます。最大クロックレート は、内部クロックモードで2MHz、外部クロックモードで は400kHzです。

### パワーダウンモードの選択

変換と変換の間にコンバータを低電流のシャットダウン状態 にすることにより、電力を節減することができます。フル パワーダウンまたは高速パワーダウンモードを選択するに は、SHDNがハイまたはオープンの状態で、DIN制御バイ トのビット1とビット0を使用します(表1および表5)。いず れのソフトウェアシャットダウンモードでも、シリアルインタ フェースは動作状態に留まりますが、ADCは変換を実行し ません。SHDNをローにすることにより、いつでもコンバー タを完全にシャットダウンすることができます。SHDNは、 制御バイトのビット1とビット0より優先します。

フルパワーダウンモード時には、電流を消費する全ての チップ機能がターンオフされ、消費電流が2µA (typ)に低下 します。高速パワーダウンモードでは、バンドギャップリ ファレンス以外の全ての回路がターンオフされます。高速 パワーダウンモードの消費電流は30µAです。内部補償モー ドでは、パワーアップ時間を5us短縮することができます。

図11a. 外部クロックモード、15クロック/変換のタイミング

図11b. 外部クロックモード、16クロック/変換のタイミング

図12a. パワーダウンモードのタイミング図(外部クロック)

表4は、どのリファレンスバッファ補償およびパワーダウンモードを選択するかによって、パワーアップ遅延および最大サンプリングレートがどのように影響されるかを示しています。外部補償モードにおいて、コンデンサが初めに完全に放電している場合のパワーアップ時間は、4.7µFの補償コンデンサを使用した場合に20msとなります。高速パワーダウンからのスタートアップ時間は、シャットダ

ウン中に1/2 LSB以上放電しない低リークコンデンサを使用することによって完全に無くすことができます。パワーダウン中には、VREFでのリーク電流によって、リファレンスバイパスコンデンサでドループが生じます。図12a および図12bに、外部および内部クロックモード時の様々なパワーダウンシーケンスを示します。

図12b. パワーダウンモードのタイミング図(内部クロック)

### 表5. ソフトウェアパワーダウンおよび クロックモード

| PD1 | PD0 | DEVICE MODE     |  |

|-----|-----|-----------------|--|

| 0   | 0   | Full Power-Down |  |

| 0   | 1   | Fast Power-Down |  |

| 1   | 0   | Internal Clock  |  |

| 1   | 1   | External Clock  |  |

# 表6. 配線固定時のパワーダウンおよび内部クロック周波数

| SHDN<br>STATE | DEVICE<br>MODE | REFERENCE<br>BUFFER<br>COMPENSATION | INTERNAL<br>CLOCK<br>FREQUENCY |

|---------------|----------------|-------------------------------------|--------------------------------|

| 1             | Enabled        | Internal                            | 225kHz                         |

| Unconnected   | Enabled        | External                            | 1.8MHz                         |

| 0             | Power-<br>Down | _                                   | _                              |

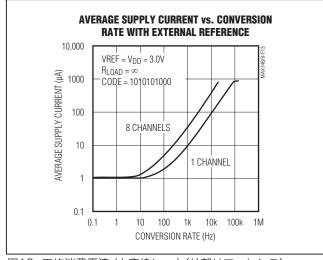

図13. 平均消費電流 対 変換レート(外部リファレンス)

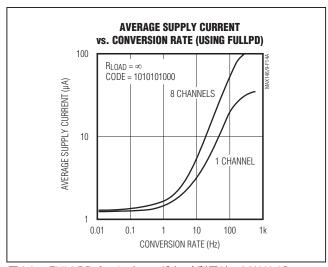

図14a. FULLPD (フルパワーダウン)利用時のMAX149の 消費電流 対 変換レート

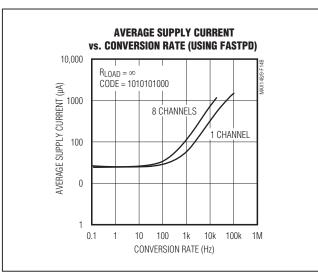

図14b. FASTPD (高速パワーダウン)利用時のMAX149の 消費電流 対 変換レート

図14c.リファレンスバッファの公称パワーアップ遅延 対シャットダウン時間

### ソフトウェアパワーダウン

制御バイトのビットPD1およびPD0を用いることで、ソフトウェアパワーダウンが起動されます。表5に示すように、PD1およびPD0はクロックモードを指定するためにも用いられます。ソフトウェアシャットダウンが発生すると、変換が完了するまでADCは最後に指定されたクロックモードで動作し続けます。その後、ADCはパワーダウンし、低自己消費電流状態になります。内部クロックモードでは、MAX148/MAX149がソフトウェアパワーダウンに入った後でもインタフェースはアクティブ状態を保ち、変換結果をクロック出力することができます。

DINの最初のロジック[1]がスタートビットと見なされ、これによってMAX148/MAX149はパワーアップします。スタートビットに続いて、データ入力ワードまたは制御バイトがやはりクロックモードとパワーダウン状態を決定します。例えば、DINワードがPD1 = 1を含む場合には、製品はパワーアップ状態に留まります。PD0 = PD1 = 0の時は、1回だけ変換を行い、その後再びパワーダウンします。

#### ハードウェアパワーダウン

SHDNがローになると、コンバータはハードウェアパワーダウン状態に入ります(表6)。ソフトウェアパワーダウンモードとは異なり、変換は完了せずに、 $\overline{SHDN}$ がローになった時点で停止します。 $\overline{SHDN}$ は内部クロックモードでのクロック周波数も制御します。 $\overline{SHDN}$ がオープンでは、内部クロック周波数が1.8MHzに設定されます。 $\overline{SHDN}$ がオープン状態で通常動作に戻った場合、約2M $\Omega$  x CLの $\Omega$  に延延時間があります(ここでCLは $\overline{SHDN}$ ピンでの容量性負荷です)。 $\overline{SHDN}$ をハイにすると内部クロック周波数が225kHzに設定されます。この機能はリファレンス電圧によるセトリング時間の必要条件を緩和します。外部リファレンスでは、MAX148/MAX149は $\overline{SHDN}$ がアクティブにハイにされた後2 $\mu$ s以内で完全にパワーアップします。

### パワーダウンシーケンス

最大サンプリングレートよりも遅い速度で動作している場合、MAX148/MAX149を自動パワーダウンモードに設定することで大幅に電力を節減することができます。図13、14aおよび14bに、平均消費電流とサンプリングレートの関係を示します。以下に、様々なパワーダウンシーケンスについて説明します。

#### 最大500変換/チャネル/秒の最低電力動作

以下に、2つのパワーダウンシーケンス例を示します。他の アプリケーションの場合は、これ以外のクロックレート、 補償モードおよびパワーダウンモードの組合せにより最小 の消費電力を実現できることもあります。

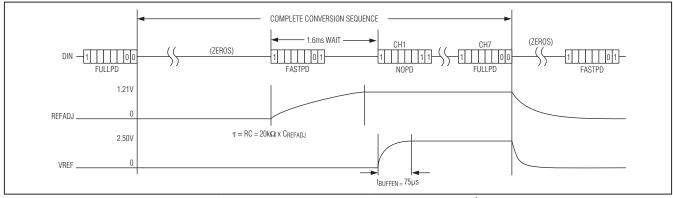

図14aに、フルパワーダウンモードおよび内部リファレンス 補償を使用した場合のMAX149の1または8チャネル変換 に対する消費電力を示します。REFADJの0.01μFのバイパスコンデンサは内部20kΩリファレンス抵抗により、時定数0.2msのRCフィルタを形成します。完全10ビット精度を実現するには、パワーアップ後この時定数の8倍または1.6msが必要です。フルパワーアップモードではなく、高速パワーダウン(FASTPD)モードでこの1.6msを待つことで消費電力を10分の1以下に低減することができます。これは、図15に示すシーケンスにより実行されます。

図15. MAX149のFULLPD (フルパワーダウン)/FASTPD (高速パワーダウン)のパワーアップシーケンス

図16. MAX149リファレンス調整回路

#### 高スループットでの最低電力

図14bは1および8チャネル変換、高速パワーダウン時の外部リファレンス補償での消費電力を示します。外部4.7µF補償は、ダミー変換と共にパワーアップ後75µsのウェイトが必要です。このグラフは可能な限り最小の電力消費で、高速、多チャネル変換を示しています。MAX148/MAX149が長時間動作しないが、断続的な高速バースト変換を必要とするアプリケーションでは、フルパワーダウンモードはより省電力を実現します。

#### 内部および外部リファレンス

MAX148は外部リファレンスを必要としますが、MAX149は内部または外部リファレンス電圧で使用することができます。外部リファレンスはVREFまたはREFADJピンに直接接続することができます。

MAX148およびMAX149では、内部バッファはVREFにおいて2.5Vを生成するよう設計されています。MAX149の内部調整された1.21Vリファレンスは、利得2.06倍でバッファされます。MAX148のREFADJピンは利得2.00倍でバッファされ、REFADJで外部1.25VリファレンスをVREFで2.5Vに拡大します。

図17. ユニポーラの伝達関数、フルスケール(FS) = VREF + COM、ゼロスケール(ZS) = COM

#### 内部リファレンス(MAX149)

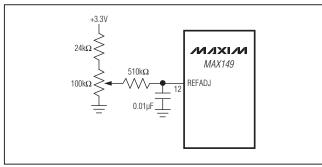

MAX149の内部リファレンスによるフルスケール範囲は、ユニポーラ入力で2.5V、バイポーラ入力で±1.25Vです。内部リファレンス電圧は図16の回路で±1.5%まで調整することができます。

#### 外部リファレンス

MAX148およびMAX149では、外部リファレンスは内部リファレンスバッファアンプの入力(REFADJ)または出力(VREF)に接続することができます。REFADJ入力インピーダンスはMAX149で20k $\Omega$ (typ)、MAX148で100k $\Omega$ 以上です。VREFのDC入力抵抗は最低18k $\Omega$ です。変換期間中、VREFの外部リファレンスは最大350 $\mu$ AのDC負荷

### 表7. フルスケールおよびゼロスケール

| UNIPOL     | AR MODE    | BIPOLAR MODE        |            |                     |

|------------|------------|---------------------|------------|---------------------|

| Full Scale | Zero Scale | Positive Full Scale | Zero Scale | Negative Full Scale |

| VREF + COM | COM        | VREF/2 + COM        | COM        | -VREF/2 + COM       |

図18. バイポーラの伝達関数、フルスケール(FS) = VREF/2 + COM、ゼロスケール(ZS) = COM

電流を供給でき、出力インピーダンスは10Ω以下でなけ ればなりません。リファレンスの出力インピーダンスがこ れより高い場合やノイズが多い場合は、4.7µFのコンデン サでVREFピンの近くでバイパスして下さい。

REFADJ入力を使用すると外部リファレンスをバッファする 必要がなくなります。VREF入力を直接使用する場合は、 REFADJをVDDに接続し内部バッファをディセーブルします。 REFADJがVDDに接続された場合の、パワーダウン時の REFADJへの入力バイアス電流は25µA typ (MAX149) です。パワーダウン時に入力バイアス電流を最低限に抑え るにはREFADJをAGNDに接続して下さい。

図19. 電源グランド接続図

#### 伝達関数

表7にユニポーラおよびバイポーラモードでのフルスケー ル電圧範囲を示します。

民生用温度範囲(0℃~+70℃)で1 LSB以内の精度を達成 するためには、外部リファレンスの温度係数は20ppm/℃ 以下でなければなりません。

図17は通常のユニポーラ入力/出力(I/O)伝達関数を示し ています。図18はバイポーラ入力/出力(I/O)伝達関数を 示しています。コード遷移は隣り合う整数のLSB値の間の 中間点で起こります。出力コーディングはバイナリで、 ユニポーラ動作では1 LSB = 2.44mV (2.500V/1024)、 バイポーラ動作では1 LSB = 2.44mV [(2.500V/2 --2.500V/2)/1024]となります。

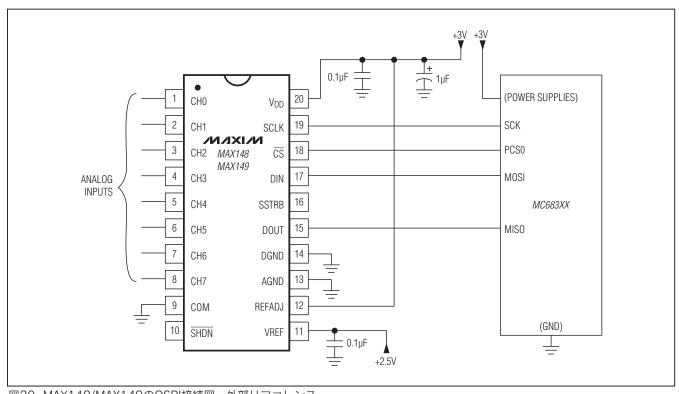

図20. MAX148/MAX149のQSPI接続図、外部リファレンス

図21. MAX148/MAX149からTMS320へのシリアルインタ フェース

### レイアウト、グランドおよびバイパス

最高の性能を得るためにはプリント基板を使用して下 さい。ワイヤラップボードは推奨されません。基板レイア

ウトはディジタル信号ラインとアナログ信号ラインが確実 に分離されるようにして下さい。アナログとディジタル (特にクロック) ラインを互いに並行に走らせないで下さい。 またディジタルラインがADCパッケージの下に来ないよう にして下さい。

図19に推奨されるシステムグランド接続法を示します。 一点アナロググランド(スターグランドポイント)をAGNDの 所で設定し、ロジックグランドとは分離します。その他全ての アナロググランドとDGNDをスターグランドに接続して下 さい。このグランドに他のディジタルシステムグランドを 接続しないで下さい。ノイズを排除するために、スターグ ランドから電源へのグランドリターンはできるだけ短くし、 また、低インピーダンスにして下さい。

VDD電源内の高周波ノイズはADC内の高速コンパレータに 影響を与える可能性があります。この電源はMAX148/ MAX149のピン20に近いところで、0.1μFおよび1μFの コンデンサでスターグランドにバイパスして下さい。最高 の電源ノイズ除去比を得るためには、コンデンサのリード 線をできるだけ短くして下さい。電源のノイズが特に大き い場合は、10Ωの抵抗をローパスフィルタとして接続し て下さい(図19)。

図22. TMS320のシリアルインタフェースタイミング図

#### QSPIとの高速ディジタルインタフェース

図20の回路を用いると、MAX148/MAX149をQSPIとインタフェースさせることができます( $f_{SCLK}$  = 2.0MHz、CPOL = 0、CPHA = 0)。このQSPI回路は8個の各チャネル全てで変換を行うようにプログラムすることができます。QSPIはそれ自体がマイクロシーケンサを備えているため、変換結果はCPUに負担をかけることなくメモリに記憶されます。

MAX148/MAX149はQSPIコンパチブルで、最大外部クロック周波数は2MHzです。

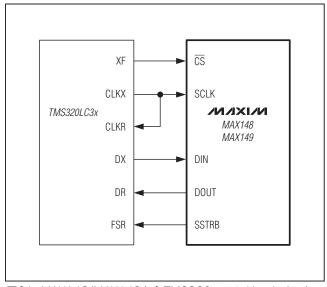

### TMS320LC3xとのインタフェース

図21に外部クロックモードでMAX148/MAX149をTMS320にインタフェースするためのアプリケーション回路を示します。このインタフェースのタイミング図を図22に示します。

MAX148/MAX149の変換動作を初期化し、そして結果を読み取るための手順は次のとおりです。

1) TMS320はCLKX (送信クロック)がアクティブハイ出 カクロック、CLKR (TMS320受信クロック)がアクティ ブハイ入カクロックとなるように設定して下さい。 TMS320の CLKXと CLKR は MAX148/MAX149の SCLK入力と共に接続されます。

- 2) MAX148/MAX149の $\overline{\text{CS}}$ ピンはTMS320のXF\_I/Oポートによってローにされ、MAX148/MAX149のDINにデータがクロック入力できるようになります。

- 3) 変換を開始するために8ビットワード(1XXXXX11)を MAX148/MAX149に書き込み、デバイスを外部クロックモードに設定します。特定のアプリケーションに適したXXXXXビットを選択するためには、表1を参照して下さい。

- 4) MAX148/MAX149のSSTRB出力はTMS320のFSR 入力を通じて監視されます。SSTRB出力の立下がり エッジは、変換が進行中でデータをMAX148/MAX149 から受け取る準備ができていることを示します。

- 5) TMS320は続くSCLK 16個の各立上りエッジで1データ ビットずつ読み込みます。これらのデータビットは 10 + 2ビットの変換結果と後に続く4ビットを表してい ます。この後に続く4ビットは無視して下さい。

- 6) 次の変換が開始されるまでは<del>CS</del>をハイにし、MAX148/ MAX149をディセーブルします。

| <b>PART</b> †  | TEMP RANGE      | PIN-<br>PACKAGE | INL<br>(LSB |

|----------------|-----------------|-----------------|-------------|

| MAX148AEPP     | -40°C to +85°C  | 20 Plastic DIP  | ±1/2        |

| MAX148BEPP     | -40°C to +85°C  | 20 Plastic DIP  | ±1          |

| MAX148AEAP     | -40°C to +85°C  | 20 SSOP         | ±1/2        |

| MAX148BEAP     | -40°C to +85°C  | 20 SSOP         | ±1          |

| MAX148AMJP     | -55°C to +125°C | 20 CERDIP*      | ±1/2        |

| MAX148BMJP     | -55°C to +125°C | 20 CERDIP*      | ±1          |

| MAX149ACPP     | 0°C to +70°C    | 20 Plastic DIP  | ±1/2        |

| MAX149BCPP     | 0°C to +70°C    | 20 Plastic DIP  | ±1          |

| MAX149ACAP     | 0°C to +70°C    | 20 SSOP         | ±1/2        |

| MAX149BCAP     | 0°C to +70°C    | 20 Plastic DIP  | ±1          |

| MAX149AEPP     | -40°C to +85°C  | 20 Plastic DIP  | ±1/2        |

| MAX149BEPP     | -40°C to +85°C  | 20 Plastic DIP  | ±1          |

| MAX149AEAP     | -40°C to +85°C  | 20 SSOP         | ±1/2        |

| MAX149BEAP     | -40°C to +85°C  | 20 SSOP         | ±1          |

| MAX149AMJP     | -55°C to +125°C | 20 CERDIP*      | ±1/2        |

| MAX149BMAP/PR  | -55°C to +125°C | 20 SSOP         | ±1          |

| MAX149BMAP/PR2 | -55°C to +125°C | 20 SSOP         | ±1          |

| MAX149BMAP/PR3 | -55°C to +125°C | 20 SSOP         | ±1          |

| MAX149BMJP     | -55°C to +125°C | 20 CERDIP*      | ±1          |

|                |                 |                 |             |

†代替の表面実装パッケージの供給性についてはお問い合わせ 下さい。鉛フリー対応品は、オーダー時に型番末尾に[+]を 付加して下さい。

\*CERDIPパッケージ、MIL-STD-883B製品の供給性については お問い合わせ下さい。鉛フリー対応品は提供されていません。

### ピン配置

### パッケージ

最新のパッケージ図面情報およびランドパターンはjapan. maxim-ic.com/packages を参照してください。なお、 パッケージコードに含まれる[+]、[#]、または[-]は RoHS対応状況を表したものでしかありません。パッケージ 図面はパッケージそのものに関するものでRoHS対応 状況とは関係がなく、図面によってパッケージコードが 異なることがある点を注意してください。

| パッケージタイプ       | パッケージコード | ドキュメントNo.      |

|----------------|----------|----------------|

| 20 Plastic Dip | P20-4    | 21-0043        |

| 20 SSOP        | A20-1    | <u>21-0056</u> |

| 20 CERDIP      | J20-2    | <u>21-0045</u> |

### 改訂履歴

| 版数 | 改訂日  | 説明                                                                           | 改訂ページ                            |

|----|------|------------------------------------------------------------------------------|----------------------------------|

| 3  | 5/09 | 「型番」、「Electrical Characteristics (電気的特性)」の表、「端子説明」、<br>図9を改訂し、頑丈なプラスティックを追加。 | 1–4, 7, 13, 14, 16, 17,<br>22–23 |

| 4  | 1/10 | 「型番」を改訂。                                                                     | 22                               |

マキシム·ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは随時予告なく回路及び仕様を変更する権利を留保します。