#

# 40V、高性能、同期バックコントローラ

### 概要

同期ステップダウンコントローラのMAX15046は、 4.5V~40Vの入力電圧範囲で動作し、最大25Aの負荷に 対応しつつ、入力電圧の85%から最低0.6Vまでの可変の 出力電圧を生成します。このデバイスは、出力の放電なし にプリバイアスされたバスでの単調性起動が可能で、適応 型内蔵デジタルソフトスタートを備えています。

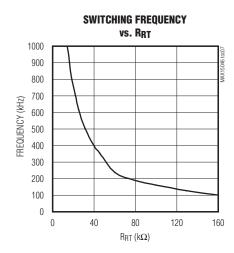

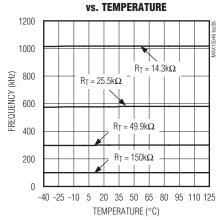

MAX15046は、外付け抵抗によってスイッチング周波数を 100kHz~1MHzに調整することができます。MAX15046 の適応型同期整流によって、外付けのフリーホイール ショットキーダイオードが不要になります。また、このデバ イスは外付けのローサイドMOSFETのオン抵抗を電流 検出素子として利用するため、電流検出抵抗も不要です。 これによって、電流検出抵抗を必要とせずに、DC-DC部品 を出力過電圧状態または出力短絡フォルト時の損傷から 保護されます。ヒカップモード電流制限は、短絡状態時の 電力損失を低減します。MAX15046は、正確なターンオン/ ターンオフスレッショルドの1つのパワーグッド出力と1つ のイネーブル入力を備えており、入力電源監視および電源 シーケンスに使用することができます。

その他の保護機能として、シンクモード電流制限とサーマ ルシャットダウンがあります。シンクモード電流制限は、 デバイスが出力から電流をシンクするときに、逆インダクタ 電流が危険なレベルに達するのを防止します。

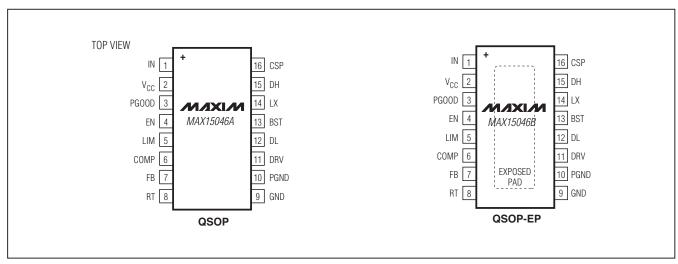

MAX15046は16ピンQSOPまたは16ピンQSOP-EPパッ ケージで提供され、-40℃~+125℃の温度範囲で動作し ます。

ピン配置はデータシートの最後に記載されています。

### 特長

- ◆ 入力電圧範囲: 4.5V~40Vまたは5V ±10%

- ◆ 可変出力: V<sub>IN</sub> x 0.85~0.6V

- ◆ 可変スイッチング周波数(100kHz~1MHz)、±10% (1MHz)の精度

- ◆ 適応型デジタルソフトスタート内蔵

- ◆ 出力性能: 25A (max)

- ◆ 可変温度補償スレッショルド(30mV~300mV)内蔵、 サイクル単位の谷モード電流制限

- ◆ プリバイアス出力への単調性起動

- ◆ 電圧リファレンス精度:±1%

- ◆ 3Aピークゲートドライバ

- ◆ ヒカップモード短絡保護

- ◆ 温度過昇シャットダウン

- ◆ ±5%精度のスレッショルドを備えたパワーグッド (PGOOD)出力およびイネーブル入力(EN)

- ◆ 放熱特性を高めた16ピンQSOPパッケージ

### アプリケーション

産業用電源(PLC、産業コンピュータ、フィールドバス コンポーネント、フィールドバス結合器)

テレコム電源

基地局

### 型番

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX15046AAEE+ | -40°C to +125°C | 16 QSOP     |

| MAX15046BAEE+ | -40°C to +125°C | 16 QSOP-EP* |

+は鉛(Pb)フリー/RoHS準拠パッケージを表します。 \*EP = エクスポーズドパッド

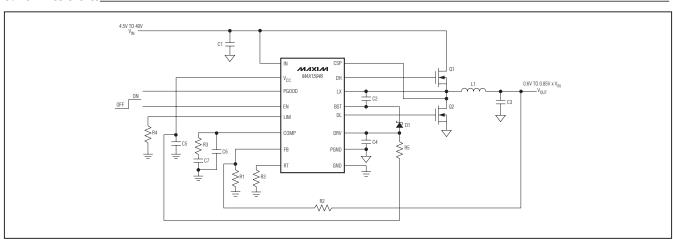

### 標準動作回路

Maxim Integrated Products 1

| 4.0 |                           |                                        |

|-----|---------------------------|----------------------------------------|

| 9   | ABSOLUTE MAXIMU           | M RATINGS                              |

| 4   | IN to GND                 | 0.3V to +45V                           |

| 0   | VCC to GND0.3V            | to lower of $(V_{IN} + 0.6V)$ and $6V$ |

| Ŋ   | EN, DRV to GND            | 0.3V to +6V                            |

| 7   |                           | 0.3V to +45V                           |

|     |                           | 0.3V to +0.3V                          |

| ~   |                           | 0.3V to (V <sub>DRV</sub> + 0.3V)      |

| d   |                           | 0.3V to +50V                           |

| MA  |                           | 1V to +45V                             |

|     | LX and CSP to PGND        |                                        |

|     |                           | 0.3V to +6V                            |

|     |                           | 0.3V to +0.3V                          |

|     |                           | 0.3V to (V <sub>BST</sub> + 0.3V)      |

|     |                           | 0.3V to (V <sub>CC</sub> + 0.3V)       |

|     |                           | Continuous                             |

|     | PGOOD Maximum Sink Curren | t20mA                                  |

| Continuous Power Dissipation (TA = +70°C):               |              |

|----------------------------------------------------------|--------------|

| 16-Pin QSOP (derate 9.6mW/°C above +70°C)                | 771.5mW      |

| 16-Pin QSOP-EP (derate 22.7mW/°C above +70°C             | C) 1818.2mW  |

| Junction-to-Case Thermal Resistance ( $\theta$ JC) (Note | 1)           |

| 16-Pin QSOP                                              | 37°C/W       |

| 16-Pin QSOP-EP                                           | 6°C/W        |

| Junction-to-Ambient Thermal Resistance (θJA) (No         | ote 1)       |

| 16-Pin QSOP                                              | 103.7°C/W    |

| 16-Pin QSOP-EP                                           |              |

| Operating Temperature Range40°                           | °C to +125°C |

| Junction Temperature                                     | +150°C       |

| Storage Temperature Range65°                             | °C to +150°C |

| Lead Temperature (soldering, 10s)                        | +300°C       |

| Soldering Temperature (reflow)                           | +260°C       |

|                                                          |              |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://japan.maxim-ic.com/thermal-tutorial">http://japan.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VIN = 24V, VEN = 5V, VGND = VPGND = 0V, CIN = 1\mu F, CVCC = 4.7\mu F, RRT = 49.9k\Omega, TA = TJ = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                              | PARAMETER SYMBOL CONDITIONS |                                                                                           | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

| SYSTEM SPECIFICATIONS                  |                             |                                                                                           |      |      |      |       |

| Leavit Valta de Davis                  | \                           |                                                                                           | 4.5  |      | 40   | V     |

| Input-Voltage Range                    | VIN                         | VIN = VCC = VDRV                                                                          | 4.5  |      | 5.5  | V     |

| Quiescent Supply Current               | I <sub>IN_Q</sub>           | V <sub>IN</sub> = 24V, V <sub>FB</sub> = 0.9V, no switching                               |      | 2    | 3    | mA    |

| Shutdown Supply Current                | I <sub>IN_SBY</sub>         | V <sub>IN</sub> = 24V, V <sub>EN</sub> = 0V, I <sub>VCC</sub> = 0,<br>PGOOD = unconnected |      | 0.35 | 0.55 | mA    |

| V <sub>CC</sub> REGULATOR              |                             |                                                                                           |      |      |      |       |

| Output Voltage                         | Vcc                         | $6V \le V_{IN} \le 40V$ , $I_{LOAD} = 6mA$                                                | 5    | 5.25 | 5.5  | V     |

| VCC Regulator Dropout                  |                             | V <sub>IN</sub> = 4.5V, I <sub>LOAD</sub> = 25mA                                          |      | 0.18 | 0.45 | V     |

| VCC Short-Circuit Output Current       |                             | VIN = 5V                                                                                  | 30   | 55   | 90   | mA    |

| VCC Undervoltage Lockout               | VCCUVLO                     | V <sub>CC</sub> rising                                                                    | 3.8  | 4    | 4.2  | V     |

| VCC Undervoltage Lockout<br>Hysteresis |                             |                                                                                           |      | 400  |      | mV    |

| ERROR AMPLIFIER (FB, COMP)             |                             |                                                                                           |      |      |      |       |

| FB Input-Voltage Set Point             | V <sub>FB</sub>             |                                                                                           | 584  | 590  | 596  | mV    |

| FB Input Bias Current                  | IFB                         | VFB = 0.6V                                                                                | -250 |      | +250 | nA    |

| FB to COMP Transconductance            | дм                          | ICOMP = ±20µA                                                                             | 600  | 1200 | 1800 | μS    |

| Open-Loop Gain                         |                             |                                                                                           |      | 80   |      | dB    |

| Unity-Gain Bandwidth                   |                             | Capacitor from COMP to GND = 47pF                                                         |      | 5    |      | MHz   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=24V, V_{EN}=5V, V_{GND}=V_{PGND}=0V, C_{IN}=1\mu F, C_{VCC}=4.7\mu F, R_{RT}=49.9k\Omega, T_{A}=T_{J}=-40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ .) (Note 2)

| PARAMETER                              | SYMBOL                   | СО                                                       | NDITIONS                     | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|--------------------------|----------------------------------------------------------|------------------------------|------|------|------|-------|

| VCOMP-RAMP Minimum Voltage             |                          |                                                          |                              |      | 200  |      | mV    |

| COMP Source/Sink Current               | ICOMP                    | VCOMP = 1.4V                                             |                              | 50   | 80   | 110  | μΑ    |

| ENABLE (EN)                            |                          |                                                          |                              | •    |      |      |       |

| EN Input High                          | VEN_H                    | V <sub>EN</sub> rising                                   |                              | 1.14 | 1.20 | 1.26 | V     |

| EN Input Low                           | VEN_L                    | VEN falling                                              |                              |      | 1.05 |      | V     |

| EN Input Leakage Current               | IEN                      | V <sub>EN</sub> = 5.5V                                   |                              | -1   |      | +1   | μΑ    |

| OSCILLATOR                             |                          |                                                          |                              |      |      |      |       |

| Switching Frequency (100kHz)           | fsw                      | $R_{RT} = 150 k\Omega$                                   |                              | 80   | 100  | 120  | kHz   |

| Switching Frequency (300kHz)           | fsw                      | $R_{RT} = 49.9 k\Omega$                                  |                              | 270  | 300  | 330  | kHz   |

| Switching Frequency (1MHz)             | fsw                      | $R_{RT} = 14.3 k\Omega$                                  |                              | 0.9  | 1    | 1.1  | MHz   |

| Switching Frequency Adjustment Range   |                          | (Note 3)                                                 |                              | 100  |      | 1000 | kHz   |

| RT Voltage                             | V <sub>RT</sub>          | $R_{RT} = 49.9 k\Omega$                                  |                              | 1.15 | 1.2  | 1.25 | V     |

| PWM MODULATOR                          |                          | •                                                        |                              | '    |      |      |       |

| PWM Ramp Peak-to-Peak<br>Amplitude     | VRAMP                    |                                                          |                              |      | 1.5  |      | V     |

| PWM Ramp Valley                        | VVALLEY                  |                                                          |                              |      | 1.5  |      | V     |

| Minimum Controllable On-Time           |                          |                                                          |                              |      | 70   | 125  | ns    |

| Maximum Duty Cycle                     |                          | $f_{SW} = 300 \text{kHz} (R_{RT} = 49.9 \text{k}\Omega)$ |                              | 85   | 87.5 |      | %     |

| Minimum Low-Side On-Time               |                          | fsw = 1MHz (R                                            | $RT = 14.3k\Omega$ )         |      | 110  |      | ns    |

| <b>OUTPUT DRIVERS/DRIVERS SUI</b>      | PPLY (V <sub>DRV</sub> ) |                                                          |                              |      |      |      |       |

| Undervoltage Lockout                   | VDRV_UVLO                | VDRV rising                                              |                              | 4.0  | 4.2  | 4.4  | V     |

| DRV Undervoltage Lockout<br>Hysteresis |                          |                                                          |                              |      | 400  |      | mV    |

| DUO B : I                              |                          | Low, sinking 10<br>VBST - VLX = 5\                       |                              |      | 1    | 3    |       |

| DH On-Resistance                       |                          | High, sourcing VBST - VLX = 5\                           | •                            |      | 1.5  | 4    |       |

|                                        |                          | Low, sinking 10<br>VDRV = VCC = 9                        |                              |      | 1    | 3    | Ω     |

| DL On-Resistance                       |                          | High, sourcing VDRV = VCC = \$                           |                              |      | 1.5  | 4    |       |

| DUD 10                                 |                          | 0 10 5                                                   | Sinking,<br>VBST - VLX = 5V  |      | 3    |      |       |

| DH Peak Current                        |                          | CLOAD = 10nF                                             | Sourcing,<br>VBST - VLX = 5V |      | 2    |      | А     |

# **★ ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=24V, V_{EN}=5V, V_{GND}=V_{PGND}=0V, C_{IN}=1\mu F, C_{VCC}=4.7\mu F, R_{RT}=49.9k\Omega, T_{A}=T_{J}=-40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 2)

| PARAMETER                                                    | SYMBOL           | CO                                                                       | NDITIONS                                                       | MIN | TYP  | MAX  | UNITS               |  |

|--------------------------------------------------------------|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|-----|------|------|---------------------|--|

| DL Peak Current                                              |                  | Cuana 10nE                                                               | Sinking, VDRV = VCC<br>= 5.25V                                 |     | 3    |      | Α                   |  |

| DE Peak Current                                              |                  | CLOAD = 10nF                                                             | Sourcing, VDRV = VCC = 5.25V                                   |     | 2    |      |                     |  |

| DH, DL Break-Before-Make Time (Dead Time)                    |                  |                                                                          |                                                                |     | 10   |      | ns                  |  |

| SOFT-START                                                   |                  |                                                                          |                                                                |     |      |      |                     |  |

| Soft-Start Duration                                          |                  |                                                                          |                                                                |     | 2048 |      | Switching Cycles    |  |

| Reference Voltage Steps                                      |                  |                                                                          |                                                                |     | 64   |      | Steps               |  |

| CURRENT LIMIT/HICCUP                                         |                  |                                                                          |                                                                |     |      |      |                     |  |

| Cycle-by-Cycle Valley Current-<br>Limit Threshold Adjustment |                  | VCSP - VPGND, valley limit =                                             | V <sub>LIM</sub> = 0.3V                                        |     | 30   |      | - mV                |  |

| Range                                                        |                  | VLIM/10                                                                  | V <sub>LIM</sub> = 3V                                          |     | 300  |      | 1111                |  |

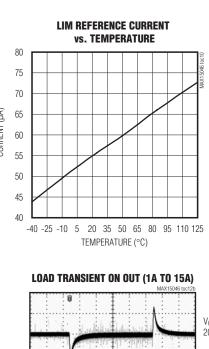

| LIM Reference Current                                        | I <sub>LIM</sub> | $V_{LIM} = 0.3V \text{ to } 3$                                           | $BV, T_A = +25^{\circ}C$                                       | 45  | 50   | 55   | μΑ                  |  |

| LIM Reference Current<br>Temperature Coefficient             |                  |                                                                          |                                                                |     | 2300 |      | ppm/°C              |  |

| CSP Input Bias Current                                       |                  | VCSP = 40V                                                               |                                                                | -1  |      | +1   | μΑ                  |  |

| Number of Consecutive Current-<br>Limit Events to Hiccup     |                  |                                                                          |                                                                |     | 7    |      | Events              |  |

| Hiccup Timeout                                               |                  |                                                                          |                                                                |     | 4096 |      | Switching<br>Cycles |  |

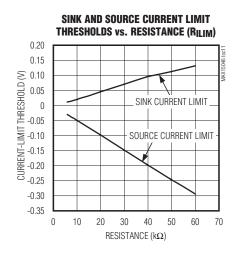

| Peak Low-Side Sink Current-Limit Threshold                   |                  | $V_{CSP}$ - $V_{PGND}$ , $R_{ILIM} = 30k\Omega$ , $V_{A} = +25^{\circ}C$ | sink limit = V <sub>LIM</sub> /20,<br>/ <sub>LIM</sub> = 1.5V, |     | 75   |      | mV                  |  |

| POWER-GOOD (PGOOD)                                           |                  | 1                                                                        |                                                                |     |      |      |                     |  |

| PGOOD Threshold                                              |                  | V <sub>FB</sub> rising                                                   |                                                                | 90  | 94   | 97.5 | %V <sub>FB</sub>    |  |

| PGOOD Threshold Hysteresis                                   |                  | VFB falling                                                              |                                                                |     | 2.65 |      | %VFB                |  |

| PGOOD Output Low Voltage                                     | Vpgood_l         | IPGOOD = 2mA                                                             | , V <sub>EN</sub> = 0V                                         |     |      | 0.4  | V                   |  |

| PGOOD Output Leakage Current                                 | ILEAK_PGOOD      | VPGOOD = 40V                                                             | , V <sub>EN</sub> = 5V, V <sub>FB</sub> = 1V                   | -1  |      | +1   | μΑ                  |  |

| THERMAL SHUTDOWN                                             |                  |                                                                          |                                                                |     |      |      |                     |  |

| Thermal Shutdown Threshold                                   |                  | Temperature ris                                                          | sing                                                           |     | +150 |      | °C                  |  |

| Thermal Shutdown Hysteresis                                  |                  |                                                                          |                                                                |     | 20   |      | °C                  |  |

Note 2: All devices are 100% tested at room temperature and guaranteed by design over the specified temperature range. Note 3: Select R<sub>RT</sub> as:  $R_{RT} = \frac{17.3 \times 10^9}{f_{SW} + (1 \times 10^{-7})(f_{SW}^2)}$ , where  $f_{SW}$  is in Hertz.

MIXIM

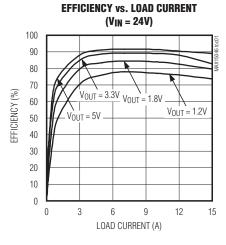

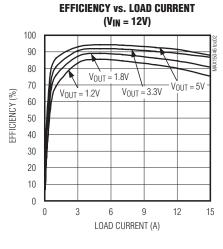

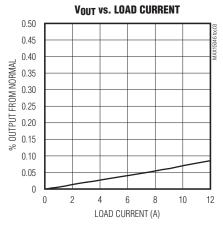

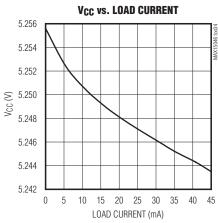

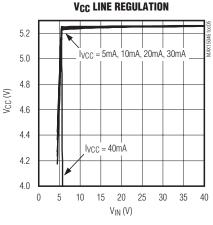

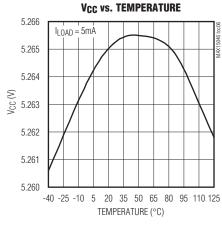

### 標準動作特性

$(V_{IN} = 24V, T_A = +25^{\circ}C, unless otherwise noted.)$

**SWITCHING FREQUENCY**

# *MAX15046*

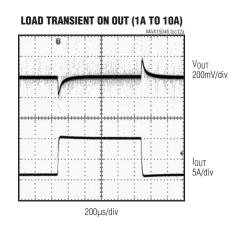

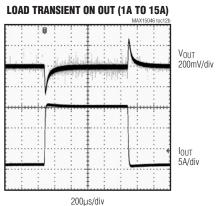

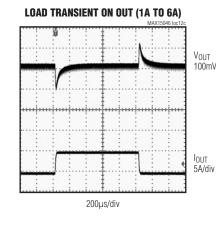

## 標準動作特性(続き)

$(V_{IN} = 24V, T_A = +25^{\circ}C, unless otherwise noted.)$

### 標準動作特性(続き)

$(VIN = 24V, TA = +25^{\circ}C, unless otherwise noted.)$

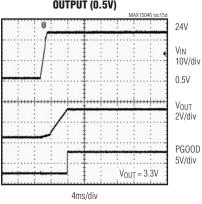

STARTUP WITH PREBIASED

10V/div 2V  $V_{\text{OUT}}$ 2V/div PG00D 5V/div  $V_{OUT} = 3.3V$ 4ms/div

STARTUP WITH PREBIASED **OUTPUT (0.5V)**

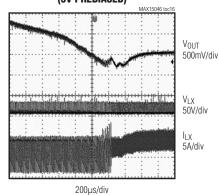

SINK CURRENT-LIMIT WAVEFORMS (5V PREBIASED)

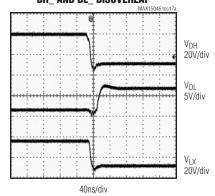

DH\_ AND DL\_ DISOVERLAP

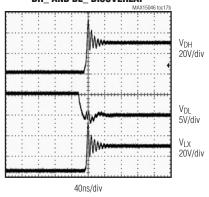

DH\_ AND DL\_ DISOVERLAP

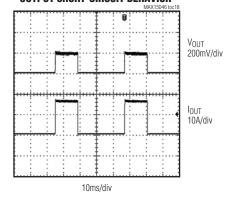

**OUTPUT SHORT-CIRCUIT BEHAVIOR**

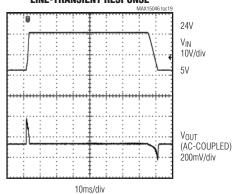

**LINE-TRANSIENT RESPONSE**

| 端子 | 名称    | 機能                                                                                                                                                         |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | IN    | レギュレータ入力。バックコンバータの入力レイルに接続してください。100nF (min)のセラミッコンデンサで、INをPGNDにバイパスしてください。5V ±10%の範囲で動作させる場合は、INをVccに接続してください。                                            |

| 2  | Vcc   | $5.25$ Vリニアレギュレータ出力。 $V_{CC}$ がDRVからMOSFETゲートドライバ電流を供給する場合は少なくとも $4.7\mu$ F、 $V_{CC}$ をDRVへの給電に使用しない場合は $2.2\mu$ Fのセラミックコンデンサで、 $V_{CC}$ をPGNDにバイパスしてください。 |

| 3  | PGOOD | オープンドレインのパワーグッド出力。外付けの抵抗で、PGOODを外部の電源または出力にプルアップしてください。                                                                                                    |

| 4  | EN    | アクティブハイのイネーブル入力。バックコンバータの出力をディセーブルするには、ENをGNDに<br>してください。常時オンの動作とする場合は、V <sub>CC</sub> に接続してください。ENは、電源シーケンス用ま<br>びUVLO調整入力として使用することができます。                 |

| 5  | LIM   | 電流制限入力。LIMとGNDの間に抵抗を接続して、電流制限スレッショルドを $30mV$ ( $R_{LIM}=6k\Omega$ ) $300mV$ ( $R_{LIM}=60k\Omega$ )に設定してください。                                              |

| 6  | COMP  | エラーアンプ出力。COMPとFBの間またはCOMPとGNDの間に補償回路を接続してください。                                                                                                             |

| 7  | FB    | フィードバック入力(エラーアンプの反転入力)。バックコンバータの出力とGNDの間の抵抗分圧器FBを接続して、出力電圧を0.6V~IN x 0.85に調整してください。                                                                        |

| 8  | RT    | 発振器タイミング抵抗入力。RTとGNDの間に抵抗を接続して、発振器の周波数を100kHz~1MIに設定してください。                                                                                                 |

| 9  | GND   | アナロググランド。PGNDとAGNDを1点で相互に接続してください。                                                                                                                         |

| 10 | PGND  | 電源グランド。ローサイドMOSFETゲートドライバのリターン経路としてPGNDを使用してください                                                                                                           |

| 11 | DRV   | ゲートドライバ電源電圧。DRVは内部でローサイドドライバ電源に接続されています。2.2μF (mir セラミックコンデンサで、DRVをPGNDにバイパスしてください(「標準アプリケーション回路」を参                                                        |

| 12 | DL    | ローサイド外付けMOSFETゲートドライバ出力。DLのスイング範囲はDRV~PGNDです。                                                                                                              |

| 13 | BST   | ブーストフライングコンデンサ接続。内部でハイサイドドライバ電源に接続されています。BSTとL間に少なくとも100nFのセラミックコンデンサを、BSTとDRVの間にダイオードを接続して、ハイイドMOSFETゲートドライバに給電してください。                                    |

| 14 | LX    | インダクタ接続。ハイサイドMOSFETドライバ電流のリターン端子としての役割も果たします。LX<br>インダクタのスイッチング側に接続してください。                                                                                 |

| 15 | DH    | ハイサイド外付けMOSFETゲートドライバ出力。DHのスイング範囲はBST~LXです。                                                                                                                |

| 16 | CSP   | 電流検出の正の入力。ローサイドMOSFETのドレインにケルビン接続を行ってください。                                                                                                                 |

| _  | EP    | エクスポーズドパッド。EPは、内部でグランドに接続されています。最大の放熱性能を実現するため<br>EPを大面積の銅グランドプレーンに接続してください。                                                                               |

N/IXI/N

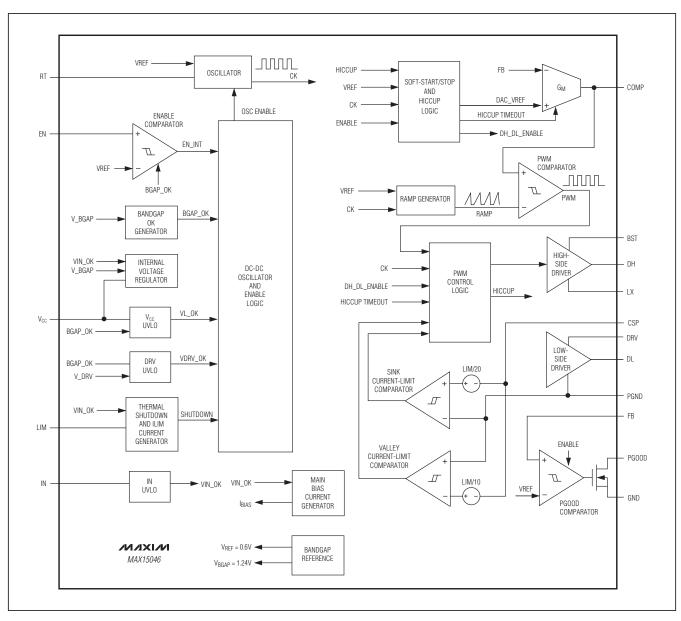

## ファンクションダイアグラム

同期ステップダウンコントローラのMAX15046は、4.5V ~40Vの入力電圧範囲で動作し、0.6V~入力電圧の ■ 85%の可変出力電圧を生成して、最大25Aの負荷に対応 ▶ します。デバイスの電源電圧が5.0V~5.5Vの範囲内であ ★ る限り、入力電源バス(V<sub>IN</sub>)は最低3.3Vまで下げることが 可能です。

MAX15046は、外付け抵抗を使用して100kHz~1MHz のスイッチング周波数をプログラムできます。可変スイッ チング周波数によって、受動部品の選択に関して設計の柔軟 性が提供されます。MAX15046は適応型同期整流を採用 しているため、外付けのフリーホイールショットキーダイ オードが不要で、効率が向上しています。このデバイスは、 外付けローサイドMOSFETのオン抵抗を、電流検出素子 として利用します。電流制限スレッショルド電圧は抵抗で 30mV~300mVに調整可能で、温度変化によるMOSFET のRDS(ON)の変動の影響を低減するための温度補償を 備えています。この電流検出方式によって、電流検出抵抗を 必要とせずに出力過電圧状態や出力短絡フォルト時の損傷 から外部の部品が保護されます。ヒカップモード電流制限 は、短絡状態時の電力損失を低減します。MAX15046は、 監視および電源シーケンスに使用するための、正確なターン オン/オフスレッショルドのパワーグッド出力とイネーブル 入力を備えています。

MAX15046は、出力の放電なしにプリバイアススタート アップを実現するデジタルソフトスタートを内蔵しています。 デジタルソフトスタート機能は、シンク電流制限の採用に よって、設定された安定状態レギュレーションレベルをプリ バイアス電圧が上回る場合にレギュレータが過剰な電流 をシンクすることを防止しています。デジタルソフトスタート 機能は、レギュレータが出力から電流をシンクしていると きに、同期整流MOSFETおよびハイサイドMOSFETの ボディダイオードが危険な電流レベルになるのを防止し ます。MAX15046は接合部温度+150℃でシャットダウン して、デバイスの損傷を防止します。

### DC-DC PWMコントローラ

MAX15046ステップダウンコントローラは、PWM電圧 モード制御方式を使用しています(「ファンクションダイアグ ラム」を参照)。動作周波数および出力LCフィルタ部品の 選択について最大限の柔軟性を提供するために、制御 ループの補償は外部で行うようになっています。内蔵の トランスコンダクタンスエラーアンプは、DC精度の向上 に役立つ積分された誤差電圧をCOMPに生成します。 COMPの電圧によって、PWMコンパレータおよびランプ ジェネレータを使用してデューティサイクルが設定されます。 内部クロックの立上りエッジでハイサイドnチャネル MOSFETがターンオンして、適切なデューティサイクルまた は最大デューティサイクルのいずれかに到達するまでオン のままになります。ハイサイドMOSFETのオン時間の間、 インダクタ電流が漸増します。スイッチングサイクルの後半 は、ハイサイドMOSFETがターンオフしてローサイドnチャ ネルMOSFETがターンオンします。インダクタ電流の漸減 とともにインダクタは蓄積されたエネルギーを解放して、 出力に電流を供給します。プログラムされた谷電流制限 スレッショルド(「電流制限回路(LIM)」の項を参照)をイン ダクタ電流が上回る過負荷条件下では、後続のクロック 立上りエッジでハイサイドMOSFETがターンオンせず、ロー サイドMOSFETがオンのままになってインダクタ電流を漸減 させます。

### 内蔵5.25Vリニアレギュレータ

内蔵リニアレギュレータ(V<sub>CC</sub>)は公称5.25Vの電源を提供 して、内部機能への給電とローサイドMOSFETの駆動を行 います。5V ±10%の外部電源を使用する場合は、INと VCCを相互に接続してください。レギュレータの最大入力 電圧 $(V_{IN})$ は40Vです。 $1\mu$ Fのセラミックコンデンサで、IN をGNDにバイパスしてください。4.7µFのセラミックコン デンサで、リニアレギュレータの出力(Vcc)をGNDにバイ パスしてください。Vccのドロップアウト電圧は180mV (typ) です。V<sub>IN</sub>が5.5Vより高い場合、V<sub>CC</sub>は5.25V (typ)にな ります。MAX15046は、V<sub>CC</sub>が3.6V (typ)を下回った場合 に内蔵リニアレギュレータをディセーブルする低電圧ロッ クアウト回路も採用しています。400mVのUVLOヒス テリシスによって、パワーアップ/パワーダウン時のチャタ リングが防止されます。

### MOSFETゲートドライバ(DH、DL)

DHおよびDLは、大型nチャネルパワーMOSFETの駆動用 に最適化されています。通常の動作状態およびスタート アップ後には、DLのローサイド駆動波形は常にDHのハイ サイド駆動波形の相補形となり、交差導通または「貫通 電流」を防止する制御されたデッドタイムを備えています。 適応型デッドタイム回路はDHおよびDL出力を監視して、 MOSFETが完全にオフになるまで反対側のMOSFETの ターンオンを防止します。これによって、この回路はDLゲー トドライバのターンオフが完了した時点でのみハイサイドド ライバをターンオンさせ、DHゲートドライバがターンオフ を完了するまでローサイド(DL)のターンオンを防止します。

適応型のドライバデッドタイムによって、広範なMOSFET で貫通電流のない動作が可能になり、遅延が最小限に抑え られて効率が維持されます。適応型デッドタイム回路が 適切に動作するためには、DLおよびDHとMOSFETのゲート の間に、低抵抗、低インダクタンスの経路が存在する必要が あります。ゲート放電経路の浮遊インピーダンスが原因で、 MOSFETのVGSがまだハイの間に検出回路がMOSFET ゲートを「オフ」と解釈する可能性があります。 浮遊インピー

ダンスを最小限に抑えるために、非常に短く、太いトレース を使用してください。

同期整流は、通常のローサイドのショットキーキャッチダイオードを低抵抗のMOSFETスイッチに置き換えることによって、整流器の導通損失を低減します。MAX15046は、DLをローに駆動するための、 $R_{DS(ON)}$ が $1\Omega$ (typ)の堅牢なプルダウントランジスタを内蔵しています。この低オン抵抗によって、LX端子の高速立上り時間中に、ローサイド同期整流器MOSFETのドレインとゲート間の容量性結合が原因でDLがプルアップされるのを防止します。

### ハイサイドゲート駆動電源(BST)

ゲート電圧をLXより高い値にブーストして、ハイサイド MOSFETのターンオンに必要なゲート-ソース間電圧を提供 するために、BSTとDHの間に外付けのショットキーダイオードを接続する必要があります。BSTとLXの間に接続 されたブーストコンデンサは、ハイサイドMOSFETのオン 時間の間ゲートドライバ両端間の電圧を維持します。

ゲート電荷を供給するために失われたブーストコンデンサの電荷は、ハイサイドMOSFETがターンオフしてLX端子がグランドレベルになるときに補充されます。LXがローのとき、VDRVとBSTの間の外付けダイオードがブーストコン

デンサを再充電します。適切なブーストコンデンサおよび ダイオードの選択については、「アプリケーション情報」の 「ブーストコンデンサおよびダイオードの選択」の項を参照 してください。

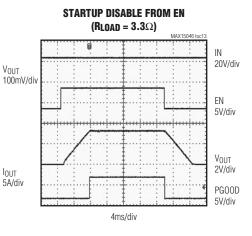

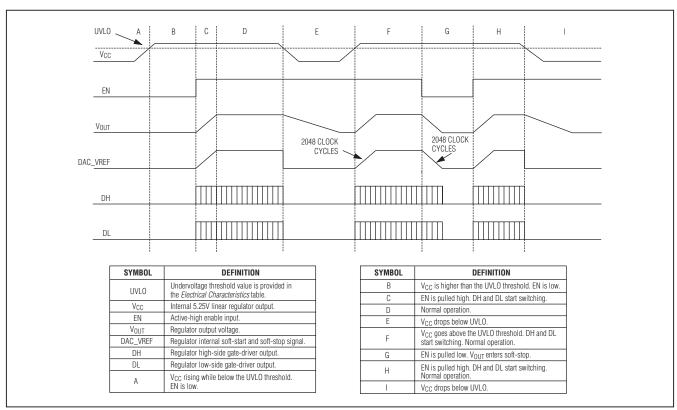

イネーブル入力(EN)、ソフトスタート、およびソフトストップ

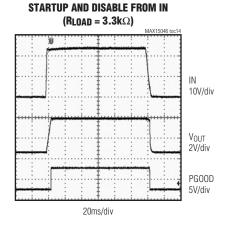

MAX15046をオンにするには、ENをハイに駆動してください。ソフトスタートシーケンスによって、エラーアンプのリファレンス電圧の(段階的な)増大が開始されます。ソフトスタートのランプ時間は2048スイッチングサイクルで、分解能は安定状態のレギュレーション電圧の1/64であるため、出力電圧のスムーズな増大が可能です。ENをロジッ

ため、出力電圧のスムーズな増大が可能です。ENをロジックローとすることで、エラーアンプのリファレンス電圧の段階的な低下によるソフトストップシーケンスが開始されます。ソフトストップシーケンスの完了後は、両方のMOSFETドライバがオフになります。図1を参照してください。

常時オンの動作とする場合は、ENをV<sub>CC</sub>に接続してください。正確なターンオン/オフスレッショルドを備えているため、ENはUVLO調整入力として使用することが可能で、PGOOD出力とともに電源シーケンス用に使用することも可能です。

図1. パワーオン/オフシーケンス

ソフトスタート中に谷電流制限に達した場合、MAX15046 は出力インピーダンスとインダクタ電流制限値の積にレギュレーションを行い、4096クロックサイクル後にオフになります。(たとえば)大きい容量性負荷に対して起動する場合も、突入電流が電流制限値を超えることはありません。4096クロックサイクルまでにソフトスタートが完了しない場合、デバイスはオフになります。デバイスは8192クロックサイクルの間オフのままになった後、再度ソフトスタートを試みます。この実装によって、出力コンデンサの充電中にインダクタ電流を制限値以下に保つために必要となる時間に、ソフトスタート時間を自動的に適応させることが可能です。

### パワーグッド出力(PGOOD)

MAX15046は、出力電圧を監視してパワーグッドスレッショルド(公称FB電圧の93%に固定)の検出を行うパワーグッドコンパレータを内蔵しています。PGOOD出力はオープンドレインのため、外付けのプルアップ抵抗が必要です。PGOODがローのとき、最大2mAの電流をシンクします。

レギュレータ出力が設計上の公称レギュレーション電圧の93%を上回った場合、PGOODはハイ(ハイインピーダンス)になります。レギュレータ出力電圧が公称レギュレーション電圧の90%を下回った場合、PGOODはローになります。ヒカップタイムアウト時間中、PGOODはローにアサートされます。

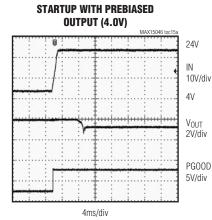

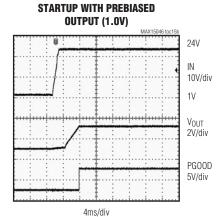

### プリバイアス出力へのスタートアップ

MAX15046がプリバイアス出力に対して起動する場合、コンバータが出力から電流をシンクしないので、DHおよびDLはオフになります。PWMコンパレータが最初のPWMパルスを発行するまで、DHおよびDLはスイッチングを開始しません。最初のPWMパルスは、リファレンス電圧ランプがFB電圧を上回った時点で発生します。

出力電圧が出力設定ポイント以上にバイアスされている場合、内部ソフトスタートが完了した時点で、コントローラは出力を設定ポイントにプルダウンしようと試みます。このプルダウンは、出力アンダーシュートを最小限に抑えるために低速で通常の値まで増大されるシンク電流制限によって制御されます。

### 電流制限回路(LIM)

電流制限回路は、ローサイドMOSFETのオン抵抗を電流 検出素子として使用することによって高コストの検出抵抗 を不要にする、「谷」およびシンク電流検出アルゴリズムを 採用しています。電流制限回路は、MOSFETの温度過昇 によるオン抵抗の変動に追従するための温度補償も備え ています。電流制限値はLIMの外付け抵抗で調整可能で、 広範なオン抵抗特性のMOSFETに対応します(「谷電流制 限の設定」の項を参照)。谷電流制限の調整範囲は $0.3V\sim 3V$ で、 $6k\Omega\sim 60k\Omega$ の抵抗値に相当します。ローサイド MOSFETの谷電流制限スレッショルドは正確にLIMの電圧の1/10で、シンク電流制限スレッショルドはLIMの電圧の1/20です。

谷電流制限は、ローサイドMOSFETのオン時間中にイン ダクタ電流が負荷に向かって流れ、CSPがPGNDより負側 である場合に作動します。ローサイドMOSFETのオン時間 の最後で電流検出信号の大きさが谷電流制限スレッショルド を上回っていた場合、MAX15046は新しいPWMサイクル を開始せず、次のサイクルでインダクタ電流を減衰させます。 また、コントローラは内部のリファレンス電圧を「ロール バック」して、電流制限値と短絡の抵抗によって決定され るレギュレーションポイントが見つかるようにします。この ようにして、コントローラは定低電流ソースとして機能し ます。この方法では、短絡イベント中のインダクタのリップル 電流が大幅に低減するため、インダクタのサイズの制限が緩和 され、可聴ノイズが発生する可能性も減少します。4096 クロックサイクル後、デバイスはヒカップモードに移行し ます。短絡が除去された時点で、内部リファレンス電圧が ソフトスタートを使用して再び通常のリファレンス電圧に 戻り、レギュレーションが続行されます。

シンク電流制限は、CSPがPGNDより正側であるときに、ローサイドMOSFETの電圧降下を監視することによって実現されます。ローサイドMOSFETのオン時間中の任意の時点でローサイドMOSFETの電圧降下がLIMの電圧の1/20を超えた場合、ローサイドMOSFETがオフになり、ハイサイドMOSFETのボディダイオードを通って出力からインダクタ電流が流れます。シンク電流制限が作動した場合、DH/DLのスイッチングシーケンスは相補形ではなくなり、両方のMOSFETがオフになります。

CSPとPGNDにおいてノイズとDC誤差による電流検出信号の劣化がないことを保証するために、PCBレイアウトのガイドラインを十分に遵守してください。MAX15046はローサイドMOSFETの近くに実装して、短い直接的なトレースを使用してケルビン接続を行い、トレース抵抗によってローサイドMOSFETのR<sub>DS(ON)</sub>が増加しないようにしてください。

### ヒカップモード過電流保護

ヒカップモード過電流保護は、短絡や激しい過負荷状態が長時間続く場合に、電力消費を低減します。谷電流制限スレッショルドに到達している場合、内部の3ビットカウンタが各スイッチングサイクルでカウントアップします。スレッショルドに到達していない場合、カウンタは各スイッチングサイクルでカウントダウンして、ゼロ(000)で停止します。電流制限状態が持続してカウンタが111 (= 7イベント)に

到達した場合、MAX15046はDLとDHの両方のドライバを停止して、4096スイッチングサイクル(ヒカップタイムアウト遅延)の間待機した後に新しいソフトスタートシーケンスを試行します。ヒカップモード保護はソフトスタート時間中も作動したままになります。

### 低電圧ロックアウト

MAX15046は、V<sub>CC</sub>の電圧を監視するための低電圧ロックアウト(UVLO)回路を内蔵しています。UVLO回路は、V<sub>CC</sub>がV<sub>UVLO</sub>より低いときにMAX15046が動作するのを防止します。UVLOのスレッショルドは4Vで、電源電圧の立上り/立下りエッジでのチャタリングを防止するために400mVのヒステリシスを備えています。デバイスが低電圧ロックアウト状態の場合、スイッチングを抑止するためにDLおよびDHはローのままになります。

### 熱過負荷保護

熱過負荷保護は、MAX15046内の総電力消費を制限します。デバイスの接合部温度が+150℃を超えた時点で、内部の温度センサーがデバイスをシャットダウンして、DLおよびDHをローに強制することによって、デバイスの温度を低下させます。接合部温度が20℃低下すると、温度センサーはデバイスを再びオンにします。サーマルシャットダウン中に、レギュレータがシャットダウンされ、ソフトスタートがリセットされます。LDOレギュレータの電力消費およびDH/DLにおける過度の駆動損失によって熱過負荷保護がトリガされます。通常動作時の不要な熱過負荷保護のトリガを防止するために、総電力消費を慎重に評価してください(「電力消費」の項を参照)。

### アプリケーション情報

### 有効入力電圧範囲

MAX15046は4.5V~40Vの入力電源で動作して、最小 0.6Vに出力をレギュレートします。電圧変換比( $V_{OUT}/V_{IN}$ )の最小値は、制御可能な最小オン時間によって制限 されます。正常な固定周波数PWM動作のためには、電圧 変換比が次の条件を満たす必要があります。

$$\frac{V_{OUT}}{V_{IN}} > t_{ON(MIN)} \times f_{SW}$$

ここで、ton(MIN)は125nsで、fswはスイッチング周波数 (単位: Hz)です。所望の電圧変換が上記の条件に適合しない場合、実効デューティサイクルを減少させるためにパルススキップ動作が発生します。パルススキップ動作を防止する

には、スイッチング周波数を低下させるか、または入力電圧 V<sub>IN</sub>を低下させてください。

電圧変換比の最大値は、最大デューティサイクル(D<sub>max</sub>)によって制限されます。

$$\frac{V_{OUT}}{V_{IN}} < D_{max} - \frac{D_{max} \times V_{DROP2} + (1 - D_{max}) \times V_{DROP1}}{V_{IN}}$$

ここで、VDROP1は、同期整流器、インダクタ、およびPCBの抵抗を含む、インダクタ放電経路の寄生電圧降下の合計です。VDROP2は、ハイサイドスイッチ、インダクタ、およびPCBの抵抗を含む、充電経路の抵抗による電圧降下の合計です。実際には、良好な負荷過渡応答を実現するために、上記の条件に適切なマージンを付加してください。

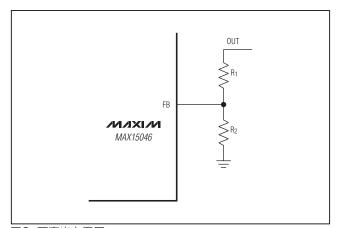

### 出力電圧の設定

MAX15046の出力電圧は、出力とFBおよびGNDの間に抵抗分圧器を接続することによって設定してください (図2)。R2は、 $4k\Omega\sim16k\Omega$ の範囲で選択してください。R1は次式を使用して計算します。

$$R_1 = R_2 \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$$

ここで、 $V_{FB}=0.59V$  (「Electrical Characteristics (電気的特性)」の表を参照)、 $V_{OUT}$ の範囲は $0.6V\sim(V_{IN}\times0.85)$ が可能です。

抵抗 $R_1$ は、Type III補償回路の設計にも関与します。 Type III補償回路を使用する場合は、 $R_1$ および $R_2$ の値を 検討してください(「Type III補償回路(図4)」の項を参照)。

図2. 可変出力電圧

### スイッチング周波数の設定

RTとGNDの間に接続する外付け抵抗によって、スイッチング周波数 $(f_{SW})$ が設定されます。 $f_{SW}$ と $R_{RT}$ の関係は、次のとおりです。

$$R_{RT} = \frac{17.3 \times 10^9}{f_{SW} + (1 \times 10^{-7}) \times (f_{SW}^2)}$$

ここで、 $f_{SW}$ の単位はHz、 $R_{RT}$ の単位は $\Omega$ です。たとえば、300kHzのスイッチング周波数は、 $R_{RT}=49.9k\Omega$ によって設定されます。周波数が高いほど、より低いインダクタ値と出力容量を使用する設計が可能になります。スイッチング周波数が高いほど、ピーク電流および $I^2$ R損失が減少しますが、コア損失、ゲート充電電流、およびスイッチング損失は増大します。

### インダクタの選択

MAX15046による動作のためには、インダクタンス値(L)、 インダクタ飽和電流(I<sub>SAT</sub>)、およびDC抵抗(R<sub>DC</sub>)の、3つ の主要なインダクタのパラメータを指定する必要があり ます。インダクタンスを決定するためには、最初にインダ クタのピークトゥピークAC電流とDC平均電流の比率(LIR) を選択する必要があります。LIRの値が大きすぎる場合、 RMS電流が大きくなるため、I<sup>2</sup>R損失が増大します。小さ いLIR値を実現するには、大きい値のインダクタを使用し てください。通常、特定のパッケージタイプについてイン ダクタの抵抗はインダクタンスに比例するため、LIR値が 非常に小さい場合にもI<sup>2</sup>R損失が大きくなります。サイズと 損失の間の適切な妥協点として、ピークトゥピークリップ ル電流と平均電流の比率が30%の場合(LIR = 0.3)があ ります。スイッチング周波数、入力電圧、出力電圧、およ び選択したLIRによって、次のようにインダクタの値が決定 されます。

$$L = \frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times I_{OLIT} \times LIR}$$

ここで、VIN、VOUT、およびIOUTは標準値です。スイッチング周波数は、RTによって設定されます(「スイッチング周波数の設定」の項を参照)。インダクタの正確な値は重要ではなく、サイズ、コスト、および効率の間のトレードオフを行うために調整することができます。インダクタの値が小さいほどサイズとコストが最小限に抑えられ、過渡応答も改善されますが、ピーク電流が増大するため効率が低下します。逆に、インダクタンスが大きいほど、RMS電流が減少するため効率が向上します。

割り当てられた寸法に適合するものの中で、可能な限りDC抵抗値が小さい低損失のインダクタを探してください。ローサイドMOSFETのオン抵抗とLIMリファレンス電流(I<sub>LIM</sub>)の許容誤差を考慮した上で、最大電流制限値(I<sub>CL(MAX)</sub>)より下では飽和が発生する可能性がないことを保証するために、飽和電流定格(I<sub>SAT</sub>)は十分に高い値とする必要があります。これらの条件の組み合わせから、次式の飽和電流(I<sub>SAT</sub>)を備えたインダクタを選択してください。

$$I_{SAT} \ge 1.35 \times I_{CL(TYP)}$$

ここで、 $I_{CL(TYP)}$ は標準電流制限設定ポイントです。係数の1.35は、 $R_{DS(ON)}$ の25%の変動とLIMリファレンス電流の誤差10%を含んだ値です。この要件に適合する各種のインダクタが様々なメーカーから提供されています(たとえば、Vishay IHLP-4040DZ-1-5および同じシリーズの他のインダクタ)。

### 谷電流制限の設定

ローサイドMOSFETのがR<sub>DS(ON)</sub>が電流検出素子として使用されるため、最小電流制限スレッショルドはワーストケースのローサイドMOSFETのオン抵抗値で予想される最大の負荷電流に対応した十分な高さとする必要があります。インダクタの谷電流は、I<sub>LOAD(MAX)</sub>からリップル電流の半分を引いた値で発生します。リップル電流の谷の間、電流制限スレッショルド電圧(V<sub>ITH</sub>)の最小値がローサイドMOSFETの電圧より高い必要があります。

$$V_{ITH} > R_{DS(ON,MAX)} \times I_{LOAD(MAX)} \times \left(1 - \frac{LIR}{2}\right)$$

ここで、 $R_{DS(ON,MAX)}$ (単位: $\Omega$ )は最大負荷電流 $I_{LOAD(MAX)}$ におけるローサイドMOSFETの最大オン抵抗で、次式から計算されます。

$R_{DS(ON,MAX)} = R_{DS(ON)} \times [1 + TC_{MOSFET} \times (T_{MAX} - T_{AMB})]$

ここで、 $R_{DS(ON)}$ (単位: $\Omega$ )は周囲温度 $T_{AMB}$ (単位: $\mathbb{C}$ ) でのローサイドMOSFETのオン抵抗、 $TC_{MOSFET}$ (単位: $ppm/\mathbb{C}$ )はローサイドMOSFETの温度係数、 $T_{MAX}$ (単位: $\mathbb{C}$ )は最大負荷電流 $I_{LOAD(MAX)}$ での温度です。 $R_{DS(ON)}$ と $TC_{MOSFET}$ は、MOSFETのデータシートに記載されています。

LIMとGNDの間に外付け抵抗( $R_{LIM}$ )を接続して、電流制限スレッショルドを調整してください。電流制限スレッショルドは、2300ppm/ $^{\circ}$ の温度係数で温度補償されます。電流制限スレッショルド( $V_{ITH}$ )と $R_{LIM}$ の関係は、次のとおりです。

$$R_{LIM} = \frac{10 \times V_{ITH}}{50 \times 10^{-6} \times \left[1 + 2300 \frac{ppm}{^{\circ}C} \times (T_{MAX} - T_{AMB})\right]}$$

ここで、R<sub>LIM</sub>の単位はΩ、V<sub>ITH</sub>の単位はV、T<sub>MAX</sub>とT<sub>AMB</sub>の単位は℃です。

$R_{LIM}$ の $6k\Omega \sim 60k\Omega$  の抵抗値範囲が、 $30mV \sim 300mV$  の電流制限スレッショルドに対応します。電流制限を調整する際には、許容誤差1%の抵抗を使用して電流制限スレッショルドの誤差を最小限に抑えてください。

### 入力コンデンサ

入力フィルタコンデンサは、電力ソースから流れるピーク電流を低減するとともに、スイッチング回路が原因で発生する入力のノイズおよび電圧リップルを軽減します。入力コンデンサは、次式で定義されるスイッチング電流によって課せられるリップル電流の要件(IRMS)に適合する必要があります。

$$I_{RMS} = I_{LOAD(MAX)} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

IRMSは、入力電圧が出力電圧の2倍に等しいとき(VIN = 2Vout)最大値となるため、IRMS(MAX) = ILOAD(MAX)/2です。タンタル以外のコンデンサ(セラミック、アルミ、ポリマー、またはOS-CON)は、非常にローインピーダンスのソースからシステムの給電が行われる場合に発生する大きい突入電流に耐える堅牢性を備えているため、大部分のアプリケーションでは入力にタンタル以外のコンデンサが適しています。さらに、高周波数ノイズを低減するために、2個(またはそれ以上)のより小さい値の低ESRコンデンサを並列に接続してください。

### 出力コンデンサ

出力コンデンサの選択に関する主要なパラメータは、容量値、ESR、および電圧定格です。これらのパラメータは、全体的な安定性、出力リップル電圧、および過渡応答に影響します。出力リップルには、出力コンデンサに蓄積される電荷の変動と、コンデンサに出入りする電流によって発生するコンデンサのESR両端での電圧降下という、2つの成分があります。

$\Delta VRIPPLE = \Delta VESR + \Delta VQ$

ESRと出力容量のそれぞれに起因する出力電圧リップルは、次のとおりです。

$$\begin{split} &\Delta V_{ESR} = I_{P-P} \times ESR \\ &\Delta V_{Q} = \frac{I_{P-P}}{8 \times C_{OUT} \times f_{SW}} \\ &I_{P-P} = & \left( \frac{V_{IN} - V_{OUT}}{f_{SW} \times L} \right) \times \left( \frac{V_{OUT}}{V_{IN}} \right) \end{split}$$

ここで、IP-Pはピークトゥピークインダクタ電流リップルです (「インダクタの選択」の項を参照)。最初にコンデンサを選択する際には、これらの式を使用してください。最終的な値は、プロトタイプや評価用回路のテストによって決定してください。

負荷過渡応答の要件に対して、出力コンデンサの確認を行ってください。高速負荷過渡中に許容される出力電圧の逸脱によって、コンデンサの出力容量、ESR、および等価直列インダクタンス(ESL)が決定されます。負荷ステップ中は、コントローラが応答してデューティサイクルを増大させるまでの間、出力コンデンサが負荷電流を供給します。応答時間(tresponse)は、コンバータのクローズドループ帯域幅に依存します(「補償の設計」の項を参照)。出力コンデンサのESRによる抵抗性降下、コンデンサのESLによる電圧降下(ΔVESL)、およびコンデンサの放電によって、負荷ステップ中に電圧ドループが発生します。

過渡負荷および電圧リップル性能を向上させるために、低ESRのタンタル/アルミ電解コンデンサとセラミックコンデンサの組み合わせを使用してください。リードのないコンデンサとコンデンサの並列接続は、ESLの低減に役立ちます。出力電圧の最大の逸脱を許容可能な負荷の制限以下に維持してください。次の各式を使用して、負荷ステップ中に必要なESR、ESL、および容量値を計算してください。

$$\begin{aligned} & \mathsf{ESR} = \frac{\Delta V_{\mathsf{ESR}}}{I_{\mathsf{STEP}}} \\ & C_{\mathsf{OUT}} = \frac{I_{\mathsf{STEP}} \times t_{\mathsf{RESPONSE}}}{\Delta V_{\mathsf{Q}}} \\ & \mathsf{ESL} = \frac{\Delta V_{\mathsf{ESL}} \times t_{\mathsf{STEP}}}{I_{\mathsf{STEP}}} \\ & t_{\mathsf{RESPONSE}} \cong \frac{1}{3 \times f_{\mathsf{Q}}} \end{aligned}$$

ここで、ISTEPは負荷ステップ、tSTEPは負荷ステップの立上り時間、tRESPONSEはコントローラの応答時間、foはクローズドループのクロスオーバー周波数です。

### 補償の設計

MAX15046は、外部での周波数補正に使用可能な反転入力および出力を備えたトランスコンダクタンスアンプを内蔵しています。外部補償の柔軟性によって、出力フィルタ部品(特に出力コンデンサ)の広範な選択肢が提供されます。コストに敏感なアプリケーションには、高ESRのアルミ電解コンデンサを使用します。サイズに敏感なアプリケーションの出力には、低ESRのタンタルまたはセラミックコンデンサを使用します。MAX15046はスイッチング周波数が高いため、出力にセラミックコンデンサを使用することが可能です。出力リップル、部品サイズ、および部品コストの要件に適合するようにすべての受動電力部品を選択してください。エラーアンプが所望のクローズドループ帯域幅と位相マージンを実現するように補償用の部品を選択してください。

適切な補償回路のタイプを選択するためには、電源のポールとゼロ、ゼロクロスオーバー周波数、および出力コンデンサのタイプを最初に決定する必要があります。

バックコンバータの場合、出力段のLCフィルタによって次の周波数に1組の複合ポールが発生します。

$$f_{PO} = \frac{1}{2\pi \times \sqrt{L_{OUT} \times C_{OUT}}}$$

出力コンデンサによって、次の周波数にゼロが発生します。

$$f_{ZO} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

ここで、ESRは出力コンデンサの等価直列抵抗です。

ループ利得が1 (OdB)に等しくなるループ利得クロスオーバー周波数(fo)は、スイッチング周波数の1/10より下に設定してください。

$$f_O \leq \frac{f_{SW}}{10}$$

より低いクロスオーバー周波数を選択することで、デュー ティサイクルのジッタなど、フードバックループへのノイズ 混入による影響が軽減されます。

安定したシステムを維持するには、安定性に関する2つの 基準を満たす必要があります。

1) クロスオーバー周波数(f<sub>0</sub>)における位相シフトが180° 未満であること。言い換えると、ループの位相マージン が0より大きいこと。 2) 位相シフトが-180°の周波数における利得(利得マージン)が1未満であること。

堅牢なループ安定性および良好な過渡応答を実現するために、60°程度の位相マージンを維持してください。

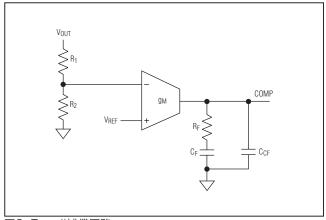

電解または高ESRのタンタル出力コンデンサを使用する場合、コンデンサのESRゼロ( $f_{ZO}$ )は通常はLCポールとクロスオーバー周波数 $f_{O}$ の間で発生します( $f_{PO}$  <  $f_{ZO}$  <  $f_{O}$ )。Type II (PI:比例、積分)補償回路を選択してください。セラミックまたは低ESRのタンタル出力コンデンサを使用する場合、コンデンサのESRゼロは通常は所望のクロスオーバー周波数 $f_{O}$ より上で発生して、 $f_{PO}$  <  $f_{O}$  <  $f_{ZO}$ になります。Type III (PID:比例、積分、および微分)補償回路を選択してください。

### Type II補償回路(図3)

$f_{ZO}$ が $f_{O}$ より低く、 $f_{PO}$ に近い場合、コンデンサのESRゼロの位相リードによって、クロスオーバー周波数付近のLCフィルタの複合ポールの一方の位相損失がほぼ相殺されます。ループを安定させるために、中帯域のゼロおよび高周波数のポールを備えたType II補償回路を使用してください。図3では、 $R_F$ および $C_F$ によって中帯域のゼロ( $f_{Z1}$ )が発生します。Type II補償回路の $R_F$ および $C_C$ Fが高周波数ポール( $f_{P1}$ )を提供して、出力の高周波数リップルの影響を軽減します。

以下の手順を使用して、図3に示すType II補償回路の部品の値を計算してください。

1) レギュレータのパルス幅モジュレータ、LCフィルタ、フィードバック分圧器、および関連回路で構成されるモジュレータのクロスオーバー周波数における利得(GAIN<sub>MOD</sub>)を計算してください。

$$GAIN_{MOD} = \frac{V_{IN}}{V_{RAMP}} \times \frac{ESR}{(2\pi \times f_O \times L_{OUT})} \times \frac{V_{FB}}{V_{OUT}}$$

ここで、 $V_{IN}$ はレギュレータの入力電圧、 $V_{RAMP}$ はパルス幅モジュレータでのランプの大きさ、 $V_{FB}$ はFBの入力電圧設定ポイント(0.6V typ、[Electrical Characteristics]の表を参照)、 $V_{OUT}$ は所望の出力電圧です。

中帯域周波数でのエラーアンプの利得(GAIN<sub>EA</sub>)は、次のとおりです。

$$GAINEA = gm \times RF$$

ここで、gMはエラーアンプの相互コンダクタンスです。

foにおけるモジュレータの利得とエラーアンプの利得の積である全ループ利得は、次のようになります。

1)  $GAIN_{MOD} \times GAIN_{EA} = 1$  よって、

$$\frac{V_{\text{IN}}}{V_{\text{OSC}}} \times \frac{\text{ESR}}{(2\pi \times f_{\text{O}} \times L_{\text{OUT}})} \times \frac{V_{\text{FB}}}{V_{\text{OUT}}} \times g_{\text{M}} \times R_{\text{F}} = 1$$

R<sub>F</sub>について解くと、

$$R_{F} = \frac{V_{OSC} \times (2\pi \times f_{O} \times L_{OUT}) \times V_{OUT}}{V_{FB} \times V_{IN} \times g_{M} \times ESR}$$

2) 中帯域のゼロ( $f_{Z1}$ )を、(LCポールの一方を相殺するために)  $f_{PO} \times 0.75$ に設定してください。

$$f_{Z1} = \frac{1}{2\pi \times R_F \times C_F} = 0.75 \times f_{PO}$$

CFについて解くと、

$$C_{F} = \frac{1}{2\pi \times R_{F} \times f_{PO} \times 0.75}$$

3) 高周波数のポールを(スイッチング周波数 $f_{SW}$ におけるリップルを減衰させるために)  $f_{P1} = f_{SW} \times 0.5$ の位置として、次式を使用して $C_{CF}$ を計算してください。

$$C_{CF} = \frac{1}{\pi \times R_F \times f_{SW} - \frac{1}{C_F}}$$

図3. Type II補償回路

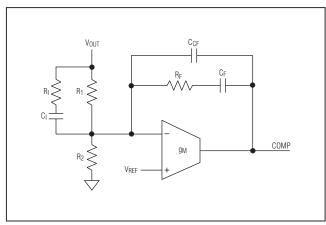

### Type III補償回路(図4)

低ESRのタンタルまたはセラミックタイプを使用する場合、ESRによるゼロ周波数は、通常は目標のゼロクロスオーバー周波数(fo)より高くなります。Type III補償を使用してください。Type III補償は、下記の周波数に2つのゼロと3つのポールを提供します。

$$f_{Z1} = \frac{1}{2\pi \times R_F \times C_F}$$

$$f_{Z2} = \frac{1}{2\pi \times C_I \times (R_1 + R_I)}$$

2つの中帯域のゼロ( $f_{Z1}$ および $f_{Z2}$ )が、LCフィルタによって発生する1組の複合ポールを相殺します。

$$f_{P1} = 0$$

fp1は、DC出力電圧誤差を排除するために、ゼロ周波数にポールを生成します(積分器)。

$$f_{P2} = \frac{1}{2\pi \times R_{I} \times C_{I}}$$

fp2は、ESRゼロ(fZO)の位置に応じて、fZOを相殺するか、 または高周波数の出力リップルに対する減衰を追加するた めに使用してください。

$$f_{P3} = \frac{1}{2\pi \times R_F \times \frac{C_F \times C_{CF}}{C_F + C_{CF}}}$$

fp3は、高周波数の出力リップルを減衰させます。

位相マージンがfo付近でピークになるように、ゼロおよびポールの位置を設定してください。

$R_F >> 2/g_M$ であることと、 $R_1$ 、 $R_2$ 、および $R_1$ の並列抵抗値が $1/g_M$ より大きいことを確認してください。そうでない場合は、応答に $180^\circ$ の位相シフトが発生してループが不安定になります。

以下の補償の手順を使用してください。

1) R<sub>F</sub> >> 10kΩの場合、最初のゼロ(f<sub>Z1</sub>)をf<sub>PO</sub> x 0.8の 位置としてください。

$$f_{Z1} = \frac{1}{2\pi \times R_F \times C_F} = 0.8 \times f_{PO}$$

よって、

$$C_F = \frac{1}{2\pi \times R_F \times 0.8 \times f_{PO}}$$

2) パルス幅モジュレータ、LCフィルタ、フィードバック分 圧器、および関連回路で構成されるモジュレータのクロ スオーバー周波数における利得(GAIN<sub>MOD</sub>)は、次の とおりです。

$$GAIN_{MOD} = \frac{V_{IN}}{V_{RAMP}} \times \frac{1}{(2\pi \times f_{O})^{2} \times L_{OUT} \times C_{OUT}}$$

中帯域周波数でのエラーアンプの利得(GAIN<sub>EA</sub>)は、次のとおりです。

$$GAIN_{EA} = 2\pi \times f_O \times C_I \times R_F$$

foにおけるモジュレータの利得とエラーアンプの利得の積である全ループ利得は1です。

$$GAIN_{MOD} \times GAIN_{FA} = 1$$

よって、

$$\frac{V_{IN}}{V_{RAMP}} \times \frac{1}{(2\pi \times f_O)^2 \times C_{OUT} \times L_{OUT}} \times 2\pi \times f_O \times C_I \times R_F = 1$$

$C_I$ について解くと、

$$C_{I} = \frac{V_{RAMP} \times \left(2\pi \times f_{O} \times L_{OUT} \times C_{OUT}\right)}{V_{IN} \times R_{F}}$$

3)  $f_{PO} < f_O < f_{ZO} < f_{SW/2}$ の場合は、第2のポール( $f_{P2}$ ) を使用して $f_{ZO}$ を相殺してください。ループ利得の周波数応答は、0dBクロスオーバーの後すぐには平坦にならず、最大でスイッチング周波数の1/2まで-20dB/decadeの傾きを維持します。出力コンデンサが低ESRのタンタルの場合、その可能性が高くなります。 $f_{P2} = f_{ZO}$ に設定してください。

セラミックコンデンサを使用する場合、コンデンサのESR ゼロ( $f_{ZO}$ )はスイッチング周波数の半分よりさらに上に位置する可能性が高くなります( $f_{PO}$  <  $f_{O}$  <  $f_{SW/2}$  <  $f_{ZO}$ )。この場合は、クロスオーバー周波数において位相マージンを大幅に損なうことがないように、第2のポールの周波数( $f_{P2}$ )を十分に高い位置としてください。たとえば、 $f_{P2}$ を $f_{O}$  × 5に設定することで、クロスオーバー周波数 $f_{O}$ における位相損失への寄与は約11°のみとなります。

$$f_{P2} = 5 \times f_{O}$$

fp2が決定した後、Riを計算してください。

$$R_{I} = \frac{1}{2\pi \times f_{P2} \times C_{I}}$$

4) 第2のゼロ( $f_{Z2}$ )を $f_{O}$  x 0.2または $f_{PO}$ のいずれか低い位置として、次式を使用して $R_1$ を計算してください。

$$R_1 = \frac{1}{2\pi \times f_{72} \times C_1} - R_1$$

5) 第3のポール(f<sub>P3</sub>)をスイッチング周波数の半分の位置 として、C<sub>CF</sub>を計算してください。

$$C_{CF} = \frac{C_F}{(2\pi \times 0.5 \times f_{SW} \times R_F \times C_F) - 1}$$

6) R2を次のように計算してください。

$$R_2 = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R_1$$

### MOSFETの選択

ステップダウンコントローラのMAX15046は、2つの外付けロジックレベルnチャネルMOSFETを駆動します。これらのMOSFETを選択するための主なパラメータとして、以下が含まれます。

- オン抵抗(R<sub>DS(ON)</sub>)

- 最大ドレイン-ソース間電圧(V<sub>DS(MAX)</sub>)

- 最小スレッショルド電圧(V<sub>TH(MIN)</sub>)

- ・ 総ゲート電荷量(QG)

- 帰還容量(C<sub>RSS</sub>)

- 電力消費

2つのnチャネルMOSFETは、VGS = 4.5Vでのオン抵抗の仕様が保証されているロジックレベルタイプである必要があります。最大の効率を実現するために、標準入力電圧においてスイッチング損失と等しい導通損失を備えたハイサイドMOSFETを選択してください。最小入力電圧における導通損失がMOSFETのパッケージの熱的限界を超えず、全体的な熱許容量にも抵触しないことを確認してください。また、最大入力電圧における導通損失とスイッチング損失の和がパッケージの定格を超えず全体的な熱許容量にも抵触しないことを確認してください。DLゲートドライバがローサイドMOSFETを駆動可能であることを確認してください。特に、ハイサイドMOSFETのターンオンによるdv/dtが、ローサイドMOSFETのドレイン-ゲート間容量を

図4. Type III補償回路

通してローサイドMOSFETのゲートをプルアップすることがないか検討してください。これは、交差導通の問題が発生する最大の原因です。

内蔵リニアレギュレータを使用してゲートドライバに給電する場合は、電力消費を検討してください。デバイスのオーバーヒートなしにV<sub>CC</sub>が両方のドライバに給電することができるように、ゲート電荷量の低いMOSFETを選択してください。

PDRIVE = VCC x QG\_TOTAL x fsw

ここで、 $Q_{G\_TOTAL}$ は、2つの外付けMOSFETのゲート電荷量の合計です。

### ブーストコンデンサおよびダイオードの選択

MAX15046は、ハイサイドMOSFETのターンオンに必要なゲート-ソース間電圧を、ブートストラップ回路を使用して生成します。選択したnチャネルハイサイドMOSFETによって、次式にしたがつて適切なブースト容量値(「標準アプリケーション回路」のCBST)が決定されます。

$$C_{BST} = \frac{QG}{\Delta V_{BST}}$$

ここで、 $Q_G$ はハイサイドMOSFETの総ゲート電荷量、 $\Delta V_{BST}$ はターンオン後にハイサイドMOSFETドライバで許容される電圧変動です。 $C_{BST}$ を決定する際には、利用可能なゲート駆動電圧が大幅に減少しないような $\Delta V_{BST}$ を選択してください(たとえば、 $\Delta V_{BST}$  = 100mV ~ 300mV)。

ブーストコンデンサには、100nF (min)の低ESRのセラミックコンデンサを使用してください。

小信号ダイオードをブートストラップ回路に使用することが可能で、BSTの最大電圧に耐えるためにV<sub>IN</sub> + 3Vの最小電圧定格を備えている必要があります。ダイオードの平均順方向電流は、次の要件に適合するようにしてください。

IF > QGATE x fsw

ここで、QGATEはハイサイドMOSFETのゲート電荷です。

### 電力消費

デバイスの最大電力消費は、ダイから周囲環境への熱抵抗および周囲温度に依存します。熱抵抗は、デバイスのパッケージ、PCBの銅面積、その他の熱質量、およびエアフローに依存します。

パッケージの電力消費 $(P_T)$ は、電源構成に依存します (「標準アプリケーション回路」を参照)。次式を使用して、電力消費を計算してください。

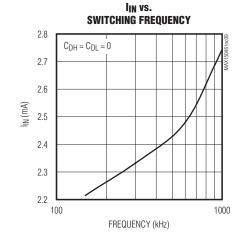

$$PT = VIN \times [QG\_TOTAL \times fSW + IQ]$$

ここで、 $I_Q$ はスイッチング周波数における自己消費電流です。「標準動作特性」の $[I_{IN}$  vs. Switching Frequency ( $I_{IN}$  とスイッチング周波数の関係)」のグラフから、 $I_Q$ を判断してください。

次式を使用して、ダイの温度上昇を推定してください。

$$T_J = T_A + (P_T \times \theta_{JA})$$

ここで、 $\theta_{JA}$ はパッケージの接合部-周囲間熱インピーダンス、 $P_T$ はデバイス内で消費される電力、 $T_A$ は周囲温度です。 $\theta_{JA}$ は、それぞれに該当するJEDEC規格(JESD51-5、JESD51-7)で規定された条件で、16ピンQSOPの場合は103.7  $^{\circ}$ C/W、16ピンQSOP-EPパッケージの場合は多層基板上において44  $^{\circ}$ C/Wです。実際の動作条件がJEDEC規格に記載されているものと大幅に異なる場合、接合部温度の正確な評価を行うためにはケース温度( $T_C$ )を直接測定する必要があります。その場合、接合部温度は次のようになります。

$$T_J = T_C + (P_T \times \theta_{JC})$$

16ピンQSOPパッケージの場合は $\theta$ JC熱インピーダンスとして37 $^{\circ}$ C/Wを使用して、16ピンQSOP-EPパッケージの場合は $6^{\circ}$ C/Wを使用してください。ケース-周囲間熱インピーダンス( $\theta$ CA)は、PCBから周囲に熱がどの程度良好に伝達されるかに依存します。大面積の銅領域を使用して、PCBを低い温度に維持してください。

# *MAX15046*

### PCBレイアウトのガイドライン

クリーンで安定した動作を実現するためには、注意深い PCBレイアウトが非常に重要です。スイッチングパワー段 には特別な注意が必要です。適切なPCBレイアウトとする ため、以下のガイドラインにしたがつてください。

- 1) デカップリングコンデンサはできる限りICの近くに配置 してください。電源グランドプレーン(PGNDに接続)と 信号グランドプレーン(GNDに接続)を、デバイスの近く の1点で接続してください。

- 2) 入力および出力コンデンサは、電源グランドプレーン に接続してください。他のすべてのコンデンサは、信号 グランドプレーンに接続してください。

- 3) 大電流の経路は、できる限り短くかつ太くしてください。 スイッチング電流の経路(C2-IN間およびC2-PGND間) は短くしてください。スイッチング経路にはビアを使用 しないでください。

- 4) 電流制限の検出を正確に行うために、CSPをローサイド FETのドレインにケルビン接続してください。

- 5) すべてのフィードバック接続が短く直接的であることを確認してください。フィードバック抵抗はできる限りIC の近くに配置してください。

- 6) 高速スイッチング端子(BST、LX、DH、およびDL)は、 敏感なアナログ領域(RT、FB、COMP、およびLIM) から離れた位置に配線してください。

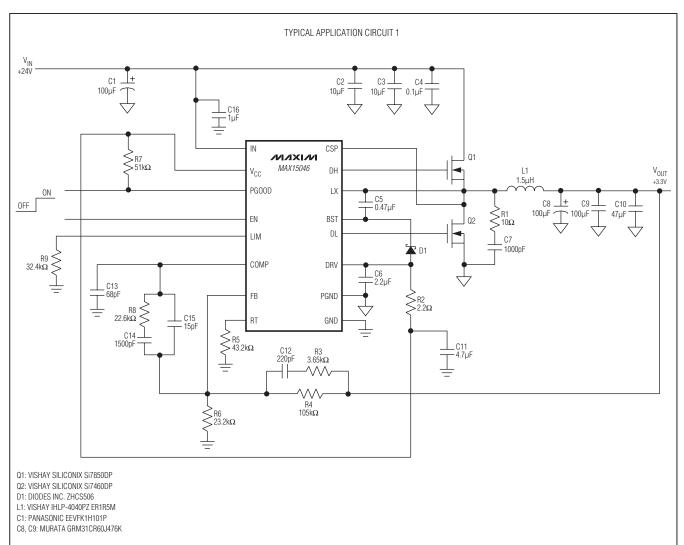

### 24V電源、3.3V出力動作

「標準アプリケーション回路」の項の「Typical Application Circuit 1 (標準アプリケーション回路1)」は、24Vで動作して3.3Vで最大10Aを出力するアプリケーション回路を示します。R5は、スイッチング周波数を350kHzに設定しています。

### 单一4.5V~5.5V電源動作

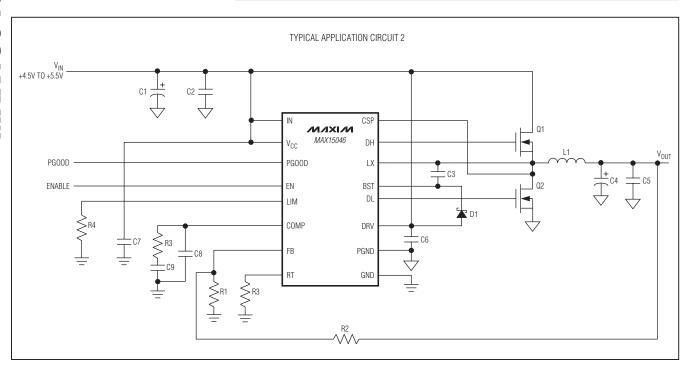

「標準アプリケーション回路」の項の「Typical Application Circuit 2 (標準アプリケーション回路2)」は、単一+4.5V ~+5.5V電源動作用のアプリケーション回路を示します。

### 補助5V電源動作

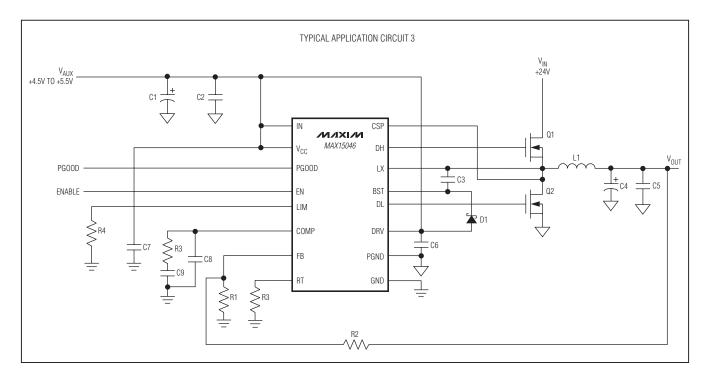

「標準アプリケーション回路」の項の「Typical Application Circuit 3 (標準アプリケーション回路3)」は、+24V電源で外付けMOSFETを駆動して補助+5V電源でデバイスに 給電するアプリケーション回路を示します。

## 標準アプリケーション回路

MIXIM

## 標準アプリケーション回路(続き)

### ピン配置

### チップ情報

PROCESS: BiCMOS

### パッケージ

最新のパッケージ図面情報およびランドパターンはjapan.maxim-ic.com/packages を参照してください。なお、パッケージコードに含まれる「+」、「#」、または「-」はRoHS対応状況を表したものでしかありません。パッケージ図面はパッケージそのものに関するものでRoHS対応状況とは関係がなく、図面によってパッケージコードが異なることがある点を注意してください。

| パッケージタイプ   | パッケージコード | ドキュメントNo.      |

|------------|----------|----------------|

| 16 QSOP    | E16+4    | <u>21-0055</u> |

| 16 QSOP-EP | E16E+9   | 21-0112        |

# MAX15046

### 改訂履歴

| 版数 | 改訂日  | 説明                                                                                                                                                                                                            | 改訂ページ                              |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 0  | 7/09 | 初版                                                                                                                                                                                                            |                                    |

| 1  | 2/10 | 「Electrical Characteristics」の「Minimum Low-Side On-Time (最小ローサイドオン時間)」の条件を修正。TOCの2、18、および19を修正。「MOSFETゲートドライバ(DH、DL)」、「スイッチング周波数の設定」、「谷電流制限の設定」、「MOSFETの選択」、および「電力消費」の項を修正。「Typical Application Circuit 1」を修正。 | 3, 5, 7, 10, 14,<br>15, 18, 19, 21 |

マキシム・ジャパン株式会社 〒141-0032 東京都品川区大崎1-6-4 大崎ニューシティ 4号館 20F TEL: 03-6893-6600

Maximは完全にMaxim製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。Maximは随時予告なく回路及び仕様を変更する権利を留保します。