#

## アクティブマトリックス液晶ディスプレイ (AMLCD)電源

概要

MAX1664は、アクティブマトリックス薄膜トランジスタ (TFT)液晶ディスプレイの電源にバックプレーン駆動回路 を統合したデバイスです。単一出力パルス幅変調ブースト コンバータ(0.25 スイッチ)、1個のインダクタを使用し たデュアル出力(正及び負)ゲートドライバ電源、LCD バックプレーンドライバ及び3つの出力全てを同期させる ためのシンプルな位相ロックループを備えています。

高スイッチング周波数(公称1MHz)及び位相ロック動作 により、出力ノイズを低く抑えつつ薄い小型の外部部品 を使用することができます。入力電圧範囲が+2.8V~ +5.5Vであるため、どのようなロジック電源とでも使用 できます。出力電圧は、+5.5Vまで(DC-DC1)及び +28V及び-10Vまで(DC-DC2)調節可能です。 負の 出力電圧は、部品を追加すると-20Vまで調節できます。 又、ロジックレベルシャットダウン及び3つの出力全て が安定化状態にあることを知らせる「レディ」出力(RDY) も備えています。

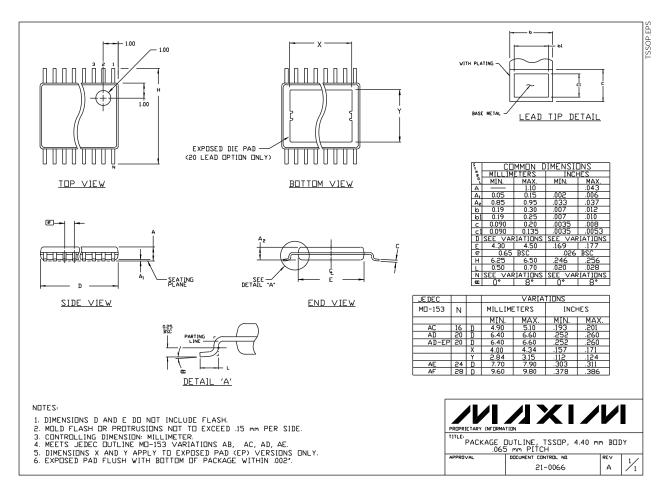

ブーストコンバータの動作周波数は、バックプレーン クロックの16、24又は32倍に設定できます。この柔 軟性により、LCDバックプレーンクロックレート 20kHz~72kHzに対して高いDC-DCコンバータ周波数 が可能です。MAX1664は高さ1.1mmのTSSOPパッ ケージで提供されています。

#### アプリケーション \_\_\_\_

LCDモジュール

LCDパネル

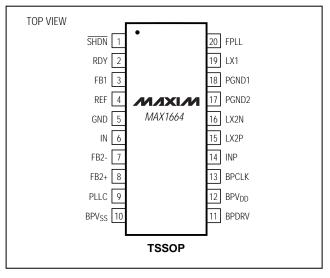

#### ピン配置

#### 特長

- ◆ 3個のDC-DCコンバータ用の全てのアクティブ 回路を統合

- ◆ 超小型外部部品(セラミックコンデンサ、  $2\mu H \sim 5\mu H の インダクタ)$

- ◆ DC-DCコンバータをバックプレーン周波数に 位相ロックしてノイズを低減

◆ 低動作電圧:最低+2.8V

◆ 可変出力電圧: V<sub>IN</sub>~+5.5V

◆ 負荷電流:500mAまで

◆ 可変TFTゲートドライバ出力:

正、V<sub>IN</sub>~+28V

負、0~-10V(部品を追加した場合は-20Vまで)

- ◆ 0.35 のバックプレーンドライバを装備

- ◆ シャットダウン電流:1µA

- ◆ パワーレディ出力信号

#### 型番

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX1664CUP | 0°C to +70°C | 20 TSSOP    |

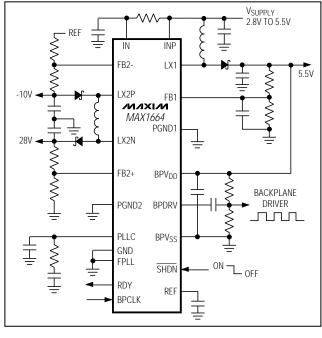

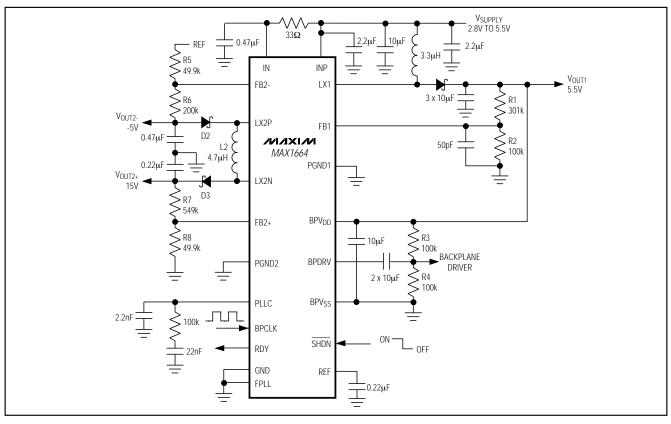

#### 標準動作回路

#### **ABSOLUTE MAXIMUM RATINGS**

| RDY, IN, BPV <sub>DD</sub> to GNDFB2-, PGND1, PGND2 to GND | ±0.3V                               | RDY Sink Current20mA<br>LX2P, LX2N Peak Switch Currents±750mA |

|------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------|

| LX1 to PGND1                                               | 0.3V to +6V                         | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )         |

| BPVss to GND                                               | 3.3V to +0.3V                       | 20-Pin TSSOP (derate 7mW/°C above+70°C)559mW                  |

| BPVDD to BPVss                                             | 0.3V to +6V                         | Operating Temperature Range0°C to +70°C                       |

| BPDRV to BPVSS                                             | 0.3V to (V <sub>BPVDD</sub> + 0.3V) | Junction Temperature+150°C                                    |

| LX2P to INP                                                | 15V to +0.3V                        | Storage Temperature Range65°C to +160°C                       |

| LX2N to PGND2                                              | 0.3V to +30V                        | Lead Temperature (soldering, 10sec)+300°C                     |

| SHDN, INP, FB1, FB2+, REF, PLLC,                           |                                     |                                                               |

| BPCLK FPLL to GND                                          | $-0.3V$ to $(V_{INI} + 0.3V)$       |                                                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=V_{INP}=3.3V,\overline{SHDN}=IN,V_{BPVDD}=4V,V_{BPVSS}=-1V,PGND1=PGND2=FPLL=GND,f_{BPCLK}=30kHz,T_{A}=0^{\circ}C\ to\ +70^{\circ}C,unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C$ .)

| PARAMETER                         | SYMBOL                | CONDITIONS                                                             | MIN    | TYP                     | MAX   | UNITS |  |

|-----------------------------------|-----------------------|------------------------------------------------------------------------|--------|-------------------------|-------|-------|--|

| Input Supply Range                | VIN                   |                                                                        | 2.8    |                         | 5.5   | V     |  |

| Undervoltage Lockout<br>Threshold | V <sub>UVLO</sub>     |                                                                        | 2.5    |                         | 2.8   | V     |  |

| Quiescent Current                 | IQ                    | $V_{FB1+} = V_{FB2+} = 1.3V$ , $V_{FB2-} = -0.1V$ ; $I_{IN} + I_{INP}$ |        | 0.5                     | 2     | mA    |  |

| Shutdown Current                  | I <sub>SD</sub>       | $\overline{SHDN} = GND$ , $V_{IN} = 5.5V$ ; $I_{IN} + I_{INP}$         |        | 0.01                    | 10    | μΑ    |  |

| DC-DC 1 (PWM MAIN OUTPUT)         |                       |                                                                        |        |                         |       |       |  |

| Output Voltage Range              | Vout1                 |                                                                        | VIN    |                         | 5.5   | V     |  |

|                                   |                       | FPLL = GND                                                             | 3      | 32 x f <sub>BPCLK</sub> |       |       |  |

| Operating Frequency               | f <sub>OP1</sub>      | FPLL = REF                                                             | 2      | 24 x f <sub>BPCLK</sub> |       |       |  |

|                                   |                       | FPLL = IN                                                              | 1      | 16 x fBPCLK             |       |       |  |

| FB1 Regulation Voltage            | V <sub>FB1</sub>      | $0 < I_{LX1} < 1.2A$                                                   | 1.2125 | 1.2500                  | 1.275 | V     |  |

| FB1 Input Bias Current            | I <sub>FB1</sub>      | V <sub>FB1</sub> = 1.3V                                                |        |                         | 100   | nA    |  |

| LX1 On Resistance                 | Ron(LX1)              |                                                                        |        | 0.25                    | 0.5   | Ω     |  |

| LX1 Leakage Current               | I <sub>LKG(LX1)</sub> | $V_{LX1} = 6V$                                                         |        | 0.1                     | 10    | μΑ    |  |

| LX1 Peak Current Limit            | I <sub>LIM(LX1)</sub> |                                                                        | 1.2    | 1.5                     | 1.8   | А     |  |

| Power-Ready Trip Level            | V <sub>TH_RDY</sub>   | Rising edge, 2% hysteresis                                             | 1.091  | 1.125                   | 1.159 | V     |  |

| DC-DC 2 (PFM)                     |                       |                                                                        |        |                         |       |       |  |

| Positive Output Voltage Range     | V <sub>OUT2+</sub>    |                                                                        | VIN    |                         | 28    | V     |  |

| Negative Output Voltage Range     | V <sub>OUT2</sub> -   |                                                                        | -10    |                         | 0     | V     |  |

|                                   |                       | FPLL = GND                                                             | 1      | 16 x f <sub>BPCLK</sub> |       |       |  |

| Maximum Operating Frequency       | fop2(MAX)             | FPLL = REF                                                             | 1      | 12 x f <sub>BPCLK</sub> |       |       |  |

|                                   |                       | FPLL = IN                                                              |        | 8 x fbpclk              |       | ]     |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{INP} = 3.3V, \overline{SHDN} = IN, V_{BPVDD} = 4V, V_{BPVSS} = -1V, PGND1 = PGND2 = FPLL = GND, f_{BPCLK} = 30kHz, T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C, unless otherwise noted. Typical values are at <math>T_{A} = +25^{\circ}C$ .)

| PARAMETER                                   | SYMBOL                                              | CONE                                          | DITIONS            | MIN                   | TYP   | MAX                   | UNITS |

|---------------------------------------------|-----------------------------------------------------|-----------------------------------------------|--------------------|-----------------------|-------|-----------------------|-------|

| FB2+ Regulation Voltage                     | V <sub>FB2+</sub>                                   |                                               |                    | 1.225                 | 1.25  | 1.275                 | V     |

| FB2- Regulation Voltage                     | V <sub>FB2</sub> -                                  |                                               |                    | -15                   | 0     | 15                    | mV    |

| FB2+, FB2- Input Bias Current               | I <sub>FB2+</sub> ,<br>I <sub>FB2-</sub>            | V <sub>FB2+</sub> = 1.3V, V <sub>FB2-</sub> = | -0.1V              | -100                  |       | 100                   | nA    |

| LX2N, LX2P On-Resistance                    | RON(LX2N),<br>RON(LX2P)                             |                                               |                    |                       | 0.9   | 1.7                   | Ω     |

| LX2N, LX2P Leakage Current                  | I <sub>LKG</sub> (LX2N),<br>I <sub>LKG</sub> (LX2P) | VLX2N = 28V, VLX2P                            | = -10V             |                       | 0.05  | 10                    | μΑ    |

| FB2- Power-Ready Trip Level                 | V <sub>TH</sub> (RDY)                               | Falling edge, 40mV hy                         | ysteresis          | 85                    | 120   | 165                   | mV    |

| FB2+ Power-Ready Trip Level                 | V <sub>TH</sub> (RDY)                               | Rising edge, 40mV hy                          | steresis           | 1.091                 | 1.125 | 1.159                 | V     |

| BACKPLANE DRIVER                            |                                                     |                                               |                    |                       |       |                       |       |

| BPV <sub>DD</sub> Supply Range              | VBPVDD                                              |                                               |                    | 2.5                   |       | 5.5                   | V     |

| BPV <sub>SS</sub> Supply Range              | VBPVSS                                              |                                               |                    | -3                    |       | 0                     | V     |

| BPV <sub>DD</sub> to BPVss Voltage<br>Range | V <sub>VDD</sub> to VSS                             |                                               |                    |                       |       | 5.5                   | V     |

| BPV <sub>DD</sub> Shutdown Current          | ISHDN(BP)                                           | SHDN = GND                                    | SHDN = GND         |                       |       | 10                    | μΑ    |

| BPDRV On-Resistance                         | RON(BPDRV)                                          | Source and sink                               |                    |                       | 0.35  | 0.7                   | Ω     |

| BPDRV Leakage Current                       | ILKG(BPDRV)                                         | SHDN = GND                                    | -10                |                       | 10    | μΑ                    |       |

| BPV <sub>DD</sub> Supply Current            | I <sub>IN</sub> (BPVDD)                             | $V_{BPCLK} = 0 \text{ or } 3.3V$              | VBPCLK = 0 or 3.3V |                       | 80    | 200                   | μΑ    |

| BPCLK Input Low Voltage                     | VIL(BPCLK)                                          |                                               |                    |                       |       | 0.3 x V <sub>IN</sub> | V     |

| BPCLK Input High Voltage                    | VIH(BPCLK)                                          |                                               |                    | 0.7 x V <sub>IN</sub> |       |                       | V     |

| BPCLK Input Current                         | IN(BPCLK)                                           |                                               |                    |                       | 0.01  | 1                     | μΑ    |

| PLL                                         |                                                     |                                               |                    |                       |       |                       |       |

| VCO Center Frequency<br>(Note 1)            | fc                                                  | PLLC = REF, BPCLK :                           | = GND              | 1.63                  | 1.92  | 2.20                  | MHz   |

|                                             |                                                     | CPLLC = 22nF                                  | FPLL = GND         | 20                    |       | 36                    |       |

| BPCLK Input Frequency Range                 | fBPCLK                                              | $R_{PLLC} = 100k\Omega$                       | FPLL = REF         | 27                    |       | 48                    | kHz   |

| Range                                       |                                                     | $C_{SHUNT} = 2.2nF$                           | FPLL = IN          | 40                    |       | 72                    |       |

| Reference Voltage                           | V <sub>REF</sub>                                    | -2μA < I <sub>REF</sub> < 50μA                |                    | 1.225                 | 1.250 | 1.275                 | V     |

| Undervoltage Lockout                        | V <sub>REF(UVLO)</sub>                              |                                               |                    | 0.90                  | 1.05  | 1.20                  | V     |

| LOGIC SIGNALS                               |                                                     |                                               |                    |                       |       |                       |       |

| SHDN Input Low Voltage                      | VIL(SHDN)                                           | (0.10 x V <sub>IN</sub> ) typical hy          | steresis           |                       |       | 0.3 x V <sub>IN</sub> | V     |

| SHDN Input High Voltage                     | VIH(SHDN)                                           |                                               |                    | 0.7 x V <sub>IN</sub> |       |                       | V     |

| SHDN Input Current                          | In(SHDN)                                            |                                               |                    |                       | 0.01  | 1                     | μΑ    |

| FPLL Input Current                          | I <sub>IN(FPLL)</sub>                               | FPLL = GND or IN                              |                    |                       | 0.01  | 1                     | μΑ    |

| RDY Output Low Voltage                      | Vol(RDY)                                            | I <sub>SINK</sub> = 2mA                       |                    |                       | 0.05  | 0.4                   | V     |

| RDY Output High Leakage                     | ILKG(RDYOH)                                         | $V_{RDY} = 5.5V$                              |                    |                       | 0.01  | 1                     | μΑ    |

Note 1: DC-DC 1 operates at one-half of the V<sub>CO</sub> frequency (f<sub>C</sub> / 2).

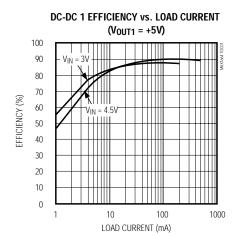

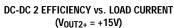

#### 標準動作特性

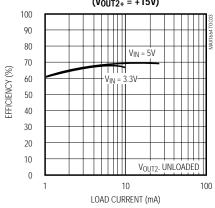

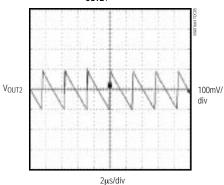

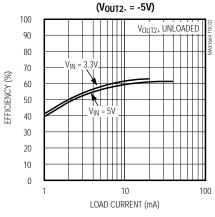

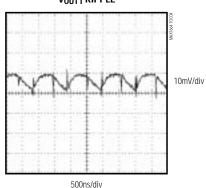

( $f_{BPCLK} = 22.5 \text{kHz}$ , FPLL = GND, L1 =  $3.3 \mu\text{H}$ , L2 =  $4.7 \mu\text{H}$ ,  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

#### V<sub>OUT2+</sub> RIPPLE

$$\begin{split} &V_{OUT2+}=15\text{V},\ V_{IN}=3.3\text{V},\ I_{LOAD}=9\text{mA},\\ &C_{OUT2}=0.22\mu\text{F},\ \text{AC COUPLED} \end{split}$$

## DC-DC 2 EFFICIENCY vs. LOAD CURRENT (VOIT2- = -5V)

#### V<sub>0UT1</sub> RIPPLE

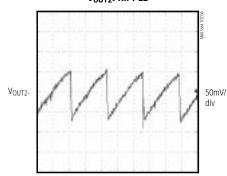

V<sub>0UT2</sub>- RIPPLE

$I_{OUT1}=~250mA,~L=3.3\mu H$

$\begin{array}{c} 5\mu s/div \\ V_{OUT2-} = -5V, \ V_{IN} = 3.3V, \ I_{LOAD} = 5mA, \\ C_{OUT2-} = 0.47\mu F, \ AC \ COUPLED \end{array}$

#### 標準動作特性(続き).

( $f_{BPCLK} = 22.5 \text{kHz}$ , FPLL = GND, L1 =  $3.3 \mu\text{H}$ , L2 =  $4.7 \mu\text{H}$ ,  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

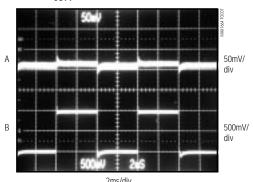

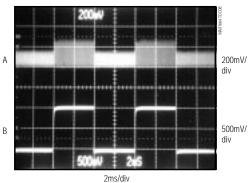

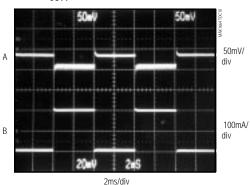

#### **VOUT1 LINE-TRANSIENT RESPONSE**

$V_{OUT1}$  = 5V,  $I_{LOAD}$  = 250mA,  $C_{OUT1}$  =  $20\mu F$  A:  $V_{OUT1}$  , 50mV/div, AC COUPLED B:  $V_{IN}$  , 3V to 4V

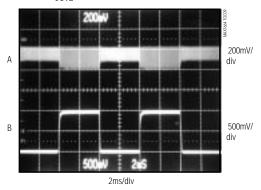

#### V<sub>OUT2</sub>- LINE-TRANSIENT RESPONSE

$V_{OUT2-}$  = -5V,  $I_{LOAD}$  = 5mA,  $C_{OUT2-}$  = 0.47  $\mu F$  A:  $V_{OUT2-}$  , 200mV/div, AC COUPLED B:  $V_{IN}$  , 3V to 4V

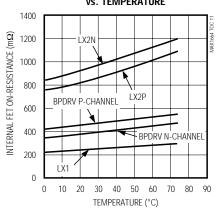

## INTERNAL FET ON-RESISTANCE vs. TEMPERATURE

#### V<sub>OUT2+</sub> LINE-TRANSIENT RESPONSE

$$\begin{split} &V_{OUT2+}=15V,\ I_{LOAD}=5mA,\ C_{OUT2+}=0.22\mu F\\ &A:\ V_{OUT2+},\ 200mV/div,\ AC\ COUPLED\\ &B:\ V_{IN},\ 3V\ to\ 4V \end{split}$$

#### **VOUT1 LOAD-TRANSIENT RESPONSE**

$$\begin{split} &V_{OUT1}=5\text{V, V}_{IN}=3.3\text{V, C}_{OUT1}=20\mu\text{F}\\ &A:V_{OUT1},50\text{mV/div, AC COUPLED}\\ &B:I_{OUT1},25\text{mA TO }225\text{mA, }100\text{mA/div}\\ \end{split}$$

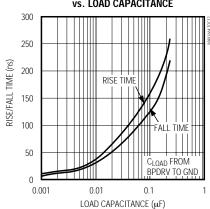

## BPDRV RISE AND FALL TIME vs. Load Capacitance

#### 標準動作特性(続き)\_

(f<sub>BPCLK</sub> = 22.5kHz, FPLL = GND, L1 =  $3.3\mu$ H, L2 =  $4.7\mu$ H, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

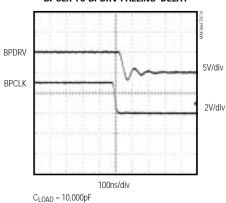

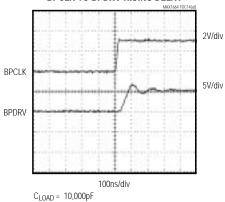

#### **BPCLK TO BPDRV FALLING DELAY**

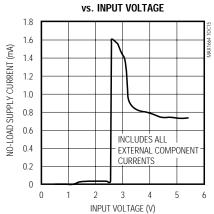

#### NO-LOAD SUPPLY CURRENT

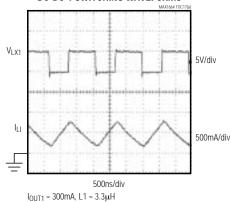

#### DC-DC 1 SWITCHING WAVEFORMS

#### **BPCLK TO BPDRV RISING DELAY**

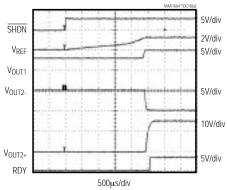

#### **OUT-OF-SHUTDOWN SEQUENCE**

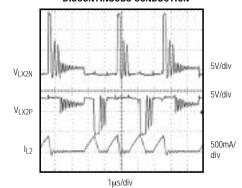

## DC-DC 2 SWITCHING WAVEFORMS DISCONTINUOUS CONDUCTION

$V_{IN}$  = 3.3V;  $V_{OUT2+}$  = 15V/8mA,  $V_{OUT2-}$  = -5V/10mA NOTE: LX2N, LX2P PULSES ARE SYNCHED TO DC-DC 1

#### 端子説明 \_\_\_\_\_\_

| 端子 | 名称                | 機能                                                                                 |

|----|-------------------|------------------------------------------------------------------------------------|

| 1  | SHDN              | シャットダウン入力。ローにするとシャットダウンモードになります。ハイにするか、INに接続すると通常動作になります。SHDNがローの場合は、IC全体がオフになります。 |

| 2  | RDY               | レディインジケータ出力。DC-DC 1及びDC-DC 2。3つの出力全てが10%以内に安定化すると、オープンドレインNチャネル出力がハイインピーダンスになります。  |

| 3  | FB1               | レギュレータフィードバック入力(DC-DC 1)。公称1.25Vに安定化します。                                           |

| 4  | REF               | 内部リファレンス出力。このピンとGNDの間に0.22µFコンデンサを接続してください。REFは最大50µAのソースになります。                    |

| 5  | GND               | アナロググランド。PGND1及びPGND2に接続してください。「電源の接続」及び「レイアウト」の項を参照してください。                        |

| 6  | IN                | ICへの電源入力。入力電圧範囲は+2.8V~+5.5Vです。                                                     |

| 7  | FB2-              | 負出力用のレギュレータフィードバック(DC-DC 2)。公称0Vに安定化します。                                           |

| 8  | FB2+              | 正出力用のレギュレータフィードバック(DC-DC 2)。公称1.25Vに安定化します。                                        |

| 9  | PLLC              | PLL補償。図4に示す方法で補償ネットワークを接続してください。                                                   |

| 10 | BPVss             | バックプレーンドライバの負電源。通常はPGND1に接続します。別電源に接続することもできます。                                    |

| 11 | BPDRV             | バックプレーンドライバ出力                                                                      |

| 12 | BPV <sub>DD</sub> | バックプレーンドライバの正電源。通常はDC-DC 1のV <sub>OUT1</sub> に接続します。別電源に接続することもできます。               |

| 13 | BPCLK             | バックプレーンドライバクロック入力。入力周波数範囲については表1を参照。                                               |

| 14 | INP               | DC-DC 2電源入力。内部LX2P PチャネルMOSFETのソース。                                                |

| 15 | LX2P              | 内部LX2P PチャネルMOSFETのドレイン                                                            |

| 16 | LX2N              | 内部LX2N NチャネルMOSFETのドレイン                                                            |

| 17 | PGND2             | 電源グランド2。PGND1に接続してください。内部LX2N NチャネルMOSFETのソース。                                     |

| 18 | PGND1             | 電源グランド1。PGND2に接続してください。内部LX1N NチャネルMOSFETのソース。                                     |

| 19 | LX1               | 内部LX1 NチャネルMOSFETのドレイン                                                             |

| 20 | FPLL              | PLL同期用のBPCLK入力周波数を設定。GND、REF又はINに接続してください。表1を参照。                                   |

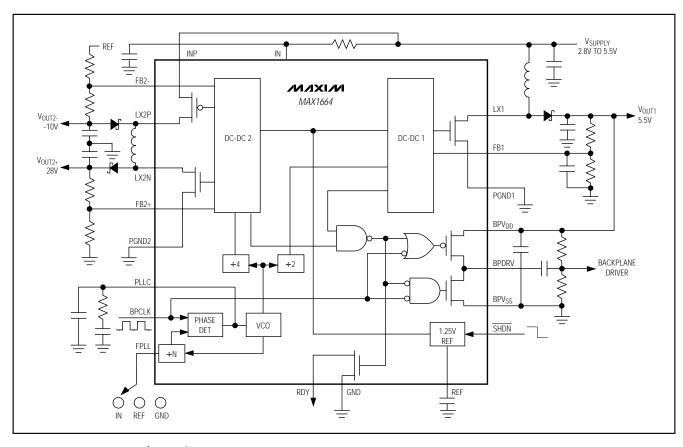

図1. ファンクションダイアグラム

#### 詳細

MAX1664は、アクティブマトリックス薄膜トランジスタ(TFT)液晶ディスプレイ(LCD)用の電源及びバックプレーン駆動回路を1個のICに統合しています。パルス幅変調(PWM)ブーストコンバータ、1個のインダクタを使用したデュアル出力(正及び負)コンバータ、LCDバックプレーンドライバ及び3つの出力全てをバックプレーンクロックに同期させるための位相ロックループ(PLL)を備えています。

高スイッチング周波数特性(公称1MHz)及び位相ロック動作により、出力ノイズを低く抑えつつ薄い小型の外部部品を使用することができます。出力電圧は、+5.5Vまで(DC-DC 1)及び+28V及び-10Vまで(DC-DC 2)調節可能です。負の出力電圧は部品を追加すると-20Vまで調節できます。

DC-DC 1コンバータとバックプレーンクロックの周波数比は16、24又は32に設定できます。この柔軟性により、20kHz~72kHzの範囲のLCDバックプレーンクロックレートに対して高NDC-DCコンバータ周波数が可能です。

#### スタートアップ

スタートアップ時には、 $V_{REF}$ が公称値の90%に達するまで両方のコンバータがディセーブル状態に留まります。 $V_{OUT1}$ が最初に起動します。 $V_{OUT1}$ が安定化状態になると、 $V_{OUT2-}$ がイネーブルされます。 $V_{OUT2+}$ は、 $V_{OUT2-}$ がレギュレーション目標の90%に達するまで0に維持されます。3つの出力は、いずれも電源の投入時とシャットダウンの解除時に同様の順番でパワーアップします。「標準動作特性」の項の「Out-of-Shutdown Sequence」を参照してください。

#### DC-DC 1ブーストコンバータ

DC-DC 1は電流モードブーストPWM構造を使用して、 $3V \sim 5.5V$ (但し、 $V_{IN}$ 以上)の可変安定化正電圧を生成します。このコンバータは、内部NチャネルMOSFET (最大オン抵抗0.5)を使用しています。サイクル毎のピーク電流制限により障害条件でスイッチが保護されます。スタートアップ時には、DC-DC 1が最初にイネーブルされるコンバータとなります。

表1. 選択可能なスイッチング周波数

| FPLL | fBPCLK<br>(kHz) | fDC-DC 1 fDC-DC 2 MAX fDC-DC 1: fDC-DC 2 MA fBPCLK |            | fDC-DC 2 MAX:<br>fBPCLK | N*   |    |

|------|-----------------|----------------------------------------------------|------------|-------------------------|------|----|

| IN   | 40 to 72        | 640 to 1152                                        | 320 to 576 | 16:1                    | 8:1  | 32 |

| REF  | 27 to 48        | 640 to 1152                                        | 320 to 576 | 24:1                    | 12:1 | 48 |

| GND  | 20 to 36        | 640 to 1152                                        | 320 to 576 | 32:1                    | 16:1 | 64 |

#### \* 図2を参照

固定周波数電流モード動作では、スイッチングノイズを動作周波数及び高調波のみに限定できます。スイッチング周波数はバックプレーンクロック入力に位相ロックされます。表1に選択可能なスイッチング周波数を示します。

#### DC-DC 2デュアル出力

DC-DC 2は、同期固定オンタイムPFM構造を使用することによって正及び負の出力電圧を生成します。ドライバICは、これらの出力電圧を使用してTFTゲートをオン/オフします。パルスの発生時にはDC-DC 1に同期されるため、コンバータの相互作用と低調波干渉を最小限に抑えることができます。

DC-DC 2のインダクタ電流は常に断続的であるため、デュアル出力を個別に安定化できます。このため、片方の出力が100%負荷の時に他方を無負荷にすることもできます。

#### DC-DC 2の動作

通常動作ではDC-DC 2は負及び正の出力を交互に充電します(図1)。PFMクロック周期の前半では、NチャネルMOSFET及びPチャネルMOSFETの両方がターンオンして、インダクタL2の両端に入力電圧を印加します。これによりV<sub>INP</sub>に比例するレートでインダクタ電流が直線的に増加します。周期の後半ではPチャネルMOSFETがターンオフして、インダクタのエネルギーが負の出力フィルタコンデンサに転送されます。

この周期の後半でエネルギーの転送が完了し、インダクタ電流がゼロまで減少したと仮定すると、次のクロックサイクルではこのプロセスが正出力の方で繰り返されます。第2のクロックサイクルの前半では、NチャネルMOSFET及びPチャネルMOSFETの両方が再びターンオンします。インダクタ内の電流は、同じレートで再び増加します。第2のクロックサイクルの後半では、NチャネルMOSFETがターンオフして、今度はインダクタのエネルギーが正の出力フィルタコンデンサに転送されます。

重負荷時には、DC-DC2がこのようにして引き続き動作して、負及び正の出力に交互にパルスを供給します。

軽負荷時には、コントローラがいずれかの極性を1サイクル以上スキップすることにより、出力を安定化状態に維持します。最大DC-DC2パルス周波数とバックプレーンクロック周波数の関係については、表1を参照してください。

#### 低ステップアップ又は反転比の出力

DC-DC 2出力電圧の電圧設定値は、最小ステップアップ 又は反転比(例えばV<sub>INP</sub>=5Vの時に、V<sub>OUT+</sub> < 6V又は V<sub>OUT-</sub> > -3V)を必要としますが、適当な出力フィルタ コンデンサヘインダクタエネルギーを転送するために、 1つの半サイクル以上を必要とする場合があります。 こうした場合は、必要に応じてその後の変換サイクルを 1 PFMクロック以上遅延させることによって断続モード 動作を維持します。

#### バックプレーンドライバ

MAX1664は、BPCLK信号をロジックレベルから BPV<sub>DD</sub>/BPV<sub>SS</sub>レベルにレベルトランスレートする低インピーダンスバックプレーンドライバを提供します(図1を参照)。バックプレーンドライバは、Nチャネル/Pチャネルの大電流MOSFETの相補的なペアで構成されています。これらのデバイスは、BPCLKがハイ又はローになった時に、それぞれBPDRVをBPV<sub>DD</sub>又はBPV<sub>SS</sub>に駆動します。スイッチの最大オン抵抗は0.7、標準伝播遅延は50nsです。バックプレーンドライバの電源は、DC-DC1の出力( $V_{OUT1}$ )から取ることができます(「標準動作回路」を参照)。

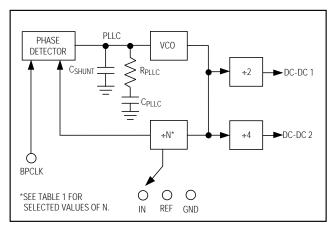

#### 位相ロックループ

MAX1664は、PWM及びPFMコンバータクロックをバックプレーンクロックに同期させるためのPLLを内蔵しています(図2)。これによりノイズ及び干渉が最小限に抑えられます。PLLは周波数逓倍タイプで、DC-DC1用に公称1MHzクロック信号、DC-DC2用に公称500kHzクロック信号を生成します。20kHz~72kHzにわたって3つの入力周波数範囲があるため、最適変換周波数を維持しつつ、広範囲のバックプレーンクロック入力周波数に同期できます(表1)。

図2. MAX1664の内部PLL動作

PLLの心臓部は、制御電圧(PLLCピン)1.250Vに対して公称周波数が1.92MHzになるようにトリミングされたVCOです。この高周波内部クロックがディジタルで分周されます。分周比は、FPLLピンをGND、REF又はINに接続することによって選択されます。この分周されたクロックが、内部位相コンパレータ(立上がリエッジトリガ)によってバックプレーンクロックと比較されます。そして今度は、位相ディテクタがVCO制御電圧を調節して2つの周波数(及び位相)を一致させます。このフィードバックループはPLLCピンにおいて補償されます。

一部のアプリケーションでは、スクリーンスキャンとスクリーンスキャンの間でバックプレーンクロックが数サイクル停止されたり、電源投入時にすぐに印加されない場合があります。本PLLは、2サイクル以上のクロックドロップアウトがあっても周波数誤差を最小限に抑え、クロックが再開した時に直ちにロックを再確立する独自の位相ディテクタ構造を採用しています。

#### レディインジケータ(RDY)

RDYピンはオープンドレイン出力を備えており、3つの出力全てがレギュレーション状態になっていることを知らせます。3つのコンバータ出力がレギュレーション設定値から10%以内になると、このオープンドレイン出力はハイインピーダンスになります。

#### 設計手順及び部品の選択 \_\_\_\_\_

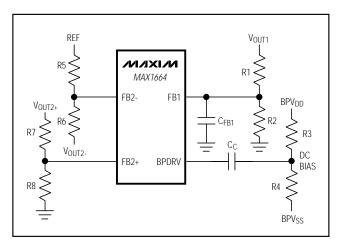

#### 出力電圧の選択

MAX1664の3つの出力電圧及びバックプレーンクロックのDCバイアスは調節可能です(図3を参照)。2つの標準1%抵抗を使用して、選択された出力と対応するフィードバックピンの間に分圧器を形成することにより、各出力を設定してください。抵抗の値は次式で計算してください。

図3. 出力電圧の選択

#### DC-DC 1出力

$V_{OUT1}$ = 5Vの場合、標準値はR2 = 100k 及びR1 = 301k です。 $V_{OUT1}$ を別の電圧に設定するには、R2 = 100k 、 $C_{FB1}$ = 50pFとして次式でR1を計算してください。

$$R1 = R2 \left( \frac{V_{OUT1}}{V_{FB1}} - 1 \right)$$

#### DC-DC 2の正出力

$V_{OUT2+}$  = 15Vの場合、標準値はR8 = 49.9k 及び R7 = 549k です。 $V_{OUT2+}$ を別の電圧に設定するには、R8 = 49.9k として次式でR7を計算してください。

$$R7 = R8 \left( \frac{V_{OUT2+}}{V_{FR2+}} - 1 \right)$$

#### DC-DC 2の負出力

負出力電圧の場合、 $FB2-スレッショルド電圧は0です。 <math>V_{OUT2-} = -5V$ の場合、標準値はR5 = 49.9k 及び R6 = 200k です。 $V_{OUT2+}$ を別の電圧に設定するには、R5 = 49.9k として次式でR6を計算してください。

$$R6 = R5 \left| \frac{V_{OUT2}}{V_{RFF}} \right|$$

#### バックプレーンドライバのDCバイアス

$V_{DCBIAS} = V_{BPVDD}/2$ の場合、標準値はR3 = R4 = 100k です。DCバイアスを別の値に設定するには、R4を選択してから次式でR3を計算してください。

$$R3 = R4 \left( \frac{V_{BPVDD} - V_{BPVSS}}{V_{DCBIAS} - V_{BPVSS}} - 1 \right)$$

図4. 標準動作回路の詳細図

#### インダクタの選択

L1の最適インダクタ値は $3.3\mu$ Hです(図4参照)。最高の効率を得るためには、DC直列抵抗が300m 以下のインダクタを推奨します。L1をこれより大きくすると(例えば $4.7\mu$ H)、ピークリップル電流が減少してDC-DC 1の出力電流能力が増加します。但し、サイズが大きくなりループ安定性に必要な出力フィルタ容量が増えます。

DC-DC 2における高入力電圧(5V)かつ低スイッチング 周波数(400kHz以下)の条件では、L2の値を増やして (例えば6.8µH又は10µH)ピーク電流を制限してください。場合によっては、DC-DC 2の出力電流能力を増やすためにL2の値を減らすことが必要になることもあります(表2)。DC-DC 2の入力電圧、出力電圧、スイッチング周波数、インダクタ値及び最大負荷電流の間の関係は、複雑で非線形です。この関係は表2にまとめられています。L2の式は下記のとおりです。

$$L2 > \frac{V_{\text{INP}} - \left[R_{\text{ON(LX2P)}} + R_{\text{ON(LX2N)}} + R_{L2}\right] \frac{(I_{\text{PEAK}})}{2}}{I_{\text{PEAK}} \times 2 \left(f_{\text{DC-DC 1}}\right)}$$

ここで、

内部MOSFETオン抵抗:

$R_{ON(LX2P)} = R_{ON(LX2N)} = 0.9$  (typ)

外部インダクタDC抵抗:

$R_{L2} = 0.3$  (typ)

インダクタピーク電流:

I<sub>PEAK</sub> = 700mA(絶対最大値750mA)

MAX1664はスイッチング周波数が高いため、フェライトのような高周波コア材質のインダクタを推奨します。鉄粉入りはコア損失が大きいため推奨できません。標準的な小型薄型インダクタとしては、ILS-3825 (Dale Electronics-Vishay)及びCLQ61B(スミダ電機)が挙げられます。これらのインダクタは、主に薄さが要求されるDC-DCコンバータに使用されます。薄型インダクタを提供しているメーカについては、表3を参照してください。

表2. 標準的なDC-DC 2の動作

| V <sub>OUT2+</sub> (V) | V <sub>OUT2-</sub><br>(V) | V <sub>IN</sub> (V) | fBPCLK<br>(kHz) | L2<br>(µH) | I <sub>OUT2+(MAX)</sub><br>(mA) | I <sub>OUT2-(MAX)</sub><br>(mA) | f <sub>DC-DC</sub> 2(MAX)<br>(kHz) | INDUCTOR PEAK<br>CURRENT*<br>(mA) |

|------------------------|---------------------------|---------------------|-----------------|------------|---------------------------------|---------------------------------|------------------------------------|-----------------------------------|

| +15                    | -5                        | 3.0                 | 22.5            | 4.7        | 6                               | 15                              | 360                                | 375                               |

| +15                    | -5                        | 3.0                 | 22.5            | 2.7        | 8                               | 23                              | 360                                | 585                               |

| +15                    | -5                        | 3.3                 | 22.5            | 4.7        | 7                               | 19                              | 360                                | 425                               |

| +15                    | -5                        | 3.3                 | 22.5            | 2.7        | 10                              | 27                              | 360                                | 643                               |

| +15                    | -5                        | 4.5                 | 22.5            | 4.7        | 15                              | 35                              | 360                                | 550                               |

| +15                    | -5                        | 5.0                 | 22.5            | 4.7        | 20                              | 43                              | 360                                | 600                               |

| +20                    | -10                       | 3.0                 | 22.5            | 4.7        | 3                               | 6                               | 360                                | 385                               |

| +20                    | -10                       | 3.0                 | 22.5            | 2.7        | 5                               | 10                              | 360                                | 585                               |

| +20                    | -10                       | 3.0                 | 25.0            | 4.7        | 2                               | 5                               | 400                                | 340                               |

| +20                    | -10                       | 3.0                 | 25.0            | 2.7        | 4                               | 8                               | 400                                | 530                               |

| +20                    | -10                       | 3.0                 | 30.0            | 4.7        | 3                               | 4                               | 480                                | 300                               |

| +20                    | -10                       | 3.0                 | 30.0            | 2.7        | 3                               | 6                               | 480                                | 451                               |

| +20                    | -10                       | 3.3                 | 22.5            | 4.7        | 4                               | 8                               | 360                                | 425                               |

| +20                    | -10                       | 3.3                 | 22.5            | 2.7        | 6                               | 12                              | 360                                | 643                               |

| +20                    | -10                       | 3.3                 | 25.0            | 4.7        | 4                               | 7                               | 400                                | 370                               |

| +20                    | -10                       | 3.3                 | 25.0            | 2.7        | 6                               | 10                              | 400                                | 583                               |

| +20                    | -10                       | 3.3                 | 30.0            | 4.7        | 4                               | 5                               | 480                                | 340                               |

| +20                    | -10                       | 3.3                 | 30.0            | 4.7        | 4                               | 8                               | 480                                | 496                               |

| +20                    | -10                       | 4.5                 | 22.5            | 4.7        | 9                               | 16                              | 360                                | 580                               |

| +20                    | -10                       | 4.5                 | 25.0            | 4.7        | 8                               | 14                              | 400                                | 500                               |

| +20                    | -10                       | 4.5                 | 30.0            | 4.7        | 8                               | 12                              | 480                                | 450                               |

| +20                    | -10                       | 4.5                 | 30.0            | 2.7        | 10                              | 17                              | 480                                | 679                               |

| +20                    | -10                       | 5.0                 | 22.5            | 4.7        | 11                              | 20                              | 360                                | 640                               |

| +20                    | -10                       | 5.0                 | 25.0            | 4.7        | 10                              | 18                              | 400                                | 550                               |

| +20                    | -10                       | 5.0                 | 30.0            | 4.7        | 10                              | 15                              | 480                                | 500                               |

<sup>\*</sup>注記:LX2P及びLX2Nにおける絶対最大ピーク電流は750mAです。

#### ダイオードの選択

MAX1664はスイッチング周波数が高いため、高速ダイオードを必要とします。MBR0520L及びMBR0540L(Motorola)等のショットキダイオードは、薄型SOD-123パッケージでしかも必要な電力定格を持っているため推奨できます。高さ1.1mmのMBRM5817も推奨できます。順方向電流定格が下記の値よりも大きなショットキダイオードを使用してください。

$$I_F > \frac{I_{OUT} V_{OUT}}{0.9 V_{INI}}$$

DC-DC 2の正出力用には、電圧定格が $V_{OUT2+}$ を超えるショットキダイオードをご使用ください。負出力の場合は、定格が $V_{IN}+|V_{OUT2-}|$ を超えるショットキダイ

オードをご使用ください。ショットキダイオードの メーカについては、表3を参照してください。

#### フィルタコンデンサの選択

次式に示すように、出力フィルタコンデンサのESR及び サイズは、スイッチングコンバータの出力リップルに 大きな影響を与えます。

$$V_{RIPPLE(PK-PK)} \cong I_{PEAK} \times R_{ESR} + I_{OUT} \left(\frac{t_{ON}}{C_{OUT}}\right)$$

$$DC - DC \ 1 \ t_{ON} = \frac{1}{f_{DC-DC \ 1}} \left(\frac{V_{OUT1} + V_F - V_{IN}}{V_{OUT1} + V_F}\right)$$

$$DC - DC \ 2 \ t_{ON} = \frac{1}{2 \ f_{DC-DC \ 1}}$$

セラミックコンデンサは、ESRが低く薄いためお勧めできます。標準的なセラミックコンデンサは、TDKのC3225X5Rシリーズ及びTaiyo YudenのJMK325シリーズです。表面実装セラミックコンデンサのメーカについては、表3を参照してください。

#### PLL補償

殆どのアプリケーションでは、図4に示す推奨補償部品 定数により最適のシステム性能が得られます。バック プレーンクロックが使用されていない場合は、PLLCを REFに接続してください。

#### 表3. 部品メーカ

| MANUFACTURER              | PHONE          | FAX            |

|---------------------------|----------------|----------------|

| INDUCTORS                 | •              |                |

| Dale Inductors            | (605) 668-4131 | (605) 665-1627 |

| Sumida USA                | (847) 956-0666 | (847) 956-0702 |

| DIODES                    |                |                |

| Central Semiconductor     | (516) 435-1110 | (516) 435-1824 |

| International Rectifier   | (310) 322-3331 | (310) 322-3232 |

| Motorola                  | (602) 303-5454 | (602) 994-6430 |

| CERAMIC CAPACITOR         | S              |                |

| Marcon/United<br>Chemicon | (847) 696-2000 | (847) 696-9278 |

| TDK                       | (847) 390-4373 | (847) 390-4428 |

| Taiyo Yuden               | (408) 573-4150 | (408) 573-4159 |

| Vishay/Vitramon           | (203) 268-6261 | (203) 452-5670 |

#### アプリケーション情報

#### V<sub>OUT</sub>を5.5V以上にする場合

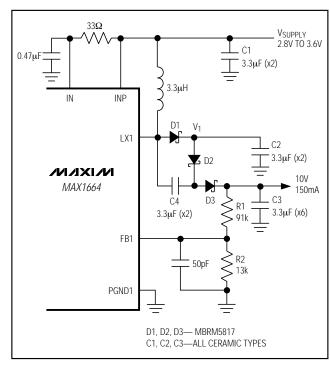

$V_{OUT1}$ 出力電圧を5.5V以上にするには、図5に示すように補助チャージポンプ回路を接続してください。図示の接続により、10V、150mAの出力が得られます。適当なR1及びR2の値を選ぶことにより、 $2 \times V_{IN} 10V$ の範囲の電圧も可能です(「DC-DC 1出力」の項を参照)。 $C2 \sim C4$ は1.1mmの高さ制限を満たすように、3.3 $\mu F$ セラミックコンデンサの並列構成になっています。高さが制限されない場合は、並列構成の代わりに値の大きなコンデンサを使用できます。

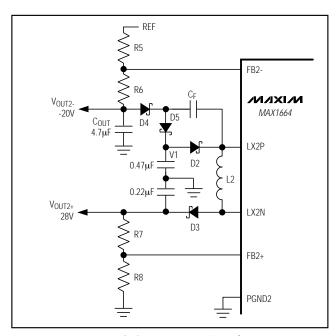

#### 3.3 Vから-20 Vへのチャージポンプ構成

-20Vまでの負電圧を必要とするアプリケーションでは、 $V_{OUT2}$ -出力に反転チャージポンプブロックを追加できます(図6)。 $C_F$ 及び $C_{OUT}$ の標準的な値は、それぞれ

図5. V<sub>OUT1</sub>を5.5V以上にするためのチャージポンプ 構成

- $0.47\mu F \sim 1\mu F$ 及び $4.7\mu F \sim 10\mu F$ です。原則として、 $C_{OUT}$ を $C_F$ の10倍にしてください。この回路の動作は、以下の通りです。

- 1) V1の電圧は、最初のPFMサイクル中、インダクタ L2によって最終的な定常状態電圧の数分の一程度 まで充電されます。これは「詳細」で説明した通常の 動作と同じです。

- 2) 次のPFMサイクルの前半で、ピンLX2Pが $V_{INP}$ に 内部接続され、コンデンサ $C^F$ は( $V_{INP}$ = +  $V_1$ !  $V_D$ ) まで充電されます。ここで、 $V_D$ はダイオードの順方 向電圧です。

- 3) それに続く後半サイクルでLX2Pが負に変化してV1 以下になると、コンデンサ $C_F$ はエネルギーの一部を出力コンデンサ $C_{OUT}$ に転送します。これにより、 $C_{OUT}$ は約( $V_{INP}$  + 2 x  $|V_1|$  2 x  $|V_D|$ の負電圧まで充電されます。

- 4) このプロセスは、 $V_{OUT}$ が希望の電圧(FB2-フィードバック抵抗の比によって決定)に達するまで続きます。

- 5) 定常状態(レギュレーション状態)動作では、LX2Pの電圧の絶対値は( $V_{OUT}$ )2  $V_{INP}$ 2 +  $V_{D}$ )に等しくなりますが、この値は10V以内に制限することが必要です。

#### 電源の接続及びレイアウト

MAX1664は高精度アナログ機能及び大電力スイッチング機能の両方を持っています。電源接続、バイパス及びレイアウトには十分注意してください。INのINPの間に33 のアイソレーション抵抗(図4のR9)を使用して、バイパスしてください。さらに、DC-DC 1の安定性を確保するために、INPバスに十分な低ESRバイパスが必要です。

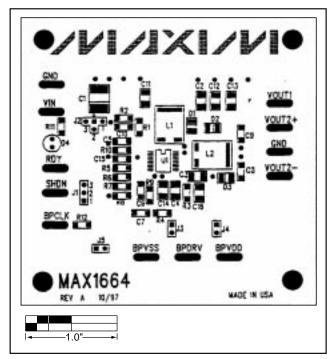

電力部品の下にソリッドグランドプレーンを設け、アナログノードの下には別のグランドプレーンを設けることを特にお勧めします。これらのグランドプレーン同士を単一の電圧変動の少ないポイントで接続してください。アナログリファレンス及びフィードバック信号は、アナロググランドプレーンを基準とし、アナロググランドプレーンの上に配線してください。図7に個別のグランドプレーンを使用した標準レイアウトを示します。

図6. VOUT2-電圧ダブラチャージポンプ

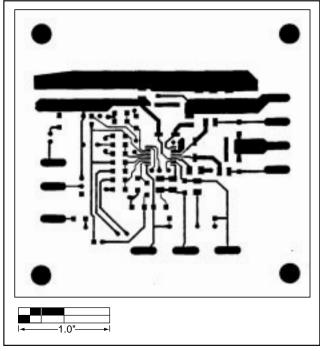

図7a. MAX1664の部品配置図

図7b. MAX1664のプリント基板レイアウト(部品面側)

# MAX1664

## アクティブマトリックス液晶ディスプレイ (AMLCD)電源

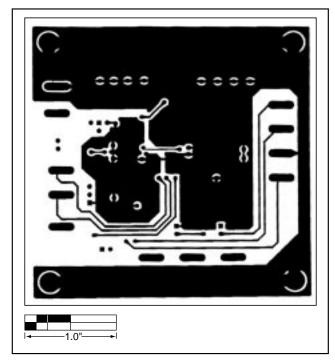

図7c. MAX1664のプリント基板レイアウト(ハンダ面側)

| チッ | プ情報 |  |  |  |  |  |  |  |

|----|-----|--|--|--|--|--|--|--|

|    |     |  |  |  |  |  |  |  |

**TRANSISTOR COUNT: 838**

パッケージ \_\_\_\_\_

販売代理店

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600