# MIXIM

### 広輝度範囲の CCFLバックライトコントローラ

#### 概要

MAX1739/MAX1839は、業界で性能実証済みのRoyer 発振器インバータ構造を使用して冷陰極蛍光ランプ (CCFL)を駆動するために最適化されたコントローラ です。Royer構造は、全入力範囲に渡ってサイン波に 近い駆動波形を提供することによってCCFLの寿命を 最大限に延ばします。MAX1739/MAX1839において は、高効率を達成し、調光範囲を最大限に拡張し、広い 入力電圧範囲(4.6V~28V)で動作するようにこの構造 が最適化されています。

MAX1739/MAX1839は、トランスのセンタータップ 電圧を監視・制限することでトランスへの電圧ストレスを 最小限に抑え、動作寿命の延長と設計条件の緩和を 実現しています。本コントローラはまた、ランプ切れ、 バック短絡その他の障害条件に対する保護も提供して います。

本コントローラは、ランプ電流を調整すると同時にCCFL をオン/オフに「チョッピング」することにより、50:1の 調光範囲を達成しています。このチョッピングは、 ディジタル調整のパルス幅変調(DPWM)法によって 行われています。CCFLの輝度はアナログ電圧を印加 するか、あるいはSMBus™コンパチブルの2線インタ フェース(MAX1739)を使用して制御できます。

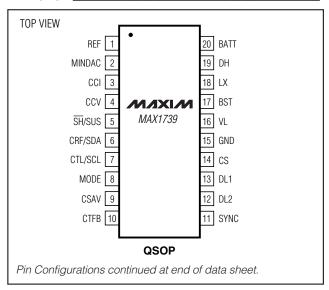

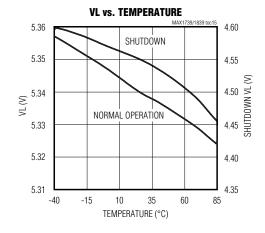

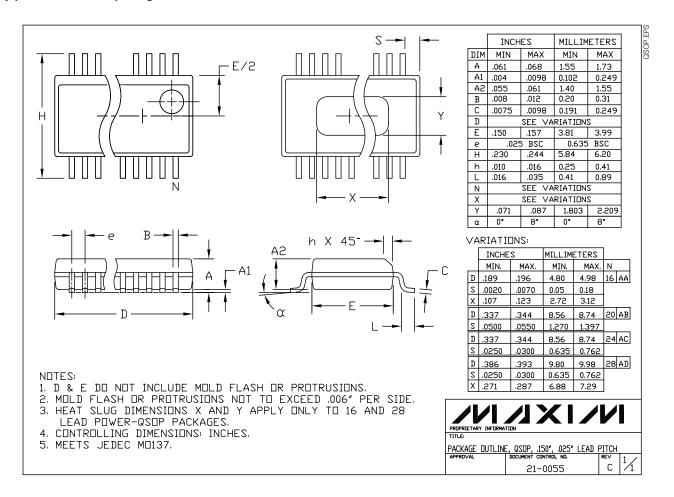

MAX1739/MAX1839は外部ハイサイドNチャネル パワーMOSFETと2つのローサイドNチャネルパワー MOSFETを駆動します(これらは全てRoyer発振器に同 期されています)。内部5.3Vリニアレギュレータが MOSFETドライバと内部回路の大部分を駆動します。 MAX1739/MAX1839は省スペースの20ピンQSOP パッケージで提供されており、温度範囲は拡張工業用 (-40°~+85°)のものが用意されています。

#### アプリケーション

ノートブック/ラップトップコンピュータ

自動車ナビゲーションディスプレイ

LCDモニタ

POS端末

ポータブルディスプレイエレクトロニクス

†特許申請中

SMBusはIntel Corp.の商標です。

#### 特長

- ◆ 入力変化に迅速に応答

- ◆ 広入力電圧範囲: 4.6V~28V

- ◆ 高い電力―光変換効率

- ◆ トランスの電圧ストレスが最小限

- ◆ 2秒のタイムアウトによるランプ出力保護

- ◆ 降圧スイッチの短絡および他の1点障害の保護

- ♦ Royer MOSFETドライバ内臓でトランスの 端子数を削減

- ◆ Royer発振器に同期された降圧動作

- ◆ 同期可能なDPWM周波数

- ◆ 輝度制御インタフェースはピン選択可能

- ♦ SMBusシリアルインタフェース(MAX1739)

- ◆ アナログインタフェース(MAX1739/MAX1839)

#### 型番

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1739EEP | -40°C to +85°C | 20 QSOP     |

| MAX1839EEP | -40°C to +85°C | 20 QSOP     |

#### ピン配置

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| 0.3V to 30V                     |

|---------------------------------|

| 0.3V to 34V                     |

| 0.3V to 6V                      |

| 0.3V to $(V_{BST} + 0.3V)$      |

| 6V to (V <sub>BST</sub> + 0.3V) |

| 0.3V to 6V                      |

| 0.3V to $(VL + 0.3V)$           |

| 0.3V to 6V                      |

| 0.6V to $(VL + 0.3V)$           |

|                                 |

| V <sub>MODE</sub> to GND                             | 6V to 12V      |

|------------------------------------------------------|----------------|

| VCRF/SDA, VCRF, VCTL/SCL, VCTL, VSH/SUS,             |                |

| V SH to GND                                          | 0.3V to 6V     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C | <del>(</del> ) |

| 20-Pin QSOP (derate 9.1mW/°C above +                 | +70°C)727mW    |

| Operating Temperature                                | 40°C to +85°C  |

| Storage Temperature                                  | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                    | +300°C         |

|                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+=8.2V,\ V_{\overline{SH}}/SUS=V_{\overline{SH}}=5.5V,\ MINDAC=GND,\ \textbf{T_A=0°C to +85°C},\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ T_A=+25°C.)$

|                                                  | ••                                                                          |                         |      |      |     |       |

|--------------------------------------------------|-----------------------------------------------------------------------------|-------------------------|------|------|-----|-------|

| PARAMETER                                        | CONDITIONS                                                                  |                         | MIN  | TYP  | MAX | UNITS |

| SUPPLY AND REFERENCE                             |                                                                             |                         | 1    |      |     |       |

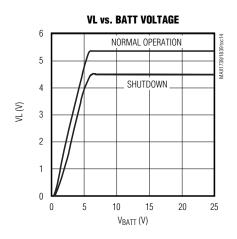

| V Lagrat Valtaga Dagas                           | V <sub>L</sub> = V <sub>BATT</sub>                                          |                         | 4.6  |      | 5.5 | V     |

| V <sub>BATT</sub> Input Voltage Range            | V <sub>L</sub> = open                                                       |                         | 6    |      | 28  | V     |

| VBATT Quiescent Current, Operation               | DH = DL1 = DL2 = open                                                       | V <sub>BATT</sub> = 28V |      | 3.2  | 6   | mA    |

| with Full Duty Cycle on DH                       | DIT = DET = DEZ = Open                                                      | $V_{BATT} = V_{L} = 5V$ |      | 3.2  | 6   |       |

| VBATT Quiescent Current, Shutdown                | $\overline{SH}/SUS = \overline{SH} = GND$                                   |                         |      | 6    | 20  | μΑ    |

| VL Output Voltage, Normal Operation              | 6V < V <sub>BATT</sub> < 28V, 0 < I <sub>LOAI</sub>                         | <sub>D</sub> < 15mA     | 5.0  | 5.35 | 5.5 | V     |

| VL Output Voltage, Shutdown                      | $\overline{SH}/SUS = \overline{SH} = GND$ , no loa                          | ad                      | 3.5  | 4.5  | 5.5 | V     |

| VI Undervoltage Leekout Threehold                | VL rising (leaving lockout)                                                 |                         |      |      | 4.6 |       |

| VL Undervoltage Lockout Threshold                | VL falling (entering lockout)                                               |                         | 4.0  |      |     | V     |

| VL Undervoltage Lockout Hysteresis               |                                                                             |                         |      | 300  |     | mV    |

| REF Output Voltage, Normal Operation             | 4.5V < VL < 5.5V, I <sub>REF</sub> = 40µ                                    | 1.96                    | 2.00 | 2.04 | V   |       |

| V <sub>L</sub> POR Threshold                     |                                                                             | 0.9                     |      | 2.7  | V   |       |

| SWITCHING REGULATOR                              |                                                                             |                         | 1    |      |     |       |

| DH Driver On-Resistance                          |                                                                             |                         |      |      | 18  | Ω     |

| DL1, DL2 Driver On-Resistance                    |                                                                             |                         |      |      | 18  | Ω     |

| Minimum DH Switching Frequency                   | 1/t <sub>DH</sub> , SYNC = CS or GND, r                                     | not synchronized        | 49   | 56   | 64  | kHz   |

| DH Minimum Off-Time                              |                                                                             |                         | 250  | 375  | 500 | ns    |

| DH Maximum Duty Cycle                            |                                                                             |                         |      | 98   |     | %     |

| SYNC Synchronization Range                       | Detect falling edges on SYN                                                 | IC                      | 64   |      | 200 | kHz   |

| SYNC Input Current                               | 0 < V <sub>SYNC</sub> < 30V                                                 |                         | -2   |      | 2   | μΑ    |

| SYNC Input Threshold                             | SYNC falling, referred to CS                                                |                         |      | 500  | 600 | mV    |

| SYNC Input Hysteresis                            | Referred to the SYNC input threshold                                        |                         |      | 100  | 150 | mV    |

| SYNC Threshold Crossing to DL1, DL2 Toggle Delay | V <sub>SYNC</sub> = 0 to 5V, C <sub>DL_1</sub> and 50% point on SYNC to 50% |                         |      |      | 120 | ns    |

| CS Overcurrent Threshold                         |                                                                             |                         | 408  | 450  | 492 | mV    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=8.2V, V_{\overline{SH}}/SUS=V_{\overline{SH}}=5.5V, MINDAC=GND, T_A=0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER                                           | С                                                 | ONDITIONS                    | MIN      | TYP  | MAX  | UNITS    |

|-----------------------------------------------------|---------------------------------------------------|------------------------------|----------|------|------|----------|

| DAC AND ERROR AMPLIFIER                             |                                                   |                              |          |      |      |          |

| DAC Resolution                                      | Guaranteed monoto                                 | pnic                         | 5        |      |      | Bits     |

| MINDAC Input Voltage Range                          |                                                   |                              |          |      | 2    | V        |

| MINDAC Input Bias Current                           | 0 < V <sub>MINDAC</sub> < 2V                      |                              | -1       |      | 1    | μΑ       |

| MINDAC Digital PWM Disable                          | MINDAC = VL                                       |                              | 2.4      | 2.9  | 4    | V        |

| Threshold                                           | WIII VID NO = VL                                  |                              |          | 2.0  |      |          |

| CSAV Input Voltage Range                            |                                                   |                              | 0        |      | 0.8  | V        |

| 22.11.                                              |                                                   | code = 11111 binary          | 188      | 194  | 200  | <u> </u> |

| CSAV Regulation Point                               |                                                   | code = 00001 binary          | 2        | 6.25 | 16   | mV       |

|                                                     | $V_{MINDAC} = 1V, DAC$                            | C code = 00000 binary        | 93       | 100  | 110  |          |

| CSAV Input Bias Current                             |                                                   |                              | -1       |      | 1    | μΑ       |

| CSAV to CCI Transconductance                        | 1V < V <sub>CCI</sub> < 2.7V                      |                              |          | 100  |      | μmho     |

| CTFB Input Voltage Range                            |                                                   |                              | 0        |      | 2    | V        |

| CTFB Input Bias Current                             |                                                   |                              | -1       |      | 1    | μΑ       |

| CTFB Regulation Point                               |                                                   |                              | 570      | 600  | 630  | mV       |

| CTFB to CCV Transconductance                        | $1V < V_{CCV} < 2.7V$                             |                              | 30       | 40   | 50   | μmho     |

| TIMERS AND FAULT DETECTION                          |                                                   |                              |          |      |      |          |

| Chopping Oscillator Frequency                       | No AC signal on MODE, not synchronized            |                              | 24       | 28   | 32   | kHz      |

| Digital PWM Chop-Mode Frequency                     | No AC signal on MODE                              |                              | 205      | 220  | 235  | <u> </u> |

|                                                     | 32kHz AC signal on MODE                           |                              |          | 250  |      | Hz       |

|                                                     | 100kHz AC signal on MODE                          |                              |          | 781  |      |          |

| MODE to DPWM Sync Ratio                             | FMODE / FDPWM                                     |                              |          | 128  |      |          |

| Lamp-Out Detection Timeout Timer                    | V <sub>CSAV</sub> < CSAV                          | No AC signal on MODE         | 2.06     | 2.33 | 2.73 | S S      |

| (Center-Tap Voltage Stuck at                        | lamp-out                                          | 32kHz AC signal on MODE      |          | 2.05 |      |          |

| Maximum) (Note 1)                                   | threshold 100kHz AC signal on MODE                |                              |          | 0.66 |      |          |

| CSAV Lamp-Out Threshold                             |                                                   |                              | 50       | 75   | 100  | mV       |

| Fault-Detection Threshold on CCV                    | (Note 2)                                          | T                            | 0.4      |      | 1    | V        |

| Shorted Buck-Switch Detection                       | V <sub>CCV</sub> < fault-                         | No AC signal on MODE         | 332      | 291  | 259  |          |

| Timeout Timer (UL1950 Protection)                   | detection                                         | 32kHz AC signal on MODE      |          | 256  |      | ms       |

| (Note 3)                                            | threshold on CCV                                  | 100kHz AC signal on MODE     |          | 82   |      |          |

| Lamp Turn-On Delay                                  | After SH/SUS or SH                                | forces device on or SH rises |          | 4    |      | ms       |

| MODE Operating Voltage Range                        |                                                   |                              | -5.5     |      | 11   | V        |

| MODE = GND Threshold<br>(min Brightness = 0)        | To sync DPWM oscillator, not in shutdown (Note 4) |                              |          |      | 0.6  | V        |

| MODE = REF Threshold<br>(max Brightness = 0)        | To sync DPWM oscillator, not in shutdown (Note 4) |                              | 1.4      |      | 2.6  | V        |

| MODE = VL Threshold<br>(MAX1739 SMB Interface Mode) | To sync DPWM oscillator, not in shutdown (Note 4) |                              | VL - 0.6 |      |      | V        |

| MODE AC Signal Amplitude                            | Peak to peak (Note                                | 5)                           | 2        |      |      | V        |

| MODE AC Signal Synchronization Range                | · · · · · · · · · · · · · · · · · · ·             | synchronized to MODE AC      | 32       |      | 100  | kHz      |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=8.2V, V_{\overline{SH}}/SUS=V_{\overline{SH}}=5.5V, MINDAC=GND, \textbf{T}_{\textbf{A}}=\textbf{0}^{\circ}\textbf{C} \text{ to } +\textbf{85}^{\circ}\textbf{C}, \text{ unless otherwise noted. Typical values are at } T_{A}=+25^{\circ}C.)$

| PARAMETER                                                                  | CONDITIONS                                | MIN                       | TYP        | MAX         | UNIT |

|----------------------------------------------------------------------------|-------------------------------------------|---------------------------|------------|-------------|------|

| ANALOG INTERFACE BRIGHTNESS                                                | CONTROL (MODE connected to REF or GND )   | •                         |            |             |      |

| CRF/SDA, CRF Input Range                                                   |                                           | 2.7                       |            | 5.5         | V    |

| CDE/CDA CDE Input Current                                                  | VCRF/SDA = VCRF = 5.5V                    |                           |            | 20          | μΑ   |

| CRF/SDA, CRF Input Current                                                 | VCRF/SDA = VCRF = 5.5V, SH/SUS = SH = 0   | -1                        |            | 1           | μΑ   |

| CTL/SCL, Input Range                                                       | MAX1739                                   | 0                         |            | CRF/<br>SDA | V    |

| CTL Input Range                                                            | MAX1839                                   | 0                         |            | CRF         | V    |

| CTL/SCL, CTL Input Current                                                 | MODE = REF or GND                         | -1                        |            | 1           | μΑ   |

| ADC Resolution                                                             | Guaranteed monotonic                      |                           | 5          |             | Bits |

| ADC Hysteresis                                                             |                                           |                           | 1          |             | LSB  |

| SH Input Low Voltage                                                       |                                           |                           |            | 0.8         | V    |

| SH Input High Voltage                                                      |                                           | 2.1                       |            |             | V    |

| SH/SUS Input Hysteresis when<br>Transitioning In and Out of Shutdown       |                                           |                           | 150        |             | mV   |

| SH Input Bias Current                                                      |                                           | -1                        |            | 1           | μΑ   |

| SYSTEM MANAGEMENT BUS BRIGH                                                | TNESS CONTROL (MAX1739, MODE connected to | V <sub>L</sub> , see Figu | ıres 12 an | d 13)       |      |

| CRF/SDA, CTL/SCL, SH/SUS Input                                             |                                           |                           |            | 0.8         | V    |

| CRF/SDA, CTL/SCL, SH/SUS Input                                             |                                           | 2.1                       |            |             | V    |

| CRFSDA, CTLSCL Input Hysteresis                                            |                                           |                           | 300        |             | mV   |

| CRF/SDA, CTL/SCL, SH/SUS Input                                             |                                           | -1                        |            | 1           | μΑ   |

| CRF/SDA Output Low Sink Current                                            | VCRF/SDA = 0.4V                           | 4                         |            |             | mA   |

| CTL/SCL Serial Clock High Period                                           | thigh                                     | 4                         |            |             | μs   |

| CTL/SCL Serial Clock Low Period                                            | tLOW                                      | 4.7                       |            |             | μs   |

| Start Condition Setup Time                                                 | tsu:sta                                   | 4.7                       |            |             | μs   |

| Start Condition Hold Time                                                  | thd:sta                                   | 4                         |            |             | μs   |

| CRF/SDA Valid to CTL/SCL Rising Edge<br>Setup Time, Slave Clocking in Data | tsu:dat                                   | 250                       |            |             | ns   |

| CTL/SCL Falling Edge to CRF/SDA<br>Transition                              | t <sub>HD:DAT</sub>                       | 0                         |            |             | ns   |

| CTL/SCL Falling Edge to CRF/SDA<br>Valid, Reading Out Data                 | t <sub>DV</sub>                           |                           |            | 1           | μs   |

#### **ELECTRICAL CHARACTERISTICS**

$(V+=8.2V, V_{\overline{SH}}/SUS=V_{\overline{SH}}=5.5V, MINDAC=GND, T_A=-40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 6)$

| PARAMETER                                      | CONDITIONS                                                    | MIN TYP         | MAX  | UNITS |

|------------------------------------------------|---------------------------------------------------------------|-----------------|------|-------|

| SUPPLY AND REFERENCE                           |                                                               |                 |      |       |

| V 1 1V 11 5                                    | VL = V <sub>BATT</sub>                                        | 4.6             | 5.5  |       |

| V <sub>BATT</sub> Input Voltage Range          | VL = open                                                     | 6               | 28   | \ \   |

| VBATT Quiescent Current, Shutdown              | $\overline{SH}/SUS = \overline{SH} = GND$                     |                 | 20   | μΑ    |

| VL Output Voltage, Normal Operation            | 6V < V <sub>BATT</sub> < 28V,<br>0 < I <sub>LOAD</sub> < 15mA | 5.0             | 5.6  | V     |

| VI Lindaryaltaga Lagkaut Thrashald             | VL rising (leaving lockout)                                   |                 | 4.6  | V     |

| VL Undervoltage Lockout Threshold              | VL falling (entering lockout)                                 | 4.0             |      | V     |

| REF Output Voltage, Normal Operation           | 4.5V < VL < 5.5V, I <sub>REF</sub> = 40μA                     | 1.95            | 2.05 | V     |

| VL POR Threshold                               |                                                               | 0.9             | 2.7  | V     |

| SWITCHING REGULATOR                            |                                                               |                 |      |       |

| DH Driver On-Resistance                        |                                                               |                 | 18   | Ω     |

| DL1, DL2 Driver On-Resistance                  |                                                               |                 | 18   | Ω     |

| SYNC Synchronization Range                     | Detect falling edges on SYNC                                  | 64              | 200  | kHz   |

| CS Overcurrent Threshold                       |                                                               | 408             | 492  | mV    |

| DAC AND ERROR AMPLIFIER                        |                                                               |                 |      |       |

| CSAV Regulation Point                          | V <sub>MINDAC</sub> = 0, DAC code = 11111 binary              | 186             | 202  | mV    |

| CTFB Regulation Point                          |                                                               | 560             | 640  | mV    |

| CTFB to CCV Transconductance                   | 1V < V <sub>CCV</sub> < 2.7V                                  | 30              | 50   | μmho  |

| ANALOG INTERFACE BRIGHTNESS                    | CONTROL (MODE connected to REF or MODE co                     | nnected to GND) |      |       |

| SH Input Low Voltage                           |                                                               |                 | 0.8  | V     |

| SH Input High Voltage                          |                                                               | 2.1             |      | V     |

| SYSTEM MANAGEMENT BUS BRIGH                    | TNESS CONTROL (MODE connected to VL)                          |                 |      |       |

| CRF/SDA, CTL/SCL, SH/SUS Input<br>Low Voltage  |                                                               |                 | 0.8  | V     |

| CRF/SDA, CTL/SCL, SH/SUS Input<br>High Voltage |                                                               | 2.1             |      | V     |

| CRF/SDA Output Low Sink Current                | VCRF/SDA = 0.4V                                               | 4               |      | mA    |

- Note 1: Corresponds to 512 DPWM cycles or 65536 MODE cycles.

- **Note 2:** When the buck switch is shorted, V<sub>CTFB</sub> goes high causing V<sub>CCV</sub> to go below the fault detection threshold.

- Note 3: Corresponds to 64 DPWM cycles or 8192 MODE cycles.

- Note 4: The MODE pin thresholds are only valid while the part is operating. In shutdown, V<sub>REF</sub> = 0 and the part only differentiates between SMB mode and ADC mode. In shutdown with ADC mode selected, the CRF/SDA and CTL/SCL pins are at high impedance and will not cause extra supply current when their voltages are not at GND or VL.

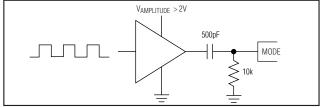

Note 5: The amplitude is measured with the following circuit:

**Note 6:** Specifications from -40°C to +85°C are guaranteed by design, not production tested.

#### 標準動作特性

(V<sub>IN</sub> = 12V, V<sub>CTL</sub> = V<sub>CRF</sub>, V<sub>MINDAC</sub> = 1V, MODE = GND, Circuit of Figure 8.)

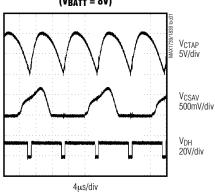

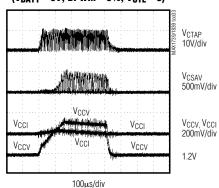

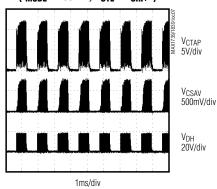

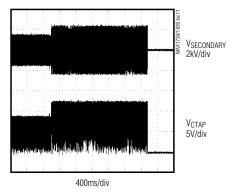

#### WIDE INPUT RANGE (VBATT = 8V)

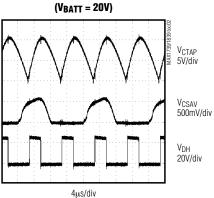

### WIDE INPUT RANGE

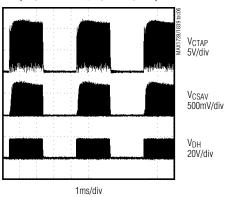

### WIDE INPUT RANGE (VBATT = 8V, DPWM = 9%, VCTL = 0)

WIDE INPUT RANGE (VBATT = 20V, DPWM = 9%, VCTL = 0)

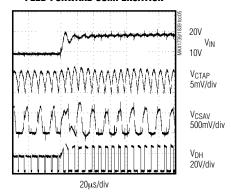

#### FEED-FORWARD COMPENSATION

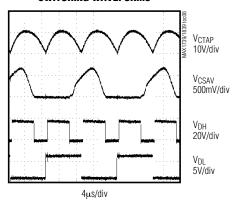

#### SWITCHING WAVEFORMS

#### 標準動作特性(続き)

(VIN = 12V, VCTL = VCRF, VMINDAC = 1V, MODE = GND, Circuit of Figure 8.)

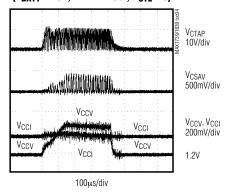

#### SYNCHRONIZED DPWM (fmode = 100kHz, Vctl = Vcrf/2)

# (fmode = 32kHz, Vctl = Vcrf/2)

SYNCHRONIZED DPWM

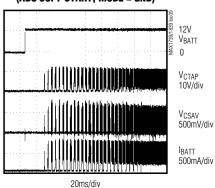

#### **STARTUP** (ADC SOFT-START, MODE = GND)

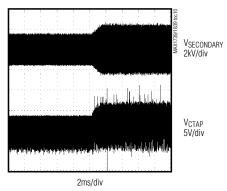

#### **LAMP-OUT VOLTAGE LIMITING**

#### **LAMP-OUT VOLTAGE LIMITING**

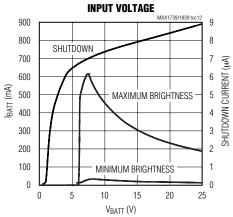

### **INPUT CURRENT vs.**

#### 標準動作特性(続き)\_

(V<sub>IN</sub> = 12V, V<sub>CTL</sub> = V<sub>CRF</sub>, V<sub>MINDAC</sub> = 1V, MODE = GND, Circuit of Figure 8.)

### 端子説明

| тт — | 4称      |         | 機能                                                                                                                                                                                                                                                                                                                                             |  |  |

|------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 端子   | MAX1739 | MAX1839 | 1茂 比                                                                                                                                                                                                                                                                                                                                           |  |  |

| 1    | REF     | REF     | 2Vリファレンス出力。0.1μFでGNDにバイパスして下さい。シャットダウン中は強制的にローになります。                                                                                                                                                                                                                                                                                           |  |  |

| 2    | MINDAC  | MINDAC  | DACのゼロスケール入力。V <sub>MINDAC</sub> はDACの最小スケール出力電圧を設定します。<br>MINDACをVLに接続するとDPWMがディセーブルされます。                                                                                                                                                                                                                                                     |  |  |

| 3    | CCI     | CCI     | GMI出力。CCFL電流を制御する電流ループGMIアンプの出力。<br>通常は0.1µFでGNDにバイパスして下さい。                                                                                                                                                                                                                                                                                    |  |  |

| 4    | CCV     | CCV     | GMV出力。最大平均一次トランス電圧を制御する電圧ループGMVアンプの出力。<br>通常は3300pFでGNDにバイパスして下さい。                                                                                                                                                                                                                                                                             |  |  |

| 5    | SH/SUS  | SH      | アナログインタフェースモードにおいてはロジックローシャットダウン入力。SMBusは<br>SMBusインタフェースモードにおいては入力をサスペンドします(MAX1739のみ)。                                                                                                                                                                                                                                                       |  |  |

| 6    | CRF/SDA | CRF     | アナログインタフェースモードにおいては5ビットADCリファレンス入力。SMBusインタフェースモードにおいてはSMBusシリアルデータ入力/オープンドレイン出力(MAX1739のみ)。                                                                                                                                                                                                                                                   |  |  |

| 7    | CTL/SCL | CTL     | アナログインタフェースモードにおいてはCCFL輝度制御入力。SMBusインタフェース<br>モードにおいてはSMBusシリアルクロック入力(MAX1739のみ)。                                                                                                                                                                                                                                                              |  |  |

| 8    | MODE    | MODE    | インタフェース選択入力及びDPWMチョッピングの同期入力(「DPWM周波数の同期」を参照)。 MODEピンの平均電圧によって、3つのCCFL輝度制御インタフェースのうち1つが選択されます。 1) MODE = VLの場合、SMBusシリアルインタフェースがイネーブルされます (MAX1739のみ)。 2) MODE = GNDの場合、アナログインタフェースがイネーブルされます(正スケールのアナログインタフェースモード)。VCTL/SCL = 0は輝度が最低であることを意味します。 3) MODE = REFの場合、アナログインタフェースがイネーブルされます(負スケールのアナログインタフェースモード)。VCTL/SCL = 0は輝度が最高であることを意味します。 |  |  |

| 9    | CSAV    | CSAV    | 電流検出入力。CCIを駆動するGMIエラーアンプへの入力。                                                                                                                                                                                                                                                                                                                  |  |  |

| 10   | CTFB    | CTFB    | センタータップ電圧フィードバック入力。平均V <sub>CTFB</sub> は0.6Vに制限されています。                                                                                                                                                                                                                                                                                         |  |  |

| 11   | SYNC    | SYNC    | Royer同期入力。SYNCの立下がりエッジでDHが強制的にオンになり、DL1及びDL2ドライバがトグルされます。Royerのセンタータップに直接接続して下さい。                                                                                                                                                                                                                                                              |  |  |

| 12   | DL2     | DL2     | ローサイドNチャネルMOSFET 2のゲートドライブ。Royer発振器スイッチを駆動します。<br>DL1とDL2はメーク・ビフォ・ブレークスイッチングになっているため、少なくとも1つは<br>常にオンです。SYNCの立下がりエッジでDL1とDL2がトグルされ、DHがターンオンします。                                                                                                                                                                                                |  |  |

| 13   | DL1     | DL1     | ローサイドNチャネルMOSFET 1のゲートドライブ。                                                                                                                                                                                                                                                                                                                    |  |  |

| 14   | CS      | CS      | 電流検出入力(電流リミット)。V <sub>CS</sub> が(V <sub>REF</sub> - V <sub>CCI</sub> )を超えると、電流モードレギュレータはスイッチサイクルを終了します。                                                                                                                                                                                                                                        |  |  |

| 15   | GND     | GND     | システムグランド                                                                                                                                                                                                                                                                                                                                       |  |  |

| 16   | VL      | VL      | 5.3Vリニアレギュレータ出力。殆どの内部回路の電源電圧。 $1\mu$ FコンデンサでGNDにバイパスして下さい。 $V_{BATT} < 5.5V$ である場合は $V_{BATT}$ に接続出来ます。                                                                                                                                                                                                                                        |  |  |

| 17   | BST     | BST     | ハイサイドドライバのブートストラップ入力。ダイオードを通じてVLに接続し、<br>0.1μFでLXにバイパスして下さい。                                                                                                                                                                                                                                                                                   |  |  |

| 18   | LX      | LX      | ハイサイドドライバのグランド入力                                                                                                                                                                                                                                                                                                                               |  |  |

| 19   | DH      | DH      | ハイサイドゲートドライバ出力。SYNCの立下がりエッジでDHがターンオンします。                                                                                                                                                                                                                                                                                                       |  |  |

| 20   | BATT    | BATT    | 電源入力。チップを駆動する内部5.3Vリニアレギュレータの入力。                                                                                                                                                                                                                                                                                                               |  |  |

#### 詳細

MAX1739/MAX1839はCCFLの輝度を下記の3通りの 方法で制御します。

- 1) ランプ電流のリニア制御

- 2) ランプ電流のディジタルパルス幅変調(DPWM)/ チョッピング

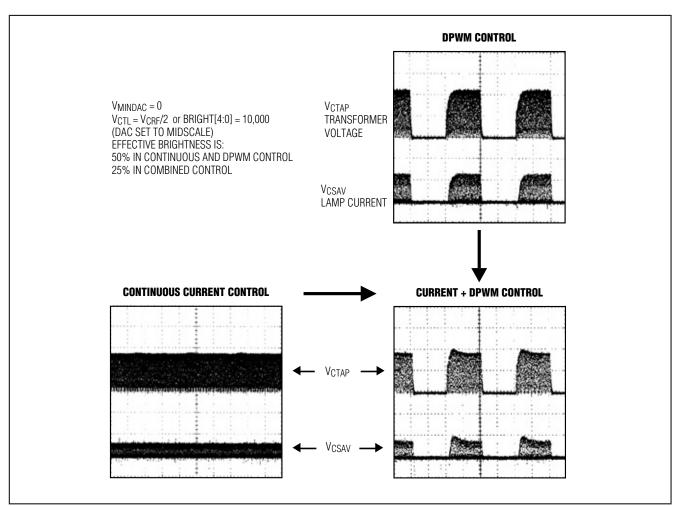

- 3) 両方を同時に使用して非常に広い調光範囲を実現 DPWMは人間の目には止まらない速さでランプ電流 をパルス幅変調することによって実現されます。図1に

輝度制御をフルスケールの50%に設定した状態における これら3つの動作モードを示します。

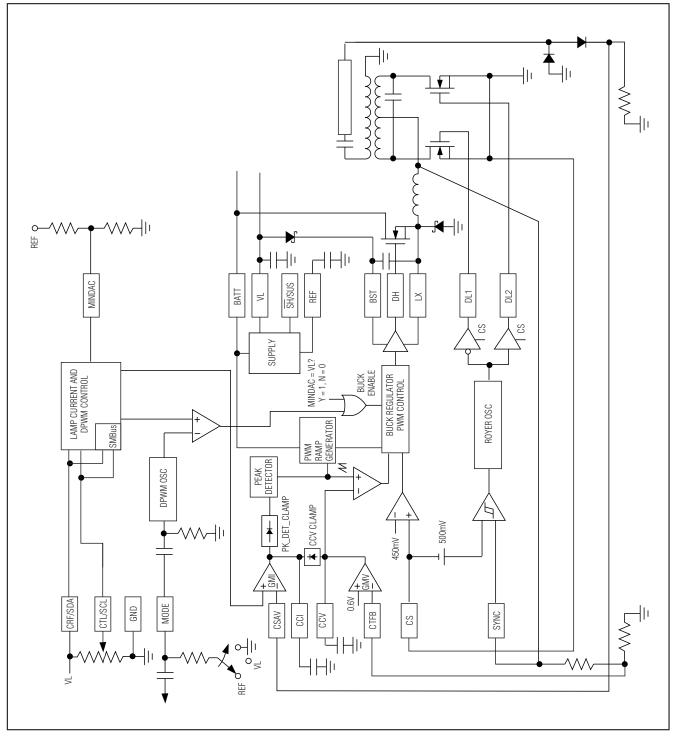

MAX1739/MAX1839は5.3Vリニアレギュレータを内蔵しており、これにより殆どの内部回路、バック及びRoyerスイッチのドライバ及び同期可能なDPWM発振器を駆動します。MAX1739/MAX1839は非常にフレキシブルで、様々な動作モードを備えているほか、アナログインタフェース、SMBusインタフェース(MAX1739のみ)、シャットダウンモード、ランプアウト検出及びバックスイッチ短絡検出機能を備えています。

図1. 輝度制御法

#### 電圧及び電流制御ループ

MAX1739/MAX1839は2つの制御ループを使用しています。電流制御ループは平均ランプ電流を制御します。電圧制御ループは、最大平均一次側トランス電圧を制御し、DPWMオンサイクルの始め及び一部の障害条件時にアクティブになります。トランスの一次電圧を制限することにより、トランスの二次電圧定格を下げることが可能となるため、トランスのコストが下がり、信頼性が向上します。電圧制御ループは、電流制御ループがトランス電圧を $V_{CTFB}$ によって設定されたリミットを超えて駆動しようとした時にトランス電圧を制限するように動作します(「検出抵抗」を参照)。

電圧制御ループは、トランスコンダクタンスアンプを使用して、CTFBと内部リファレンスレベル(600mV typ)の間の電圧に基づいてエラー電流を生成します(図2)。このエラー電流を使用して $C_{CCV}$ が充電・放電され、エラー電圧 $V_{CCV}$ が生成されます。電流制御ループは、CSAVと内部リファレンスレベルの間の電圧に基づいてこれと似た信号を生成します(「調光範囲」を参照)。このエラー電圧は $V_{CCI}$ と呼ばれます。 $V_{CCV}$ と、 $V_{CCI}$ のうちの低い方とバックレギュレータのアューティサイクルが設定されます。

DPWM中、この2つの制御ループが協同してトランス電圧を制限し、良好なライン除去比で広い調光範囲を実現します。DPWMのオフサイクル中、 $V_{CCV}$ は1.2Vに設定され、CCIはハイインピーダンスに設定されます。 $V_{CCV}$ を1.2Vに設定するのは、各DPWMオンサイクルの始めにソフトスタートを生成することによってトランスの一次側のオーバシュートを避けるためです。 $V_{CCI}$ はハイインピーダンスに設定されます。これは、オフサイクル中に $V_{CCI}$ が変化するのを防ぐためです。これにより、電流制御ループがDPWMのオンサイクル中にのみ平均ランプ電流を制御することが可能になります(全体的な平均ランプ電流を制御するわけではありません。)

$V_{CCI}$ は、パワーアップ時に緩やかに上昇してデューティサイクルを増加させるため、ソフトスタートになります。この時 $V_{CCV}$ (速い方の制御ループ)はCCV-CLAMPによって $V_{CCI}$ の150mV上に制限されます。二次電圧がストライク電圧に達すると、ランプ電流が増加し始めます。ランプ電流がレギュレーションポイントに達すると、 $V_{CCI}$ は定常状態に達します。MINDAC = VL(DPWMがディセーブル)の時は、電流制御ループが引き続き制御を受け持ち、ランプ電流をレギュレートします。

MINDACがREFとGNDの間である時、DPWMはイネーブル状態となり、MAX1739/MAX1839はランプ電流のパルス化を始めます。オンサイクル中、 $V_{CCV}$ は $V_{CCI}$ の150mV上になります。オンサイクルが終了すると、 $V_{CCV}$ は強制的に1.2Vに下げられ、次のオンサイクルの初めにソフトスタートを提供します。また、 $V_{CCI}$ の値は次のオンサイクルの開始時まで保持されます。

$V_{CCV}$ が増加すると、バックレギュレータのデューティサイクルが増加して、ソフトスタートをもたらします。  $V_{CCV}$ が $V_{CCI}$ を超えると、電流制御ループが再び制御権を得て、ランプ電流をレギュレートします。オンサイクルの残りの期間中、 $V_{CCV}$ は $V_{CCI}$ の150mV上に制限されます。

ランプアウト状態の時、 $V_{CCI}$ はランプ電流のレギュレーションを維持しようとして一次電圧を増加させます。 $V_{CCI}$ が増加すると共に $V_{CCV}$ も増加し、一次電圧が設定されたリミットに達します。この時点で $V_{CCV}$ の上昇が止まり、デューティサイクルを制限することによって一次電圧を制限します。 $V_{CCV}$ は $V_{CCI}$ の150mV上に制限されているため、電圧制御ループは素早く一次電圧を制限することが出来ます。このクランプ機能がないと、トランスの電圧は危険なレベルまでオーバシュートします。これは、 $V_{CCV}$ が電源電圧からスルーダウンするにはより長い時間がかかるためです。 $V_{CCV}$ が電流の1/6以下であることを検出すると、 $V_{CCV}$ に開流の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることでは $V_{CCV}$ に表対の1/6以下であることであります。 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることでは $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを検出すると、 $V_{CCV}$ に表対の1/6以下であることを持力の1/6以下であることを対対の1/6以下でありかかからないでするに対すると、 $V_{CCV}$ の1/6以下でありために表対の1/6以下であります。 $V_{CCV}$ の1/6以下であります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下であります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下であります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下でなります。 $V_{CCV}$ の1/6以下でなります。

電圧及び電流制御ループのスレッショルドの設定に ついては、「検出抵抗」を参照して下さい。

#### フィードフォワード制御

いずれの制御ループも、MAX1739/MAX1839の入力電圧フィードフォワード(VBATT)制御回路の影響を受けます。フィードフォワード制御は、入力電圧の変化を検出した時に直ちにバックレギュレータのデューティサイクルを調整します。これにより、全輝度レベルにおいて入力電圧変化への耐性が与えられます。この機能により、広い入力範囲にわたる補償が容易になるだけでなく、スタートアップトランジェントの入力電圧に対する依存性が小さくなり、またDPWMオン時間が短い時のラインレギュレーションが向上します。

MAX1739/MAX1839のフィードフォワード制御は、バックスイッチのPWMランプ振幅を変化させることによって実現されます。これにより、同じ $V_{CCI}$ と $V_{CCV}$ を維持しつつ、デューティサイクルが入力電圧の関数として変化します。つまり、 $V_{BATT}$ のフィードフォワードにより、 $V_{BATT}$ の変化に応答するためにエラー信号電圧 ( $V_{CCI}$ 及び $V_{CCV}$ )を変化させる必要がなくなります。また、 $V_{BATT}$ の変化に応答する際のコンデンサ電圧の変化は僅かで済むため、コントローラの応答は殆ど瞬間的です。

#### ドロップアウトによる トランジェント過電圧保護

MAX1739/MAX1839は、全てのトランジェント条件においてトランスの一次側を精密に制御するように設計されています。これには、ドロップアウトによるトランジェントも含まれます(ドロップアウトとは、VBATTが低くなってコントローラがレギュレーションを喪失し、最大デューティサイクルに達した状態です)。バックライトの設計では、トランスの巻線比を最小化

図2. ファンクションダイアグラム

するように回路部品定数を選択して、一次電流と $I^2R$  損失を最小限に抑える必要があります。これを実現するには、バックライトの性能が重要でなくなるような非常に低いバッテリ電圧において回路がドロップアウトで動作することを許容します。全てのバックライト回路は、ラップトップがACアダプタに接続されて $V_{BATT}$ が急激に上昇すると、過渡的な過電圧条件になる場合があります。MAX1739/MAX1839は独特なクランプ回路を $V_{CCI}$ に備えており、フィードフォワード回路とこのクランプ回路によって、ドロップアウト状態が解除された時に過渡的なトランス過電圧が生じないことが保証されます。

PK\_DET\_CLAMP回路は、V<sub>CCI</sub>をバックレギュレータの PWMランプ発生器のピークに制限します。回路が ドロップアウトになると、VCCIは最大デューティサイ クルに達するためにPWMランプ発生器のピークに近づき ます。VRATTがさらに低下すると、制御ループはレギュ レーションを喪失し、VCCIは正電源電圧に達しようと します。VCCIのクランプ回路はこの状態が発生するのを 防ぎ、V<sub>CCI</sub>はPWMランプのピークのすぐ上になります。 VBATTがさらに低下すると、フィードフォワードPWM ランプ発生器は振幅を喪失し、クランプは回路がドロップ アウトでなかった場合にVCCIが達したであろう電圧より 低い電圧までV<sub>CCI</sub>と共に低下します。VBATTが突然 ドロップアウトから抜け出して増加すると、Vcciは依然 として低いまま留まり、トランスのドライブを古い ドロップアウトレベルに維持します。その後、回路は 緩やかにVCCIを補正して増加させ、回路を安定化状態に 戻します。

#### バックレギュレータ

バックレギュレータは、PWMコンパレータからの信号、CSにおける電流リミット検出及びDPWM信号を使用してハイサイドMOSFETのデューティサイクルを制御します。このレギュレータは電圧モードPWM制御を採用しており、Royer発振器に同期しています。SYNCの立下がりエッジは、375nsの最小オフ時間遅延の後でハイサイドMOSFETをターンオンします。オンサイクルは、PWMコンパレータ又はCS電流リミットによって終了されます。

#### インタフェースの選択

表1に、MAX1739/MAX1839の3つの各インタフェース モードにおけるSH/SUS、CRF/SDA及びCTL/SCLの 機能が挙げられています。MAX1739はSMBusディジタルインタフェースとアナログインタフェースの両方を備えていますが、MAX1839はアナログインタフェースのみです。MODEはDPWMの周波数を同期することも出来ることに注意して下さい(「DPWM周波数の同期」を参照)。

#### 調光範囲

輝度はアナログインタフェース(「アナログインタフェース」を参照)又はSMBus(「SMBusインタフェース」を参照)によって制御されます。CCFL輝度は以下の3つの方法で調整されます。

- 1) ランプ電流制御:平均ランプ電流の大きさが調整されます。

- 2) DPWM制御:平均ランプ電流が可変デューティ サイクルでパルス的にランプに流れます。

- 3) 上の2つの方法の組合わせ

これら3つの方法のいずれの場合も、5ビット輝度コードは選択されたインタフェースから生成され、ランプ電流やDPWMデューティサイクルを設定するために使用されます。

5ビットの輝度コードは、ランプ電流レベルを定義します (ob00000が最小ランプ電流を表し、ob11111が最大 ランプ電流を表します)。平均ランプ電流は外付検出抵抗 の両端で測定されます(「検出抵抗」を参照)。検出抵抗の電圧はCSAVで測定されます。輝度コードはCSAVにおけるレギュレーション電圧(V<sub>CSAV</sub>)を調整します。最小平均V<sub>CSAV</sub>はV<sub>MINDAC</sub>/10となり、最大平均は次式で設定されます。

$V_{CSAV} = V_{REF} \times 31 / 320 + V_{MINDAC} / 320$ これは193.75mVと200mVの間になります。

V<sub>CSAV</sub>が2秒以上に渡って100mVピーク(平均としては 約32mV)を超えないと、MAX1739/MAX1839はランプ アウト条件とみなしてシャットダウンします(「ランプ アウト検出」を参照)。

輝度コードとC<sub>SAV</sub>のレギュレーション電圧の間の関係は次式で与えられます。

V<sub>CSAV</sub> = V<sub>REF</sub> × n / 320 + V<sub>MINDAC</sub> × (32 - n) / 320 ここで、nは輝度コードです。

DPWM制御を使用する際、常に最大平均ランプ電流を使用するには、 $V_{MINDAC}$ を $V_{REF}$ に設定して下さい。

#### 表1. インタフェースモード

| PIN     | DIGITAL<br>INTERFACE        | ANALOG INTERFACE                                                              |  |  |  |  |

|---------|-----------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| PIN     | MODE = VL<br>(MAX1739 only) | MODE = REF,                                                                   |  |  |  |  |

| SH/SUS  | SMBus suspend               | Logic-level shutdown control input                                            |  |  |  |  |

| CRF/SDA | SMBus data I/O              | Reference input for minimum brightness Reference input for maximum brightness |  |  |  |  |

| CTL/SCL | SMBus clock input           | Analog control input to set brightness (range from 0 to CRF/SDA)              |  |  |  |  |

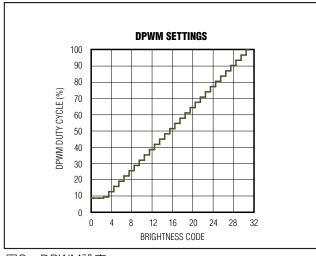

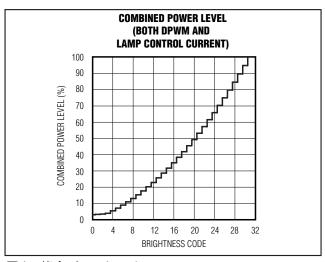

DPWM制御は、5ビット輝度コードに応答するという点でランプ電流制御に似ています。輝度コードob00000はDPWMのデューティサイクル9.375%に対応し、輝度コードob11111はDPWMのデューティサイクル100%に対応します。デューティサイクルはステップ当たり3.125%変化しますが、例外としてob00000からob00011までのコードは9.375%の変化をもたらします(図3)。

DPWMをディセーブルして常に100%のデューティサイクルを使用するには、 $V_{MINDAC}$ をVLに設定して下さい。DPWMがディセーブルされている場合、上の式では $V_{MINDAC} = VL$ の代わりに $V_{MINDAC} = 0$ と仮定する必要があることに注意して下さい。表2に、MINDACの機能を示します。また、表3に輝度調整の標準的な設定をいくつか示します。

通常動作においては、 $V_{MINDAC}$ は0と $V_{REF}$ の間に設定され、MAX1739/MAX1839はランプ電流制御とDPWM制御の両方を使用してランプ輝度を変化させます(図4)。このモードでは、ランプ電流制御機能は全体的な平均ランプ電流に対してではなく、DPWMオンサイクル中の平均ランプ電流に対してレギュレーションを行います。

#### アナログインタフェースと輝度コード

MAX1739/MAX1839のアナログインタフェースは、 ヒステリシス1ビットの内部ADCを使用して、ランプを 調光するための輝度コードを発生します(「調光範囲」を 参照)。CTL/SDAはADCの入力、CRF/SCLはリファ レンス電圧です。このADCは正スケールモードADCと 負スケールADCモードの両方で動作可能です。正スケール ADCモードでは、 $V_{CTL}$ が0から $V_{CRF}$ に増加するのに対応 して輝度コードが0から31に増加します。負スケール モードでは、 $V_{CTL}$ が0から $V_{CRF}$ に増加するのに対応して 輝度コードが31から0に減少します(図5)。

アナログインタフェースの内部ADCは、1ビットのヒステリシスを使用して、ランプが2つのコードの間でちらつくのを防ぎます。 $V_{CTL}$ の正スレッショルド( $V_{CTL}$ (TH))は、 $V_{CTL}$ が増加する時に輝度コードを遷移させるために必要な電圧です。 $V_{CTL}$ は次式で計算出来ます。

VCTL(TH) = (n + 2) / 33 VCRF (正スケールADCモード、MODE = GND)

VCTL(TH) = (33 - n) / 33 VCRF (負スケール ADCモード、MODE = GND)

ここで、nは電流で選択された輝度コードです。 $V_{CTL}$ の 負のスレッショルドは $V_{CTL}$ が減少する時に輝度コードを遷移させるために必要な電圧です。 $V_{CTL}$ は次式で計算出来ます。

VCTL(TH) = n / 33 VCRF (正スケール ADCモード、MODE = GND)

VCTL(TH) = (31 - n) / 33 VCRF (負スケール ADCモード、MODE = GND)

図5にスレッショルドの図解を示します。CRF/SDAとCTL/SCLの入力電圧範囲は2.7V~5.5Vです。

図3. DPWM設定

図4. 複合パワーレベル

#### 表2. MINDACの機能

| MINDAC = VL                    | DPWM disabled (always on 100% duty cycle). Operates in lamp current control only. (Use V <sub>MINDAC</sub> = 0 in the equations.) |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| MINDAC = REF                   | DPWM control enabled, duty cycle ranges from 9% to 100%. Lamp current control is disabled (always maximum current).               |

| 0 ≤ V <sub>MINDAC</sub> < VREF | The device uses both lamp current control and DPWM.                                                                               |

| 表3. 輝度調整範囲(調光比33 | ) . 4 の坦へ)         |

|------------------|--------------------|

| 表 5 相比副参加用(副分尺)  | ( · I (/ ) TE (E ) |

| BRIGHTNESS            | POSITIVE-<br>SCALE ADC                              | NEGATIVE-<br>SCALE ADC                                  | SMBus                                       | DAC<br>OUTPUT                              | DPWM DUTY<br>CYCLE<br>(%) | COMBINED<br>POWER<br>LEVEL (%) |

|-----------------------|-----------------------------------------------------|---------------------------------------------------------|---------------------------------------------|--------------------------------------------|---------------------------|--------------------------------|

| Maximum<br>Brightness | MODE = GND,<br>VCTL/SCL =<br>VCRF/SDA               | MODE = REF,<br>VCTL/SCL = 0                             | Bright [4:0] = ob11111                      | Full-scale<br>DAC OUTPUT =<br>195.83mV     | 100                       | 100                            |

| Minimum<br>Brightness | MODE = GND,<br>VCTL/SCL = 0,<br>VMINDAC =<br>VREF/3 | MODE = REF,<br>VCTL/SCL = VCRF/SDA,<br>VMINDAC = VREF/3 | Bright [4:0] = ob00000,<br>VMINDAC = VREF/3 | Zero-scale<br>DAC OUTPUT =<br>VMINDAC / 10 | 9                         | 3                              |

注記: 電流レベル範囲はMINDAC対REFの比率によって決まり、外部で設定されます。

SMBusインタフェースの使い方については、「ディジタルインタフェース」を参照して下さい。

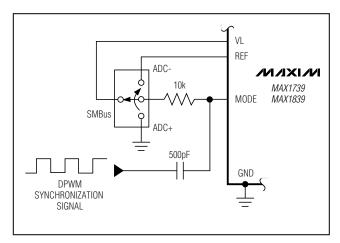

#### DPWM周波数の同期

MODEは2つの機能を備えています。1つは「インタフェースの選択」で述べるインタフェースモードの選択、そしてもう1つはディスプレイ画面に望ましくない影響が出るのを防ぐためにDPWMの「チョッピング」周波数を外部信号に同期させることです。

DPWM周波数を同期させるには、10kΩ抵抗を通じて MODEをVL、REF又はGNDに接続して下さい。次に、図6に示すように500pFコンデンサをAC信号ソースと MODEの間に接続して下さい。同期範囲は32kHzから 100kHzです。これは、DPWM周波数範囲としては 250Hz~781Hzに対応します(DPWMの1サイクル当たり 128個のMODEパルス)。DPWM周波数が高いと、調光範囲が制限されます。高DPWM周波数に関する詳細については「ループ補償」を参照して下さい。

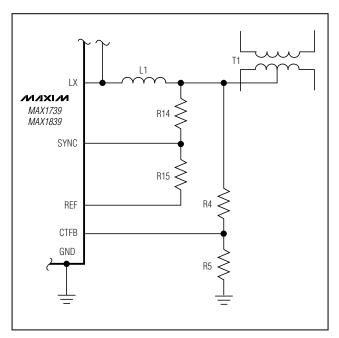

#### Royer発振器のMOSFETドライバ

MAX1739/MAX1839は、Royer発振器に使用されている2つの外部MOSFETを直接駆動します。この方法は、バイポーラスイッチングとトランスの特別な巻線を使った従来の方法と比べて多くの利点を備えています。MOSFETを直接駆動することにより、トランスの特別な巻線が不要になるため、コストが低減すると共に、トランスのサイズが最小限になります。また、スイッチを特別駆動することにより、転換効率と転換タイミングが向上します。通常、スイッチとしてMOSFETを使用すると、スイッチドロップが減少するためにインバータの全体的な効率が向上します。

Royerトポロジーはゼロ電圧クロス(ZVC)ディテクタとして動作し、トランスの一次巻線の2セクション間の電流を切替えます。この2つの巻線は交互に動作し、

各々が波の半分を発生して、それが二次巻線に転送されて完全なサイン波のランプ電圧及び電流を生成します。MAX1739/MAX1839はSYNCピンを通じてゼロクロスを検出します。スレッショルドはCSを基準とした場合の500mVに設定され、標準遅延は50nsです。能動的なスイッチングを行うと、ZVCポイントの非常に近くで転換が強制的に起こり、従来の巻線を使ったZVC切換えと比較して性能が向上します。図7に示すR14とR15を使用することにより、転換がさらに最適化されます。この抵抗分圧器はゼロクロスポイントの

図5. 輝度コード

図6. DPWM同期

出来る限り近くで転換が起こるように強制するために 使用することが出来ます。

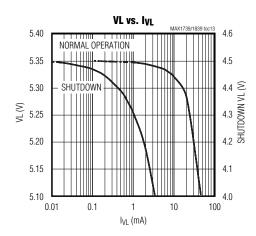

#### POR及びUVLO

MAX1739/MAX1839は、パワーオンリセット(POR) 及び低電圧ロックアウト(UVLO)機能を備えています。PORは、DAC出力、障害条件及び全てのSMBusレジスタなど、全ての内部レジスタをリセットします。PORはVLが1.5Vより低い時に発生します。SMBus入力ロジックスレッショルドはVLが最低3.5Vまで下がつても電気的特性のリミットに適合するように設計されていますが、インタフェースはPORスレッショルドまで機能し続けます。

UVLOスレッショルドは、VLが4.2V(typ)よりも低い時に 発生し、バックスイッチドライバをディセーブルします。

#### 低電力シャットダウン

MAX1739/MAX1839がシャットダウン状態になると、各内部レジスタとSMBusインタフェース(MAX1739)を駆動する5Vリニアレギュレータ以外の全てのIC機能がターンオフされます。SMBusインタフェースはシャットダウン中にもアクセス可能です。シャットダウン中、リニアレギュレータの出力電圧は約4.5Vまで下がり、消費電流は $6\mu A(typ)$ になります(これは全ての内部レジスタの状態を維持するために必要です)。シャットダウン中、ランプアウト検出及びバックスイッチ短絡検出ラッチはリセットされます。本デバイスは、MODEレジスタへの書込み(MAX1739のSMBusモードのみ)あるいは $\overline{SH}/SUS$ によってシャットダウン状態にすることが出来ます。

#### ランプアウト検出

安全のため、ランプアウト条件時にはMAX1739/MAX1839 は最大平均一次側トランス電圧を制限し(「検出抵抗」を参照)、2秒後にランプをシャットダウンします。

図7. ZVC検出の調整

ランプアウト検出回路は $V_{CSAV}$ を監視し、 $V_{CSAV}$ が2秒以内に75mVを超えないとランプをシャットダウンします。この回路は200ns以下の殆どのパルスを無視します。ただし、場合によってはCSAVに小型コンデンサを付けることにより、この回路がノイズでトリップするのを防ぐ必要があります。ノイズの大きい環境やレイアウトが優れない場合には特にこのコンデンサが必要となります。

CSAVの電圧は半波整流されたサイン波であることが 理想的です。この場合、CSAVランプアウトスレッショルド は次式で与えられます。

#### $I_{MIN} = I_{MAX} / 6$

ここで、 $I_{MIN}$ はCSAVランプアウトスレッショルド、 $I_{MAX}$ は最大ランプ電流です(「検出抵抗」を参照)。注記:これらの式ではワーストケースのCSAVランプアウトスレッショルド100mV、最大CSAV平均電圧200mVを仮定しています。

MINDACを使用するか、あるいは輝度コードを制限することにより、ランプ電流の設定がCSAVランプアウトスレッショルドより低くなるのを防いで下さい。

ランプアウト検出回路がデバイスをシャットダウンすると、STATUS1ビットが設定されます。

#### バックスイッチの短絡障害検出及び保護

バックスイッチ(N1)が短絡すると、トランスには電圧制限がないため、入力によって二次側に過剰な電圧が強制的に発生します。これにより、回路の消費電流が増えますが、ヒューズを熔断するには及ばない場合も

あります。バックスイッチが短絡した状態ではセンタータップがレギュレーションポイントを超えて上昇し、このためにCCVアンプの出力( $V_{CCV}$ )がローになります。これを検出するために、MAX1739/MAX1839は各DPWM周期の最後に $V_{CCV}$ が1Vより低いかどうかをチェックします。この状態が250ms(64 DPWMパルス)を超えて継続すると、DL1又はDL2のどちらかがオンの状態でインバータスイッチの転換が停止します。バックスイッチが短絡した状態では、これによってヒューズを熔断するために十分な短絡電流が生じます。バックスイッチが短絡されていないと、インバータはランプアウト条件の時と同様にラッチオフします。

バックスイッチ短絡及びランプアウト検出はいずれも SMBusインタフェースのSTATUS1ビットをクリアし ます。STATUS1ビットは直ちにクリアされるわけでは ありませんが、インバータが強制的にオフになった後約2秒 でクリアします(「ディジタルインタフェース」を参照)。

インバータ基板のヒューズが熔断すると、MAX1739が電源を失うために本素子とのSMBus通信が止まることに注意して下さい。

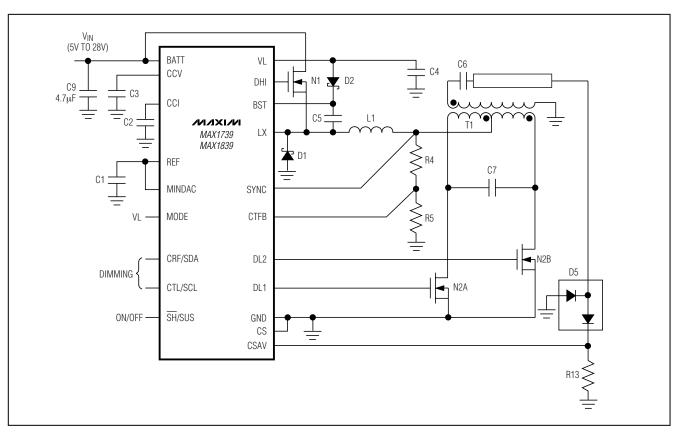

#### アプリケーション情報

標準アプリケーション回路(図8)に示すように、MAX1739/MAX1839は4.5W CCFLの電流を制御します。本ICのアナログ電圧インタフェースは最小20:1の電力調整範囲でランプ輝度を設定します。この回路は7V~24Vという広い電源電圧範囲で動作します。標準アプリケーションとしては、ノートブック、デスクトップモニタ及び自動車のナビゲーションディスプレイ等が挙げられます。

#### CCFLの仕様

MAX1739/MAX1839の回路に対して適正な部品定数を 選択するには、いくつかのCCFLパラメータ(表4)と最小 DC入力電圧の仕様を指定する必要があります。

#### Royer発振器

部品T1、C6、C7、N2A及びN2BはRoyer発振器を 形成します。Royer発振器はC7、T1の一次磁化インダク タンス(LP)、及びT1の二次側から見たインピーダンスに 依存する周波数で発振する共振タンクです。図8は広 範囲のCCFL管及び電力範囲に対して有用な実証済みの

図8. 標準アプリケーション回路

回路です。表5に4.5Wアプリケーション用の推奨部品を示します。

#### **MOSFET**

MAX1739/MAX1839の動作には3つの外部スイッチN1、N2A及びN2Bが必要です。N1はバックスイッチです。導通損失を最小限に抑えるため、R<sub>DSON</sub>の小さなロジックレベルNチャネルMOSFET(100m $\Omega$ 、30V typ)を選択して下さい。また、D1としては同等パワーのショットキダイオードを選択して下さい。N2A/N2Bはトランスの一次側を駆動するRoyer発振器スイッチです。導通損失を最小限に抑えるため、R<sub>DSON</sub>の小さなデュアルロジックレベルNチャネルMOSFET (100m $\Omega$ 、30V typ)を選択して下さい。

#### 検出抵抗

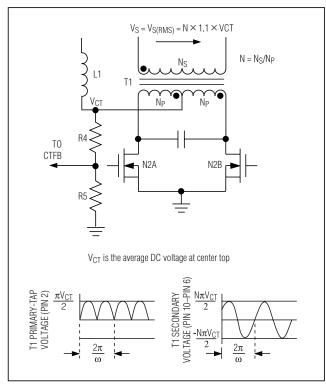

R4及びR5はトランスの一次電圧を検出します。図9に一次側と二次側の電圧の関係を示します。最大平均二次トランス電圧を設定するには、R5 = 10kΩに設定し、R5は次式で選択して下さい。

$$R4 = R5 \left( \frac{1.5V_{S(RMS)}}{N} - 1 \right)$$

ここで、 $V_S$ は最大RMS二次トランス電圧(ストライク電圧 の上)及びNはトランスの巻線比です。

#### 表4. CCFLの仕様

| SPECIFICATION                                        | SYMBOL | UNITS             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|--------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCFL Minimum Strike<br>Voltage<br>(Kick-Off Voltage) | Vs     | V <sub>RMS</sub>  | Although CCFLs typically operate at <550VRMS, a higher voltage (1000V <sub>RMS</sub> and up) is required initially to start the tube. The strike voltage is typically higher at cold temperatures and at the tube's end of life. This voltage is set by the combination of the maximum primary voltage (center-tap voltage limit corresponding to V <sub>CTFB</sub> = 0.6V) and the transformer (T1) turns ratio. |

| CCFL Typical Operating<br>Voltage<br>(Lamp Voltage)  | VL     | VRMS              | Once a CCFL has been struck, the voltage required to maintain light output falls to approximately 550V <sub>RMS</sub> . Short tubes may operate on as little as 250V <sub>RMS</sub> . The CCFL operating voltage stays relatively constant, even as the tube's brightness is varied.                                                                                                                              |

| CCFL Maximum Operating<br>Current (Lamp Current)     | ΙL     | mA <sub>RMS</sub> | The maximum RMS AC current through a CCFL is typically 5mA <sub>RMS</sub> . DC current is not allowed through CCFLs. The maximum lamp current is set by the sense resistor (R13) at the maximum brightness setting.                                                                                                                                                                                               |

| CCFL Maximum Frequency<br>(Lamp Frequency)           | f∟     | kHz               | The maximum AC-lamp-current frequency. The MAX1739/ MAX1839 synchronize to the Royer oscillator frequency set by the external components and are designed to operate between 32kHz and 100kHz.                                                                                                                                                                                                                    |

#### 表5. 標準アプリケーション回路の部品

| DESIGNATION | DESCRIPTION                           | RECOMMENDED DEVICE        | MANUFACTURER |

|-------------|---------------------------------------|---------------------------|--------------|

| L1          | 47μH, 1.1A inductor                   | CR104-470                 | Sumida       |

| N1          | 30V, 0.1Ω N-channel MOSFET            | FDN361AN                  | Fairchild    |

| N2          | 30V, 95mΩ dual N-channel MOSFET       | FDC6561AN                 | Fairchild    |

| T1          | 8.7µH, 180:1 transformer              | 5371-T001 (CIUH842 style) | Sumida       |

| D1          | 30V, 1A Schottky diode                | CRS02                     | Toshiba      |

| D2          | 0.1A Schottky diode                   | BAT54                     | Fairchild    |

| D3          | 0.1A dual Schottky diode              | MMBD4148SE                | Fairchild    |

| C6          | 22pF, 3.1kV capacitor                 | GHM1038-SL-220J-3K        | Murata       |

| C7          | 0.1µF, 63V, low-dissipation capacitor | SMD1812                   | WIMA         |

図9. トランスの一次/二次電圧の関係

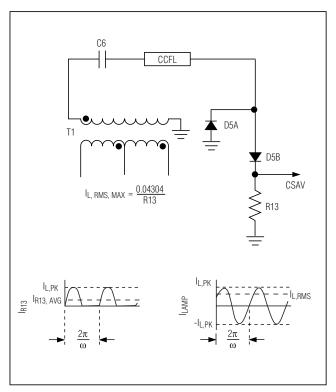

MAX1739/MAX1839はCCFLを流れる平均電流を制御します。電流はCSAVの検出抵抗(R13)で検出されます。CSAVの電圧はランプを流れる電流の半波整流表現となっています(図10)。MAX1739/MAX1839はCSAVにおける平均電圧( $I_{R13,AVG} \times R13$ )を制御し、アナログインタフェース又はSMBusインタフェースによって制御されます。最大ランプ電流を設定するには、次式でR13を決定して下さい。

#### $R13 = 0.4304 / I_{L,RMS,MAX}$

ここで、 $I_{L,RMS,MAX}$ は最大RMSランプ電流です。実際の最大RMSランプ電流はMINDAC及び波形に影響されます。R13の最終調整にはRMS電流メータを使用して下さい。

#### ループ補償

$C_{CCI}$ は、スタートアップ中、ランプ電流レギュレーションの維持及びランプ電流設定の変更に起因するトランジェント中に使用される電流制御ループの速度を設定します。標準 $C_{CCI}$ 値は $0.01\mu F$ です。この値が大きいと、ランプ電流のオーバシュートが制限されます。この値が小さいと、ランプ電流設定の変化に対する応答が速くなりますが、極度に小さい値だと不安定になる恐れがあります。 $C_{CCI}$ が非常に大きいと、DPWMのストライク電圧の遅延が増加して、極端な場合には

図10. 電流検出波形

レギュレーションが喪失することがあります。C<sub>CCV</sub>が非常に大きい場合にも同じ結果になることに注意して下さい。

$C_6$ はループ補償に影響するだけでなく、波形、全体的な効率及び必要な最大二次トランス電圧にも影響します。 $C_6$ の値が小さいと、ループ安定性が向上します。この傾向は、リストライク電圧とDPWM中の動作電圧間の差が大きい(長くて細いCCFLの特徴)CCFLを使用しているシステムの場合に特に顕著です。 $C_6$ が小さいと、ランプ電流の増加と共にランプの動作電圧が落ちた時の安定性も向上します。ただし、 $C_6$ が小さいと必要な最大トランス電圧が増加します。 $C_7$ は $C_6$ と相互作用して、Royer周波数、RoyerのQ値及び全体的な効率に影響します。

$C_{CCV}$ はDPWMトランジェントと障害条件時の動作に影響する電圧制御ループの速度を設定します。DPWMが使用されていない場合、電圧制御ループは障害条件時にのみアクティブにする必要があります。 $C_{CCV}$ の標準値は3300pFです。障害過渡応答が許容範囲内で、DPWMパルスの始めに過剰なリンギングを生じさせないために必要な最小の $C_{CCV}$ 値を選択して下さい。 $C_{CCV}$ が設計上保護するようになっているワーストケースの障害条件は、DPWMパルスの開始時のオープンチューブ状態であることに注意して下さい。

C<sub>CCV</sub>が大きいと過渡的なオーバシュートは小さくなりますが、ストライク電圧への遅延が増加するためにDPWMのデューティサイクルが小さい時にレギュレーションを喪失する可能性があります。C<sub>CCV</sub>が小さいと、DPWMスタートアップが速くなり、障害条件への応答が速くなります。C<sub>CCV</sub>が小さすぎると、リンギングが起こりやすくなり、極端な場合には不安定になります。Royer発振器とバックインダクタの間では、幾分かのリンギングの発生が予想されますが、リンギングの一部はR5と並列にコンデンサを追加することによって抑圧することが出来ます。このコンデンサは次式を満たすように選択して下さい。

$1/(2 \times \pi \times R5 \times C) = リンギング周波数$

DPWM周波数が高く、DPWMのデューティサイクルが小さい場合、DPWMオン時間は短くなります。これにより、ランプ電流のトランジェントがDPWMオン時間を超える場合もあります。この場合、MAX1739/MAX1839はレギュレーションを喪失し、ランプ電流は決してランプ電流の設定点に達しません。この条件で動作している時は電源除去比が劣化します。DPWMオン時間が短すぎると、ランプ電流がランプアウトスレッショルドに達するだけの時間がなく、ランプアウト検出が作動します。これを防ぐには、(C<sub>CCV</sub>を下げることにより)ターンオントランジェントの継続時間を短くするか、(輝度コードを制限することにより)DPWMデューティサイクルを増やすか、あるいはDPWM周波数を低くして下さい(「DPWM周波数の同期」を参照)。

DPWMを始めとした「チョッピング」法は、一部のトランスで可聴ノイズを発生することがあります。これを防ぐために、トランスの選択に注意して下さい。

#### 調光範囲

調光範囲を設定するために必要な外部部品は、使用されているCCFLに大きく依存します。標準アプリケーション回路では、条件の厳しいCCFLが使用されています。 20:1 の調光範囲を実現するために、標準回路はC6の両端でフルランプ電流設定におけるCCFL両端の電圧降下よりも僅かに大きな電圧降下を生じさせています。これにより、 $V_{MINDAC}$ が最低 1Vまで低下してもこの回路の安定性が保証されます。このCCFLを使用してさらに調光範囲を増やすには、C6を増加させる必要がありますが、最大二次トランス電圧が増加するため、電圧定格の高いトランスが必要になります。良好な波形、Royer効率及び望ましいRoyer周波数を維持するには、その他の部品 $(-次トランスのインダクタンス及びC_7$ 等)も調整する必要があります。

#### その他の部品

ハイサイドMOSFETドライバは、C5とD2で形成される

外部ブースト回路によって駆動されます。BSTはシングルレベルショットキダイオードを通じてVLに接続し、0.1 μFセラミックコンデンサを通じてLXに接続して下さい。この回路は図8に示すように、N1を駆動するために必要な電力を供給します。ゲート容量の大きなMOSFETを使用する場合は、バイパスコンデンサのサイズも大きくする必要があります。BSTにおいて必要な電流は次式で表されます。

$IBST = 1mA d + QT \times f$

ここで、dはバックコントローラのデューティサイクル (98% max)、 $Q_T$ はMOSFETの全ゲート電荷、fは Royer発振器周波数の2倍です。

D2を流れる最大電流(I<sub>D</sub>)は次式で与えられます。

ID = IBST / (1 - d)

D5AとD5BはR13の両端の電流検出電圧を生成するために使用されます。これらのダイオードを流れる電流はランプ電流です。デュアル直列信号レベルダイオードを使用して下さい。

#### バイパス及び基板レイアウト

C4はVLとGNDの間に接続して下さい(他の信号経路と 共有されていない専用のトレースを使用して出来る 限り近くに配置して下さい)。グランドライン(静かな グランド、電源グランド及びランプ電流検出グランド)は C4のGND端で終わるようにして下さい。静かなグランド は、REF、CCV、R5及び(抵抗分圧器を使用する場合) MINDAC用に使用されます。電源グランドはC4のグランド から直接C9のグランド側に行きます。電源グランドが、 D1、N2及びバック電流検出抵抗(使用されている場合は CSとGNDの間)のリターン経路も提供するようにして 下さい。R13のグランド経路は独立にして下さい。これは、 静かなグランドを乱さないためと、また電源グランド の電圧降下に影響されないようにするためです。良好な レイアウトの例についてはMAX1739EVキットを参照 して下さい。

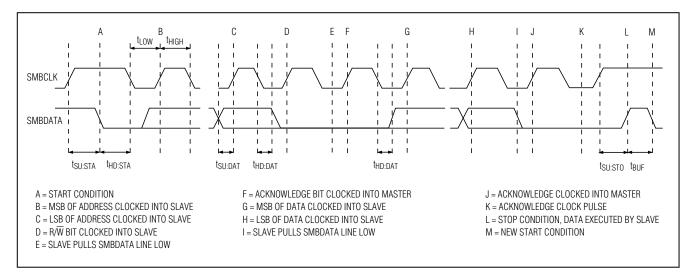

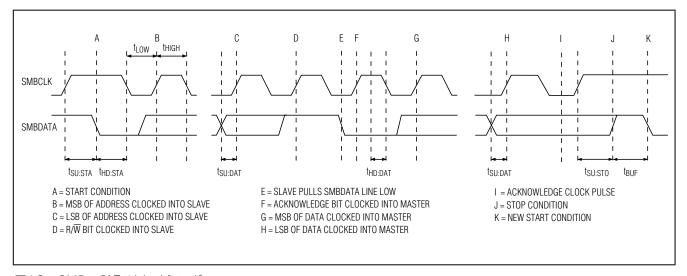

#### ディジタルインタフェース (MAX1739)

MODEがVLに接続されていると、CRF/SDA及びCTL/SCLピンはアナログ入力として機能しなくなり、代わりにSMBusコンパチブルな2線ディジタルインタフェースとして機能します。CRF/SDAは双方向性のデータライン、CTL/SCLは2線インタフェースのクロックラインで、それぞれSMBusのSMBDATA及びSMBCLKラインに対応しています。MAX1739はバイト書込み、バイト読取り及びバイト受信プロトコルを使用します(図11)。SMBusプロトコルはSystem Management Bus Specification v1.08に記載されており、www.sbsforum.orgで参照することが出来ます。

#### Write-Byte Format

| S | ADDRESS | WR | ACK | COMMAND | ACK | DATA   | ACK | Р |

|---|---------|----|-----|---------|-----|--------|-----|---|

|   | 7 bits  | 1b | 1b  | 8 bits  | 1b  | 8 bits | 1b  |   |

Slave Address

Command Byte: selects which register you are writing to

Data Byte: data goes into the register set by the command byte

#### **Read-Byte Format**

| S | ADDRESS | WR | ACK | COMMAND | ACK | s | ADDRESS | RD | ACK | DATA   | /// | Р |

|---|---------|----|-----|---------|-----|---|---------|----|-----|--------|-----|---|

|   | 7 bits  | 1b | 1b  | 8 bits  | 1b  |   | 7 bits  | 1b | 1b  | 8 bits | 1b  |   |

Slave Address

Command Byte: selects which register you are reading from

Slave Address: repeated due to change in data-flow direction

Data Byte: reads from the register set by the command byte

#### Send-Byte Format

#### **Receive-Byte Format**

| S | ADDRESS | WR | ACK | COMMAND | ACK | Р | S | ADDRESS | RD | ACK | DATA   | /// | Р |

|---|---------|----|-----|---------|-----|---|---|---------|----|-----|--------|-----|---|

|   | 7 bits  | 1b | 1b  | 8 bits  | 1b  |   |   | 7 bits  | 1b | 1b  | 8 bits | 1b  |   |

Command Byte: sends command with no data; usually used for one-shot command

Slave Address

Data Byte: reads data from the register commanded by the last read-byte or write-byte transmission; also used for SMBus Alert Response return address

$S = Start \ condition$  $P = Stop \ condition$  Shaded = Slave transmission Ack= Acknowledged = 0 WR = Write = 0RD = Read = 1

/// = Not acknowledged = 1

図11. SMBusプロトコル

MAX1739はスレーブオンリーデバイスで、7ビットアドレス0b0101101に応答します(つまり、RWがクリアで書込みを示す場合は、0x5Aに対応)。MAX1739は3つの機能レジスタを持っています。つまり、5ビット輝度レジスタ(BRIGHT4~BRIGHT0)、3ビットシャットダウンモードレジスタ(SHMD2~SHMD0)及び2ビット状態レジスタ(STATUS1~STATUS0)の3つです。さらに、本デバイスは、8ビットチップIDレジスタ、8ビットチップ改訂レジスタ及び8ビット製造元レジスタという3つの識別(ID)レジスタを持っています。

CRF/SDA及びCTL/SCLピンは遅いエッジに対応できるシュミットトリガ入力を備えていますが、立上り/立下りエッジはそれぞれ1µs及び300nsより速くして下さい。

通信は、マスターがSTART条件(CTL/SCLがハイの時のCRF/SDAのハイからローへの遷移)によって送信の開始を知らせた時に始まります。マスターがスレーブとの通信を終えると、マスターはSTOP条件(P)を発生します(これはCTL/SCLがハイの時のCRF/SDAのローからハイへの遷移です)(図10、11)。これでバスがフリーになり次の遷移を受け付けることが出来ます。図12と13に2線インタフェースの信号のタイミング図を示します。アドレスバイト、コマンドバイト及びデータ

バイトがSTART条件とSTOP条件の間に送信されます。 CRF/SDAの状態はCTL/SCLがローの時にのみ変化する ことが許されます(STARTとSTOP条件を除く)。データ は8ビットワードで送信され、CTL/SCLの立上がり エッジでサンプリングされます。各バイトがMAX1739に 出入りするのに9バイトを要します。これは、9番目の クロックでマスター又はスレーブが正しいバイトの受信 をアクノレッジするためです。MAX1739は正しい スレーブアドレスの後で $R\overline{W} = 0$ を受取ると、(プロトコル に応じて)1又は2バイトの情報を受信することを予期し ます。データのバイトを同期入力する前にスタート 又はストップ条件を検出すると、デバイスはこれをエラー 条件とみなして全てのデータを無視します。送信が 正しく完了すると、STOP(又はRESTART)条件の直後に レジスタが更新されます。MAX1739は正しいスレーブ アドレスの後でRW=1を受信した場合、その前のコマンド バイトで選択されたレジスタのデータを同期出力する ことを予期します。

#### SMBusコマンド

MAX1739レジスタは幾つかの冗長なコマンド(バイト 読取り及びバイト書込みプロトコルのコマンドバイト) を通じてアクセスすることが出来ます。これらの

図12. SMBus書込みタイミング

図13. SMBus読取りタイミング

コマンドは、輝度、SHMD、状態又はIDレジスタを読む ために使用することが出来ます。

表6にコマンドバイトのレジスタ割当及び各レジスタのパワーオン状態がまとめてあります。MAX1739はより速いデータ転送を行うためのバイト読取りプロトコルもサポートしています。このプロトコルは最後のコマンドバイトによって指し示されたレジスタ構成にアクセスします。パワーアップの直後、バイト受信プロトコルによって返されたデータバイトは左に行揃えされた輝度レジスタの内容です(つまり、BRIGHT4はデータバイトのMSB位置にあります)。残りのビットは1、STATUS1及びSTATUS0を含んでいます。これにより、0b10XXXXXX(0x80)コマンドでバイト読取りプロトコルを使うの

と同じ結果が得られます。マルチマスターシステムでは短いプロトコルを使用する際に注意が必要です。これは、第2のマスターが第1のマスターに知らせることなくコマンドバイトを上書きする可能性があるためです。シャットダウン中、シリアルインタフェースは完全機能状態に留まります。本デバイスは制限付でワード読取り/書込みプロトコルもサポートします。ワード読取りは、第2のバイトが0xFFを返すほかはバイト読取りと同様です。また、ワード書込みもバイト書込みと同様に機能します。第2のデータバイトのアクノレッジ及び更新は、最初のデータバイトのアクノレッジ及び更新の後で行われます。

#### 表6. コマンドの説明

|                    |                        | POR  |                  |              | DATA         | REGISTER         | BIT ASSIG        | NMENT       |             |                  |

|--------------------|------------------------|------|------------------|--------------|--------------|------------------|------------------|-------------|-------------|------------------|

| R OR W<br>PROTOCOL |                        |      | BIT 7<br>(MSB)   | BIT 6        | BIT 5        | BIT 4            | BIT 3            | BIT 2       | BIT 1       | BIT 0<br>(LSB)   |

| Read and<br>Write  | 0x01<br>0b0XXX<br>XX01 | 0x17 | 0                | 0            | 0            | BRIGHT4<br>(MSB) | BRIGHT3          | BRIGHT2     | BRIGHT1     | BRIGHTO<br>(LSB) |

| Read and<br>Write  | 0x02<br>0b0XXX<br>XX10 | 0xF9 | STATUS1          | STATUS0      | 1            | 1                | 1                | SHMD2       | SHMD1       | SHMD0            |

| Read<br>Only       | 0x03<br>0b0XXX<br>XX11 | 0x96 | ChipID7          | ChipID6<br>0 | ChipID5<br>0 | ChipID4          | ChipID3<br>0     | ChipID2     | ChipID1     | ChipID0<br>0     |

| Read<br>Only       | 0x04<br>0b0XXX<br>XX00 | 0x00 | ChipRev7         | ChipRev6     | ChipRev5     | ChipRev4         | ChipRev3         | ChipRev2    | ChipRev1    | ChipRev0<br>0    |

| Read and<br>Write  | 0x40<br>0b10XX<br>XXXX | 0xBF | BRIGHT4<br>(MSB) | BRIGHT3      | BRIGHT2      | BRIGHT1          | BRIGHT0<br>(LSB) | 1           | STATUS1     | STATUS0          |

| Read<br>Only       | 0xFE<br>0b11XX<br>XXX0 | 0x4D | MfgID7<br>0      | MfgID6<br>1  | MfgID5<br>0  | MfgID4<br>0      | MfgID3<br>1      | MfgID2<br>1 | MfgID1<br>0 | MfgID0<br>1      |

| Read<br>Only       | 0xFF<br>0b11XX<br>XXX1 | 0x96 | ChipID7          | ChipID6<br>0 | ChipID5<br>0 | ChipID4          | ChipID3<br>0     | ChipID2     | ChipID1     | ChipID0<br>0     |

<sup>\*</sup>The hexadecimal command byte shown is recommended for maximum forward compatibility with future MAXIM products.

#### 輝度レジスタ [BRIGHT4-BRIGHT0](POR = 0b10111)

5ビット輝度レジスタは調光制御に使用される5ビット輝度コードに対応しています(「調光範囲」を参照)。BRIGHT4-BRIGHT0 = 0b00000は最小輝度を設定し、BRIGHT4-BRIGHT0 = 0b11111は最大輝度を設定します。デバイスが電流をアナログ調光、DPWM調光、あるいはその両方で制御するかを決定するのは、SMBusインタフェースではなくMINDACです(表2)。

#### シャットダウンモードレジスタ [SHMD2-SHMD0](POR = 0b001)

3ビットシャットダウンモードレジスタは、SH/SUSピンが表7に示すようにトグルされた時にデバイスの動作を設定します。SH/SUSの状態にかかわりなく直接CCFLをシャットオフするためにシャットダウンモードレジスタを使うことも出来ます(表8)。

#### 状態レジスタ [STATUS1-STATUS0](POR = 0b11)

状態レジスタは障害条件に関する情報を返します。ランプがトランスの二次側に接続されていないと、MAX1739はCSAVの検出スレッショルドを超えていないことを検出し、2秒後にSTATUS1ビットをクリアします(「ランプアウト検出」を参照)。STATUS1ビットはラッチされているため、ランプアウト条件がなくなっても0に留まります。STATUS1=0の場合、ランプは強制的にオフになります。STATUS0は、過電流条件が検出される限り1です。あるDPWM期間中に過電流条件が検出されると、STATUS0はその次のDPWM期間中クリアされた状態を維持します。あるDPWM期間中に過電流条件が検出されないと、STATUS0はその次のDPWM期間中セットされた状態を

維持します。シャットダウン状態に入ったり、モードレジスタに書込んだり、SH/SUSをトグルすることによりCCFLランプを強制的にオフにすると、STATUS1がセットされます。

#### IDレジスタ

IDレジスタは製造元、チップID及びチップ改訂番号に関する状態を返します。MAX1739は高機能CCFLコントローラの最初の世代であるため、ChipRevは0x00です。MfgIDレジスタを読むと、(マキシム社を示す)"M"のASCIIコードである0x4Dが返されます。ChipIDレジスタは0x96を返します。これらのレジスタに書込んでも何も起こりません。

#### 表7. SHMDレジスタのビット説明

| BIT | NAME  | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                               |  |

|-----|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2   | SHMD2 | 0            | SHMD2 = 1 forces the lamp off and sets STATUS1. SHMD2 = 0 allows the lamp to operate, though it may still be shut down by the $\overline{\text{SH}}/\text{SUS}$ pin (depending on the state of SHMD1 and SHMD0).                                          |  |

| 1   | SHMD1 | 0            | When $\overline{SH}$ /SUS = 0, this bit has no effect. $\overline{SH}$ /SUS = 1 and SHMD1 = 1 forces the lamp off and sets STATUS1. $\overline{SH}$ /SUS = 1 and SHMD1 = 0 allow the lamp to operate, though it may still be shut down by the SHMD2 bit.  |  |

| 0   | SHMD0 | 1            | When $\overline{SH}$ /SUS = 1, this bit has no effect. $\overline{SH}$ /SUS = 0 and SHMD0 = 1 forces the lamp off and sets STATUS1. $\overline{SH}$ /SUS = 0 and SHMD0 = 0 allows the lamp to operate, though it may still be shut down by the SHMD2 bit. |  |

#### 表8. SH/SUS及びSHMDレジスタの真理値表

| SH/SUS | SHMD2 | SHMD1 | SHMD0 | OPERATING MODE        |

|--------|-------|-------|-------|-----------------------|

| 0      | 0     | X     | 0     | Operate               |

| 0      | 0     | X     | 1     | Shutdown, STATUS1 set |

| 1      | 0     | 0     | X     | Operate               |

| 1      | 0     | 1     | X     | Shutdown, STATUS1 set |

| X      | 1     | X     | X     | Shutdown, STATUS1 set |

X = Don't care

#### 表9. 状態レジスタのビット説明(読取り専用/書込んでも何も起こりません)

| ВІТ | IT NAME POR STATE |   | DESCRIPTION                                                                                                                                                                                                                                             |

|-----|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | STATUS1           | 1 | STATUS1 = 0 means that a lamp-out condition has been detected. The STATUS1 bit stays clear even after the lamp-out condition has gone away. The only way to set STATUS1 is to shut off the lamp by programming the mode register or by toggling SH/SUS. |

| 0   | STATUS0           | 1 | STATUS0 = 0 means that an overcurrent condition was detected during the previous digital PWM period. STATUS0 = 1 means that no overcurrent condition was detected during the previous digital PWM period.                                               |

### ピン配置(続き)\_\_\_\_\_

| TOP VIEW |          | 1       |

|----------|----------|---------|

| REF [    | <u> </u> | 20 BATT |

| MINDAC : | 2        | 19 DH   |

| CCI      | 3        | 18 LX   |

| CCV -    | MIXKM    | 17 BST  |

| SH [     | MAX1839  | 16 VL   |

| CRF [    | 6        | 15 GND  |

| CTL [    | 7        | 14 CS   |

| MODE [   | 3        | 13 DL1  |

| CSAV     | 9        | 12 DL2  |

| CTFB 1   | 0        | 11 SYNC |

|          |          | J       |

|          | QSOP     |         |

### チップ情報 \_\_\_\_\_

TRANSISTOR COUNT: 7194

#### パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packages をご参照下さい。)

### マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

26 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600