#

## 低電力、デュアル、10ビット電圧出力DAC シリアルインタフェース付

概要

MAX5158/MAX5159は、低電力、シリアル、電圧出力、 デュアル10ビットD/Aコンバータ(DAC)です。これらの 製品は、単一電源+5V(MAX5158)又は+3V(MAX5159) からの消費電流が僅か500µAとなっています。これら のデバイスはレイルトゥレイル®出力スイングを特長と し、省スペースの16ピンQSOPパッケージで提供されて います。DAC出力アンプは、ダイナミックレンジを最小 にするために、+2V/Vの内部利得で構成されています。

3線シリアルインタフェースは、SPI™/QSPI™及び Microwire™とコンパチブルです。各DACには、入力レジ スタとして構成したダブルバッファ入力と、入力レジ スタ及びDACレジスタを16ビットシリアルワードで個別 又は同時に更新できるDACレジスタを備えています。さ らに、2µAプログラマブルシャットダウン、ハードウェア シャットダウンロックアウト、AC及びDC信号を受け付け る各DAC用の個別リファレンス電圧入力、全てのレジ スタとDACをゼロにリセットするアクティブロークリア 入力(CL)も備えています。MAX5158/MAX5159では、 機能拡張用のプログラマブルロジックピンに加え、デイ ジーチェーン構成用のシリアルデータ出力ピンも提供 されています。

#### アプリケーション \_\_\_

ディジタルオフセット及び利得調整

μP制御システム

モーション制御

リモート工業制御

#### 特長

- ◆ 内部利得+2V/Vの10ビットデュアルDAC

- ◆ レイルトゥレイル出力スイング

- ◆ 8µsセトリング時間

- ◆ 単一電源動作: +5V (MAX5158)

- +3V (MAX5159)

- ◆ 低自己消費電流:500µA(通常動作時)

- 2μA(シャットダウンモード時)

- ◆ SPI/QSPI及びMicrowireとコンパチブル

- ◆ 省スペースの16ピンQSOPパッケージで提供

- ◆ パワーオンリセットによってレジスタ及び DACをゼロにクリア

- ◆ 調整可能な出力オフセット

#### 型番

| PART       | TEMP. RANGE     | PIN-PACKAGE    |

|------------|-----------------|----------------|

| MAX5158CPE | 0°C to +70°C    | 16 Plastic DIP |

| MAX5158CEE | 0°C to +70°C    | 16 QSOP        |

| MAX5158EPE | -40°C to +85°C  | 16 Plastic DIP |

| MAX5158EEE | -40°C to +85°C  | 16 QSOP        |

| MAX5158MJE | -55°C to +125°C | 16 CERDIP*     |

#### Ordering Information continued at end of data sheet.

\*Contact factory for availability.

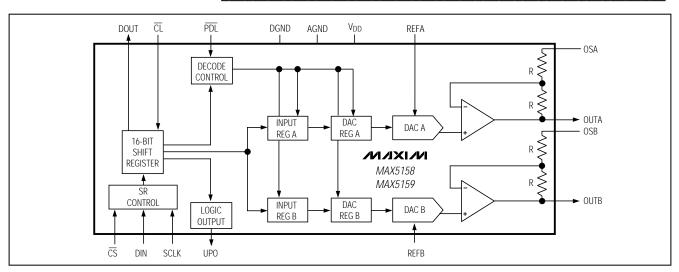

#### ファンクションダイアグラム

レイルトゥレイルは日本モトローラの登録商標です。MicrowireはNational Semiconductor Corp.の商標です。 SPI及びQSPIはモトローラの商標です。

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD to DGND       -0.3V to +6V         AGND to DGND       ±0.3V         OSA, OSB to AGND       (AGND - 4V) to (VDD + 0.3V)         REF_, OUT_ to AGND       -0.3V to (VDD + 0.3V) | Continuous Power Dissipation (T <sub>A</sub> = +70°C) Plastic DIP (derate 10.5mW/°C above +70°C)842mW QSOP (derate 8.30mW/°C above +70°C) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Inputs (SCLK, DIN, CS, CL, PDL) to DGND(-0.3V to +6V)                                                                                                                     | MAX515C_ E0°C to +70°C<br>MAX515E_ E40C° to +85°C                                                                                         |

| Digital Outputs (DOUT, UPO) to DGND0.3V to (V <sub>DD</sub> + 0.3V)  Maximum Current into Any Pin±20mA                                                                            | MAX515MJE55°C to +125°C Storage Temperature Range65°C to +160°C Lead Temperature (soldering, 10sec)+300°C                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—MAX5158**

$(V_{DD} = +5V \pm 10\%, V_{REFA} = V_{REFB} = 2.048V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{AB} = +25^{\circ}C$  (OS\_ tied to AGND for a gain of +2V/V).)

| PARAMETER                                       | SYMBOL            | CONDITIONS                                                                              | MIN   | TYP  | MAX                   | UNITS  |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|-------|------|-----------------------|--------|

| STATIC PERFORMANCE                              | L                 |                                                                                         |       |      |                       | ı      |

| Resolution                                      |                   |                                                                                         | 10    |      |                       | Bits   |

| Integral Nonlinearity                           | INL               | (Note 1)                                                                                |       |      | ±1                    | LSB    |

| Differential Nonlinearity                       | DNL               | Guaranteed monotonic                                                                    |       |      | ±1                    | LSB    |

| Offset Error                                    | Vos_              | Code = 2                                                                                |       |      | ±6                    | mV     |

| Offset Tempco                                   | TCVos             | Normalized to 2.048V                                                                    |       | 4    |                       | ppm/°C |

| Gain Error                                      |                   |                                                                                         |       | -0.1 | 1                     | LSB    |

| Gain-Error Tempco                               |                   | Normalized to 2.048V                                                                    |       | 4    |                       | ppm/°C |

| V <sub>DD</sub> Power-Supply<br>Rejection Ratio | PSRR              | 2.7V ≤ V <sub>DD</sub> ≤ 5.5V                                                           |       | 20   | 260                   | μV/V   |

| REFERENCE INPUT                                 |                   |                                                                                         |       |      |                       | ı      |

| Reference Input Range                           | REF               |                                                                                         | 0     |      | V <sub>DD</sub> - 1.4 | V      |

| Reference Input Resistance                      | R <sub>REF</sub>  | Minimum with code 1558 hex                                                              | 18 25 |      |                       | kΩ     |

| MULTIPLYING-MODE PERFO                          | RMANCE            |                                                                                         | •     |      |                       |        |

| Reference 3dB Bandwidth                         |                   | Input code = 1FF8 hex,<br>V <sub>REF</sub> _ = 0.67Vp-p at 0.75V <sub>DC</sub>          |       | 300  |                       | kHz    |

| Reference Feedthrough                           |                   | Input code = 0000 hex,<br>V <sub>REF</sub> _ = (V <sub>DD</sub> - 1.4 Vp-p) at 1kHz     |       | -82  |                       | dB     |

| Signal-to-Noise plus<br>Distortion Ratio        | SINAD             | Input code = 1FF8 hex,<br>V <sub>REF</sub> _ = 1Vp-p at 1.25V <sub>DC</sub> , f = 25kHz | 75    |      | dB                    |        |

| DIGITAL INPUTS                                  | "                 |                                                                                         | '     |      |                       |        |

| Input High Voltage                              | VIH               | CL, PDL, CS, DIN, SCLK                                                                  | 3     |      |                       | V      |

| Input Low Voltage                               | VIL               | CL, PDL, CS, DIN, SCLK 0.                                                               |       | 0.8  | V                     |        |

| Input Hysteresis                                | V <sub>H</sub> YS | 200                                                                                     |       |      | mV                    |        |

| Input Leakage Current                           | I <sub>IN</sub>   | $V_{IN} = 0V \text{ to } V_{DD}$ 0.001 ±1                                               |       |      | ±1                    | μΑ     |

| Input Capacitance                               | CIN               |                                                                                         |       | 8    |                       | pF     |

#### **ELECTRICAL CHARACTERISTICS—MAX5158 (continued)**

$(V_{DD} = +5V \pm 10\%, V_{REFA} = V_{REFB} = 2.048V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C \ (OS\_ \ tied \ to \ AGND \ for \ a \ gain \ of \ +2V/V).)$

| PARAMETER                                    | SYMBOL           | CONDITIONS                                                                                                                      |                       | TYP                  | MAX  | UNITS |

|----------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|-------|

| DIGITAL OUTPUTS (DOUT, UPO)                  |                  |                                                                                                                                 | <u>'</u>              |                      |      |       |

| Output High Voltage                          | Voн              | ISOURCE = 2mA                                                                                                                   | V <sub>DD</sub> - 0.5 |                      |      | V     |

| Output Low Voltage                           | V <sub>OL</sub>  | I <sub>SINK</sub> = 2mA                                                                                                         |                       | 0.13                 | 0.4  | V     |

| DYNAMIC PERFORMANCE                          |                  |                                                                                                                                 | •                     |                      |      |       |

| Voltage Output Slew Rate                     | SR               |                                                                                                                                 |                       | 0.75                 |      | V/µs  |

| Output Settling Time                         |                  | To 1/2LSB of full-scale, V <sub>STEP</sub> = 4V                                                                                 |                       | 8                    |      | μs    |

| Output Voltage Swing                         |                  | Rail-to-rail (Note 2)                                                                                                           |                       | 0 to V <sub>DD</sub> |      | V     |

| OSA or OSB Input Resistance                  | Ros_             |                                                                                                                                 | 24                    | 34                   |      | kΩ    |

| Time Required to Exit Shutdown               |                  |                                                                                                                                 |                       | 25                   |      | μs    |

| Digital Feedthrough                          |                  | $\overline{\text{CS}} = \text{V}_{\text{DD}},  \text{f}_{\text{DIN}} = 100 \text{kHz},  \text{V}_{\text{SCLK}} = 5 \text{Vp-p}$ |                       | 5                    |      | nV-s  |

| Digital Crosstalk                            |                  |                                                                                                                                 |                       | 5                    |      | nV-s  |

| POWER SUPPLIES                               |                  |                                                                                                                                 | <u>'</u>              |                      |      |       |

| Positive Supply Voltage                      | V <sub>DD</sub>  |                                                                                                                                 | 4.5                   |                      | 5.5  | V     |

| Power-Supply Current                         | I <sub>DD</sub>  | (Note 3)                                                                                                                        |                       | 0.5                  | 0.65 | mA    |

| Power-Supply Current in Shutdown             | IDD(SHDN)        | (Note 3)                                                                                                                        |                       | 2                    | 10   | μΑ    |

| Reference Current in Shutdown                |                  |                                                                                                                                 |                       | 0                    | ±1   | μΑ    |

| TIMING CHARACTERISTICS                       |                  |                                                                                                                                 |                       |                      |      |       |

| SCLK Clock Period                            | tcp              | (Note 4)                                                                                                                        | 100                   |                      |      | ns    |

| SCLK Pulse Width High                        | tch              |                                                                                                                                 | 40                    |                      |      | ns    |

| SCLK Pulse Width Low                         | tcL              |                                                                                                                                 | 40                    |                      |      | ns    |

| CS Fall to SCLK Rise Setup Time              | tcss             |                                                                                                                                 | 40                    |                      |      | ns    |

| SCLK Rise to CS Rise Hold Time               | tcsh             |                                                                                                                                 | 0                     |                      |      | ns    |

| SDI Setup Time                               | t <sub>DS</sub>  |                                                                                                                                 | 40                    |                      |      | ns    |

| SDI Hold Time                                | t <sub>DH</sub>  |                                                                                                                                 | 0                     |                      |      | ns    |

| SCLK Rise to DOUT<br>Valid Propagation Delay | t <sub>DO1</sub> | C <sub>LOAD</sub> = 200pF                                                                                                       |                       |                      | 80   | ns    |

| SCLK Fall to DOUT<br>Valid Propagation Delay | t <sub>DO2</sub> | C <sub>LOAD</sub> = 200pF                                                                                                       |                       |                      | 80   | ns    |

| SCLK Rise to CS Fall Delay                   | tcs0             |                                                                                                                                 | 10                    |                      |      | ns    |

| CS Rise to SCLK Rise Hold                    | tCS1             |                                                                                                                                 | 40                    |                      |      | ns    |

| CS Pulse Width High                          | tcsw             |                                                                                                                                 | 100                   |                      |      | ns    |

- Note 1: Accuracy is specified from code 2 to code 1023.

- Note 2: Accuracy is better than 1LSB for V<sub>OUT</sub> greater than 6mV and less than V<sub>DD</sub> 50mV. Guaranteed by PSRR test at the end points.

- **Note 3:** Digital inputs are set to either  $V_{DD}$  or DGND, code = 0000 hex,  $R_L = \infty$ .

- Note 4: SCLK minimum clock period includes rise and fall times.

#### **ELECTRICAL CHARACTERISTICS—MAX5159**

$(V_{DD} = +2.7V \text{ to } +3.6V, V_{REFA} = V_{REFB} = 1.25V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$  (OS\_ pins tied to AGND for a gain of +2V/V).)

| PARAMETER                                           | PARAMETER SYMBOL CONDITIONS |                                                                                      | MIN                   | TYP                 | MAX                   | UNITS  |

|-----------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|--------|

| STATIC PERFORMANCE                                  | <u>'</u>                    |                                                                                      |                       |                     |                       |        |

| Resolution                                          |                             |                                                                                      | 10                    |                     |                       | Bits   |

| Integral Nonlinearity                               | INL                         | (Note 5)                                                                             |                       |                     | ±1                    | LSB    |

| Differential Nonlinearity                           | DNL                         | Guaranteed monotonic                                                                 |                       |                     | ±1                    | LSB    |

| Offset Error                                        | Vos                         | Code = 3                                                                             |                       |                     | ±6                    | mV     |

| Offset Tempco                                       | TCVos                       | Normalized to 1.25V                                                                  |                       | 6.5                 |                       | ppm/°C |

| Gain Error                                          |                             |                                                                                      |                       | -0.1                | ±1                    | LSB    |

| Gain-Error Tempco                                   |                             | Normalized to 1.25V                                                                  |                       | 6.5                 |                       | ppm/°C |

| V <sub>DD</sub> Power-Supply<br>Rejection Ratio     | PSRR                        | 2.7V ≤ <sub>VDD</sub> ≤ 3.6V                                                         |                       | 40                  | 320                   | μV/V   |

| REFERENCE INPUT (VREF)                              |                             |                                                                                      |                       |                     |                       |        |

| Reference Input Range                               | REF                         |                                                                                      | 0                     |                     | V <sub>DD</sub> - 1.4 | V      |

| Reference Input Resistance                          | R <sub>REF</sub>            | Minimum with code 1558 hex                                                           | 18                    | 25                  |                       | kΩ     |

| MULTIPLYING-MODE PERFOR                             | RMANCE                      |                                                                                      |                       |                     |                       |        |

| Reference 3dB Bandwidth                             |                             | Input code = 1FF8 hex,<br>V <sub>REF</sub> _ = 0.67Vp-p at 0.75V <sub>DC</sub>       |                       | 300                 |                       | kHz    |

| Reference Feedthrough                               |                             | Input code = 0000 hex,<br>V <sub>REF</sub> _ = (V <sub>DD</sub> - 1.4)Vp-p at 1kHz   |                       | -82                 |                       | dB     |

| Signal-to-Noise plus<br>Distortion Ratio            | SINAD                       | Input code = 1FF8 hex,<br>V <sub>REF</sub> _ = 1Vp-p at 1V <sub>DC</sub> , f = 15kHz |                       | 73                  |                       | dB     |

| DIGITAL INPUTS                                      |                             |                                                                                      |                       |                     |                       |        |

| Input High Voltage                                  | VIH                         | CL, PDL, CS, DIN, SCLK                                                               | 2.2                   |                     |                       | V      |

| Input Low Voltage                                   | VIL                         | CL, PDL, CS, DIN, SCLK                                                               |                       |                     | 0.8                   | V      |

| Input Hysteresis                                    | VHYS                        |                                                                                      |                       | 200                 |                       | mV     |

| Input Leakage Current                               | I <sub>IN</sub>             | $V_{IN} = OV \text{ to } V_{DD}$                                                     |                       | 0                   | ±1                    | μΑ     |

| Input Capacitance                                   | CIN                         |                                                                                      |                       | 8                   |                       | рF     |

| DIGITAL OUTPUTS                                     | *                           |                                                                                      |                       |                     |                       |        |

| Output High Voltage                                 | Voн                         | I <sub>SOURCE</sub> = 2mA                                                            | V <sub>DD</sub> - 0.5 |                     |                       | V      |

| Output Low Voltage                                  | VoL                         | I <sub>SINK</sub> = 2mA                                                              |                       | 0.13                | 0.4                   | V      |

| DYNAMIC PERFORMANCE (D                              | OUT, UPO)                   |                                                                                      |                       |                     |                       |        |

| Voltage Output Slew Rate                            | SR                          |                                                                                      |                       | 0.75                |                       | V/µs   |

| Output Settling Time                                |                             | To 1/2LSB of full-scale, V <sub>STEP</sub> = 2.5V                                    |                       | 8                   |                       | μs     |

| Output Voltage Swing                                |                             | Rail-to-rail (Note 6)                                                                |                       | 0 to V <sub>D</sub> | D                     | V      |

| OSA or OSB Input Resistance                         | Ros_                        |                                                                                      | 24                    | 34                  |                       | kΩ     |

| Time Required for Valid<br>Operation after Shutdown |                             |                                                                                      |                       | 25                  |                       | μs     |

| Digital Feedthrough                                 |                             | $\overline{CS} = V_{DD}$ , $f_{DIN} = 100$ kHz, $V_{SCLK} = 3$ Vp-p                  |                       | 5                   |                       | nV-s   |

| Digital Crosstalk                                   |                             |                                                                                      |                       | 5                   |                       | nV-s   |

#### **ELECTRICAL CHARACTERISTICS—MAX5159 (continued)**

$(V_{DD} = +2.7 \text{V to } +3.6 \text{V}, V_{REFA} = V_{REFB} = 1.25 \text{V}, R_L = 10 \text{k}\Omega, C_L = 100 \text{pF}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C} \text{ (OS\_pins tied to AGND for a gain of } +2 \text{V/V}).)$

| PARAMETER                                             | SYMBOL                 | CONDITIONS                | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------|------------------------|---------------------------|-----|-----|-----|-------|

| POWER SUPPLIES                                        |                        |                           |     |     |     | ,     |

| Positive Supply Voltage                               | V <sub>DD</sub>        |                           | 2.7 |     | 3.6 | V     |

| Power-Supply Current                                  | IDD                    | (Note 7)                  |     | 0.5 | 0.6 | mA    |

| Power-Supply Current in Shutdown                      | I <sub>DD</sub> (SHDN) | (Note 7)                  |     | 1   | 8   | μΑ    |

| Reference Current in Shutdown                         |                        |                           |     |     | ±1  | μΑ    |

| TIMING CHARACTERISTICS                                | S                      |                           |     |     |     |       |

| SCLK Clock Period                                     | tcp                    | (Note 4)                  | 100 |     |     | ns    |

| SCLK Pulse Width High                                 | tcH                    |                           | 40  |     |     | ns    |

| SCLK Pulse Width Low                                  | t <sub>CL</sub>        |                           | 40  |     |     | ns    |

| CS Fall to SCLK Rise<br>Setup Time                    | tcss                   |                           | 40  |     |     | ns    |

| SCLK Rise to $\overline{\text{CS}}$ Rise<br>Hold Time | tCSH                   |                           | 0   |     |     | ns    |

| SDI Setup Time                                        | t <sub>DS</sub>        |                           | 50  |     |     | ns    |

| SDI Hold Time                                         | tDH                    |                           | 0   |     |     | ns    |

| SCLK Rise to DOUT Valid Propagation Delay             | t <sub>DO1</sub>       | C <sub>LOAD</sub> = 200pF |     |     | 120 | ns    |

| SCLK Fall to DOUT Valid<br>Propagation Delay          | t <sub>DO2</sub>       | C <sub>LOAD</sub> = 200pF |     |     | 120 | ns    |

| SCLK Rise to CS Fall Delay                            | tcs0                   |                           | 10  |     |     | ns    |

| CS Rise to SCLK Rise Hold                             | t <sub>CS1</sub>       |                           | 40  |     |     | ns    |

| CS Pulse Width High                                   | tcsw                   |                           | 100 |     |     | ns    |

Note 5: Accuracy is specified from code 3 to code 1023.

Note 6: Accuracy is better than 1LSB for V<sub>OUT</sub> greater than 6mV and less than V<sub>DD</sub> - 80mV. Guaranteed by PSRR test at the end points.

**Note 7:** Digital inputs are set to either  $V_{DD}$  or DGND, code = 0000 hex,  $R_L = \infty$ .

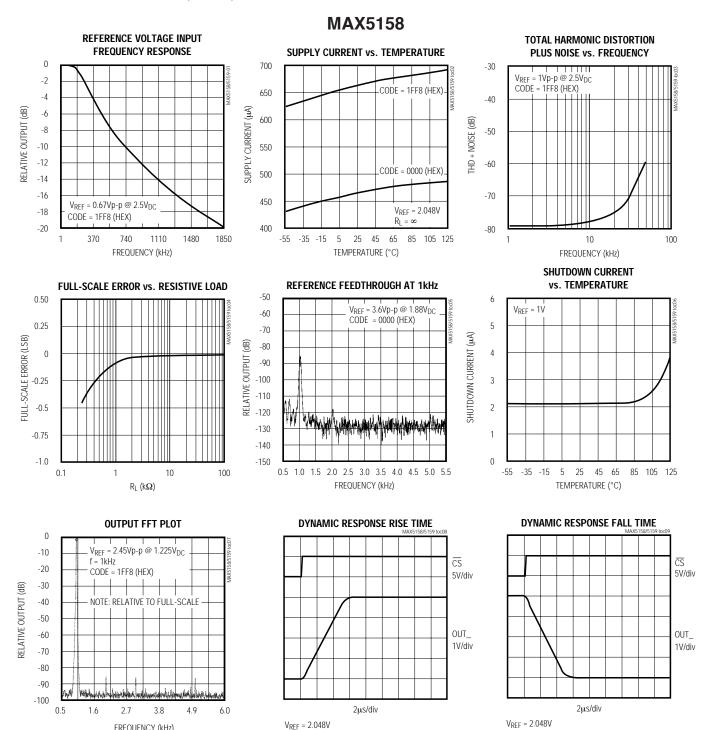

標準動作特性

$(V_{DD} = +5V, R_I = 10k\Omega, C_I = 100pF, OS_pins tied to AGND, T_A = +25°C, unless otherwise noted.)$

FREQUENCY (kHz)

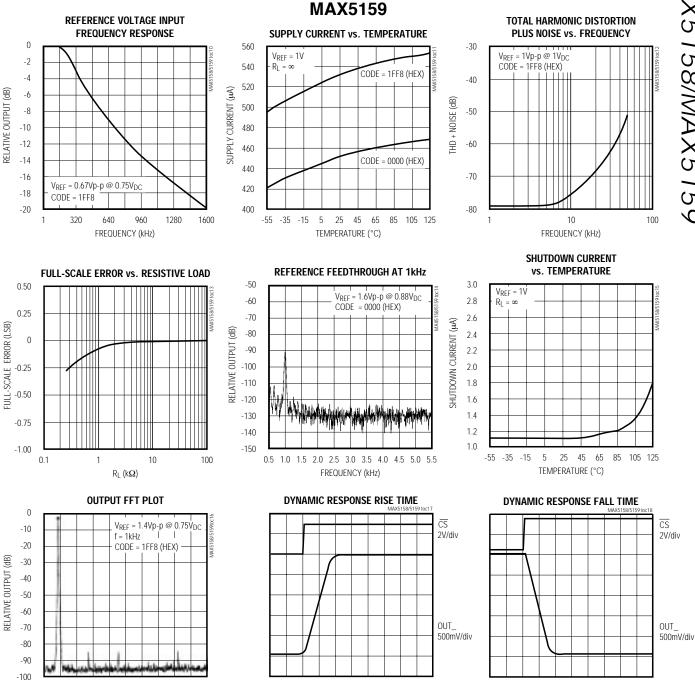

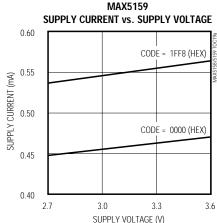

標準動作特性(続き)\_

$(V_{DD} = +3V, R_{I} = 10k\Omega, C_{I} = 100pF, OS_{pins} \text{ tied to AGND, } T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

2us/div

V<sub>REF</sub> = 1.25V

0.5

3.8

FREQUENCY (kHz)

4.9

6.0

2μs/div

$V_{REF} = 1.25V$

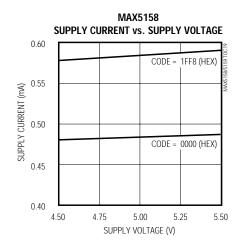

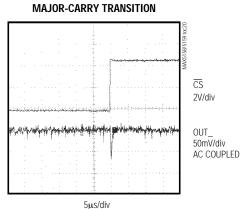

標準動作特性(続き)\_

$(V_{DD} = +5V \text{ (MAX5158)}, V_{DD} = +3V \text{ (MAX5159)}, R_L = 10k\Omega, C_L = 100pF, OS_pins tied to AGND, unless otherwise noted.)$

#### MAX5158/MAX5159

MAX5158

TRANSITION FROM 1000 (HEX) TO 0FF8 (HEX)

MAX5158

DIGITAL FEEDTHROUGH

SCLK

5V/div

OUTA

500µV/div

AC COUPLED

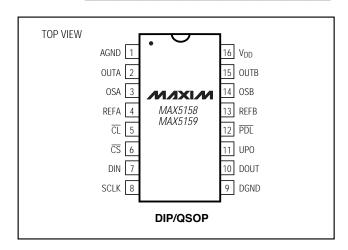

#### 端子説明

| 端子 | 名称              | 機能                                                |

|----|-----------------|---------------------------------------------------|

| 1  | AGND            | アナロググランド                                          |

| 2  | OUTA            | DAC A出力電圧                                         |

| 3  | OSA             | DAC Aオフセット調整                                      |

| 4  | REFA            | DAC Aのリファレンス                                      |

| 5  | CL              | アクティブロークリア入力。全レジスタをゼロ<br>にリセットします。DAC出力はOVになります。  |

| 6  | CS              | チップセレクト入力                                         |

| 7  | DIN             | シリアルデータ入力                                         |

| 8  | SCLK            | シリアルクロック入力                                        |

| 9  | DGND            | ディジタルグランド                                         |

| 10 | DOUT            | シリアルデータ出力                                         |

| 11 | UPO             | ユーザープログラマブル出力                                     |

| 12 | PDL             | パワーダウンロックアウト。PDLがローの時は、<br>デバイスをパワーダウンすることはできません。 |

| 13 | REFB            | DAC Bのリファレンス                                      |

| 14 | OSB             | DAC Bオフセット調整                                      |

| 15 | OUTB            | DAC B出力電圧                                         |

| 16 | V <sub>DD</sub> | 正電源                                               |

#### 詳細

MAX5158/MAX5159デュアル、10ビット、電圧出力 DACは、3線シリアルインタフェースで容易に構成できます。これらのデバイスは、16ビットデータイン/データ アウトシフトレジスタを含み、各DACには入力レジスタ 及びDACレジスタから構成されるダブルバッファ入力 が備わっています(「ファンクションダイアグラム」参照)。さらに、トリミングした内部抵抗は、出力電圧スイング が最大になる+2V/Vの内部利得を提供します。アンプのオフセット調整ピンは、DAC出力のDCシフトを可能にします。

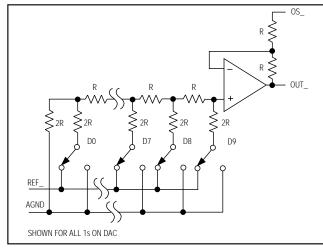

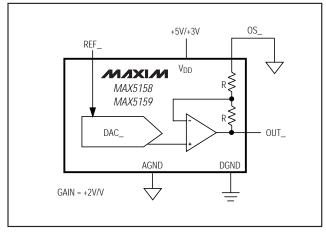

これらのDACは、入力電圧に比例した重み付け電圧を発生する反転R-2Rラダーネットワークを使用しています。各DACには専用のリファレンス入力があり、独立したフルスケール値を提供します。図1に、このDACの概略回路図を示します。

#### リファレンス入力

リファレンス入力は、 $0V \sim (V_{DD} - 1.4V)$ の範囲のAC値及びDC値の両方を受け付けます。出力電圧は次式で計算できます(OS\_ = AGND)。

$V_{OUT} = (V_{REF} \times NB / 1024) \times 2$

図1. DACの概略回路図

ここで、NBはDACのバイナリ入力コードの数値(0~1023)を示し、 $V_{REF}$ はリファレンス電圧を示します。

リファレンス入力インピーダンスの範囲は、18k (16進表示:1558)~数G (入力コードの16進表示:0000)です。リファレンス入力キャパシタンスはコードに依存し、通常15pF(入力コードが全部ゼロの場合)から50pF(フルスケール入力コード)の範囲になります。

#### 出力アンプ

MAX5158/MAX5159の出力アンプは、OS\_をAGNDに接続した時の利得が+2V/Vになる内部抵抗を備えています。これらの抵抗は、利得誤差が最小になるようにトリミングされています。負荷10k を100pFと並列に接続した場合、出力アンプのスルーレートは0.75V/µs(typ)で、8µs以内に1/2LSBにセトリングします。2k 以下の負荷では性能が低下します。

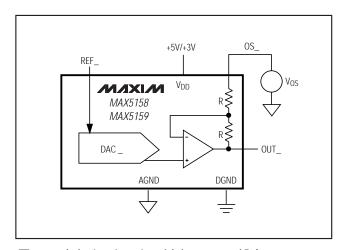

OS\_ピンは、出力段で調整可能なオフセット電圧を得るために使用できます。例えば、1Vのオフセットを得るには、OS\_ピンに-1Vを印可し、1V~(1V+VREF  $\times$  2)の出力範囲を発生します。但し、最大出力電圧仕様の制約は、この場合もDACの出力範囲に適用されます。

#### パワーダウンモード

MAX5158/MAX5159は、公称消費電流を2μAに低減するソフトウェアプログラマブル シャットダウンモードを備えています。これら2つのDACは、プログラミングコマンドで個別又は同時にシャットダウンできます。シャットダウンモードは、指定の入力制御ワードを記述することによって設定します(表1)。シャットダウンモードにすると、リファレンス入力及びアンプ出力がハイインピーダンスになり、シリアルインタフェースはアクティブのまま維持されます。この時入力レジスタ内のデータ

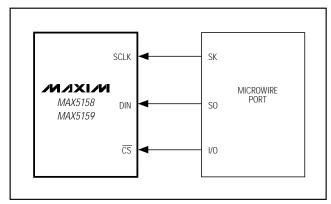

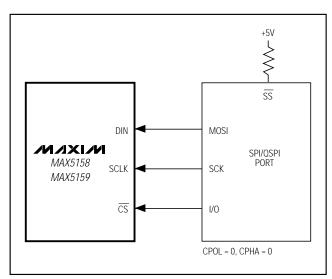

図2. Microwireの接続

は保存されているため、通常モードに切り替えた時には、MAX5158/MAX5159をシャットダウン直前の出力状態に戻すことができます。シャットダウンモードを終了するには、直前の状態を復元するか、又はDACを別の情報で更新します。(シャットダウンモードを終了し)通常動作に切り替えた時は、出力を安定させるために20μs待ってください。

#### シリアルインタフェース

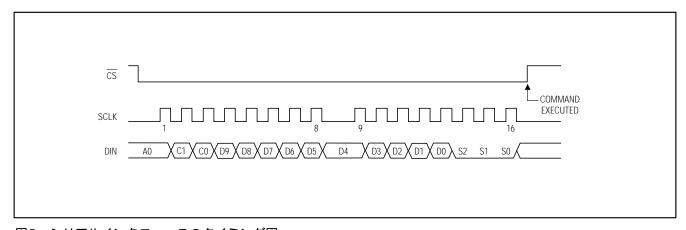

MAX5158/MAX5159 3線シリアルインタフェースは、Microwire(図2)及びSPI/QSPI(図3)シリアルインタフェース標準とコンパチブルです。16ビットのシリアル入力ワードは、図4に示すように1ビットのアドレスビット、2ビットの制御ビット、10ビットのデータ(MSBからLSB)及び3ビットのサブビットで構成されています。MAX5158/MAX5159の応答は、表1に示すようにアドレスビット及び制御ビットで決まります。

表1. シリアルインタフェース プログラミングコマンド

|    | 16ビットシリアルワード |    |                  |       |                                                                  |

|----|--------------|----|------------------|-------|------------------------------------------------------------------|

| Α0 | C1           | C0 | D9D0 (MSB) (LSB) | S2-S0 | 機能                                                               |

| 0  | 0            | 1  | 10ビットのDACデータ     | 000   | 入力レジスタAをロード。DACレジスタは不変。                                          |

| 1  | 0            | 1  | 10ビットのDACデータ     | 000   | 入力レジスタBをロード。DACレジスタは不変。                                          |

| 0  | 1            | 0  | 10ビットのDACデータ     | 000   | 入力レジスタAをロード。全てのDACレジスタを更新。                                       |

| 1  | 1            | 0  | 10ビットのDACデータ     | 000   | 入力レジスタBをロード。全てのDACレジスタを更新。                                       |

| 0  | 1            | 1  | 10ビットのDACデータ     | 000   | シフトレジスタから全てのDACレジスタへロード(両方のDACを新しいデータでスタートアップ)。                  |

| 1  | 0            | 0  | xxxxxxxxx        | 000   | 両方のDACレジスタを各々の入力レジスタで更新(両方のDACを<br>入力レジスタに既に保存されているデータでスタートアップ)。 |

| 1  | 1            | 1  | XXXXXXXXX        | 000   | PDL = 1の場合に両方のDACをシャットダウン。                                       |

| 0  | 0            | 0  | 0 0 1 x xxxxxx   | 000   | DACレジスタAを入力レジスタAで更新(DAC Aを入力レジスタAに既に保存されているデータでスタートアップ)。         |

| 0  | 0            | 0  | 1 0 1 x xxxxxx   | 000   | DACレジスタBを入力レジスタBで更新(DAC Bを入力レジスタBに既に保存されているデータでスタートアップ)。         |

| 0  | 0            | 0  | 1 1 0 x xxxxxx   | 000   | PDL = 1の場合にDAC Aをシャットダウン。                                        |

| 0  | 0            | 0  | 1 1 1 x xxxxxx   | 000   | PDL = 1の場合にDAC Bをシャットダウン。                                        |

| 0  | 0            | 0  | 0 1 0 x xxxxxx   | 000   | UPOがローになります(デフォルト)。                                              |

| 0  | 0            | 0  | 0 1 1 x xxxxxx   | 000   | UPOがハイになります。                                                     |

| 0  | 0            | 0  | 1 0 0 1 xxxxxx   | 000   | モード1、DOUTはSCLKの立上がりエッジでクロック出力。                                   |

| 0  | 0            | 0  | 1 0 0 0 xxxxxx   | 000   | モード0、DOUTはSCLKの立下がりエッジでクロック出力(デフォルト)。                            |

| 0  | 0            | 0  | 0 0 0 x xxxxxx   | 000   | ノーオペレーション(NOP)                                                   |

#### x = 任意

注記: AO、C1及びCO="0"の場合、D9、D8、D7及びD6が制御ビットになります。S2 S0はサブビットで常にゼロです。

図3. SPI/QSPIの接続

| MSBLSB                 |              |                         |          |  |  |  |

|------------------------|--------------|-------------------------|----------|--|--|--|

| 16 Bits of Serial Data |              |                         |          |  |  |  |

| Address Bits           | Control Bits | MSBDataBitsLSB          | Sub Bits |  |  |  |

| A0                     | C1, C0       | D9D0                    | S2-S0    |  |  |  |

| 1 Addi<br>2 Contr      |              | <b>─</b> 10 Data Bits → | 000      |  |  |  |

図4. シリアルデータフォーマット

MAX5158/MAX5159のディジタル入力はダブルバッファ構成になっているため、DACレジスタを更新することなく入力レジスタをロードすることも、入力レジスタからDACレジスタを更新することも、又入力レジスタとDACレジスタを同時に更新することもできます。DACは、これらのアドレスビット及び制御ビットによって個別に動作させることができます。

この期間は、CSがローの状態で、16ビットデータを1つの16ビットワード(QSPI)又は2つの8ビットパケット(SPI、Microwire)として送信します。このアドレス及び制御ビットは、更新するレジスタとシャットダウンモードを終了する時のレジスタの状態を決定します。3ビットのアドレス/制御は、次の事項を決定します。

- 更新するレジスタ

- ・ どのクロックエッジでデータがシリアルデータ出力 (DOUT)からクロック出力されるか

- ・ ユーザプログラマブルロジック出力の状態

- ・ シャットダウン後のデバイス構成

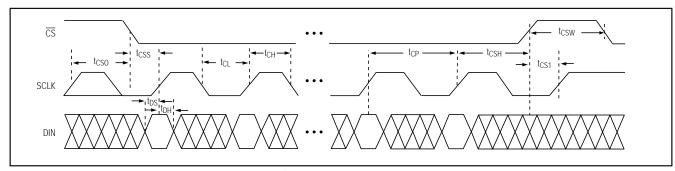

図5のタイミング図は、データがどのように取得されるかを示したものです。データは、CSをローで駆動すると受信できます。これ以外の状態では、インタフェース制御回路がディセーブルされます。CSがローの時は、DINのデータがSCLKの立上りエッジでレジスタ内にクロックされます。CSがハイになると、アドレスビットと制御ビットに従って、入力レジスタ及び(又は)DACレジスタ内にデータがラッチされます。正しい動作を保証できる最大クロック周波数は10MHzです。図6に、シリアルインタフェースのより詳細なタイミングを示します。

図5. シリアルインタフェースのタイミング図

図6. 詳細なシリアルインタフェースタイミング図

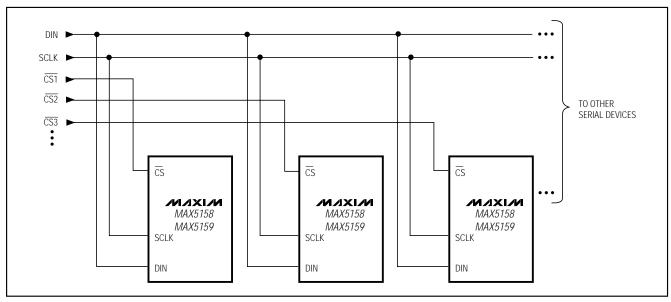

図7. MAX5158/MAX5159をデイジーチェーン構成した場合

図8. 複数のMAX5158/MAX5159でDINラインを共用した場合

表2. ユニポーラコード表(利得 = +2)

| MS |      | ONTEN | TS<br>LSB | ANALOG OUTPUT                                              |

|----|------|-------|-----------|------------------------------------------------------------|

| 11 | 1111 | 1111  | (000)     | $+V_{REF} \left(\frac{1023}{1024}\right) \times 2$         |

| 10 | 0000 | 0001  | (000)     | $+V_{REF} \left(\frac{513}{1024}\right) \times 2$          |

| 10 | 0000 | 0000  | (000)     | $+V_{REF}\left(\frac{512}{1024}\right) \times 2 = V_{REF}$ |

| 01 | 1111 | 1111  | (000)     | $+V_{REF} \left(\frac{511}{1024}\right) \times 2$          |

| 00 | 0000 | 0001  | (000)     | $+V_{REF}\left(\frac{1}{1024}\right)$                      |

| 00 | 0000 | 0000  | (000)     | OV                                                         |

Note: ( ) are for the sub bits.

#### シリアルデータ出力

シリアルデータ出力DOUTは、内部シフトレジスタの出力です。DOUTは、デバイスのデイジーチェーン構成やデータの読み戻しを可能にします。MAX5158/MAX5159は、SCLKの立下リエッジ(モード0)又は立上リエッジ(モード1)でDOUTのデータをシフトするようにプログラムできます。モード0は16クロックサイクルの遅れを提供し、SPI/QSPI及びMicrowireインタフェースとの互換性を維持します。モード1では、出力データの遅れが15.5クロックサイクルになります。パワーアップ時には、デバイスがモード0(標準設定)に設定されます。

#### ユーザプログラマブルロジック出力(UPO)

UPOは、シリアルインタフェースを介した外部デバイスの制御を可能にするため(表1)、必要なマイクロコントローラI/Oピンの数が低減できます。パワーアップ時には、UPOがローになります。

#### パワーダウンロックアウト入力(PDL)

パワーダウンロックアウトピン(PDL)がローの時は、ソフトウェアシャットダウンがディセーブルされます。シャットダウン時にPDLをハイからローに設定すると、シャットダウン前の出力状態でデバイスがウェイクアップされます。このPDLは、デバイスを非同期でウェイクアップするために利用することもできます。

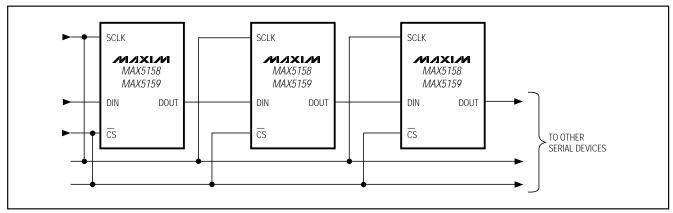

#### デバイスのデイジーチェーン構成

MAX5158/MAX5159のDOUTピンを別のMAX5158/MAX5159のDINピンに接続することにより、複数のMAX5158/MAX5159をデイジーチェーン式に構成できます(図7)。

図9. ユニポーラ出力回路(レイルトゥレイル)

図10. 出力オフセットに対するOS\_の設定

MAX5158/MAX5159のDOUTピンには内部アクティブプルアップが備わっているため、容量性負荷の放電/充電に掛かる時間は、DOUTシンク/ソース機能によって決まります。「Electrical Characteristics」のディジタル出力 $V_{OH}$ 及び $V_{OL}$ の仕様を参照してください。

図8に、いくつかのMAX5158/MAX5159を別方法で接続した場合を示します。この構成では、全デバイスに対して共通のデータバスを使用しているため、データはデイジーチェーンでシフトされません。この場合、各ICに専用のチップセレクト入力(CS)が必要になるため、より多くのI/Oラインが必要になります。

#### アプリケーション情報

#### ユニポーラ出力

図9に、+2V/Vの利得でユニポーラ、レイルトゥレイル 動作用に構成したMAX5158/MAX5159を示します。 この構成のMAX5158は、2.048Vリファレンスで0V ~4.096V出力を発生し(図9)、MAX5159は1.25V

表3. バイポーラコード表

| MS |      | ONTEN | TS<br>LSB | ANALOG OUTPUT                                        |

|----|------|-------|-----------|------------------------------------------------------|

| 11 | 1111 | 1111  | (000)     | $+V_{REF}\left(\frac{511}{512}\right)$               |

| 10 | 0000 | 0001  | (000)     | $+V_{REF}\left(\frac{1}{512}\right)$                 |

| 10 | 0000 | 0000  | (000)     | OV                                                   |

| 01 | 1111 | 1111  | (000)     | $-V_{REF}\left(\frac{1}{512}\right)$                 |

| 00 | 0000 | 0001  | (000)     | $-V_{REF}$ $\left(\frac{511}{512}\right)$            |

| 00 | 0000 | 0000  | (000)     | $-V_{REF} \left( \frac{512}{512} \right) = -V_{REF}$ |

Note: ( ) are for the sub bits.

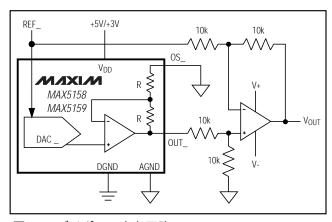

図11. バイポーラ出力回路

リファレンスで0V~2.5Vを発生します。表2に、ユニポーラ出力コードを示します。出力のオフセットは、図10に示すように電圧をOS\_に接続することによって得られます。 $V_{OS}=-1$ Vを印可すると、出力値が1V~(1V +  $V_{RFF}$  x 2)の範囲になります。

#### バイポーラ出力

MAX5158/MAX5159は、図11に示すようにバイポーラ 出力用として構成できます。出力電圧は次式から得ら れます(OS\_ = AGND)。

$V_{OUT} = V_{RFF}[((2 \times NB)/1024) - 1]$

ここで、NBは、DACのバイナリ入力コードの数値を示します。表3に、図11の回路のディジタルコード及びこれに該当する出力電圧を示します。

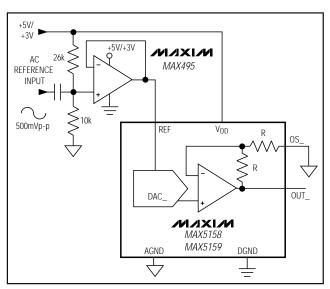

図12. ACリファレンス入力回路

図13. ディジタルキャリブレーション

#### ACリファレンスの使用

リファレンスにAC信号コンポーネントが伴なうアプリケーションでは、MAX5158/MAX5159がリファレンス入力電圧範囲仕様内で乗算能力があります。図12は、正弦波入力をREF\_に適用する方法を示したもので、AC信号はリファレンス入力に送る前にオフセットされます。

#### 高調波歪み及びノイズ

全高調波歪み及びノイズ(THD+N)は、5kHzの1Vp-p 入力スイング、フルスケールで通常-78dB以下です。 -3dB周波数は、「標準動作特性」で示すように両方の デバイスとも300kHzです。

図14. 利得とオフセットのディジタル制御

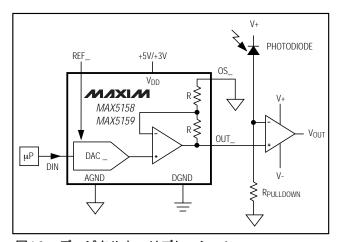

#### ディジタルキャリブレーション及び スレッショルド選択

図13に、ディジタルキャリブレーションアプリケーションに適用したMAX5158/MAX5159を示します。フォトダイオードに光が当たっているとき(オン)、コンパレータがトリップされるまでDACの出力をディジタル的に増加させます。"ハイ"キャリブレーション値は、マイクロプロセッサ( $\mu$ P)に保存されます。次に、光を暗くして(オフ)同じ手順を繰り返し、暗電流キャリブレーションを得ます。この後 $\mu$ Pは、出力電圧がこれら2つのキャリブレーション値の中間になるように、DACをプログラムします。アプリケーションとしては、タコメータ、モーションセンサ、自動リーダ及び液体鮮度分析が挙げられます。

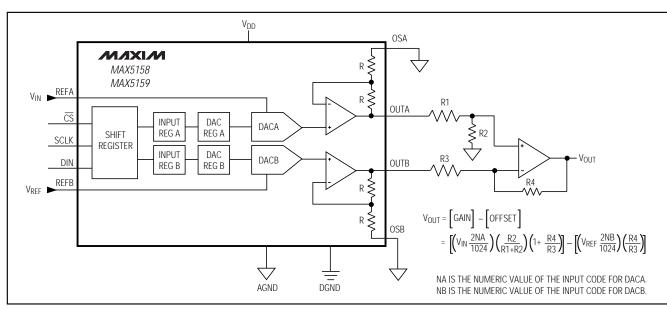

#### 利得及びオフセットのディジタル制御

MAX5158/MAX5159の2つのDACは、トランスデューサ線形化やアナログ圧縮/拡張アプリケーションのような、カーブフィティング非線形機能のオフセット及び利得を制御する目的に使用できます。この場合入力信号は、利得調整DACのリファレンスとして使用し、DACの出力はオフセット調整DACの出力と加算します。各DAC出力の相対重みは、R1、R2、R3及びR4で調整します(図14)。

#### 電源の留意点

パワーアップ時は、入力とDACレジスタがクリア(ゼロのコードに設定)されます。定格性能では、 $V_{REF}$ が少なくとも $V_{DD}$ の1.4V以下になることが必要です。電源は、AGNDへの0.1 $\mu$ Fコンデンサと並列に接続した4.7 $\mu$ Fコンデンサでバイパスしてください。

#### グランド及びレイアウトの留意点

AGNDのディジタル及びAC過渡信号は、出力段におけるノイズ発生の原因になります。AGNDは最高品質のグランドに接続してください。この場合、低インダクタンスグランドプレーンを持つ多層ボードなどの正しいグランド方法を使用します。チャネル間のトレースは、ACクロスカップリングやクロストークを低減できるように配線します。ワイヤーラップ式ボードやソケットの使用は避けてください。ノイズが問題になる場合は、シールドを使用してください。

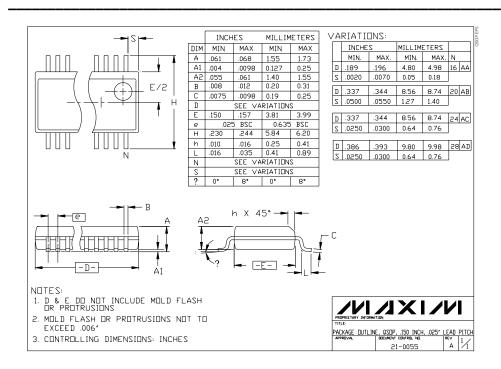

ピン配置

#### 型番(続き) \_\_\_\_\_

| PART       | TEMP. RANGE     | PIN-PACKAGE    |

|------------|-----------------|----------------|

| MAX5159CPE | 0°C to +70°C    | 16 Plastic DIP |

| MAX5159CEE | 0°C to +70°C    | 16 QSOP        |

| MAX5159EPE | -40°C to +85°C  | 16 Plastic DIP |

| MAX5159EEE | -40°C to +85°C  | 16 QSOP        |

| MAX5159MJE | -55°C to +125°C | 16 CERDIP*     |

<sup>\*</sup>Contact factory for availability.

チップ情報 \_\_\_\_\_

TRANSISTOR COUNT: 3053

SUBSTRATE CONNECTED TO AGND

パッケージ \_

## マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600