#

### 低電力シリアル14ビットDAC フォース/センス電圧出力付

概要

MAX5171/MAX5173は、高精度出力アンプ付の低電力 シリアル14ビット電圧出力D/Aコンバータ(DAC)を 省スペースの16ピンQSOPパッケージに内蔵しています。 MAX5171は+5V単一電源で動作し、MAX5173は+3V 単一電源で動作します。出力アンプの反転入力の使用に より、特定の利得設定、リモートセンシング及び大出力 駆動能力が実現できるため、MAX5171/MAX5173は 工業用プロセス制御等の広範囲のアプリケーションに 最適です。いずれのデバイスも消費電流は僅か260µA となっており、シャットダウンモードではさらに1uAに 低減します。さらに、設定可能なパワーアップリセット 機能により、初期出力状態として0V又は中間値に選択 できます。

3線シリアルインタフェースは、SPI™、QSPI™及び MICROWIRE™規格とコンパチブルです。入力レジスタ にDACレジスタが続く形で構成されたダブルバッファ付 入力を備えているため、16ビットシリアルワードに よってDACレジスタを入力レジスタと同時又は個別に 更新できます。その他の特長としては、ソフトウェア 及びハードウェアシャットダウン、シャットダウン ロックアウト、ハードウェアクリアピン、そしてDC 及びオフセットAC信号を許容するリファレンス入力等 が挙げられます。これらのデバイスは、機能性を増す ための設定可能なディジタル出力ピン及びデイジー チェーン接続用のシリアルデータ出力ピンを備えて います。全てのロジック入力はTTL/CMOSコンパチブル で、内部シュミットトリガでバッファされているため、 フォトカプラと直接インタフェースすることが可能です。

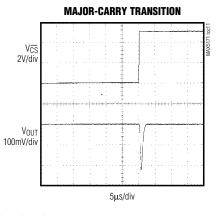

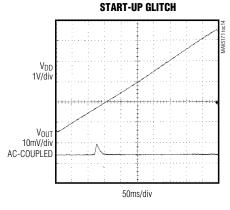

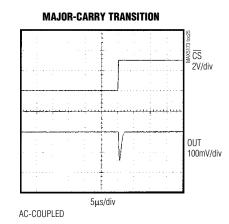

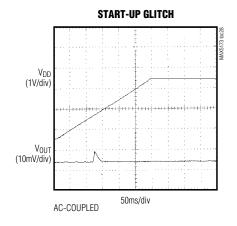

MAX5171/MAX5173は独自の内蔵回路により、パワー アップ時のグリッチを数ミリボルトに抑えて出力電圧 を実質的に「グリッチフリー」に保ちます。

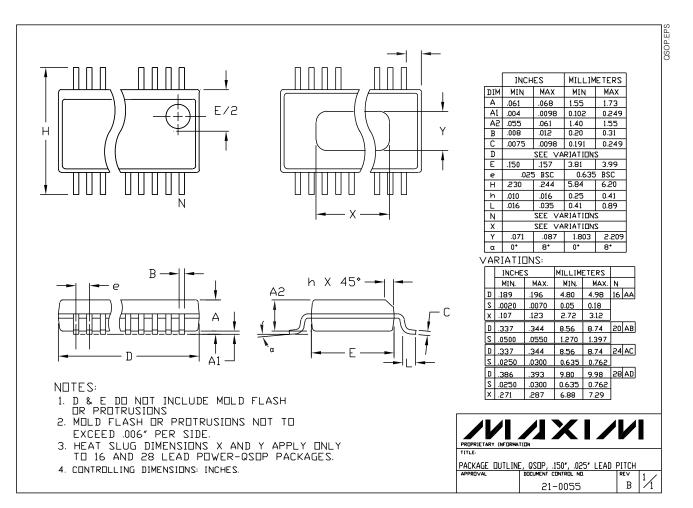

いずれのデバイスも16ピンQSOPパッケージで提供されて おり、温度範囲は拡張工業用(-40 ~+85 )のものが 用意されています。MAX5171/MAX5173は、12ビット MAX5175/MAX5177とピンコンパチブルなアップ グレード製品です。100%ピンコンパチブルの内部 リファレンス付DAC製品については、13ビット MAX5130/MAX5131及び12ビットMAX5120/ MAX5121のデータシートを参照して下さい。

#### アプリケーション

ディジタル設定の4~20mA電流ループ

工業用プロセス制御

ディジタルオフセット及び利得調節

モーションコントロール

自動試験機器(ATE)

リモート工業用制御

uP制御機器

SPI及びQSPIはMotorola Inc.の商標です。

MICROWIREはNational Semiconductor Corp.の商標です。 レイルトゥレイルは日本モトローラの登録商標です。

#### 特長

- ♦ INL: ±1LSB

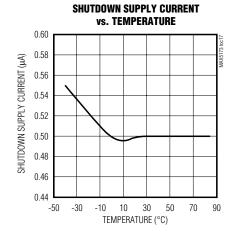

- ◆ シャットダウン電流:1µA

- ◆ パワーアップ時に出力がグリッチフリー

- ◆ 単一電源動作

- +5V(MAX5171)

- +3V(MAX5173)

- ◆ フルスケール出力範囲

- $+2.048V(MAX5173, V_{REF} = +1.25V)$

- $+4.096V(MAX5171, V_{REF} = +2.5V)$

- ◆ レイルトゥレイル<sup>®</sup>出力アンプ

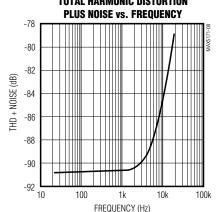

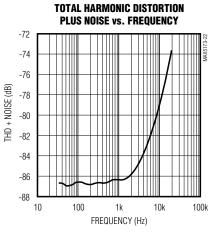

- ◆ 乗算動作における低THD: -80dB

- ◆ 3線シリアルインタフェース: SPI/QSPI/MICROWIREコンパチブル

- ◆ 設定可能なシャットダウンモード及び パワーアップリセット

- ◆ バッファ付出力:5k 1100pF負荷を駆動可能

- ◆ ユーザ設定可能なディジタル出力ピンを使って外部 部品のシリアル制御が可能

- ◆ 12ビットMAX5175/MAX5177のピンコンパチブル アップグレード製品

#### 型番

| PART        | TEMP. RANGE    | PIN-PACKAGE | INL<br>(LSB) |

|-------------|----------------|-------------|--------------|

| MAX5171AEEE | -40°C to +85°C | 16 QSOP     | ±1           |

| MAX5171BEEE | -40°C to +85°C | 16 QSOP     | ±2           |

| MAX5173AEEE | -40°C to +85°C | 16 QSOP     | ±2           |

| MAX5173BEEE | -40°C to +85°C | 16 QSOP     | ±4           |

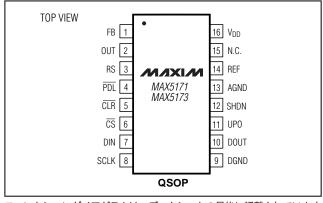

#### ピン配置

ファンクションダイアグラムは、データシートの最後に記載されています。

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to AGND, DGND | 0.3V to +6.0V                    |

|-------------------------------|----------------------------------|

| AGND to DGND                  | 0.3V to +0.3V                    |

| Digital Inputs to DGND        | 0.3V to +6.0V                    |

| DOUT, UPO to DGND             | 0.3V to (V <sub>DD</sub> + 0.3V) |

| FB, OUT, REF to AGND          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| Maximum Current into Any Pin  | 50mA                             |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

|------------------------------------------------|----------------|

| 16-pin QSOP (derate 8mW/°C above +70°C).       | 667mW          |

| Operating Temperature Range                    | 40°C to +85°C  |

| Storage Temperature Range                      | 65°C to +150°C |

| Lead Temperature (soldering, 10sec)            | +300°C         |

|                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—MAX5171**

$(V_{DD} = +5.0V \pm 10\%, V_{REF} = +2.5V, AGND = DGND, FB = OUT, R_L = 5k\Omega, C_L = 100pF$  referenced to ground,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER SYMBOL                      |                   | CONDITIONS                                                                | MIN                   | TYP   | MAX                   | UNITS  |

|---------------------------------------|-------------------|---------------------------------------------------------------------------|-----------------------|-------|-----------------------|--------|

| STATIC PERFORMANCE                    | <u>'</u>          |                                                                           |                       |       |                       |        |

| Resolution                            |                   |                                                                           | 14                    |       |                       | Bits   |

| Interval Nanling with (Nato 1)        | INL               | MAX5171A                                                                  |                       |       | ±1                    | LSB    |

| Integral Nonlinearity (Note 1)        | IINL              | MAX5171B                                                                  |                       |       | ±2                    | LSD    |

| Differential Nonlinearity             | DNL               |                                                                           |                       |       | ±1                    | LSB    |

| Offset Error (Note 2)                 | Vos               |                                                                           |                       |       | ±10                   | mV     |

| Gain Error                            | GE                | R <sub>L</sub> = ∞                                                        |                       | -0.6  | ±4                    | LSB    |

| Gaill Elloi                           | GE                | $R_L = 5k\Omega$                                                          |                       | -1.6  | ±8                    | LOD    |

| Power-Supply Rejection Ratio          | PSRR              |                                                                           |                       | 10    | 120                   | μV/V   |

| Output Noise Voltage                  |                   | f = 100kHz                                                                |                       | 1     |                       | LSBp-p |

| Output Thermal Noise Density          |                   |                                                                           |                       | 50    |                       | nV/√Hz |

| REFERENCE                             |                   |                                                                           |                       |       |                       |        |

| Reference Input Range                 | V <sub>REF</sub>  |                                                                           | 0                     |       | V <sub>DD</sub> - 1.4 | V      |

| Reference Input Resistance            | RREF              |                                                                           | 18                    |       |                       | kΩ     |

| MULTIPLYING-MODE PERFOR               | RMANCE            |                                                                           |                       |       |                       |        |

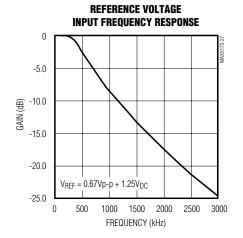

| Reference -3dB Bandwidth              |                   | V <sub>REF</sub> = 0.5Vp-p + 2.5V <sub>DC</sub> , slew-rate limited       |                       | 350   |                       | kHz    |

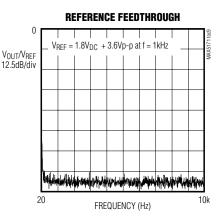

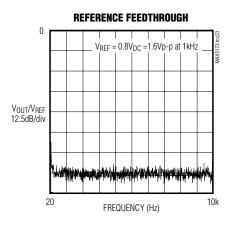

| Reference Feedthrough                 |                   | V <sub>REF</sub> = 3.6Vp-p + 1.8V <sub>DC</sub> , f = 1kHz, code = all 0s |                       | -84   |                       | dB     |

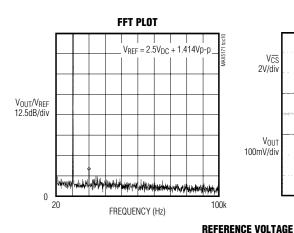

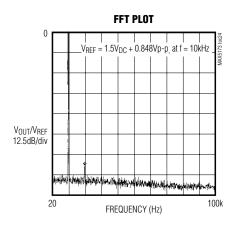

| Signal-to-Noise Plus Distortion Ratio | SINAD             | VREF = 1.4Vp-p + 2.5VDC, f = 10kHz, code = 3FFF hex                       |                       | 84    |                       | dB     |

| DIGITAL INPUTS                        |                   |                                                                           |                       |       |                       |        |

| Input High Voltage                    | VIH               |                                                                           | 3                     |       |                       | V      |

| Input Low Voltage                     | VIL               |                                                                           |                       |       | 0.8                   | V      |

| Input Hysteresis                      | V <sub>H</sub> YS |                                                                           |                       | 200   |                       | mV     |

| Input Leakage Current                 | I <sub>IN</sub>   | V <sub>IN</sub> = 0 or V <sub>DD</sub>                                    |                       | 0.001 | ±1                    | μΑ     |

| Input Capacitance                     | CIN               |                                                                           |                       | 8     |                       | pF     |

| DIGITAL OUTPUTS                       |                   |                                                                           |                       |       |                       |        |

| Output High Voltage                   | VoH               | ISOURCE = 2mA                                                             | V <sub>DD</sub> - 0.5 |       |                       | V      |

| Output Low Voltage                    | VoL               | I <sub>SINK</sub> = 2mA                                                   |                       | 0.13  | 0.4                   | V      |

### **ELECTRICAL CHARACTERISTICS—MAX5171 (continued)**

$(V_{DD}=+5V\pm10\%,\,V_{REF}=+2.5V,\,AGND=DGND,\,FB=OUT,\,R_{L}=5k\Omega,\,C_{L}=100pF$  referenced to ground,  $T_{A}=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ .)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                                                                                                         | MIN  | TYP  | MAX      | UNITS |

|----------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|-------|

| DYNAMIC PERFORMANCE                                |                  |                                                                                                                                    | 1    |      |          | ı     |

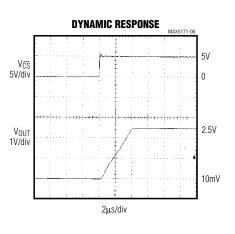

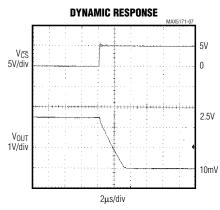

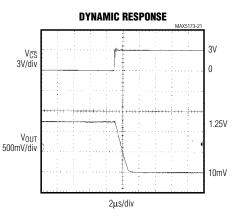

| Voltage Output Slew Rate                           | SR               |                                                                                                                                    |      | 0.6  |          | V/µs  |

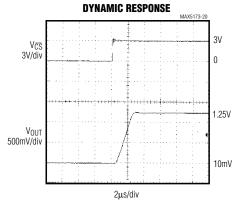

| Output Settling Time                               |                  | To ±0.5LSB, from 10mV to full scale                                                                                                |      | 12   |          | μs    |

| Output Voltage Swing (Note 3)                      |                  |                                                                                                                                    | 0    |      | $V_{DD}$ | V     |

| Current into FB                                    |                  |                                                                                                                                    | -0.1 | 0    | 0.1      | μΑ    |

| Time Required to Exit Shutdown                     |                  |                                                                                                                                    |      | 40   |          | μs    |

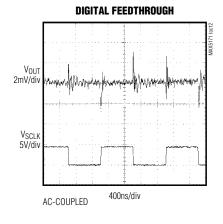

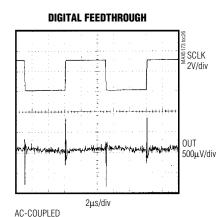

| Digital Feedthrough                                |                  | $\overline{\text{CS}} = \text{V}_{\text{DD}};  \text{f}_{\text{SCLK}} = 100  \text{kHz},  \text{V}_{\text{SCLK}} = 5  \text{Vp-p}$ |      | 1    |          | nV-s  |

| POWER SUPPLIES                                     |                  |                                                                                                                                    | •    |      |          |       |

| Positive Supply Voltage                            | $V_{DD}$         |                                                                                                                                    | 4.5  |      | 5.5      | V     |

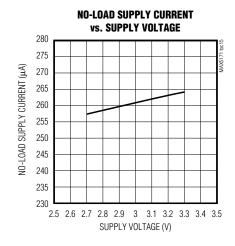

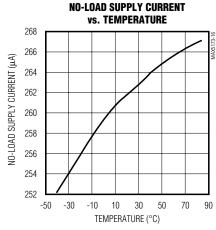

| Power-Supply Current (Note 4)                      | IDD              |                                                                                                                                    |      | 0.26 | 0.35     | mA    |

| Shutdown Current (Note 4)                          |                  |                                                                                                                                    |      | 1    | 10       | μΑ    |

| TIMING CHARACTERISTICS                             |                  |                                                                                                                                    | •    |      |          |       |

| SCLK Clock Period                                  | tcp              |                                                                                                                                    | 100  |      |          | ns    |

| SCLK Pulse Width High                              | tch              |                                                                                                                                    | 40   |      |          | ns    |

| SCLK Pulse Width Low                               | tCL              |                                                                                                                                    | 40   |      |          | ns    |

| CS Fall to SCLK Rise Setup<br>Time                 | tcss             |                                                                                                                                    | 40   |      |          | ns    |

| SCLK Rise to $\overline{\text{CS}}$ Rise Hold Time | tcsh             |                                                                                                                                    | 0    |      |          | ns    |

| SDI Setup Time                                     | t <sub>DS</sub>  |                                                                                                                                    | 40   |      |          | ns    |

| SDI Hold Time                                      | tDH              |                                                                                                                                    | 0    |      |          | ns    |

| SCLK Rise to DOUT Valid<br>Propagation Delay       | t <sub>DO1</sub> | C <sub>LOAD</sub> = 200pF                                                                                                          |      |      | 80       | ns    |

| SCLK Fall to DOUT Valid<br>Propagation Delay       | t <sub>DO2</sub> | C <sub>LOAD</sub> = 200pF                                                                                                          |      |      | 80       | ns    |

| SCLK Rise to CS Fall Delay                         | tcso             |                                                                                                                                    | 10   |      |          | ns    |

| CS Rise to SCLK Rise Hold Time                     | tCS1             |                                                                                                                                    | 40   |      |          | ns    |

| CS Pulse Width High                                | tcsw             |                                                                                                                                    | 100  |      |          | ns    |

|                                                    | 1                | I .                                                                                                                                | 1    |      |          |       |

#### **ELECTRICAL CHARACTERISTICS—MAX5173**

$(V_{DD}=+2.7V \text{ to } +3.6V, V_{REF}=1.25V, \text{AGND}=DGND, FB=OUT, R_L=5k\Omega, C_L=100pF referenced to ground, T_A=T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at T_A=+25°C).}$

| PARAMETER                             | SYMBOL            | BOL CONDITIONS                                                       |                       | TYP   | MAX                   | UNITS  |

|---------------------------------------|-------------------|----------------------------------------------------------------------|-----------------------|-------|-----------------------|--------|

| STATIC PERFORMANCE                    |                   |                                                                      |                       |       |                       |        |

| Resolution                            |                   |                                                                      | 14                    |       |                       | Bits   |

| Integral Nonlinearity (Note 5)        | INL               | MAX5173A                                                             |                       |       | ±2                    | LSB    |

| integral Nonlinearity (Note 5)        | IINL              | MAX5173B                                                             |                       |       | ±4                    | LOD    |

| Differential Nonlinearity             | DNL               |                                                                      |                       |       | ±1                    | LSB    |

| Offset Error (Note 2)                 | Vos               |                                                                      |                       |       | ±10                   | mV     |

| Gain Error                            | GE                | R <sub>L</sub> = ∞                                                   |                       | -0.6  | ±4                    | LSB    |

| dain Endi                             | GL GL             | $R_L = 5k\Omega$                                                     |                       | -1.6  | ±8                    | LOD    |

| Power-Supply Rejection Ratio          | PSRR              |                                                                      |                       | 10    | 120                   | μV/V   |

| Output Noise Voltage                  |                   | f = 100kHz                                                           |                       | 2     |                       | LSBp-p |

| Output Thermal Noise Density          |                   |                                                                      |                       | 50    |                       | nV/√Hz |

| REFERENCE                             |                   |                                                                      |                       |       |                       |        |

| Reference Input Range                 | VREF              |                                                                      | 0                     |       | V <sub>DD</sub> - 1.4 | V      |

| Reference Input Resistance            | R <sub>REF</sub>  |                                                                      | 18                    |       |                       | kΩ     |

| MULTIPLYING-MODE PERFORI              | MANCE             |                                                                      |                       |       |                       |        |

| Reference -3dB Bandwidth              |                   | V <sub>REF</sub> = 0.5Vp-p + 1.25V <sub>DC</sub> , slew-rate limited |                       | 350   |                       | kHz    |

| Reference Feedthrough                 |                   | $V_{REF} = 1.6Vp-p + 0.8V_{DC}$ , $f = 1kHz$ , $code = all 0s$       |                       | -84   |                       | dB     |

| Signal-to-Noise Plus Distortion Ratio | SINAD             | $V_{REF} = 0.9V_{p-p} + 1.25V_{DC}, f = 10kHz,$<br>code = 3 FFF Hex  |                       | 78    |                       | dB     |

| DIGITAL INPUTS                        |                   |                                                                      | 1                     |       |                       |        |

| Input High Voltage                    | VIH               |                                                                      | 2.2                   |       |                       | V      |

| Input Low Voltage                     | VIL               |                                                                      |                       |       | 0.8                   | V      |

| Input Hysteresis                      | V <sub>H</sub> YS |                                                                      |                       | 200   |                       | mV     |

| Input Leakage Current                 | liN               | VIN = 0 or VDD                                                       | -1                    | 0.001 | ±1                    | μΑ     |

| Input Capacitance                     | CIN               |                                                                      |                       | 8     |                       | pF     |

| DIGITAL OUTPUTS                       |                   |                                                                      | •                     |       |                       |        |

| Output High Voltage                   | Vон               | ISOURCE = 2mA                                                        | V <sub>DD</sub> - 0.5 |       |                       | V      |

| Output Low Voltage                    | Vol               | ISINK = 2mA                                                          |                       | 0.13  | 0.4                   | V      |

### **ELECTRICAL CHARACTERISTICS—MAX5173 (continued)**

$(V_{DD} = +2.7V \text{ to } +3.6V, V_{REF} = 1.25V, AGND = DGND, FB = OUT, R_L = 5k\Omega, C_L = 100pF referenced to ground, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25°C).$

| Voltage Output Slew Rate   SR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PARAMETER                      | SYMBOL           | CONDITIONS                          | MIN  | TYP  | MAX      | UNITS |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-------------------------------------|------|------|----------|-------|

| Output Settling Time         To ±0.5LSB, from 10mV to full-scale         12         μs           Output Voltage Swing (Note 3)         0         VDD         V           Current into FB         -0.1         0         0.1         μA           Time Required to Exit Shutdown         -0.1         0         0.1         μA           Digital Feedthrough         \(\bar{CS}\) = VDD, DIN = 50kHz; fsCLK = 100kHz, vsCLK = 100kHz, vsCLK = 3VP-P         1         nV-s           POWER SUPPLIES           Power-Supply Voltage         VDD         2.7         3.6         V           Power-Supply Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         IDD         150         ns           SCLK Place Width High         tcP         150         ns           SCLK Pulse Width Low         tcL         75         ns           SCLK Rise to CS Rise Hold         tcss         0         ns           SDI Setup Time         tcss         0         ns           SDI Hold Time         tbH         CLOAD = 200pF         200         ns           SCLK Ri                                                                                                                                                                    | DYNAMIC PERFORMANCE            | "                |                                     | 1    |      |          |       |

| Output Voltage Swing (Note 3)         0         VpD         V           Current into FB         -0.1         0         0.1         μA           Time Required to Exit Shutdown         40         μs           Digital Feedthrough         CS = VpD, DIN = 50kHz; fsCLK = 100kHz, vsCLK = 3Vp-p         1         nV-s           POWER SUPPLIES           Power-Supply Voltage         VpD         2.7         3.6         V           Power-Supply Current (Note 4)         lpp         0.26         0.35         mA           Shutdown Current (Note 4)         lpp         0.26         0.35         mA           Shutdown Current (Note 4)         lpp         1         10         μA           TIMING CHARACTERISTICS         SCLK Clock Period         tcp         150         ns           SCLK Pulse Width High         tch         75         ns           SCLK Pulse Width Low         tcl         75         ns           SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tp         ns           SCLK Rise to DOUT Valid Propagation Delay         tbo1         CLOAD = 200pF         200         ns           SCLK Rilse to CS Fall Delay <td< td=""><td>Voltage Output Slew Rate</td><td>SR</td><td></td><td></td><td>0.6</td><td></td><td>V/µs</td></td<>                                              | Voltage Output Slew Rate       | SR               |                                     |      | 0.6  |          | V/µs  |

| Current into FB         -0.1         0         0.1         μA           Time Required to Exit Shutdown         CS = VDD, DIN = 50kHz; fSCLK = 100kHz, VSCLK = 100kHz, VSCLK = 3Vp-p         1         nV-s           POWER SUPPLIES           Power-Supply Voltage         VDD         2.7         3.6         V           Power-Supply Current (Note 4)         IDD         0.26         0.35         mA           Shutdown current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         IDD         1         10         μA           TIMING CHARACTERISTICS         SCLK Clock Period         150         ns           SCLK Pulse Width Low         1CL         75         ns           SCLK Pulse Width Low         1CL         75         ns           SCLK Rise Setup Time         1cSs         60         ns           SCLK Rise to CS Rise Hold Time         1bH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         1bO1         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         1cSo         CLOAD = 200pF         200 <t< td=""><td>Output Settling Time</td><td></td><td>To ±0.5LSB, from 10mV to full-scale</td><td></td><td>12</td><td></td><td>μs</td></t<> | Output Settling Time           |                  | To ±0.5LSB, from 10mV to full-scale |      | 12   |          | μs    |

| Time Required to Exit Shutdown   CS = VDD, DIN = 50kHz; fSCLK = 100kHz, VSCLK = 3VP-P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output Voltage Swing (Note 3)  |                  |                                     | 0    |      | $V_{DD}$ | V     |

| Digital Feedthrough   CS = VDD, DIN = 50kHz; fsCLK = 100kHz, VSCLK = 3Vp-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Current into FB                |                  |                                     | -0.1 | 0    | 0.1      | μΑ    |

| VSCLK = 3Vp-p         INV-S           POWER SUPPLIES           Positive Supply Voltage         VDD         2.7         3.6         V           Power-Supply Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         IDD         1         10         μA           TIMING CHARACTERISTICS           SCLK Clock Period         tCP         150         ns           SCLK Pulse Width High         tCH         75         ns           SCLK Pulse Width Low         tCL         75         ns           CS Fall to SCLK Rise Setup Time         tCSS         60         ns           SCLK Rise to CS Rise Hold Time         tDS         60         ns           SDI Setup Time         tDS         60         ns           SDI Hold Time         tDH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tDO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tCS         10         ns           SCLK Rise to CS Fall Delay         tCS0         10         ns           SCLK Rise to CS Fall Delay         tCS0         10                                                                                                                                                                                                           | Time Required to Exit Shutdown |                  |                                     |      | 40   |          | μs    |

| Positive Supply Voltage         VDD         2.7         3.6         V           Power-Supply Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         1         10         μA           TIMING CHARACTERISTICS         5         150         ns           SCLK Clock Period         tcp         150         ns           SCLK Pulse Width High         tch         75         ns           SCLK Pulse Width Low         tcl         75         ns           SCLK Pulse Width Low         tcl         75         ns           SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tbs         60         ns           SDI Hold Time         tbH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbo2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tcso         10         ns         ns           SCLK Rise to SCLK Rise Hold Time         tcso         10         ns         ns                                                                                                                                                                                           | Digital Feedthrough            |                  |                                     |      | 1    |          | nV-s  |

| Power-Supply Current (Note 4)         IDD         0.26         0.35         mA           Shutdown Current (Note 4)         1         10         μA           TIMING CHARACTERISTICS           SCLK Clock Period         tcp         150         ns           SCLK Pulse Width High         tcH         75         ns           SCLK Pulse Width Low         tcL         75         ns           CS Fall to SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tcss         0         ns           SDI Setup Time         tbs         60         ns           SDI Hold Time         tbH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbO2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tcs0         10         ns           SCLK Rise to SCLK Rise Hold Time         tcs1         75         ns                                                                                                                                                                                                                                                                                                                             | POWER SUPPLIES                 |                  | 1                                   | 1    |      |          |       |

| Shutdown Current (Note 4)         1         10         μA           TIMING CHARACTERISTICS           SCLK Clock Period         tcp         150         ns           SCLK Pulse Width High         tcH         75         ns           SCLK Pulse Width Low         tcL         75         ns           CS Fall to SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tcss         0         ns           SDI Setup Time         tbs         60         ns           SDI Hold Time         tbh         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbo1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbo2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tcso         10         ns           SCLK Rise to SCLK Rise Hold Time         tcsi         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                      | Positive Supply Voltage        | $V_{DD}$         |                                     | 2.7  |      | 3.6      | V     |

| TIMING CHARACTERISTICS           SCLK Clock Period         tCP         150         ns           SCLK Pulse Width High         tCH         75         ns           SCLK Pulse Width Low         tCL         75         ns           CS Fall to SCLK Rise Setup Time         tCSS         60         ns           SCLK Rise to CS Rise Hold Time         tCSS         0         ns           SDI Setup Time         tDS         60         ns           SDI Hold Time         tDH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tDO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tDO2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tCS0         10         ns           SCLK Rise to SCLK Rise Hold Time         tCS1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power-Supply Current (Note 4)  | I <sub>DD</sub>  |                                     |      | 0.26 | 0.35     | mA    |

| SCLK Clock Period         tcp         150         ns           SCLK Pulse Width High         tch         75         ns           SCLK Pulse Width Low         tcl         75         ns           CS Fall to SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tcss         0         ns           SDI Setup Time         tbs         60         ns           SDI Hold Time         tbh         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbo1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbo2         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tcso         10         ns           SCLK Rise to CS Fall Delay         tcso         10         ns           SCLK Rise to SCLK Rise Hold Time         tcsi         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                    | Shutdown Current (Note 4)      |                  |                                     |      | 1    | 10       | μΑ    |

| SCLK Pulse Width High         tch         75         ns           SCLK Pulse Width Low         tcl         75         ns           CS Fall to SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tcss         0         ns           SDI Setup Time         tbs         60         ns           SDI Hold Time         tbh         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbo1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbo2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tcso         10         ns           CS Rise to SCLK Rise Hold Time         tcsi         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TIMING CHARACTERISTICS         |                  |                                     | '    |      |          | •     |

| SCLK Pulse Width Low         tCL         75         ns           \$\overline{\text{CS}}\$ Fall to SCLK Rise Setup Time         tCSS         60         ns           \$\text{SCLK Rise to \$\overline{\text{CS}}\$ Rise Hold Time         tCSS         0         ns           \$\text{SDI Setup Time}\$         tDS         60         ns           \$\text{SDI Hold Time}\$         tDH         0         ns           \$\text{SCLK Rise to DOUT Valid Propagation Delay}         tD01         \$\text{CLOAD} = 200pF\$         200         ns           \$\text{SCLK Fall to DOUT Valid Propagation Delay}         tD02         \$\text{CLOAD} = 200pF\$         200         ns           \$\text{SCLK Rise to \$\overline{\text{CS}}\$ Fall Delay         tCS0         10         ns           \$\overline{\text{CS Rise to SCLK Rise Hold Time}}         tCS1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SCLK Clock Period              | tcp              |                                     | 150  |      |          | ns    |

| CS Fall to SCLK Rise Setup Time         tcss         60         ns           SCLK Rise to CS Rise Hold Time         tcss         0         ns           SDI Setup Time         tbs         60         ns           SDI Hold Time         tbh         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tbo1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tbo2         CLOAD = 200pF         200         ns           SCLK Rise to CS Fall Delay         tcso         10         ns           CS Rise to SCLK Rise Hold Time         tcs1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCLK Pulse Width High          | tch              |                                     | 75   |      |          | ns    |

| Time         tCSS         60         ns           SCLK Rise to \overline{CS} Rise Hold Time         tCSS         0         ns           SDI Setup Time         tDS         60         ns           SDI Hold Time         tDH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tD01         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tD02         CLOAD = 200pF         200         ns           SCLK Rise to \overline{CS} Fall Delay         tCSO         10         ns           \overline{CS} Rise to SCLK Rise Hold Time         tCS1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SCLK Pulse Width Low           | tcl              |                                     | 75   |      |          | ns    |

| Time         tCSS         0         ns           SDI Setup Time         tDS         60         ns           SDI Hold Time         tDH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tDO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tDO2         CLOAD = 200pF         200         ns           SCLK Rise to \overline{CS} Fall Delay         tCS0         10         ns           \overline{CS} Rise to SCLK Rise Hold Time         tCS1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                              | tcss             |                                     | 60   |      |          | ns    |

| SDI Hold Time         tDH         0         ns           SCLK Rise to DOUT Valid Propagation Delay         tDO1         CLOAD = 200pF         200         ns           SCLK Fall to DOUT Valid Propagation Delay         tDO2         CLOAD = 200pF         200         ns           SCLK Rise to \overline{CS} Fall Delay         tCS0         10         ns           \overline{CS} Rise to SCLK Rise Hold Time         tCS1         75         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                | tcss             |                                     | 0    |      |          | ns    |

| SCLK Rise to DOUT Valid<br>Propagation Delay $t_{DO1}$ $C_{LOAD} = 200pF$ $200$ nsSCLK Fall to DOUT Valid<br>Propagation Delay $t_{DO2}$ $C_{LOAD} = 200pF$ $200$ nsSCLK Rise to $\overline{CS}$ Fall Delay $t_{CSO}$ $10$ ns $\overline{CS}$ Rise to SCLK Rise Hold Time $t_{CS1}$ $75$ ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SDI Setup Time                 | t <sub>DS</sub>  |                                     | 60   |      |          | ns    |

| Propagation DelaytD01CLOAD = 200pF200nsSCLK Fall to DOUT Valid<br>Propagation DelaytD02 $C_{LOAD} = 200pF$ 200nsSCLK Rise to $\overline{CS}$ Fall DelaytCs010ns $\overline{CS}$ Rise to SCLK Rise Hold TimetCs175ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SDI Hold Time                  | tDH              |                                     | 0    |      |          | ns    |

| Propagation Delay $tDO2$ $CLOAD = 200pF$ $200$ $ns$ SCLK Rise to $\overline{CS}$ Fall Delay $tCS0$ $10$ $ns$ $\overline{CS}$ Rise to SCLK Rise Hold Time $tCS1$ $75$ $ns$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                | tDO1             | C <sub>LOAD</sub> = 200pF           |      |      | 200      | ns    |

| CS Rise to SCLK Rise Hold Time tCS1 75 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                | t <sub>DO2</sub> | C <sub>LOAD</sub> = 200pF           |      |      | 200      | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCLK Rise to CS Fall Delay     | tcso             |                                     | 10   |      |          | ns    |

| CS Pulse Width High tosw 150 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS Rise to SCLK Rise Hold Time | tCS1             |                                     | 75   |      |          | ns    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS Pulse Width High            | tcsw             |                                     | 150  |      |          | ns    |

Note 1: INL guaranteed between codes 64 and 16383.

Note 2: Offset is measured at the code that comes closest to 10mV.

Note 3: Accuracy is better than 1.0 LSB for VouT = 10mV to Vpp - 180mV. Guaranteed by PSR test on end points.

**Note 4:**  $R_L$  = open and digital inputs are either  $V_{DD}$  or DGND.

Note 5: INL guaranteed between codes 128 and 16383.

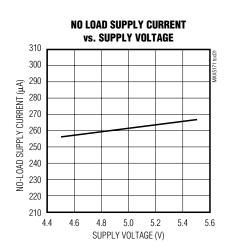

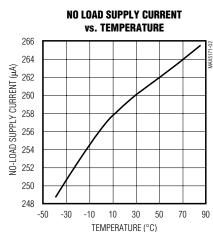

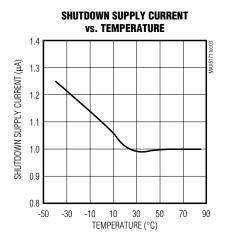

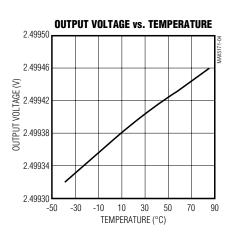

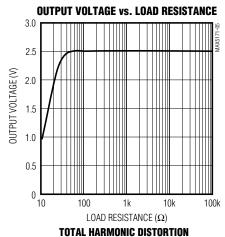

#### 標準動作特性

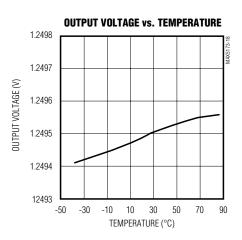

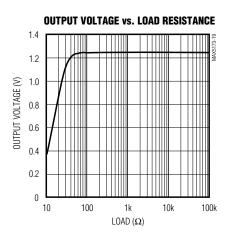

$(\text{MAX5171: V}_{\text{DD}} = +5\text{V}, \text{V}_{\text{REF}} = 2.5\text{V}; \text{MAX5173: V}_{\text{DD}} = +3\text{V}, \text{V}_{\text{REF}} = 1.25\text{V}; \text{C}_{\text{L}} = 100\text{pF}, \text{FB} = \text{OUT}, \text{code} = 3\text{FFF hex}, \text{T}_{\text{A}} = +25^{\circ}\text{C}, \text{unless otherwise noted.})$  MAX5171

### 標準動作特性(続き)

$(MAX5171: V_{DD} = +5V, V_{REF} = 2.5V; MAX5173: V_{DD} = +3V, V_{REF} = 1.25V; C_{L} = 100pF, FB = OUT, code = 3FFF hex, T_{A} = +25^{\circ}C, unless otherwise noted.)$

### **MAX5171**

#### **INPUT FREQUENCY RESPONSE** 0 -5 GAIN (dB) -10 -15 -20 $V_{REF} = 0.67V_{p-p} + 2.5V_{DC}$ -25 0 500 1000 1500 2000 2500 3000 FREQUENCY (kHz)

#### **MAX5173**

標準動作特性(続き)\_

(MAX5171:  $V_{DD}$  = +5V,  $V_{REF}$  = 2.5V; MAX5173:  $V_{DD}$  = +3V,  $V_{REF}$  = 1.25V;  $C_L$  = 100pF, FB = OUT, code = 3FFF hex,  $T_A$  = +25°C, unless otherwise noted.)

### **MAX5173**

### 標準動作特性(続き)\_

(MAX5171:  $V_{DD}$  = +5V,  $V_{REF}$  = 2.5V; MAX5173:  $V_{DD}$  = +3V,  $V_{REF}$  = 1.25V;  $C_L$  = 100pF, FB = OUT, code = 3FFF hex,  $T_A$  = +25°C, unless otherwise noted.)

### 端子説明

| 端子 | 名称              | 機能                                                                                                       |

|----|-----------------|----------------------------------------------------------------------------------------------------------|

| 1  | FB              | フィードバック入力                                                                                                |

| 2  | OUT             | 出力電圧。シャットダウン中はハイインピーダンスです。出力電圧はV <sub>DD</sub> に制限されています。                                                |

| 3  | RS              | リセットモード選択(ディジタル入力)。V <sub>DD</sub> に接続するとミッドスケールがリセット出力電圧になります。<br>DGNDに接続すると0Vがリセット出力電圧になります。           |

| 4  | PDL             | パワーダウンロックアウト(ディジタル入力)。V <sub>DD</sub> に接続するとシャットダウンが許容されます。DGNDに接続すると、ソフトウェア及びハードウェアのシャットダウンがディセーブルされます。 |

| 5  | CLR             | DACクリア(ディジタル入力)。DACをRSで設定される出力状態にクリアします。                                                                 |

| 6  | CS              | チップセレクト入力(ディジタル入力)                                                                                       |

| 7  | DIN             | シリアルデータ入力(ディジタル入力)。データはSCLKの立上がりエッジで同期入力されます。                                                            |

| 8  | SCLK            | シリアルクロック入力(ディジタル入力)                                                                                      |

| 9  | DGND            | ディジタルグランド                                                                                                |

| 10 | DOUT            | シリアルデータ出力                                                                                                |

| 11 | UPO             | ユーザ設定出力。状態はシリアル入力によって設定されます。                                                                             |

| 12 | SHDN            | シャットダウン(ディジタル入力)。 $\overline{PDL} = V_{DD}$ の時にSHDNをハイにすると、チップはシャットダウン状態になります。最大シャットダウン電流は10 $\mu$ Aです。  |

| 13 | AGND            | アナロググランド                                                                                                 |

| 14 | REF             | リファレンス入力。最大V <sub>REF</sub> はV <sub>DD</sub> - 1.4Vです。                                                   |

| 15 | N.C.            | 無接続                                                                                                      |

| 16 | V <sub>DD</sub> | 正電源。4.7µFコンデンサと0.1µFコンデンサを並列にしたものでAGNDにバイパスして下さい。                                                        |

詳細

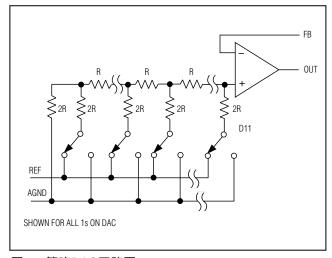

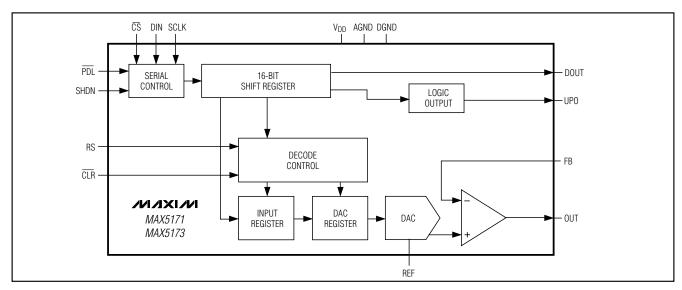

MAX5171/MAX5173 14ビットシリアル電圧出力 DACは、3線シリアルインタフェースで動作します。これらのデバイスは16ビットシフトレジスタを含み、入力レジスタ及びDACレジスタからなるダブルバッファ付入力を備えています(「ファンクションダイアグラム」を参照)。さらに、出力アンプの負端子が利用可能です。これらのDACは、ディジタル入力コードに比例する重み付き出力電圧を生成する反転R-2Rラダーネットワーク(図1)を使用して設計されています。

#### リファレンス入力

リファレンス入力は、 $0 \sim (V_{DD}-1.4V)$ の範囲のAC及びDC値を受け付けます。出力電圧は次式で表されます。

$$V_{OUT} = \frac{V_{REF} \cdot N \cdot Gain}{16384}$$

ここで、NはMAX5171/MAX5173の入力コードの数値  $(0 \sim 16383)$ 、 $V_{REF}$ はリファレンス電圧、「Gain」は外部で設定された電圧利得です。最大出力電圧は、 $V_{DD}$ です。REFピンの入力抵抗は最小値が18kで、コードに依存します。

#### 出力アンプ

MAX5171/MAX5173のDAC出力は、標準スルーレートが 0.6V/µsの内部高精度アンプでバッファされています。 出力アンプの反転入力へのアクセスが可能であるため、出力利得設定及び信号調節に融通が利きます(「アプリケーション情報」を参照)。

出力アンプは、5k と100pFの並列負荷の時、フルスケール遷移から $12\mu$ s以内に $\pm 0.5LSB$ までセトリングします。負荷が2k 以下になると性能が劣化します。

#### シャットダウンモード

MAX5171/MAX5173は、ソフトウェア及びハードウェア・プログラマブルのシャットダウンモードを備えています。このモードでは標準消費電流が1µAに低減します。シャットダウンモードに入るには、表1に示すように該当する入力制御ワードを書き込むか、あるいはハードウェアシャットダウンを使って下さい。シャットダウンモード時のリファレンス入力及びアンプ出力はハイインピーダンスになり、シリアルインタフェースはアクティブ状態に留まります。入力レジスタのデータはセーブされるため、MAX5171/MAX5173は通常動作状態に戻った時に、シャットダウン以前の出力状態を呼び戻すことができます。シャットダウンモードを解除するには、DACレジスタにシフトレジスタのデータを再ロードするか、入力レジスタ及びDACレジスタに同時にロードするか、あるいはPDLをトグルして下さい。

図1. 簡略DAC回路図

シャットダウンモードから戻った時は、リファレンスが落ち着くまで40us待って下さい。

#### パワーダウンロックアウト

パワーダウンロックアウトは、ソフトウェア/ハードウェアシャットダウンモードをディセーブルします。 PDLがハイからローに遷移すると、デバイスのシャットダウンが解除され、この時出力は、以前の状態に戻ります。

#### シャットダウン

PDLがハイの時にSHDNをハイに引き上げると、MAX5171/MAX5173はシャットダウンします。SHDNをローに引き下げてもデバイスは通常動作に戻りません。シャットダウンを解除するには、PDLのハイからローへの遷移、あるいはシリアルインタフェースを通じた適切なコマンドが必要です(コマンドについては表1を参照)。

#### シリアルインタフェース

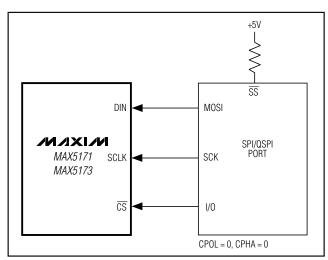

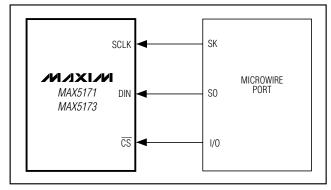

MAX5171/MAX5173の3線シリアルインタフェースは、SPI/QSPI(図2)及びMICROWIRE(図3)インタフェース 規格とコンパチブルです。16ビットのシリアル入力 ワードは、2つの制御ビットと14個のデータビット (MSBからLSBへ)からなっています。

制御ビットは、表1にしたがってMAX5171/MAX5173 の動作を決定します。MAX5171/MAX5173のディジタル入力はダブルバッファ付であるため、ユーザは以下の作業を行うことができます。

- DACレジスタを更新することなく入力レジスタに ロードすること

- 入力レジスタからのデータでDACレジスタを更新 すること

- 入力及びDACレジスタを同時に更新すること

図2. SPI/QSPIインタフェースの接続

図3. MICROWIREインタフェースの接続

でSがローの状態の時に、MAX5171/MAX5173は送られてきた1つの16ビットパケットあるいは2つの8ビットパケットを受け付けます。MAX5171/MAX5173は下記の構成が設定可能になっています。

- どのクロックエッジでDOUTが同期出力されるか

- ユーザ設定可能なロジック出力の状態

- リセット状態の構成

表1に、これらの設定に必要なコマンドが記載されています。

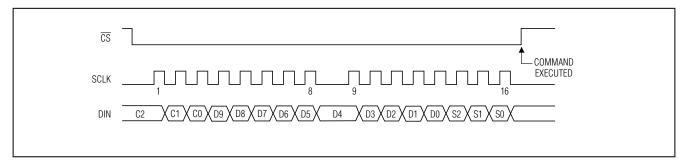

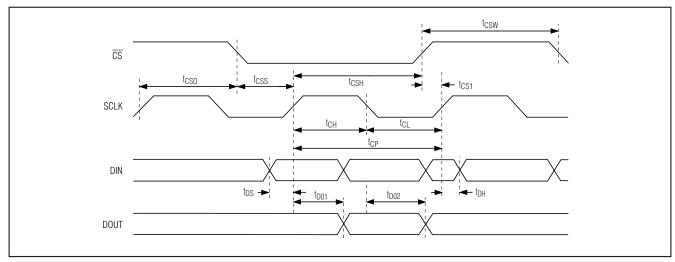

図4の一般タイミング図に、MAX5171/MAX5173 データ収集の方法が図解されています。 $\overline{CS}$ はシリアルクロック(SCLK)の立上がりエッジよりも少なくとも $t_{CSS}$ 前にローになることが必要です。 $\overline{CS}$ がローの状態で、データがSCLKの立上がりエッジでレジスタに同期入力されます。適正動作が保証された最大シリアルクロック周波数は、MAX5171が10MHz、MAX5173が6MHzです。図5に、シリアルインタフェースの詳細タイミング図を示します。

#### シリアルデータ出力(DOUT)

シリアルデータ出力(DOUT)は、内部シフトレジスタの出力です。これにより、複数デバイスのデイジーチェーン接続及びデータの読み戻しが可能です(アプリケーション情報」を参照)。スタートアップ時のデフォルト状態では、データはシリアルクロックの立上がリエッジ(モードの)でDOUTからシフトアウトされるため、遅れが16クロックサイクルとなり、SPI、QSPI及びMICROWIREコンパチビリティが確保されます。しかし、デバイスがモード1に設定されていると、出力はDINから16.5クロックサイクル遅れ、シリアルクロックの立上がリエッジで同期出力されます。シャットダウン中、DOUTはシャットダウン前の最後のディジタル状態を保持します。

| - 表1. シリアルインタフェースのブログラ | ゚゙ミングコマンド |

|------------------------|-----------|

|------------------------|-----------|

|    | 16-BIT SE | RIAL WORD           | FUNCTION                                                                                                   |

|----|-----------|---------------------|------------------------------------------------------------------------------------------------------------|

| C1 | C0        | D13D0               | FUNCTION                                                                                                   |

| 0  | 0         | 14-bit DAC data     | Load input register; DAC registers are unchanged.                                                          |

| 0  | 1         | 14-bit DAC data     | Load input register; DAC registers are updated (start up DAC with new data).                               |

| 1  | 0         | X X X XXX XXXX XXXX | Update DAC register from input register (start up DAC with data previously stored in the input registers). |

| 1  | 1         | 0 0 x xxx xxxx xxxx | No operation (NOP).                                                                                        |

| 1  | 1         | 0 1 x xxx xxxx xxxx | Shut down DAC (provided PDL = 1).                                                                          |

| 1  | 1         | 1 0 0 xxx xxxx xxxx | UPO goes low (default).                                                                                    |

| 1  | 1         | 1 0 1 xxx xxxx xxxx | UPO goes high.                                                                                             |

| 1  | 1         | 1 1 0 xxx xxxx xxxx | Mode 1, DOUT clocked out on SCLK's rising edge.                                                            |

| 1  | 1         | 1 1 1 xxx xxxx xxxx | Mode 0, DOUT clocked out on SCLK's falling edge (default).                                                 |

図4. シリアルインタフェースのタイミング

図5. シリアルインタフェースの詳細タイミング

#### ユーザ設定可能な出力(UPO)

UPO機能により、シリアルインタフェースを通じて外部デバイスを制御できます。このため、必要なマイクロコントローラI/Oポート数が減らせます。パワーダウン中、この出力は、シャットダウン前の最後のディジタル状態を保持します。CLRがローに引き下げられると、UPOはデフォルト状態にリセットされます。UPOを制御するための具体的なコマンドについては、表1を参照して下さい。

#### リセット(RS)及びクリア(CLR)

MAX5171/MAX5173は、出力電圧をリセットする クリアピンを備えています。RST = DGNDの時、 $\overline{CLR}$  は出力電圧を最小電圧(オフセットがない場合は0)に リセットします。RST =  $V_{DD}$ の時、 $\overline{CLR}$ は出力電圧を ミッドスケールにリセットします。いずれの場合も、  $\overline{CLR}$ はUPOを設定されたデフォルト状態にリセットします。

#### アプリケーション情報

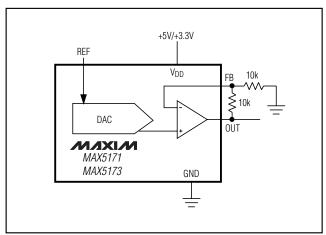

#### ユニポーラ出力

図6に、MAX5171/MAX5173を利得+2V/Vのユニポーラ、レイルトゥレイル動作にセットアップした例を示します。表2に、ユニポーラ出力電圧のコードを示します。出力電圧は $V_{DD}$ に制限されています。

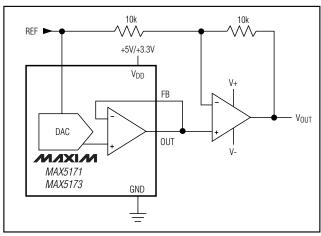

#### バイポーラ出力

図7は、MAX5171/MAX5173をバイポーラ動作に設定した場合です。出力電圧は次式によって与えられます (FB = OUT)。

$$V_{OUT} = V_{REF} \left( \frac{2 \cdot N}{16384} - 1 \right)$$

ここで、NはDACのバイナリ入力コードの数値、V<sub>REF</sub>は外部リファレンスの電圧です。表3に、図7の回路のディジタルコード及び対応する出力電圧を示します。

図6. ユニポーラ出力回路(レイルトゥレイル)

### 表2. ユニポーラコード表(図6の回路)

| DAC CONTE         | NTS<br>LSB | ANALOG OUTPUT                      |

|-------------------|------------|------------------------------------|

| 11 1111 1111      | 1111       | 2 • V <sub>REF</sub> (16383/16384) |

| 10 0000 0000      | 0001       | 2 • V <sub>REF</sub> (8193/16384)  |

| 10 0000 0000      | 0000       | 2 • V <sub>REF</sub> (8192/16384)  |

| 01 1111 1111      | 1111       | 2 • V <sub>REF</sub> (8191/16384)  |

| 00 0000 0000 0001 |            | 2 • V <sub>REF</sub> (1/16384)     |

| 00 0000 0000      | 0000       | 0                                  |

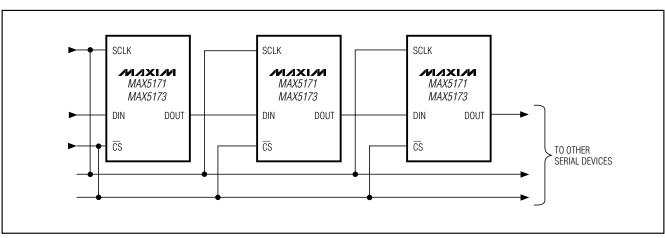

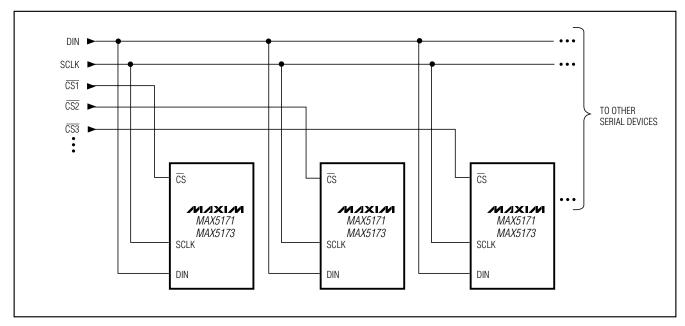

#### デバイスのデイジーチェーン接続

シリアルデータ出力ピン(DOUT)を使用することによって、複数のMAX5171/MAX5173をまとめてデイジーチェーン接続できます(図8)。この方式の長所は、僅か2本のラインで、ライン上の全てのDACを制御できることにあります。但し、DACを設定するためにn個のコマンドが必要であるという短所があります。図9に、1本の共通なDIN信号ラインを共有するいくつかのMAX5171/MAX5173を示します。この構成においては、データバスは全てのデバイスの共通です。しかし、この構成は各デバイスが専用のCSラインを必要とするため、必要なI/Oラインの数が多くなります。この構成の長所は、いずれのDACの設定にも僅か1つのコマンドしか必要としないことです。

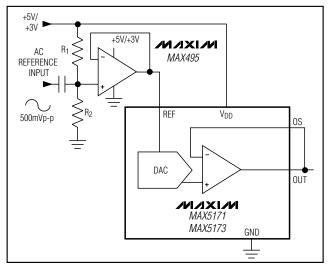

#### ACリファレンスの使用

MAX5171/MAX5173は、リファレンス電圧が0~ $(V_{DD}-1.4V)$ の範囲に収まっている限り、AC成分を含むリファレンスを許容します。図10は、REFにサイン波入力を印加する技法を示しています。リファレンス電圧はAGNDよりも上に維持される必要があります。

図7. バイポーラ出力回路

#### 表3. バイポーラコード表(図7の回路)

| DAC CONTEN     | TS<br>LSB | ANALOG OUTPUT                             |

|----------------|-----------|-------------------------------------------|

| 11 1111 1111 1 | 111       | +V <sub>REF</sub> [(2 • 16383/16384) - 1] |

| 10 0000 0000 0 | 001       | +V <sub>REF</sub> [(2 • 8193/16384) - 1]  |

| 10 0000 0000 0 | 000       | +V <sub>REF</sub> [(2 • 8192/16384) - 1]  |

| 01 1111 1111 1 | 111       | +V <sub>REF</sub> [(2 • 8191/16384) - 1]  |

| 00 0000 0000 0 | 001       | +V <sub>REF</sub> [(2 • 1/16384) - 1]     |

| 00 0000 0000 0 | 000       | -V <sub>REF</sub>                         |

#### ディジタルプログラマブル電流ソース

図11の回路を使用すると、オペアンプのフィードバックループ内のNPNトランジスタ(2N3904等)がディジタルでプログラムできる一方向性電流ソースになります。出力電流は、次式で計算されます。

$$I_{OUT} = \frac{V_{REF} \cdot N}{R \cdot 16384}$$

ここで、NはDACのバイナリ入力コードの数値、Rは 図11に示されている検出抵抗です。

#### 電源及びレイアウト上の考慮

ワイヤラップ基板はお勧めできません。最高のシステム性能を得るには、アナログとディジタルのグランドプレーンが別々になったプリント基板を使用して下さい。2つのグランドプレーンは、低インピーダンス電源ソースのところで一緒にまとめて接続して下さい。DGNDとAGNDピンはICのところで一緒にまとめて接続して下さい。最善のグランドを得るためには、DACのDGNDピンとAGNDピンを一緒にまとめて接続し、それを今度はシステムアナロググランドプレーンに接続して下さい。DACのDGNDがシステムディジタルグランドに接続されていると、ディジタルノイズがDACのアナログ部分に漏れる可能性があります。

4.7µFコンデンサと0.1µFコンデンサを並列にしたもので、電源をAGNDにバイパスして下さい。リードインダクタンスを小さくするために、リードはできるだけ短くして下さい。ノイズが問題になる場合は、シールド及び/又はフェライトビーズを使用して分離を改善して下さい。

利得ドリフト及びINLとDNL性能を維持するには、DACリファレンス入力ピンのところでリファレンス出力インピーダンスをできるだけ低くすることが非常に重要です。REFピンの直列抵抗が0.1 を超えるとINLが劣化します。AGNDピンについても同様の配慮が必要です。

図8. 複数のMAX5171/MAX5173デバイスのデイジーチェーン接続

図9. 複数のMAX5171/MAX5173が1つの共通のDINとSCLKラインを共有する場合

+5V/+3.3V REF  $V_{DD}$ MIXIM  $V_L$ MAX5171 MAX5173 I<sub>OUT</sub> DAC OUT 2N3904 FB

図10. ACリファレンス入力回路

図11. ディジタルプログラマブル電流ソース

### ファンクションダイアグラム

チップ情報

TRANSISTOR COUNT: 3457

パッケージ \_\_\_\_\_

**( 販売代理店**

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600