概要

MAX5222は、小型8ピンSOT23パッケージに2つの 8ビット、バッファ付電圧出力ディジタルアナログコン バータ(DAC A及びDAC B)を含んでいます。いずれの DAC出力も、グランド及びV<sub>DD</sub>の100mV以内まで1mA の電流のソース/シンクが可能です。MAX5222は +2.7V~+5.5V単一電源で動作します。

本素子が使用している3線シリアルインタフェースは 25MHzまでのクロックレートで動作し、SPI™、QSPI™ 及びMICROWIRE™インタフェース規格とコンパチブル です。シリアル入力シフトレジスタは16ビット長で、 DAC入力データの8ビットとDAC選択及びシャットダウン 制御用の8ビットからなっています。DACレジスタは CSの正エッジで互いに独立して、あるいは平行して ロードすることができます。

MAX5222は超低消費電力で超小型8ピンSOT23パッ ケージであるため、ポータブル及びバッテリ駆動アプリ ケーションに最適です。消費電流は1mA以下で、 シャットダウンモードにおいては1µA以下になります。 また、シャットダウン中はリファレンス入力をREFピン から切断することにより、システムの全消費電力をさら に低減しています。

#### アプリケーション

ディジタル利得及びオフセット調整

設定可能な電流ソース

設定可能な電圧ソース

パワーアンプのバイアス制御

VCO同調

MIXIM

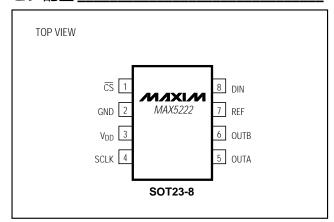

#### ピン配置

SPI及びQSPIはMotorola Inc.の商標です。 MICROWIREはNational Semiconductor Corp.の商標です。 特長

◆ 単一電源動作:+2.7V~+5.5V

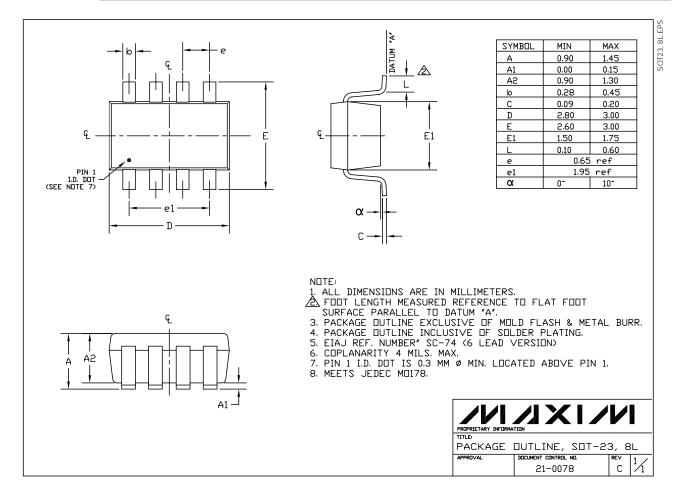

◆ パッケージ:超小型8ピンSOT23(3mm x 3mm)

◆ デュアルバッファ付電圧出力

◆ 低消費電力

動作電流: 0.4mA

シャットダウン電流: < 1μA

- ◆ 設定可能なシャットダウンモード

- ◆ 25MHz、3線シリアルインタフェース

- ◆ SPI、QSPI及びMICROWIREコンパチブル

#### 型番

| PART         | TEMP. RANGE    | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX5222EKA-T | -40°C to +85°C | 8 SOT23-8   |

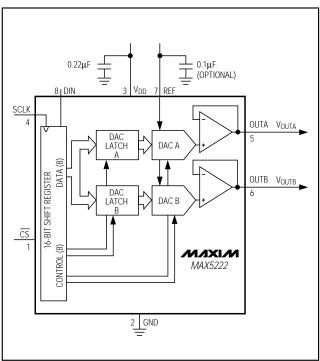

#### ファンクションダイアグラム

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

|  | All Other Pins to GND (Note 1)0.3V to (V <sub>DD</sub> + 0.3V)<br>Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Operating Temperature Range40°C to +85°C Junction Temperature+150°C Storage Temperature Range65°C to +150°C Lead Temperature (soldering, 10s)+300°C |

|--|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|--|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

Note 1: The outputs may be shorted to V<sub>DD</sub> or GND if the package power dissipation is not exceeded. Typical short-circuit current to GND is 70mA

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7V \text{ to } +5.5V, \text{ REF} = V_{DD}, \text{ T}_A = \text{T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted. Typical values are at T}_A = +25^{\circ}\text{C.})$

| PARAMETER                                  | SYMBOL           | CONDITIONS                                      | MIN                   | TYP  | MAX                   | UNITS |

|--------------------------------------------|------------------|-------------------------------------------------|-----------------------|------|-----------------------|-------|

| STATIC PERFORMANCE                         |                  |                                                 | '                     |      |                       |       |

| Resolution                                 | N                |                                                 | 8                     |      |                       | Bits  |

| Differential Nonlinearity                  | DNL              | Guaranteed monotonic                            |                       | ±0.3 | ±1                    | LSB   |

| Integral Nonlinearity                      | INL              | (Note 2)                                        |                       | ±0.3 | ±1                    | LSB   |

| Total Unadjusted Error                     | TUE              | (Note 2)                                        |                       | ±1   |                       | LSB   |

| Zero-Code Offset                           | Vzs              |                                                 |                       | 10   |                       | mV    |

| Zero-Code Temperature<br>Coefficient       | TCvzs            |                                                 |                       | 100  |                       | μV/°C |

|                                            | 2000             | $4.5V \le V_{DD} \le 5.5V$ , $V_{REF} = 4.096V$ |                       | 0.15 |                       |       |

| Power-Supply Rejection Ratio               | PSRR             | $2.7V \le V_{DD} \le 3.6V$ , $V_{REF} = 2.4V$   |                       | 0.5  |                       | mV/V  |

| REFERENCE INPUT                            | 1                |                                                 |                       |      |                       |       |

| Reference Input Voltage Range              |                  |                                                 | GND                   |      | $V_{DD}$              | V     |

| Reference Input Capacitance                |                  |                                                 |                       | 25   |                       | pF    |

| Reference Input Resistance                 | R <sub>REF</sub> | (Note 3)                                        | 8                     | 16   |                       | kΩ    |

| Reference Input Resistance (Shutdown Mode) |                  |                                                 |                       | 2    |                       | ΜΩ    |

| DAC OUTPUTS                                | 1                |                                                 |                       |      |                       |       |

| Output Voltage Range                       |                  |                                                 | 0                     |      | REF                   | V     |

| Capacitive Load at OUT_                    |                  |                                                 |                       |      | 100                   | pF    |

| Output Resistance                          |                  |                                                 |                       | 50   |                       | Ω     |

| DIGITAL INPUTS                             | •                | •                                               |                       |      |                       |       |

| Input High Voltage                         | VIH              |                                                 | 0.7 x V <sub>DD</sub> |      |                       | V     |

| Input Low Voltage                          | VIL              |                                                 |                       |      | 0.3 x V <sub>DD</sub> | V     |

| Input Current                              | I <sub>IN</sub>  | $V_{IN} = 0$ or $V_{DD}$                        |                       | 0.1  | ±10                   | μΑ    |

| Input Capacitance                          | CIN              | (Note 4)                                        |                       |      | 10                    | pF    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 V \text{ to } +5.5 V, \text{ REF} = V_{DD}, \text{ T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted. Typical values are at } \text{T}_{A} = +25 ^{\circ}\text{C.})$

| PARAMETER                         | SYMBOL          | C                                 | ONDITIONS              | MIN      | TYP  | MAX | UNITS |

|-----------------------------------|-----------------|-----------------------------------|------------------------|----------|------|-----|-------|

| DYNAMIC PERFORMANCE               | •               |                                   |                        |          |      |     |       |

| Voltage-Output Slew Rate          | SR              | C <sub>L</sub> = 100pF            |                        |          | 1    |     | V/µs  |

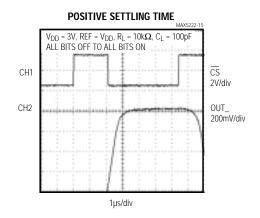

| Voltage-Output Settling Time      |                 | To $\pm \frac{1}{2}LSB$ , $C_L =$ | 100pF                  |          | 10   |     | μs    |

| Digital Feedthrough and Crosstalk |                 | All 0s to all 1s                  |                        |          | 0.25 |     | nV-s  |

| POWER SUPPLY                      | 1               |                                   |                        | <u>'</u> |      |     |       |

| Supply Voltage Range              | V <sub>DD</sub> |                                   |                        | 2.7      |      | 5.5 | V     |

| Supply Current                    | las             | All inputs O                      | $V_{DD} = 5.5V$        |          | 0.55 | 1   | mA    |

| Supply Current                    | IDD             | All inputs = 0                    | V <sub>DD</sub> = 3.6V |          | 0.38 | 0.8 | IIIA  |

| Shutdown Supply Current           |                 | $V_{DD} = 5.5V$                   | ·                      |          | 0.1  |     |       |

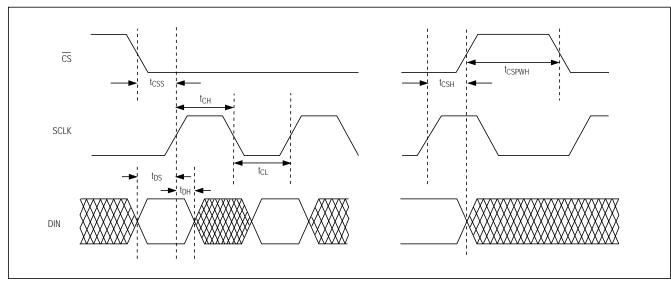

#### TIMING CHARACTERISTICS

(Figure 3,  $V_{DD}$  = +2.7V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 4)

| PARAMETER                       | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------|-----------------|------------|-----|-----|-----|-------|

| SERIAL INTERFACE TIMING         |                 |            | ,   |     |     |       |

| CS Fall to SCLK Rise Setup Time | tcss            |            | 50  |     |     | ns    |

| SCLK Rise to CS Rise Setup Time | tcsh            |            | 50  |     |     | ns    |

| DIN to SCLK Rise Setup Time     | t <sub>DS</sub> |            | 20  |     |     | ns    |

| DIN to SCLK Rise Hold Time      | tDH             |            | 20  |     |     | ns    |

| SCLK Pulse Width High           | t <sub>CH</sub> |            | 20  |     |     | ns    |

| SCLK Pulse Width Low            | t <sub>CL</sub> |            | 20  |     |     | ns    |

| CS Pulse Width High             | tcspwh          |            | 50  |     |     | ns    |

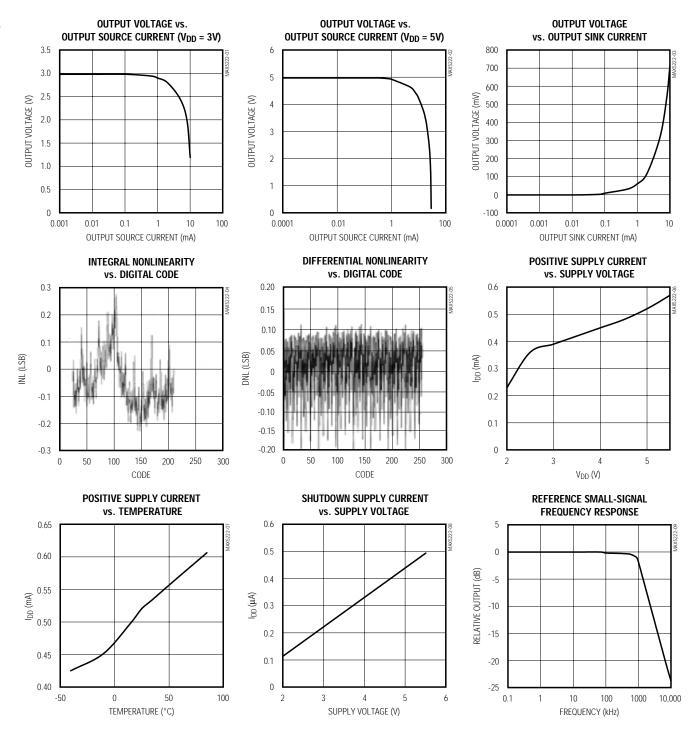

- **Note 2:** Reduced digital code range (code 24 through code 232) is due to swing limitations of the output amplifiers. See *Typical Operating Characteristics*.

- **Note 3:** Reference input resistance is code dependent. The lowest input resistance occurs at code 55hex. See the *Reference Input* section.

- Note 4: Guaranteed by design. Not production tested.

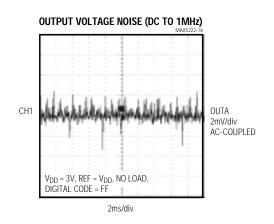

#### 標準動作特性

$(V_{DD} = +3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### 標準動作特性(続き)\_

$(V_{DD} = +3V, T_A = +25$ °C, unless otherwise noted.)

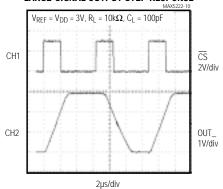

#### LARGE-SIGNAL OUTPUT STEP RESPONSE

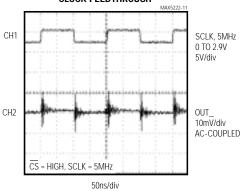

### **CLOCK FEEDTHROUGH**

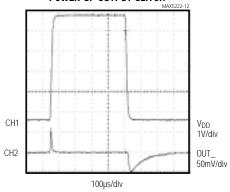

#### POWER-UP OUTPUT GLITCH

$V_{DD}$  = CHANGES BETWEEN 0 AND 5V RAMP TIME IS  $10\mu s$

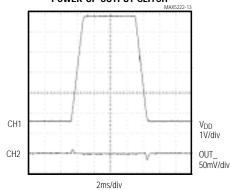

#### POWER-UP OUTPUT GLITCH

V<sub>DD</sub> = CHANGES BETWEEN 0 AND 5V RAMP TIME IS 1ms

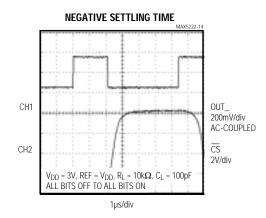

標準動作特性(続き)\_

$(V_{DD} = +3V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### 端子説明

| 端子 | 名称              | 機能                                                                                  |

|----|-----------------|-------------------------------------------------------------------------------------|

| 1  | CS              | チップセレクト。アクティブロー。データの16ビットシフトレジスタへの同期入力をイネーブルします。<br>プログラミングコマンドはCSの立ち上がりエッジで実行されます。 |

| 2  | GND             | グランド                                                                                |

| 3  | V <sub>DD</sub> | 正電源(+2.7V~+5.5V)。0.22µFでGNDにバイパスして下さい。                                              |

| 4  | SCLK            | シリアルクロック入力。データはSCLKの立上がりエッジで同期入力されます。                                               |

| 5  | OUTA            | DAC A出力電圧(バッファ付)                                                                    |

| 6  | OUTB            | DAC B出力電圧(バッファ付)                                                                    |

| 7  | REF             | DAC A及びDAC Bのリファレンス入力                                                               |

| 8  | DIN             | 16ビットシフトレジスタのシリアルデータ入力。データはSCLKの立上がりエッジで同期入力されます。                                   |

#### 詳細

#### アナログ部

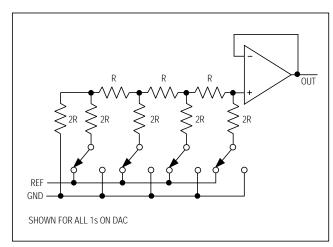

MAX5222は2つの8ビット電圧出力DACを備えています。これらのDACは、8ビットディジタル入力を相当するアナログ出力電圧(印加されているリファレンス電圧に比例)に変換する相補的スイッチを使った「反転」R-2Rラダーネットワークです

MAX5222は、DAC AとDAC Bによって共有される1つのリファレンス入力を持っています。本素子の両方のDAC及び入力ロジックはそれぞれ出力バッファアンプを備えているため、マイクロプロセッサ( $\mu$ P)及びCMOSインタフェースがシンプルになっています。電源範囲は+5.5V~+2.7Vです。

#### リファレンス入力及びDAC出力範囲

REFの電圧がDACのフルスケール出力を設定します。REF入力の入力インピーダンスはコードに依存します。入力コードが01010101(55 hex)の時に最小値の約8k になり、入力コードがゼロの時無限大になります。シャットダウンモードにおいては、DACレジスタに保存された値は変化しませんが、選択されたDAC出力はゼロに設定されます。これにより、リファレンスから負荷が除去されて電力が節約されます。MAX5222のシャットダウンモードを解除すると、DAC出力電圧が回復します。REFにおける入力抵抗はコードに依存するため、DACのリファレンスソースの出力インピーダンスは5 以下にして下さい。REFピンにおける入力容量もやはリコードに依存し、通常は25pF以下です。

レイルトゥレイルは日本モトローラの登録商標です。

REFのリファレンス電圧はGND~V<sub>DD</sub>の間が可能です。 詳細については「出力バッファアンプ」の項を参照して 下さい。

図1にDACの簡略化回路図を示します。

#### 出力バッファアンプ

DAC A及びDAC B電圧出力は内部でバッファされています。バッファアンプは、レイルトゥレイル® (GND ~  $V_{DD}$ )の出力電圧範囲を持っています。

いずれのDAC出力アンプも1mAの電流をソース/シンクすることができます。「標準動作特性」のINL対ディジタルコードのグラフを参照して下さい。アンプは100pF以下の容量性負荷に対してユニティゲイン安定です。スルーレートは1V/µs(typ)です。

#### シャットダウンモード

シャットダウンモードに設定されると、DAC A及び DAC Bの出力は直列5k 抵抗で受動的にGNDに引きつけられます。シャットダウンモードにおいては、REF入力はハイインピーダンス(2M typ)となってシステムリファレンスの消費電流を節約します。このため、システムリファレンスをパワーダウンする必要がありません。

シャットダウン解除時には、DAC出力はレジスタに保存された値に戻ります。この回復時間はDACのセトリング時間と同程度です。

図1. DACの簡略化回路図

#### シリアルインタフェース

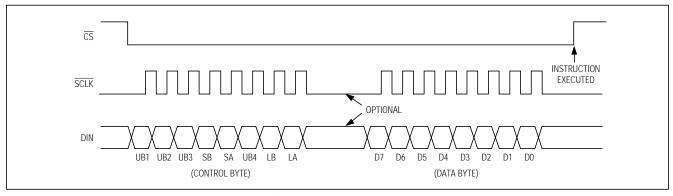

アクティブローのチップセレクト(CS)により、シフトレジスタはシリアルデータ入力からのデータを受け取ることができるようになります。データはシリアルクロック信号(SCLK)の立上がりエッジごとにシフトレジスタに同期入力されます。クロック周波数は最大25MHzまで可能です。

データは最上位ビット(MSB)を先にして送られ、1つの16ビットワード単位で送信できます。 CSがアクティブ (ロー)に保たれていれば、書込みサイクルをセグメント化することができます。このため、例えば2つの8ビット幅転送が可能です。16ビット全てをシフトレジスタに同期入力した後、CSの立上がリエッジでDAC出力とシャットダウン状態が更新されます。これらのDACはシングルバッファ構造であるため、両者を異なるディジタル値に同時に更新することはできません。

表1. 入力シフトレジスタ

|              | B0*   | DAC Data Bit 0 (LSB)        |

|--------------|-------|-----------------------------|

|              | B1    | DAC Data Bit 1              |

| ပ            | B2    | DAC Data Bit 2              |

| ₩            | В3    | DAC Data Bit 3              |

| DATA BITS    | B4    | DAC Data Bit 4              |

| 2            | B5    | DAC Data Bit 5              |

|              | B6    | DAC Data Bit 6              |

|              | В7    | DAC Data Bit 7 (MSB)        |

|              | LA    | Load Reg DAC A, Active High |

| (n           | LB    | Load Reg DAC B, Active High |

| CONTROL BITS | UB4   | Uncommitted Bit 4           |

| J            | SA    | Shut Down, Active High      |

| ¥            | SB    | Shut Down, Active High      |

| Ö            | UB3   | Uncommitted Bit 3           |

|              | UB2   | Uncommitted Bit 2           |

|              | UB1** | Uncommitted Bit 1           |

|              |       |                             |

<sup>\*</sup>Clocked in last.

シリアル入力データフォーマット及び制御コード表2にシリアル入力データフォーマットを示します。16ビット入力ワードは、8ビットの制御バイトと8ビットのデータバイトからなっています。8ビット制御バイトは内部でディコードされません。各制御ビットが1つの機能を実行します。データはUB1(未使用ビット)を先頭にして同期入力され、その後に残りの制御ビットとデータバイトが続きます。データバイト(B0)の最下位ビット(LSB)がシフトレジスタに同期入力される最後のビットとなります(図2)。

表3に16ビット入力ワードの例を示します。これは以下の機能を持っています。

- 80 hex(10進法の128)をDACレジスタA及びBに ロード

- DAC AとDAC Bはアクティブ

<sup>\*\*</sup>Clocked in first.

図2. 3線シリアルインタフェースのタイミング図

#### 表2. シリアルインタフェースのプログラミングコマンド

|     |     |     | CON | ΓROL | •   |    |    | DATA                          |   |    |        |       |     |          |                        |                               |  |  |  |  |

|-----|-----|-----|-----|------|-----|----|----|-------------------------------|---|----|--------|-------|-----|----------|------------------------|-------------------------------|--|--|--|--|

| UB1 | UB2 | UB3 | SB  | SA   | UB4 | LB | LA | A B7 B6 B5 B4 B3 B2 B1 B0 LSB |   |    |        |       | B2  | FUNCTION |                        |                               |  |  |  |  |

| Х   | Х   | 1   | *   | *    | 0   | 0  | 0  | X X X X X X X X               |   |    |        |       |     |          |                        | No Operation to DAC Registers |  |  |  |  |

| Χ   | Х   | 1   | *   | *    | 0   | 0  | 0  |                               |   | •  |        | •     |     | •        | •                      | Unassigned Command            |  |  |  |  |

| Χ   | Х   | 1   | *   | *    | 0   | 1  | 0  |                               |   | 8- | Bit DA | AC Da | nta |          | Load Register to DAC B |                               |  |  |  |  |

| Χ   | Χ   | 1   | *   | *    | 0   | 0  | 1  |                               |   | 8- | Bit DA | AC Da | ıta |          |                        | Load Register to DAC A        |  |  |  |  |

| Χ   | Х   | 1   | *   | *    | 0   | 1  | 1  |                               |   | 8- | Bit DA | AC Da | ıta |          |                        | Load Both DAC Registers       |  |  |  |  |

| Χ   | Х   | 1   | 0   | 0    | 0   | *  | *  | Х                             | Χ | Х  | Х      | Х     | Х   | Х        | Х                      | All DACs Active               |  |  |  |  |

| Χ   | Х   | 1   | 0   | 0    | 0   | *  | *  | X X X X X X X X X X           |   |    |        |       |     | Х        | Unassigned Command     |                               |  |  |  |  |

| Χ   | Χ   | 1   | 1   | 0    | 0   | *  | *  | x x x x x x x x x             |   |    |        |       |     |          | Shut Down              |                               |  |  |  |  |

| Χ   | Х   | 1   | 0   | 1    | 0   | *  | *  | x x x x x x x x x             |   |    |        |       |     |          | Shut Down              |                               |  |  |  |  |

| Χ   | Χ   | 1   | 1   | 1    | 0   | *  | *  | Х                             | Χ | Х  | Х      | Х     | Х   | Х        | Х                      | Shut Down                     |  |  |  |  |

X = Don't care.

#### 表3. 16ビット入力ワードの例

| LOADED LOADE IN FIRST IN LAS |     |     |    |    |     |    |    |    |    |    |    |    |    |    |    |

|------------------------------|-----|-----|----|----|-----|----|----|----|----|----|----|----|----|----|----|

| UB1                          | UB2 | UB3 | SB | SA | UB4 | LB | LA | В7 | В6 | B5 | В4 | В3 | B2 | B1 | В0 |

| Х                            | Х   | 1   | 0  | 0  | 0   | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

<sup>\* =</sup> Not shown, for the sake of clarity. The functions of loading and shutting down the DACs and programming the logic can be combined in a single command.

図3. シリアルインタフェースの詳細タイミング図

#### ディジタル入力

ディジタル入力はCMOSロジックとコンパチブルです。 ロジック入力が0.3V x V<sub>DD</sub>と0.7 x V<sub>DD</sub>の遷移ゾーンを よぎってトグルされる時、消費電流が僅かに増加します。

#### マイクロプロセッサとのインタフェース

MAX5222のシリアルインタフェースは、MICROWIRE、SPI及びQSPIとコンパチブルです。SPIの場合はCPOLとCPHAビットをクリアして下さい(CPOL = 0、CPHA = 0)。CPOL = 0にすると、インアクティブクロック状態がゼロに設定され、CPHA = 0の時はSCLKの立下がリエッジでデータが変化します。この設定により、SPIはフルクロック速度で動作できます。µPのシリアルポートが使用できない場合は、パラレルポートの3ビットを使って、ビット操作によりシリアルポートをエミュレートすることができます。シリアルクロックを必要な時にだけ動作させることにより、電圧出力におけるディジタルフィードスルーを最小限に抑えて下さい。

表4. コード表

|    | I  | DAC | СО | NTE | NTS | ANALOG |    |                                                             |  |  |  |

|----|----|-----|----|-----|-----|--------|----|-------------------------------------------------------------|--|--|--|

| В7 | В6 | B5  | B4 | ВЗ  | B2  | B1     | В0 | OUTPUT                                                      |  |  |  |

| 1  | 1  | 1   | 1  | 1   | 1   | 1      | 1  | +REF $\times \left(\frac{255}{256}\right)$                  |  |  |  |

| 1  | 0  | 0   | 0  | 0   | 0   | 0      | 1  | +REF $\times \left(\frac{129}{256}\right)$                  |  |  |  |

| 1  | 0  | 0   | 0  | 0   | 0   | 0      | 0  | $+REF \times \left(\frac{128}{256}\right) = +\frac{REF}{2}$ |  |  |  |

| 0  | 1  | 1   | 1  | 1   | 1   | 1      | 1  | +REF $\times \left(\frac{127}{256}\right)$                  |  |  |  |

| 0  | 0  | 0   | 0  | 0   | 0   | 0      | 1  | +REF $\times \left(\frac{1}{256}\right)$                    |  |  |  |

| 0  | 0  | 0   | 0  | 0   | 0   | 0      | 0  | OV                                                          |  |  |  |

#### Note

1LSB = REF

$$\times$$

2<sup>-8</sup> = REF  $\times$   $\left(\frac{1}{256}\right)$

ANALOG OUTPUT = REF  $\times$   $\left(\frac{D}{256}\right)$  where D = decimal value of digital input

| アプリケー     | ション情報 |  |

|-----------|-------|--|

| , , , , , | /     |  |

MAX5222は、 $V_{DD}$ が2.7 $V \sim 5.5$ Vの範囲の単一電源で動作するため、3V及び5Vシステムで通常使用される全ての電源電圧をカバーすることができます。

#### 初期化

内部パワーオンリセット回路が出力を強制的にゼロスケールにして、全ての外部レジスタをゼロに初期化します。これはシャットダウン状態と同等です。このため、パワーアップ時には初期書き込み動作を行うことにより、出力を希望の電圧に設定して下さい。

#### 電源及びグランド管理

GNDは最も高品質のグランドに接続して下さい。 $V_{DD}$ は $0.1\mu F \sim 0.22\mu F$  コンデンサでGNDにバイパスして下さい。リファレンス入力はバイパスなしで使用できます。最適のライン/負荷過渡応答及びノイズ性能を得るために、 $0.1\mu F \sim 4.7\mu F$  でリファレンスをGNDにバイパスして下さい。プリント基板を注意深くレイアウトすることにより、DAC出力、リファレンス及びディジタル入力間のクロストークを最小限に抑えることができます。アナログライン同士の間にグランドトレースをはさんで互いに分離して下さい。高周波ディジタルラインをアナログラインと平行に走らせないようにして下さい。

| チッ | ブ | 情報 |  |  |  |  |  |  |  |  |

|----|---|----|--|--|--|--|--|--|--|--|

|    |   |    |  |  |  |  |  |  |  |  |

**TRANSISTOR COUNT: 1480**

PROCESS TECHNOLOGY: BICMOS

パッケージ \_\_\_\_\_

販売代理店

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシム社では全体がマキシム社製品で実現されている回路以外の回路の使用については責任を持ちません。回路特許ライセンスは明言されていません。マキシム社は随時予告なしに回路及び仕様を変更する権利を保留します。

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600