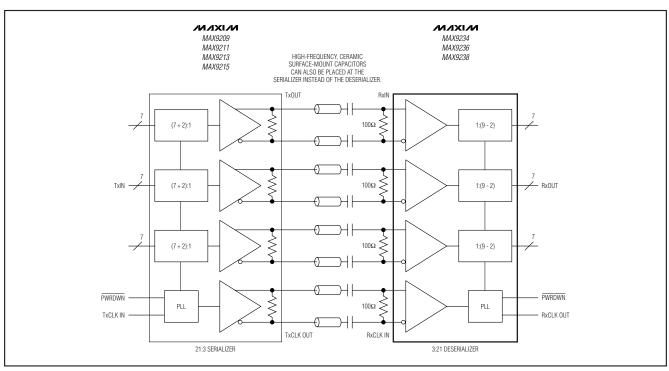

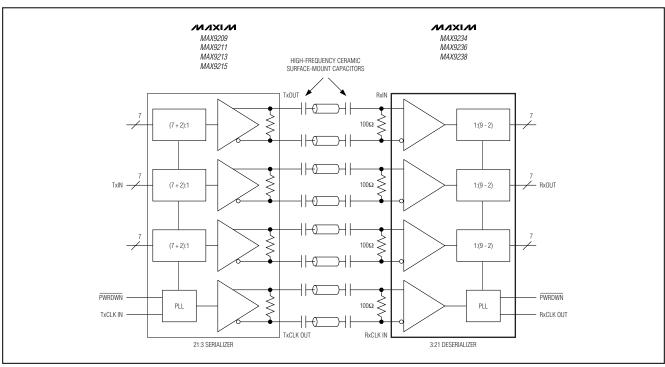

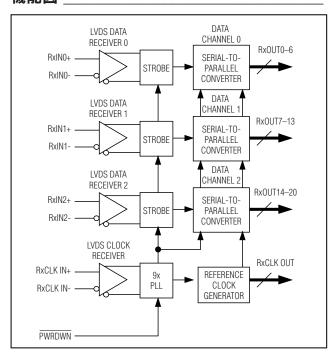

MAX9234/MAX9236/MAX9238は、3つのLVDSシリ アルデータ入力を21個のシングルエンドLVCMOS/LVTTL 出力にデシリアライズします。LVDSデータストリーム で受信されたパラレルレートLVDSクロックは、デシリア ライズ用のタイミングを提供します。出力は独立した 電源を備え、1.8V~5Vの出力ロジックレベルを可能に します。これらの製品はすべて、ホットスワップ可能 で、「オンザフライ」周波数プログラミングが可能です。

MAX9234/MAX9236/MAX9238は、DCバランス されており、AC結合によってシリアライザとデシリア ライザを分離することが可能です。各デシリアライザは、 シリアライザのMAX9209/MAX9211/MAX9213/ MAX9215の1つが送信したデータをデコードします。

MAX9234は、立上りエッジ出力ストローブを備えて います。MAX9236/MAX9238は、立下りエッジ出力 ストローブを備えています。MAX9234/MAX9236/ MAX9238は、DCバランスモードのみで動作します。

MAX9234/MAX9236は8MHz~34MHzのパラレル 入力クロックで動作しますが、MAX9238は16MHz~ 66MHzで動作します。シングルエンド出力の遷移時間 は、低周波バージョン製品(MAX9234/MAX9236)で 長くなり、EMIを低減させます。LVDS入力は、ISO 10605のESD仕様(空中放電の±25kVと接触放電の±8kV) を満たしています。

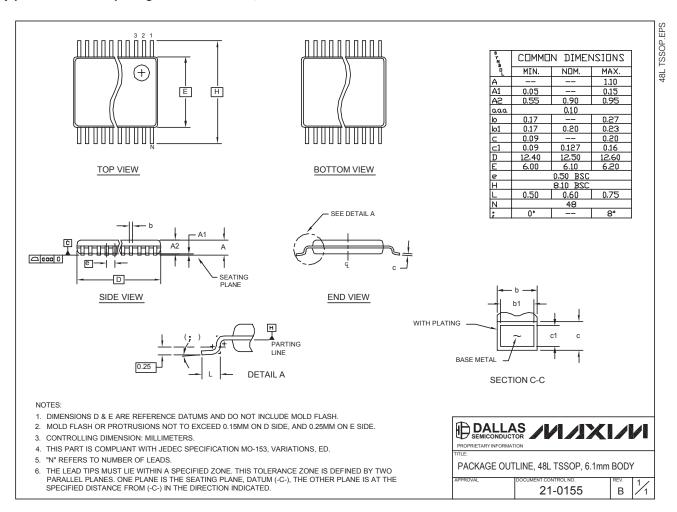

MAX9234/MAX9236/MAX9238は、48ピンTSSOP パッケージで提供され、-40℃~+85℃の温度範囲で 動作します。

#### アプリケーション

車載用ナビゲーションシステム 車載用DVDエンタテイメントシステム ディジタルコピー機 レーザプリンタ

#### 特長

- ◆ DCバランスにより入力コモンモード電圧の広範囲で AC結合を可能

- ♦ オンザフライ周波数プログラミング

- ♦ 動作周波数範囲 8MHz~34MHz(MAX9234/MAX9236) 16MHz~66MHz(MAX9238)

- ◆ 立下りエッジ出力ストローブ (MAX9236/MAX9238)

- ◆ 低速出力遷移によりEMIを低減 (MAX9234/MAX9236)

- ◆ PWRDWNがローのとき、ハイインピーダンス出力に よって出力をバス形式とすることが可能

- ◆ 5VトレラントPWRDWN入力

- ◆ 外付け部品が不要なPLL

- ◆ 最大スループット: 1.386Gbps

- ◆ 独立した出力電源ピンにより1.8V、2.5V、3.3V、 および5Vロジックとのインタフェース可能

- ◆ LVDS入力はISO 10605 ESD要項に適合

- ◆ LVDS入力はANSI TIA/EIA-644 LVDS規格に準拠

- ◆ 薄型48リードTSSOPパッケージ

- ◆ メイン電源:+3.3V

- ♦ 動作温度範囲:-40℃~+85℃

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX9234EUM | -40°C to +85°C | 48 TSSOP    |

| MAX9236EUM | -40°C to +85°C | 48 TSSOP    |

| MAX9238EUM | -40°C to +85°C | 48 TSSOP    |

機能図とピン配置は、データシートの最後に記載されています。

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND             |                       | ESD Protection               |

|------------------------------------|-----------------------|------------------------------|

| V <sub>CCO</sub> to GND            | 0.5V to +6.0V         | Human Body Model (R          |

| RxIN_, RxCLK IN_ to GND            | 0.5V to +4.0V         | All Pins to GND              |

| PWRDWN to GND                      | 0.5V to 6.0V          | ISO 10605 (RD = $2k\Omega$ , |

| RxOUT_, RxCLK OUT to GND           | 0.5V to (VCCO + 0.5V) | Contact Discharge (          |

| Continuous Power Dissipation (TA = |                       | Air Discharge (RxIN          |

| 48-Pin TSSOP (derate 16mW/°C       | above +70°C) 1282mW   | Lead Temperature (solde      |

| Storage Temperature Range          | 65°C to +150°C        |                              |

| Junction Temperature               | +150°C                |                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 V \text{ to } +3.6 V, V_{CCO} = +3.0 V \text{ to } +5.5 V, \overline{PWRDWN} = \text{high, differential input voltage } |V_{ID}| = 0.05 V \text{ to } 1.2 V, \text{input common-mode voltage } V_{CM} = |V_{ID}/2| \text{ to } 2.4 V - |V_{ID}/2|, T_A = -40 ^{\circ} C \text{ to } +85 ^{\circ} C, \text{ unless otherwise noted. Typical values are at } V_{CC} = V_{CCO} = +3.3 V, |V_{ID}| = 0.2 V, V_{CM} = 1.25 V, T_A = +25 ^{\circ} C.) \text{ (Notes 1, 2)}$

| PARAMETER                           | SYMBOL          | CONDITIONS                                               |            | MIN                    | TYP                     | MAX | UNITS |     |

|-------------------------------------|-----------------|----------------------------------------------------------|------------|------------------------|-------------------------|-----|-------|-----|

| SINGLE-ENDED INPUT (PWRDW           | N)              |                                                          |            |                        |                         |     |       |     |

| High-Level Input Voltage            | VIH             |                                                          |            |                        | 2.0                     |     | 5.5   | V   |

| Low-Level Input Voltage             | VIL             |                                                          |            |                        |                         |     | +0.8  | V   |

| Input Current                       | I <sub>IN</sub> | V <sub>IN</sub> = high or lov                            | V          |                        | -70                     |     | +70   | μΑ  |

| Input Clamp Voltage                 | V <sub>CL</sub> | $I_{CL} = -18mA$                                         |            |                        |                         |     | -1.5  | V   |

| SINGLE-ENDED OUTPUTS (RxO           | UT_, RxCLK      | OUT)                                                     |            |                        |                         |     |       |     |

|                                     |                 | I <sub>OH</sub> = -100μA                                 |            | V <sub>CCO</sub> - 0.1 |                         |     |       |     |

| High-Level Output Voltage           | N/              | I <sub>OH</sub> = -2mA                                   | MAX9234/   | RxCLK OUT              | V <sub>CCO</sub> - 0.25 |     |       | - V |

|                                     | VOH             |                                                          | MAX9236    | RxOUT_                 | V <sub>CCO</sub> - 0.40 |     |       |     |

|                                     |                 |                                                          | MAX9238    |                        | V <sub>CCO</sub> - 0.25 |     |       | 1   |

|                                     | V <sub>OL</sub> | I <sub>OL</sub> = 100μA                                  |            |                        |                         | 0.1 |       |     |

| Law Law LOwer A Vallage             |                 | I <sub>OL</sub> = 2mA                                    | MAX9234/   | RxCLK OUT              |                         |     | 0.2   | V   |

| Low-Level Output Voltage            |                 |                                                          | MAX9236    | RxOUT_                 |                         |     | 0.26  |     |

|                                     |                 |                                                          | MAX9238    |                        |                         |     | 0.2   |     |

| High-Impedance Output Current       | loz             | PWRDWN = low,<br>Vout = -0.3V to Vcco + 0.3V             |            | -20                    |                         | +20 | μA    |     |

|                                     |                 |                                                          | MAX9234/   | RxCLK OUT              | -10                     |     | -40   |     |

| Output Short-Circuit Current        |                 | $V_{CCO} = 3.0V \text{ to}$<br>3.6V, $V_{OUT} = 0$       | MAX9236    | RxOUT_                 | -5                      |     | -20   | 1   |

|                                     | los             | 0.0v, v <sub>001</sub> = 0                               | MAX9238    |                        | -10                     |     | -40   |     |

| (Note: Short one output at a time.) |                 | V <sub>CCO</sub> = 4.5V to<br>5.5V, V <sub>OUT</sub> = 0 | LINIMASZOU | RxCLK OUT              | -28                     |     | -75   | mA  |

|                                     |                 |                                                          |            | RxOUT_                 | -14                     |     | -37   |     |

|                                     |                 | 0.50, 0001 - 0                                           | MAX9238    |                        | -28                     |     | -75   |     |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 V \text{ to } +3.6 V, V_{CCO} = +3.0 V \text{ to } +5.5 V, \overline{PWRDWN} = \text{high, differential input voltage } |V_{ID}| = 0.05 V \text{ to } 1.2 V, \text{input common-mode voltage } V_{CM} = |V_{ID}/2| \text{ to } 2.4 V - |V_{ID}/2|, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = V_{CCO} = +3.3 V, |V_{ID}| = 0.2 V, V_{CM} = 1.25 V, T_A = +25 ^{\circ}\text{C}.) \text{ (Notes 1, 2)}$

| PARAMETER                         | SYMBOL                                | CONDITIONS                                                            |                     | MIN   | TYP | MAX | UNITS |    |  |

|-----------------------------------|---------------------------------------|-----------------------------------------------------------------------|---------------------|-------|-----|-----|-------|----|--|

| LVDS INPUTS                       |                                       |                                                                       |                     |       |     |     |       |    |  |

| Differential Input-High Threshold | V <sub>TH</sub>                       |                                                                       |                     |       |     |     | 50    | mV |  |

| Differential Input-Low Threshold  | V <sub>TL</sub>                       |                                                                       |                     |       | -50 |     |       | mV |  |

| Input Current                     | I <sub>IN+,</sub> I <sub>IN-</sub>    | PWRDWN = high                                                         | or low              |       | -25 |     | +25   | μΑ |  |

| Power-Off Input Current           | I <sub>INO+</sub> , I <sub>INO-</sub> | V <sub>CC</sub> = V <sub>CCO</sub> = 0 or open,<br>PWRDWN = 0 or open |                     | -40   |     | +40 | μΑ    |    |  |

|                                   | R <sub>IN1</sub>                      | PWRDWN = high or low (Figure 1)                                       |                     | 42    | 78  | 70  | kΩ    |    |  |

| Input Resistor 1                  |                                       | V <sub>CC</sub> = V <sub>CCO</sub> = 0 or open (Figure 1)             |                     |       |     | 42  |       | 78 |  |

| POWER SUPPLY                      |                                       |                                                                       |                     |       |     |     |       |    |  |

|                                   | Icew                                  | C <sub>L</sub> = 8pF,<br>worst-case                                   | MAX9234/<br>MAX9236 | 8MHz  |     |     | 42    |    |  |

|                                   |                                       |                                                                       |                     | 16MHz |     |     | 57    |    |  |

| Worst-Case Supply Current         |                                       |                                                                       |                     | 34MHz |     |     | 98    | I  |  |

|                                   |                                       | pattern; V <sub>CC</sub> = V <sub>CCO</sub> = 3.0V to                 |                     | 16MHz |     |     | 63    | mA |  |

|                                   |                                       |                                                                       | MAX9238             | 34MHz |     |     | 106   |    |  |

|                                   |                                       |                                                                       |                     | 66MHz |     |     | 177   |    |  |

| Power-Down Supply Current         | Iccz                                  | PWRDWN = low                                                          |                     |       |     |     | 50    | μΑ |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$\begin{array}{l} (V_{CC} = V_{CCO} = +3.0 V \ to \ +3.6 V, \ 100 mV_{P-P} \ at \ 200 kHz \ supply \ noise, \ C_L = 8pF, \ \overline{PWRDWN} = high, \ differential \ input \ voltage \ \left|V_{ID}\right| = 0.1 V \ to \ 1.2 V, \ input \ common \ mode \ voltage \ V_{CM} = \left|V_{ID}/2\right| \ to \ 2.4 V \ - \left|V_{ID}/2\right|, \ T_A = -40 ^{\circ}C \ to \ +85 ^{\circ}C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ V_{CC} = V_{CCO} = +3.3 V, \ \left|V_{ID}\right| = 0.2 V, \ V_{CM} = 1.25 V, \ T_A = +25 ^{\circ}C.) \ (Notes \ 3, \ 4, \ 5) \end{array}$

| PARAMETER                             | SYMBOL | CONDITIONS                                                  |                       | MIN       | TYP            | MAX  | UNITS           |    |

|---------------------------------------|--------|-------------------------------------------------------------|-----------------------|-----------|----------------|------|-----------------|----|

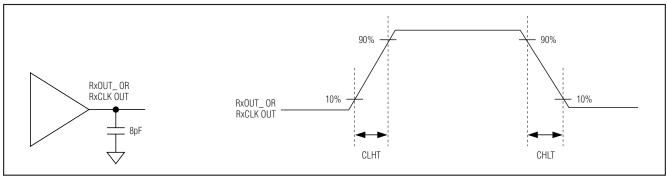

| Output Rise Time                      | CLHT   | 0.1V <sub>CCO</sub> to<br>0.9V <sub>CCO</sub> ,<br>Figure 3 | 7000 10 1417 01020-17 | RxOUT     | 3.52           | 5.04 | 6.24            | ns |

|                                       |        |                                                             |                       | RxCLK OUT | 2.2            | 3.15 | 3.9             |    |

|                                       |        |                                                             | MAX9238               |           | 2.2            | 3.15 | 3.9             |    |

|                                       |        | 0.9V <sub>CCO</sub> to 0.1V <sub>CCO</sub> ,                | MAX9234/              | RxOUT     | 1.95           | 3.18 | 4.35            |    |

| Output Fall Time                      | CHLT   |                                                             | MAX9236               | RxCLK OUT | 1.3            | 2.12 | 2.9             | ns |

|                                       |        | Figure 3                                                    | MAX9238               |           | 1.3            | 2.12 | 2.9             |    |

|                                       |        |                                                             |                       | 8MHz      | 6600           | 7044 |                 |    |

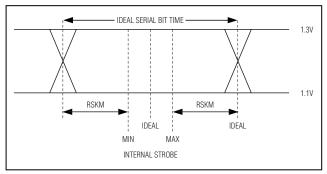

| RxIN Skew Margin                      | RSKM   | Figure 4                                                    |                       | 16MHz     | 2560           | 3137 |                 | ps |

| HXIIN Skew Margin                     | HOKIVI | (Note 6)                                                    |                       | 34MHz     | 900            | 1327 |                 |    |

|                                       |        |                                                             | MAX9238               | 66MHz     | 330            | 685  |                 |    |

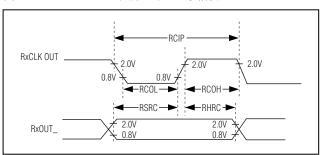

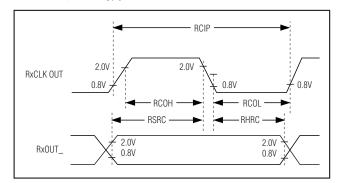

| RxCLK OUT High Time                   | RCOH   | Figures 5a, 5b                                              |                       |           | 0.35 x<br>RCOP |      |                 | ns |

| RxCLK OUT Low Time                    | RCOL   | Figures 5a, 5b                                              |                       |           | 0.35 x<br>RCOP |      |                 | ns |

| RxOUT Setup to RxCLK OUT              | RSRC   | Figures 5a, 5b                                              |                       |           | 0.30 x<br>RCOP |      |                 | ns |

| RxOUT Hold from RxCLK OUT             | RHRC   | Figures 5a, 5b                                              |                       |           | 0.45 x<br>RCOP |      |                 | ns |

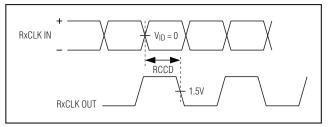

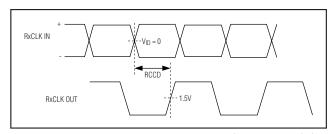

| RxCLK IN to RxCLK OUT Delay           | RCCD   | Figures 6a, 6b                                              |                       |           | 4.9            | 6.17 | 8.1             | ns |

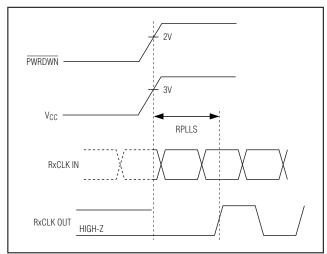

| Deserializer Phase-Locked Loop<br>Set | RPLLS  | Figure 7                                                    |                       |           |                |      | 32800<br>x RCIP | ns |

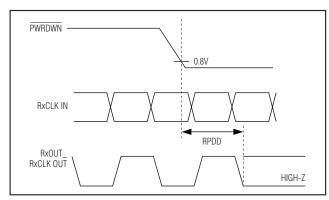

| Deserializer Power-Down Delay         | RPDD   | Figure 8                                                    |                       |           |                |      | 100             | ns |

- Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub> and V<sub>TL</sub>.

- Note 2: Maximum and minimum limits overtemperature are guaranteed by design and characterization. Devices are production tested at T<sub>A</sub> = +25°C.

- Note 3: AC parameters are guaranteed by design and characterization, and are not production tested. Limits are set at ±6 sigma.

- Note 4: C<sub>L</sub> includes probe and test jig capacitance.

- Note 5: RCIP is the period of RxCLK IN. RCOP is the period of RxCLK OUT. RCIP = RCOP.

- Note 6: RSKM measured with ≤150ps cycle-to-cycle jitter on RxCLK IN.

#### 標準動作特性

(VCC = VCCO = +3.3V, CL = 8pF, PWRDWN = high, differential input voltage | VID | = 0.2V, input common-mode voltage VCM = 1.2V,  $T_A = +25$ °C, unless otherwise noted.)

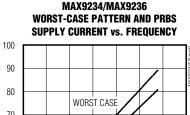

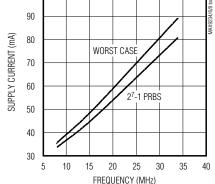

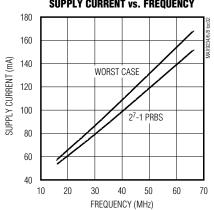

#### **MAX9238 WORST-CASE PATTERN AND PRBS SUPPLY CURRENT vs. FREQUENCY**

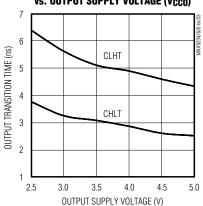

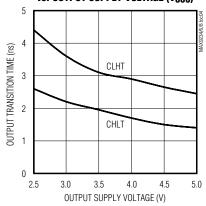

#### MAX9234/MAX9236 **RXOUT TRANSITION TIME** vs. OUTPUT SUPPLY VOLTAGE (VCCO)

#### **MAX9238 RXOUT TRANSITION TIME** vs. OUTPUT SUPPLY VOLTAGE (VCCO)

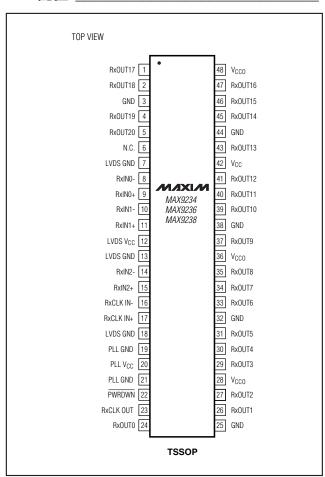

#### 端子説明

| 端子                            | 名称                   | 機能                                                                                                                              |

|-------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 5, 45,<br>46, 47     | RxOUT14-RxOUT20      | チャネル2シングルエンド出力                                                                                                                  |

| 3, 25, 32, 38,<br>44          | GND                  | グランド                                                                                                                            |

| 6                             | N.C.                 | 接続なし                                                                                                                            |

| 7, 13, 18                     | LVDS GND             | LVDSグランド                                                                                                                        |

| 8                             | RxIN0-               | 反転チャネルO LVDSシリアルデータ入力                                                                                                           |

| 9                             | RxIN0+               | 非反転チャネルO LVDSシリアルデータ入力                                                                                                          |

| 10                            | RxIN1-               | 反転チャネル1 LVDSシリアルデータ入力                                                                                                           |

| 11                            | RxIN1+               | 非反転チャネル1 LVDSシリアルデータ入力                                                                                                          |

| 12                            | LVDS V <sub>CC</sub> | LVDS電源電圧。LVDS $V_{CC}$ にできる限り近ずけて、 $0.1\mu$ Fと $0.001\mu$ Fの並列コンデンサでLVDS GNDにバイパスしてください。最小のコンデンサ値になるように電源端子にできる限り近付けてください。      |

| 14                            | RxIN2-               | 反転チャネル2 LVDSシリアルデータ入力                                                                                                           |

| 15                            | RxIN2+               | 非反転チャネル2 LVDSシリアルデータ入力                                                                                                          |

| 16                            | RxCLK IN-            | 反転LVDSパラレルレートクロック入力                                                                                                             |

| 17                            | RxCLK IN+            | 非反転LVDSパラレルレートクロック入力                                                                                                            |

| 19, 21                        | PLL GND              | PLLグランド                                                                                                                         |

| 20                            | PLL V <sub>CC</sub>  | PLL電源電圧。PLL $V_{CC}$ にできる限り近付けて、 $0.1 \mu F$ $\geq 0.001 \mu F$ の並列コンデンサでPLL GNDに バイパスしてください。最小のコンデンサ値になるように電源端子にできる限り近付けてください。 |

| 22                            | PWRDWN               | 5VトレラントLVTTL/LVCMOSパワーダウン入力。内部でGNDにプルダウンされています。<br>PWRDWN = ローまたはオープンのとき、出力はハイインピーダンスです。                                        |

| 23                            | RxCLK OUT            | パラレルレートクロックシングルエンド出力。MX9234は立上りエッジストローブを備えています。MAX9236/MAX9238は立下りエッジストローブを備えています。                                              |

| 24, 26, 27, 29,<br>30, 31, 33 | RxOUT0-RxOUT6        | チャネル0シングルエンド出力                                                                                                                  |

| 28, 36, 48                    | Vcco                 | 出力電源電圧。V <sub>CCO</sub> にできる限り近付けて、0.1µFと0.001µFの並列コンデンサでGNDにバイパスしてください。最小のコンデンサ値になるように電源端子にできる限り近付けてください。                      |

| 34, 35, 37, 39,<br>40, 41, 43 | RxOUT7-RxOUT13       | チャネル1シングルエンド出力                                                                                                                  |

| 42                            | Vcc                  | ディジタル電源電圧。V <sub>CC</sub> にできる限り近付けて、0.1µFと0.001µFの並列コンデンサでGNDに<br>バイパスしてください。最小のコンデンサ値になるように電源端子にできる限り近付けてください。                |

#### 表1. 製品互換表

| PART    | EQUIVALENT WITH DCB/NC = HIGH OR OPEN | OPERATING<br>FREQUENCY (MHz) | OUTPUT STROBE |

|---------|---------------------------------------|------------------------------|---------------|

| MAX9234 | MAX9210                               | 8 to 34                      | Rising edge   |

| MAX9236 | MAX9220                               | 8 to 34                      | Falling edge  |

| MAX9238 | MAX9222                               | 16 to 66                     | Falling edge  |

#### 詳細

MAX9234/MAX9236は8MHz~34MHzのパラレルクロック周波数で動作します。MAX9238は16MHz~66MHzのパラレルクロック周波数で動作します。シングルエンド出力の遷移時間は、EMIを低減させるため、MAX9234/MAX9236では長くなっています。

#### DCバランス

シリアライザのMAX9209/MAX9211/MAX9213/MAX9215(これは、デシリアライザのMAX9234/MAX9236/MAX9238の姉妹製品です)によるデータコーディングは、各チャネルで送信される1と0の不均衡を制限します。送信された各2進数の1に+1を割り当て、送信された各2進数の0に-1を割り当てた場合、割り当てた値の現行合計値の変動はディジタル合計値変動(DSV)と呼ばれます。データチャネルに対する最大DSVは10です。送信されるのは、せいぜい、0の数が1の数の10倍、もしくは1の数が0の数の10倍です。クロックチャネルに対する最大DSVは5です。DSVを制限し正しい結合コンデンサを選定することで、差動信号振幅が維持され、AC結合リンク上のドループに起因するジッタが抑制されます。

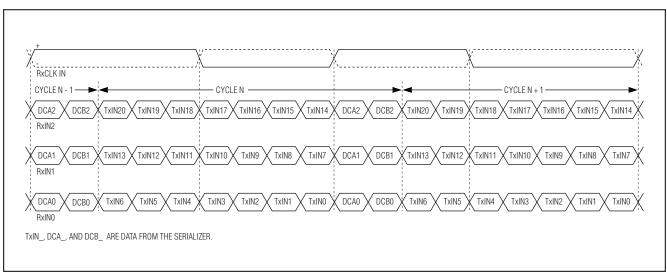

データチャネル上のDCバランスを保つために、シリアライザのパラレルデータはワード境界におけるディジタル合計値の符号に応じて反転されたり、反転されなかったりします。2つの補数ビットが7パラレル入力データビットの各グループに付加されて、データビットが反転されているかどうかをデシリアライザのMAX9234/MAX9236/MAX9238に示します(図9参照)。デシリアライザは、パラレルデータの当初の状態を復元します。LVDSクロック信号は、4/9と5/9のデューティサイクルを交互に繰り返して、DCバランスを保ちます。

#### AC結合の利点

DC結合によって発生するビットエラーは、AC結合によりレシーバのコモンモード電圧範囲を広げることによって排除することができます。AC結合では、LVDSレシーバのコモンモード電圧範囲はコンデンサの電圧定格と同程度まで増加します。標準的なLVDSドライバ出力は、1.25Vのオフセット電圧を中心として350mVであるため、1.425Vと1.075Vのシングルエンド出力

電圧を生成します。LVDSレシーバは、0~2.4Vの信号 を受け入れるため、DC結合リンク上でドライバと レシーバの間に約±1Vのコモンモード差を許容します (2.4V-1.425V=0.975Vおよび1.075V-0V= 1.075V)。コモンモード電圧差は、グランド電位の変 動やコモンモードノイズに起因することがあります。 ±1Vを超える差があると、レシーバは入力信号を正しく 読み取るとは限らずビットエラーを生じる場合があり ます。AC結合は、低周波のグランドシフトとコモン モードノイズをフィルタ除去し、高周波データを通過 させます。結合コンデンサの電圧定格までのコモン モード電圧差(差動振幅の1/2を差し引いた)は許容され ます。差動信号振幅を維持しAC結合リンク上のジッタを 制限するために、データのDCバランスコーディングが 必要です。LVDSドライバの各出力と直列接続された コンデンサがあれば、AC結合としては十分です。ただし、 2個のコンデンサ(シリアライザ出力の1個とデシリア ライザ入力の1個)は、ケーブルのいずれか一端が高電圧 に短絡された場合の保護に役立ちます。

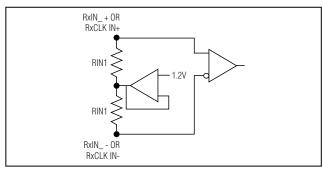

図1. LVDSの入力回路

図2. 最悪ケースのテストパターン

図3. 出力負荷と遷移時間

図4. LVDSレシーバの入力スキュー余裕度

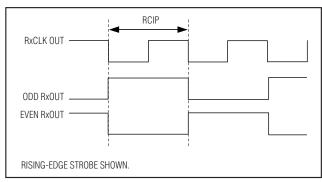

図5a. MAX9234出力のセットアップ/ホールドおよび ハイ/ロー時間

図5b. MAX9236/MAX9238出力のセットアップ/ホールド およびハイ/ロー時間

図6a. MAX9234のクロック入力-クロック出力間遅延

図6b. MAX9236/MAX9238のクロック入力-クロック出力 間遅延

図7. PLLの設定時間

図8. パワーダウン遅延

# MAX9234/MAX9236/MAX9238 & MAX9210/MAX9220/MAX9222

MAX9234/MAX9236/MAX9238は、DCバランスモードでのみで動作します。ピン配列は、MAX9234/MAX9236/MAX9238のピン6が接続なし(N.C.)であることを除いてMAX9210/MAX9220/MAX9222と同じです。DCバランスによって、直列コンデンサによるAC結合が可能になります。MAX9234/MAX9236/MAX9238は、ホットスワップが可能で、入力周波数をテストサイクルごとに変更することができますが、それ以外の仕様と機能はDCバランスモードで動作しているMAX9210/MAX9220/MAX9222と同じです。表1を参照してください。

#### アプリケーション情報

#### AC結合コンデンサの選択

送信される符号に電圧ドループとDSVがあると、信号の 遷移が種々の電圧レベルから始まります。遷移時間は 有限であるため、信号の遷移が種々の電圧レベルから 始まるとタイミングジッタが生じます。AC結合リンク の時定数は、ドループとジッタが許容レベルまで減少 するように選定する必要があります。

AC結合リンクのRCネットワークは、LVDSレシーバの終端抵抗器  $(R_T)$ 、LVDSドライバの出力抵抗器  $(R_O)$ 、および直列AC結合コンデンサ(C)で構成されます。値の等しい2個の直列コンデンサのRC時定数は、 $(C\times(R_T+R_O))/2$ です(図10)。値の等しい4個の直列コンデンサのRC時定数は、 $(C\times(R_T+R_O))/4$ です(図11)。

$R_T$ は、伝送ラインのインピーダンス(通常100 $\Omega$ )の整合に必要で、 $R_O$ はLVDSドライバの設計によって決まります(以下の例では、シリアライザのMAX9209/MAX9211/MAX9213/MAX9215に対して $78\Omega$ の最小差動出力抵抗が使用されています)。このため、システム時定数を変える場合はコンデンサを選択し直すことになります。

図9. デシリアラアイザのシリアル入力

図10. リンク当たり2個のコンデンサ、AC結合

図11. リンク当たり4個のコンデンサ、AC結合

以下の例では、2%のドループに対応するコンデンサの値を計算します。つぎに、1nsの遷移時間を仮定してこのドループに起因するジッタを計算します。

$C = -(2 \times t_B \times DSV) / (ln (1 - D) \times (R_T + R_O))$  (式1) ここで、

C = AC結合コンデンサ(F)

t<sub>B</sub> = ビット時間(s)

DSV = ディジタル合計値変動(整数)

In = 自然対数

D = ドループ(信号振幅の%)

$R_T = 終端抵抗器(\Omega)$

$R_{\Omega} =$  出力抵抗器( $\Omega$ )

式1は、直列コンデンサが2個の場合です(図10)。ビット時間( $t_B$ )は、パラレルクロックの周期を9で割った時間です。DSVは10です。直列コンデンサが4個の場合は、式3をご覧ください(図11)。

8MHzのパラレルレートクロックにおける2%の最大ドループに対応するコンデンサは、次式によって計算されます。

$C = -(2 \times t_B \times DSV) / (In (1 - D) \times (R_T + R_O))$   $C = -(2 \times 13.9ns \times 10) / (In (1 - 0.02) \times (100\Omega + 78\Omega))$   $C = 0.0773 \mu F$

ドループに起因するジッタは、ドループと遷移時間に 比例します。

$t_J = t_T \times D$  (式2)

ここで、

$t_1 = ジッタ(s)$

tT = 遷移時間(s)(0~100%)

D = ドループ(信号振幅の%)

2%のドループと1nsと仮定した遷移時間によるジッタは、次のようになります。

$t_{J} = 1ns \times 0.02$  $t_{J} = 20ps$

実際のシステムにおける遷移時間は、シリアライザによって駆動されるケーブルの周波数応答に左右されます。 パラレルクロックのより高い周波数およびドループと ジッタのより高いレベルに対しては、コンデンサの値が 小さくなります。高周波の表面実装型セラミックコン デンサを使用してください。

式1は、4個の直列コンデンサ(図11)の場合、次式のように書き換えられます。

$C = -(4 \times t_B \times DSV) / (ln (1 - D) \times (R_T + R_O))$  (式3)

#### 入力バイアスと周波数検出

反転および非反転の各LVDS入力は、AC結合にバイアスを供給するために内部で $42k\Omega$  (min)を通じて+1.2Vに接続されています(図1)。クロック入力の周波数検出回路は、低周波で入力がスイッチングしていないか、または低周波でスイッチングしているかを検出します。この場合、すべての出力はローに駆動されます。クロック入力が駆動されていないときのノイズによるスイッチングを防止するため、 $10k\Omega\pm1\%$ のプルアップ抵抗器を非反転入力と $V_{CC}$ の間に接続し、 $10k\Omega\pm1\%$ のプルグウン抵抗器を反転入力とグランドの間に接続することによって、クロック入力を差動の+15mVにバイアスしてください。これらのバイアス抵抗器は、 $100\Omega\pm1\%$ 許容差の終端抵抗器とともに+15mVの差動入力を構成します。

#### 未使用のLVDSデータ入力

未使用の各LVDSデータ入力で、反転入力を10kΩの抵抗器を使ってV<sub>CC</sub>にプルアップし、非反転入力を10kΩの抵抗器を使ってグランドにプルダウンしてください。終端抵抗器は接続しないでください。プルアップおよびプルダウン抵抗器は、対応する出力をローに駆動しノイズによるスイッチングを防止します。

#### **PWRDWN**

PWRDWNをローに駆動すると、出力がハイインピーダンスになり、PLLが停止して、消費電流を50µA以下に減少させます。PWRDWNをハイに駆動すると、PLLがロックするまで出力をローに駆動します。2個のデシリアライザの出力をバスにして、出力がPWRDWNによって制御される2:1のマルチプレクサを構成することができます。1個のデシリアライザをディセーブル(PWRDWNをローに駆動)してから次の1個をイネーブル(PWRDWNをハイに駆動)するまで100nsの間待って、バス接続された出力の衝突を回避してください。

#### 入力クロックとPLLロック時間

PWRDWN、または適正なPLLロックのための電源立上げに関するパラレルレートクロック(RxCLK IN)の印加または再印加にはタイミングシーケンスが不要です。PLLロック時間は、内蔵のカウンタによって設定されます。ロックの最大時間は32,800クロック周期です。電源とクロックは、ロック時間の仕様を満たすように安定している必要があります。PLLがロックしているとき出力はローとなっています。

#### 電源のバイパス

ディジタル回路、出力、PLL、およびLVDS入力には、独立した電源領域が内蔵されています。 $V_{CC}$ 、 $V_{CCO}$ 、PLL  $V_{CC}$ 、およびLVDS  $V_{CC}$ の各ピンを、高周波、表面実装型の $0.1\mu$ Fと $0.001\mu$ Fの並列セラミックコンデンサを用いてデバイスのできる限り近くでバイパスしてください。その際、最小値のコンデンサを電源ピンにできる限り近付けてください。

#### ケーブルとコネクタ

LVDSの相互接続は、通常、差動インピーダンスが100Ωです。インピーダンスの不連続性を最小限にするため、 差動インピーダンスが整合されたケーブルとコネクタを使用してください。

ツイストペアケーブルとシールド付きツイストペアケーブルは、リボンケーブルに比べて優れた信号品質を提供し、磁場の相殺効果によってEMIの発生を抑制する傾向があります。平衡ケーブルはノイズをコモンモードとして拾うため、LVDSレシーバによって除去されます。

#### 基板レイアウト

LVTTL/LVCMOS出力とLVDS入力の各信号を引き離して、 クロストークを防止してください。電源、グランド、 LVDS入力、およびディジタル信号に対して各層が分離 された4層のプリント基板が推奨されます。

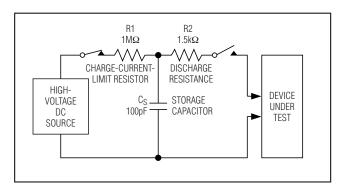

#### ESD保護

図12. ヒューマンボディモデルのESD試験回路

#### 5Vトレラント入力

PWRDWNは、5Vトレラントで、内部でGNDにプルダウンされています。

#### スキューマージン(RSKM)

スキューマージン(RSKM)は、デシリアライザ以外の原因によるシリアルデータのサンプリングセットアップ時間とホールド時間への悪影響に対して許容される時間です。デシリアライザのサンプリングには不確定性がありますが、これをRSKMから差し引く必要はありません。RSKMを損なうジッタとスキューの主な外部要因は、相互接続の符号間干渉、シリアライザパルス位置の不確定性、およびペア間スキューです。

#### VCCO出力電源と電力消費

各出力は、定格入力ロジックレベルが $1.8V\sim5V$ のシステムとのインタフェース用に独立した電源( $V_{CCO}$ )を備えています。「DC電気的特性(DC Electrical Characteristics)」表には、すべての出力がワーストケースのスイッチングパターンでスイッチングした場合の複数のスイッチング周波数における8pF負荷、 $V_{CCO}=3.6V$ に対する最大消費電流が記載されています。同じ8pF負荷とワーストケースパターンの場合の3.6V以外の $V_{CCO}$ に対する概略の差分消費電流は、次式から計算することができます。

I<sub>I</sub> = C<sub>T</sub>V<sub>I</sub> 0.5f<sub>C</sub> x 21 (データ出力) + C<sub>T</sub>V<sub>I</sub>f<sub>C</sub> x 1 (クロック出力)

ここで、

l<sub>1</sub> = 差分消費電流

$C_T = 内部(C_{INT})$ と外部( $C_I$ )の全負荷容量

V<sub>I</sub> = 差分電源電圧

fc = 出力クロックスイッチング周波数

差分電流は、「DC電気的特性(DC Electrical Characteristics)」 表の最大消費電流に加えられるか( $V_{CCO} > 3.6V$ の場合)、またはこの最大消費電流から差し引かれます( $V_{CCO} < 3.6V$ の場合)。内部の出力バッファ容量は $C_{INT} = 6pF$

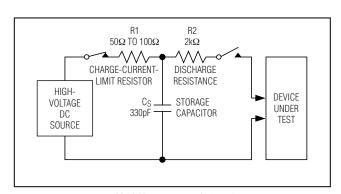

図13. ISO 10605接触放電のESD試験回路

です。データ出力のワーストケースパターンのスイッチング周波数は、出力クロックのスイッチング周波数の 1/2です。

以下の例では、 $V_{CCO} = 5.5V$ 、 $f_C = 34MHz$ 、および  $C_I = 8pF$ の場合の差分消費電流を計算します。

$$V_1 = 5.5V - 3.6V = 1.9V$$

CT = CINT + CL = 6pF + 8pF = 14pF

ここで、

$I_I = C_T V_I 0.5 F_C \times 21 (データ出力) + C_T V_I f_C \times 1 (クロック出力)$

$I_I = (14pF \times 1.9V \times 0.5 \times 34MHz \times 21) + (14pF \times 1.9V \times 34MHz)$

$I_1 = 9.5 \text{mA} + 0.9 \text{mA} = 10.4 \text{mA}$

出力電源電圧がV<sub>CCO</sub> = 3.6Vよりも低い場合は、同じ式と 方法によって、低減された消費電流を計算することが できます。

高いスイッチング周波数、高い電源電圧、および大きい容量性負荷では、電力消費パッケージの電力消費定格を超える場合があります。パッケージの最大電力消費定格を超えないようにしてください。パッケージの最大電力消費容量と温度ディレーティングについては、

#### 機能図

「絶対最大定格(Absolute Maximum Ratings)」をご覧ください。

#### 立上りまたは立下りエッジ出力ストローブ

MAX9234は立上りエッジ出力ストローブを備えており、このストローブはRxCLK OUTの立上りエッジでパラレル出力データを次のチップにラッチします。MAX9236/MAX9238は立下りエッジ出力ストローブを備えており、このストローブはRxCLK OUTの立下りエッジでパラレル出力データを次のチップにラッチします。デシリアライザ出力ストローブの極性は、シリアライザ入力ストローブの極性と一致している必要はありません。立上りまたは立下りエッジ出力ストローブを備えたデシリアライザは、立上りエッジ入力ストローブを備えたシリアライザによって駆動することができます。

#### ピン配置

#### チップ情報

MAX9234 TRANSISTOR COUNT: 14,104 MAX9236 TRANSISTOR COUNT: 14,104 MAX9238 TRANSISTOR COUNT: 14,104

PROCESS: CMOS

#### パッケージ

(このデータシートに掲載されているパッケージ仕様は、最新版が反映されているとは限りません。最新のパッケージ情報は、japan.maxim-ic.com/packagesをご参照下さい。)

# マキシム・ジャパン株式会社

〒169-0051東京都新宿区西早稲田3-30-16(ホリゾン1ビル) TEL. (03)3232-6141 FAX. (03)3232-6149

マキシムは完全にマキシム製品に組込まれた回路以外の回路の使用について一切責任を負いかねます。回路特許ライセンスは明言されていません。マキシムは随時予告なく回路及び仕様を変更する権利を留保します。

14 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600