### 24ビット、2MSPS/500kSPSのSAR ADC

### 特長

#### ▶ 高性能

▶ スループット: 2MSPS (AD4030-24) または500kSPS (AD4032-24) のオプション

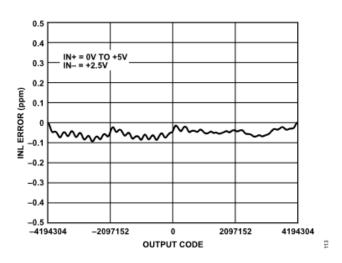

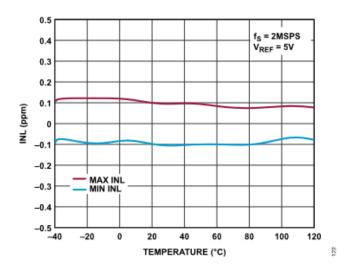

▶ INL: ±0.9ppm (最大値) (-40°C~+125°C)

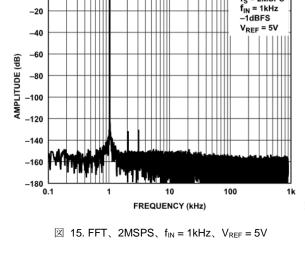

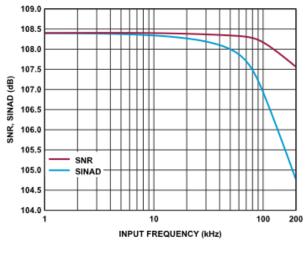

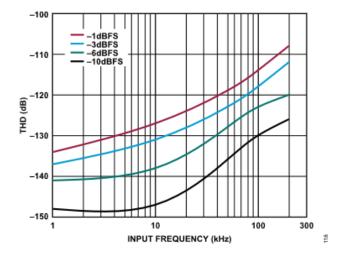

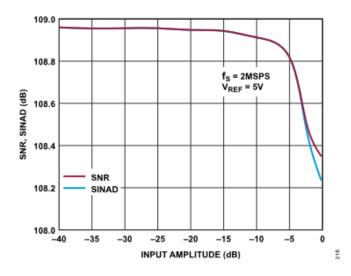

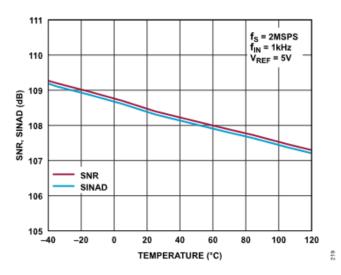

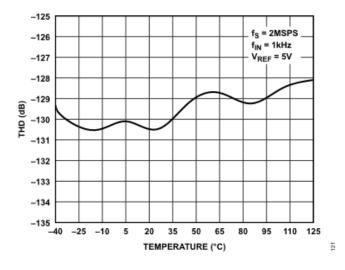

► S/N比: 108.4dB(代表值)► THD: -127dB(代表值)

▶ NSD: -169dBFS/Hz(代表値)

▶ 低消費電力

▶ 30mW (2MSPS時)

▶ 10mW (500kSPS時)

▶ 3mW (10kSPS時)

▶ Easy Drive™機能によるシステムの複雑さの軽減

▶ DC入力に対し1.2µAの低入力電流(2MSPS時)

▶ 広いコモンモード入力範囲: -(1/128) × V<sub>REF</sub>~ +(129/128) × V<sub>REF</sub>

▶ 柔軟な外部リファレンス電圧範囲: 4.096V~5V

▶ 2µFのバイパス・コンデンサを使用する高精度リファレンス・バッファを内蔵

▶プログラマブルなブロック平均化フィルタによる最大2<sup>16</sup>のデシメーション

▶ サンプリング分解能を30ビットに拡張

▶ オーバーレンジ・ビットおよび同期ビット

▶ Flexi-SPIデジタル・インターフェース

▶ 1、2、または4個のSDOレーンによりSCKの低速化が可能

▶ エコー・クロック・モードにより、デジタル・アイソレータが容易に使用可能

▶ 1.2V~1.8Vのロジックに対応

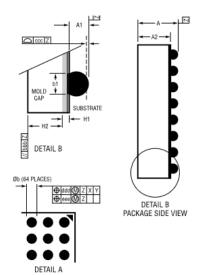

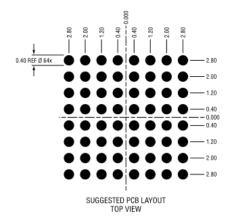

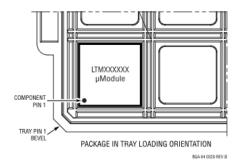

▶ 7mm x 7mmの64ボール CSP\_BGAパッケージに電源およびリファレンス・コンデンサを内蔵し、システム・フットプリントを低減

### アプリケーション

▶ ATE (自動試験装置)

▶ デジタル制御ループ

▶ 医療用計測機器

▶ 地震計測

▶ 半導体製造

▶ 科学計測器

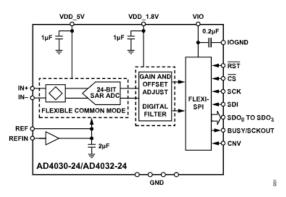

### 機能ブロック図

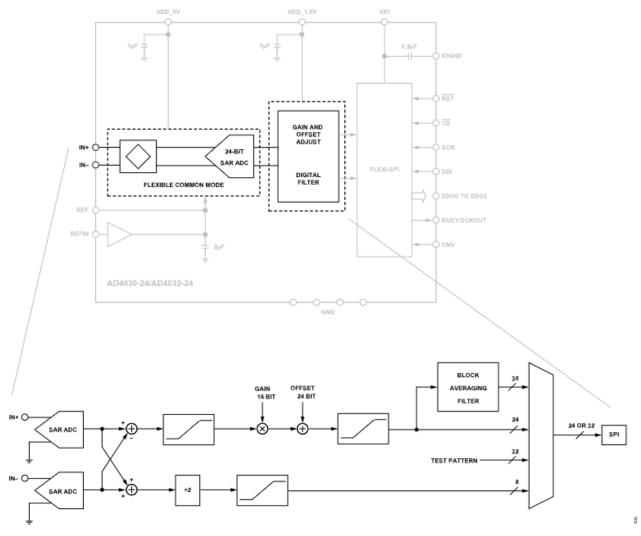

図 1. 機能ブロック図

### 概要

AD4030-24/AD4032-24は、Easy Drive™を備えた2MSPSまたは500kSPSの逐次比較レジスタ(SAR)A/Dコンバータ(ADC)です。最大±0.9ppmの積分非直線性(INL)と24ビットでのノー・ミス・コードが確保されたAD4030-24/AD4032-24は、 $-40^{\circ}$ Cで比類ない精度を実現します。AD4030-24/AD4032-24の機能アーキテクチャを図1に示します。

低ドリフト高精度のリファレンス・バッファが内蔵されているため、電圧リファレンスを他のシステム回路と容易に共有できます。5Vのリファレンスを使用する場合、AD4030-24/AD4032-24のダイナミック・レンジは109dB(代表値)です。低ノイズ・フロアであるため、シグナル・チェーンに必要なゲインや消費電力を下げることができます。デシメーション・レシオがプログラマブルなブロック平均化フィルタにより、ダイナミック・レンジを最大155.5dBまで増加させることができます。差動入力範囲とコモンモード電圧範囲が広いため、入力において±VREFの全範囲を飽和することなく使用でき、シグナル・コンディショニング条件とシステム・キャリブレーションを簡素化できます。Easy Driveアナログ入力ではセトリングが向上しているため、AD4030-24/AD4032-24に対応可能なアナログ・フロント・エンド部品の選択肢が広がります。シングルエンド信号と差動信号のどちらもサポートされています。

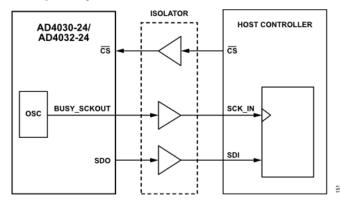

用途の広いFlexi-SPIシリアル・ペリフェラル・インターフェース (SPI) により、ホスト・プロセッサとADCの統合を容易に行うことができます。広いデータ・クロック・ウィンドウ、複数のSDOレーン、オプションのデュアル・データ・レート (DDR) データ・クロックにより、2MSPSまたは500kSPSのサンプリング・レートで動作しながら、シリアル・クロックを10MHzに下げることができます。エコー・クロック・モードとADCホスト・クロック・モードは、タイミング条件を緩和し、デジタル・アイソレータの使用を簡素化します。

AD4030-24/AD4032-24の7mm×7mm、64ボールCSP\_BGAパッケージには、重要な電源とリファレンス・バイパス・コンデンサがすべて搭載されているため、フットプリントとシステムの部品数を削減すると共に、ボード・レイアウトによる影響を軽減することができます。

#### Rev. A

文書に関するご意見

アナログ・デバイセズ社の提供する情報は、「そのままで」正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関しては一切の責任を負いません。仕様は予告なく変更される場合があります。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。本紙記載の商標および登録商標は、各社の所有に属します。

# 目次

| 特長                                | 1  | デバイスのリセット                    | 27              |

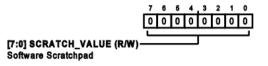

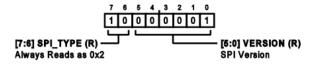

|-----------------------------------|----|------------------------------|-----------------|

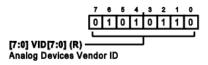

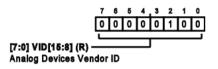

| アプリケーション                          | 1  | 電源                           | 27              |

| 機能ブロック図                           | 1  | シリアル・インターフェース                | 29              |

| 概要                                | 1  | SPI信号                        | 29              |

| 仕様                                | 4  | サンプル変換タイミングとデータ転送            | 31              |

| タイミング仕様                           | 6  | クロック・モード                     | 32              |

| 絶対最大定格                            | 12 | データ・クロック条件とタイミング             | 35              |

| 熱抵抗                               | 12 | レイアウトのガイドライン                 | 39              |

| 静電放電(ESD)定格                       | 12 | レジスタ                         | 40              |

| ESDに関する注意                         | 12 | レジスタの詳細                      | 41              |

| ピン配置およびピン機能の説明                    | 13 | インターフェース設定 <b>A</b> レジスタ     | 41              |

| 代表的な性能特性                          | 15 | インターフェース設定Bレジスタ              | 41              |

| 用語                                | 20 | デバイス設定レジスタ                   | 42              |

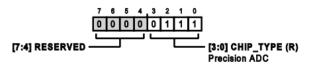

| 積分非直線性誤差(INL)                     | 20 | チップ・タイプ・レジスタ                 | 42              |

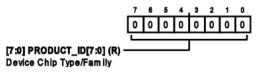

| 微分非直線性誤差(DNL)                     | 20 | 製品IDロー・レジスタ                  | 42              |

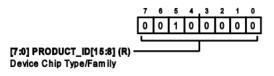

| ゼロ誤差( <b>ZE</b> )                 | 20 | 製品IDハイ・レジスタ                  | 42              |

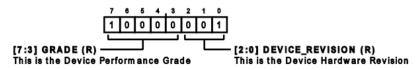

| ゲイン誤差( <b>GE</b> )                | 20 | チップ・グレード・レジスタ                | 43              |

| スプリアスフリー・ダイナミック・レンジ (SFDR)        | 20 | スクラッチ・パッド・レジスタ               | 43              |

| 有効ビット数( <b>ENOB</b> )             | 20 | SPIリビジョン・レジスタ                | 43              |

| 全高調波歪み(THD)                       | 20 | ベンダ <b> D</b> ロー・レジスタ        | 44              |

| ダイナミック・レンジ (DR)                   | 20 | ベンダ <b>ID</b> ハイ・レジスタ        | 44              |

| S/N比(SNR)                         | 20 | ストリーム・モード・レジスタ               | 44              |

| 信号/ノイズ+歪み(SINAD)比                 | 20 | インターフェース・ステータス <b>A</b> レジスタ | 44              |

| アパーチャ遅延                           | 20 | 設定モード終了レジスタ                  | 45              |

| 過渡応答                              | 20 | 平均化モード・レジスタ                  | 45              |

| 同相ノイズ除去比( <b>CMRR</b> )           | 20 | オフセット・レジスタ                   | 46              |

| 電源電圧変動除去比(PSRR)                   | 20 | ゲイン・レジスタ                     | 46              |

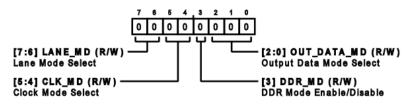

| 動作原理                              | 21 | モード・レジスタ                     | 47              |

| 概要                                | 21 | 内部発振器レジスタ                    | 47              |

| コンバータの動作                          | 21 | 出力ドライバ・レジスタ                  | 48              |

| 伝達関数                              | 22 | テスト・パターン・レジスタ                | 48              |

| アナログ機能                            | 22 | デジタル診断レジスタ                   | 49              |

| デジタル・サンプリング処理機能                   | 22 | デジタル誤差レジスタ                   | 49              |

| アプリケーション情報                        | 25 | 外形寸法                         | 50              |

| 代表的なアプリケーション図                     | 25 | オーダー・ガイド                     | 50              |

| アナログ・フロント・エンドの設計                  | 25 | 評価用ボード                       | 50              |

| リファレンス回路の設計                       | 25 |                              |                 |

|                                   |    |                              |                 |

| 改訂履歴                              |    |                              |                 |

| 2022年8月 Revision 0からRevision Aに改定 | :  |                              |                 |

| AD4032-24を追加                      |    |                              | 1               |

| 特長のセクション、図1、概要のセクションを変更           |    |                              | 1               |

| analog.com                        |    |                              | Rev. A   2 / 50 |

# AD4030-24/AD4032-24

| 表1を変更                    | 4  |

|--------------------------|----|

| 表2を変更                    | 6  |

| 表9を変更                    | 12 |

| 表11を変更                   | 13 |

| 図25のキャプションを変更            | 17 |

| 図26を追加。ナンバリング変更          | 17 |

| 図30のキャプション、図35を変更        | 18 |

| 図31を追加                   | 18 |

| 図36を追加                   | 19 |

| 概要のセクションを変更              | 21 |

| 図44、図45を変更               | 25 |

| 図46、リファレンス回路の設計のセクションを変更 | 26 |

| 図50を変更                   | 29 |

| 図54、図55を変更               | 33 |

| 表23を変更                   | 43 |

| 表28を変更                   | 44 |

| 表29を変更                   | 45 |

| 表38を変更                   | 48 |

| 外形寸法を更新                  | 50 |

| オーダー・ガイドを変更              | 50 |

## 2022年4月 Revision 0: 初版

## 仕様

特に指定のない限り、VDD\_5V = 5.4V、VDD\_1.8V = 1.8V、VIO = 1.8V、REFIN = 5V、入力コモンモード = 2.5V、 $f_S$  = 2MSPS(AD4030-24)または500kSPS(AD4032-24)、および全仕様は $T_{MIN} \sim T_{MAX}$ での値です。代表値は $T_A$  = 25°Cでの値です。

表 1.

| パラメータ                                        | テスト条件/コメント                                 | 最小値                         | 代表值     | 最大値                           | 単位     |

|----------------------------------------------|--------------------------------------------|-----------------------------|---------|-------------------------------|--------|

| RESOLUTION                                   |                                            | 24                          |         |                               | Bits   |

| ANALOG INPUT                                 |                                            |                             |         |                               |        |

| Voltage Range                                | $V_{IN}$ + - $V_{IN}$ -                    | -(65/64) × V <sub>REF</sub> |         | $+(65/64) \times V_{REF}$     | V      |

| Absolute Input Voltage                       | GNDを基準としたV <sub>IN</sub> +、V <sub>IN</sub> | -(1/128) × V <sub>REF</sub> |         | +(129/128) × V <sub>REF</sub> | V      |

| Common-Mode Input Range                      | (V <sub>IN</sub> + + V <sub>IN</sub> -)/2  | -(1/128) × V <sub>REF</sub> |         | +(129/128) × V <sub>REF</sub> | V      |

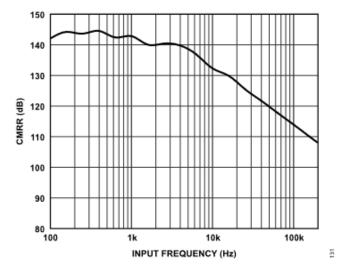

| Common-Mode Rejection Ratio (CMRR)           | f <sub>IN</sub> = 10kHz                    |                             | 132     |                               | dB     |

| Analog Input Current                         | アクイジション・フェーズ、T = 25°C                      |                             | 0.8     |                               | nA     |

|                                              | DC入力を2MSPSで変換                              |                             | 1.2     |                               | μΑ     |

| Analog Input Capacitance                     | アクイジション・フェーズ                               |                             | 120     |                               | pF     |

|                                              | アクイジション・フェーズ (C <sub>PIN</sub> )           |                             | 4       |                               | pF     |

| THROUGHPUT                                   |                                            |                             |         |                               |        |

| Complete Cycle                               |                                            |                             |         |                               |        |

| AD4030-24                                    |                                            | 500                         |         |                               | ns     |

| AD4032-24                                    |                                            | 2000                        |         |                               | ns     |

| Conversion Time                              |                                            | 264                         | 282     | 300                           | ns     |

| Acquisition Phase <sup>1</sup>               |                                            |                             |         |                               |        |

| AD4030-24                                    |                                            | 244                         | 260     | 275                           | ns     |

| AD4032-24                                    |                                            | 1744                        | 1760    | 1775                          | ns     |

| Throughput Rate                              |                                            |                             |         |                               |        |

| AD4030-24                                    |                                            | 0                           |         | 2                             | MSPS   |

| AD4032-24                                    |                                            | 0                           |         | 500                           | kSPS   |

| DC ACCURACY                                  |                                            |                             |         |                               |        |

| No Missing Codes                             |                                            | 24                          |         |                               | Bits   |

| Integral Nonlinearity Error (INL)            |                                            | -0.9                        | ±0.1    | +0.9                          | ppm    |

| Differential Nonlinearity Error (DNL)        |                                            |                             | ±0.5    |                               | LSB    |

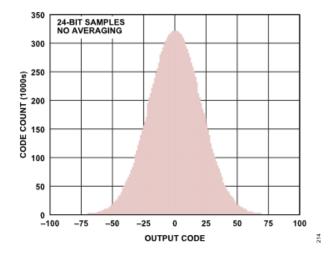

| Transition Noise                             |                                            |                             | 21      |                               | LSB rm |

| Zero Error                                   |                                            | -90                         | 0       | +90                           | μV     |

| Zero Error Drift                             |                                            |                             | ±0.007  |                               | ppm/°C |

| Gain Error                                   | バッファをディスエーブル、REF = 5V                      | -0.004                      | ±0.0002 | +0.004                        | %FS    |

|                                              | バッファをイネーブル、REFIN = 5V                      | -0.008                      | ±0.0006 | +0.008                        | %FS    |

| Gain Error Temperature Drift                 | バッファをディスエーブル、REF = 5V                      |                             | ±0.025  |                               | ppm/°C |

|                                              | バッファをイネーブル、REFIN = 5V                      |                             | ±0.07   |                               | ppm/°C |

| Power Supply Sensitivity                     | VDD_5V = 5.4V ± 0.1V                       |                             | ±0.1    |                               | ppm    |

|                                              | VDD_1.8V = 1.8V ± 5%                       |                             | ±0.2    |                               | ppm    |

| Low Frequency Noise <sup>2</sup>             | 带域幅 = 0.1Hz~10Hz                           |                             | 1.3     |                               | μV p-p |

| AC ACCURACY                                  |                                            |                             |         |                               |        |

| Dynamic Range                                |                                            |                             | 109     |                               | dB     |

| Noise Spectral Density (NSD)                 |                                            |                             | -169    |                               | dBFS/F |

| Total RMS Noise                              |                                            |                             | 12.5    |                               | μV rms |

| Signal-to-Noise Ratio (SNR)                  | f <sub>IN</sub> = 1kHz、−0.5dBFS            | 105.6                       | 108.4   |                               | dB     |

| Spurious-Free Dynamic Range (SFDR)           | f <sub>IN</sub> = 1kHz、−0.5dBFS            |                             | 127     |                               | dB     |

| Total Harmonic Distortion (THD)              | f <sub>IN</sub> = 1kHz、−0.5dBFS            |                             | -127    | <b>−</b> 115                  | dB     |

| Signal-to-Noise-and-Distortion (SINAD) Ratio | f <sub>IN</sub> = 1kHz、−0.5dBFS            | 105.6                       | 108.3   |                               | dB     |

| Oversampled Dynamic Range                    | 平均化 = 2                                    |                             | 112     |                               | dB     |

|                                              | 平均化 = 256                                  |                             | 133     |                               | dB     |

analog.com Rev. A | 4 / 50

| パラメータ                                  | テスト条件/コメント                                                                               | 最小値               | 代表値   | 最大値         | 単位     |

|----------------------------------------|------------------------------------------------------------------------------------------|-------------------|-------|-------------|--------|

|                                        | 平均化 = 65536                                                                              |                   | 155.5 |             | dB     |

| SNR                                    | $VDD_{5}V = 5.0V$ , $f_{IN} = 1kHz$ , $-0.5dBFS$ , $REFIN = 4.096V$                      |                   | 106.7 |             | dB     |

| SFDR                                   | $VDD_5V = 5.0V$ , $f_{1N} = 1kHz$ , $-0.5dBFS$ ,                                         |                   | 130   |             | dB     |

| THD                                    | REFIN = $4.096V$<br>VDD_5V = $5.0V$ , $f_{IN} = 1kHz$ , $-0.5dBFS$ ,                     |                   | -130  |             | dB     |

| SINAD                                  | REFIN = $4.096V$<br>VDD_5V = $5.0V$ , $f_{IN} = 1kHz$ , $-0.5dBFS$ ,<br>REFIN = $4.096V$ |                   | 106.7 |             | dB     |

| SNR                                    | f <sub>IN</sub> = 100kHz、-0.5dBFS                                                        |                   | 108.1 |             | dB     |

| THD                                    | f <sub>IN</sub> = 100kHz、−0.5dBFS                                                        |                   | -113  |             | dB     |

| SINAD                                  | f <sub>IN</sub> = 100kHz、-0.5dBFS                                                        |                   | 106.9 |             | dB     |

| −3 dB Input Bandwidth                  | ·                                                                                        |                   | 74    |             | MHz    |

| Aperture Delay                         |                                                                                          |                   | 0.7   |             | ns     |

| Aperture Jitter                        |                                                                                          |                   | 1.4   |             | ps rms |

| INTERNAL REFERENCE BUFFER              | 外部リファレンスがREFINを駆動                                                                        |                   |       |             |        |

| REFIN Voltage Range                    | 5.3V ≤ VDD 5V ≤ 5.5V                                                                     | 4.95              | 5     | 5.05        | V      |

|                                        | 4.8V ≤ VDD 5V ≤ 5.25V                                                                    |                   | 4.5   |             | V      |

|                                        | 4.75V ≤ VDD_5V ≤ 5.25V                                                                   | 4.046             | 4.096 | 4.146       | V      |

| REFIN Bias Current                     |                                                                                          | -50               | 5     | +50         | nA     |

| REFIN Input Capacitance                |                                                                                          |                   | 40    |             | pF     |

| Reference Buffer Offset Error          | REFIN = $5V$ , $T_A = 25$ °C                                                             | -100              | ±25   | +100        | μV     |

|                                        | REFIN = 4.5V, T <sub>A</sub> = 25°C                                                      |                   | ±25   |             | μV     |

|                                        | REFIN = 4.096V, T <sub>A</sub> = 25°C                                                    | -100              | ±25   | +100        | μV     |

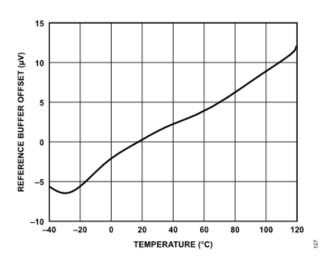

| Reference Buffer Offset Drift          |                                                                                          |                   | ±0.3  |             | μV/°C  |

| Power-On Settling Time                 |                                                                                          |                   | 3     |             | ms     |

| EXTERNALLY OVERDRIVEN REFERENCE        | 外部リファレンスがREFを駆動(REFIN =                                                                  |                   |       |             |        |

|                                        | 0)                                                                                       |                   |       |             |        |

| REF Voltage Range                      | 5.3V ≤ VDD_5V ≤ 5.5V                                                                     | 4.95              | 5     | 5.05        | V      |

|                                        | 4.8V ≤ VDD_5V ≤ 5.25V                                                                    |                   | 4.5   |             | V      |

|                                        | 4.75V ≤ VDD_5V ≤ 5.25V                                                                   | 4.046             | 4.096 | 4.146       | V      |

| REF Current                            |                                                                                          |                   |       |             |        |

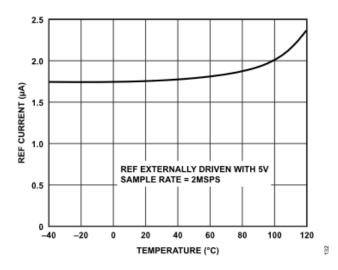

| AD4030-24                              | fS = 2MSPS                                                                               |                   | 1.8   |             | μΑ     |

| AD4032-24                              | fS = 500kSPS                                                                             |                   | 0.5   |             | μA     |

| REF Input Capacitance                  |                                                                                          |                   | 2     |             | μF     |

| DIGITAL INPUTS                         | 1.14V ≤ VIO ≤ 1.89V                                                                      |                   |       |             |        |

| Logic Levels                           |                                                                                          |                   |       |             |        |

| Input Voltage Low (V <sub>IL</sub> )   |                                                                                          | -0.3              |       | +0.35 × VIO | V      |

| Input Voltage High (V <sub>IH</sub> )  |                                                                                          | 0.65 × VIO        |       | VIO + 0.3   | V      |

| Input Current Low (I∟)                 |                                                                                          | -10               |       | +10         | μA     |

| Input Current High (I <sub>IH</sub> )  |                                                                                          | -10               |       | +10         | μA     |

| Input Pin Capacitance                  |                                                                                          |                   | 2     |             | pF     |

| DIGITAL OUTPUTS                        | 1.14V ≤ VIO ≤ 1.89V                                                                      | Conversion        |       |             |        |

|                                        |                                                                                          | results available |       |             |        |

|                                        |                                                                                          | immediately       |       |             |        |

|                                        |                                                                                          | after completed   |       |             |        |

|                                        |                                                                                          | conversion        |       |             |        |

| Pipeline Delay                         |                                                                                          |                   |       |             |        |

| Output Voltage Low (V <sub>OL</sub> )  | I <sub>SINK</sub> = 2mA                                                                  |                   |       | 0.25 × VIO  | V      |

| Output Voltage High (V <sub>OH</sub> ) | Isource = 2mA                                                                            | 0.75 × VIO        |       |             | V      |

analog.com Rev. A | 5 / 50

| パラメータ                        | テスト条件/コメント                         | 最小値  | 代表值  | 最大値  | 単位 |

|------------------------------|------------------------------------|------|------|------|----|

| POWER SUPPLIES               |                                    |      |      |      |    |

| VDD_5V                       | REF = 5V                           | 5.3  | 5.4  | 5.5  | V  |

|                              | REF = 4.5V                         | 4.8  | 5    | 5.25 | V  |

|                              | REF = 4.096V                       | 4.75 | 5    | 5.25 | V  |

| VDD_1.8V                     |                                    | 1.71 | 1.8  | 1.89 | V  |

| VIO <sup>3</sup>             |                                    | 1.14 |      | 1.89 | V  |

| Standby Current              |                                    |      |      |      |    |

| VDD_5V                       |                                    |      | 500  |      | μA |

| VDD_1.8V                     |                                    |      | 90   |      | μA |

| VIO                          |                                    |      | < 1  |      | μA |

| Shutdown Current             |                                    |      |      |      |    |

| VDD_5V                       |                                    |      | 5    |      | μA |

| VDD_1.8V                     |                                    |      | 5    |      | μA |

| VIO                          |                                    |      | < 1  |      | μA |

| Operating Current, AD4030-24 | 2MSPS                              |      |      |      |    |

| VDD_5V                       | VDD_5V = 5.4V                      |      | 2.7  | 3.2  | mA |

| VDD_1.8V                     | VDD_1.8V = 1.8V                    |      | 8.2  | 11.2 | mA |

| VIO                          | VIO = 1.8V、1レーンSDO                 |      | 0.6  |      | mA |

| Operating Current, AD4032-24 | 500kSPS                            |      |      |      |    |

| VDD_5V                       | VDD_5V = 5.4V                      |      | 1.1  | 1.5  | mA |

| VDD_1.8V                     | VDD_1.8V = 1.8V                    |      | 2.1  | 3.1  | mA |

| VIO                          | VIO = 1.8V、1レーンSDO                 |      | 0.15 |      | mA |

| Power Dissipation            | 2MSPS                              |      | 30   | 39   | mW |

|                              | 500kSPS                            |      | 10   | 14.2 | mW |

| treset_delay                 | パワーオン後、VDD_5VおよびVDD_1.8V           | 3    |      |      | ms |

|                              | が有効になってから RST がアサートされ              |      |      |      |    |

|                              | るまでの遅延                             |      |      |      |    |

| treset_pw                    | RST のパルス幅                          | 50   |      |      | ns |

| TEMPERATURE RANGE            |                                    |      |      |      |    |

| Specified Performance        | T <sub>MIN</sub> ~T <sub>MAX</sub> | -40  |      | +125 | °C |

<sup>1</sup> アクイジション・フェーズとは、AD4030-24では2MSPS、AD4032-24では500kSPSのスループット・レートで動作しているときに、入力サンプリング・コンデンサが新規の入力値を取得するために使用できる時間です。

### タイミング仕様

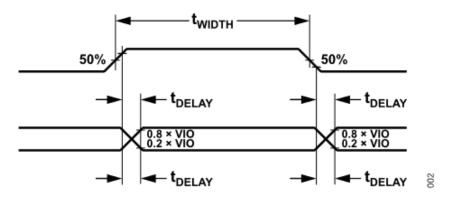

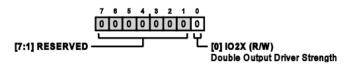

特に指定のない限り、VDD\_5V = 5.4V、VDD\_1.8V = 1.8V、VIO = 1.8V、REFIN = 5V、入力コモンモード = 2.5V、 $f_S$  = 2MSPS(AD4030-24)または500kSPS(AD4032-24)、および全仕様は $T_{MIN} \sim T_{MAX}$ での値です。代表値は $T_A$  = 25°Cでの値です。タイミング電圧レベルについては図2を参照してください。VIO < 1.4Vの場合、ビットIO2Xを1に設定する必要があります。

#### 表 2. デジタル・タイミング・インターフェース

| パラメータ1                                             | 記号                | 最小値  | 代表值  | 最大値  | 単位 |

|----------------------------------------------------|-------------------|------|------|------|----|

| Conversion Time: CNV Rising Edge to Data Available | t <sub>CONV</sub> | 264  | 282  | 300  | ns |

| Acquisition Phase <sup>2</sup>                     | t <sub>ACQ</sub>  |      |      |      |    |

| AD4030-24                                          |                   | 244  | 260  | 275  | ns |

| AD4032-24                                          |                   | 1744 | 1760 | 1775 | ns |

| Time Between Conversions                           | tcyc              |      |      |      |    |

| AD4030-24                                          |                   | 500  |      |      | ns |

| AD4032-24                                          |                   | 2000 |      |      | ns |

analog.com Rev. A | 6 / 50

<sup>2</sup> 図24の低周波数ノイズ・プロットを参照してください。1/fノイズは、オートゼロ機能により内部で打ち消されます。ノイズ・スペクトル密度は、DC~fs/2の範囲で実質的に一定です。

<sup>3</sup> VIO < 1.4Vの場合、ビットIO2Xを1に設定する必要があります。出力ドライバ・レジスタのセクションを参照してください。

| CNV High Time                 | tcnvh             | 10   |    |      | ns  |

|-------------------------------|-------------------|------|----|------|-----|

| CNV Low Time                  | t <sub>CNVL</sub> | 20   |    |      | ns  |

| Internal Oscillator Frequency | fosc              | 75.1 | 80 | 84.7 | MHz |

- 1 タイミング仕様は、デジタル出力ピンでの負荷容量が5pFであると仮定しています。tconv、tcyc、tscκ、tscκoutは出荷テスト済みです。 それ以外のタイミング仕様 は特性評価および設計により確保されています。

- 2 アクイジション・フェーズとは、AD4030-24では2MSPS、AD4032-24では500kSPSのスループット・レートで動作しているときに、入力サンプリング・コンデン サが新規の入力値を取得するために使用できる時間です。

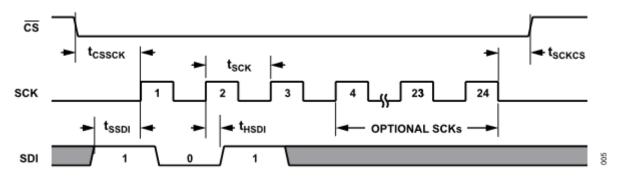

図 2. タイミングの電圧レベル

#### 表 3. レジスタの読出しと書込みのタイミング

| パラメータ                                    | 記号                 | 最小値  | 代表值 | 最大値  | 単位 |

|------------------------------------------|--------------------|------|-----|------|----|

| CS Pulse Width                           | tcspw              | 10   |     |      | ns |

| SCK Period                               | tsck               |      |     |      |    |

| VIO > 1.71 V                             |                    | 11.6 |     |      | ns |

| VIO > 1.14 V                             |                    | 12.3 |     |      | ns |

| SCK Low Time                             | t <sub>SCKL</sub>  | 5.2  |     |      | ns |

| SCK High Time                            | t <sub>SCKH</sub>  | 5.2  |     |      | ns |

| SCK Falling Edge to Data Remains Valid   | thspo              | 2.1  |     |      | ns |

| SCK Falling Edge to Data Valid Delay     | tospo              |      |     |      |    |

| VIO > 1.71 V                             |                    |      |     | 9.4  | ns |

| VIO > 1.14 V                             |                    |      |     | 11.8 | ns |

| CS Rising Edge to SDO High Impedance     | t <sub>CSDIS</sub> |      |     | 9    | ns |

| SDI Valid Setup Time to SCK Rising Edge  | tssdi              | 1.5  |     |      | ns |

| SDI Valid Hold Time from SCK Rising Edge | thsdi              | 1.5  |     |      | ns |

| CS Falling Edge to First SCK Rising Edge | tcssck             |      |     |      |    |

| VIO > 1.71 V                             |                    | 11.6 |     |      | ns |

| VIO > 1.14 V                             |                    | 12.3 |     |      | ns |

| Last SCK Edge to CS Rising Edge          | tsckcs             | 5.2  |     |      | ns |

analog.com Rev. A | 7 / 50

SD00 \_\_\_\_\_\_\_ | Hi-Z

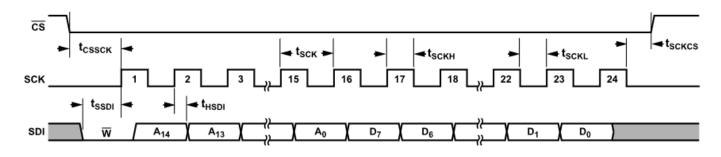

図 3. レジスタ設定モードの書込みタイミング

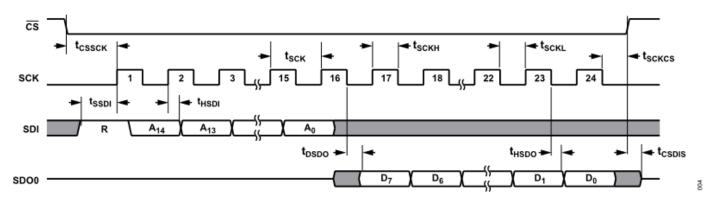

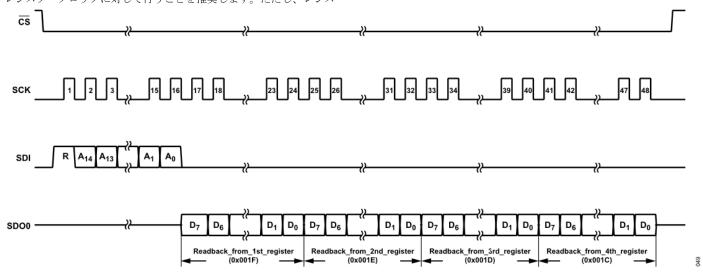

図 4. レジスタ設定モードの読出しタイミング

図 5. レジスタ設定モードのコマンド・タイミング

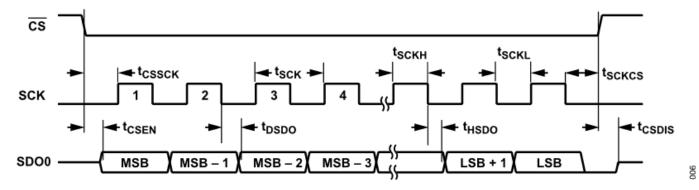

#### 表 4. SPI互換モードのタイミング

| パラメータ                                  | 記号                | 最小値  | 代表值 | 最大値 | 単位 |

|----------------------------------------|-------------------|------|-----|-----|----|

| SCK Period                             | tscк              |      |     |     |    |

| VIO > 1.71 V                           |                   | 9.8  |     |     | ns |

| VIO > 1.14 V                           |                   | 12.3 |     |     | ns |

| SCK Low Time                           | tsckl             |      |     |     |    |

| VIO > 1.71 V                           |                   | 4.2  |     |     | ns |

| VIO > 1.14 V                           |                   | 5.2  |     |     | ns |

| SCK High Time                          | tscкн             |      |     |     |    |

| VIO > 1.71 V                           |                   | 4.2  |     |     | ns |

| VIO > 1.14 V                           |                   | 5.2  |     |     | ns |

| SCK Falling Edge to Data Remains Valid | thspo             | 1.4  |     |     | ns |

| SCK Falling Edge to Data Valid Delay   | t <sub>DSDO</sub> |      |     |     |    |

| VIO > 1.71 V                           |                   |      |     | 5.6 | ns |

| VIO > 1.14 V                           |                   |      |     | 8.1 | ns |

analog.com Rev. A | 8 / 50

| CS Falling Edge to SDO Valid             | tcsen              |      |     | ns |

|------------------------------------------|--------------------|------|-----|----|

| VIO > 1.71 V                             |                    |      | 6.8 | ns |

| VIO > 1.14 V                             |                    |      | 9.3 | ns |

| CS Falling Edge to First SCK Rising Edge | tcsscĸ             |      |     |    |

| VIO > 1.71 V                             |                    | 9.8  |     | ns |

| VIO > 1.14 V                             |                    | 12.3 |     | ns |

| Last SCK Edge to CS Rising Edge          | t <sub>SCKCS</sub> | 4.2  |     | ns |

| CS Rising Edge to SDO High Impedance     | t <sub>CSDIS</sub> |      | 9   | ns |

| CS Falling Edge to BUSY Rising Edge      | tcsbusy            | 6    |     | ns |

図 6. SPIクロック・モードの1レーンSDRのタイミング

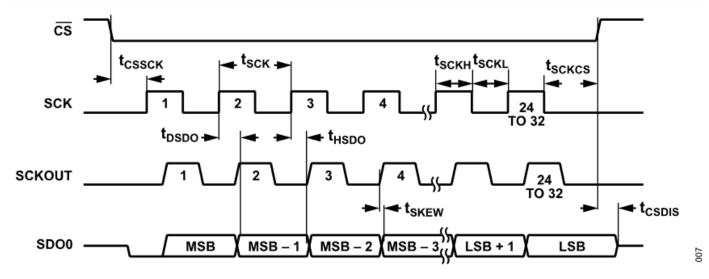

### 表 5. エコー・クロック・モードのタイミング、SDR、1レーン

| パラメータ                                        | 記号                                    | 最小値  | 代表值 | 最大値  | 単位 |

|----------------------------------------------|---------------------------------------|------|-----|------|----|

| SCK Period                                   | t <sub>scк</sub>                      |      |     |      |    |

| VIO > 1.71 V                                 |                                       | 9.8  |     |      | ns |

| VIO > 1.14 V                                 |                                       | 12.3 |     |      | ns |

| SCK Low Time, SCK High Time                  | t <sub>SCKL</sub> , t <sub>SCKH</sub> |      |     |      |    |

| VIO > 1.71 V                                 |                                       | 4.2  |     |      | ns |

| VIO > 1.14 V                                 |                                       | 5.2  |     |      | ns |

| SCK Rising Edge to Data/SCKOUT Remains Valid | t <sub>HSDO</sub>                     | 1.1  |     |      | ns |

| SCK Rising Edge to Data/SCKOUT Valid Delay   | tospo                                 |      |     |      |    |

| VIO > 1.71 V                                 |                                       |      |     | 5.6  | ns |

| VIO > 1.14 V                                 |                                       |      |     | 8.1  | ns |

| CS Falling Edge to First SCK Rising Edge     | tcsscк                                |      |     |      |    |

| VIO > 1.71 V                                 |                                       | 9.8  |     |      | ns |

| VIO > 1.14 V                                 |                                       | 12.3 |     |      | ns |

| Skew Between Data and SCKOUT                 | t <sub>SKEW</sub>                     | -0.4 | 0   | +0.4 | ns |

| Last SCK Edge to CS Rising Edge              | tsckcs                                | 4.2  |     |      | ns |

| CS Rising Edge to SDO High Impedance         | tcspis                                |      |     | 9    | ns |

analog.com Rev. A | 9 / 50

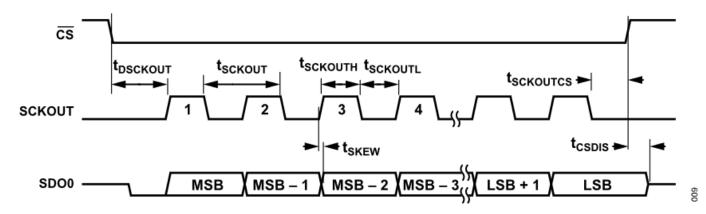

図 7. エコー・クロック・モードのタイミング、SDR、1レーン

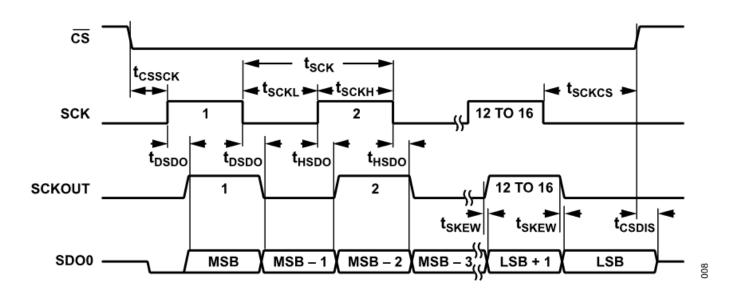

表 6. エコー・クロック・モードのタイミング、DDR、1レーン

| パラメータ                                    | 記号                 | 最小値    | 代表値 | 最大値  | 単位 |

|------------------------------------------|--------------------|--------|-----|------|----|

| SCK Period                               | tscк               | 12.3   |     |      | ns |

| SCK Low Time, SCK High Time              | tsckl, tsc         | кн 5.2 |     |      | ns |

| SCK Edge to Data/SCKOUT Remains Valid    | t <sub>HSDO</sub>  | 1.1    |     |      | ns |

| SCK Edge to Data/SCKOUT Valid Delay      | t <sub>DSDO</sub>  |        |     |      |    |

| VIO > 1.71 V                             |                    |        |     | 6.2  | ns |

| VIO > 1.14 V                             |                    |        |     | 8.7  | ns |

| CS Falling Edge to First SCK Rising Edge | tcssck             | 12.3   |     |      | ns |

| Skew Between Data and SCKOUT             | tskew              | -0.4   | 0   | +0.4 | ns |

| Last SCK Edge to CS Rising Edge          | tsckcs             | 9      |     |      | ns |

| CS Rising Edge to SDO High Impedance     | t <sub>CSDIS</sub> |        |     | 9    | ns |

図 8. エコー・クロック・モードのタイミング、DDR、1レーン

analog.com Rev. A | 10 / 50

### 表 7. ホスト・クロック・モードのタイミング

| パラメータ                                       | 記号        | 最小値                        | 代表値  | 最大値                      | 単位 |

|---------------------------------------------|-----------|----------------------------|------|--------------------------|----|

| SCK Period                                  | tscкоит   |                            |      |                          |    |

| OSC_DIV = No Divide                         |           | 11.8                       | 12.5 | 13.3                     | ns |

| OSC_DIV = Divide by 2                       |           | 23.6                       | 25   | 26.6                     | ns |

| OSC_DIV = Divide by 4                       |           | 47.4                       | 50   | 53.2                     | ns |

| SCK Low Time                                | tsckoutl  | 0.45 × t <sub>SCKOUT</sub> |      | $0.55 \times t_{SCKOUT}$ | ns |

| SCK High Time                               | tscкоитн  | 0.45 × t <sub>SCKOUT</sub> |      | $0.55 \times t_{SCKOUT}$ | ns |

| CS Falling Edge to First SCKOUT Rising Edge | tosckout  |                            |      |                          |    |

| VIO > 1.71 V                                |           | 10                         | 13.6 | 19                       | ns |

| VIO > 1.14 V                                |           | 10                         | 15   | 21                       | ns |

| Skew Between Data and SCKOUT                | tskew     | -0.4                       | 0    | +0.4                     | ns |

| Last SCKOUT Edge to CS Rising Edge          | tsckoutcs | 5.2                        |      |                          | ns |

| CS Rising Edge to SDO High Impedance        | tcspis    |                            |      | 9                        | ns |

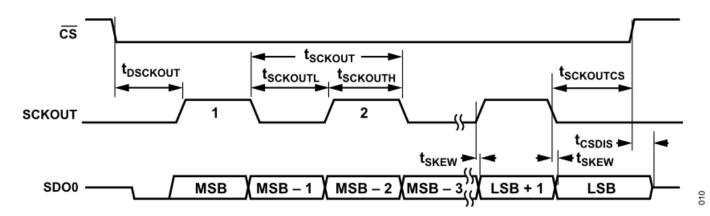

図 9. ホスト・クロック・モードのタイミング、SDR、1レーン

図 10. ホスト・クロック・モードのタイミング、DDR、1レーン

### 絶対最大定格

#### 表 8.

| パラメータ                                | 定格                       |

|--------------------------------------|--------------------------|

| Analog Inputs                        |                          |

| IN+, IN−, REFIN to GND               | -0.3 V to VDD_5V + 0.3 V |

| Supply Voltage                       |                          |

| VDD_5V, REF to GND                   | -0.3 V to +6.0 V         |

| VDD_1.8V, VIO to GND                 | -0.3 V to +2.1 V         |

| Digital Inputs to GND                | -0.3 V to VIO + 0.3 V    |

| CNV to GND                           | -0.3 V to VIO + 0.3 V    |

| Digital Outputs to GND               | -0.3 V to VIO + 0.3 V    |

| Storage Temperature Range            | −55°C to +150°C          |

| Operating Junction Temperature Range | -40°C to +125°C          |

| Maximum Reflow (Package Body)        | 260°C                    |

| Temperature                          |                          |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与える可能性があります。この仕様規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCBの熱設計には、細心の注意を払う必要があります。

#### 表 9. 熱抵抗

| パッケージ・タイプ  | θja | θις | 単位   |

|------------|-----|-----|------|

| 05-08-1797 | 35  | 16  | °C/W |

### 静電放電(ESD)定格

以下のESD情報は、ESDに敏感なデバイスを取り扱うために示したものですが、対象はESD保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001準拠の人体モデル(HBM)。

ANSI/ESDA/JEDEC JS-002準拠の電界誘起帯電デバイス・モデル (FICDM)。

#### AD4030-24/AD4032-24のESD定格

#### 表 10. AD4030-24/AD4032-24、64ポールCSP\_BGA

| ESDモデル | 耐久閾値(kV) | クラス |

|--------|----------|-----|

| НВМ    | 4        | 3A  |

| FICDM  | 1.25     | C3  |

### ESDに関する注意

ESD (静電気放電)に敏感なデバイスです。帯電したデバイスおよび回路基板は、検出されることなく放電されることがあります。この製品は特許取得済みまたは独自の保護回路を備えていますが、高エネルギーESDにさらされるとデバイスに損傷が生じる可能性があります。したがって、性能低下や機能低下を避けるために、適切なESD予防措置を講じる必要があります。

analog.com Rev. A | 12 / 50

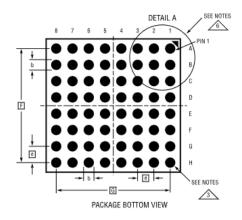

## ピン配置およびピン機能の説明

|   |              |            |          |            | Scale)     |            |                   |                |

|---|--------------|------------|----------|------------|------------|------------|-------------------|----------------|

|   | 1            | 2          | 3        | 4          | 5          | 6          | 7                 | 8              |

| A | <b>F</b> GND | REFIN      | VDD_5V   | GND        | GND        | CNV        | RST               | VIO            |

|   | $\bigcirc$   | (_)        | (_)      | (_)        | (_)        | $\bigcirc$ | $\langle \rangle$ | (_)            |

| В | IN+          | GND        | VDD_5V   | GND        | GND        | IOGND      | IOGND             | VIO            |

|   | 0            | 0          | Ü        | 0          | $\circ$    | ( )        |                   | $\circ$        |

| С | in-          | GND        | GND      | GND        | GND        | IOGND      | SD03              | SDO1           |

| D | GND          | REF        | REF      | GND        | GND        | IOGND      | SDO2              | SDO0           |

| E | GND<br>(_)   | REF<br>(_) | REF      | GND<br>(_) | GND<br>(_) | IOGND      | IOGND             | BUSY<br>SCKOUT |

| F | NIC          | GND        | GND      | GND        | GND        | IOGND      | DNC               | DNC            |

| G | NIC          | GND        | VDD_1.8V | GND        | GND        | IOGND      | DNC               | DNC            |

| н | GND          | GND        | VDD_1.8V | GND        | CS<br>(_)  | SDI        | SCK               | IOGND          |

AD4030-24/AD4032-24

- NOTES

1. NIC = NOT INTERNALLY CONNECTED. THESE PINS ARE NOT CONNECTED INTERNALLY.

2. DNC = DO NOT CONNECT TO THESE PINS. THEY ARE INTERNALLY CONNECTED TO DIGITAL OUTPUT DRIVERS IN HIGH-Z MODE.

3. NIC = NOT INTERNALLY CONNECTED. THESE PINS ARE NOT CONNECTED INTERNALLY.

図 11. ピン配置

表 11. ピン機能の説明

| ピン番号                           | 記号     | タイプ1 | 説明                                                                                    |

|--------------------------------|--------|------|---------------------------------------------------------------------------------------|

| A1, A4, A5, B2, B4, B5, C2 to  | GND    | Р    | 電源グラウンド。                                                                              |

| C5, D1, D4, D5, E1, E4, E5, F2 |        |      |                                                                                       |

| to F5, G2, G4, G5, H1, H2, H4  |        |      |                                                                                       |

| A2                             | REFIN  | Al   | バッファ付きリファレンス入力。内部リファレンス・バッファとして用いる場合、REFINは                                           |

|                                |        |      | 4.096V~5V(グラウンド基準)で駆動します。リファレンス・バッファをディスエーブルするには、REFINをグラウンドに接続し、REFを4.096V~5Vで駆動します。 |

| A3, B3                         | VDD_5V | Р    | 5V電源。VDD_5Vの範囲はリファレンスの値によって異なり、5Vのリファレンスの場合は5.3V                                      |

|                                |        |      | ~5.5V、4.096Vのリファレンスの場合は4.75V~5.25Vです。このピンにはパッケージ内に1µFのバイパス・コンデンサがあります。                |

| A6                             | CNV    | DI   | 変換入力。この入力の立上がりエッジによってデバイスが起動し、変換が開始されます。ADC                                           |

|                                |        |      | の仕様規定された性能を実現するには、この信号が低ジッタであることが必要です。ロジッ                                             |

|                                |        |      | ク・レベルはVIOピンによって決まります。                                                                 |

| A7                             | RST    | DI   | リセット入力(アクティブ・ロー)。非同期デバイス・リセット。                                                        |

| A8, B8                         | VIO    | Р    | 入出力インターフェースのデジタル電源。形式上、このピンはホスト・インターフェースと同                                            |

|                                |        |      | じ電源(1.8V、1.5V、または1.2V)です。このピンにはパッケージ内に0.2μFのバイパス・コン                                   |

|                                |        |      | デンサがあります。VIO < 1.4Vの場合、出力ドライバ・レジスタのビットIO2Xを1に設定する。                                    |

|                                |        |      | 要があります。                                                                               |

| B1                             | IN+    | Al   | 正のアナログ入力。                                                                             |

| B6, B7, C6, D6, E6, E7, F6,    | IOGND  | Р    | VIOグラウンド。すべてのGNDピンと同じグランド・プレーンに接続します。                                                 |

| G6, H8                         |        |      |                                                                                       |

| C1                             | IN-    | Al   | 負のアナログ入力。                                                                             |

| C7                             | SDO3   | DO   | シリアル・データ出力。変換結果はこのピンに出力されます。SCKに同期されます。                                               |

| C8                             | SDO1   | DO   | シリアル・データ出力。変換結果はこのピンに出力されます。SCKに同期されます。                                               |

| D2, D3, E2, E3                 | REF    | AI   | オプションのバッファなしリファレンス入力REFは4.096V~5V(グラウンド基準)で駆動しま                                       |

|                                |        |      | す。このピンにはパッケージ内に2µFのバイパス・コンデンサがあります。内部リファレンス                                           |

|                                |        |      | バッファを用いる場合は、REFを接続しないでください。                                                           |

Rev. A | 13 / 50 analog.com

| ピン番号           | 記号          | タイプ¹ | 説明                                                                                                                                                                           |

|----------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7             | SDO2        | DO   | シリアル・データ出力。変換結果はこのピンに出力されます。SCKに同期されます。                                                                                                                                      |

| D8             | SDO0        | DO   | シリアル・データ出力。変換結果はこのピンに出力されます。SCKに同期されます。                                                                                                                                      |

| E8             | BUSY_SCKOUT | DO   | SPIクロック・モードではBUSYインジケータ。このピンは、新たな変換の開始時にハイとなり、変換が終了するとローになります。ロジック・レベルはVIOピンによって決まります。<br>SCKOUTがイネーブルされている場合、このピン機能は、ホスト・コントローラから入力されるSCKのエコー、または内部発振器から送られるクロックのどちらかになります。 |

| F1             | NIC         |      | 内部では未接続。これらのピンは、内部で接続されません。                                                                                                                                                  |

| F7, F8, G7, G8 | DNC         |      | これらのピンには接続しないでください。高インピーダンス・モードの場合、これらはデジタ<br>ル出カドライバに内部で接続されます。                                                                                                             |

| G1             | NIC         |      | 内部では未接続。これらのピンは、内部で接続されません。                                                                                                                                                  |

| G3, H3         | VDD_1.8V    | Р    | 1.8V電源。VDD_1.8Vの範囲は1.71V~1.89Vです。このピンにはパッケージ内に1μFのバイパス・コンデンサがあります。                                                                                                           |

| H5             | CS          | DI   | チップ・セレクト入力(アクティブ・ロー)。                                                                                                                                                        |

| H6             | SDI         | DI   | シリアル・データ入力。                                                                                                                                                                  |

| H7             | SCK         | DI   | シリアル・データ・クロック入力。デバイスが選択されると ( CS = ロー)、変換結果はこのクロックによってシフト出力されます。                                                                                                             |

<sup>1</sup> Alはアナログ入力、Pは電源、Dlはデジタル入力、DOはデジタル出力です。

f<sub>S</sub> = 2MSPS

216

### 代表的な性能特性

特に指定のない限り、VDD\_5V = 5.4V、VDD\_1.8V = 1.8V、VIO = 1.8V、REFIN = 5V、入力コモンモード = 2.5V、 $f_S$  = 2MSPS(AD4030-24)または500kSPS(AD4032-24)、および全仕様は $T_{MIN} \sim T_{MAX}$ での値です。代表値は $T_A$  = 25°Cでの値です。

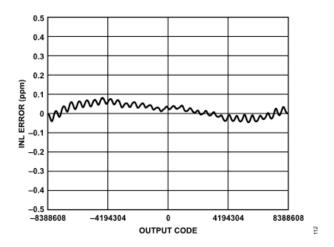

図 12. INL誤差と出力コードの関係 (差動入力)

図 13. INL誤差と出力コードの関係 (シングルエンド入力)

図 16. SNR、SINADと入力周波数の関係

図 14. 入力を短絡した場合のコードのヒストグラム

図 17. 異なる振幅でのTHDと入力周波数の関係

図 18. SNR、SINADと入力振幅の関係、 $f_{IN} = 1kHz$

図 19. SNR、SINADと温度の関係、 $f_{IN}$  = 1kHz

図 20. THDと温度の関係、f<sub>IN</sub> = 1kHz

図 21. INLと温度の関係

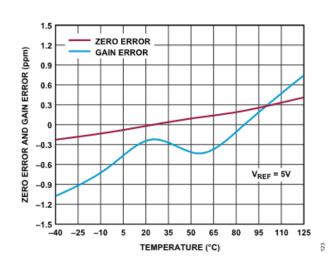

図 22. ゼロ誤差、ゲイン誤差と温度の関係

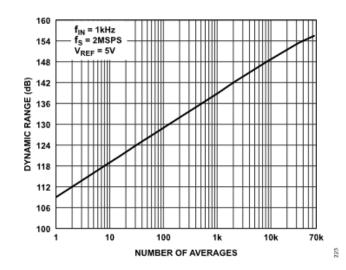

図 23. ダイナミック・レンジと平均化回数の関係

analog.com Rev. A | 16 / 50

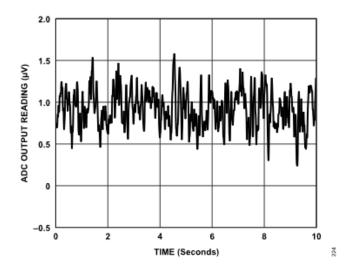

図 24. 低周波数ノイズ(出力データ・レート = 19.5SPS (2048サンプルの平均化ブロック後))

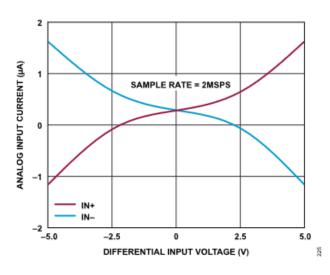

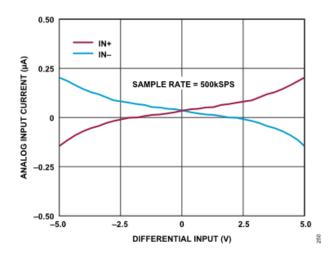

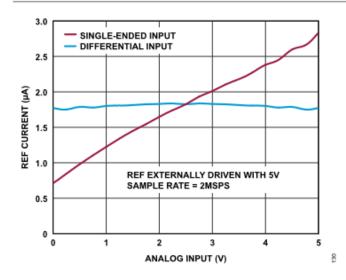

図 25. アナログ入力電流と差動入力電圧の関係、AD4030-24、 2MSPS

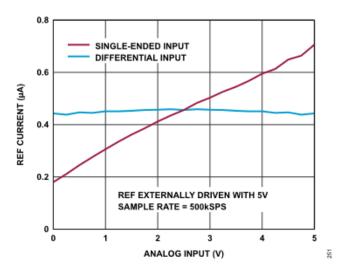

図 26. アナログ入力電流と差動入力電圧の関係、AD4032-24、 500kSPS

図 27. リファレンス・バッファ・オフセットと温度の関係

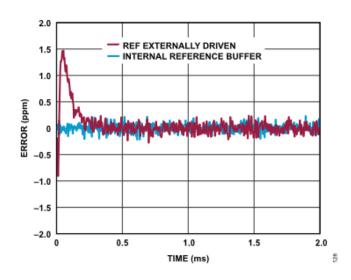

図 28. 長いアイドリング時間後の変換バースト時の誤差

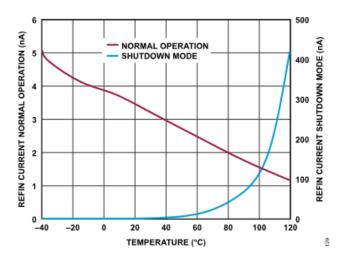

図 **29**. 通常動作時**REFIN**電流およびシャットダウン・モード時 **REFIN**電流と温度の関係

analog.com Rev. A | 17 / 50

図 30. REF電流とアナログ入力の関係、AD4030-24、2MSPS

図 31. REF電流とアナログ入力の関係、AD4032-24、500kSPS

図 32. 同相ノイズ除去比 (CMRR) と入力周波数の関係

図 33. REF電流と温度の関係

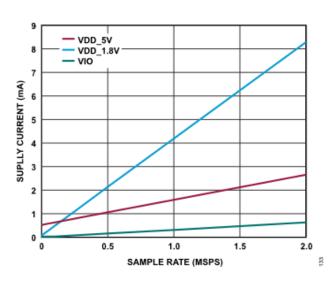

図 34. 電源電流とサンプル・レートの関係

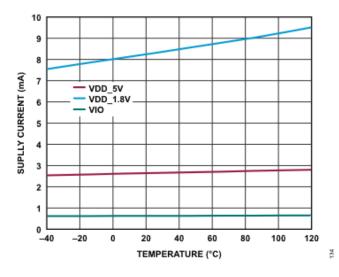

図 35. 電源電流と温度の関係、AD4030-24、2MSPS

analog.com Rev. A | 18 / 50

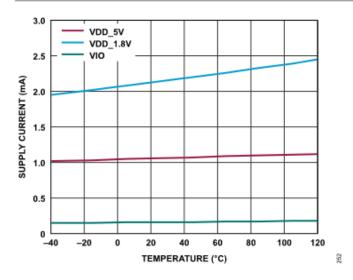

図 36. 電源電流と温度の関係、AD4032-24、500kSPS

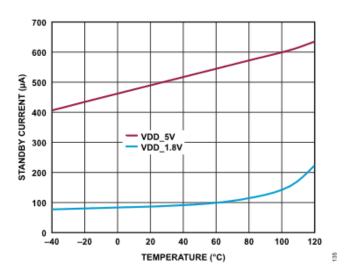

図 37. スタンバイ電流と温度の関係

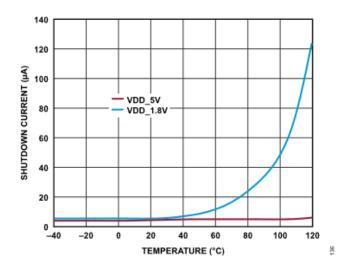

図 38. シャットダウン電流と温度の関係

### 用語

### 積分非直線性誤差(INL)

INLは、負のフルスケールと正のフルスケールを結ぶ直線と個々のコードとの偏差です。最初のコード遷移より%LSBだけ手前の点を負のフルスケールとして使います。正のフルスケールは、最後のコード遷移を1%LSB上回ったレベルとして定義されます。偏差は各コードの中央から真の直線までの距離として測定されます(図40参照)。

#### 微分非直線性誤差(DNL)

理想的なADCでは、コード遷移は1LSBだけ離れた位置で発生します。DNLとは、この理想値からの最大偏差のことです。多くの場合、ノー・ミス・コードが確保される分解能で仕様規定されます。

#### ゼロ誤差 (ZE)

ゼロ誤差は、理想的なミッドスケール電圧 (OV) とミッドスケール出 カコード (OLSB) を生成する実際の電圧との差です。

### ゲイン誤差 (GE)

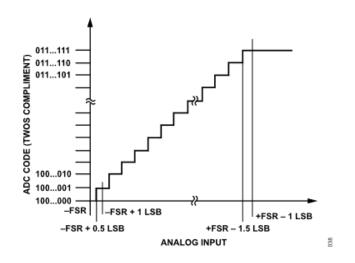

最初の遷移(100…00から100…01)は負の公称フルスケールより½LSB上のレベルで発生します。最後の遷移(011…10から011…11)は、公称フルスケールより1½LSB低いアナログ電圧で発生します。ゲイン誤差とは、最後の遷移の実際のレベルと最初の遷移の実際のレベルとの差が、理論値レベルの差とどれだけ異なるかを示すものです。

### スプリアスフリー・ダイナミック・レンジ (SFDR)

SFDRは、フルスケール入力信号の実効値振幅とピーク・スプリアス信号との差で、単位はデシベル(dB)です。

#### 有効ビット数(ENOB)

ENOBは、サイン波入力による分解能の測定値です。次のように SINADを使用して計算します。 ENOB = (SINADdB - 1.76)/6.02. ENOBの単位はビットです。

### 全高調波歪み(THD)

THDは、フルスケール入力信号実効値に対する最初の5次の高調波成分の実効値を合計した値の比率で、単位はデシベルです。

### ダイナミック・レンジ (DR)

ダイナミック・レンジは、測定したノイズの合計実効値電圧に対するフルスケール・サイン波の実効値電圧の比率です。ダイナミック・レンジの単位はデシベルです。すべてのノイズ源とDNLアーティファクトが含まれるように、-60dBFSの信号で測定されます。

#### S/N比 (SNR)

SNRは、ナイキスト周波数を下回るすべてのスペクトル成分(高調波とDCを除く)の実効値総和に対するフルスケール・サイン波の実効値電圧値の比率です。S/N比の単位はデシベルです。

### 信号/ノイズ+歪み (SINAD) 比

SINADは、ナイキスト周波数を下回るすべてのスペクトル成分の実効値総和(高調波成分は含むが、直流成分は除く)に対するフルスケール・サイン波の実効値電圧の比です。SINADの単位はデシベルです。

#### アパーチャ遅延

アパーチャ遅延は、アクイジション性能の尺度です。**CNV**入力の立上がりエッジから入力信号が変換のために保持されている間までの時間です。

#### 過渡応答

過渡応答は、ADCが±1LSBの精度でフルスケール入力ステップを達成するのに必要な時間です。

### 同相ノイズ除去比(CMRR)

CMRRは、周波数fの入力コモンモード電圧に印加される4.5V p-pサイン波の電力と、周波数fにおけるADC出力の比です。

CMRR (dB) =  $10 \times log(P_{ADC\_IN}/P_{ADC\_OUT})$

ここで、

P<sub>ADC IN</sub>は入力に印加された周波数fのコモンモード電力、

PADC OUTは、周波数fでのADCの出力電力です。

### 電源電圧変動除去比 (PSRR)

PSRRは、周波数fでのADC VDD電源に加えられた200mV p-pのサイン波の電力に対する周波数fでのADC出力電力の比です。

$PSRR (dB) = 10 \times log(P_{VDD\_IN}/P_{ADC\_OUT})$

ここで、

P<sub>VDD\_IN</sub>は、周波数fでのVDDピンの電力、P<sub>ADC\_OUT</sub>は、周波数fでのADCの出力電力です

analog.com Rev. A | 20 / 50

### 動作原理

AD4030-24/AD4032-24の基本機能を図39に示します。

図 39. AD4030-24/AD4032-24の機能ブロック図と信号処理アーキテクチャ

### 概要

AD4030-24/AD4032-24は低ノイズ、低消費電力の高速24ビット逐次比較レジスタ(SAR)A/Dコンバータ(ADC)です。AD4030-24は1秒あたり2,000,000サンプルを変換でき(2MSPS)、AD4032-24は1秒あたり500,000サンプルを変換できます(500kSPS)。システム設計を簡単なものにする、いくつかのアナログ機能とデジタル機能を備えています。アナログ機能には、レベル・シフト条件を緩和する幅広いコモンモード電圧範囲や、シグナル・コンディショニングのマージン条件を緩和する±(65/64)  $\times$   $V_{REF}$ の広い完全差動入力範囲などがあります。

AD4030-24/AD4032-24には、デカップリング・コンデンサが統合されたリファレンス・バッファが内蔵されており、ボード上の外付け部品数を最小限に抑えることができます。内部のトラック&ホールド回路にはパイプライン遅延などの遅延がないため、制御ループや高速アプリケーションに最適な回路となっています。デジタル機能には、オフセット補正、ゲイン調整、平均化などがあり、ホスト・プロセッサの負荷を軽減します。ユーザは、デバイスをいくつかの出力コード・フォーマットのいずれかに設定できます(選択可能な出力データ・フォーマットのセクションを参照)。

AD4030-24/AD4032-24はFlexi-SPIを用いているため、複数のSPIレーンを介してデータにアクセスできます。そのため、ホストSPIコントローラに対するクロック条件が緩和されます。エコー・クロック・モードも、データ・クロックの補助として使用できるため、絶縁型データ・インターフェースを簡単に使用できます。AD4030-24/AD4032-24では、パワーダウン・モードからの復帰後の最初の変換で有効な結果が得られます。このアーキテクチャは、±0.9 ppm(最大値)のINLを実現し、24ビットのノーミス・コード性能と108.4dBのS/N比を備えています。AD4030-24の消費電力は2MSPS時にわずか30mWです。

### コンバータの動作

AD4030-24/AD4032-24は、アクイジション・フェーズと変換フェーズの2つのフェーズで動作します。アクイジション・フェーズでは、内部のトラック&ホールド回路が各入力ピン(IN+、IN-)に接続され、それぞれのピンで独立に電圧をサンプリングします。立上がりエッジ・パルスがCNVピンに入力されると変換が始まります。CNVピンの立上がりエッジは、変換が進行中であることを示すBUSY信号もアサートします。BUSY信号は変換の終了時にデアサートされます。変換結果は、入力電圧差を表す24ビットのコードと、入力コモンモード電圧を表す8ビットのコードになります。デバイス設定に応じて、こ

analog.com Rev. A | 21 / 50

の変換結果はデジタル的に処理され、内部の出力レジスタにラッチされます。各入力ピンのアクイジション回路も、直前のサンプル電圧にプリチャージされるため、入力ドライバへのキックバック電荷を最小限に抑えることができます。ホスト・プロセッサは、内蔵の出力レジスタに内部接続されているSDOピンを介して出力コードを再取得します。

#### 伝達関数

デフォルト設定では、AD4030-24/AD4032-24は $2 \times V_{REF}$ のフルスケール差動電圧を $2^{24}$ のレベルにデジタル化し、LSBサイズは $0.596\mu V$

$(V_{REF} = 5V$ 時)となります。なお、24ビットでの1LSBは約0.06ppmです。理想的な伝達関数を図40に示します。差動出力データは2の補数フォーマットです。表12に、入力電圧と差動出力コードの対応関係を示します。

図 40. 差動出力コードに対するADCの理想的な伝達関数(FSRはフルスケール範囲)

表 12. 入力電圧と出力コードの対応関係

| Description     | Analog Input Voltage<br>Difference       | Digital Output Code<br>(Twos Complement,<br>Hex) |

|-----------------|------------------------------------------|--------------------------------------------------|

| FSR - 1LSB      | (8388607 × V <sub>REF</sub> )/(8388608)  | 0x7FFFFF                                         |

| Midscale + 1LSB | V <sub>REF</sub> /(8388608)              | 0x000001                                         |

| Midscale        | 0 V                                      | 0x000000                                         |

| Midscale - 1LSB | -V <sub>REF</sub> /(8388608)             | 0xFFFFFF                                         |

| -FSR + 1LSB     | -(8388607 x V <sub>REF</sub> )/(8388608) | 0x800001                                         |

| -FSR            | - VREF                                   | 0x800000                                         |

| FSR - 1LSB      | (8388607 × V <sub>REF</sub> )/(8388608)  | 0x7FFFFF                                         |

#### アナログ機能

AD4030-24/AD4032-24には、内部トラック&ホールド回路の一部としてプリチャージ回路があります。これは、直前にサンプリングした人力電圧まで内部のサンプリング・コンデンサを充電する回路です。

これにより、電荷キックバックが減少し、他の従来のSAR ADCに比べ、AD4030-24/AD4032-24のアナログ入力のプリチャージ回路をより容易に駆動できます。このキックバックの減少とより長いアクイジション・フェーズを組み合わせることで、駆動アンプでのセトリング条件が緩和されます。また、この組み合わせにより、より大きな抵抗値を使用できるようになり、アンプの安定性向上に役立ちます。更に、RCフィルタの帯域幅が狭くなるため、シグナル・チェーンのノイズや消費電力が低減します。

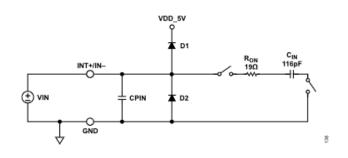

コモンモード電圧には、各入力の絶対電圧範囲( $-1/128 \times V_{REF}$ ~ 129/128  $\times V_{REF}$ )以外には制限がありません。アナログ入力は、図41 に示す等価回路でモデル化できます。アクイジション・フェーズでは、各入力ピンには約116pFの入力容量( $C_{IN}$ )があり、これは、サンプリング・スイッチの19 $\Omega$ のオン抵抗( $R_{ON}$ )と直列に接続されたサンプリング・コンデンサによるものです。変換フェーズでは、各入力には入力ピンの容量( $C_{PIN}$ )があり、これは約4pFです。両入力に共通の信号はすべて、ADCの同相ノイズ除去によって減らすことができます。変換時のアナログ入力にはわずかなリーク電流が流れます。

図 41. AD4030-24/AD4032-24の差動アナログ入力の等価回路

入力は独立にサンプリングされます。各入力が仕様規定されたフルスケール入力範囲内にある限り、変換結果は飽和しません。なお、デジタル・オフセット・パラメータおよびデジタル・ゲイン・パラメータが、変換結果をフルスケール・デジタル範囲(24ビット・ワードの場合- $2^{23}$ ~+ $2^{23}$ -1)を超える数値に割り当てるよう設定されている場合は、デジタル領域の飽和が発生します。デジタル・ゲイン・パラメータを1未満の値に設定することで、 $\pm$ (65/64) ×  $V_{REF}$ までの入力電圧差を飽和することなくキャプチャし変換できます。

良好な性能を発揮するには、アナログ入力ピンのスルー・レートが、アクイジション・フェーズ時には $400V/\mu$ s未満、サンプリング時には  $30V/\mu$ s未満であることが必要です。これは、RC時定数が12.5ns(R×C > 12.5e-9)より大きくなるよう、外部RC回路の値を選択することで実現できます。

#### デジタル・サンプリング処理機能

AD4030-24/AD4032-24は、信号サンプルに適用できるいくつかのデジタル処理機能およびデータ処理機能をサポートしています。これらの機能は、AD4030-24/AD4032-24の制御レジスタを介してイネーブルやディスエーブルができます。図39には、使用可能なデジタル処理機能およびアナログ処理機能を示す信号処理アーキテクチャのブロック図が含まれています。

analog.com Rev. A | 22 / 50

#### フルスケール飽和

どちらかの入力または両方の入力がここで仕様規定されているアナログ制限値を超えた場合、変換結果は、(ポスト処理の前に)デジタル的に飽和します。オフセットおよびゲインのスケーリングを施したのち、結果は24ビット表示に切り捨てられます(最大値0x7FFFFFおよび最小値0x800000で飽和)。オフセットやゲインのデジタル・スケーリングを施す場合は特に、意図せぬ飽和を避けるための注意が必要です。これらの機能の詳細については、デジタル・オフセット調整およびデジタル・ゲインのセクションを参照してください。

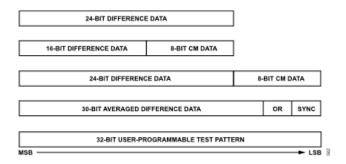

#### コモンモード出力

ホスト・コントローラがOx1またはOx2をモード・レジスタのOUT\_DATA\_MDビット・フィールドに書き込むと(モード・レジスタのセクションを参照)、入力コモンモード電圧を表す8ビットのコードが、入力電圧差を表す16ビットまたは24ビットのコードに追加されます。この8ビット・コードのLSBの大きさは、V<sub>REF</sub>/256です。8ビット・コードは、コモンモード入力電圧がOVの場合はO、V<sub>REF</sub>の場合は255で飽和します。8ビット・コードはオフセットおよびゲインのデジタル・スケーリングには影響されません。これは、入力電圧差を表すコードにのみ追加されるためです。

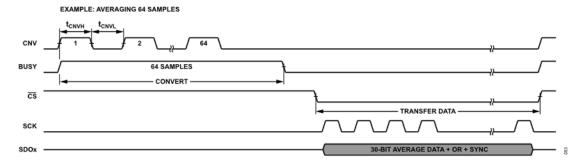

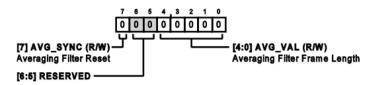

#### ブロック平均化

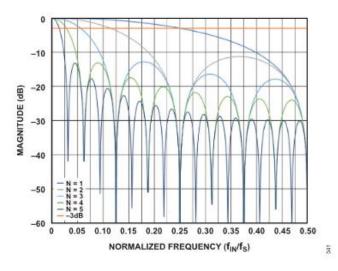

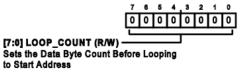

AD4030-24/AD4032-24は、プログラマブルなブロック長 $2^N$  (N = 1、 2、3、...、16) を持つブロック平均化フィルタ (SINC1) を備えてい ます。2<sup>N</sup>サンプルの各ブロックを処理した後、フィルタはリセットさ れます。このフィルタは、モード・レジスタのOUT\_DATA\_MDビッ ト・フィールドに**0x3**を書き込むことでイネーブルできます(モー ド・レジスタのセクションを参照)。また、平均化モード・レジスタ のAVG VALビット・フィールドに値(1≤N≤16)を書き込むことで もイネーブルできます(平均化モード・レジスタのセクションを参 照)。この設定では、出力サンプル・ワードは32ビットです。30個の 最上位ビット (MSB) は2<sup>N</sup>サンプルのブロックで平均化された24ビッ ト・コードの数値を表します。自動スケーリングにより、一定値のブ ロックを平均化する場合は、30ビット・コードの24MSBが24ビッ ト・コードになるようにできます。31番目のビット(OR)は、ブロ ックの1つ以上のサンプルが飽和する場合にハイになる、オーバーレ ンジ警告ビットです。32番目のビット (SYNC) は、2<sup>N</sup>変換サイクル ごとにハイになり、平均値がサンプルの各ブロックの最後でアップデ ートされたことを通知します。詳細については、デジタル・サンプリ ング処理機能のセクションを参照してください。

平均化モデルの実効データ・レートは $f_{CNV}/2^N$ です。 $AVG_VAL$ ビット・フィールドのNのリセット値は、0x00(平均化なし)です。②57に、平均化モードでのタイミング例の図を示します。②42に、N=1、2、3、4、5の場合のフィルタの周波数応答を示します。

図 42. ブロック平均化フィルタの周波数応答例

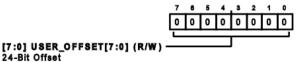

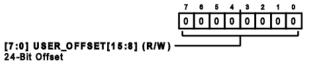

#### デジタル・オフセット調整

ADCは、サンプル・データに24ビットの符号付きオフセット値を追加するようプログラムできます(レジスタの詳細のセクションを参照)。オフセットをサンプルに追加すると、サンプル・データが数値的に飽和する原因となる場合があります。オフセット機能を使用する場合、このことを考慮する必要があります。デフォルト値は0x000000です。詳細については、オフセット・レジスタのセクションを参照してください。

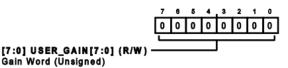

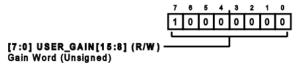

#### デジタル・ゲイン

ADCは、デジタル・サンプルに16ビットの符号なしデジタル・ゲイン (レジスタ0x1Cおよびレジスタ0x1D) を適用するようプログラムできます (レジスタの詳細のセクションを参照)。ゲインは次式に基づいて各サンプルに適用されます。

$Code_{OUT} = Code_{IN} \times (USER\_GAIN/0x8000)$  $\subset \subset \mathcal{T}$

#### 0x0000 ≤ USER GAIN ≤ 0xFFFF

有効なゲイン範囲は $0\sim1.99997$ です。なお、サンプルにゲインを適用すると、数値の飽和の原因となる可能性があります。デフォルト値は0x8000(ゲイン = 1)です。 $\pm V_{REF}$ を超える入力電圧差を測定するには、ゲインを1未満に設定して、24ビット、16ビット、30ビットの出力差分コードの数値的な飽和を避けるようにしてください。詳細については、ゲイン・レジスタのセクションを参照してください。

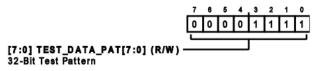

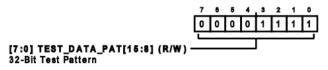

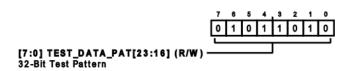

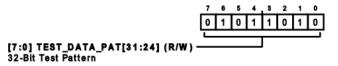

#### テスト・パターン

SPIの機能テストとデバッグを容易にするために、ホスト・コントローラはAD4030-24/AD4032-24に32ビットのテスト・パターンを書き込むことができます(テスト・パターン・レジスタのセクションを参照)。テスト・パターン・レジスタに書き込まれた値は、通常のサンプル・サイクル・タイミングを用いて出力されます。32ビットのテスト・パターン出力モードは、モード・レジスタのOUT\_DATA\_MDビット・フィールドに0x4を書き込むことでイネーブルできます(モード・レジスタのセクションを参照)。テスト・パターン・レジスタに保存されているデフォルト値は0x5A5A0F0Fです。

analog.com Rev. A | 23 / 50

### 選択可能な出力データ・フォーマットの概要

図43に、AD4030-24/AD4032-24で使用可能な出力データ・フォーマットの概要を示します。これらはモード・レジスタで選択できます(モード・レジスタのセクションを参照してください)。なお、ORフラグとSYNCフラグはそれぞれ1ビットです。

図 43. 選択可能な出力サンプル・フォーマットの概要

analog.com Rev. A | 24 / 50

### アプリケーション情報

#### 代表的なアプリケーション図

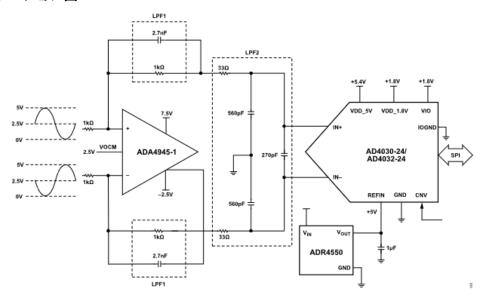

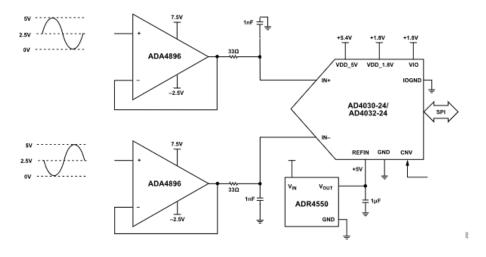

図 44. 差動ドライバのアナログ・フロント・エンド

図 45. ユニティ・ゲイン・デュアル・バッファの構成

### アナログ・フロント・エンドの設計

### ドライバ・アンプの選択

図44にAD4030-24/AD4032-24を駆動する2つの例を示します。どちらも追加のシグナル・コンディショニングを行う上流段と組み合わさっています。また、どちらもシングルエンド入力または差動入力に対応できます。AD4030-24/AD4032-24のSNRとTHDの性能を生かすためには、アプリケーション条件を満たすだけの低ノイズ性能とTHD性能を持つドライバ・アンプを選択することが重要です。図44に示すアンプの他、LTC6227もドライバとして選択できます。アナログ・デバイセズでは、いくつかの関連ドライバ・アンプを用意しており、これらはADC用ドライバのウェブページに掲載されています。

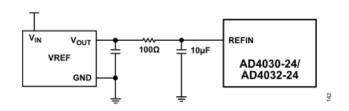

#### リファレンス回路の設計

AD4030-24/AD4032-24は、その入力範囲を指定するために外部リファレンスを必要とします。このリファレンスは4.096V~5Vである必要があります。選択対象となる最適なリファレンスは、ADR4550またはADR4540です。AD4030-24/AD4032-24にはリファレンスから引き出される電荷を減らす機能がいくつかあるため、他のADCよりもかなり使いやすくなります。ほとんどのアプリケーションでは、リファレンスとADC回路を絶縁する高精度バッファが内蔵されているREFINピンをリファレンスが駆動できます。このバッファは高入力インピーダンスで入力電流が小さい(代表値5nA)ため、複数のADCが共通のリファレンスを共有できます。リファレンスとREFINピンの間のRC回路を使用すると、リファレンス・ノイズを除去できます(図46参照)。推奨値は、100 $\Omega$  < R < 1k $\Omega$ 、および、C ≥ 10 $\mu$ Fです。

analog.com Rev. A | 25 / 50

図 46. ノイズ・フィルタ付きリファレンス

ゲイン誤差をできるだけ抑えるために、内部バッファをディスエーブルし(REFIN = 0V)、外部リファレンスを用いてREFピンを駆動することができます。REFピンによって引き出される電流は小さく(2µA 未満)、サンプル・レートおよび出力コードによって異なります。

(図30参照)。REFピンに内蔵される2μFのコンデンサは、最適なリファレンス・バイパスを提供し、部品数とレイアウトの影響を軽減することでPCB設計を簡略化します。

図47に示すように、長時間のアイドリング後にサンプルのバーストが生じるようなアプリケーションでは、リファレンス電流( $I_{REF}$ )が約 $O\mu$ Aから最大値1.8 $\mu$ A(2MSPS時)または約 $O\mu$ Aから0.5 $\mu$ A

(500kSPS時) に急増します。このようにDC電流が流れてステップ 状に増加することにより、リファレンスの過渡応答が生じます。リファレンス出力電圧の変化は出力コードの精度に影響するため、この過 渡応答を考慮する必要があります。リファレンスが

REFINピンを駆動している場合は、内部バッファによってこれらの遷移を処理できます(図28参照)。REFピンが外部バッファなしで駆動されている場合、およびリファレンスの過渡応答が重要でない場合は、セトリングが高速なLTC6655LN-5リファレンスを推奨します。

図 47. バースト・サンプリングを示すCNV波形

analog.com Rev. A | 26 / 50

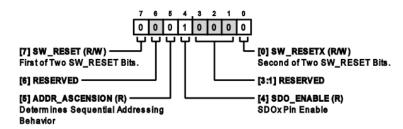

### デバイスのリセット

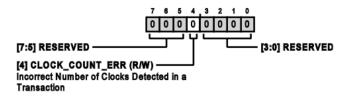

AD4030-24/AD4032-24には、シリアル・インターフェースを使用してデバイス・リセットを実行するオプションが2つあります。ハードウェア・リセットは、RST ピンにロー・パルスを入力することによって開始されます。ソフトウェア・リセットは、同じ書込み命令でインターフェース設定AレジスタのSW\_RESETビットとSW\_RESETXビットの両方を1に設定することで開始されます(インターフェース設定Aレジスタのセクションを参照)。

ハードウェア・リセットまたはソフトウェア・リセットを実行する と、デジタル診断レジスタのRESET\_OCCURREDビットがアサート されます(デジタル診断レジスタのセクションを参照)。

RESET\_OCCURREDビットはこのビットに1を書き込むとクリアされます。RESET\_OCCURREDは、AD4030-24/AD4032-24がデバイス・リセットを実行したことをデジタル・ホストが確認するために用いることができます。

AD4030-24/AD4032-24は、VDD\_5VとVDD\_1.8Vが最初に印加されたときに、パワーオン・リセット (POR) を生成するよう設計されています。PORは、ユーザ設定リジスタの状態をリセットし、

RESET\_OCCURREDビットをアサートします。VDD\_5Vまたは VDD\_1.8Vが仕様規定された動作範囲を下回ると、PORが発生します。POR後にハードウェア・リセットまたはソフトウェア・リセットを行うことを推奨します。

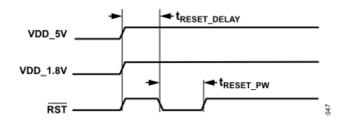

図48に RST 入力を用いてデバイスのリセットを行うためのタイミング図を示します。最小の RST パルス幅は50nsで、図48および表1ではtresetrwと表記されています。リセットは、電源が有効になり安定してから3ms以後に実行する必要があります(この遅延は図48および表1ではtreset Delayと表記されています)。

ハードウェア・リセットまたはソフトウェア・リセット後は、SPIコマンドや変換は750µsの間、開始できません。

図 48. パワーオン・リセット (POR) のタイミング

#### 雷源

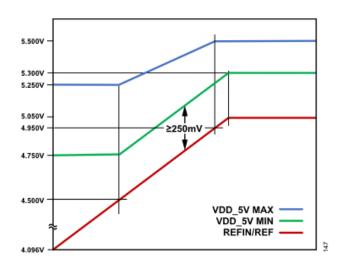

AD4030-24/AD4032-24には、特別な電源シーケンシング条件はありません。絶対最大定格のセクションに記載されている最大電圧の関係を遵守してください。VDD\_5V電源の電圧範囲は、選択するリファレンス電圧によって異なります(仕様の表のInternal Reference BufferまたはExternally Overdriven Referenceを参照)。図49に、REFINとREFに対するVDD\_5Vの最大値と最小値を示します。VDD\_5Vの電圧値が、最大値を超える場合、または最小値を下回る場合、デバイスの損傷または性能の低下の原因となります。

図 49. REFIN/REFに対するVDD\_5Vの最小値と最大値

AD4030-24/AD4032-24には、最初の起動時、またはVDD\_5Vもしくは VDD\_1.8Vが規定された動作範囲を下回った場合に、AD4030-24/AD4032-24をリセットするPOR回路があります。

なお、VDD\_5V電源およびVDD\_1.8V電源はパッケージ内に1μFのバイパス・コンデンサを内蔵しており、VIOは0.2μFのバイパス・コンデンサを内蔵しています。これらの内蔵コンデンサにより、部品表 (BOM) 数やソリューション・サイズを縮小します。バルク電源バイパス・コンデンサがADCの近くにない場合、外部コンデンサをADCに隣接させることができます。全電源の最小立上がり時間は100μsです。

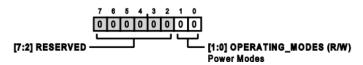

#### 電力消費状態

変換時、AD4030-24/AD4032-24の電力消費率は最大になります。変換が終了すると、スタンバイ状態になり、内部回路の大半がパワーダウンして、消費電流は変換状態時の20%未満に低下します。完全な精度を確保するため、リファレンス・バッファなど一部の回路は、スタンバイ状態時もパワーオン状態を維持します。

デバイス設定レジスタのOPERATING\_MODESビット・フィールドに 0x3を書き込むことで、変換クロックがアイドル状態になっている 間、デバイスをより低消費電力のシャットダウン・モードにすることができます(デバイス設定レジスタのセクションを参照)。このビット・フィールドのデフォルト値は[00]で、通常動作モードになります。シャットダウン・モードでは、消費電流は、10μA未満まで低下します。

### シャットダウン・モード

ADCがシャントダウン・モードに入ると、内部リファレンス・バッファがディスエーブルされ、 $500\Omega$ のスイッチによってREFINピンがREFピンに接続されます(REFINピンが接地され、REFピンが外部駆動されている場合を除く)。これにより、REFピンの $2\mu$ Fのコンデンサが充電され、ADCがシャットダウン・モードを終了したときに高速回復が可能となります。このキープアライブ・スイッチがあるため、

analog.com Rev. A | 27 / 50

ADCがシャットダウン・モードに入るとき(400pC)とシャットダウン・モードを終了するとき(5pC)に、REFINピンに電荷が注入されますシャットダウン・モードを終了すると、REFピンは30µs後に正確なものとなります。

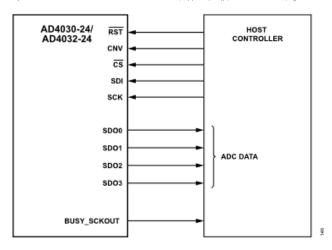

### シリアル・インターフェース

AD4030-24/AD4032-24は、共通のビット・クロック(SCK)を用いた複数レーンのSPIシリアル・デジタル・インターフェースに対応しています。柔軟なVIOピン電源により、AD4030-24/AD4032-24は1.2V~1.8Vで動作する任意のデジタル・ロジックと通信できます。ただし、VIOピンのレベルが1.4V未満の場合は、出力ドライバ・レジスタのIO2Xビットを1に設定する必要があります(出力ドライバ・レジスタのセクションを参照)。シリアル出力データは、最大4個のSDOレーンにクロック同期出力されます。(図50参照)。出力データに同期したエコー・クロック・モードは、デジタル・インターフェースでの絶縁を使用する場合のタイミング条件を緩和するために利用できます。ホスト・クロック・モードも使用でき、内部発振器を使用してデータ・ビットをクロック同期出力できます。

SPIクロック・モードのセクション、エコー・クロック・モードのセクション、ホスト・クロック・モードのセクション、シングル・データ・レートのセクション、デュアル・データ・レートのセクション、1レーン出力データ・クロック・モードのセクション、4レーン出力データ・クロック・モードのセクション、データ出力モードの概要の概要のセクションに、AD4030-24/AD4032-24のSPIの動作が記載されています。

図 50. AD4030-24/AD4032-24の複数レーンSPI

### SPI信号

SPIは、ADCの設定とサンプリングされたデータの取得の両方を行うために使用される、複数レーンのインターフェースです。以下の信号で構成されます。

- ▶ CS (入力) (チップ・セレクト)。ADCのSDIピンまたは SDOxピンとの間でデータ転送を行うには、CS をローに設定する必要があります。サンプル・データ読出しのためのCS のタイミングは、BUSYピンの状態を調べることで、極端なものにならないようにできます。エコー・クロック・モードおよびホスト・クロック・モードでは、BUSY\_SCKOUTピンがこれらのクロック・モードのビット・クロック出力として用いられるため、CS のタイミングはホスト・プロセッサが制御する必要があります。

- ▶ SDI (入力)。ホスト・コントローラからADCへのシリアル・データ入力の流れ。SDI信号は、AD4030-24/AD4032-24のユーザ・レジスタの1つにデータを書き込む場合にのみ使用されます。

- ▶ CNV (入力)。 CNV信号はホスト・コントローラから出され、サンプル変換を開始させます。 CNV信号の周波数によってAD4030-24/AD4032-24のサンプリング・レートが決まります。 CNVクロックの最大周波数は2MSPSです。

- ▶ SCK (入力)。ホスト・コントローラが供出するシリアル・データ・クロック。出力データ転送をサポートする最大SCKレートは 100MHzです。レジスタの読出しと書込みの場合の最大SCKレートは、VIOピン > 1.71Vの場合で86MHz、1.14V ≤ VIOピン < 1.71Vの場合で81MHzです。

- ▶ SD00~SD03 (出力)。ホスト・コントローラへのデータ・レーン。アクティブなデータ・レーンの数は1、2、または4です (表14参照)。データ・レーンの数はモード・レジスタのセクションで設定されます。

- ▶ BUSY\_SCKOUT (出力)。BUSY\_SCKOUTピンの機能は、選択 するクロック・モードによって異なります。表13に各クロック・ モードに対するBUSY\_SCKOUTピンの機能を示します。

#### 表 13. BUSY\_SCKOUTピンの機能とクロック・モードの関係

| Clocking Mode     | Behavior                                               |

|-------------------|--------------------------------------------------------|

| SPI Clocking Mode | Valid BUSY_SCKOUT pin signal for the ADC conversion    |

|                   | status. The busy signal on the BUSY_SCKOUT pin goes    |

|                   | high when a conversion is triggered by the CNV signal. |

|                   | The busy signal on the BUSY_SCKOUT pin goes low        |

|                   | when the conversion is complete.                       |

| Echo Clock Mode   | Bit clock. The BUSY_SCKOUT pin is a delayed version    |

|                   | of SCK input.                                          |

| Host Clock Mode   | Bit clock. The BUSY_SCKOUT pin sources the clock       |

|                   | signal from the internal oscillator.                   |

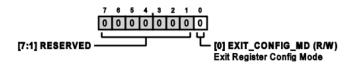

### レジスタ・アクセス・モード

該当のユーザ・レジスタとの間で読み書きを行った後、ホスト・コントローラは、EXIT設定モード・レジスタに詳細を示すように、レジスタ・アドレス0x0014に0x01を書き込むことで、レジスタ設定モードを終了する必要があります。レジスタの読み書きアクセスのアルゴリズムは、以下のとおりです。

- 1. ダミー・レジスタ・アドレス**0x3FFF**からの読出しを行って、レジスタ設定モードに入る。

- 2. 目的のユーザ・レジスタ・アドレスとの間で読出しや書込みを行う。

- 3. レジスタ・アドレス0x0014に0x01を書き込むことで、レジスタ設 定モードを終了する。レジスタ設定モードを終了するとレジスタの 更新が有効になります。

analog.com Rev. A | 29 / 50

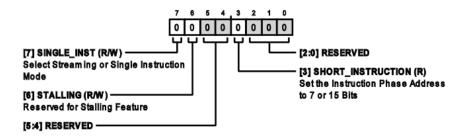

#### ストリーム・モード

AD4030-24/AD4032-24がレジスタ設定モードにある間に、レジスタの読出し/書込みトランザクションを一括して実行する方法もあります。読出し/書込みレジスタ・トランザクションを一括して実行するには、 CS をローに維持するとともに、各レジスタが1バイト (8ビット)幅のみであるためSCKパルスを8の倍数で送出する必要があります。ストリーム・モードでは、アドレスのデクリメントのみが許容されます。つまり、読み書きできるのは最初のレジスタ・アドレスと最初のレジスタ・アドレスのすぐ下のレジスタ・アドレスです。ストリーム・モードでのレジスタ・アクセスは、連続するアドレスを持つレジスタ・ブロックに対して行うことを推奨します。ただし、レジス

タ・マップにないレジスタのアドレスを指定することができます。これを行うには、これらのレジスタにすべてゼロを書き込むだけです。あるいは、読み出す場合は、単にこれらのレジスタから読み出された内容を廃棄するだけです。これはランダムなデータであるためです。有効で連続的なレジスタ・アドレスを調べるには、レジスタのセクションを参照してください。例えば、24ビットのオフセット値を一回で読み出すには、レジスタ・アドレス0x0018から始まる24個のSCKパルスを送出する必要があります。所定アドレスから一括読出しを行うためのタイミング図を図51に示します。

図 51. ストリーム・モードの一括レジスタ読出し動作

analog.com Rev. A | 30 / 50

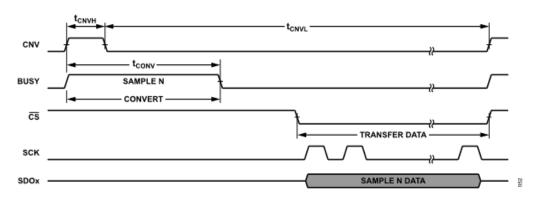

### サンプル変換タイミングとデータ転送

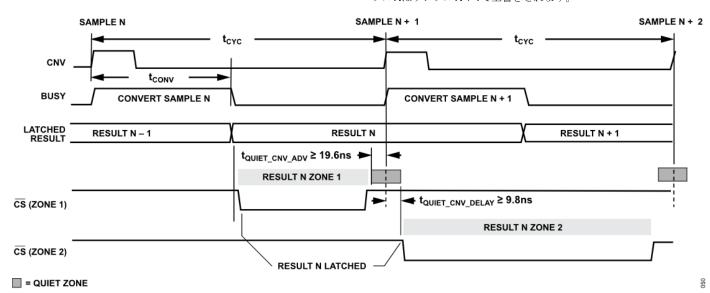

変換は、図52に示すように、CNV信号の立上がりエッジで開始されます。変換が完了すると、 CS をアサートでき、これによって電流変換結果が出力シフト・レジスタにロードされます。

図52に示されるように、サンプルNにはデータ転送ゾーンに2つのオプションがあります。ゾーン1はサンプルNの変換のBUSY信号がデアサートされた直後(SPI変換モード)、あるいは300ns後(エコー・モードおよびホスト・クロック・モード)に  $\overline{CS}$  がアサートされる場合です。ゾーン1では、サンプルNを読み出すために利用できる時間が次式で与えられます。

ゾーン1のデータ読出しウィンドウ =  $t_{CYC} - t_{CONV} - t_{QUIET\_CNV\_ADV}$  例えば、 $f_{CNV}$ が2MSPS( $t_{CYC}$  = 500ns)で $t_{CONV}$ の代表値(282ns)を用

例えば、 $f_{CNV}$ か2MSPS( $f_{CYC}$  = 500ns)で $f_{CONV}$ の代表値(282ns)を用いる場合、使用可能なウィンドウ幅は198.4ns(= 500ns – 282ns – 19.6ns)です。

ゾーン2は、サンプルNを読み出すための  $\overline{CS}$  のアサートがサンプル N+1の変換が開始されるまで遅延される場合です。

データの破損を防ぐため、図52に示すように、CNV信号の各立上がりエッジ前後に静止ゾーンを置く必要があります。CNVの立上がりエッジ直前の静止ゾーンはtquiet\_cnv\_advで、19.6nsです。CNVの立上がりエッジ直後の静止ゾーンはtquiet\_cnv\_belayで、9.8nsです。CNVの立上がりエッジを中心とする静止ゾーンの直後に CS がアサートされると仮定すると、データをクロック同期出力するために使用できる時間は次式のようになります。

ゾーン2のデータ読出しウィンドウ =  $t_{CYC} - t_{QUIET\_CNV\_DELAY} -$

#### $t_{\text{QUIET\_CNV\_ADV}}$

例えば、 $f_{CNV}$ が2MSPS( $t_{CYC}$  = 500ns)で $t_{CONV}$ の代表値(282ns)を用いる場合、使用可能なウィンドウ幅は470.6ns(= 500ns - 9.8ns - 19.6ns)です。ゾーン2の転送ウィンドウはゾーン1のウィンドウより長いため、SPIでより低速のSCKを使用でき、インターフェースのタイミング条件を緩和できます。ゾーン2を使用してデータ転送を行う場合、静止ゾーンの直後に $\overline{CS}$ をアサートすることを推奨します。ただし、ゾーン2はサンプルN + 1のBUSYの立下がりエッジより少なくとも25ns前にアサートする必要があります。そうでない場合、サンプルNはサンプルN + 1で上書きされます。

図 52. データ転送ゾーンのタイミング例

analog.com Rev. A | 31 / 50

### クロック・モード

このセクションでは、AD4030-24/AD4032-24 SPIがサポートする各種 クロック・モードについて説明します。これらのモードは、1レーン、2レーン、4レーンで使用できます。クロック・モードは、モード・レジスタ(レジスタの説明については表16を参照)で設定できます。

#### SPIクロック・モード

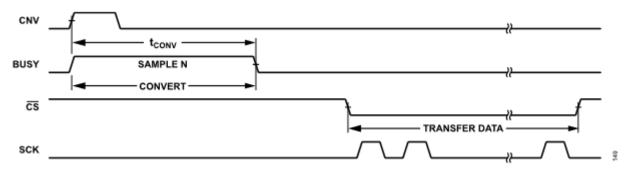

SPIクロック・モードは、AD4030-24/AD4032-24のデフォルト・クロック・モードで、ホスト・コントローラが固有のクロックを使用して出力データをラッチする、ホストをソースとするビット・クロック (SCK) と等価です。SPI互換のクロック・モードは、モード・レジ

スタのCLK\_MDビット・フィールドにOxOを書き込むことでイネーブルできます(モード・レジスタのセクションを参照)。インターフェースの接続を図50に示します。このモードでは、BUSY\_SCKOUTピンの信号が有効で、変換の完了を示します(BUSY\_SCKOUTピンのハイからローへの遷移)。簡略化したサンプル・サイクルを図53に示します。平均化モード以外では、ホスト・コントローラが変換の完了を検出するためにBUSY\_SCKOUTピン信号を使用せず、内部タイマを使用してデータを再取得する場合には、ホスト・コントローラはCNVパルスの立上がりエッジの後300ns以上待機してから CS をローにアサートする必要があります。ブロック平均化モードで動作する場合は、ホスト・コントローラはブロック最後のサンプルにおけるCNVパルスの立上がりエッジの後300ns以上経過してから CS をローにアサートする必要があります。

図 53. SPIクロック・モードの代表的なサンプル・サイクル

analog.com Rev. A | 32 / 50

#### エコー・クロック・モード

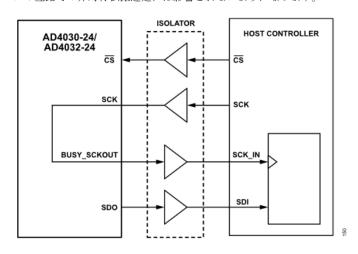

図54にエコー・クロック・モードの信号接続を示します。エコー・ク ロック・モードは、モード・レジスタのCLK MDビット・フィールド に0x1を書き込むことでイネーブルできます(モード・レジスタのセ クションを参照)。このモードでは、BUSY SCKOUTピンを使用し て変換の完了を検出することはできません。BUSY\_SCKOUTピンは ビット・クロック出力となり、ホスト・コントローラのSCKを介して BUSY\_SCKOUTピンにループすることで出力されます(VIOピンの電 圧に応じて5.4ns~7.9nsの固定遅延あり)。非平均化モードで変換デ ータの再取得を開始するには、ホスト・コントローラはCNVパルスの 立上がりエッジの後300ns以上経過してから CS をアサートする必要 があります。ADCがブロック平均化モードに設定されている場合は、 ホスト・コントローラはブロック最後のサンプルにおけるCNVパルス の立上がりエッジの後300ns以上経過してから CS をアサートする必 要があります。タイミング図の例は、データ・クロック条件とタイミ ングのセクションに示されています。エコー・クロック・モードがイ ネーブルされている場合、BUSY\_SCKOUTピンはSDOxピンの遷移に 一致するため、データとクロックのタイミングはSDOxピンとSCKピ ンの経路での非対称伝搬遅延には影響されないようになります。

図 54.エコー・クロック・モードの信号経路図

#### ホスト・クロック・モード

ホスト・クロック・モードがイネーブルされている場合、内部発振器 をビット・クロック源として用います。ホスト・クロック・モード は、モード・レジスタのCLK\_MDビット・フィールドに0x2を書き込 むことでイネーブルできます。ビット・クロックの周波数は、1、2、 または4の除数を用いて、内部発振器レジスタのOSC\_DIVビット・フ ィールドでプログラムできます(内部発振器レジスタのセクションを 参照)。図55は、ホスト・クロック・モードの信号接続を示していま す。このモードでは、BUSY SCKOUTピンはビット・クロック出力 を提供し、これを使用して変換の完了を検出することはできません。 AD4030-24/AD4032-24は、ワード・サイズ、アクティブなレーン の数、シングル・データ・レート・モードとデュアル・データ・ レート・モードのどちらを選択しているか、に応じて、変換デー タをクロック同期出力するために必要なクロック・パルス数を自 動的に計算します。クロック・パルスの数は、内部発振器レジス タのOSC LIMITビット・フィールドから読み出すことができま す。ホストからのSCK\_INはアクティブにはできません。非平均化 モードで変換データを再取得する場合、ホストはCNVパルスの立 上がりエッジ後300nsより前に $\overline{CS}$ をローにアサートすることは できません。ADCが2<sup>N</sup>回平均化を行う平均化モードに設定されて いる場合、ホストは、ブロック最後のサンプルにおけるCNVパル

ス立上がりエッジ後300nsより前に $\overline{\mathsf{CS}}$ をローにアサートすることはできません。

図 55. ホスト・クロック・モードの信号経路例

#### シングル・データ・レート

シングル・データ・レート・クロック (SDR) は、1クロック・サイクルの間に1個のビット (アクティブ・レーンあたり) がクロック同期出力されるもので、すべての出力設定およびサンプル・フォーマットでサポートされています (表14参照)。SDRクロック・モードは、デフォルトで起動時にイネーブルされる他、モード・レジスタのDDR\_MDビットに0を書き込むことでもイネーブルできます(モード・レジスタのセクションを参照)。

#### デュアル・データ・レート

デュアル・データ・レート (DDR) モード (1アクティブ・レーンに つき1クロック・サイクルあたり2個のデータ・ビット遷移) は、ホスト・クロック・モードおよびエコー・クロック・モードでのみ使用可能です。

DDRクロック・モードは、モード・レジスタのDDR\_MDビットに1を書き込むことでイネーブルできます(モード・レジスタのセクションを参照)。DDRモードは、SDRモードに比べ、変換データをクロック同期出力するために使用するSCKパルスの数が半分になります。

#### 1-レーン出力データ・クロック・モード

1-レーンが起動時のデフォルトの出力データ・クロック・モードです。1レーン出力データ・クロック・モードは、モード・レジスタのLANE\_MDビット・フィールドに0x0を書き込むことでイネーブルできます(モード・レジスタのセクションを参照)。アクティブ・レーンはSDOOです。SPIクロック・モード、エコー・クロック・モード、ホスト・クロック・モードを使用する1・レーン・モードのタイミング図の例は、データ・クロック条件とタイミングのセクションにあります。

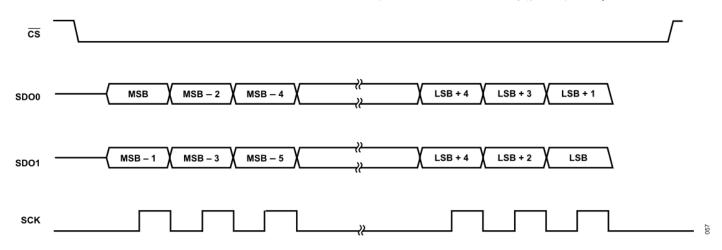

#### 2-レーン出力データ・クロック・モード

2レーン出力データ・クロック・モードがイネーブルされている場合、サンプル・ワード・ビットは2つのSDOレーンの間で分割されます。図58に2レーン・モードのレーン間でのビット割当て方法を示します。ビットの配列は、SPIクロック・モード、エコー・クロック・モード、ホスト・クロック・モードで同じです。2レーン出力データ・クロック・モードは、モード・レジスタのLANE\_MDビット・フィールドに0x1を書き込むことでイネーブルできます(モード・レジスタのセクションを参照)。ホスト・コントローラは、SDOからのデータを再結合し、元のサンプル・ワードを再構築します。変換データをクロック同期出力するために必要なSCKパルス数は、1-レーン・モードに比べ半分になります。表14に、2レーン・モードでのアクティ

ブなSDOレーンを示します。SPIクロック・モード、エコー・クロック・モード、ホスト・クロック・モードを使用する2レーン・モードのタイミング図の例は、データ・クロック条件とタイミングのセクションにあります。

#### 4レーン出力データ・クロック・モード

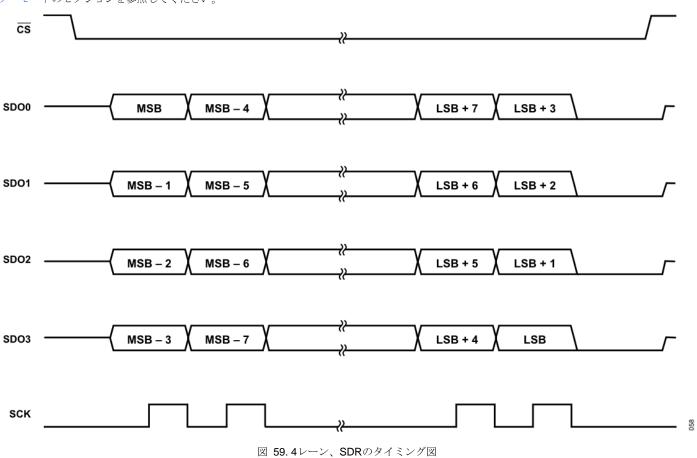

4レーン出力データ・クロック・モードがイネーブルされている場合、サンプル・ワード・ビットは4つのSDOレーンの間で分割されます。図59に4レーン・モードのレーン間でのビット割当て方法を示します。ビットの配列は、SPIクロック・モード、エコー・クロック・モード、ホスト・クロック・モードで同じです。4レーン出力データ・クロック・モードは、モード・レジスタのLANE\_MDビット・フィールドに0x2を書き込むことでイネーブルできます(モード・レジ

スタのセクションを参照)。ホスト・コントローラは、SDOからのデータを再結合し、元のサンプル・ワードを再構築します。変換データをクロック同期出力するために必要なSCKパルス数は、1レーン出力データ・クロックに比べ、4分の1になります。4レーン・モードでのアクティブなSDOレーンを表14に示します。SPIクロック・モード、エコー・クロック・モード、ホスト・クロック・モードを使用する4レーン・モードのタイミング図の例は、データ・クロック条件とタイミングのセクションにあります。

#### データ出力モードのまとめ

AD4030-24/AD4032-24がサポートするデータ出力モードの概要を表 14にまとめます。

表 14. AD4030-24/AD4032-24がサポートするデータ出力モード

| Number of<br>Lanes | Active SDO Lanes       | Clock<br>Mode | Supported Data Clocking<br>Mode | Output Sample Data-Word<br>Length |

|--------------------|------------------------|---------------|---------------------------------|-----------------------------------|

| 1                  | SDO0                   | SPI           | SDR only                        | 24 or 32                          |

|                    |                        | Echo          | SDR and DDR                     | 24 or 32                          |

|                    |                        | Host          | SDR and DDR                     | 24 or 32                          |

| 2                  | SD00, SD01             | SPI           | SDR only                        | 24 or 32                          |

|                    |                        | Echo          | SDR and DDR                     | 24 or 32                          |

|                    |                        | Host          | SDR and DDR                     | 24 or 32                          |

| 4                  | SD00, SD01, SD02, SD03 | SPI           | SDR only                        | 24 or 32                          |

|                    |                        | Echo          | SDR and DDR                     | 24 or 32                          |

|                    |                        | Host          | SDR and DDR                     | 24 or 32                          |

analog.com Rev. A | 34 / 50

### データ・クロック条件とタイミング

#### 基本および平均化変換サイクル

図56に、1回のサンプリングの基本変換サイクルを示します。このサイクルはSPIクロック・モードにあてはまります。エコー・クロック・モードおよびホスト・クロック・モードを使用する場合は、BUSY\_SCKOUTピンの機能はディスエーブルされ、ビット・クロックがBUSY\_SCKOUTピンに出力されます。データ転送はサンプル変換タイミングとデータ転送のセクションに記載の条件を満たす必要があります。

表15に、変換タイミング・パラメータの最小値と最大値を示します。 これらはすべてのクロック・モードにあてはまります。

表 15. 変換サイクルのタイミング・パラメータ

| Parameter         | Min    | Max                 |

|-------------------|--------|---------------------|

| t <sub>CNVH</sub> | 10 ns  | No specific maximum |

| t <sub>CNVL</sub> | 20 ns  | No specific maximum |

| tconv             | 264 ns | 300 ns              |

データ転送時間の長さは、サンプル分解能、アクティブなレーンの数、SCK周波数、データ・クロック・モード(SDRまたはDDR)によって異なります。転送時間の公称値は次式で与えられます。

Data Transfer Duration =

$$t_{TRANS} = \frac{N_{BITS}}{M_{LANES}}$$

$\times \frac{1}{f_{SCK}} \times \frac{1}{K}$  seconds

ここで、

N<sub>BITS</sub> = クロック同期出力されるビット数

$M_{LANES}$  = データをクロック同期出力するために使用されるレーン数 (1、2、または4)

f<sub>SCK</sub> = SCKクロック周波数(単位はHz)

K=1 (SDRのみ、DDRはSPIクロック・モードでは使用できません) 所定のf<sub>SCK</sub>、データ・レーン数、サンプル・ワード・サイズ、 SDR/DDRモードに対し、データ転送にゾーン1を使用した場合の最小 サンプル時間は、次式のようになります。

ゾーン1の最小サンプル時間:

$$t_{CYC} \geq \left( \frac{N_{BITS}}{M_{LANES} imes f_{SCK} imes K}

ight) + t_{CONV} + t_{QUIET\_CNV\_ADV}$$

ゾーン**2**を用いてデータ転送を行う場合の最小サンプル時間は次のとおりです。

$$t_{CYC} \ge \left(\frac{N_{BITS}}{M_{LANES} \times f_{SCK} \times K}\right) + t_{QUIET\_CNV\_DELAY} + t_{QUIET\_CNV\_ADV}$$

図57に、平均化モードが有効でSPIクロック・モードが使用されている場合の、代表的な変換サイクルを示します。平均化されるサンプルの設定数に等しいCNVクロック周期数の間、BUSY信号がアサートされます。BUSY信号がデアサートされると平均化されたサンプルが使用できます。非平均化モードの場合と同様、設定されたクロック・モードがエコー・クロックまたはホスト・クロックの場合、BUSY信号は出力ビット・クロック(SCKOUT)で置き換えられます。ホスト・コントローラは CS をアサートするタイミングを管理しなければなりません。

図 56. 基本的なシングル・サンプル変換サイクル

図 57. 平均化モードの変換サイクル例

analog.com Rev. A | 35 / 50

### SPIクロック・モードのタイミング図

#### 1レーン、SDRモード

図6に、1レーン・データ出力でSDRモード(クロック・サイクルあたり1ビット)の場合の変換サイクルを示します。

#### 2-レーン、SDRモード

図58に、SDRクロック・モードを使用する2レーン・データ出力の変換サイクルを示します。詳細については、2レーン出力データ・クロック・モードのセクションを参照してください。

図 58.2レーン・モード、SDRのタイミング図

### 4レーン、SDRモード

図59にSDRクロック・モードを使用する4レーン・データ出力の変換サイクルを示します。詳細については、4レーン出力データ・クロック・モードのセクションを参照してください。

analog.com Rev. A | 37 / 50

#### エコー・クロックのタイミング図

#### 1- レーン、SDRモード、エコー・クロック・モード

図7に1レーン・エコー・クロック・モードでのSDRモード(SCK周期 あたり1ビット)のタイミング関係を示します。シグナル間のタイミング関係は24ビットと32ビットのどちらのサンプル・ワード・フォーマットにも適用されます。

SCKOUTは、入力SCKの遅延バージョンです。この遅延(tDSDO)の最大値は5.6ns(VIO > 1.71V)です。SDOxのロジック状態の変化は、SCKOUTの立上がりエッジに一致します。クロックとデータのエッジの一致は、1レーン、2レーン、4レーンの出力データ・モードで同じです。

#### 1- レーン、DDRモード、エコー・クロック・モード