# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2022年4月4日現在、アナログ・デバイセズ株式会社で確認した誤りを記 したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2022年4月4日

製品名:ADA4099-1

対象となるデータシートのリビジョン(Rev): Rev.A

訂正箇所:1ページ、 右の段、下から13行目

# 【誤】

$\lceil \cdot \cdot 70V > V_s \cdot \cdot \rfloor$

#### 【正】

$\lceil \cdot \cdot \cdot \cdot V_S + 70V \cdot \cdot \rfloor$

# データシー ADA4099-1/ADA4099-2

# 50V、8MHz、1.5mA/チャンネルの 堅牢な Over-The-Top 高精度オペアンプ

#### 特長

- ▶ 極めて広いコモンモード電圧範囲: -V<sub>s</sub> 0.1V~-V<sub>s</sub> + 70V

- ▶ 広い電源電圧範囲: (V<sub>SY</sub>): +3.15V~+50V (PSRR を確保) して±25V)

- ▶ 低電源電流: 1.5mA/チャンネル(代表値)

- ▶ 低入力オフセット電圧:±40µV(最大値)

- ▶ 低入力オフセット電圧ドリフト:±0.4µV/°C(最大値)

- ▶ 低い電圧ノイズ:

- ▶ 1/fノイズ・コーナ:6Hz(代表値)

- ▶ 0.1Hz~10Hz で 150nV p-p (代表値)

- ▶ 100Hz で 7nV/√Hz(代表値)(e<sub>n</sub>)

- ▶ 高速

- ▶ GBP:8MHz(代表值)

- スルー・レート: ΔV<sub>OUT</sub> = 25V で 5.5V/μs (代表値)

- ▶ 低消費電力のシャットダウン:20µA (最大値)

- ▶ 低入力バイアス電流:±10nA(最大値)

- ▶ 大きい信号電圧ゲイン: 120dB (最小値)

- ► CMRR: 118dB(最小値)

- ▶ PSRR: 123dB(最小値)

- ▶ 入力オーバードライブ耐性(位相反転なし)

- ▶ ±2kV HBM および±1.25kV FICDM

- ▶ 広い動作温度範囲: -55°C~+150°C(Hグレード)

#### アプリケーション

- ▶ 工業用センサーのコンディショニング

- ▶ 電源電流の検出

- ▶ バッテリおよび電源のモニタリング

- ▶ 過酷な環境でのフロント・エンド・アンプ

- ▶ 4mA~20mA のトランスミッタ

#### 概要

ADA4099-1 および ADA4099-2 は堅牢で高精度のシングル/デュ アル・レール to レール入出力オペアンプで、-Vsから最高で+Vs を超える範囲の入力で動作できます。これをこのデータシート では Over-The-Top™と呼んでいます。このデバイスのオフセッ ト電圧は 40μV 未満、入力バイアス電流 (I<sub>B</sub>) は 10nA 未満で、 3.15V~50V の範囲の単電源または分離電源で動作できます。 ADA4099-1 および ADA4099-2 の消費する静止電流は 1.5mA で す。

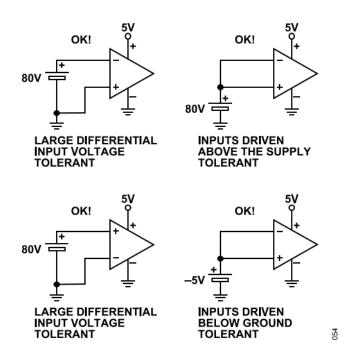

ADA4099-1 および ADA4099-2 の Over-The-Top 入力段は、過酷 な環境にも対応できるよう堅牢な入力保護機能を備えています。 入力は、損傷や DC 精度の低下を生じることなく最大 80V の差 動電圧に耐えられます。動作入力コモンモード電圧範囲は、レ ール to レールを超え、 $+V_s$  電源によらず、 $70V > -V_s$ にまで広が っています。

ADA4099-1 および ADA4099-2 はユニティ・ゲインで安定動作し、 チャンネルあたり最大 20mA を必要とする負荷を駆動できます。 また、このデバイスは、100pF もの容量性負荷も駆動できます。 低消費電力のシャットダウンが可能なアンプです。

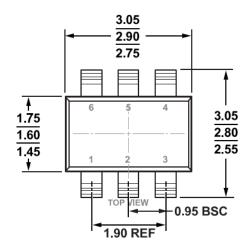

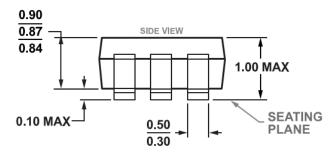

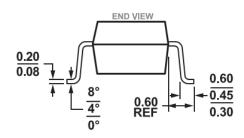

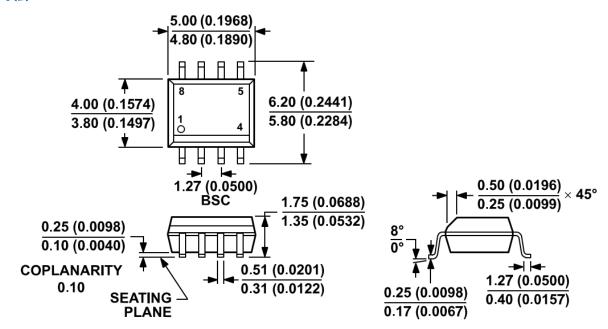

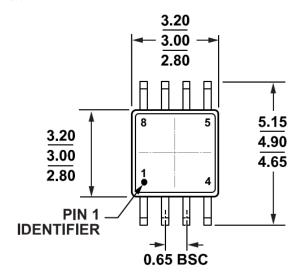

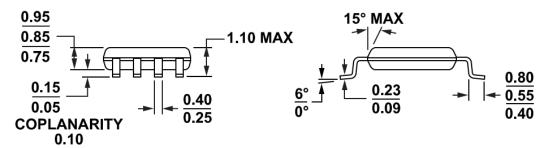

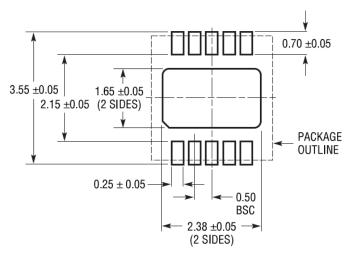

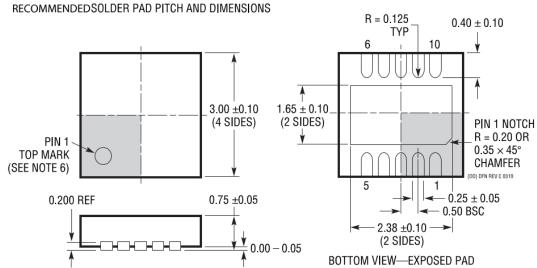

ADA4099-1 は標準的な 6 ピン薄型スモール・アウトライン・ト ランジスタ (TSOT) パッケージを採用しています。ADA4099-2 は、8 ピンの標準スモール・アウトライン・パッケージ (SOIC N)、8 ピンのミニ・スモール・アウトライン・パッケ ージ (MSOP)、10 ピンのリード・フレーム・チップ・スケー ル・パッケージ (LFCSP) を採用しています。

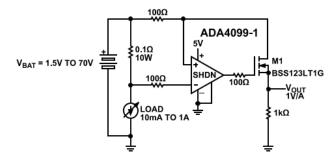

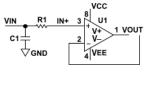

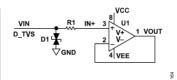

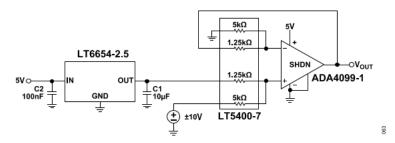

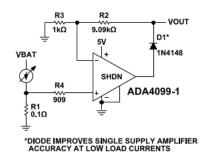

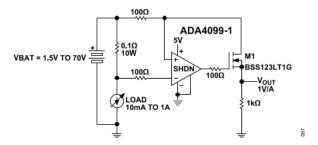

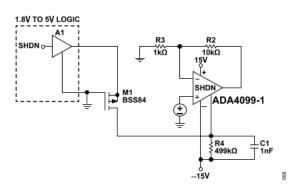

# 代表的なアプリケーション回路

図 1. 1V/A Over-The-Top 電流検出アプリケーション (ADA4099-1 6 ピン TSOT)

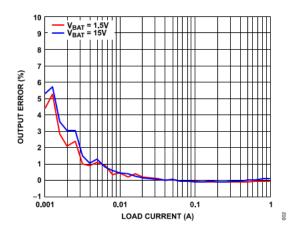

図 2. 出力誤差と負荷電流の関係

Rev. A

**DOCUMENT FEEDBACK TECHNICAL SUPPORT**

# 目次

| 特長1                                                                      | 出力                | 22 |

|--------------------------------------------------------------------------|-------------------|----|

| アプリケーション1                                                                | シャットダウン・ピン        | 22 |

| 概要1                                                                      | アプリケーション情報        | 24 |

| 代表的なアプリケーション回路1                                                          | 大きな抵抗によるゲインの操作    | 24 |

| 仕様                                                                       | 様々なゲインに対する推奨値     | 24 |

| 5V 電源3                                                                   | ノイズ               | 25 |

| ±15V 電源5                                                                 | 歪み                | 25 |

| 絶対最大定格8                                                                  | 消費電力とサーマル・シャットダウン | 26 |

| 最大消費電力8                                                                  | 回路レイアウト時の考慮事項     | 26 |

| 熱抵抗8                                                                     | 電源のバイパス           | 26 |

| 静電放電(ESD)定格8                                                             | グラウンド接続           | 26 |

| ESD に関する注意9                                                              | 通電時の ESD 保護       | 27 |

| ピン配置およびピン機能の説明10                                                         | 関連製品              |    |

| 代表的な性能特性                                                                 | 代表的なアプリケーション      |    |

| 動作原理                                                                     | 外形寸法              |    |

| 入力保護                                                                     | オーダー・ガイド          |    |

| Over-The-Top 動作の考慮事項21                                                   | 評価用ボード            |    |

| 改訂履歴                                                                     |                   |    |

| 1/2022—Rev. 0 to Rev. A                                                  |                   |    |

| Added ADA4099-2                                                          |                   |    |

| Change to Data Sheet Title                                               |                   |    |

| Changes to Features Section                                              |                   |    |

| Changes to General Description Section                                   |                   | 1  |

| Changes to 5 V Supply Section and Table 1                                |                   | 3  |

| Changes to ±15 V Supply Section and Table 2                              |                   | 5  |

| Changes to Table 3                                                       |                   |    |

| Changes to Table 4                                                       |                   |    |

| Change to Table 6 Title                                                  |                   |    |

| Added Figure 5, Figure 6, Table 7, and Table 8; Renumbered Sequentially. |                   | 10 |

| Added Figure 50                                                          |                   |    |

| Changes to Shutdown Pins Section and Title                               |                   |    |

| Changes to Power Supply Bypassing                                        |                   |    |

| Changes to Table 10                                                      |                   | 27 |

1/2021—Revision 0: Initial Version

# 5V 電源

特に指定のない限り、コモンモード電圧( $V_{CM}$ ) = 2.5V、SHDN ピン(ADA4099-1)および SHDNx ピン(ADA4099-2 10 ピン LFCSP)はオープン、負荷抵抗( $R_L$ ) = 499 $k\Omega$  は中間電源に接続、周囲温度( $T_A$ ) = 25C。

表 1.

| Parameter                                    | Test Conditions/Comments                                                                |              | B Grade   |           |              | ade H Grade |           |           |

|----------------------------------------------|-----------------------------------------------------------------------------------------|--------------|-----------|-----------|--------------|-------------|-----------|-----------|

|                                              |                                                                                         | Min          | Тур       | Max       | Min          | Тур         | Max       |           |

| DC PERFORMANCE                               |                                                                                         |              |           |           |              |             |           |           |

| Input Offset Voltage (Vos)1                  | $0.25 \text{ V} < \text{V}_{\text{CM}} < 3.25 \text{ V}$                                |              | $\pm 10$  | $\pm 40$  |              | $\pm 10$    | $\pm 40$  | μV        |

|                                              | Minimum temperature $(T_{MIN}) \le T_A \le$                                             |              |           | $\pm 90$  |              |             | $\pm 90$  | μV        |

|                                              | maximum temperature (T <sub>MAX</sub> )                                                 |              |           |           |              |             |           |           |

|                                              | $0.25 \text{ V} < \text{V}_{\text{CM}} < 70 \text{ V}$                                  |              | ±25       | $\pm 65$  |              | $\pm 25$    | $\pm 65$  | μV        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | $\pm 125$ |              |             | $\pm 140$ | μV        |

|                                              | $-0.1 \text{ V} < \text{V}_{\text{CM}} < +70 \text{ V}$                                 |              | ±25       | $\pm 70$  |              | $\pm 25$    | $\pm 70$  | μV        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | $\pm 125$ |              |             | $\pm 200$ | μV        |

| Input Offset Voltage Drift <sup>2</sup>      | $T_{MIN} < T_A < T_{MAX}$                                                               |              | $\pm 0.1$ | $\pm 0.4$ |              | $\pm 0.1$   | $\pm 0.8$ | μV/°C     |

| Input Bias Current (I <sub>B</sub> )         |                                                                                         |              | ±4        | $\pm 10$  |              | ±4          | $\pm 10$  | nA        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | ±15       |              |             | $\pm 30$  | nA        |

|                                              | $V_{CM} = 70 \text{ V}$ , Over-The-Top                                                  | 70           | 82.5      | 98        | 70           | 82.5        | 98        | μΑ        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               | 40           |           | 125       | 40           |             | 125       | μΑ        |

|                                              | $0 \text{ V} < \text{V}_{\text{CM}} < 70 \text{ V}, \text{V}_{\text{SY}} = 0 \text{ V}$ |              | 0.001     | 10        |              | 0.001       | 10        | μΑ        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | 25        |              |             | 25        | μΑ        |

| Input Offset Current (Ios)                   |                                                                                         |              | ±2        | $\pm 4$   |              | ±2          | ±4        | nA        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | $\pm 10$  |              |             | ±20       | nA        |

|                                              | $V_{CM} = 70 \text{ V}$ , Over-The-Top3                                                 |              | $\pm 0.5$ | ±2        |              | $\pm 0.5$   | ±2        | μΑ        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               |              |           | ±5        |              |             | ±5        | μΑ        |

| Common-Mode Rejection Ratio (CMRR)           | $V_{CM} = -0.1 \text{ V to } +70 \text{ V}$                                             | 118          | 136       |           | 118          | 136         |           | dB        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               | 110          |           |           | 108          |             |           | dB        |

|                                              | $V_{CM} = 0.25 \text{ V to } 3.25 \text{ V}$                                            | 114          | 132       |           | 114          | 132         |           | dB        |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               | 108          |           |           | 108          |             |           | dB        |

| Common-Mode Input Range                      | Guaranteed by CMRR tests                                                                | $-V_S$       |           | $-V_S +$  | $-V_S$       |             | $-V_S +$  | V         |

| Large Signal Voltage Gain (A <sub>OL</sub> ) | $\Delta V_{OUT} = 4 V$                                                                  | - 0.1<br>126 | 140       | 70        | - 0.1<br>126 | 140         | 70        | dB        |

| Large Signar Voltage Gain (AoL)              | $T_{MIN} < T_A < T_{MAX}$                                                               | 116          | 140       |           | 110          | 140         |           | dB        |

|                                              | $\Delta V_{OUT} = 4 \text{ V}, R_{L} = 10 \text{ k}\Omega$                              | 120          | 130       |           | 120          | 130         |           | dB        |

|                                              | $T_{\text{MIN}} < T_{\text{A}} < T_{\text{MAX}}$                                        | 110          | 130       |           | 102          | 150         |           | dB        |

| NOISE PERFORMANCE                            | I MIN I A I MAX                                                                         | 110          |           |           | 102          |             |           | ub        |

| Input Voltage Noise                          | Frequency (f) = 0.1 Hz to 10 Hz                                                         |              | 150       |           |              | 150         |           | nV p-p    |

| input voltage (volse                         | 1/f noise corner                                                                        |              | 6         |           |              | 6           |           | Hz        |

|                                              | f = 100  Hz                                                                             |              | 7         |           |              | 7           |           | nV/√Hz    |

| Over-The-Top                                 | $f = 100 \text{ Hz}, V_{CM} > 5 \text{ V}$                                              |              | 8         |           |              | 8           |           | nV/√Hz    |

| Input Current Noise                          | $f = 100 \text{ Hz}, V_{CM} = 3.7$                                                      |              | 0.5       |           |              | 0.5         |           | pA/√Hz    |

| Over-The-Top                                 | $f = 100 \text{ Hz}, V_{CM} > 5 \text{ V}$                                              |              | 5         |           |              | 5           |           | pA/√Hz    |

| DYNAMIC PERFORMANCE                          | Z ZVO ZZZ, COM Z V                                                                      |              | -         |           |              |             |           | F-5 ( 712 |

| Slew Rate                                    | $\Delta V_{OUT} = 2 V$                                                                  | 2.7          | 4         |           | 2.7          | 4           |           | V/µs      |

|                                              | $T_{MIN} < T_A < T_{MAX}$                                                               | 1.75         | •         |           | 1.75         | •           |           | V/µs      |

| Gain Bandwidth Product (GBP)                 | Test frequency $(f_{TEST}) = 25 \text{ kHz}$                                            | 7.5          | 8         |           | 7.5          | 8           |           | MHz       |

| Sam Dandwiddi i ioddet (ODI )                | Test frequency $(T_{EST}) = 25 \text{ kHz}$ $T_{MIN} < T_A < T_{MAX}$                   | 6.75         | G         |           | 6.5          | U           |           | MHz       |

| Phase Margin                                 | IMIN I A I IMAX                                                                         | 0.75         | 47        |           | 0.5          | 47          |           | Degrees   |

| 1% Settling Time                             | $\Delta V_{OUT} = \pm 2 \text{ V}$                                                      |              | 1.15      |           |              | 1.15        |           | μs        |

| 1% Settling Time                             | $\Delta V_{OUT} = \pm 2 V$                                                              |              | 1.15      |           |              | 1.15        |           |           |

analog.com.jp Rev. A | 3 of 34

表 1.

| Parameter                               | Test Conditions/Comments                                                                           |                          | B Grade | Э        |                          | H Grade | 9      | Unit     |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|---------|----------|--------------------------|---------|--------|----------|

|                                         |                                                                                                    | Min                      | Тур     | Max      | Min                      | Тур     | Max    |          |

| 0.1% Settling Time                      | $\Delta V_{OUT} = \pm 2 \text{ V}$                                                                 |                          | 1.5     |          |                          | 1.5     |        | μs       |

| Total Harmonic Distortion Plus Noise    | $f = 10 \text{ kHz}, V_{OUT} = 2 \text{ V p-p}, R_L = 10 \text{ k}\Omega,$                         |                          | 0.001   |          |                          | 0.001   |        | %        |

| (THD + N)                               | bandwidth = 80 kHz                                                                                 |                          |         |          |                          |         |        |          |

| Channel Separation                      | $f = 1 \text{ kHz}, R_L = 2 \text{ k}\Omega$                                                       |                          | 115     |          |                          | 115     |        | dB       |

| INPUT CHARACTERISTICS                   |                                                                                                    |                          |         |          |                          |         |        |          |

| Input Resistance                        | Differential mode                                                                                  |                          | 100     |          |                          | 100     |        | kΩ       |

|                                         | Common mode                                                                                        |                          | >1      |          |                          | >1      |        | GΩ       |

| Over-The-Top                            | Differential mode, V <sub>CM</sub> > 5 V                                                           |                          | 600     |          |                          | 600     |        | Ω        |

| •                                       | Common mode, $V_{CM} > 5 \text{ V}$                                                                |                          | >100    |          |                          | >100    |        | ΜΩ       |

| Input Capacitance                       | Differential mode                                                                                  |                          | 9       |          |                          | 9       |        | pF       |

| •                                       | Common mode                                                                                        |                          | 3       |          |                          | 3       |        | pF       |

| SHDN AND SHDNx PINS                     |                                                                                                    |                          |         |          |                          |         |        |          |

| Input Logic Low                         | Amplifier active, SHDN and SHDNx                                                                   |                          |         | $-V_{S}$ |                          |         | $-V_S$ | V        |

| 1                                       | voltage $(V_{SHDN}) < -V_S + 0.5 \text{ V}, T_{MIN}$                                               |                          |         | + 0.5    |                          |         | + 0.5  |          |

|                                         | $<$ $T_A$ $<$ $T_{MAX}$                                                                            |                          |         |          |                          |         |        |          |

|                                         |                                                                                                    |                          |         |          |                          |         |        |          |

| Input Logic High                        | Amplifier shutdown, V <sub>SHDN</sub> >                                                            | -V <sub>s</sub><br>+ 1.5 |         |          | -V <sub>S</sub><br>+ 1.5 |         |        | V        |

|                                         | $-V_S + 1.5 V, T_{MIN} < T_A < T_{MAX}$                                                            |                          |         |          |                          |         |        |          |

| Response Time                           | Amplifier active to shutdown                                                                       |                          | 2.5     |          |                          | 2.5     |        | μs       |

| 1                                       | Amplifier shutdown to active                                                                       |                          | 10      |          |                          | 10      |        | μs       |

| Pull-Down Current                       | $V_{SHDN} = -V_S + 0.5 \text{ V}, T_{MIN} < T_A < T_{MAX}$                                         |                          | 0.6     | 3        |                          | 0.6     | 3      | μA       |

|                                         | $V_{SHDN} = -V_S + 1.5 \text{ V}, T_{MIN} < T_A < T_{MAX}$                                         |                          | 0.3     | 2.5      |                          | 0.3     | 2.5    | μA       |

| OUTPUT CHARACTERISTICS                  | SIDA S - ) MIN A MIN                                                                               |                          |         |          |                          |         |        | •        |

| Output Voltage Swing Low                | Overdrive voltage $(V_{OD}^4) = 30 \text{ mV}$ , no                                                |                          | 45      | 60       |                          | 45      | 60     | mV       |

|                                         | load                                                                                               |                          |         |          |                          |         |        |          |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          |         | 105      |                          |         | 120    | mV       |

|                                         | $V_{OD} = 30 \text{ mV}$ , sink current, $(I_{SINK}) =$                                            |                          | 260     | 325      |                          | 260     | 325    | mV       |

|                                         | 10 mA                                                                                              |                          |         |          |                          |         |        |          |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          |         | 435      |                          |         | 450    | mV       |

| Output Voltage Swing High               | $V_{OD} = 30 \text{ mV}, \text{ no load}$                                                          |                          | 45      | 55       |                          | 45      | 55     | mV       |

| 1 & & &                                 | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          |         | 110      |                          |         | 140    | mV       |

|                                         | $V_{OD} = 30 \text{ mV}$ , source current,                                                         |                          | 900     | 1100     |                          | 900     | 1100   | mV       |

|                                         | $(I_{\text{SOURCE}}) = 10 \text{ mA}$                                                              |                          |         |          |                          |         |        |          |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          |         | 1500     |                          |         | 1650   | mV       |

| Short-Circuit Current                   | I <sub>SOURCE</sub>                                                                                | 20                       | 30      |          | 20                       | 30      |        | mA       |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          | 15                       |         |          | 15                       |         |        | mA       |

|                                         | I <sub>SINK</sub>                                                                                  | 40                       | 50      |          | 40                       | 50      |        | mA       |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          | 20                       | 50      |          | 20                       | 50      |        | mA       |

| Output Pin Leakage During Shutdown      | $V_{SHDN} = -V_S + 1.5 \text{ V}$                                                                  | 20                       | ±0.01   | ±100     | 20                       | ±0.01   | ±100   | nA       |

| Carput I in Dountage During Diluted Wil | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          | -0.01   | ±100     |                          | _0.01   | ±100   | μA       |

| POWER SUPPLY                            | - MIN * A * MAA                                                                                    |                          |         | -10      |                          |         | -10    | P** 1    |

| Maximum Operating Voltage <sup>5</sup>  |                                                                                                    |                          |         | 50       |                          |         | 50     | V        |

| Voltage Range                           | Guaranteed by power supply rejection                                                               | 3.15                     |         | 50       | 3.15                     |         | 50     | v        |

| , orage Range                           | ratio (PSRR)                                                                                       | 3.13                     |         | 50       | 3.13                     |         | 50     | '        |

| Supply Current/Channel                  | Amplifier active                                                                                   |                          | 1.5     | 1.6      |                          | 1.5     | 1.6    | mA       |

| вирріу Синсписпаннеі                    | $T_{MIN} < T_A < T_{MAX}$                                                                          |                          | 1.3     | 2.2      |                          | 1.3     | 2.35   | mA       |

|                                         | $\begin{array}{c} I_{MIN} < I_A < I_{MAX} \\ Amplifier shutdown V_{SHDN} = -V_S + 1.5 \end{array}$ |                          | 12      | 2.2      |                          | 12      | 2.33   | mΑ<br>μΑ |

|                                         | Ampinier shutdown $V_{SHDN} = V_S + 1.5$                                                           |                          | 14      | 20       |                          | 14      | 20     | μΑ       |

|                                         |                                                                                                    |                          |         | 22.5     |                          |         | 22.5   |          |

|                                         | $T_{MIN} < T_A < T_{MAX}$                                                                          | I                        |         | 22.5     | I                        |         | 22.5   | μA       |

analog.com.jp Rev. A | 4 of 34

表 1.

| Parameter                     | Test Conditions/Comments                       |     | B Grade H |      |     | H Grade |      | Unit |

|-------------------------------|------------------------------------------------|-----|-----------|------|-----|---------|------|------|

|                               |                                                | Min | Тур       | Max  | Min | Тур     | Max  |      |

| PSRR                          | $V_{SY} = 3.15 \text{ V to } \pm 25 \text{ V}$ | 123 | 136       |      | 123 | 136     |      | dB   |

|                               | $T_{MIN} < T_A < T_{MAX}$                      | 119 |           |      | 120 |         |      | dB   |

| THERMAL SHUTDOWN <sup>6</sup> |                                                |     |           |      |     |         |      |      |

| Temperature                   | Junction temperature (T <sub>J</sub> )         |     | 175       |      |     | 175     |      | °C   |

| Hysteresis                    |                                                |     | 20        |      |     | 20      |      | °C   |

| Operating Temperature         | Ambient temperature (T <sub>A</sub> )          | -40 |           | +125 | -55 |         | +150 | °C   |

<sup>&</sup>lt;sup>1</sup> 高速出荷テスト時に発生する熱電電圧によって、このパラメータの測定精度は制限されます。表 1 に示す制限はテスト能力によって決まるもので、必ずしも実際のデバイス性能を表すものではありません。

### ±15V 電源

特に指定のない限り、 $V_{CM}=0V$ 、SHDN ピン(ADA4099-1)および SHDNx ピン(ADA4099-2 10 ピン LFCSP)はオープン、 $R_L=499k\Omega$  は グラウンドに接続、 $T_A=25$ °C。

表 2

| Parameter                               | Test Conditions/Comments                         |       | B Grade   | е         | I     | H Grade   | Э         | Unit    |

|-----------------------------------------|--------------------------------------------------|-------|-----------|-----------|-------|-----------|-----------|---------|

|                                         |                                                  | Min   | Тур       | Max       | Min   | Тур       | Max       |         |

| DC PERFORMANCE                          |                                                  |       |           |           |       |           |           |         |

| Input Offset Voltage (Vos)1             |                                                  |       | ±12       | $\pm 40$  |       | $\pm 12$  | $\pm 40$  | μV      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | ±95       |       |           | $\pm 90$  | $\mu V$ |

|                                         | $V_{SY} = \pm 25 \text{ V}$                      |       | ±15       | ±40       |       | $\pm 15$  | $\pm 40$  | $\mu V$ |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | $\pm 105$ |       |           | $\pm 90$  | $\mu V$ |

| Input Offset Voltage Drift <sup>2</sup> | $T_{MIN} < T_A < T_{MAX}$                        |       | $\pm 0.1$ | $\pm 0.4$ |       | $\pm 0.1$ | $\pm 0.9$ | μV/°C   |

| Input Bias Current                      |                                                  |       | $\pm 4$   | $\pm 10$  |       | $\pm 4$   | $\pm 10$  | nA      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | ±25       |       |           | $\pm 60$  | nA      |

|                                         | $V_{SY} = \pm 25 \text{ V}$                      |       | $\pm 4$   | $\pm 10$  |       | $\pm 4$   | $\pm 10$  | nA      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | ±35       |       |           | $\pm 100$ | nA      |

| Input Offset Current                    |                                                  |       | ±2        | ±5        |       | ±2        | ±5        | nA      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | ±15       |       |           | ±30       | nA      |

|                                         | $V_{SY} = \pm 25 \text{ V}$                      |       | $\pm 4$   | ±5        |       | $\pm 4$   | ±5        | nA      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        |       |           | ±20       |       |           | ±35       | nA      |

| CMRR                                    | $V_{CM} = -14.75 \text{ V to } +13.25 \text{ V}$ | 118   | 130       |           | 118   | 130       |           | dB      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        | 112   |           |           | 114   |           |           | dB      |

|                                         | $V_{CM} = -15.1 \text{ V to } +13.25 \text{ V}$  | 115   | 126       |           | 115   | 126       |           | dB      |

|                                         | $T_{MIN} < T_A < T_{MAX}$                        | 105   |           |           | 101   |           |           | dB      |

|                                         | $V_{CM} = -15.1 \text{ V to } +55 \text{ V}$     | 117   | 126       |           | 117   | 126       |           | dB      |

|                                         | $T_{\rm MIN} < T_{\rm A} < T_{\rm MAX}$          | 110   |           |           | 107   |           |           | dB      |

| Common-Mode Input Range                 | Guaranteed by CMRR tests                         | -15.1 |           | +55       | -15.1 |           | +55       | V       |

analog.com.jp Rev. A | 5 of 34

$<sup>^2</sup>$ オフセット電圧ドリフトは、実験室での特性評価によって確保されたもので、出荷テストの対象外です。

<sup>&</sup>lt;sup>3</sup> テストの精度は、高速出荷テスト装置の繰り返し精度によって制限されます。ベンチ測定では、Over-The-Top 構成での入力オフセット電流は、通常、+25℃で250nA 未満、-55℃<T<sub>A</sub><+150℃の温度範囲全体では1000nA 未満に制御されています。

$<sup>^4\,</sup>V_{OD}$ は、 $V_{OUT}$ がハイの場合+30mV、 $V_{OUT}$ がローの場合-30mVです。

<sup>&</sup>lt;sup>5</sup>最大動作電圧は、オンチップ・コンデンサ酸化膜の酸化膜経時破壊(TDDB)によって制限されます。 このアンプは、仕様規定された絶対最大定格までの一時的なトランジェント・オーバーシュートには耐えられますが、DC電源電圧は、最大動作電圧以下に制限する必要があります。

<sup>6</sup> サーマル・シャットダウンは実験室でのみ特性評価したもので、出荷テストの対象外です。

表 2.

| Parameter                 | Test Conditions/Comments                                   |                          | B Grade | )     |                          | H Grad | Э                          | Unit      |

|---------------------------|------------------------------------------------------------|--------------------------|---------|-------|--------------------------|--------|----------------------------|-----------|

|                           |                                                            | Min                      | Тур     | Max   | Min                      | Тур    | Max                        |           |

| $A_{OL}$                  | $\Delta V_{OUT} = 25 \text{ V}$                            | 134                      | 154     |       | 134                      | 154    |                            | dB        |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  | 120                      |         |       | 116                      |        |                            | dB        |

|                           | $\Delta V_{OUT} = 25 \text{ V}, R_L = 10 \text{ k}\Omega$  | 120                      | 134     |       | 120                      | 134    |                            | dB        |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  | 114                      |         |       | 110                      |        |                            | dB        |

| NOISE PERFORMANCE         |                                                            |                          |         |       |                          |        |                            |           |

| Input Voltage Noise       | f = 0.1  Hz to $10  Hz$                                    |                          | 150     |       |                          | 150    |                            | nV p-p    |

|                           | 1/f noise corner                                           |                          | 6       |       |                          | 6      |                            | Hz        |

|                           | f = 100  Hz                                                |                          | 7       |       |                          | 7      |                            | nV/√Hz    |

| Over-The-Top              | $f = 100 \text{ Hz}, V_{CM} > +V_{S}$                      |                          | 8       |       |                          | 8      |                            | nV/√Hz    |

| Input Current Noise       | f = 100  Hz                                                |                          | 0.5     |       |                          | 0.5    |                            | pA/√Hz    |

| Over-The-Top              | $f = 100 \text{ Hz}, V_{CM} > +V_{S}$                      |                          | 5       |       |                          | 5      |                            | pA/√Hz    |

| DYNAMIC PERFORMANCE       |                                                            |                          |         |       |                          |        |                            |           |

| Slew Rate                 | $\Delta V_{OUT} = 25 \text{ V}$                            | 3.5                      | 5.5     |       | 3.5                      | 5.5    |                            | V/µs      |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  | 2.0                      |         |       | 2.0                      |        |                            | V/µs      |

| GBP                       | $f_{TEST} = 25 \text{ kHz}$                                | 7.5                      | 8       |       | 7.5                      | 8      |                            | MHz       |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  | 6.75                     |         |       | 6.5                      |        |                            | MHz       |

| Phase Margin              |                                                            |                          | 57      |       |                          | 57     |                            | Degrees   |

| 1% Settling Time          | $\Delta V_{OUT} = \pm 2 V$                                 |                          | 1.15    |       |                          | 1.15   |                            | μs        |

| 0.1% Settling Time        | $\Delta V_{OUT} = \pm 2 V$                                 |                          | 1.5     |       |                          | 1.5    |                            | μs        |

| THD + N                   | $f = 10 \text{ kHz}, V_{OUT} = 5.6 \text{ V p-p}, R_L =$   |                          | 0.001   |       |                          | 0.001  |                            | %         |

|                           | $10 \text{ k}\Omega$ , bandwidth = $80 \text{ kHz}$        |                          |         |       |                          |        |                            |           |

| Channel Separation        | $f = 1 \text{ kHz}, R_L = 2 \text{ k}\Omega$               |                          | 115     |       |                          | 115    |                            | dB        |

| INPUT CHARACTERISTICS     |                                                            |                          |         |       |                          |        |                            |           |

| Input Resistance          | Differential mode                                          |                          | 100     |       |                          | 100    |                            | kΩ        |

|                           | Common mode                                                |                          | >1      |       |                          | >1     |                            | $G\Omega$ |

| Input Capacitance         | Differential mode                                          |                          | 9       |       |                          | 9      |                            | pF        |

|                           | Common mode                                                |                          | 3       |       |                          | 3      |                            | pF        |

| SHDN AND SHDNx PINS       |                                                            |                          |         |       |                          |        |                            |           |

| Input Logic Low           | Amplifier active, $V_{SHDN} < -V_S + 0.5 \text{ V}$        |                          |         | -VS   |                          |        | $-\mathbf{V}_{\mathbf{S}}$ | V         |

|                           |                                                            |                          |         | + 0.5 | 3.7                      |        | + 0.5                      |           |

| Input Logic High          | Amplifier shutdown, $V_{SHDN} > -V_S + 1.5 \text{ V}$      | -V <sub>S</sub><br>+ 1.5 |         |       | -V <sub>S</sub><br>+ 1.5 |        |                            | V         |

| Response Time             | Amplifier active to shutdown                               |                          | 2.5     |       |                          | 2.5    |                            | μs        |

| 1                         | Amplifier shutdown to active                               |                          | 10      |       |                          | 10     |                            | μs        |

| Pull-Down Current         | $V_{SHDN} = -V_S + 0.5 \text{ V}, T_{MIN} < T_A < T_{MAX}$ |                          | 0.6     | 3     |                          | 0.6    | 3                          | μA        |

|                           | $V_{SHDN} = -V_S + 1.5 \text{ V}, T_{MIN} < T_A < T_{MAX}$ |                          | 0.3     | 2.5   |                          | 0.3    | 2.5                        | μA        |

| OUTPUT CHARACTERISTICS    | SHEW S - ) MIN A MAX                                       |                          |         |       |                          |        |                            |           |

| Output Voltage Swing Low  | $V_{\rm OD}^3 = 30 \text{ mV}$ , no load                   |                          | 45      | 60    |                          | 45     | 60                         | mV        |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  |                          |         | 115   |                          |        | 125                        | mV        |

|                           | $V_{OD} = 30 \text{ mV}, I_{SINK} = 10 \text{ mA}$         |                          | 260     | 325   |                          | 260    | 325                        | mV        |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  |                          |         | 435   |                          |        | 450                        | mV        |

| Output Voltage Swing High | $V_{OD} = 30 \text{ mV}, \text{ no load}$                  |                          | 45      | 55    |                          | 45     | 55                         | mV        |

|                           | $T_{MIN} < T_A < T_{MAX}$                                  |                          |         | 140   |                          |        | 165                        | mV        |

|                           | - IVILIN - A - IVIAA                                       | 1                        |         | 110   | l                        |        |                            | '         |

|                           | $V_{OD} = 30 \text{ mV}, I_{SOURCE} = 10 \text{ mA}$       |                          | 900     | 1100  |                          | 900    | 1100                       | mV        |

analog.com.jp Rev. A | 6 of 34

表 2.

| Parameter                              | Test Conditions/Comments                              |      | B Grad | е    |      | H Grad | е    | Unit |

|----------------------------------------|-------------------------------------------------------|------|--------|------|------|--------|------|------|

|                                        |                                                       | Min  | Тур    | Max  | Min  | Тур    | Max  |      |

| Short-Circuit Current                  | I <sub>SOURCE</sub>                                   | 25   | 34     |      | 25   | 34     |      | mA   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             | 20   |        |      | 20   |        |      | mA   |

|                                        | $I_{SINK}$                                            | 40   | 50     |      | 40   | 50     |      | mA   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             | 20   |        |      | 20   |        |      | mA   |

| POWER SUPPLY                           |                                                       |      |        |      |      |        |      |      |

| Maximum Operating Voltage <sup>4</sup> |                                                       |      |        | 50   |      |        | 50   | V    |

| Voltage Range                          | Guaranteed by PSRR                                    | 3.15 |        | 50   | 3.15 |        | 50   | V    |

| Supply Current/Channel                 | Amplifier active                                      |      | 1.65   | 1.8  |      | 1.65   | 1.8  | mA   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             |      |        | 2.45 |      |        | 2.6  | mA   |

|                                        | $V_{SY} = \pm 25 \text{ V}$                           |      | 1.75   | 2    |      | 1.75   | 2    | mA   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             |      |        | 2.7  |      |        | 2.85 | mA   |

|                                        | Amplifier shutdown, $V_{SHDN} = -V_S + 1.5 \text{ V}$ |      | 17     | 24   |      | 17     | 24   | μΑ   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             |      |        | 27   |      |        | 27   | μΑ   |

| PSRR                                   | $V_{SY} = 3.15 \text{ V to } 50 \text{ V}$            | 123  | 136    |      | 123  | 136    |      | dB   |

|                                        | $T_{MIN} < T_A < T_{MAX}$                             | 119  |        |      | 120  |        |      | dB   |

| THERMAL SHUTDOWN⁵                      |                                                       |      |        |      |      |        |      |      |

| Temperature                            | $T_{J}$                                               |      | 175    |      |      | 175    |      | °C   |

| Hysteresis                             |                                                       |      | 20     |      |      | 20     |      | °C   |

| Operating Temperature                  | $T_{A}$                                               | -40  |        | +125 | -55  |        | +150 | °C   |

$<sup>^1</sup>$  高速出荷テスト時に発生する熱電電圧によって、このパラメータの測定精度は制限されます。表  $^2$  に示す制限はテスト能力によって決まるもので、必ずしも実際のデバイス性能を表すものではありません。

analog.com.jp Rev. A | 7 of 34

$<sup>^2</sup>$ オフセット電圧ドリフトは、実験室での特性評価によって確保されたもので、出荷テストの対象外です。

$<sup>^3</sup>$   $V_{OD}$  は、 $V_{OUT}$  がハイの場合+30mV、 $V_{OUT}$  がローの場合-30mV です。

<sup>4</sup>最大動作電圧は、オンチップ・コンデンサ酸化膜の TDDB によって制限されます。このアンプは、仕様規定された絶対最大定格までの一時的なトランジェント・オーバーシュートには耐えられますが、DC 電源電圧は、最大動作電圧以下に制限する必要があります。

<sup>5</sup> サーマル・シャットダウンは実験室でのみ特性評価したもので、出荷テストの対象外です。

#### 絶対最大定格

#### 表 3.

| Parameter                              | Rating          |  |  |  |  |

|----------------------------------------|-----------------|--|--|--|--|

| Supply Voltage <sup>1</sup>            |                 |  |  |  |  |

| Transient                              | 60 V            |  |  |  |  |

| Continuous                             | 50 V            |  |  |  |  |

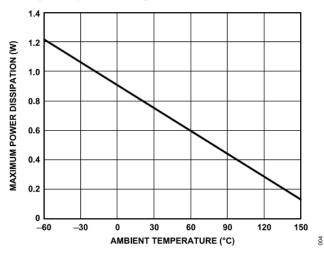

| Power Dissipation (P <sub>D</sub> )    | See Figure 3    |  |  |  |  |

| Differential Input Voltage             | ±80 V           |  |  |  |  |

| ±IN Pin Voltage                        |                 |  |  |  |  |

| Continuous                             | -5 V to +80 V   |  |  |  |  |

| Survival                               | -10 V to +80 V  |  |  |  |  |

| ±IN Pin Current                        | 20 mA           |  |  |  |  |

| SHDN and SHDNx Voltage <sup>2</sup>    | −0.3 V to +60 V |  |  |  |  |

| Storage Temperature Range              | −65°C to +150°C |  |  |  |  |

| Operating Temperature Range            | −55°C to +150°C |  |  |  |  |

| Lead Temperature (Soldering, 10 sec)   | 300°C           |  |  |  |  |

| Junction Temperature (T <sub>J</sub> ) | 175°C           |  |  |  |  |

「最大電源電圧は、オンチップ・コンデンサ酸化膜の TDDB によって制限されます。アンプは、仕様規定された絶対最大定格までの一時的なトランジェント・オーバーシュートには耐えられますが、連続動作電源電圧は、50V以下に制限する必要があります。

<sup>2</sup> SHDN は、ADA4099-1 のピン 5 です。 SHDNx は、ADA4099-2 10 ピン LFCSP の SHDN1 (ピン 5) および SHDN2 (ピン 6) を指します。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

125℃ を超えるジャンクション温度 (T<sub>J</sub>) によって経年劣化が加速されます。ADA4099-1 および ADA4099-2 は、T<sub>A</sub> = 140℃ で1400 時間以上、±25V の電源での動作が実証されています。

### 最大消費電力

デバイスの最大安全消費電力( $P_D$ )は、関連するケース温度( $T_C$ )またはダイの  $T_J$ の上昇により制限されます。 $T_C$  = 約  $150^{\circ}$ C のガラス転移温度で、プラスチック・パッケージの性質が変わります。この温度制限値を一時的にでも超えた場合、パッケージからチップに加えられる応力が変化して、このパラメータに関する ADA4099-1 および ADA4099-2 の性能が恒久的にシフトしてしまうことがあります。長時間にわたり  $T_J=175^{\circ}$ Cを超えると、シリコン・デバイスが変化し、故障の原因となる可能性があります。

パッケージの $P_D$ は、静止消費電力と出力での負荷駆動に起因するパッケージ内の消費電力との和になります。静止電力は次式で表されます。

$V_{\text{SY}} \times I_{\text{SY}}$

ここで、Isyは静止電流です。

負荷駆動による P<sub>D</sub>はアプリケーションによって異なります。負荷駆動による P<sub>D</sub>は、デバイス両端の関連する電圧降下を負荷電流に掛けることで算出されます。この計算における電圧と電流には実効値を用いる必要があります。

空気流があると放熱が増加し、 $\theta_{IA}$ が効率的に低下します。ビアを通る金属パターン、グランド・プレーン、電源プレーンなどに接続されたパッケージ・ピンに直接接触する金属面が増えると、 $\theta_{IA}$ が小さくなります。

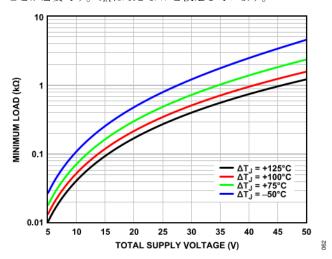

図 3 は、JEDEC 規格の 4 層基板に実装されたシングルおよびデュアルの6 ピン TSOT パッケージについて、最大  $P_D$ と  $T_A$ の関係を示しています。ここで、 $-V_S$  ピンは、プリント回路基板 (PCB) のプレーンと熱的に接触しているパッドに接続されています。 $\theta_{JA}$ の値は概数です。

図 3. 最大消費電力と周辺温度の関係

#### 熱抵抗

熱性能は、PCBの設計と動作環境に直接関連します。PCBの熱設計には、細心の注意を払う必要があります。

θ<sub>JA</sub>は、ジャンクションから周辺への熱抵抗です。

#### 表 4. 熱抵抗

| Package Type | $\theta_{JA}$ | Unit |

|--------------|---------------|------|

| UJ-6         | 192           | °C/W |

| R-8          | 120           | °C/W |

| RM-8         | 163           | °C/W |

| 05-08-1699   | 43            | °C/W |

#### 静電放電(ESD)定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帯電デバイス・モデル(FICDM)。

analog.com.jp Rev. A | 8 of 34

### 絶対最大定格

# ADA4099-1/ADA4099-2 の ESD 定格

表 5. ADA4099-1 6 ピン TSOT、ADA4099-2 8 ピン SOIC\_N、ADA4099-2 8 ピン MSOP、ADA4099-2 10 ピン LFCSP

| ESD Model | Withstand Threshold (kV) | Class |

|-----------|--------------------------|-------|

| HBM       | ±2                       | 2     |

| FICDM     | ±1.25                    | 3     |

# ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev. A | 9 of 34

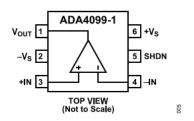

# ピン配置およびピン機能の説明

図 4. ADA4099-1 6 ピン TSOT のピン配置

### 表 6. ADA4099-1 6 ピン TSOT のピン機能の説明

| ピン番号 | 記号        | 説明                                                                                                                                                                                                                                                                                    |

|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | $V_{OUT}$ | アンプ出力。                                                                                                                                                                                                                                                                                |

| 2    | $-V_{s}$  | 負側電源。単電源アプリケーションの場合、通常このピンは低インピーダンスのグランド・プレーンにハンダ付けされます。分離電源アプリケーションでは、0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。                                                                                                                                                |

| 3    | +IN       | アンプの非反転入力。                                                                                                                                                                                                                                                                            |

| 4    | -IN       | アンプの反転入力。                                                                                                                                                                                                                                                                             |

| 5    | SHDN      | オペアンプ・シャットダウン。シャットダウンの閾値は負電源より約 $1V$ 高い電圧です。このピンが未接続の場合、または $-V_s$ に直接配線されている場合、アンプはアクティブです。このピンがハイ( $V_{SHDN}>-V_S+1.5V$ )にアサートされると、アンプはシャットダウン状態になり、アンプの出力は高インピーダンス状態になります。このピンを未接続にする場合、 $-IN$ からの信号が $SHDN$ ピンと容量性結合するのを防止するため、 $SHDN$ と $-V_s$ の間に $1nF$ の小さいコンデンサを接続することを推奨します。 |

| 6    | $+V_S$    | 正側電源。0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。                                                                                                                                                                                                                  |

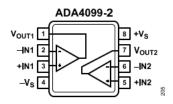

図 5. ADA4099-2 8 ピン SOIC\_N および 8 ピン MSOP のピン配置

# 表 7. ADA4099-2 8 ピン SOIC\_N および 8 ピン MSOP のピン機能の説明

| ピン番号 | 記号                | 説明                                                                                                                                     |

|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>OUT1</sub> | アンプ出力、チャンネル 1。                                                                                                                         |

| 2    | -IN1              | アンプの反転入力、チャンネル 1。                                                                                                                      |

| 3    | +IN1              | アンプの非反転入力、チャンネル 1。                                                                                                                     |

| 4    | $-V_{S}$          | 負側電源。単電源アプリケーションの場合、通常このピンは低インピーダンスのグランド・プレーンにハンダ付けされます。分離電源アプリケーションでは、0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。 |

| 5    | +IN2              | アンプの反転入力、チャンネル2。                                                                                                                       |

| 6    | -IN2              | アンプの非反転入力、チャンネル 2。                                                                                                                     |

| 7    | $V_{\text{OUT2}}$ | アンプ出力、チャンネル 2。                                                                                                                         |

| 8    | $+V_S$            | 正側電源。0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。                                                                   |

analog.com.jp Rev. A | 10 of 34

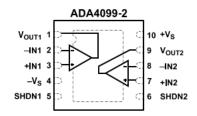

# ピン配置およびピン機能の説明

NOTES 1. EXPOSED PAD. CONNECT THE EXPOSED PAD TO  $-V_S$ .  $\mbox{\$}$

図 6. ADA4099-2 10 ピン LFCSP のピン配置

### 表 8. ADA4099-2 10 ピン LFCSP のピン機能の説明

| ピン番号 | 記号                | 説明                                                                                                                                                                                                                                                                                                  |  |  |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | $V_{\text{OUT1}}$ | アンプ出力、チャンネル 1。                                                                                                                                                                                                                                                                                      |  |  |

| 2    | -IN1              | アンプの反転入力、チャンネル 1。                                                                                                                                                                                                                                                                                   |  |  |

| 3    | +IN1              | アンプの非反転入力、チャンネル 1。                                                                                                                                                                                                                                                                                  |  |  |

| 4    | $-V_{S}$          | 負側電源。単電源アプリケーションの場合、通常このピンは低インピーダンスのグランド・プレーンにハンダ付けされます。分離電源アプリケーションでは、0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。                                                                                                                                                              |  |  |

| 5    | SHDN1             | オペアンプ・シャットダウン、チャンネル $1$ 。シャットダウンの閾値は負電源より約 $1$ V 高い電圧です。このピンが未接続の場合、または $-V_s$ に直接配線されている場合、アンプはアクティブです。このピンがハイ( $V_{SHDN}>-V_S+1.5$ V)にアサートされると、アンプはシャットダウン状態になり、アンプの出力は高インピーダンス状態になります。このピンを未接続にする場合、 $-IN$ からの信号が $SHDN1$ ピンと容量性結合するのを防止するため、 $SHDN1$ と $-V_S$ の間に $1nF$ の小さいコンデンサを接続することを推奨します。 |  |  |

| 6    | SHDN2             | オペアンプ・シャットダウン、チャンネル 2。シャットダウンの関値は負電源より約 $1V$ 高い電圧です。このピンが未接続の場合、または $-V_s$ に直接配線されている場合、アンプはアクティブです。このピンがハイ( $V_{SHDN} > -V_S + 1.5V$ )にアサートされると、アンプはシャットダウン状態になり、アンプの出力は高インピーダンス状態になります。このピンを未接続にする場合、 $-IN$ からの信号が $SHDN2$ ピンと容量性結合するのを防止するため、 $SHDN2$ と $-V_s$ の間に $InF$ の小さいコンデンサを接続することを推奨します。 |  |  |

| 7    | +IN2              | アンプの反転入力、チャンネル 2。                                                                                                                                                                                                                                                                                   |  |  |

| 8    | -IN2              | アンプの非反転入力、チャンネル 2。                                                                                                                                                                                                                                                                                  |  |  |

| 9    | $V_{\text{OUT2}}$ | アンプ出力、チャンネル 2。                                                                                                                                                                                                                                                                                      |  |  |

| 10   | $+V_S$            | 正側電源。0.1μF以上のコンデンサをこのピンのできるだけ近くに取り付けて、ピンを低インピーダンス・グランド・プレーンにバイパスします。                                                                                                                                                                                                                                |  |  |

|      | EPAD              | 露出パッド。露出パッドを-Vsに接続します。                                                                                                                                                                                                                                                                              |  |  |

analog.com.jp Rev. A | 11 of 34

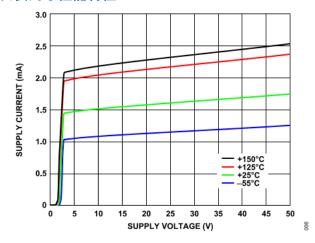

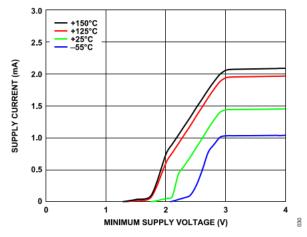

図 7. 電源電流と電源電圧の関係

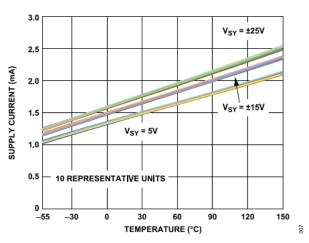

図8.様々な電源電圧での電源電流と温度の関係

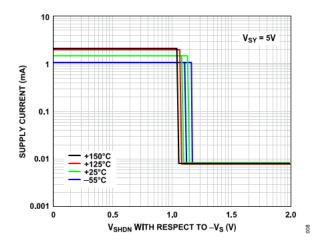

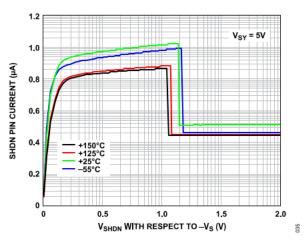

図 9. 電源電流と-V<sub>S</sub> を基準にした V<sub>SHDN</sub> との関係

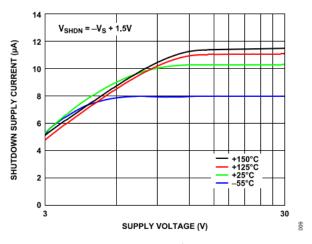

図 10. シャットダウン電源電流と電源電圧の関係

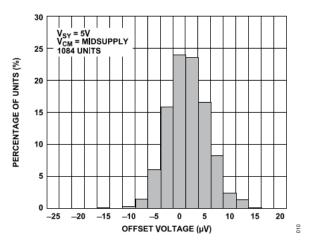

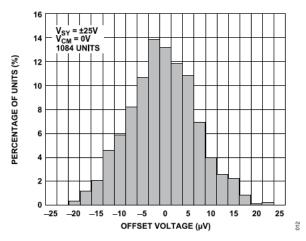

図 11. 入力オフセット電圧の代表的な分布、 $V_{SY}=5V$

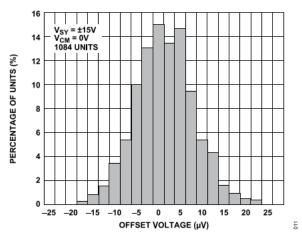

図 12. 入力オフセット電圧の代表的な分布、V<sub>SY</sub> = ±15V

analog.com.jp Rev. A | 12 of 34

図 13. 入力オフセット電圧の代表的な分布、V<sub>SY</sub> = ±25V

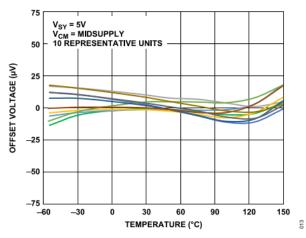

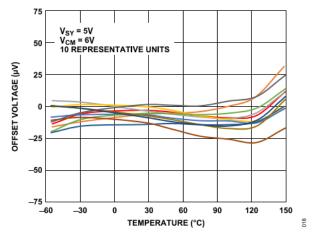

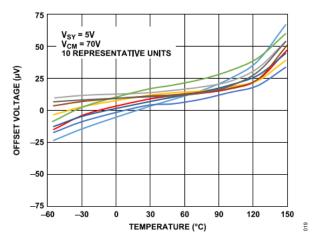

図 14. オフセット電圧と温度の関係、V<sub>SY</sub> = 5V

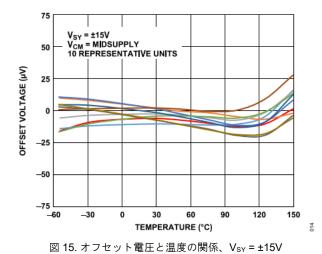

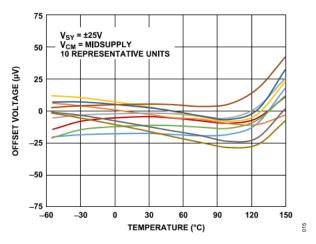

図 16. オフセット電圧と温度の関係、V<sub>SY</sub> = ±25V

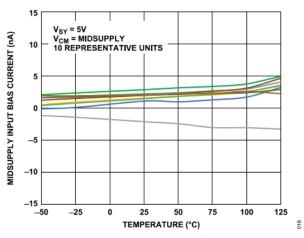

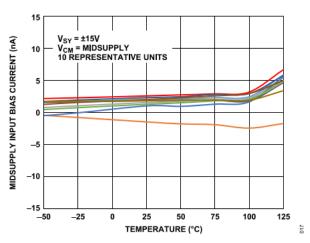

図 17. 中間電源入力バイアス電流と温度の関係、 $V_{SY}=5V$

図 18. 中間電源入力バイアス電流と温度の関係、V<sub>SY</sub> = ±15V

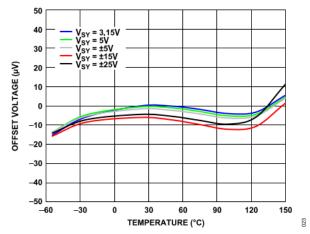

analog.com.jp Rev. A | 13 of 34

図 19. オフセット電圧と温度の関係、V<sub>CM</sub> = 6V、Over-The-Top

図 20. オフセット電圧と温度の関係、V<sub>CM</sub> = 70V

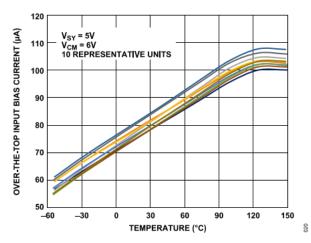

図 21. Over-The-Top 入力バイアス電流と温度の関係、V<sub>CM</sub> = 6V

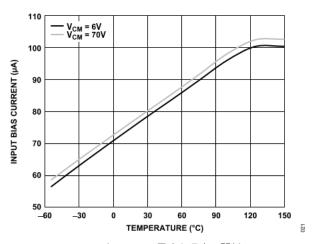

図 22. 入力バイアス電流と温度の関係、 V<sub>SY</sub> = 5V、Over-The-Top

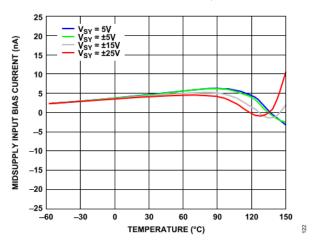

図 23. 様々な電源電圧における電源電圧の中点での 入力バイアス電流と温度の関係

図 24. 様々な電源電圧でのオフセット電圧と温度の関係

analog.com.jp Rev. A | 14 of 34

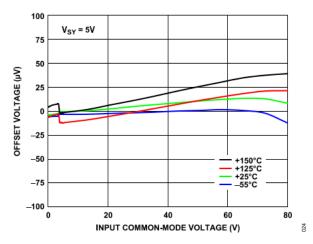

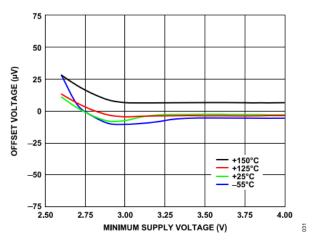

図 25. オフセット電圧と入力コモンモード電圧範囲の入力コモンモード電圧の関係

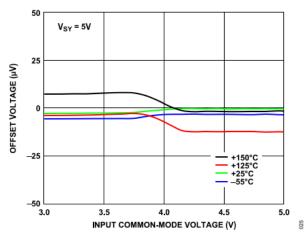

図 26. オフセット電圧と通常動作から Over-The-Top 動作の範囲の入力コモンモード電圧の関係

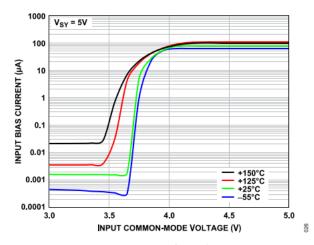

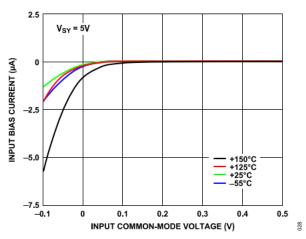

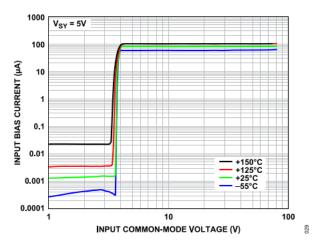

図 27. 入力バイアス電流と通常動作から Over-The-Top 動作の範囲の入力コモンモード電圧の関係

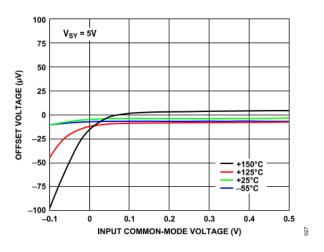

図 28. オフセット電圧とグラウンド検出アプリケーション用 入力コモンモード電圧の関係

図 29. グラウンド・センシング・アプリケーション用の 入力バイアス電流と入力コモンモード電圧の関係

図 30. 入力バイアス電流と入力コモンモード電圧の関係

analog.com.jp Rev. A | 15 of 34

図 31. 電源電流と最小電源電圧の関係

図 32. オフセット電圧と最小電源電圧の関係

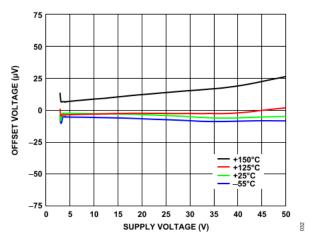

図 33. オフセット電圧と電源電圧の関係

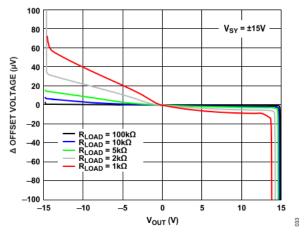

図 34.  $\Delta$  オフセット電圧と出力電圧( $V_{OUT}$ )の関係

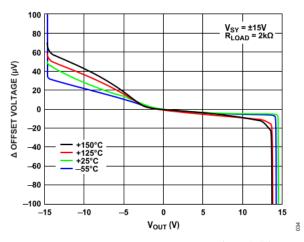

図 35.  $\Delta$  オフセット電圧と  $V_{OUT}$  の関係( $2k\Omega$  負荷)

図 36. 異なる温度での SHDN ピン電流と $-V_S$ 基準  $V_{SHDN}$ の関係

analog.com.jp Rev. A | 16 of 34

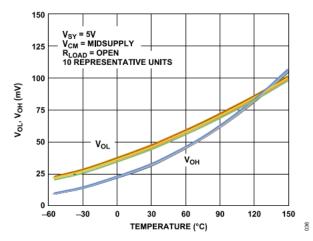

図 37. 出力電圧ロー( $V_{OL}$ )および 出力電圧ハイ( $V_{OH}$ )と温度の関係

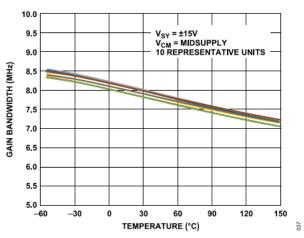

図 38. ゲイン帯域幅と温度の関係

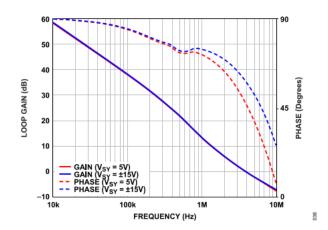

図 39. ループ・ゲインおよび位相と周波数の関係

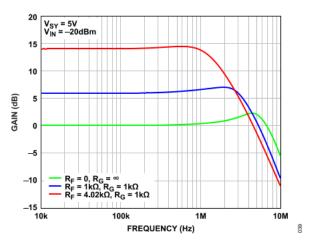

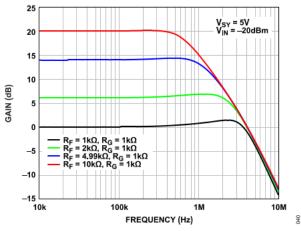

図 40. 非反転小信号周波数応答

図 41. 反転小信号周波数応答

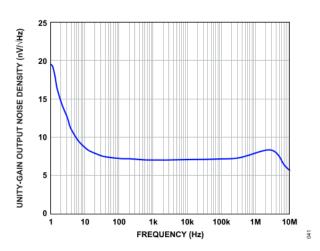

図 42. ユニティ・ゲイン出力ノイズ密度と周波数の関係

analog.com.jp Rev. A | 17 of 34

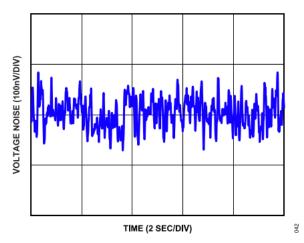

図 43. 0.1Hz~10Hz でのノイズ

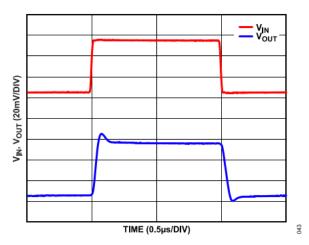

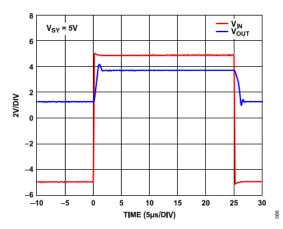

図 44. ユニティ・ゲイン小信号ステップ応答

図 45. ユニティ・ゲイン大信号ステップ応答

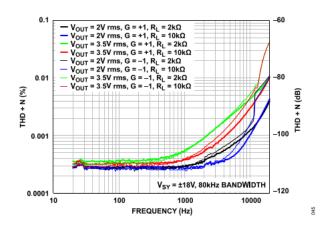

図 46. 様々な負荷での THD + N と周波数の関係

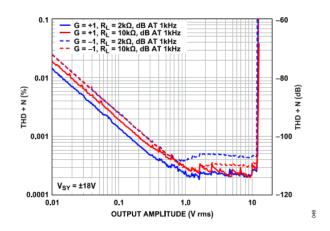

図 47. THD + N と出力振幅の関係

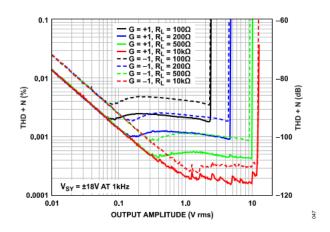

図 48. THD + N と出力振幅および負荷との関係

analog.com.jp Rev. A | 18 of 34

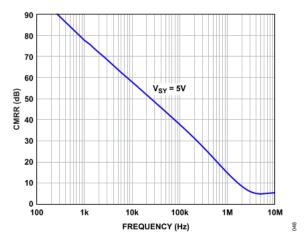

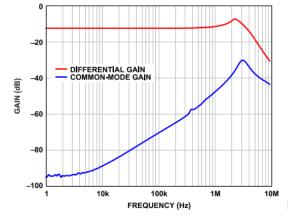

図 49. CMRR と周波数の関係

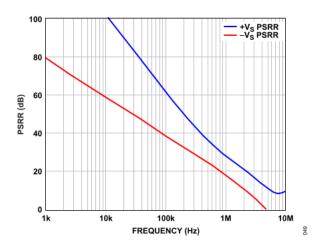

図 50. PSRR と周波数の関係

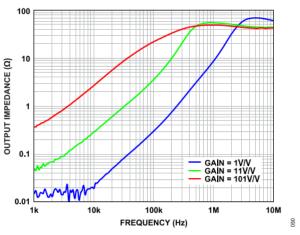

図 51. 出力インピーダンスと周波数の関係

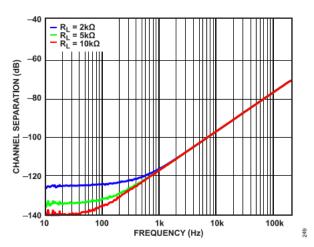

図 52. チャンネル・セパレーションと周波数の関係

analog.com.jp Rev. A | 19 of 34

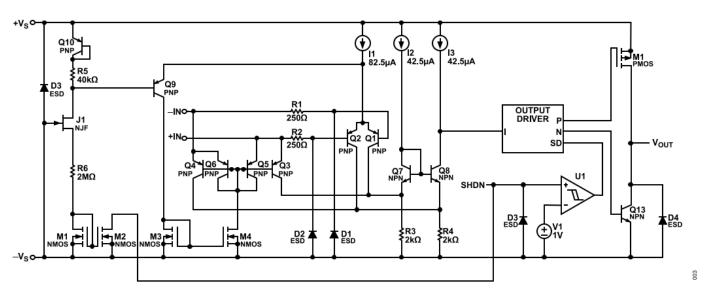

ADA4099-1 および ADA4099-2 は、ユニティ・ゲインの安定性に加え、低オフセット、低オフセット・ドリフト、 $7nV/\sqrt{Hz}$  の入力ノイズを備えた、堅牢なシングル/デュアル電圧帰還アンプです。このデバイスの簡略化した回路図を図 55 に示します。 ADA4099-1 および ADA4099-2 には、入力段が 2 つあります。1 つは、コモン・エミッタ差動入力段で、入力が $-V_s$  と $+V_s$  -1.5V の間にバイアスされた場合に動作する、Q1 および Q2 の PNPトランジスタで構成されています。もう 1 つは、コモン・ベース入力段で、コモンモード入力のバイアスが $+V_s$  -1.5V を上回っている場合に動作する、Q3~Q6 の PNPトランジスタで構成されています。これらの入力段によって、図 53 に示すように、2 つの異なる動作領域が生じます。

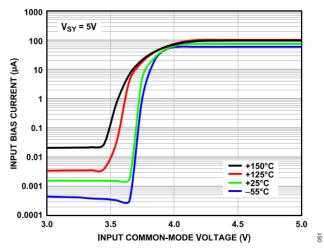

図 53. 異なる温度での入力バイアス電流と 入力コモンモード電圧の関係、 $V_{SY} = 5V$

コモンモード入力電圧が $+V_S$ 電源よりおよそ 1.5V 低い場合には、Q1  $\ge$  Q2 が作動して(図 53 を参照)、コモン・エミッタ PNP 入力段がアクティブとなります。入力バイアス電流は 4nA 未満(代表値)です。コモンモード入力が $+V_S-1.5V$  を超えると、Q9 トランジスタがオンになり、コモン・エミッタ差動入力ペアから  $M_3$  および  $M_4$  で構成されるミラーにバイアス電流を切り替えます。 $M_4$  からの電流はコモン・ベース差動入力ペア(Q3~Q6)をバイアスします。Over-The-Top 入力ペアは、コモン・ベース構成で動作し、入力バイアス電流は約  $82.5\mu A$  に増加します。両入力段のオフセット電圧は厳密に調整されており、その仕様規定値は表 1 および表 2 に示すとおりです。

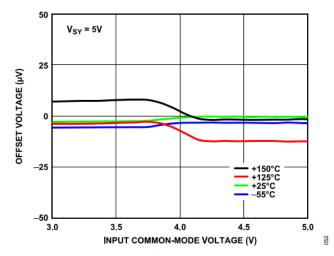

入力コモンモードが Over-The-Top 領域に移行すると、入力 CMRR は図 54 に示すように、それ以外の入力コモンモード範囲 と比べてわずかに低下します。

図 54. 異なる温度でのオフセット電圧と 入力コモンモード電圧の関係、 $V_{SY}$  = 5V

図 55. ADA4099-1 と ADA4099-2 の簡略化した回路図

analog.com.jp Rev. A | 20 of 34

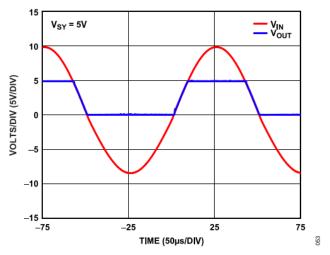

#### 入力保護

入力は、 $250\Omega$  の内蔵抵抗(図 55 を参照)によって、 $-V_s-10V$ までの一時的な電圧変動に対し保護されています(図 56 を参 照)。この抵抗は、これと直列に配置され、Q1 および Q2 トラ ンジスタのベースにそれぞれ接続されている D1 および D2 ダイ オードの電流を制限します。外付け抵抗を直列に追加すること で保護範囲を-Vs-10Vより拡張できますが、安定性が低下し熱 ノイズが増加します。ADA4099-1 および ADA4099-2 の入力段に は、位相反転保護機能が組み込まれており、-Vs 未満の入力に 対し出力の位相が反転するのを防止します。ADA4099-1 オペア ンプおよび ADA4099-2 オペアンプには、入力間のクランピン グ・ダイオードはありません。また、最大 80V まで差動オーバ ードライブが可能で、その場合でもデバイスが損傷したり、パ ラメータが変動したり、相当量の入力電流が流れたりすること はありません。図 57 に、入力の完全性を損なうことなく ADA4099-1 および ADA4099-2 に適用できる入力障害タイプを示 します。

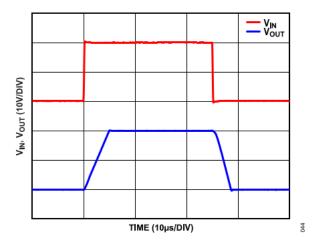

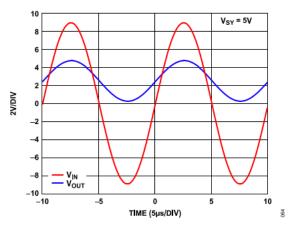

図 56. 非反転入力が電源電圧を超えて駆動される場合の ユニティ・ゲイン・バッファとしての ADA4099-1 および ADA4099-2 (V<sub>SY</sub> = 5V)

図 57. ADA4099-1 および ADA4099-2 の障害許容条件

### Over-The-Top 動作の考慮事項

ADA4099-1 および ADA4099-2 の入力コモンモードが+ $V_s$ の電源電圧近くまたはそれ以上にバイアスされた場合、アンプは Over-The-Top構成で動作します。アンプの動作を制御する差動入力ペアは、コモン・ベース・ペア Q3 $\sim$ Q6 です(図 55 を参照)。

入力段がコモン・エミッタからコモン・ベースに切り替わると、 入力バイアス電流は通常動作時の±4nA 未満から、Over-The-Top 動作時の約82.5μAに変化します。Over-The-Top 入力バイアス電 流間は良好にマッチングされ、付随するオフセットは通常 250nA 未満です。反転入力と非反転入力に接続されるインピー ダンスのマッチングを確保し、入力バイアス電流によって電圧 オフセットが発生しないようにしてください。

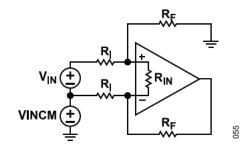

差動入力インピーダンス  $R_{\rm IN}$ (図 58 を参照)の値は、通常動作時の  $100k\Omega$  以上から、Over-The-Top 動作時の約  $600\Omega$  に減少します(表 1 および表 2 を参照)。

図 58. 通常動作と Over-The-Top 動作用に構成された ディファレンス・アンプ

analog.com.jp Rev. A | 21 of 34

この  $R_{\rm IN}$  抵抗は、コモン・ベース入力段の構成により、Over-The-Top 動作時の加算ノード間に生じます。

$R_N$  の値は、次式で表されるように、オペアンプの入力に流れる 仕様規定された  $I_B$  から求めることができます。

$R_{IN} = 2kT/(qI_B)$

ここで、

kはボルツマン定数、

Tは動作温度、

qは電子の電荷、

IBは Over-The-Top 動作時の動作入力バイアス電流です。

入力は、絶対温度に比例してバイアスされます。そのため、RIN は温度に対して比較的安定です。この抵抗はアンプの加算ノードに発生しますが、アンプの帰還動作により OV 差動となるため、悪影響はそれほど生じません。ただし、構成によっては、この入力抵抗により、ノイズ・ゲインの増加、全体的なアンプ・ループ・ゲインおよびクローズドループ帯域幅の低下、出力ノイズの増加が見られる場合があります。この構成の際立った利点は、クローズドループ・アンプの安定性が向上することです。

通常モード  $(-V_S < V_{CM} < +V_S -1.5V)$  では、 $R_{IN}$ はゲイン設定抵抗  $(R_F$  および  $R_I)$  の値と比較して大きくなるのが通常であり、 $R_{IN}$ は無視できます。

この場合、ノイズ・ゲインは次式で定義されます。

入力コモンモードが+ $V_S$  の電源電圧の近くまたはそれ以上にバイアスされ、アンプが Over-The-Top 動作に移行した場合は、 $R_{\rm IN}$  の値を考慮に入れてください。

アンプのノイズ・ゲインは次式のように増加します。

Noise

$$Gain_{OTT} = \left(\left(1 + \frac{R_F}{R_I ||R_{IN} + R_I||R_F}\right) \times \left(1 + \frac{R_I ||R_F}{R_{IN}}\right)\right)$$

ここで、Noise Gainott は Over-The-Top のノイズ・ゲインです。

DC のクローズドループ・ゲインは、ほとんど影響を受けません  $(R_F/R_I)$  。 ただし、アンプのループ・ゲインは次式で表されるように減少します。

$$\frac{A_{OL}}{1 + \frac{R_F}{R_I}} \text{ to } \frac{A_{OL}}{Noise \; Gain_{OTT}}$$

同様に、アンプのクローズドループ帯域幅(BW<sub>CLOSED\_LOOP</sub>)は、通常動作から Over-The-Top 動作への移行に伴って変化します。

通常動作では、

$$BW_{\text{CLOSED\_LOOP}} \approx \frac{GBP}{1 + \frac{R_F}{R_I}}$$

Over-The-Top 動作では、

$$BW_{CLOSED\_LOOP} \approx \frac{GBP}{Noise\ Gain_{OTT}}$$

デバイスが通常動作から Over-The-Top 動作に移行した場合、出力電圧ノイズ密度 (eno) が影響を受けます。次式において、抵抗のノイズは、どちらの動作モードでも無視されています。

通常動作では、抵抗ノイズを無視して、

$$e_{no} \cong e_n \left(1 + \frac{R_F}{R_I}\right)$$

ここで、enは入力換算電圧ノイズ密度です。

Over-The-Top 動作では、抵抗ノイズを無視して、

$$e_{no} \cong e_n \times Noise Gain_{OTT}$$

#### 出力

ADA4099-1 および ADA4099-2 の出力は、無負荷の場合、レール to レール振幅を両電源から 45mV 以内にすることができます。出力は約 30mA をソースまたはシンクできます。アンプは、最小 100pF の負荷容量  $(C_L)$  を駆動するよう内部補償されています。出力とより大きな容量性負荷との間に  $50\Omega$  の抵抗を直列に追加すると、アンプの容量性駆動能力が拡大されます。

ADA4099-1 および ADA4099-2 がシャットダウンされた場合、 $V_{OUT}$  ピンは両電源に接続された 2 つのステアリング・ダイオードにより高インピーダンスとなります。この状態では、出力リークは 5nA 未満(代表値)です。

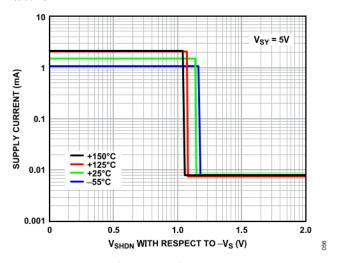

# シャットダウン・ピン

ADA4099-1 および ADA4099-2 には専用のシャットダウン・ピン (ADA4099-1 用には SHDN、ADA4099-2 10 ピン LFCSP には SHDN1 および SHDN2) があり、ハイにアサートされるとアンプが非常に低い消費電力のシャットダウン状態になります。ロジック・ハイは、 $-V_S$  ピンを基準として SHDN ピンおよび SHDNx ピンに 1.5V 以上の電圧が加えられた場合と定義されます。シャットダウン時、アンプに流れる電源電流は15 $\mu$ A未満となり(図 59 を参照)、 $V_{OUT}$  ピンは高インピーダンス状態になります。

図 59. 電源電流と-V<sub>S</sub> を基準にした V<sub>SHDN</sub> との関係

SHDN ピンまたは SHDNx ピンは、+Vs 電源電圧を超えて絶対最 大電圧 (-Vs 基準で 60V) まで駆動でき、消費電流はわずか (1.5µA 未満)です。通常のアクティブなアンプ動作の場合、 SHDN ピンまたは SHDNx ピンは、フロート状態にするか外部電 圧源によってロー (-Vsから 0.5V 以内) に駆動することができ ます。SHDN ピンまたは SHDNx ピンがフロート状態のままの場 合、内部電流源(約 600nA) が SHDN ピンを-V<sub>s</sub>にします。こ れによって、アンプはデフォルトのアクティブな増幅動作状態 になります。-IN ピン (ADA4099-1) または-INx ピン (ADA4099-2 10 ピン LFCSP) と SHDN ピンまたは SHDNx ピン は非常に近接しているため、-IN ピンまたは-INx ピンの高速エ ッジが、隣接する高インピーダンスの SHDN ピンまたは SHDNx ピンに AC 結合し、デバイスが誤ってシャットダウンすること があります。こうした状況が懸念される場合は、SHDN ピンま たは SHDNx ピンと-Vsピンの間に 1nF のコンデンサを追加して ください。

もう1つの方法として、 $+V_s$ の供給を止めることで、アンプを効果的に低消費電力状態にすることもできます。この低消費電力状態では、 $\pm IN$  ピンまたは $\pm INx$  ピンのバイアス電圧が $-V_s$   $\sim$   $-V_s$ +70V の場合、入力のリーク電流は 1nA 未満(代表値)です。 $\pm IN$  ピンまたは $\pm INx$  ピンが $-V_s$  未満の場合、これらのピンは、 $250\Omega$  の抵抗と直列に $-V_s$  電源に接続されたダイオードのようになります。この状態では、電流を 30mA 未満に制限してください。

シャットダウン状態で外部電源を用いて $\pm V_S$ の電源電圧のどちらかを超える出力を駆動すると、電流が無制限に流れデバイスに損傷を加える可能性があります。

analog.com.jp Rev. A | 23 of 34

# 大きな抵抗によるゲインの操作

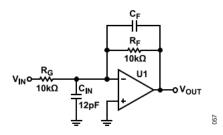

ADA4099-1 および ADA4099-2 の入力容量は約 12pF です。

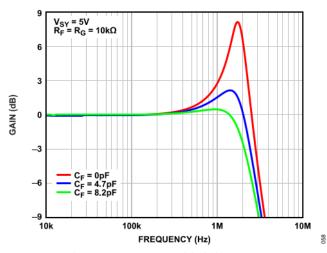

帰還抵抗( $R_F$ )とゲイン設定抵抗( $R_G$ )を反転入力部で並列に組み合わせると、この入力容量( $C_{IN}$ )を結合して極が形成され、それにより帯域幅の減少、周波数応答のピーキング、または発振の生成が生じる可能性があります(図 61 を参照)。こうした結果を緩和するため、 $C_F > C_{IN}$ ( $R_G/R_F$ )の値の帰還コンデンサを、加算ノード・インピーダンスを $1k\Omega$ より大きくする( $R_F||R_G > 1k\Omega$ )ための  $R_F$ に並列に配置します。このコンデンサ配置により入力の極が打ち消され動的性能が最適化されます(図 60 を参照)。

ノイズ・ゲインがユニティ  $(R_G \rightarrow \infty)$  で帰還抵抗が  $1k\Omega$  を超えるアプリケーションでは、 $C_F \geq C_{IN}$ です。レイアウトに関連する加算ノード容量が絶対最小値となるよう、PCB レイアウトを最適化してください。

図 60. 反転ゲイン回路図

図 61. 反転ゲイン 1 の小信号周波数応答、 $R_F = R_G = 10 k \Omega$

### 様々なゲインに対する推奨値

表9は、様々な推奨ゲインおよび関連するノイズ性能を決定するための参考資料です。反転入力に生じる合計インピーダンスは、1 より大きなゲインの場合 1  $k\Omega$  未満に設定され、最適な小信号帯域幅を維持しています。

表 9. ゲインと関連する推奨抵抗値(T<sub>A</sub> = 25℃)

| Gain | $R_G$ (k $\Omega$ ) | $R_F(k\Omega)$ | C <sub>F</sub> (pF) | Approximate −3 dB Frequency (MHz) | Total System Noise (nV/√Hz at 1 kHz),<br>Referred to Input |

|------|---------------------|----------------|---------------------|-----------------------------------|------------------------------------------------------------|

| +1   | Not applicable      | 0              | Not applicable      | 8                                 | 6.8                                                        |

| +2   | 1                   | 1              | 0                   | 4                                 | 7.2                                                        |

| +2   | 10                  | 10             | 8.2                 | 2.7                               | 11                                                         |

| +5   | 1                   | 4.02           | 0                   | 1.5                               | 7.4                                                        |

| -1   | 10                  | 10             | 8.2                 | 2.1                               | 22                                                         |

| -1   | 1                   | 1              | 0                   | 4.8                               | 14.4                                                       |

| -2   | 1                   | 2              | 0                   | 2.9                               | 11.3                                                       |

| -5   | 1                   | 4.99           | 0                   | 1.4                               | 9.2                                                        |

| -10  | 1                   | 10             | 0                   | 0.75                              | 8.7                                                        |

analog.com.jp Rev. A | 24 of 34

## ノイズ

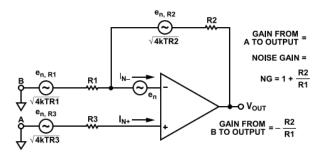

アンプ回路のノイズ性能を分析するには、ノイズ源を特定し、各ノイズ源がアンプの全体的なノイズ性能に大きく影響しているかどうかを判定します。ノイズ計算を簡略化するため、実際の電圧ではなくノイズ・スペクトル密度(NSD)を使用し、計算式から帯域幅を除外します。NSDは一般に nV/Hz 単位で表され、1Hz の帯域幅内のノイズに相当します。

図 62 に示すノイズ・モデルには、3 個の抵抗( $R1\sim R3$ )のジョンソン・ノイズ、オペアンプの電圧ノイズ、アンプの各入力の電流ノイズ( $I_{N\pm}$ )という 6 個の個別のノイズ源があります。各ノイズ源は、出力でのノイズに対し固有の影響があります。ノイズは一般的に、入力換算(RTI)で規定されますが、多くの場合、出力換算(RTO)ノイズを計算し、それをノイズ・ゲインで割って RTI ノイズを求める方が簡単です。

$$e_{N}^{2} + 4kTR3 + 4kTR1 \left(\frac{R2}{R1 + R2}\right)^{2} +$$

$$RTI NOISE = \sqrt{\frac{I_{N+}^{2}R3^{2} + I_{N-}^{2}}{I_{R1}^{2}R2^{2}}} \left(\frac{R1 \times R2}{R1 + R2}\right)^{2} + 4kTR2 \left(\frac{R1}{R1 + R2}\right)^{2}$$

$$RTO NOISE = NG \times RTI NOISE$$

図 62. オペアンプのノイズ分析モデル

$I_{N+} = I_{N-} = I_{N}$ と仮定すると、RTI ノイズの計算式は、次のように 簡略化できます。

RTI Noise =

$$\sqrt{e_{n}^2 + e_{n,R}^2 + \left(I_N R_{EQ}\right)^2}$$

$e_{n,R} = \sqrt{4kTR_{EQ}}$

$R_{EQ} = R_3 + R_1 || R_2$

ここで、

enはオペアンプの電圧ノイズ、

$e_{n,R}$ は周囲の抵抗  $R1\sim R3$  からの熱ノイズの影響、

REOは等価入力抵抗、

Tは絶対温度(ケルビン)です。

$50\Omega$  の抵抗は 25℃ で  $\ln V/\sqrt{Hz}$  のジョンソン・ノイズを発生します。

最適な性能を得るための帰還ネットワーク内の抵抗の下限は、 許容できる静止電力および歪みの量で決まります。上限は抵抗 と電流のノイズ密度で決まります。ADA4099-1 および ADA4099-2 の enは 7nV/Hz です。

抵抗と電流ノイズによる影響がこの値の半分より下である場合は、オペアンプから発生する en が支配的となり、デバイスにおける最適なノイズ性能が得られます。

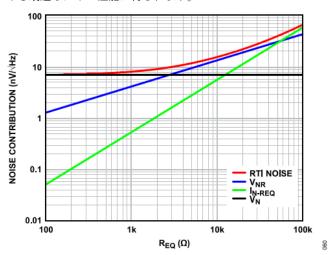

図 63. ノイズの影響と等価入力抵抗(R<sub>EQ</sub>)の関係

ADA4099-1 および ADA4099-2 の場合、帰還回路の抵抗の下限値は約750 $\Omega$ です。図 62 に示すアンプ構成では、 $R_{EQ} < 750\Omega$  とすることで安定したノイズ性能が得られます。ノイズ性能が重要とならないような場合は、 $e_n$ は所定の  $T_A$ に対し一定であることが多く、 $e_{n,R}$ は抵抗値の平方根に比例して増加します。また、 $IN \times REQ$  は抵抗値に比例して増加しますが、 $e_{n,R}$ の値に近づくまでは合計ノイズには影響しません。 $R_{EQ}$ が約60 $k\Omega$ 未満の場合、 $e_{n,R}$ は  $I_N \times R_{EQ}$ より大きくなります。 $I_N$ が入力部の合計ノイズに大きく影響しないようにするためには、 $R_{EQ}$ を約30 $k\Omega$ とするのが安全です。

図 63 に、このセクションで説明した抵抗値の範囲におけるノイズの影響を示します。

#### 歪み

オペアンプの歪みには2つの主要な要因があります。1つは出力がソースからシンクに移行する際の出力クロスオーバー歪み、もう1つは非線形の同相ノイズ除去による歪みです。オペアンプが反転構成で動作している場合は、同相ノイズによる歪みはありません。オペアンプが通常の入力コモンモード範囲( $-V_s \sim +V_s - 1.5V$ )の非反転構成で動作している場合、歪みは許容可能な範囲に収まります。入力が通常動作から Over-The-Top 動作、またはその逆へ移行する場合は、入力回路の変化により、直線性が著しく低下します。

$R_L$ が減少すると、歪みは増加します。これは、ループ・ゲインが実質的に減少することと、負荷を駆動するために必要なアンプ内部の信号振幅が増大することが原因です。入力コモンモードを中間電源にバイアスし反転構成にして ADA4099-1 およびADA4099-2 をクラス A 動作させることで、歪みを最小にできます。

analog.com.jp Rev. A | 25 of 34

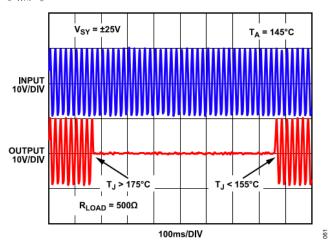

#### 消費電力とサーマル・シャットダウン

ADA4099-1 および ADA4099-2 は最大 $\pm$ 25V の電源を使用して大きな負荷を駆動できます。そのため、集積回路の  $T_1$ は 175  $^{\circ}$ C を超えないようにしてください。

ジャンクション温度が 125℃ を超えると経年劣化が加速します。ジャンクション温度が 175℃ を超えると、ADA4099-1 および ADA4099-2 の信頼性が低下する可能性があります。ジャンクション温度が 175℃ を超える場合、ADA4099-1 および ADA4099-2 には、出力段をシャットオフし内部デバイス電流を減少させる、サーマル・シャットダウンという形の最終的な安全対策があります。このサーマル・シャットダウン機能がトリガされると、ジャンクション温度が 20℃ 低下するまで出力はディスエーブルされて高インピーダンス状態になります。高負荷が永続的で周囲温度が高い場合、この高負荷がなくなるまで、ダイでの消費電力に応じて、ADA4099-1 や ADA4099-2 がサーマル・シャットダウン状態になったりサーマル・シャットダウン状態になったりすることを繰り返す原因となることがあります(図 64 を参照)。

図 64. ADA4099-1 および ADA4099-2 における サーマル・シャットダウンのオン/オフの繰り返し

最大ジャンクション温度付近で動作させることは推奨しません。

通常、 $T_I$ は、次式に示すように、 $T_A$ とデバイスの消費電力 ( $P_D$   $\times$   $\theta_{JA}$ ) から推定できます。

#### $T_J = T_A + P_D \times \theta_{JA}$

IC の消費電力は、電源電圧、出力電圧、負荷抵抗の関数として変化します。所定の電源電圧の場合、この IC での最も厳しい消費電力 (P<sub>D(MAX)</sub>) は、電源電流が最大で、出力電圧がどちらかの電源電圧の半分のときに発生します。

$$P_{D(MAX)} = V_s I_{s(MAX)} + \frac{\left(\frac{V_{SY}}{2}\right)^2}{R_I}$$

設定された電源電圧に対し、ADA4099-1 および ADA4099-2 が 所定の電源電圧と所定のジャンクション温度上昇( $\Delta T_J$ )で駆動できる最小負荷抵抗を推定するためのガイドとして、② 65 を使用できます。例えば、 $\Delta T_J$ を 50°C に制限するには、 $\pm 15$ V の電源 ( $\pm 30$ V の合計電源電圧)で駆動できる負荷は 1.2k $\Omega$ 以上であることが必要です。 $\theta_{JA}$ は 192°C/W と仮定しています。

図 65. 所定の ΔT」および V<sub>SY</sub> に対する最小負荷抵抗

### 回路レイアウト時の考慮事項

ADA4099-1 および ADA4099-2 のボードをレイアウトする際には、細部に至るまで慎重に注意を払うことで最適性能が得られます。電源のバイパス、寄生容量、部品選択などのすべてがアンプの性能全体に影響を与えます。

#### 電源のバイパス

単電源の場合、 $-V_s$ 電源ピンを低インピーダンスのグランド・プレーンに直接ハンダ付けします。等価直列抵抗(ESR)の小さな  $0.1\mu F$ (代表値)の積層セラミック・コンデンサ(MLCC)を $\pm VS$  電源ピンのできるだけ近くに実装して、 $+V_s$  ピンを低インピーダンスのグランド・プレーンにバイパスします。高負荷を駆動する場合は、 $10\mu F$  の電源コンデンサを追加します。分離電源を使用する場合は、これらの条件を $-V_s$  電源ピンに適用できます。

ADA4099-1 および ADA4099-2 には、SHDN ピン(ADA4099-1) および SHDNx ピン(ADA4099-2 10 ピン LFCSP)に約  $0.6\mu A$  の 内部電流源があり、これらのピンを $-V_S$ にプル・ダウンし、アンプをデフォルトの増幅動作状態にします。シャットダウン状態にする必要がない場合は、SHDN ピンまたは SHDNx ピンと $-V_S$  ピンを配線によって接続してください。SHDN ピンまたは SHDNx ピンがフロート状態のままになっている場合、または大きなソース・インピーダンス(> $100\Omega$ )の電源で駆動されている場合は、 $-V_S$  電源ピンを小さい 1nF のコンデンサでバイパスしてください。これにより、浮遊信号が SHDN ピンや SHDNx ピンにカップリングしてシャットダウンがトリガされるのを防止できます。

#### グラウンド接続