# ANALOG フェムトアンペア入力バイアス電流 電位計アンプ

ニータシート

ADA4530-1

## 特長

低入力バイアス電流

±20 fA max @ T<sub>A</sub> = 25 °C (出荷テストで確認)

$\pm$  20 fA max @ -40 °C < T<sub>A</sub>< +85 °C

±250 fA max @ -40°C < T<sub>A</sub>< +125°C (出荷テストで確認) 低オフセット電圧: 50 µV max (規定の CMRR 範囲内)

オフセット・ドリフト:  $0.13 \mu V/^{\circ}C$  (typ) 、 $0.5 \mu V/^{\circ}C$  (max) オフセット電圧 100 μV (max) のガード・バッファを内蔵

低電圧ノイズ密度: 14 nV/√Hz @ 10 kHz

広帯域幅: ユニティゲイン・クロスオーバー: 2 MHz

電源電圧: 4.5 V ~ 16 V (±2.25 V ~ ±8 V)

動作温度: -40 °C ~ +125 °C

## アプリケーション

実験/解析用の計測器: 分光光度計、クロマトグラフ、質量分 析器、定電位/定電流電量分析

計測器: ピコアンメータ、電量計

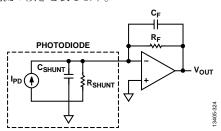

フォトダイオード用トランスインピーダンス・アンプ (TIA)、

電離箱、作業電極測定

化学センサー/容量センサー用の高インピーダンス・バッファ

### 概要

ADA4530-1 は、入力バイアス電流がフェムトアンペア $(10^{-15} A)$ レベルと小さいオペ・アンプです。ガード・バッファも内蔵し ているので、電位計としての使用に適しています。動作電圧範 囲は $4.5 \, \text{V} \sim 16 \, \text{V}$  であるため、従来の $5 \, \text{V}$ 、 $10 \, \text{V}$  の単電源シス テム、あるいは両電源  $\pm 2.5$  V、 $\pm 5$  V の両電源システムで動作 します。

ユーザーのシステムで確実に性能目標を満たすように、超低入 力バイアス電流は対象の温度で出荷時にテストされています。 ガード・バッファを内蔵しているので、プリント回路基板(PCB) 内で入力ピンをリーク電流から隔離して、基板部品数を最小限 に抑えることができるほか、システム設計が容易になります。 ADA4530-1 は、業界標準の表面実装型の8ピンSOICパッケー ジに収められています。敏感な入力ピン、電源、および出力ピ ンの間での信号の結合を防止し、ガード・リング・パターンの 配線を容易に行えるように最適化された独自のピン配置が採用 されています。

また ADA4530-1 は、非常に低いリーク電流が要求されるアプ リケーション・タイプに必要な低オフセット電圧、低オフセッ ト・ドリフト、低電圧ノイズ/電流ノイズ特性も達成していま す。システムのダイナミック・レンジが最大になるように、

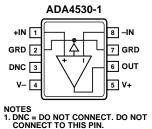

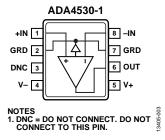

## ピン接続図

図 1.

ADA4530-1 は、10 kΩ 負荷時に電源レールの 30 mV 以内で駆 動可能なレール to レール出力段を備えています。

ADA4530-1 は -40 ℃ ~ +125 ℃ の工業温度範囲で動作し、8 ピ ン SOIC パッケージを採用しています。

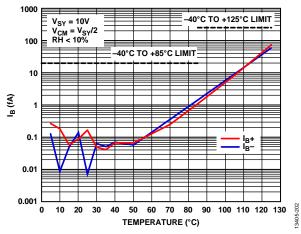

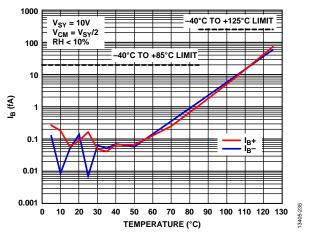

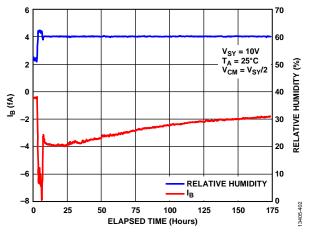

図 2. 入力バイアス電流(I<sub>B</sub>)と温度の関係、V<sub>SY</sub> = 10 V

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用に よって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利 の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告な、変更される場合があります。本紙記載の商標および登録商標 は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

電話 06(6350) 6868

©2016 Analog Devices, Inc. All rights reserved.

Rev. 0

社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー

アナログ・デバイセズ株式会社

# ADA4530-1

# 目次

| 特長                | 1  |

|-------------------|----|

| アプリケーション          | 1  |

| ピン接続図             | 1  |

| 概要                | 1  |

| 改訂履歴              | 2  |

| 仕様                | 3  |

| 公称電圧 5 V - 電気的特性  | 3  |

| 公称電圧 10 V - 電気的特性 | 5  |

| 公称電圧 15 V - 電気的特性 | 7  |

| 絶対最大定格            | 9  |

| 熱抵抗               | 9  |

| ESD に関する注意        | 9  |

| ピン配置およびピン機能の説明    | 10 |

| 代表的な性能特性          | 11 |

| メイン・アンプ、DC 性能     | 11 |

| メイン・アンプ、AC 性能     | 20 |

| ガード・アンプ           | 26 |

| 動作原理              | 28 |

| ESD 保護構造          | 28 |

| 入力段               | 28 |

| ゲイン段              | 29 |

| 出力段               | 29 |

| ガード・バッファ          | 29 |

| アプリケーション情報        | 30 |

| 入力保護              | 30 |

| 単電源とレール to レール出力  | 30 |

| 容量性負荷に対する安定性      | 30 |

| EMI 除去比           | 31 |

| 高インピーダンス測定        | 32 |

|-------------------|----|

| 入力バイアス電流          | 32 |

| 入力抵抗              | 33 |

| 入力オフセット電圧         | 33 |

| 絶縁抵抗              | 33 |

| ガーディング            | 34 |

| 誘電緩和              | 34 |

| 湿度の影響             | 36 |

| 汚染                | 37 |

| クリーニングと取り扱い       | 38 |

| ハンダ・ペーストの選択       | 38 |

| 電流ノイズに関する考慮事項     | 39 |

| レイアウトのガイドライン      | 42 |

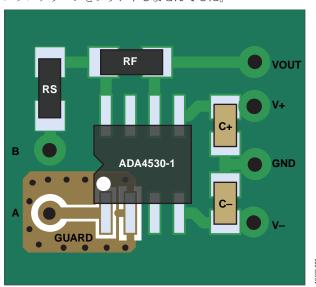

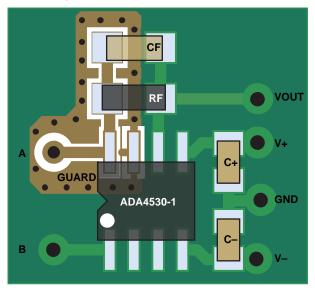

| ガーディング技法の物理的な実装   | 42 |

| ガード・リング           | 42 |

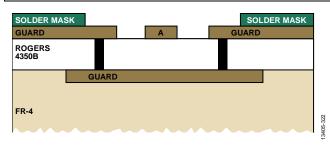

| ガード・プレーン          | 42 |

| ビア・フェンス           | 43 |

| ケーブルとコネクタ         | 43 |

| 静電干渉              | 43 |

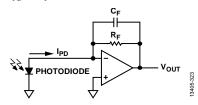

| フォトダイオード・インターフェース | 44 |

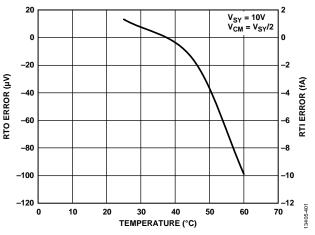

| DC 誤差解析           | 44 |

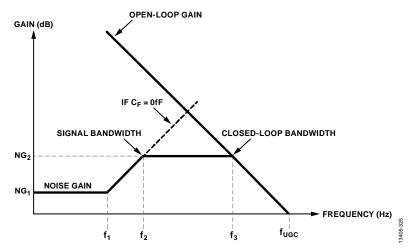

| AC 誤差解析           | 44 |

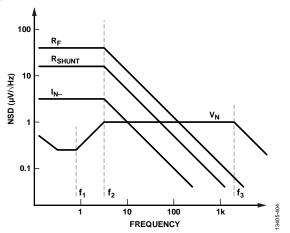

| ノイズ解析             | 45 |

| 設計の推奨事項           | 46 |

| 設計例               | 46 |

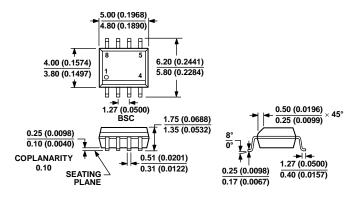

| 外形寸法              | 49 |

| オーダー・ガイド          | 49 |

## 改訂履歴

10/15—Revision 0: 初版

# 仕様

## 公称電圧 5 V - 電気的特性

特に指定のない限り、 $V_{SY}=4.5~V$ 、 $V_{CM}=V_{SY}/2$ 、 $T_A=25~C$ 。特に指定のない限り、代表的な仕様は特性評価からの分布の平均と等しい値です。特に指定のない限り、最小仕様および最大仕様は出荷時にテスト済みです。

表 1.

| Parameter <sup>1</sup>                   | Symbol                   | Test Conditions/Comments                                                                                                                                               | Min  | Тур   | Max  | Unit        |

|------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------------|

| INPUT CHARACTERISTICS                    |                          |                                                                                                                                                                        |      |       |      |             |

| Input Bias Current <sup>2, 3</sup>       | $I_B$                    | RH < 50%                                                                                                                                                               |      | <1    | ±20  | fA          |

|                                          |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}, \text{RH} < 50\%$                                                                                    |      |       | ±20  | fA          |

|                                          |                          | $-40^{\circ}$ C < $T_{A}$ < +125°C, RH < 50%                                                                                                                           |      |       | ±250 | fA          |

| Input Offset Current <sup>3</sup>        | $I_{OS}$                 | RH < 50%                                                                                                                                                               |      | <1    | ±20  | fA          |

| 1                                        |                          | $-40^{\circ}$ C < $T_{A}$ < $+125^{\circ}$ C, RH < $50\%$                                                                                                              |      |       | ±150 | fA          |

| Offset Voltage <sup>2, 4</sup>           | $V_{OS}$                 |                                                                                                                                                                        |      | +8    | ±40  | μV          |

| onge voluge                              | 103                      | $V_{CM} = 1.5 \text{ V to 3 V}$                                                                                                                                        |      | +9    | ±50  | μV          |

|                                          |                          | $V_{CM} = 1.5 \text{ V to 3 V}, 0^{\circ}\text{C} < T_{A} < 125^{\circ}\text{C}$                                                                                       |      | .,,   | ±70  | μV          |

|                                          |                          | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, 0 \text{ C} < T_A < 125 \text{ C}$<br>$V_{CM} = 1.5 \text{ V to } 3 \text{ V}, -40^{\circ}\text{C} < T_A < 0^{\circ}\text{C}$ |      |       | ±150 | μV          |

|                                          |                          | $V_{CM} = 1.5 \text{ V to 3 V}, 40 \text{ C} < 1.4 \text{ O C}$                                                                                                        |      |       |      |             |

| Off4 W-14 Duif42-4                       | ANT /AT                  | C.II                                                                                                                                                                   |      | .0.12 | ±300 | μV<br>V/0C  |

| Offset Voltage Drift <sup>2, 4</sup>     | $\Delta V_{OS}/\Delta T$ | 0°C < T <sub>A</sub> <125°C                                                                                                                                            |      | +0.13 | ±0.5 | μV/°C       |

|                                          |                          | -40°C $<$ T <sub>A</sub> $<$ 0°C                                                                                                                                       |      | -0.7  | ±2.8 | μV/°C       |

| Input Voltage Range                      | IVR                      |                                                                                                                                                                        | 0    |       | 3    | V           |

| Common-Mode Rejection Ratio              | CMRR                     | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}$                                                                                                                               | 92   | 114   |      | dB          |

|                                          |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                                     | 90   |       |      | dB          |

|                                          |                          | $V_{CM} = 0 \text{ V to } 3 \text{ V}$                                                                                                                                 | 73   |       |      | dB          |

| Large Signal Voltage Gain                | $A_{VO}$                 | $R_L = 2 \text{ k}\Omega \text{ to } V_{CM}, V_{OUT} = 0.2 \text{ V to } 4.3 \text{ V}$                                                                                | 120  | 143   |      | dB          |

|                                          |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                                     | 120  |       |      | dB          |

| Input Resistance                         | $R_{IN}$                 | $-40^{\circ}$ C < $T_{A}$ < $+125^{\circ}$ C                                                                                                                           |      | >100  |      | ΤΩ          |

| Input Capacitance                        | $C_{IN}$                 |                                                                                                                                                                        |      | 8     |      | pF          |

| OUTPUT CHARACTERISTICS                   |                          |                                                                                                                                                                        |      |       |      |             |

| Output Voltage High                      | $V_{\mathrm{OH}}$        | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                                                          | 4.47 | 4.49  |      | V           |

| 2 mg 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | · on                     | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$                                                                                                            | 4.46 |       |      | V           |

|                                          |                          | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                                                                                                   | 4.4  | 4.45  |      | v           |

|                                          |                          | $-40^{\circ}\text{C} < T_{\text{A}} < +125^{\circ}\text{C}$                                                                                                            | 4.38 | 1.15  |      | v           |

| Output Voltage Low                       | $V_{OL}$                 | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                                                          | 4.50 | 10    | 30   | mV          |

| Output Voltage Low                       | V OL                     | $-40^{\circ}\text{C} < T_{\text{A}} < +125^{\circ}\text{C}$                                                                                                            |      | 10    | 40   |             |

|                                          |                          |                                                                                                                                                                        |      | 20    |      | mV          |

|                                          |                          | $R_L = 2 k\Omega$ to $V_{CM}$                                                                                                                                          |      | 30    | 100  | mV          |

|                                          |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                                     |      |       | 120  | mV          |

| Short-Circuit Current                    | $I_{SC}$                 |                                                                                                                                                                        |      |       |      |             |

| Source                                   |                          |                                                                                                                                                                        |      | 15    |      | mA          |

| Sink                                     |                          |                                                                                                                                                                        |      | -30   |      | mA          |

| Closed-Loop Output Impedance             | $Z_{OUT}$                | $f = 1 \text{ MHz}, A_V = 1$                                                                                                                                           |      | 20    |      | Ω           |

| POWER SUPPLY                             |                          |                                                                                                                                                                        |      |       |      |             |

| Power Supply Rejection Ratio             | PSRR                     | $V_{SY} = 4.5 \text{ V to } 16 \text{ V}$                                                                                                                              | 130  | 150   |      | dB          |

|                                          |                          | $-40^{\circ}$ C < $T_{A}$ < $+125^{\circ}$ C                                                                                                                           | 130  |       |      | dB          |

| Supply Current                           | $I_{SY}$                 | $I_{OUT} = 0 \text{ mA}$                                                                                                                                               |      | 0.9   | 1.3  | mA          |

|                                          |                          | $-40^{\circ}$ C < $T_{A}$ < $+125^{\circ}$ C                                                                                                                           |      |       | 1.5  | mA          |

| DYNAMIC PERFORMANCE                      |                          | A                                                                                                                                                                      |      |       |      |             |

| Slew Rate                                | SR                       | $R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 1$                                                                                                               |      | 1.4   |      | V/µs        |

| Gain Bandwidth Product                   | GBP                      | $V_{IN} = 10 \text{ mV rms}, R_{L} = 10 \text{ k}\Omega, C_{L} = 10 \text{ pF},$                                                                                       |      | 2     |      | V/μs<br>MHz |

| Gain Bandwidin Product                   | OBP                      | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}22, C_L = 10 \text{ pF},$<br>$A_{V} = 100$                                                                              |      | 2     |      | IVITIZ      |

| Unity-Gain Crossover                     | UGC                      | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF},$                                                                                           |      | 2     |      | MHz         |

| •                                        |                          | $A_{VO} = 1$                                                                                                                                                           |      |       |      |             |

| -3 dB Closed-Loop Bandwidth              | $f_{-3dB}$               | $V_{IN}=10$ mVrms, $R_L=10$ k $\Omega$ , $C_L=10$ pF,                                                                                                                  |      | 6     |      | MHz         |

| ī                                        | - 112                    | $A_{V}=1$                                                                                                                                                              |      |       |      |             |

| Parameter <sup>1</sup>                    | Symbol                            | Test Conditions/Comments                                                                    | Min | Тур    | Max | Unit    |

|-------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------|-----|--------|-----|---------|

| Phase Margin                              | $\Phi_{ m M}$                     | $V_{IN}$ =10 mV rms, $R_L$ = 10 k $\Omega$ , $C_L$ = 10 pF, $A_{VO}$ = 1                    |     | 62     |     | Degrees |

| Settling Time to 0.1%                     | $t_{\rm S}$                       | $V_{IN} = 0.5 \text{ V step}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF},$<br>$A_V = -1$ |     | 5      |     | μs      |

| EMI Rejection Ratio of +IN                | EMIRR                             | $V_{IN} = 100 \text{ mV peak, } f = 400 \text{ MHz}$                                        |     | 50     |     | dB      |

|                                           |                                   | $V_{IN} = 100 \text{ mV peak, } f = 900 \text{ MHz}$                                        |     | 60     |     | dB      |

|                                           |                                   | $V_{IN} = 100 \text{ mV peak, } f = 1800 \text{ MHz}$                                       |     | 80     |     | dB      |

|                                           |                                   | $V_{IN} = 100 \text{ mV peak}, f = 2400 \text{ MHz}$                                        |     | 90     |     | dB      |

| NOISE PERFORMANCE                         |                                   |                                                                                             |     |        |     |         |

| Peak-to-Peak Voltage Noise                | e <sub>N</sub> p-p                | f = 0.1  Hz to  10  Hz                                                                      |     | 4      |     | μV p-p  |

| Voltage Noise Density                     | $e_N$                             | f = 10  Hz                                                                                  |     | 80     |     | nV/√Hz  |

|                                           |                                   | f = 1  kHz                                                                                  |     | 16     |     | nV/√Hz  |

|                                           |                                   | f = 10  kHz                                                                                 |     | 14     |     | nV/√Hz  |

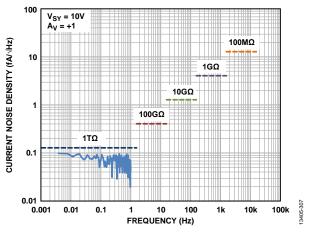

| Current Noise Density                     | $I_N$                             | f = 0.1 Hz                                                                                  |     | 0.07   |     | fA/√Hz  |

| Total Harmonic Distortion + Noise         | THD + N                           | $A_V = 1$ , $f = 1$ kHz, $V_{IN} = 0.5$ V rms                                               |     |        |     |         |

| Bandwidth = $90 \text{ kHz}$              |                                   |                                                                                             |     | 0.003  |     | %       |

| Bandwidth = $500 \text{ kHz}$             |                                   |                                                                                             |     | 0.0045 |     | %       |

| GUARD BUFFER                              |                                   |                                                                                             |     |        |     |         |

| Guard OffsetVoltage <sup>2, 4, 5</sup>    | $V_{GOS}$                         | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}$                                                    |     | 15     | 100 | μV      |

|                                           |                                   | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, 0^{\circ}\text{C} < T_{A} < 125^{\circ}\text{C}$   |     |        | 120 | μV      |

|                                           |                                   | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, -40^{\circ}\text{C} < T_{A} < 0^{\circ}\text{C}$   |     |        | 250 | μV      |

|                                           |                                   | $V_{CM} = 0.1 \text{ V to 3 V}$                                                             |     |        | 150 | μV      |

| Guard OffsetVoltage Drift <sup>2, 4</sup> | $\frac{\Delta V_{GOS}/\Delta}{T}$ | $0^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                            |     | 0.18   | 1   | μV/°C   |

|                                           |                                   | $-40$ °C < $T_A$ < $0$ °C                                                                   |     | 1.4    | 7   | μV/°C   |

| Output Impedance                          | $Z_{GOUT}$                        |                                                                                             |     | 1      |     | kΩ      |

| Output Voltage Range                      |                                   | $V_{GOS}$ < 150 $\mu$ V                                                                     | 0.1 |        | 3   | V       |

| -3 dB Bandwidth                           | $f_{-3dBGUARD}$                   | $V_{IN} = 10 \text{ mV rms}, C_L = 10 \text{ pF}$                                           |     | 5.5    |     | MHz     |

¹ これらの仕様は、 $5\,V\pm10\,\%$  電源の性能を表します。すべての仕様が最悪の条件である  $4.5\,V$  電源電圧での測定値です。  $^2-40\,^\circ\mathrm{C}<\mathrm{T_A}<+85\,^\circ\mathrm{C}$  および  $-40\,^\circ\mathrm{C}<\mathrm{T_A}<0\,^\circ\mathrm{C}$  の最大仕様は、特性評価により確保されています。  $^3\,\mathrm{RH}$  は相対湿度です(詳細については、Humidity Effects のセクションを参照してください)。

<sup>4</sup>代表的な仕様は、特性評価からの分布の平均に標準偏差を加えた値に等しくなります。

$<sup>^5</sup>$ ガード・オフセット電圧は、ガード出力と非反転入力の間の電圧差です。

## 公称電圧 10 V - 電気的特性

特に指定のない限り、 $V_{SY}=10~V$ 、 $V_{CM}=V_{SY}/2$ 、 $T_A=25~C$ 。特に指定のない限り、代表的な仕様は特性評価からの分布の平均と等しい値です。特に指定のない限り、最小仕様および最大仕様は出荷時にテスト済みです。

表 2

| Parameter <sup>1</sup>               | Symbol                   | Test Conditions/Comments                                                                                                              | Min  | Тур   | Max       | Unit              |

|--------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------|-------------------|

| INPUT CHARACTERISTICS                |                          |                                                                                                                                       |      |       |           |                   |

| Input Bias Current <sup>2, 3</sup>   | $I_{\mathrm{B}}$         | RH < 50%                                                                                                                              |      | <1    | ±20       | fA                |

|                                      |                          | $-40^{\circ}$ C < $T_{A}$ < $+85^{\circ}$ C, RH < $50\%$                                                                              |      |       | ±20       | fA                |

|                                      |                          | $-40$ °C < $T_A$ < $+125$ °C, RH < $50$ %                                                                                             |      |       | ±250      | fA                |

| Input Offset Current <sup>3</sup>    | $I_{OS}$                 | RH < 50%                                                                                                                              |      | <1    | ±20       | fA                |

|                                      |                          | $-40$ °C < $T_A$ < $+125$ °C, RH < $50$ %                                                                                             |      |       | ±150      | fA                |

| Offset Voltage <sup>2, 4</sup>       | $V_{OS}$                 |                                                                                                                                       |      | +8    | $\pm 40$  | μV                |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}$                                                                                            |      | +9    | ±50       | μV                |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}, 0^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$                                             |      |       | ±70       | μV                |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}, -40^{\circ}\text{C} < T_A < 0^{\circ}\text{C}$                                             |      |       | ±150      | μV                |

|                                      |                          | $V_{CM} = 0 \text{ V to } 8.5 \text{ V}$                                                                                              |      |       | ±300      | μV                |

| Offset Voltage Drift <sup>2, 4</sup> | $\Delta V_{OS}/\Delta T$ | $0^{\circ}\text{C} < \text{T}_{\text{A}} < 125^{\circ}\text{C}$                                                                       |      | +0.13 | ±0.5      | $\mu V/^{\circ}C$ |

|                                      |                          | $-40^{\circ}$ C $<$ T <sub>A</sub> $<$ $0^{\circ}$ C                                                                                  |      | -0.7  | $\pm 2.8$ | $\mu V/^{\circ}C$ |

| Input Voltage Range                  | IVR                      |                                                                                                                                       | 0    |       | 8.5       | V                 |

| Common-Mode Rejection Ratio          | CMRR                     | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}$                                                                                            | 105  | 114   |           | dB                |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    | 100  |       |           | dB                |

|                                      |                          | $V_{CM} = 0 \text{ V to } 8.5 \text{ V}$                                                                                              | 87   |       |           | dB                |

| Large Signal Voltage Gain            | $A_{VO}$                 | $R_L = 2 \text{ k}\Omega \text{ to } V_{CM}, V_{OUT} = 0.5 \text{ V to } 9.5 \text{ V}$                                               | 125  | 150   |           | dB                |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    | 125  |       |           | dB                |

| Input Resistance                     | $R_{IN}$                 | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    |      | >100  |           | ΤΩ                |

| Input Capacitance                    | $C_{IN}$                 |                                                                                                                                       |      | 8     |           | pF                |

| OUTPUT CHARACTERISTICS               |                          |                                                                                                                                       |      |       |           |                   |

| Output Voltage High                  | $V_{OH}$                 | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                         | 9.96 | 9.97  |           | V                 |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$                                                                           | 9.94 |       |           | V                 |

|                                      |                          | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                                                                  | 9.93 | 9.87  |           | V                 |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    | 9.75 |       |           | V                 |

| Output Voltage Low                   | $V_{OL}$                 | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                         |      | 15    | 40        | mV                |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$                                                                           |      |       | 60        | mV                |

|                                      |                          | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                                                                  |      | 70    | 170       | mV                |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    |      |       | 250       | mV                |

| Short-Circuit Current                | $I_{SC}$                 |                                                                                                                                       |      |       |           |                   |

| Source                               | 50                       |                                                                                                                                       |      | 15    |           | mA                |

| Sink                                 |                          |                                                                                                                                       |      | -30   |           | mA                |

| Closed-Loop Output Impedance         | $Z_{OUT}$                | $f = 1 \text{ MHz}, A_{V} = 1$                                                                                                        |      | 20    |           | Ω                 |

| POWER SUPPLY                         | 001                      | , ,                                                                                                                                   |      |       |           |                   |

| Power Supply Rejection Ratio         | PSRR                     | $V_{SY} = 4.5 \text{ V to } 16 \text{ V}$                                                                                             | 130  | 150   |           | dB                |

| Tower Suppry Rejection Ratio         | Torus                    | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$                                                                           | 130  | 150   |           | dB                |

| Supply Current                       | $I_{SY}$                 | $I_{OUT} = 0 \text{ mA}$                                                                                                              | 130  | 0.9   | 1.3       | mA                |

| Supply Carront                       | -51                      | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                    |      | 0.7   | 1.5       | mA                |

| DYNAMIC PERFORMANCE                  | +                        | C - 1 <sub>A</sub> < 1125 C                                                                                                           |      |       | 1.5       | 111/1             |

| Slew Rate                            | SR                       | $R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 1$                                                                              |      | 1.4   |           | V/µs              |

| Gain Bandwidth Product               | GBP                      | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF},$                                                          |      | 2     |           | V/μs<br>MHz       |

|                                      |                          | $A_{V} = 100$                                                                                                                         |      |       |           |                   |

| Unity-Gain Crossover                 | UGC                      | $\begin{aligned} V_{\rm IN} &= 10 \text{ mV rms, } R_L = 10 \text{ k}\Omega, \ C_L = 10 \text{ pF,} \\ A_{\rm VO} &= 1 \end{aligned}$ |      | 2     |           | MHz               |

| -3 dB Closed-Loop Bandwidth          | $f_{-3dB}$               | $V_{IN} = 10$ mV rms, $R_L = 10$ k $\Omega$ , $C_L = 10$ pF, $A_V = 1$                                                                |      | 6     |           | MHz               |

| Phase Margin                         | $\Phi_{\mathrm{M}}$      | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF},$<br>$A_{VO} = 1$                                          |      | 62    |           | Degrees           |

| Parameter <sup>1</sup>                    | Symbol                    | Test Conditions/Comments                                                                    | Min | Тур    | Max | Unit              |

|-------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------|-----|--------|-----|-------------------|

| Settling Time to 0.1%                     | t <sub>S</sub>            | $V_{\rm IN}=1$ V step, $R_{\rm L}=10$ k $\Omega$ , $C_{\rm L}=10$ pF, $A_{\rm V}=-1$        |     | 6      |     | μs                |

| EMI Rejection Ratio of +IN                | EMIRR                     | $V_{IN} = 100 \text{ mV peak}, f = 400 \text{ MHz}$                                         |     | 50     |     | dB                |

|                                           |                           | $V_{IN} = 100 \text{ mV peak, } f = 900 \text{ MHz}$                                        |     | 60     |     | dB                |

|                                           |                           | $V_{IN} = 100 \text{ mV peak, } f = 1800 \text{ MHz}$                                       |     | 80     |     | dB                |

|                                           |                           | $V_{IN} = 100 \text{ mV}$ peak, $f = 2400 \text{ MHz}$                                      |     | 90     |     | dB                |

| NOISE PERFORMANCE                         |                           |                                                                                             |     |        |     |                   |

| Peak-to-Peak Voltage Noise                | e <sub>N</sub> p-p        | f = 0.1  Hz to  10  Hz                                                                      |     | 4      |     | μV p-p            |

| Voltage Noise Density                     | $e_N$                     | f = 10  Hz                                                                                  |     | 80     |     | nV/√H2            |

|                                           |                           | f = 1  kHz                                                                                  |     | 16     |     | nV/√H2            |

|                                           |                           | f = 10  kHz                                                                                 |     | 14     |     | nV/√H2            |

| Current Noise Density                     | $I_N$                     | f = 0.1  Hz                                                                                 |     | 0.07   |     | fA/√Hz            |

| Total Harmonic Distortion + Noise         | THD+N                     | $A_{V} = 1$ , $f = 1$ kHz, $V_{IN} = 2$ V rms                                               |     |        |     |                   |

| Bandwidth = $90 \text{ kHz}$              |                           |                                                                                             |     | 0.0015 |     | %                 |

| Bandwidth = $500 \text{ kHz}$             |                           |                                                                                             |     | 0.0025 |     | %                 |

| GUARD BUFFER                              |                           |                                                                                             |     |        |     |                   |

| Guard Offset Voltage <sup>2, 4, 5</sup>   | $V_{GOS}$                 | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}$                                                  |     | 15     | 100 | μV                |

|                                           |                           | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}, 0^{\circ}\text{C} < T_{A} < 125^{\circ}\text{C}$ |     |        | 120 | μV                |

|                                           |                           | $V_{CM} = 1.5 \text{ V to } 8.5 \text{ V}, -40^{\circ}\text{C} < T_{A} < 0^{\circ}\text{C}$ |     |        | 250 | μV                |

|                                           |                           | $V_{CM} = 0.1 \text{ V to } 8.5 \text{ V}$                                                  |     |        | 150 | μV                |

| Guard OffsetVoltage Drift <sup>2, 4</sup> | $\Delta V_{GOS}/\Delta T$ | $0^{\circ}\text{C} < \text{T}_{\text{A}} < 125^{\circ}\text{C}$                             |     | 0.18   | 1   | $\mu V/^{\circ}C$ |

|                                           |                           | $-40$ °C < $T_A$ < 0°C                                                                      |     | 1.4    | 7   | μV/°C             |

| Output Impedance                          | $Z_{GOUT}$                |                                                                                             |     | 1      |     | $k\Omega$         |

| Output Voltage Range                      |                           | $V_{GOS}$ < 150 $\mu V$                                                                     | 0.1 |        | 8.5 | V                 |

| −3 dB Bandwidth                           | $f_{-3dBGUARD}$           | $V_{IN}=10$ m $V$ rms, $C_L=10$ p $F$                                                       |     | 5.5    |     | MHz               |

$<sup>^{\</sup>rm I}$  これらの仕様は、10 V ± 10 % 電源の性能を表します。これらの仕様は、10 V 電源の性能を表します。

$<sup>^{1}</sup>$  これらのLikeは、 $10 \, \text{V} \pm 10 \, \text{%}$  电原の注配と表します。 これらのLikeは、 $10 \, \text{V}$  电原の注配と表します。  $^{2}$   $-40 \, \text{°C} < T_{A} < +85 \, \text{°C}$  および $-40 \, \text{°C} < T_{A} < 0 \, \text{°C}$  の最大仕様は、特性評価により確保されています。  $^{3}$  RH は相対湿度です(詳細については、Humidity Effects のセクションを参照してください)。  $^{4}$  これらの代表的な仕様は、特性評価からの分布の平均に標準偏差を加えた値と等しくなります。  $^{5}$  ガード・オフセット電圧は、ガード出力と非反転入力の間の電圧差です。

## 公称電圧 15 V - 電気的特性

特に指定のない限り、 $V_{SY}=16~V$ 、 $V_{CM}=V_{SY}/2$ 、 $T_A=25~C$ 。特に指定のない限り、代表的な仕様は特性評価からの分布の平均と等しい値です。特に指定のない限り、最小仕様および最大仕様は出荷時にテスト済みです。

表 3.

| Parameter <sup>1</sup>               | Symbol                   | Test Conditions/Comments                                                                                                                            | Min   | Тур   | Max      | Unit        |

|--------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----------|-------------|

| INPUT CHARACTERISTICS                |                          |                                                                                                                                                     |       |       |          |             |

| Input Bias Current <sup>2, 3</sup>   | $I_B$                    | RH < 50%                                                                                                                                            |       | <1    | ±20      | fA          |

|                                      |                          | $-40$ °C < $T_A$ < $+85$ °C, RH < $50$ %                                                                                                            |       |       | $\pm 20$ | fA          |

|                                      |                          | $-40$ °C < $T_A$ < +125°C, RH < 50%                                                                                                                 |       |       | ±250     | fA          |

| Input Offset Current                 | $I_{OS}$                 | RH < 50%                                                                                                                                            |       | <1    | $\pm 20$ | fA          |

|                                      |                          | $-40$ °C < $T_A$ < $+125$ °C, RH < $50$ %                                                                                                           |       |       | ±150     | fA          |

| Offset Voltage <sup>2, 4</sup>       | V <sub>os</sub>          |                                                                                                                                                     |       | +8    | ±40      | μV          |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}$                                                                                                         |       | +9    | ±50      | μV          |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}, 0^{\circ}\text{C} < T_{A} < 125^{\circ}\text{C}$                                                        |       |       | ±70      | μV          |

|                                      |                          | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}, -40^{\circ}\text{C} < T_A < 0^{\circ}\text{C}$                                                          |       |       | ±150     | μV          |

|                                      |                          | $V_{CM} = 0 \text{ V to } 14.5 \text{ V}$                                                                                                           |       |       | ±300     | μV          |

| Offset Voltage Drift <sup>2, 4</sup> | $\Delta V_{OS}/\Delta T$ | $0^{\circ}\text{C} < \text{T}_{\text{A}} < 125^{\circ}\text{C}$                                                                                     |       | +0.13 | ±0.5     | μV/°C       |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 0^{\circ}\text{C}$                                                                                     |       | -0.7  | ±2.8     | μV/°C       |

| Input Voltage Range                  | IVR                      |                                                                                                                                                     | 0     |       | 14.5     | V           |

| Common-Mode Rejection Ratio          | CMRR                     | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}$                                                                                                         | 110   | 114   |          | dB          |

| -                                    |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  | 105   |       |          | dB          |

|                                      |                          | $V_{CM} = 0 \text{ V to } 14.5 \text{ V}$                                                                                                           | 93    |       |          | dB          |

| Large Signal Voltage Gain            | $A_{VO}$                 | $R_L = 2 \text{ k}\Omega \text{ to } V_{CM}, V_{OUT} = 0.5 \text{ V to } 15.5 \text{ V}$                                                            | 130   | 155   |          | dB          |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  | 125   |       |          | dB          |

| Input Resistance                     | $R_{IN}$                 | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  |       | >100  |          | ΤΩ          |

| Input Capacitance                    | $C_{IN}$                 |                                                                                                                                                     |       | 8     |          | pF          |

| OUTPUT CHARACTERISTICS               |                          |                                                                                                                                                     |       |       |          | 1           |

| Output Voltage High                  | $V_{OH}$                 | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                                       | 15.93 | 15.95 |          | V           |

| 1 2 2                                |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  | 15.9  |       |          | V           |

|                                      |                          | $R_L = 2 k\Omega$ to $V_{CM}$                                                                                                                       | 15.72 | 15.78 |          | V           |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  | 15.58 |       |          | v           |

| Output Voltage Low                   | $V_{ m OL}$              | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                                                                       |       | 25    | 70       | mV          |

|                                      | OE.                      | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}$                                                                                  |       |       | 100      | mV          |

|                                      |                          | $R_L = 2 k\Omega$ to $V_{CM}$                                                                                                                       |       | 115   | 280      | mV          |

|                                      |                          | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$                                                                                         |       | 110   | 420      | mV          |

| Short-Circuit Current                | $I_{SC}$                 | 10 C 1A ( 120 C                                                                                                                                     |       |       | .20      | 111,        |

| Source                               | -30                      |                                                                                                                                                     |       | 15    |          | mA          |

| Sink                                 |                          |                                                                                                                                                     |       | -30   |          | mA          |

| Closed-Loop Output Impedance         | $Z_{OUT}$                | $f = 1 \text{ MHz}, A_V = 1$                                                                                                                        |       | 20    |          | Ω           |

| POWER SUPPLY                         | 2001                     | 1 – 1 11112, 11v – 1                                                                                                                                |       | 20    |          | 1           |

| Power Supply Rejection Ratio         | PSRR                     | $V_{SY} = 4.5 \text{ V to } 16 \text{ V}$                                                                                                           | 130   | 150   |          | dB          |

| Tower Supply Rejection Ratio         | TSICIC                   | $-40^{\circ}\text{C} < T_{A} < +125^{\circ}\text{C}$                                                                                                | 130   | 130   |          | dB          |

| Supply Current                       | $I_{SY}$                 | $I_{OUT} = 0 \text{ mA}$                                                                                                                            | 130   | 0.9   | 1.3      | mA          |

| Suppry Current                       | 1SY                      | $-40^{\circ}\text{C} < T_{\text{A}} < +125^{\circ}\text{C}$                                                                                         |       | 0.7   | 1.5      | mA          |

| DYNAMIC PERFORMANCE                  |                          | 70 C \ 1A\ T123 C                                                                                                                                   |       |       | 1.J      | 111/1       |

| Slew Rate                            | SR                       | $R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 1$                                                                                            |       | 1.4   |          | V/µs        |

| Gain bandwidth Product               | GBP                      | $K_L = 10 \text{ k}\Omega$ , $C_L = 10 \text{ pF}$ , $A_V = 1$<br>$V_{IN} = 10 \text{mVrms}$ , $R_L = 10 \text{ k}\Omega$ , $C_L = 10 \text{ pF}$ , |       | 2     |          | V/μs<br>MHz |

|                                      |                          | $A_{V} = 100$                                                                                                                                       |       |       |          |             |

| Unity-Gain Crossover                 | UGC                      | $V_{IN}=10$ mVrms, $R_L=10$ k $\Omega$ , $C_L=10$ pF,<br>$A_{VO}=1$                                                                                 |       | 2     |          | MHz         |

| -3 dB Closed-Loop Bandwidth          | $f_{-3dB}$               | $V_{IN}=10$ m $V$ rms, $R_L=10$ k $\Omega$ , $C_L=10$ p $F$ , $A_V=1$                                                                               |       | 6     |          | MHz         |

| Phase Margin                         | $\Phi_{ m M}$            | $V_{IN}=10 \text{mVrms}, R_L=10 \text{ k}\Omega, C_L=10 \text{ pF}, A_{VO}=1$                                                                       |       | 62    |          | Degrees     |

| Parameter <sup>1</sup>                    | Symbol                        | Test Conditions/Comments                                                                     | Min | Тур    | Max  | Unit              |

|-------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------|-----|--------|------|-------------------|

| Settling Time to 0.1%                     | $t_{\rm S}$                   | $V_{IN} = 1$ V step, $R_L = 10$ k $\Omega$ , $C_L = 10$ pF, $A_V = -1$                       |     | 6      |      | μs                |

| EMI Rejection Ratio of +IN                | EMIRR                         | $V_{IN} = 100 \text{ mV peak}, f = 400 \text{ MHz}$                                          |     | 50     |      | dB                |

|                                           |                               | $V_{IN} = 100 \text{ mV peak}, f = 900 \text{ MHz}$                                          |     | 60     |      | dB                |

|                                           |                               | $V_{IN} = 100 \text{ mV peak}, f = 1800 \text{ MHz}$                                         |     | 80     |      | dB                |

|                                           |                               | $V_{IN} = 100 \text{ mV peak}, f = 2400 \text{ MHz}$                                         |     | 90     |      | dB                |

| NOISE PERFORMANCE                         |                               |                                                                                              |     |        |      |                   |

| Peak-to-Peak Voltage Noise                | e <sub>N</sub> p-p            | f = 0.1  Hz to  10  Hz                                                                       |     | 4      |      | μV p-p            |

| Voltage Noise Density                     | $e_N$                         | f = 10  Hz                                                                                   |     | 80     |      | nV/√H2            |

|                                           | $e_N$                         | f = 1  kHz                                                                                   |     | 16     |      | nV/√H2            |

|                                           | $e_N$                         | f = 10  kHz                                                                                  |     | 14     |      | nV/√H2            |

| Current Noise Density                     | $I_N$                         | f = 0.1  Hz                                                                                  |     | 0.07   |      | fA/√Hz            |

| Total Harmonic Distortion + Noise         | THD+N                         | $A_V = 1$ , $f = 1$ kHz, $V_{IN} = 4.5$ V rms                                                |     |        |      |                   |

| Bandwidth = $90 \text{ kHz}$              |                               |                                                                                              |     | 0.0012 |      | %                 |

| Bandwidth = $500 \text{ kHz}$             |                               |                                                                                              |     | 0.003  |      | %                 |

| GUARD BUFFER                              |                               |                                                                                              |     |        |      |                   |

| Guard OffsetVoltage <sup>4,5</sup>        | $V_{GOS}$                     | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}$                                                  |     | 15     | 100  | μV                |

|                                           |                               | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}, 0^{\circ}\text{C} < T_{A} < 125^{\circ}\text{C}$ |     |        | 120  | μV                |

|                                           |                               | $V_{CM} = 1.5 \text{ V to } 14.5 \text{ V}, -40^{\circ}\text{C} < T_A < 0^{\circ}\text{C}$   |     |        | 250  | $\mu V$           |

|                                           |                               | $V_{CM} = 0.1 \text{ V to } 14.5 \text{ V}$                                                  |     |        | 150  | $\mu V$           |

| Guard OffsetVoltage Drift <sup>2, 4</sup> | $\Delta V_{GOS}\!/\!\Delta T$ | $0^{\circ}C < T_{A} < +125^{\circ}C$                                                         |     | 0.18   | 1    | $\mu V/^{\circ}C$ |

|                                           |                               | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 0^{\circ}\text{C}$                              |     | 1.4    | 7    | $\mu V/^{\circ}C$ |

| Output Impedance                          | $Z_{GOUT}$                    |                                                                                              |     | 1      |      | $k\Omega$         |

| Output Voltage Range                      |                               | $V_{GOS}$ < 150 $\mu V$                                                                      | 0.1 |        | 14.5 | V                 |

| -3 dB Bandwidth                           | $f_{-3dBGUARD}$               | $V_{IN} = 10 \text{ mV rms}, C_L = 10 \text{ pF}$                                            |     | 5.5    |      | MHz               |

<sup>1</sup> これらの仕様は、 $15\,V\pm10\,\%$  電源の性能を表します。すべての仕様が最悪の条件である  $16\,V$  電源電圧での測定値です。  $^2$   $-40\,^\circ\mathrm{C}<\mathrm{T_A}<+85\,^\circ\mathrm{C}$  および  $-40\,^\circ\mathrm{C}<\mathrm{T_A}<0\,^\circ\mathrm{C}$  の最大仕様は、特性評価により確保されています。  $^3$  RH は相対湿度です(詳細については、Humidity Effects のセクションを参照してください)。  $^4$  これらの代表的な仕様は、特性評価からの分布の平均に標準偏差を加えた値と等しくなります。  $^5$  ガード・オフセット電圧は、ガード出力と非反転入力の間の電圧差です。

## 絶対最大定格

表 4.

| Parameter                                             | Rating                       |

|-------------------------------------------------------|------------------------------|

| Supply Voltage                                        | 17 V                         |

| Input Voltage                                         | (V-) - 0.3V to $(V+) + 0.3V$ |

| Input Current <sup>1</sup>                            | 10mA                         |

| Differential Input Voltage                            | ±0.7V                        |

| Output Short-Circuit Duration to GND                  | Indefinite                   |

| Storage Temperature Range                             | −65°C to +150°C              |

| Operating Temperature Range                           | −40°C to +125°C              |

| Junction Temperature Range                            | −65°C to +150°C              |

| Lead Temperature (Soldering, 60 sec)                  | 300°C                        |

| ESD                                                   |                              |

| Human Body Model <sup>2</sup>                         | 4 kV                         |

| FieldInduced ChargedDevice Model (FICDM) <sup>3</sup> | 1.25 kV                      |

$<sup>^{1}</sup>$ 入力ピンには、電源ピンへのクランプ・ダイオードが付いています。入力 信号が電源レールを  $0.3\,\mathrm{V}$  上回る場合は、入力電流を  $10\,\mathrm{mA}$  以下に制限してください。

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を引き起こす場合があります。この規定はストレ ス定格のみを指定するものであり、この仕様の動作のセクショ ンに記載する規定値以上でのデバイス動作を定めたものではあ りません。製品を長時間にわたり絶対最大定格状態に置くと、 製品の信頼性に影響を与えることがあります。

#### 熱抵抗

θJA は最悪の条件、すなわち、標準の4層 JEDEC ボードに表面 実装パッケージをハンダ付けした状態で仕様規定されています。

表 5.熱抵抗

| Package Type | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|--------------|---------------|-----------------|------|

| 8-Lead SOIC  | 122           | 41              | °C/W |

## ESD に関する注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

<sup>&</sup>lt;sup>2</sup> 適用規格 ESDA/JEDEC JS-001-2012。

³適用規格 JESD22-C101-E(JEDEC の ESD FICDM 規格)。

# ピン配置およびピン機能の説明

図 3. ピン配置

表 6. ピン機能の説明

| ピン番号 | 記号  | 説明                    |

|------|-----|-----------------------|

| 1    | +IN | 非反転入力。                |

| 2    | GRD | ガード。                  |

| 3    | DNC | 接続なし。このピンは接続しないでください。 |

| 4    | V-  | 負電源電圧。                |

| 5    | V+  | 正電源電圧。                |

| 6    | OUT | 出力。                   |

| 7    | GRD | ガード。                  |

| 8    | -IN | 反転入力。                 |

# 代表的な性能特性

## メイン・アンプ、DC 性能

特に指定のない限り、TA=25℃。

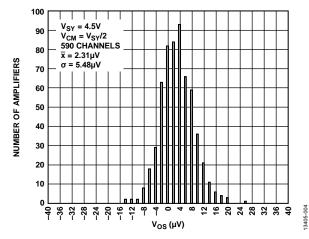

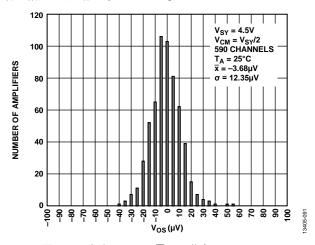

図 4. 入力オフセット電圧の分布、V<sub>SY</sub> = 4.5 V

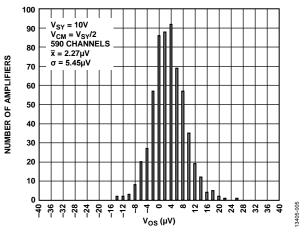

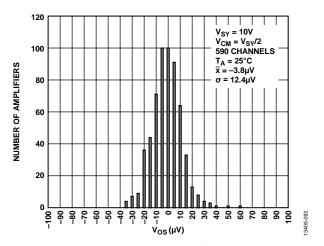

図 5. 入力オフセット電圧の分布、V<sub>SY</sub> = 10 V

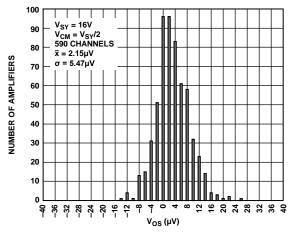

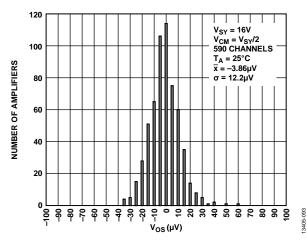

図 6. 入力オフセット電圧の分布、V<sub>SY</sub> = 16 V

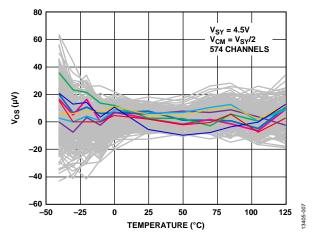

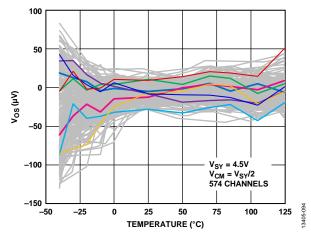

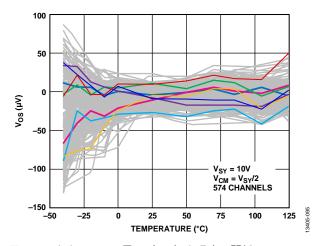

図 7. 入力オフセット電圧( $V_{OS}$ )と温度の関係、 $V_{SY} = 4.5 V$

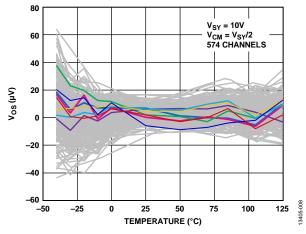

図 8. 入力オフセット電圧 (Vos) と温度の関係、Vsy = 10 V

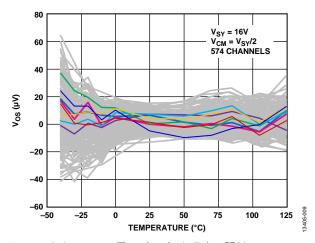

図 9. 入力オフセット電圧( $V_{OS}$ )と温度の関係、 $V_{SY}=16~V$

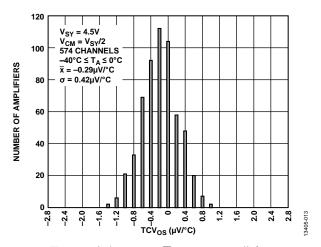

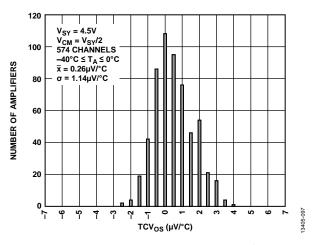

図 10. 入力オフセット電圧ドリフトの分布、-40 °C  $\leq$   $T_A \leq$  0 °C、 $V_{SY} = 4.5$  V

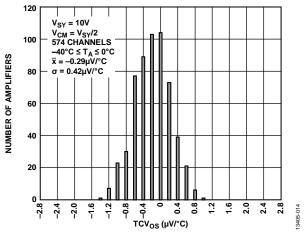

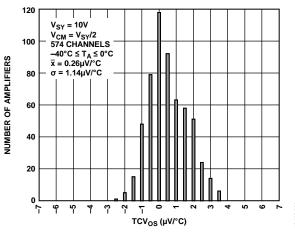

図 11. 入力オフセット電圧ドリフトの分布、 -40 °C  $\leq$  T<sub>A</sub>  $\leq$  0 °C、  $V_{SY}$  = 10 V

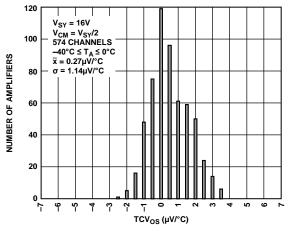

図 12. 入力オフセット電圧ドリフトの分布、  $-40\ ^{\circ}C \le T_{A} \le 0\ ^{\circ}C$ 、  $V_{SY}=16\ V$

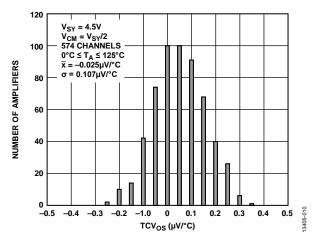

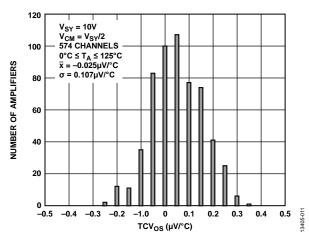

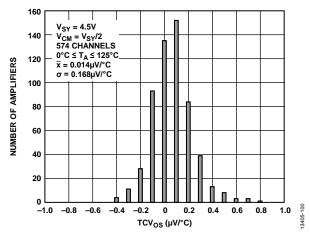

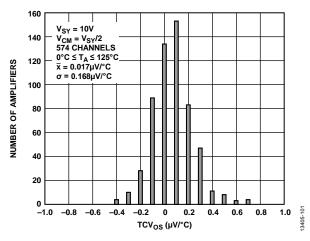

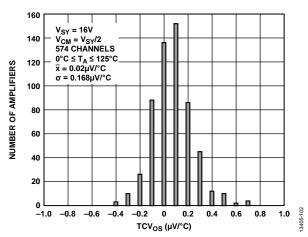

図 13. 入力オフセット電圧ドリフトの分布、0 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C、  $V_{SY} = 4.5 \ V$

図 14. 入力オフセット電圧ドリフトの分布、  $0 \, ^{\circ} \text{C} \leq T_{A} \leq 125 \, ^{\circ} \text{C}$ 、  $V_{SY} = 10 \, \text{V}$

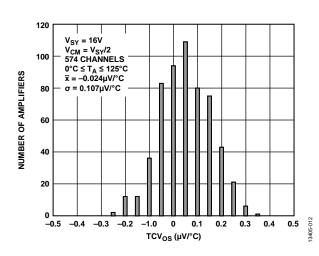

図 15. 入力オフセット電圧ドリフトの分布、  $0 \, ^{\circ} \text{C} \leq \text{T}_{A} \leq 125 \, ^{\circ} \text{C}$ 、  $\text{V}_{\text{SY}} = 16 \, \text{V}$

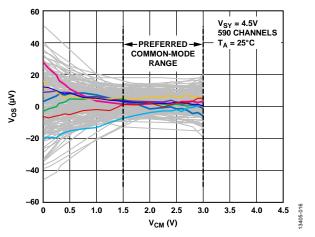

図 16. 入力オフセット電圧( $V_{OS}$ )とコモンモード電圧( $V_{CM}$ )の関係、 $V_{SY}=4.5\ V$

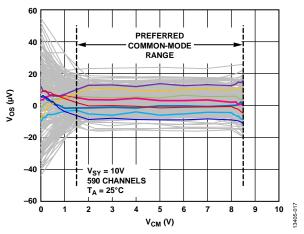

図 17. 入力オフセット電圧( $V_{OS}$ )とコモンモード電圧( $V_{CM}$ )の関係、 $V_{SY}=10\ V$

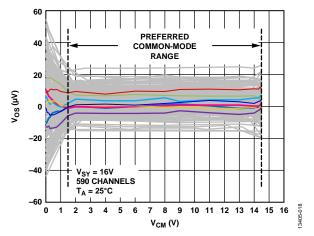

図 18. 入力オフセット電圧( $V_{OS}$ )とコモンモード電圧( $V_{CM}$ ) の関係、 $V_{SY}$  = 16 V

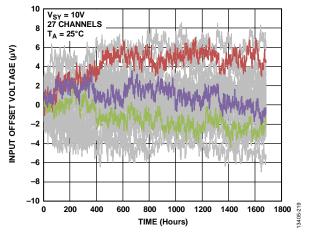

図 19. Vos 長時間ドリフト

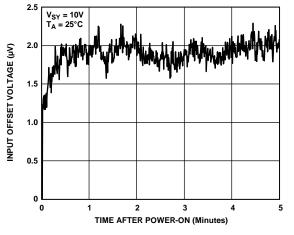

図 20. Vos ウォームアップ時間

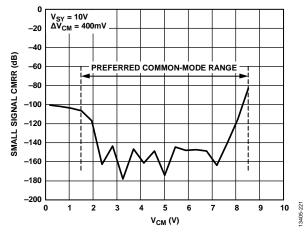

図 21. 小信号 CMRR とコモンモード電圧の関係

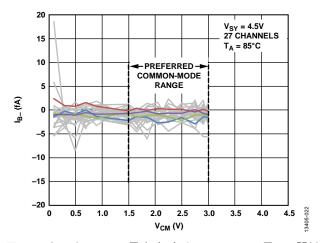

図 22. 反転入力バイアス電流( $I_{B^-}$ )とコモンモード電圧の関係 ( $V_{CM}$ )、 $V_{SY}=4.5~V$ 、 $T_A=85~C$

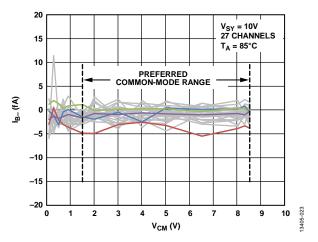

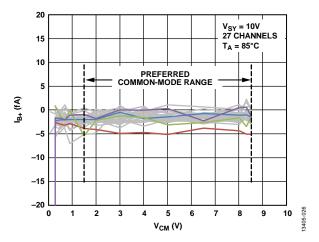

図 23. 反転入力バイアス電流( $I_{B-}$ )とコモンモード電圧の関係 ( $V_{CM}$ ) 、 $V_{SY}$  = 10 V、 $T_A$  = 85  $^{\circ}$ C

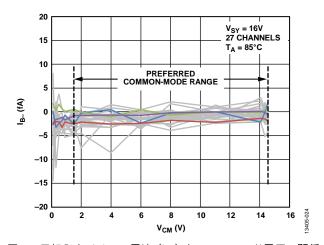

図 24. 反転入力バイアス電流( $I_{B-}$ )とコモンモード電圧の関係 ( $V_{CM}$ ) 、 $V_{SY}$  = 16 V、 $T_A$  = 85  $^{\circ}$ C

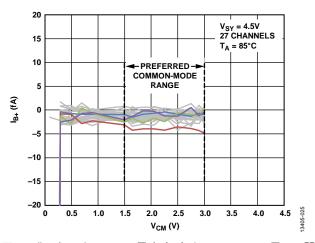

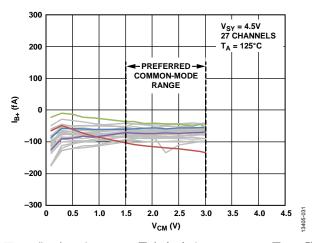

図 25. 非反転入力バイアス電流  $(I_{B+})$  とコモンモード電圧の関係  $(V_{CM})$  、  $V_{SY} = 4.5$  V、  $T_A = 85$  °C

図 26. 非反転入力バイアス電流  $(I_{B+})$  とコモンモード電圧の関係  $(V_{CM})$  、  $V_{SY}=10$  V、  $T_A=85$  °C

図 27. 非反転入力バイアス電流  $(I_{B+})$  とコモンモード電圧の関係  $(V_{CM})$  、  $V_{SY}$  = 16 V、 $T_A$  = 85 °C

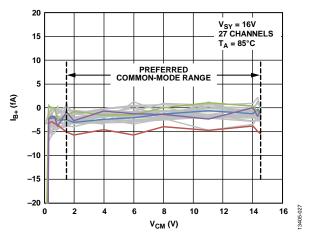

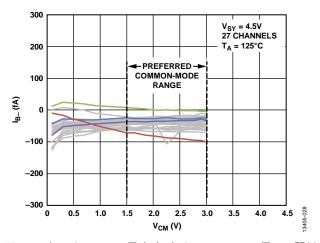

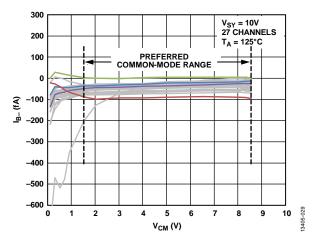

図 28. 反転入力バイアス電流 ( $I_{B-}$ ) とコモンモード電圧の関係 ( $V_{CM}$ )、  $V_{SY}$  = 4.5 V、  $T_A$  = 125  $^{\circ}$ C

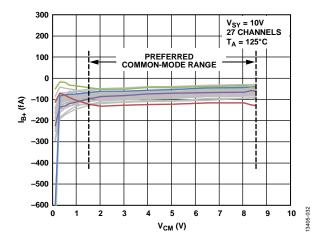

図 29. 反転入力バイアス電流( $I_{B-}$ )とコモンモード電圧の関係 ( $V_{CM}$ ) 、 $V_{SY}$  = 10 V、 $T_A$  = 125  $^{\circ}$ C

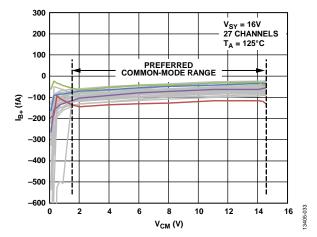

図 30. 反転入力バイアス電流( $I_{B-}$ )とコモンモード電圧の 関係( $V_{CM}$ )、 $V_{SY}=16~V$ 、 $T_A=125~C$

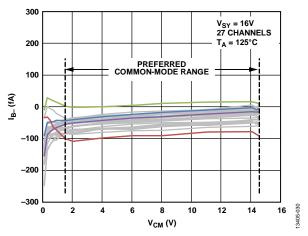

図 31. 非反転入力バイアス電流  $(I_{B+})$  とコモンモード電圧の関係  $(V_{CM})$  、 $V_{SY}=4.5$  V、 $T_A=125$  °C

図 32. 非反転入力バイアス電流  $(I_{B+})$  とコモンモード電圧の関係  $(V_{CM})$  、 $V_{SY}=10$  V、 $T_A=125$  °C

図 33. 非反転入力バイアス電流( $I_{B+}$ )とコモンモード電圧の関係( $V_{CM}$ )、 $V_{SY}=16~V$ 、 $T_A=125~C$

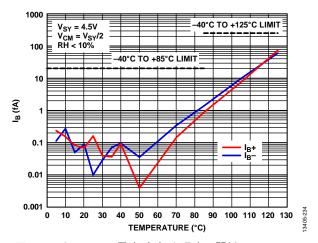

図 34. 入力バイアス電流( $I_B$ )と温度の関係、 $V_{SY}=4.5~V$

図 35. 入力バイアス電流( $I_B$ )と温度の関係、 $V_{SY}=10~V$

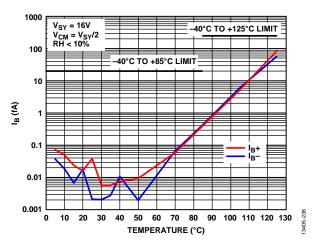

図 36. 入力バイアス電流( $I_B$ )と温度の関係、 $V_{SY}=16~V$

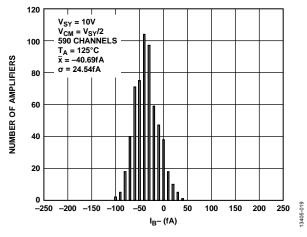

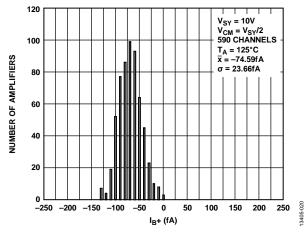

図 37. 反転入力バイアス電流のヒストグラム、 $T_A = 125$  °C、 $V_{SY} = 10$  V

図 38. 非反転入力バイアス電流のヒストグラム、 $T_A$  = 125 °C、 $V_{SY}$  = 10 V

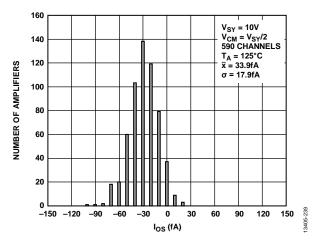

図 39. 入力オフセット電流のヒストグラム

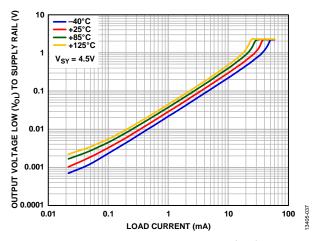

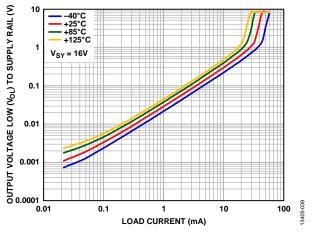

図 40. 電源レールへの出力電圧ロー( $V_{OL}$ )と 負荷電流( $I_{LOAD}$ )の関係、 $V_{SY}$  = 4.5 V

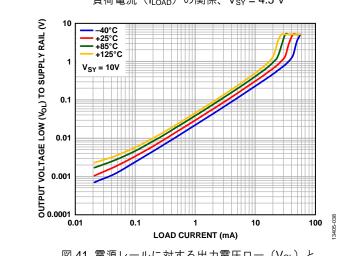

図 41. 電源レールに対する出力電圧ロー( $V_{OL}$ )と 負荷電流( $I_{LOAD}$ )の関係、 $V_{SY}$  = 10 V

図 42. 電源レールに対する出力電圧ロー( $V_{OL}$ )と 負荷電流( $I_{LOAD}$ )の関係、 $V_{SY}$  = 16 V

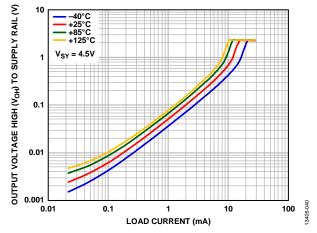

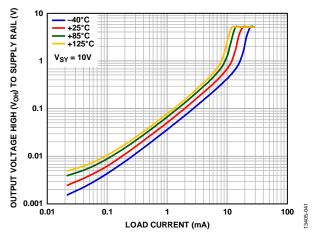

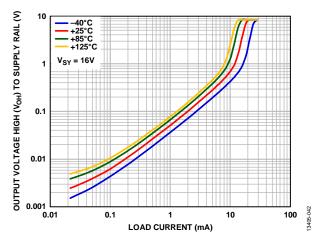

図 43. 電源レールに対する出力電圧ハイ(V<sub>OH</sub>)と 負荷電流(I<sub>LOAD</sub>)の関係、V<sub>SY</sub> = 4.5 V

図 44. 電源レールに対する出力電圧ハイ( $V_{OH}$ )と 負荷電流( $I_{LOAD}$ )の関係、 $V_{SY}$  = 10 V

図 45. 電源レールに対する出力電圧ハイ( $V_{OH}$ )と 負荷電流( $I_{LOAD}$ )の関係、 $V_{SY}$  = 16 V

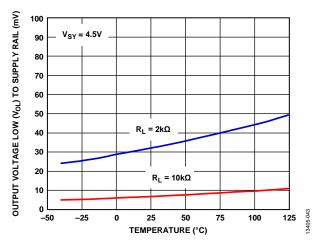

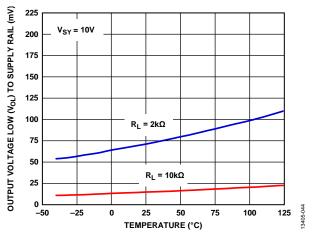

図 46. 電源レールに対する出力電圧ロー(V<sub>OL</sub>)と 温度の関係、V<sub>SY</sub> = 4.5 V

図 47. 電源レールに対する出力電圧ロー(V<sub>OL</sub>)と 温度の関係、V<sub>SY</sub> = 10 V

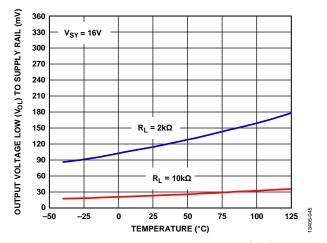

図 48. 電源レールに対する出力電圧ロー(V<sub>OL</sub>)と 温度の関係、V<sub>SY</sub> = 16 V

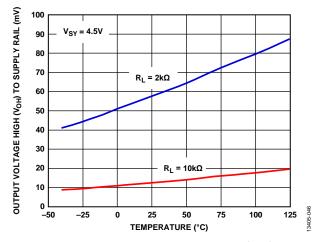

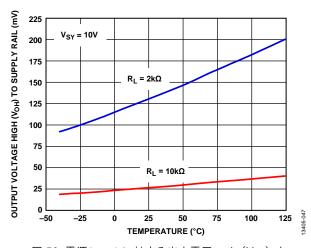

図 49. 電源レールに対する出力電圧ハイ(V<sub>OH</sub>)と 温度の関係、V<sub>SY</sub> = 4.5 V

図 50. 電源レールに対する出力電圧ハイ(V<sub>OH</sub>)と 温度の関係、V<sub>SY</sub> = 10 V

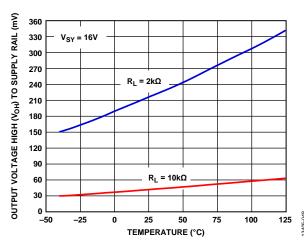

図 51. 電源レールに対する出力電圧ハイ (V<sub>OH</sub>) と 温度の関係、V<sub>SY</sub> = 16 V

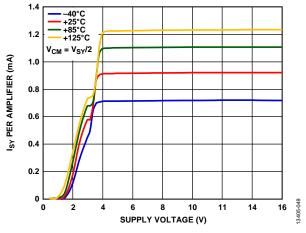

図 52. アンプあたりの電源電流(I<sub>SY</sub>) と電源電圧(V<sub>SY</sub>)の関係

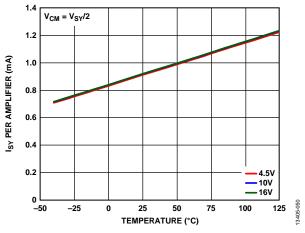

図 53. アンプあたりの電源電流(Isy) と温度の関係

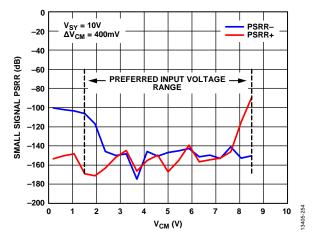

図 54. 小信号 PSRR とコモンモード電圧の関係 (V<sub>CM</sub>)

## メイン・アンプ、AC 性能

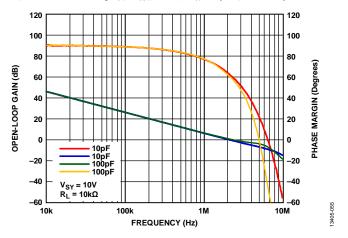

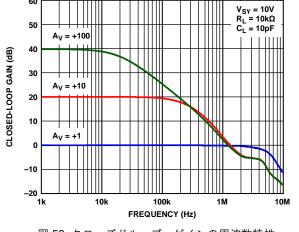

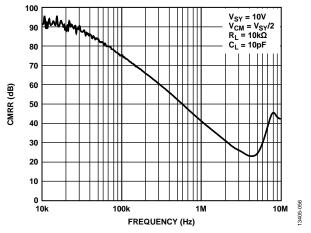

$V_{SY}=4.5~V\sim 16~V$ 。特に指定のない限り、 $V_{SY}=10~V$ 、 $T_A=25~C$ でデータを取得。

図 55. オープンループ・ゲインおよび位相マージンの 周波数特性

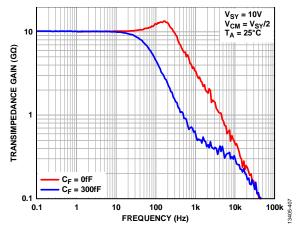

図 58. クローズドループ・ゲインの周波数特性

図 56. CMRR の周波数特性

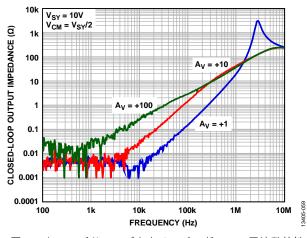

図 59. クローズドループ出力インピーダンスの周波数特性

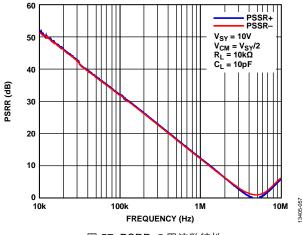

図 57. PSRR の周波数特性

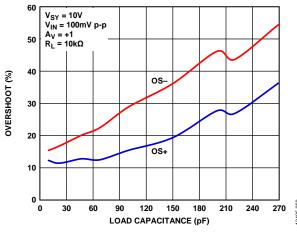

図 60. 小信号オーバーシュートと負荷容量の関係

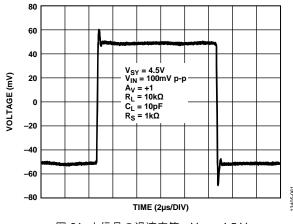

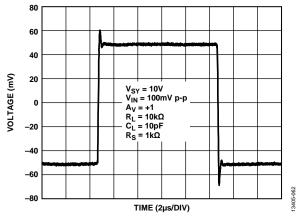

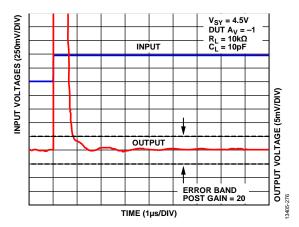

図 61. 小信号の過渡応答、V<sub>SY</sub> = 4.5 V

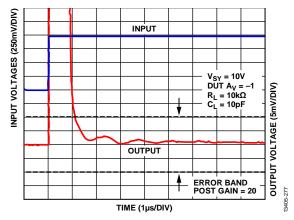

図 62. 小信号の過渡応答、V<sub>SY</sub> = 10 V

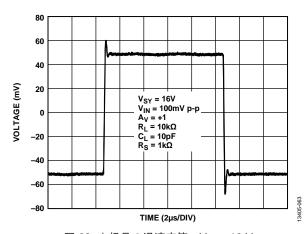

図 63. 小信号の過渡応答、V<sub>SY</sub> = 16 V

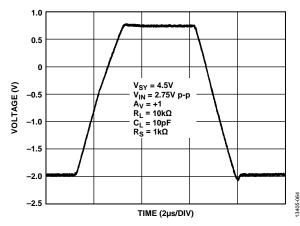

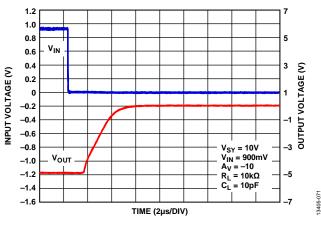

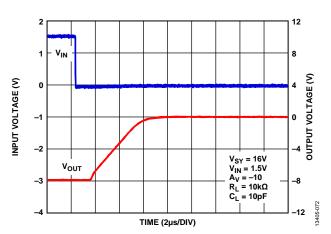

図 64. 大信号の過渡応答、V<sub>SY</sub> = 4.5 V

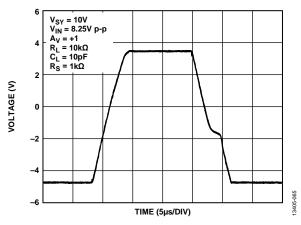

図 65. 大信号の過渡応答、V<sub>SY</sub> = 10 V

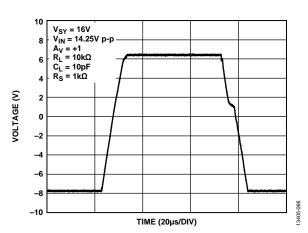

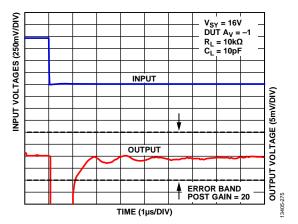

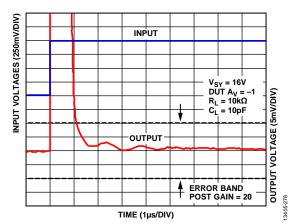

図 66. 大信号の過渡応答、V<sub>SY</sub> = 16 V

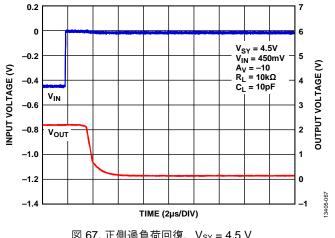

図 67. 正側過負荷回復、V<sub>SY</sub> = 4.5 V

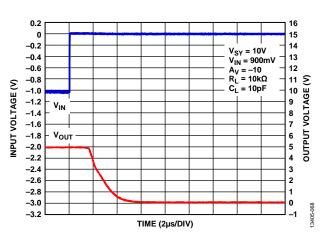

図 68. 正側過負荷回復、V<sub>SY</sub> = 10 V

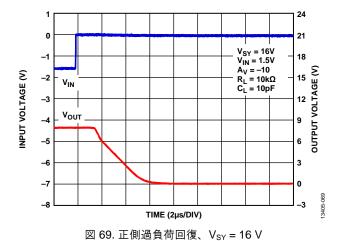

0.6 2.5 0.4 2.0  $V_{IN}$ 0.2 1.5 0 INPUT VOLTAGE (V) -0.2 -0.4 -0.6 -0.8

$$\begin{split} &V_{SY}=4.5V\\ &V_{IN}=400\text{mV}\\ &A_{V}=-10\\ &R_{L}=10\text{k}\Omega\\ &C_{L}=10\text{pF} \end{split}$$

-1.0 -1.2  $v_{out}$ -2.0 TIME (2µs/DIV)

図 70. 立下がり過負荷回復、V<sub>SY</sub> = 4.5 V

図 71. 立下がり過負荷回復、V<sub>SY</sub> = 10 V

図 72. 立下がり過負荷回復、V<sub>SY</sub> = 16 V

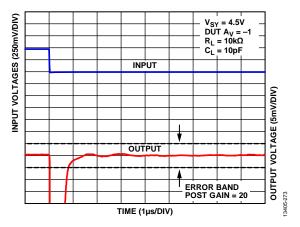

図 73.0.1% への立下がりセトリング・タイム、V<sub>SY</sub> = 4.5 V

図 74.0.1% への立下がりセトリング・タイム、V<sub>SY</sub> = 10 V

図 75. 0.1 % への立下がりセトリング・タイム、V<sub>SY</sub> = 16 V

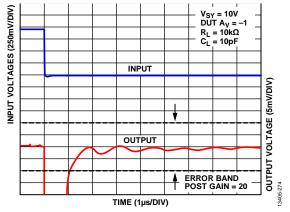

図 76.0.1% への立上がりセトリング・タイム、V<sub>SY</sub> = 4.5 V

図 77.0.1% への立上がりセトリング・タイム、V<sub>SY</sub> = 10 V

図 78.0.1% への立上がりセトリング・タイム、V<sub>SY</sub> = 16 V

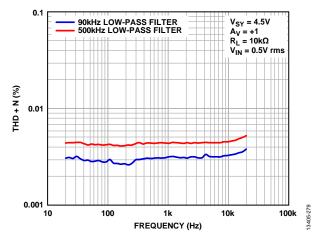

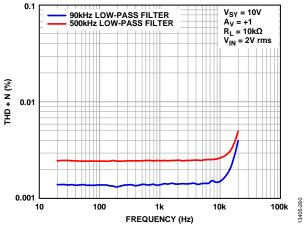

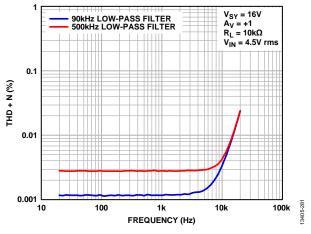

図 79. THD + N の周波数特性、V<sub>SY</sub> = 4.5 V

図 80. THD + N の周波数特性、V<sub>SY</sub> = 10 V

図 81. THD + N の周波数特性、V<sub>SY</sub> = 16 V

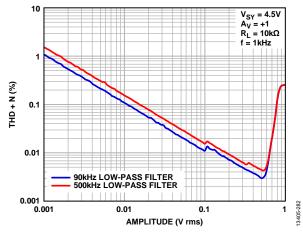

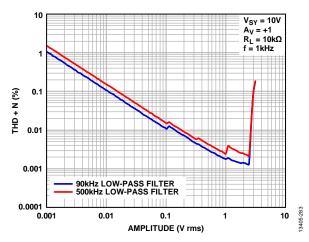

図 82. THD + N と振幅の関係、 $V_{SY}$  = 4.5 V

図 83. THD + N と振幅の関係、V<sub>SY</sub> = 10 V

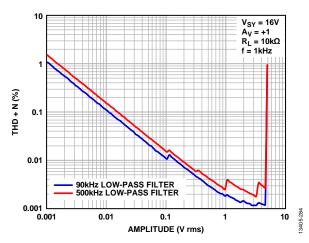

図 84. THD + N と振幅の関係、V<sub>SY</sub> = 16 V

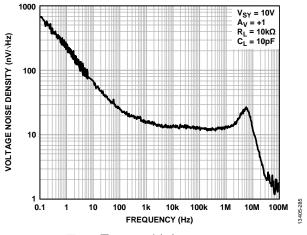

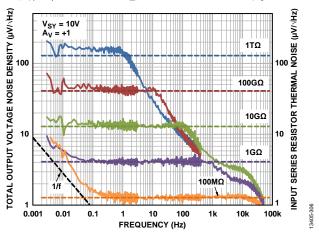

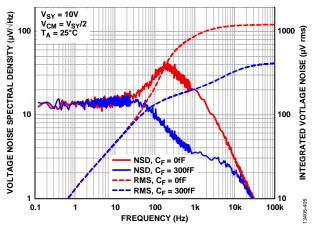

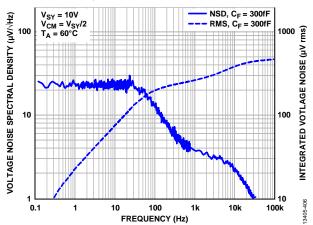

図 85. 電圧ノイズ密度、V<sub>SY</sub> = 10 V

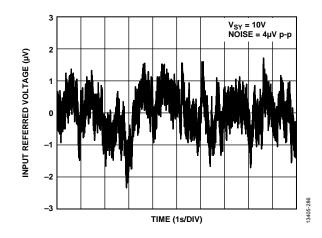

図 86. 0.1 Hz ~ 10 Hz でのノイズ

## ガード・アンプ

特に指定のない限り、TA=25℃。

図 87. 入力オフセット電圧の分布、V<sub>SY</sub> = 4.5 V

図 88. 入力オフセット電圧の分布、V<sub>SY</sub> = 10 V

図 89. 入力オフセット電圧の分布、V<sub>SY</sub> = 16 V

図 90. 入力オフセット電圧( $V_{OS}$ )と温度の関係、 $V_{SY} = 4.5 \text{ V}$

図 91. 入力オフセット電圧( $V_{OS}$ )と温度の関係、 $V_{SY}$  = 10 V

図 92. 入力オフセット電圧( $V_{OS}$ )と温度の関係、 $V_{SY}$  = 16 V

図 93. 入力オフセット電圧ドリフトの分布、  $-40~^{\circ}\text{C} \leq T_A \leq 0~^{\circ}\text{C}$ 、  $V_{\text{SY}} = 4.5~\text{V}$

図 94. 入力オフセット電圧ドリフトの分布、  $-40~^\circ C \le T_A \le 0~^\circ C,~V_{SY} = 10~V$

図 95. 入力オフセット電圧ドリフトの分布、  $-40~^\circ\text{C} \le T_A \le 0~^\circ\text{C}, V_{SY} = 16~\text{V}$

図 96. 入力オフセット電圧ドリフトの分布、 $0 \, ^{\circ}\text{C} \le T_{A} \le 125 \, ^{\circ}\text{C}$ 、 $V_{SY} = 4.5 \, V = 4.5 \, V$

図 97. 入力オフセット電圧ドリフトの分布、0 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C、  $V_{SY} = 10$  V = 4.5 V

図 98. 入力オフセット電圧ドリフトの分布、 0 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C、  $V_{SY}$  = 16 V = 4.5 V

## 動作原理

ADA4530-1 は、電位計アプリケーションで使用される超高インピーダンス・センサーとのインターフェースとして機能する目的で特別に設計されたオペ・アンプです。

MOSFET 入力段は、従来の接合ゲート型電界効果トランジスタ(JFET)電位計で発生するゲート・リーク電流を排除します。ADA4530-1 は、超低入力バイアス電流を実現するとともに、ESD 損傷に対する優れた保護能力を発揮します。独自のESDダイオード構造で保護機能を実現するとともに、ダイオードを保護して入力ピンへのリーク電流を最小限に抑えることができます。ADA4530-1 は、内蔵 ESD ダイオードのリーク経路を保護する際に使用される高精度バッファを内蔵しています。このガード・バッファの出力は外部ピンにも接続されていて、リーク電流から外部部品を保護することができます。

入力バイアス電流は、ESD ダイオードの両端に印加されるガード電圧の精度によって決まります。アンプとガード・バッファのオフセット電圧により、ガード電圧の精度(入力バイアス電流)が設定されます。

入力バイアス電流は、ESD ダイオードの両端に印加されるガード電圧の精度によって決まります。アンプとガード・バッファのオフセット電圧により、ガード電圧の精度(入力バイアス電流)が設定されます。 ADA4530-1 は、アナログ・デバイセズの  $DigiTrim^{TM}$  技術の採用により優れた性能を実現しています。

DigiTrim を使用して、アンプとガード・バッファのオフセット 電圧をトリミングし、コモンモード電圧、電源電圧、および温 度の変化を排除しています。この技法により、Vos、CMRR、PSRR、 および TCVos の仕様が大幅に向上します。

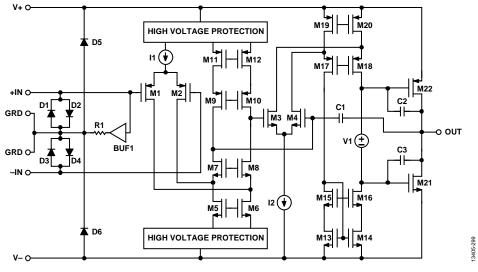

図 99 に、ADA4530-1 の簡略化した回路図を示します。アンプは、完全差動入力段のある 3 段アーキテクチャを使用して、最高の DC 性能仕様を達成します。

#### ESD 保護構造

入力の静電気放電保護 (ESD) 構造は、ダイオード D1 ~ ダイオード D6 で構成されています。非反転入力は、D1 および D2 の逆並列ダイオードによってガード・ピン (GRD) に結合されています。反転入力は、D3 および D4 の逆並列ダイオード

によってガード・ピン(GRD)に結合されています。ガード・ピンは、ダイオード D5 とダイオード D6 を通じて電源に接続されています。静電気放電(ESD)が発生すると、入力ピンからいずれかの逆並列ダイオードと電源ダイオードを通して電源に害を及ぼすことなく過渡電流が流れます。通常の動作時には、ガード・バッファ(BUF1)により逆並列ダイオードの両端にかかる電圧は 0 V になります。抵抗 R1 は、ガード・ピンに接続されている潜在的に大きい容量からガード・バッファをシールドします。その公称値は 1 k $\Omega$  です。

## 入力段

入力段は、PMOS 差動ペア (M1、M2)、フォールド型カスコード・トランジスタ ( $M5 \sim M12$ )、電流源 I1 で構成されています。

ADA4530-1 は、差動入力に低電圧 MOS デバイスを使用することで、高い性能仕様を実現しています。これらの低電圧 MOS デバイスは、高電圧デバイスと比べて、単位電流あたりで優れた1/fノイズと帯域幅を実現します。入力段は、独自の保護回路によって高システム電圧から分離されています。この調整回路は、アンプを動作できる高電源電圧から入力デバイスを保護します。

ADA4530-1 の独自の高電圧保護回路は、ほとんどの入力コモンモード電圧範囲でアンプの入力段によって発生するコモンモード電圧の変化を最小限に抑える方法で動作します。この回路により、推奨される入力コモンモード電圧範囲で動作しているときに最高の外乱除去性能を達成できます。この推奨される範囲内で動作させることによる性能上のメリットを  $V_{CS}$  と  $V_{CM}$  の関係のグラフ(図  $16 \sim$ 図 18 を参照)、小信号 CMRR と  $V_{CM}$  の関係のグラフ(図 18 を参照)、小信号 18 と 18

これらの入力デバイスは、逆並列 ESD ダイオード (D1  $\sim$  D4) によって大きな差動入力電圧から保護されます。ダイオードは、差動電圧が 700 mV を超えると、ダイオードから大量の電流を流すことができます。入力ピンに流れる電流を 10 mA の絶対最大電流に制限する必要があります。

図 99. 簡略化した回路図

## ゲイン段

アンプの 2 段目は、NMOS 差動ペア(M3、M4)とフォールド型カスコード・トランジスタ(M13  $\sim$  M20)で構成されています。アンプはネスト型ミラー補償(C1  $\sim$  C3)を備えています。

## 出力段

ADA4530-1 は、M21 および M22 トランジスタで構成される相補型コモンソース出力段を備えています。これらのトランジスタは、クラス AB トポロジで構成されていて、電圧源 V1 によってバイアスが印加されています。このトポロジにより、出力電圧を電源レールの数十ミリボルト以内の差に収めてレール toレールの出力振幅を実現できます。出力電圧は、トランジスタの出力インピーダンスによって制限されます。出力電圧の振幅は負荷電流の関数で、電源レールへの出力電圧と負荷電流の関係のグラフ(図 40~図 45 を参照)を使用して見積もることができます。

#### ガード・バッファ

ガード・バッファ(BUFI)は、入力コモンモード電圧の低インピーダンスの複製を作成するユニティゲイン・アンプです。バッファ入力は非反転入力(IN+)に接続されています。メイン・アンプ帰還ループをセトリングした場合、非反転入力電圧は入力コモンモード電圧にほぼ等しくなります。

ガード・バッファには、アンプと同じような3段アーキテクチャが採用されています。ガード・バッファには、ガード電圧が電源レールの振幅が100mV以内になるレールtoレール出力段が採用されています。ガード・バッファ出力は入力コモンモード電圧に追従するため、この出力振幅は低い入力コモンモード電圧でガード・バッファの効果を制限します。この制限は、入力バイアス電流とコモンモード電圧の関係のグラフ(図22~図33を参照)に、低いコモンモード電圧における入力バイアス電流の大幅な増加として見受けられることがあります。このため、V-電源レールから100mV未満の入力コモンモード電圧で回路を動作させないことをお勧めします。

ガード・バッファ出力電圧は、過度な負荷によって低下することがあります。 $1 \, k\Omega$  の出力抵抗が存在する場合は、 $1 \, nA$  の負荷電流あたり  $1 \, \mu V$  のガード電圧誤差が追加されます。数十ナノアンペアの負荷電流が流れる場合、ガード・オフセット電圧が仕様範囲外で駆動されるおそれがあります。このため、絶縁抵抗 (Insulation Resistance および Guarding のセクションを参照)以外のものをガード・バッファで駆動することは推奨されません。より高い駆動能力が必要な場合は、ADA4661-2 などの低オフセット、低入力バイアス電流オペ・アンプを使用してカード電圧をバッファすることができます。

## アプリケーション情報

ADA4530-1 は、フェムトアンペア入力バイアス電流と超低オフセット電圧を達成した電位計グレードのシングル CMOS オペ・アンプです。4.5 V(または  $\pm 2.25$  V 両電源)  $\sim 16$  V(または  $\pm 8$  V 両電源)の幅広い電源電圧範囲で動作します。単電源アンプとして使用する場合、入力電圧範囲には低い電源レールと同じ値が含まれ、レール to レール出力を達成します。ADA4530-1 は、 $\pm 40$   $\mu$  V(max)の低オフセット電圧と $\pm 0.5$   $\mu$  V/C(max)のオフセット電圧ドリフトも実現します。

システム・アプリケーションで確実にその性能目標を満たすように、ADA4530-1 の超低入力バイアス電流は 25 °C と 125 °C で出荷時にテストされています。ガード・バッファを内蔵しているので、プリント回路基板 (PCB) 設計の入力ピンへのリーク電流と基板部品数を最小限に抑えるとともに、システム設計が容易になります。ガード・リングの配線を容易に行い、入力ピン、電源、および出力ピン間での信号の結合を防止することができるように、ガード・バッファ出力ピンは入力ピンの横に配置されています。

ADA4530-1 は、さまざまな電流出力トランスデューサ(フォトダイオード、光電子増倍管)、分光測定、クロマトグラフィ、化学センサーの高インピーダンス・バッファリング用のプリアンプ・アプリケーションなど、非常に低い入力バイアス電流と低いオフセット電圧が要求されるアプリケーションに適しています。

## 入力保護

ADA4530-1 のどちらかの入力がいずれかの電源レールを 300 mV 超過すると、入力 ESD ダイオードに順方向バイアスがかかり、大量の電流が流れます。この過度な電流を制限しないと、デバイスに恒久的な損傷を与えることがあります。入力で過電圧状態が予期される場合、各入力に直列に抵抗を接続して入力電流を 10 mA (max) に制限してください。また、回路全体に対する抵抗熱ノイズの影響を考慮してください。

## 単電源とレール TO レール出力

ADA4530-1 は、 $V-\sim V+-1.5\,V$ (V+ より  $1.5\,V$  小さい電圧)の入力電圧範囲(IVR)に対応した単電源アンプです。アンプは、入力コモンモード電圧が仕様規定の IVR よりも大きい場合に正しく機能できる小さなキープ・アライブ入力段を実装しています。この機能により、ADA4530-1 は、パワーアップ時に IVR を超えるような特定タイプの回路ですばやく起動および回復することができます。このキープ・アライブ段の AC および DC 性能は低いため、通常の使用ではこのキープ・アライブ段に依存しないようにしてください。

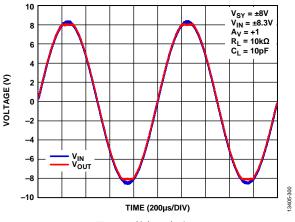

図 100 に、電源電圧  $\pm 8$  V でユニティ・ゲイン・バッファとして構成された ADA4530-1 の入力と出力の波形を示します。出力電圧が最大出力振幅でクランプされるまで、出力は全範囲にわたって入力電圧に追従します。信号が仕様規定の入力電圧範囲 (-8 V  $\leq$  IVR  $\leq$  +6.5 V) を超過しても、アンプは動作を継続します。この動作はキープ・アライブ段によって発生します。さらに、位相反転は発生しません。入力電圧範囲を超過する入力電圧を印加することは推奨されません。

図 100. 位相反転なし

## 容量性負荷に対する安定性

ADA4530-1 は、最大 250 pF までの容量性負荷を任意の構成で安全に駆動できます。多くのアンプと同様に、仕様規定より大きな容量性負荷を駆動すると、過度なオーバーシュートやリンギングが発生したり、発振が生じたりすることもあります。容量性負荷が大きいと位相マージンが減少し、アンプの周波数応答にピークが発生します。ピーク形成は、時間軸でのオーバーシュートまたはリンギングに対応します。このため、ADA4530-1が 250 pF を超える負荷を駆動する必要がある場合は、外付け補償を使用することが推奨されます。この補償は、安定性が最悪の条件となるユニティ・ゲイン構成で特に重要です。

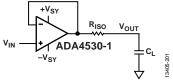

容量性負荷を駆動するオペ・アンプを迅速かつ簡単に安定化させるには、アンプ出力端子と負荷容量の間に直列抵抗  $R_{ISO}$  を接続します(図 101 を参照)。 $R_{ISO}$  は、アンプ出力と帰還回路を容量性負荷から隔離します。ただし、この補償方式では、負荷から見た出力インピーダンスが大きくなるため、ゲイン精度が低下します。

図 101. アイソレーション抵抗 RISO による安定性補償、R<sub>ISO</sub>

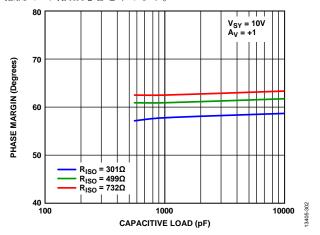

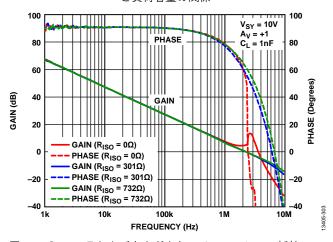

図 102 に、さまざまな値のアイソレーション抵抗および容量性 負荷における ADA4530-1 の位相マージンを示します。図 103 に、1 nF 容量性負荷およびさまざまなアイソレーション 抵抗での周波数応答を示します。

図 102. さまざまな出力アイソレーション抵抗での位相マージ と負荷容量の関係

図 103.  $C_L = 1$  nF およびさまざまなアイソレーション抵抗での 周波数応答

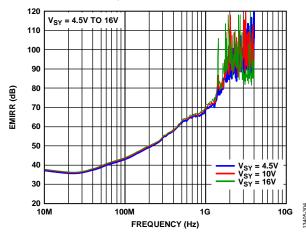

### EMI 除去比

回路性能は高周波電磁干渉(EMI)から悪影響を受けることがあります。信号強度が低く、伝送線が長い場合でも、オペ・アンプは入力信号を正確に増幅する必要があります。ただし、オペ・アンプのすべてのピン(非反転入力、反転入力、正電源、負電源、出力ピン)は EMI 信号の影響を受けやすくなっています。これらの高周波信号は、伝導、近距離放射、長距離放射などのさまざまな方法でオペ・アンプに混入します。例えば、配線と PCB パターンがアンテナとして機能し、高周波 EMI 信号を拾います。

アンプは比較的帯域が狭いため、EMI信号またはRF信号を増幅することはありません。しかし、入力デバイスの非直線性のため、オペ・アンプはこれらの帯域外信号を整流することがあります。これらの高周波信号が整流されると、出力にDCオフセットとして現れます。

電磁エネルギーが存在する中で ADA4530-1 が期待どおりに動作する能力を表現するために、非反転ピンの電磁干渉除去比 (EMIRR) が Specifications のセクションの表 1、表 2、表 3 で 仕様が規定されています。EMIRR 測定の数学的方法は、以下のように定義されます。

#### $EMIRR = 20\log(V_{IN\ PEAK}/\Delta V_{OS})$

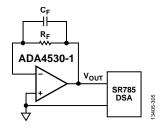

図 104 に仕様が規定された各電源電圧での代表的な EMIRR の 周波数特性を示します。

図 104. EMIRR の周波数特性

## 高インピーダンス測定

ADA4530-1 は、超高インピーダンス回路の性能を最大限引き出すように設計されています。優れた性能により、回路インピーダンスが  $100~M\Omega\sim10~T\Omega$  を超える場合でも使用できます。高インピーダンス回路の測定では、いくつかの誤差源の影響を受けます。高抵抗源から行う測定に関する一般的な情報については、 Low Level Measurements Handbook、第 6 版(Keithley Instruments, Inc., 2004)を参照してください。

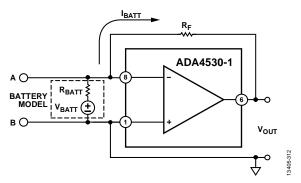

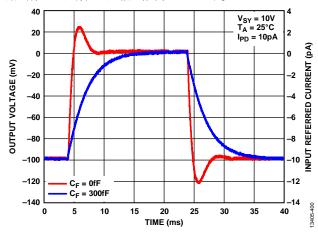

ADA4530-1 は、一般的にバッファと TIA の 2 種類の回路で使用します。バッファ回路は、高出力抵抗の電圧出力センサーを測定するのに有用です。センサーの例として、電量分析制御ループ内の pH プローブや基準電極 (RE) があります。TIA 回路は、電流出力センサーからの信号を出力電圧に変換するのに有用です。センサーの例として、フォトダイオードやイオン・チャンバーがあります。

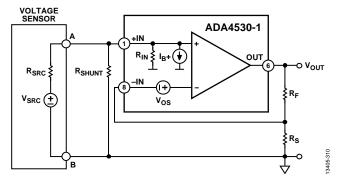

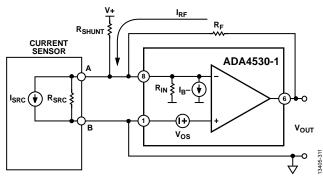

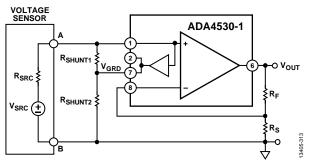

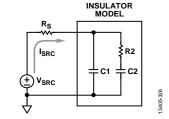

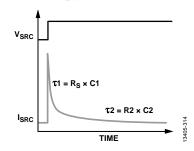

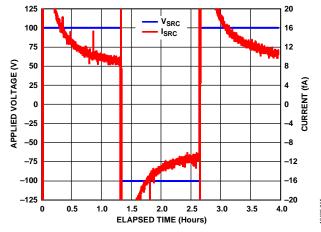

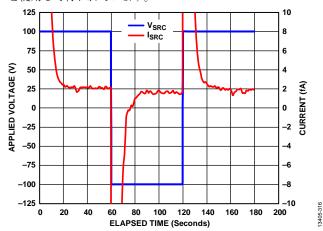

ここでは、これらの回路で ADA4530-1 を使用する場合の最も 重要な誤差源のいくつかについて説明します。バッファ回路と TIA 回路の誤差源を含む、簡略化したモデルをそれぞれ図 105 と図 106 に示します。

バッファ回路は、電圧出力センサーを出力抵抗( $R_{SRC}$ )のある電圧源( $V_{SRC}$ )としてモデル化します。A端子の電圧は、非反転ゲイン構成(またはユニティゲイン構成)の ADA4530-1 のピン1によって検出されます。B端子は、適切なリファレンス電圧(この場合は信号グラウンド)まで駆動されます。

すべての誤差源を無視した場合、回路の出力は以下のようになります。

$$V_{OUT} = V_{SRC} \left( 1 + \frac{R_F}{R_S} \right)$$

図 105. 電圧バッファ回路

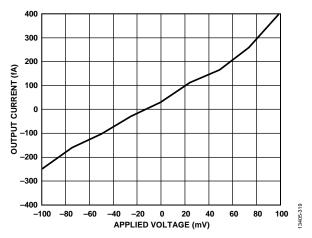

TIA 回路は、電流出力センサーをシャント抵抗 (R<sub>SRC</sub>) のある電流源 (I<sub>SRC</sub>) としてモデル化します。A 端子からの電流は、ADA4530-1 の反転入力ピンと帰還抵抗 (RF) に接続されています。アンプの B 端子と非反転入力は、適切なリファレンス電圧 (この場合は信号グラウンド)まで駆動されます。回路の負帰還は、A 端子での電圧の変化を抑制します。この抑制は、すべての電流を強制的に帰還抵抗に流すことで実現されます。すべての誤差源を無視した場合、回路の出力は以下のようになります。

$V_{OUT} = I_{SRC}R_F$

図 106. トランスインピーダンス・アンプ回路

## 入力パイアス電流

アンプの入力バイアス電流は、高インピーダンス電位計回路の 主な誤差源です。

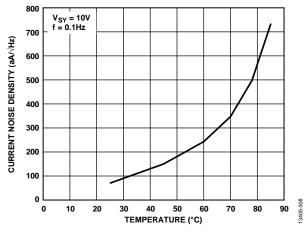

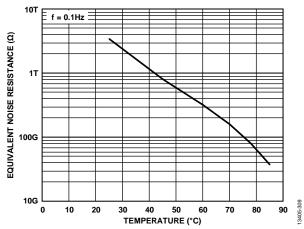

他の半導体アンプと同様、ADA4530-1 の入力バイアス電流に は、温度に関する指数関数的な依存性があります。ADA4530-1 の入力バイアス電流は、温度が10℃上昇するたびに2.5倍に なります。代表的な温度特性については、入力バイアス電流と 温度の関係のグラフ(図34~図36を参照)を参照してくださ い。指数関数的なダイオード電流は、 $60^{\circ}$ C ~  $70^{\circ}$ C を下回る 温度で入力バイアス電流を下回ります。100 aA ~ 200 aA (aA= 10<sup>-18</sup> A) の残留バイアス電流は、環境条件に非常に敏感な他の リーク経路が存在する場合は、それらの値を下回ります。これ らの非常に小さなバイアス電流を測定するには、高度に制御さ れた実験室条件が必要です。実際のアプリケーションの多くで は、他の誤差の方が大きく、ADA4530-1 の入力バイアス電流 は 70 ℃ 未満の温度では 0 であるとみなすことができます。 ADA4530-1 の入力バイアス電流は、生産環境の測定上の制限 により ±20 fA までしか確保できませんが、得られる入力バイ アス電流は1桁以上低い値になります。