# 4 チャンネル、16 ビット 連続時間データ・アクイジション

**ADC**

データシート

**ADAR7251**

#### 特長

低ノイズ:最大ゲイン設定時の入力換算電圧ノイズは 2.4nV/√Hz

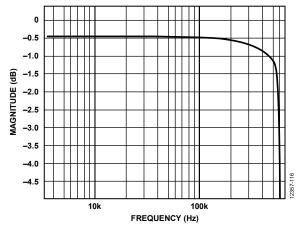

広い信号帯域幅: 500kHz (サンプル・レート 1.2MSPS、 分解能 16 ビットの場合)

サポートするその他のサンプル・レート: 300kSPS、450kSPS、600kSPS、900kSPS、1.8MSPS

4系統の差動同時サンプリング・チャンネル

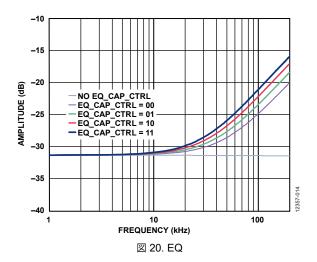

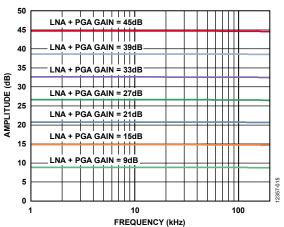

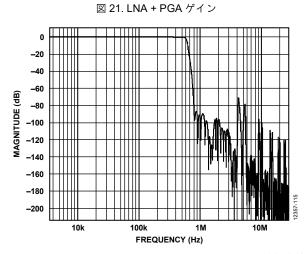

アクティブなアンチエイリアシング・フィルタは不要 ゲイン範囲 45dB(6dB ステップ)の LNA と PGA 選択可能なイコライザ

シリアルとパラレルの両方のモードをサポートする柔軟な データ・ポート

FMCW レーダー・システム向けに FSK モードをサポート 1.5V リファレンスを内蔵

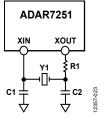

内蔵オシレータ/PLL 入力: 16MHz~54MHz 高速シリアル・データ・インターフェース

SPI制御 2つの汎用入出力

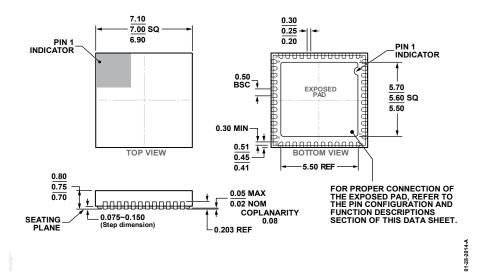

48 ピン LFCSP SS パッケージ

温度範囲:-40℃~+125℃

3.3V の単電源で動作

車載アプリケーション向けに性能を評価済み

#### アプリケーション

車載用 LSR システム データ・アクイジション・システム

#### 概要

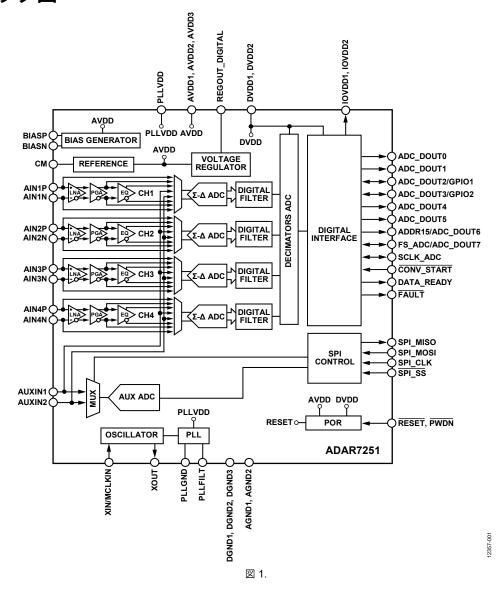

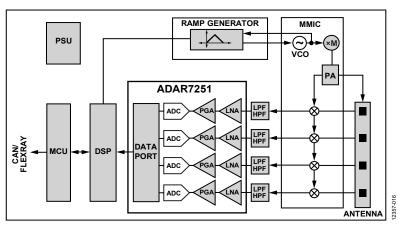

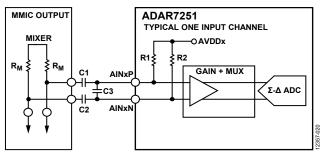

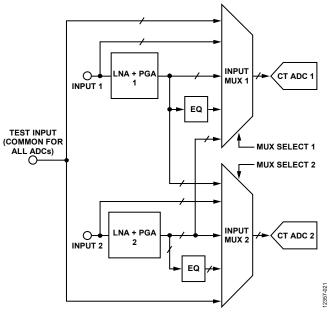

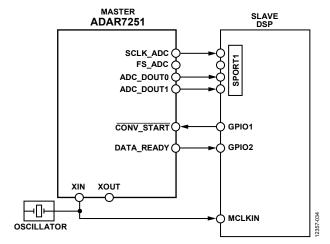

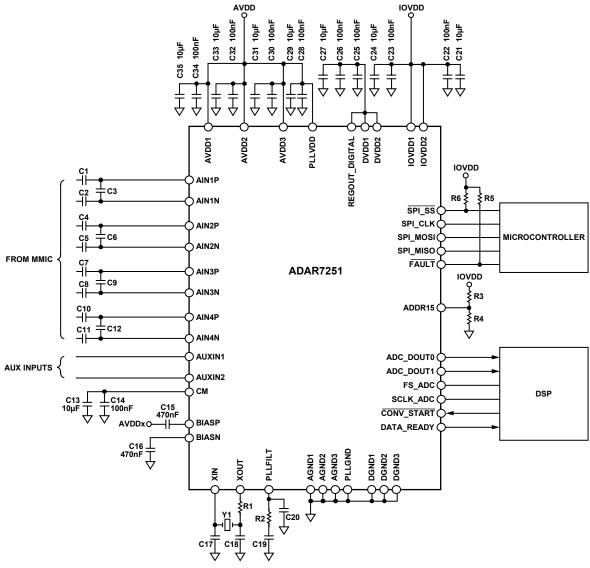

ADAR7251 は、車載用 LSR-FMCW や FSK-FMCW レーダー・システムなどのアプリケーション向けに特に設計された、 16 ビット、4 チャンネルの同時サンプリング A/D コンバータ(ADC)です。4 つのチャンネルにはそれぞれ、ロー・ノイズ・アンプ(LNA)、プログラマブル・ゲイン・アンプ(PGA)、イコライザ、マルチビット  $\Sigma$ - $\Delta$  ADC、およびデシメーション・フィルタが内蔵されています。

フロント・エンド回路は外部パッシブ・コンポーネントをほとんど必要とせず、MMIC 出力に直接接続できるよう設計されています。ADAR7251 を使用することにより、高次のアンチエイリアシング・フィルタ、ドライバ・オペアンプ、および外部バイポーラ電源が不要となります。ADAR7251 はまたチャンネル間ドリフトのマッチングも正確に行います。

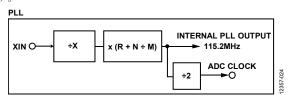

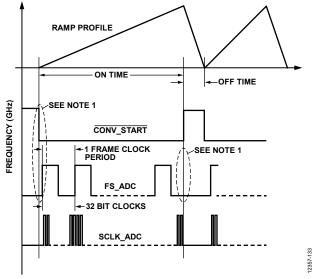

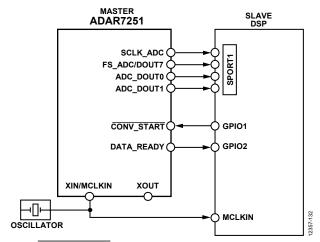

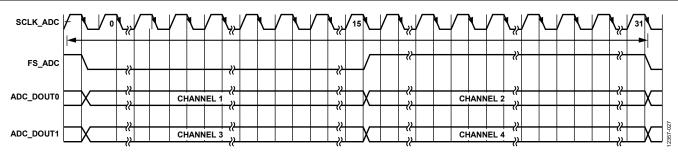

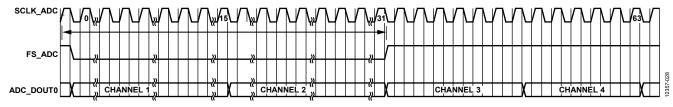

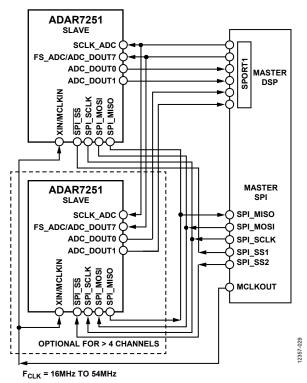

ADAR7251 はフェーズ・ロック・ループ (PLL) をオンチップ に搭載し、多様なクロック周波数に対応することによりシステムの柔軟性を高めています。FSK-FMCW レーダーなどのアプリケーションでは、CONV\_START入力信号と DATA\_READY 出力 信号により ADC と外部ランプとが同期します。

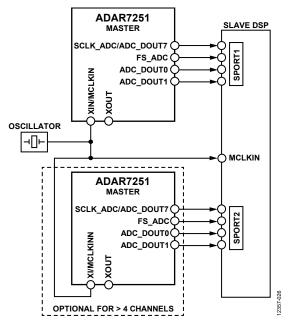

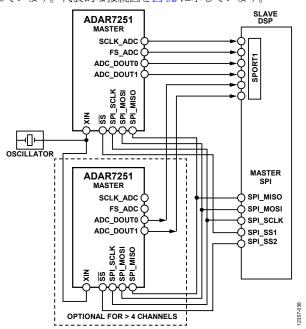

ADAR7251 の 300kSPS から 1.8MSPS までの間でプログラム可能なサンプル・レートでシリアルおよびパラレルのインターフェースをサポートし、またシステム内のデジタル・シグナル・プロセッサ (DSP) やマイクロコントローラ・ユニット (MCU)とも容易に接続することができます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2014 Analog Devices, Inc. All rights reserved.

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

## 目次

|                                                                  | 1                                                                                    |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| アプリケーション                                                         | 1                                                                                    |

| 概要                                                               | 1                                                                                    |

| 改訂履歴                                                             | 3                                                                                    |

| 機能ブロック図                                                          | 4                                                                                    |

| 仕様                                                               | 5                                                                                    |

| アナログ・チャンネル                                                       | 5                                                                                    |

| デジタル入出力                                                          | 6                                                                                    |

| 電源                                                               | 7                                                                                    |

| デジタル・フィルタ                                                        | 8                                                                                    |

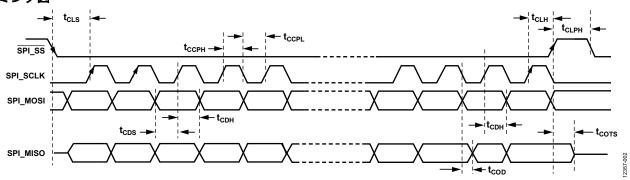

| SPI ポートのタイミング                                                    | 8                                                                                    |

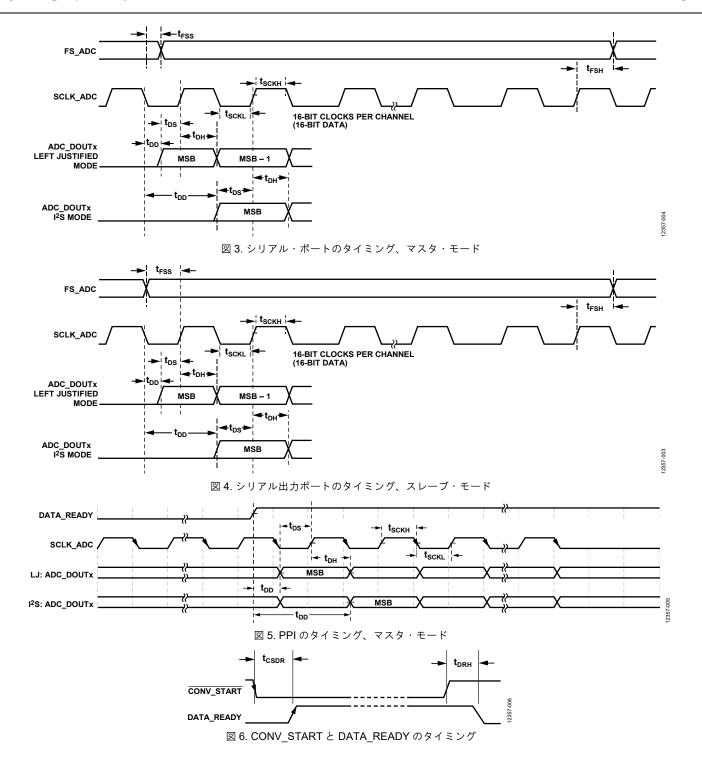

| シリアル/ペリフェラル・パラレル・インターフェース<br>(PPI)ポートのタイミング                      | 8                                                                                    |

| 絶対最大定格                                                           | . 11                                                                                 |

| 熱抵抗                                                              | . 11                                                                                 |

| ESD に関する注意                                                       | . 11                                                                                 |

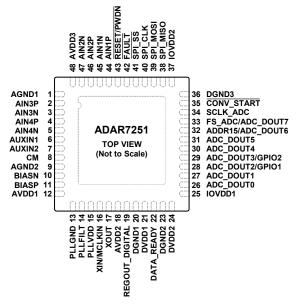

| ピン配置およびピン機能の説明                                                   | . 12                                                                                 |

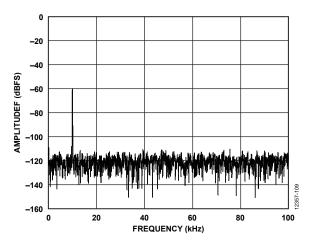

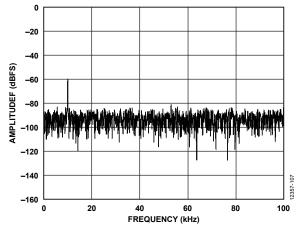

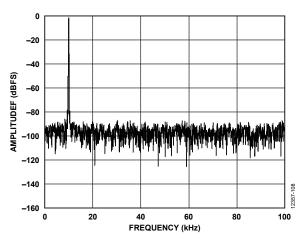

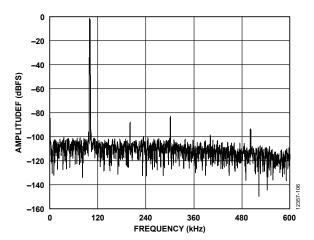

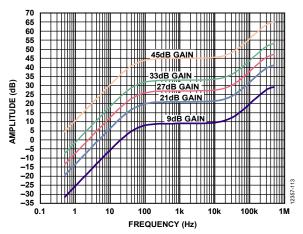

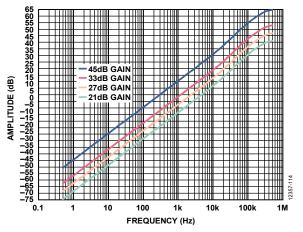

| 代表的な性能特性                                                         | . 14                                                                                 |

| 用語の定義                                                            | . 17                                                                                 |

| 動作原理                                                             | . 18                                                                                 |

| 低速ランプ・レーダーのアナログ・フロント・エンド                                         | . 18                                                                                 |

| メイン・チャンネルの概要                                                     | . 18                                                                                 |

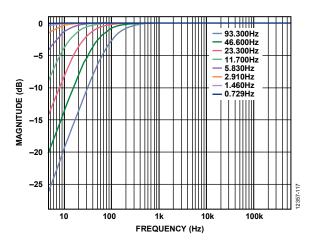

| <b>Σ-Δ</b> 変調とデジタル・フィルタリング                                       |                                                                                      |

|                                                                  | . 18                                                                                 |

| 差動入力構成                                                           |                                                                                      |

|                                                                  | . 19                                                                                 |

| 差動入力構成                                                           | . 19<br>. 19                                                                         |

| 差動入力構成イコライザ(EQ)                                                  | . 19<br>. 19<br>. 20                                                                 |

| 差動入力構成イコライザ (EQ)<br>LNA/PGA、EQ、または入力キャパシタの使用                     | . 19<br>. 19<br>. 20                                                                 |

| 差動入力構成イコライザ (EQ)LNA/PGA、EQ、または入力キャパシタの使用リファレンス                   | . 19<br>. 19<br>. 20<br>. 20                                                         |

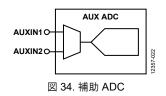

| 差動入力構成イコライザ (EQ)<br>LNA/PGA、EQ、または入力キャパシタの使用<br>リファレンス<br>補助 ADC | . 19<br>. 20<br>. 20<br>. 20                                                         |

| 差動入力構成イコライザ (EQ) LNA/PGA、EQ、または入力キャパシタの使用 リファレンス 補助 ADC 電源       | . 19<br>. 20<br>. 20<br>. 20<br>. 21                                                 |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 20<br>. 21<br>. 21                                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 20<br>. 21<br>. 21                                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 21                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23                         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23<br>. 33<br>. 34         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23<br>. 33<br>. 34         |

| 差動入力構成イコライザ (EQ)                                                 | . 19<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 23<br>. 23<br>. 33<br>. 34<br>. 37 |

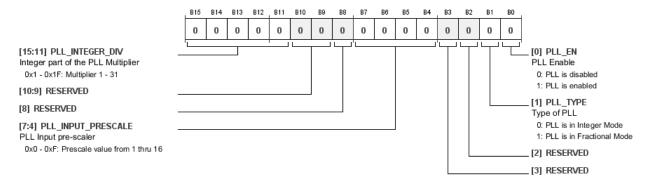

| PLL 制御レジスタ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

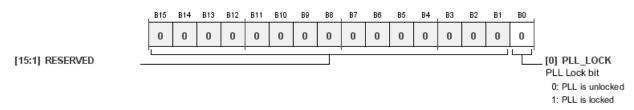

| PLL ステータス・レジスタ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8          |

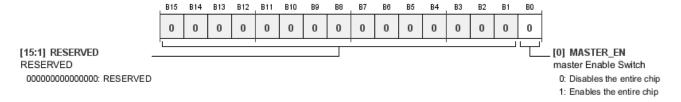

| マスタ・イネーブル・スイッチ・レジスタ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39         |

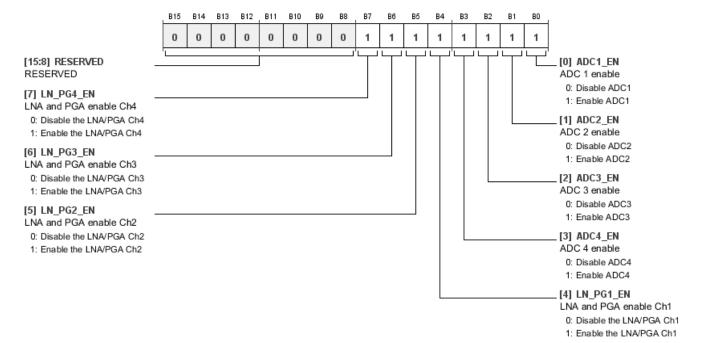

| ADC イネーブル・レジスタ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39         |

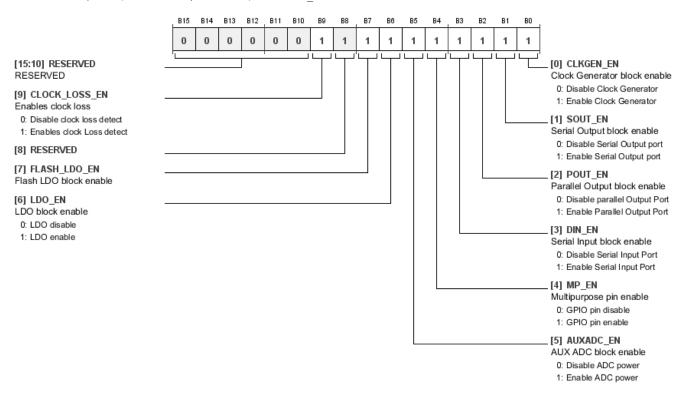

| パワー・イネーブル・レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10         |

| ASIL エラー・クリア・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>‡</b> 1 |

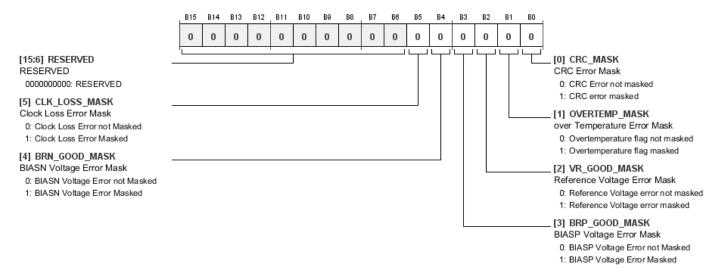

| エラー・マスク選択レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12         |

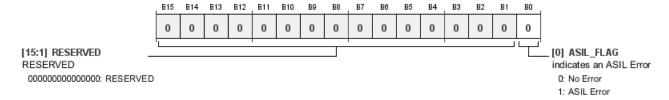

| ASIL エラー・フラグ・レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13         |

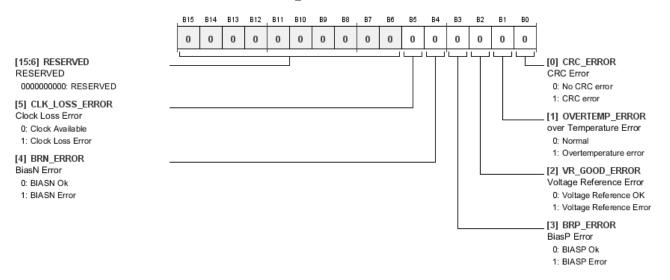

| ASIL エラー・コード・レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13         |

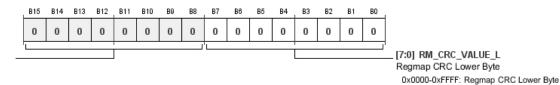

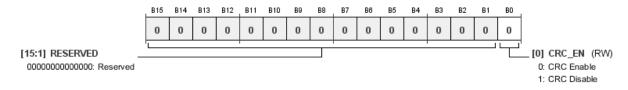

| CRC 値、ビット [7:0] レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14         |

| CRC 値レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14         |

| レジスタ・マップ・コンテンツの CRC 値計算を開始するレ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| レジスタ・マップ CRC 計算完了レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| レジスタ・マップ CRC 値、ビット [7:0] レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| レジスタ・マップ CRC 値、ビット [15:8] レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

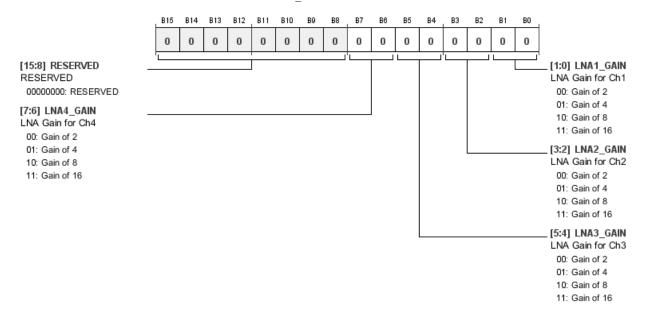

| ロー・ノイズ・アンプ・ゲイン・コントロール・レジスタ.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16         |

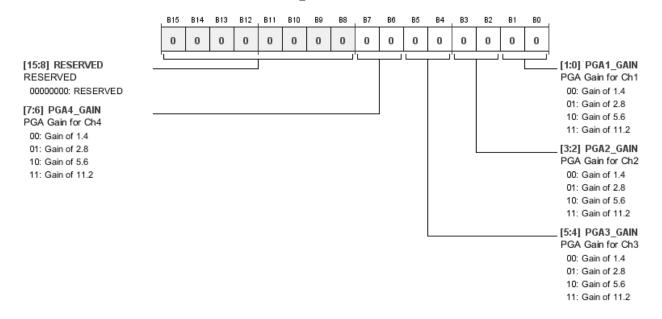

| プログラマブル・ゲイン・アンプ・ゲイン・コントロール・<br>レジスタ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

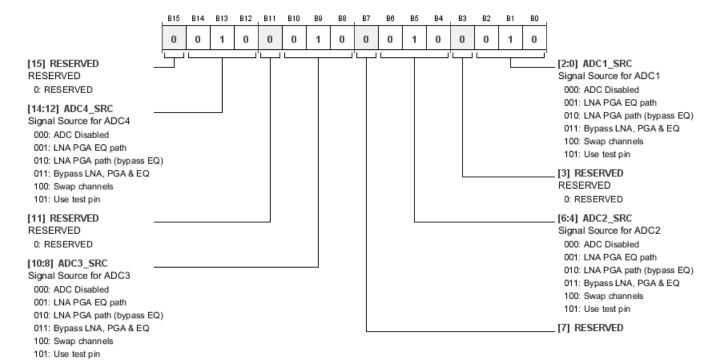

| ADC 1~ADC 4 までの信号パス・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

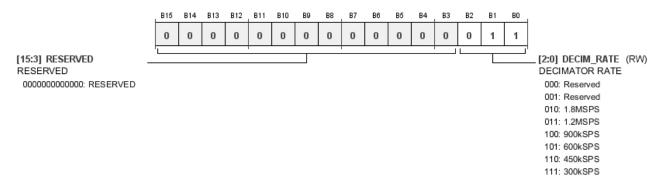

| デシメータ・レート・コントロール・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

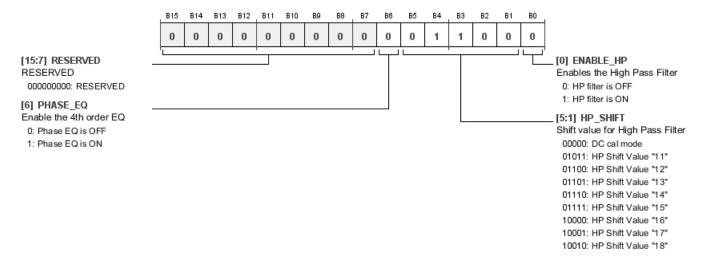

| ハイパス・フィルタ・コントロール・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

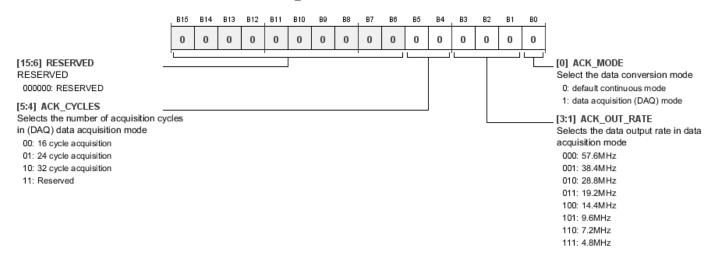

| DAQモード・コントロール・レジスタ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

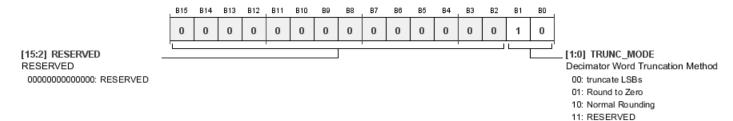

| デシメータ切り捨てコントロール・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

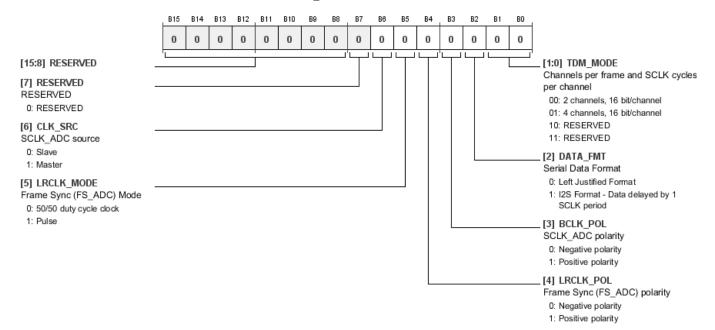

| シリアル出力ポート・コントロール・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

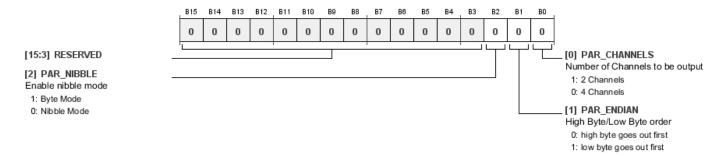

| パラレル・ポート・コントロール・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

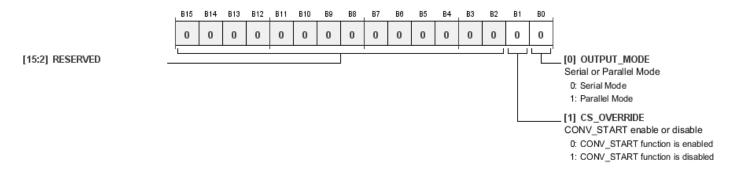

| ADC デジタル出力モード・レジスタ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

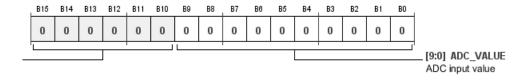

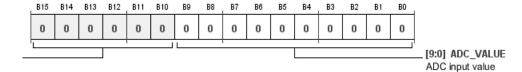

| 補助 ADC 読出し値レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 補助 ADC サンプル・レート選択レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

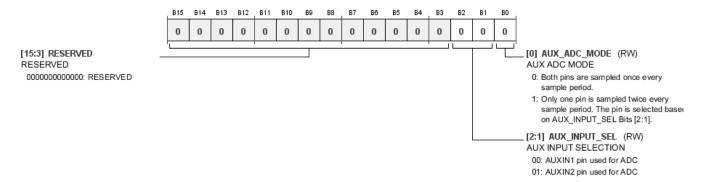

| 補助 ADC モード・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

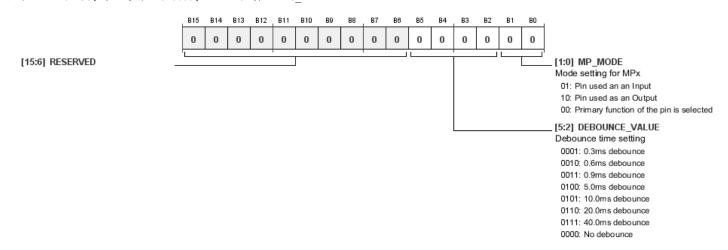

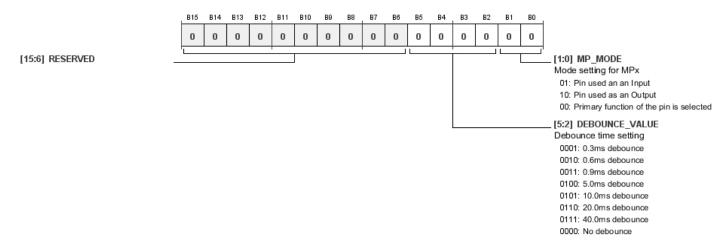

| MPx ピン・モード・レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| MP 書込み値レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

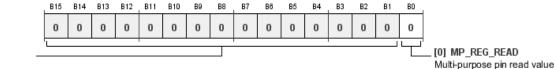

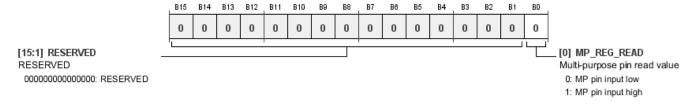

| MP 読出し値レジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

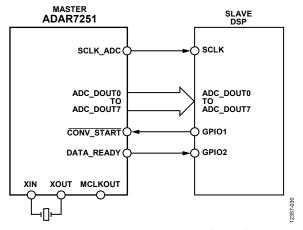

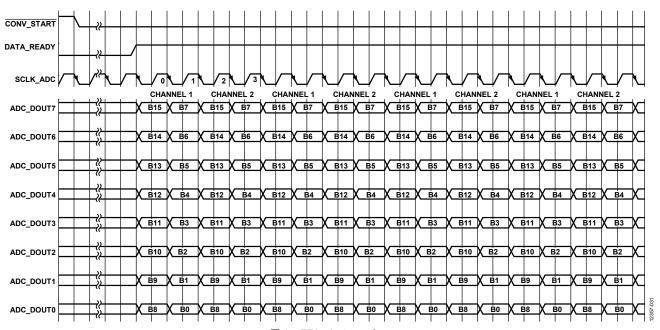

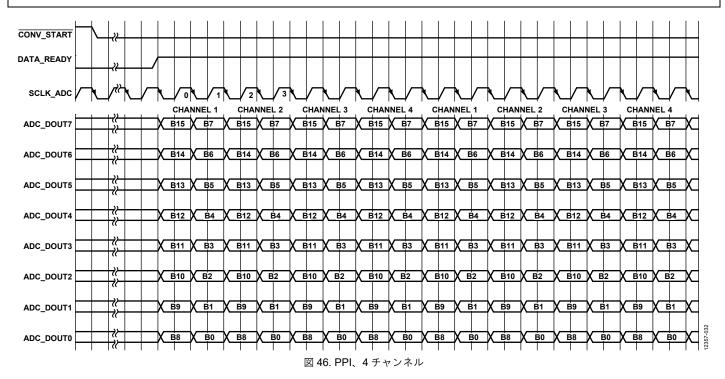

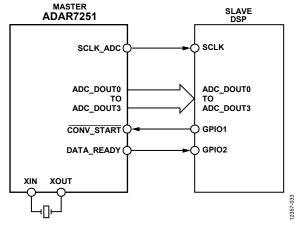

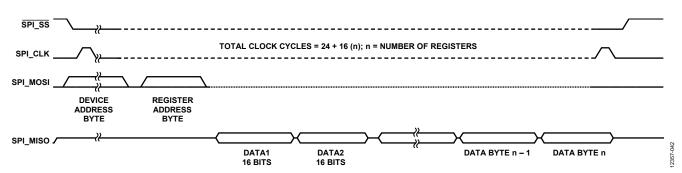

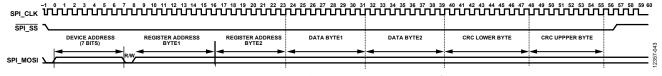

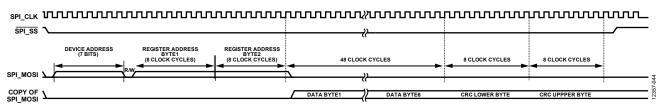

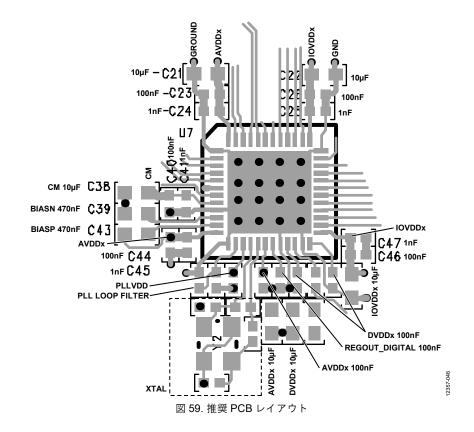

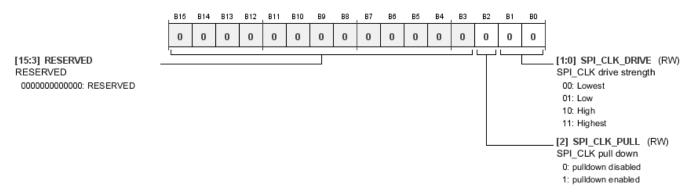

| SPI CLK ピン駆動強度およびスルー・レート・レジスタ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |