# デュアル・チャンネル 3.3GHz~4.0GHz、20W Φ レシーバー・フロント・エンド

**ADRF5515** -タシート

デュアル・チャンネル RF フロント・エンドを内蔵 2段 LNA および高出カシリコン SPDT スイッチ オンチップのバイアスおよびマッチング 単電源動作

#### ゲイン

高ゲイン・モード: 3.6GHz で 33dB(代表値) 低ゲイン・モード: 3.6GHz で 16dB (代表値)

#### 低ノイズ指数

高ゲイン・モード: 3.6GHz で 1.0dB(代表値) 低ゲイン・モード: 3.6GHz で 1.0dB (代表値)

#### 高アイソレーション

RXOUT-CHA と RXOUT-CHB: 45dB(代表値) TERM-CHA と TERM-CHB: 60dB(代表値) 低挿入損失: 3.6GHz で 0.45dB (代表値)

#### T<sub>CASE</sub> = 105°C で高出力に対応

#### 寿命全期間

正ロジック制御

平均 LTE 出力(9dB PAR): 43dBm 高 OIP3(高ゲイン・モード): 32dBm(代表値) LNA 用パワーダウン・モードおよび低ゲイン・モード

高ゲイン・モード:5Vで86mA(代表値) 低ゲイン・モード: 5V で 36mA(代表値) パワーダウン・モード:5Vで12mA(代表値)

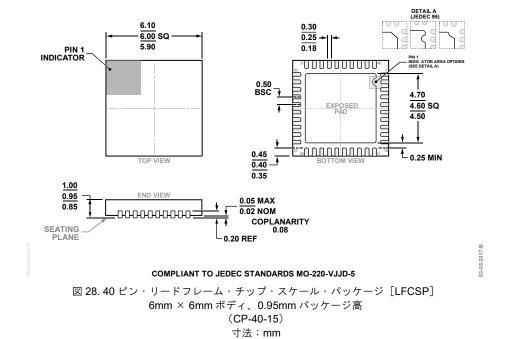

6mm × 6mm、40 ピン LFCSP パッケージ ADRF5545A (10W バージョン) とのピン互換性

### アプリケーション

ワイヤレス・インフラストラクチャ TDD Massive Multiple-Input Multiple-Output および アクティブ・アンテナ・システム TDD ベースの通信システム

#### 概要

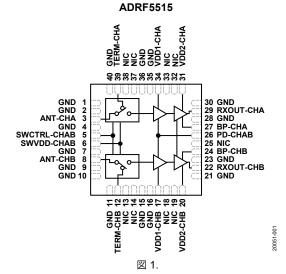

ADRF5515 は、時分割複信(TDD)アプリケーション用に設計 されたデュアル・チャンネルの統合型RFフロント・エンド・マ ルチチップ・モジュールです。このデバイスは3.3GHz~4.0GHz の範囲で動作します。2 段カスケード LNA と高出力シリコン SPDT スイッチを備えたデュアル・チャンネル構成となってい ます。

高ゲイン・モードでは、2 段カスケード LNA およびスイッチを 使用して、低ノイズ指数 1.0dB、高ゲイン 33dB (3.6GHz 時)、 出力 3 次インターセプト・ポイント (OIP3) 32dBm (代表値) を実現します。低ゲイン・モードでは、2段 LNA のうち1段は バイパスされ、36mA という低電流で 16dB のゲインを実現しま す。パワーダウン・モードでは、LNA はオフとなり、デバイス は12mAの電流を供給します。

#### 機能ブロック図

送信動作において、RF 入力が終端ピン(TERM-CHA または TERM-CHB) に接続されると、スイッチは 0.45dB という低挿入 損失となり、ロング・ターム・エボリューション (LTE) の平 均電力 (ピーク対平均値比 (PAR) 9dB) は、寿命全期間動作 で43dBmになります。

ADRF5515 は、2.4GHz~4.2GHz で動作する ADRF5545A (10W バージョン)とのピン互換性を備えています。

ADRF5515のRFポートは内部で $50\Omega$ に整合されているため、マ ッチング部品は不要です。また、ANT ポートと TERM ポートは 内部で AC カップリングされています。そのため、レシーバ ー・ポートにのみ、外付けの DC 阻止コンデンサが必要となり ます。

このデバイスは、RoHS 準拠の小型 6mm×6mm、40 ピン LFCSP パッケージを採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2020 Analog Devices, Inc. All rights reserved

Rev 0

太

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

### 目次

| 符長             |   |

|----------------|---|

| アプリケーション       |   |

|                |   |

| 概要             |   |

| 機能ブロック図        |   |

| 改訂履歴           | - |

|                |   |

| 仕様             | 1 |

| 電気仕様           | 1 |

| 絶対最大定格         |   |

|                |   |

| 熱抵抗            | 4 |

| 静電放電(ESD)定格    | 4 |

|                |   |

| ESD に関する注意     | : |

| ピン配置およびピン機能の説明 | ( |

| インターノエース回路凶   | /  |

|---------------|----|

| 代表的な性能特性      | 8  |

| 受信動作、高ゲイン・モード | 8  |

| 受信動作、低ゲイン・モード | 10 |

| 送信動作          | 12 |

| 動作原理          | 13 |

| 信号パスの選択       | 13 |

| バイアス・シーケンス    | 13 |

| アプリケーション情報    | 14 |

| 外形寸法          | 15 |

| オーダー・ガイド      | 15 |

### 改訂履歴

11/2020—Revision 0: Initial Version

### 仕様 電気仕様

特に指定のない限り、50Ω のシステムに対し、VDD1-CHA、VDD1-CHB、VDD2-CHA、VDD2-CHB、SWVDD-CHAB = 5V、SWCTRL-CHAB = 0V または SWVDD-CHAB、BP-CHA = VDD1-CHA または 0V、BP-CHB = VDD1-CHB または 0V、PD-CHAB = 0V または VDD1-CHA、T<sub>CASE</sub> = 25℃。

表 1.

| パラメータ                                                    | テスト条件/コメント                                        | Min  | Тур  | Max      | 単位    |

|----------------------------------------------------------|---------------------------------------------------|------|------|----------|-------|

| FREQUENCY RANGE                                          |                                                   | 3.3  |      | 4.0      | GHz   |

| GAIN <sup>1</sup>                                        | 3.6GHzでの受信動作                                      |      |      |          |       |

| High Gain Mode                                           |                                                   |      | 33   |          | dB    |

| Low Gain Mode                                            |                                                   |      | 16   |          | dB    |

| GAIN FLATNESS <sup>1</sup>                               | 任意の 100MHz 帯域幅での受信動作                              |      |      |          |       |

| High Gain Mode                                           |                                                   |      | 0.6  |          | dB    |

| Low Gain Mode                                            |                                                   |      | 0.2  |          | dB    |

| NOISE FIGURE <sup>1</sup>                                | 3.6GHz での受信動作                                     |      |      |          |       |

| High Gain Mode                                           |                                                   |      | 1.0  |          | dB    |

| Low Gain Mode                                            |                                                   |      | 1.0  |          | dB    |

| OUTPUT THIRD-ORDER INTERCEPT POINT (OIP3) <sup>1</sup>   | 受信動作。ツートーン出力電力:トーンあたり 8dBm (1MHzのトーン間隔時)。         |      |      |          |       |

| High Gain Mode                                           |                                                   |      | 32   |          | dBm   |

| Low Gain Mode                                            |                                                   |      | 29   |          | dBm   |

| OUTPUT 1 dB COMPRESSION (OP1dB)                          |                                                   |      |      |          |       |

| High Gain Mode                                           |                                                   |      | 18   |          | dBm   |

| Low Gain Mode                                            |                                                   |      | 15   |          | dBm   |

| INSERTION LOSS <sup>1</sup>                              | 3.6GHz での送信動作                                     |      | 0.45 |          | dB    |

| Channel to Channel Isolation <sup>1</sup>                | 3.6GHz 時                                          |      |      |          |       |

| Between RXOUT-CHA AND RXOUT-CHB                          | 受信動作                                              |      | 45   |          | dB    |

| Between TERM-CHA AND TERM-CHB                            | 送信動作                                              |      | 60   |          | dB    |

| SWITCH ISOLATION                                         |                                                   |      |      |          |       |

| ANT-CHA to TERM-CHA and ANT-CHB to TERM-CHB <sup>1</sup> | 送信動作、PD-CHAB = 0V                                 |      | 18.5 |          | dB    |

| SWITCHING CHARACTERISTICS $(t_{ON}, t_{OFF})$            | 受信動作時、50%の制御電圧から RXOUT-CHA または                    |      | 600  |          | ns    |

|                                                          | RXOUT-CHB の 90%および 10%まで                          |      | 000  |          | 118   |

|                                                          | 送信動作時、50%の制御電圧から TERM-CHA または                     |      | 595  |          | ns    |

|                                                          | TERM-CHB の 90%および 10%まで                           |      | 373  |          | 113   |

| RECOMMENDED OPERATING CONDITIONS                         | TEIGH CIB W young or o' Toylor C                  |      |      |          |       |

| Supply Voltage ( $V_{DD}$ ) Range                        | VDD1-CHA、VDD1-CHB、VDD2-CHA、VDD2-CHB、              | 4.75 | 5    | 5.25     | V     |

| C + 1V h P                                               | SWVDD-CHAB                                        |      |      | ***      | * * * |

| Control Voltage Range                                    | SWCTRL-CHAB、BP-CHA、BP-CHB、PD-CHAB                 | 0    |      | $V_{DD}$ | V     |

| RF Input Power                                           | SWCTRL-CHAB = $5V$ , $T_{CASE} = 105$ °C          |      |      |          |       |

| At ANT-CHA, ANT-CHB                                      | PD-CHAB = 5V, BP-CHA = BP-CHB = 0V                | 1    |      |          |       |

|                                                          | 9dB PAR(LTE 寿命全期間平均)                              | 1    |      | 43       | dBm   |

|                                                          | 7dB PAR(LTE シングル・イベント(10 秒未満)平<br>均) <sup>1</sup> |      |      | 46       | dBm   |

| At ANT-CHA, ANT-CHB                                      | PD-CHAB = 0V, BP-CHA = BP-CHB = 0V                |      |      |          |       |

|                                                          | 9dB PAR(LTE 寿命全期間平均)                              |      |      | 31       | dBm   |

Rev. 0 - 3/15 -

| パラメータ                                             | テスト条件/コメント                                           | Min | Тур   | Max      | 単位  |

|---------------------------------------------------|------------------------------------------------------|-----|-------|----------|-----|

| At ANT-CHA, ANT-CHB                               | PD-CHAB = 0V, BP-CHA = BP-CHB = 5V                   |     |       |          |     |

|                                                   | 9dB PAR(LTE 寿命全期間平均)、3.3GHz~4.0GHz                   |     |       | 43       | dBm |

|                                                   | 7dB PAR(LTE シングル・イベント(10 秒未満)平                       |     |       | 46       | dBm |

|                                                   | 均) 1                                                 |     |       |          |     |

| $T_{CASE}$ Range <sup>2</sup>                     |                                                      | -40 |       | +105     | °C  |

| Junction Temperature at Maximum T <sub>CASE</sub> |                                                      |     |       |          |     |

|                                                   | 受信動作3                                                |     |       | 132      | °C  |

|                                                   | 送信動作3                                                |     |       | 134      | °C  |

| DIGITAL INPUT                                     |                                                      |     |       |          |     |

| SWCTRL-CHAB, PD-CHAB                              |                                                      |     |       |          |     |

| $Low(V_{IL})$                                     |                                                      | 0   |       | 0.7      | V   |

| High (V <sub>IH</sub> )                           |                                                      | 1.4 |       | $V_{DD}$ | V   |

| BP-CHA, BP-CHB                                    |                                                      |     |       |          |     |

| $Low(V_{IL})$                                     |                                                      | 0   |       | 0.3      | V   |

| High (V <sub>IH</sub> )                           |                                                      | 1.0 |       | $V_{DD}$ | V   |

| SUPPLY CURRENT (I <sub>DD</sub> )                 | VDD1-CHx および VDD2-CHx = 5V (チャンネルあたり)                |     |       |          |     |

| High Gain Mode                                    |                                                      |     | 86    |          | mA  |

| Low Gain Mode                                     |                                                      |     | 36    |          | mA  |

| Power-Down Mode                                   |                                                      |     | 12    |          | mA  |

| Transmitter Current (Switch)                      | SWVDD-CHAB = 5V                                      |     | 1.3   |          | mA  |

| DIGITAL INPUT CURRENTS                            | SWCTRL-CHAB、PD-CHAB、BP-CHA、BP-CHB = 5V<br>(チャンネルあたり) |     |       |          |     |

| SWCTRL-CHAB                                       |                                                      |     | 0.084 |          | mA  |

| PD-CHAB                                           |                                                      |     | 0.19  |          | mA  |

| BP-CHA, BP-CHB                                    |                                                      |     | 0.19  |          | mA  |

<sup>&</sup>lt;sup>1</sup>53dBm を上回るピーク電力は評価していません。 <sup>2</sup>露出パッドで測定 <sup>3</sup>表5および表6を参照してください。

**- 4/15 -**Rev. 0

### 絶対最大定格

表 2.

| Parameter                         | Rating                                     |

|-----------------------------------|--------------------------------------------|

| Supply Voltage (V <sub>DD</sub> ) |                                            |

| VDD1-CHA, VDD1-CHB, VDD2-         | 7 V                                        |

| CHA, and VDD2-CHB                 |                                            |

| SWVDD-CHAB                        | 5.4 V                                      |

| Digital Control Input Voltage     |                                            |

| SWCTRL-CHAB                       | -0.3 V to V <sub>DD</sub> + 0.3 V          |

| BP-CHA, BP-CHB, and PD-CHAB       | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Digital Control Input Current     |                                            |

| BP-CHA, BP-CHB, PD-CHAB, and      | 20 mA                                      |

| SWCTRL-CHAB                       |                                            |

| RF Input Power                    |                                            |

| Transmit Input Power (LTE Peak,   | 53 dBm                                     |

| 9 dB PAR)                         |                                            |

| Receive Input Power (LTE Peak,    | 25 dBm                                     |

| 9 dB PAR)                         |                                            |

| Temperature                       |                                            |

| Storage Range                     | −65°C to +150°C                            |

| Reflow                            | 260°C                                      |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありま せん。デバイスを長時間にわたり絶対最大定格状態に置くと、 デバイスの信頼性に影響を与えることがあります。

#### 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接 関連しています。PCB の熱設計には、細心の注意を払う必要が あります。

$\theta_{IC}$  は、ジャンクションからケース底部(チャンネルからパッケージ底部)への熱抵抗です。

#### 表 3. 熱抵抗

| Package Type    | $\theta_{JC}$ | Unit |

|-----------------|---------------|------|

| CP-40-15        |               |      |

| High Gain Mode  | 30            | °C/W |

| Low Gain Mode   | 36            | °C/W |

| Power-Down Mode | 6             | °C/W |

#### 静電放電(ESD)定格

以下の  $\mathrm{ESD}$ 情報は、 $\mathrm{ESD}$ 保護された領域でのみ  $\mathrm{ESD}$ に敏感なデバイスを取り扱うためのものです。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の帯電デバイス・モデル (CDM)。

#### ADRF5515 の ESD 定格

表 4. ADRF5515、40 ピン LFCSP

| ESD Model | Withstand Threshold | Class |

|-----------|---------------------|-------|

| HBM       | 1 kV                | 1C    |

| CDM       | 750 V               |       |

#### ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

Rev. 0 – 5/15 –

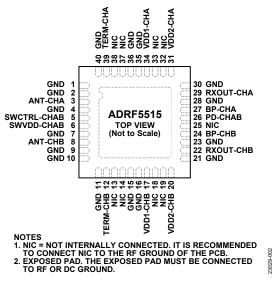

## ピン配置およびピン機能の説明

図 2. ピン配置

表 5. ピン機能の説明

| ピン番号                                                    | 記号          | 説明                                                                                                                                       |

|---------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 7, 9 to 11, 15, 16, 21, 23, 28, 30, 35, 36, 40 | GND         | グラウンド。                                                                                                                                   |

| 3                                                       | ANT-CHA     | チャンネル A の RF 入力。ANT-CHA ピンは $0$ V に AC カップリングされ、 $50$ Ω に整合されています。マッチング・コンデンサおよび DC 阻止コンデンサは不要です。                                        |

| 5                                                       | SWCTRL-CHAB | チャンネル A およびチャンネル B のスイッチ用制御電圧。                                                                                                           |

| 6                                                       | SWVDD-CHAB  | チャンネル A およびチャンネル B のスイッチ用電源電圧。                                                                                                           |

| 8                                                       | ANT-CHB     | チャンネル B の RF 入力。ANT-CHB ピンは $0$ V に AC カップリングされ、 $50$ Ω に整合されています。マッチング・コンデンサおよび DC 阻止コンデンサは不要です。                                        |

| 12                                                      | TERM-CHB    | チャンネル B の終端出力。TERM-CHB ピンはチャンネル B のトランスミッタ・パスです。TERM-CHB ピンは $0$ V に $A$ C カップリングされ、 $50$ Ω に整合されています。マッチング・コンデンサおよび $D$ C 阻止コンデンサは不要です。 |

| 13, 14, 18, 19, 25, 32, 33, 37, 38                      | NIC         | 内部では未接続。NIC は PCB の RF グラウンドに接続することを推奨します。                                                                                               |

| 17                                                      | VDD1-CHB    | チャンネルBの1段目のLNA用電源電圧。                                                                                                                     |

| 20                                                      | VDD2-CHB    | チャンネルBの2段目のLNA用電源電圧。                                                                                                                     |

| 22                                                      | RXOUT-CHB   | レシーバー出力。RXOUT-CHB ピンはチャンネル B のレシーバー・パスです。RXOUT-CHB ピンは $50\Omega$ に AC 整合されています。マッチング部品は不要ですが、DC 阻止コンデンサが必要です。                           |

| 24                                                      | BP-CHB      | チャンネルBの2段目のLNAをバイパス。                                                                                                                     |

| 26                                                      | PD-CHAB     | チャンネル A およびチャンネル B の全段の LNA をパワーダウン。                                                                                                     |

| 27                                                      | BP-CHA      | チャンネル A の 2 段目の LNA をバイパス。                                                                                                               |

| 29                                                      | RXOUT-CHA   | レシーバー出力。RXOUT-CHA ピンはチャンネル A のレシーバー・パスです。RXOUT-CHA ピンは $50\Omega$ に AC 整合されています。マッチング部品は不要ですが、DC 阻止コンデンサが必要です。                           |

| 31                                                      | VDD2-CHA    | チャンネルAの2段目のLNA用電源電圧。                                                                                                                     |

| 34                                                      | VDD1-CHA    | チャンネルAの1段目のLNA用電源電圧。                                                                                                                     |

| 39                                                      | TERM-CHA    | チャンネル A の終端出力。TERM-CHA ピンはチャンネル A のトランスミッタ・パスです。TERM-CHA ピンは $0$ V に AC カップリングされ、 $50$ Ω に整合されています。マッチング・コンデンサおよび $0$ C 阻止コンデンサは不要です。    |

|                                                         | EPAD        | 露出パッド。露出パッドは RF または DC グラウンドに接続する必要があります。                                                                                                |

Rev. 0 — 6/15 —

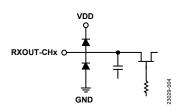

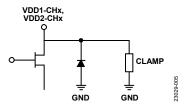

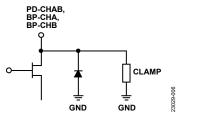

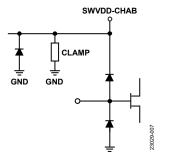

### インターフェース回路図

図 4. RXOUT-CHx のインターフェース

図 5. VDD1-CHx、VDD2-CHx のインターフェース

図 6. PD-CHAB、BP-CHx のインターフェース

図 7. SWCTRL-CHAB、SWVDD-CHAB のインターフェース

Rev. 0 - 7/15 -

### 代表的な性能特性

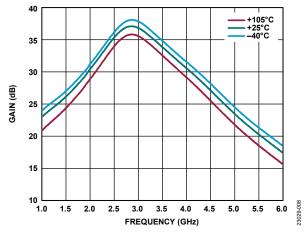

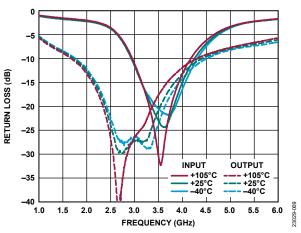

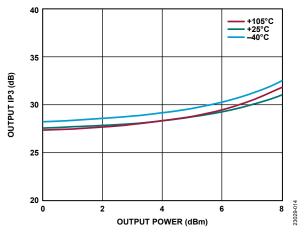

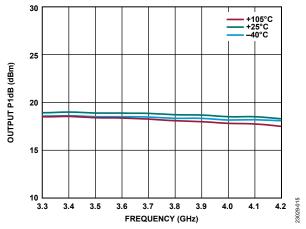

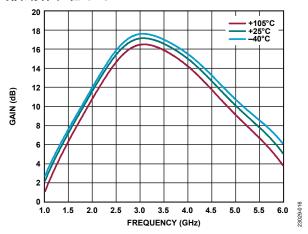

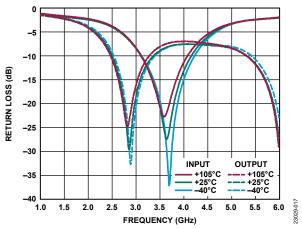

#### 受信動作、高ゲイン・モード

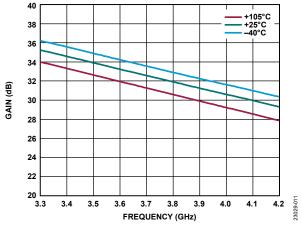

図 8. 様々な温度でのゲインの周波数特性

図 9. 様々な温度での入出力リターン・ロスの周波数特性

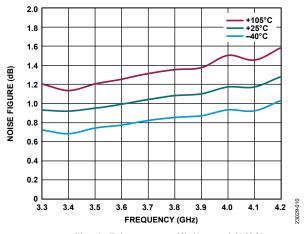

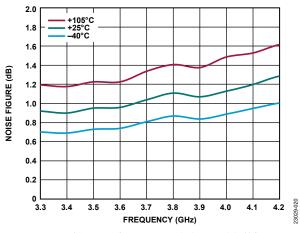

図 10. 様々な温度でのノイズ指数の周波数特性

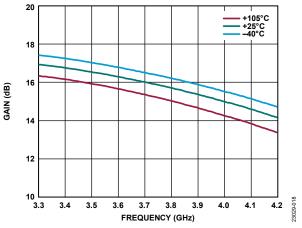

図 11. 様々な温度でのゲインの周波数特性、3.3GHz~4.2GHz

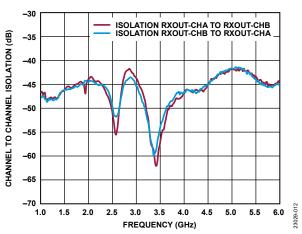

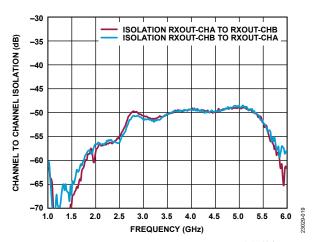

図 12. チャンネル間アイソレーションの周波数特性

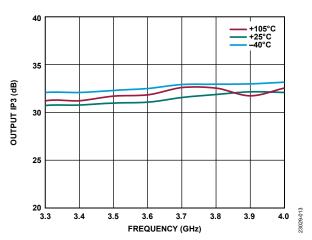

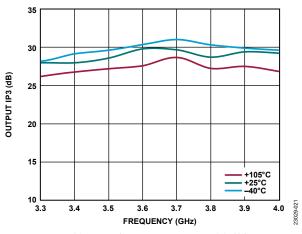

図 13. 様々な温度での出力 IP3 の周波数特性、 出力トーン電力 8dBm

Rev. 0 - 8/15 -

図 14. 様々な温度での出力 IP3 と出力電力の関係、3.6GHz

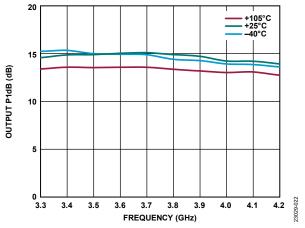

図 15. 様々な温度での出力 P1dB の周波数特性

Rev. 0 - 9/15 -

#### 受信動作、低ゲイン・モード

図 16. 様々な温度でのゲインの周波数特性

図 17. 様々な温度での入出力リターン・ロスの周波数特性

図 18. 様々な温度でのゲインの周波数特性、3.3GHz~4.2GHz

図 19. チャンネル間アイソレーションの周波数特性

Rev. 0 – 10/15 –

図 20. 様々な温度でのノイズ指数の周波数特性

図 21. 様々な温度での出力 IP3 の周波数特性、 出力トーン電力-10dBm

図 22. 様々な温度での出力 P1dB の周波数特性

Rev. 0 – 11/15 –

#### 送信動作

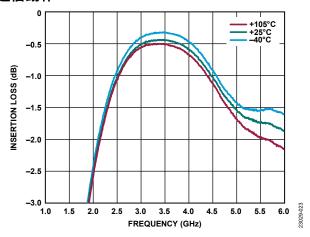

図 23. 様々な温度での挿入損失の周波数特性

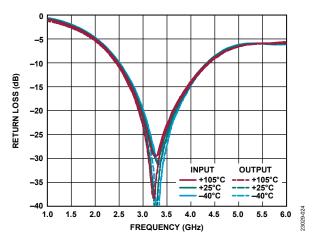

図 24. 様々な温度での入出力リターン・ロスの周波数特性

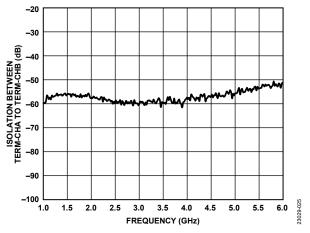

図 25. TERM-CHA と TERM-CHB 間のアイソレーションの 周波数特性

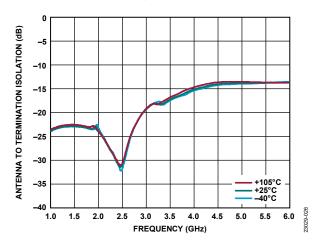

図 26. 様々な温度でのアンテナと終端間のアイソレーションの 周波数特性、LNA オン

Rev. 0 – 12/15 –

### 動作原理

ADRF5515 に は、 VDD1-CHA 、 VDD2-CHA 、 VDD1-CHB 、 VDD2-CHB、 SWVDD-CHAB に印加する正電源電圧が必要です。 ノイズを除去するため、電源ラインにはバイパス用コンデンサを使用してください。また、グリッチおよび過電流保護のため、デジタル制御ピンの BP-CHx と PD-CHAB には  $300\Omega$  の直列抵抗を使用してください。

#### 信号パスの選択

SWCTRL-CHAB に 5V が印加されると、ADRF5515 は送信動作に対応します。送信動作では、ANT-CHA および ANT-CHB に RF が入力されると、ANT-CHA から TERM-CHA、および ANT-CHB から TERM-CHB への信号パスが接続されます。

SWCTRL-CHAB に 0V が印加されると、ADRF5515 は受信動作に対応します。受信動作では、ANT-CHA および ANT-CHB に RFが入力されると、ANT-CHA から RXOUT-CHA、および ANT-CHB から RXOUT-CHB への接続が行われます。

#### 送信動作

送信動作、すなわち SWCTRL-CHAB = 5V のときには、ADRF5515 は挿入損失モードとアイソレーション・モードをサポートします。表7に詳述されているように、PD-CHABを5V、BP-CHA または BP-CHB を 0V に設定すると挿入損失モードが選択されます。同じ状況下で PD-CHABに 0V を印加すると、アイソレーション・モードが選択されます。

#### 受信動作

表7に示すように、ADRF5515は受信動作において、高ゲイン・モード、低ゲイン・モード、パワーダウン高アイソレーション・モード、パワーダウン低アイソレーション・モードをサポートします。

PD-CHAB に 0V を印加すると、LNA がパワーアップし、ユーザは高ゲイン・モードまたは低ゲイン・モードを選択できます。高ゲイン・モードを選択するには、BP-CHA または BP-CHB に 0V を印加します。低ゲイン・モードを選択するには、BP-CHA または BP-CHB に 5V を印加します。

PD-CHAB に 5V を印加すると、ADRF5515 はパワーダウン・モードになります。パワーダウン高アイソレーション・モードを選択するには、BP-CHA または BP-CHB に 0V を印加します。パワーダウン低アイソレーション・モードを選択するには、BP-CHA または BP-CHB に 5V を印加します。

#### バイアス・シーケンス

ADRF5515 にバイアスを加えるには、以下の手順を実行します。

- 1. GND を接地します。

- 2. VDD1-CHA、VDD2-CHA、VDD1-CHB、VDD2-CHB、 SWVDD-CHAB にバイアスを加えます。

- 3. SWCTRL-CHAB にバイアスを加えます。

- 4. PD-CHAB にバイアスを加えます。

- 5. BP-CHA と BP-CHB にバイアスを加えます。

- 6. RF入力信号を印加します。

バイアスを停止するには、これらの手順を逆順で実行します。

#### 表 6. 真理値表:信号パス

|             | Signal Path Select   |                   |

|-------------|----------------------|-------------------|

| SWCTRL-CHAB | Transmit Operation 1 | Receive Operation |

| Low         | Off                  | On                |

| High        | On                   | Off               |

<sup>1</sup>表6の信号パスの説明を参照してください。

#### 表 7. 真理值表:動作、SWCTRL-CHAB = 口一

| CHARLES WITH CHARLEST IN       |         |                |                                            |

|--------------------------------|---------|----------------|--------------------------------------------|

| Operation                      | PD-CHAB | BP-CHA, BP-CHB | Signal Path                                |

| Receive Operation              |         |                | ANT-CHA to RXOUT-CHA, ANT-CHB to RXOUT-CHB |

| High Gain Mode                 | Low     | Low            |                                            |

| Low Gain Mode                  | Low     | High           |                                            |

| Power-Down High Isolation Mode | High    | Low            |                                            |

| Power-Down Low Isolation Mode  | High    | High           |                                            |

Rev. 0 – 13/15 –

## アプリケーション情報

代表的なアプリケーション回路(詳細については ADRF5515-EVALZユーザ・ガイドを参照)で使用される評価用 PCBを作成するには、適切な RF 回路設計技術を使用してください。RF ポートの信号線のインピーダンスは  $50\Omega$  であることが必要です。また、パッケージのグラウンド・リードと裏面のグラウンド・スラグはグランド・プレーンに直接接続する必要があります。

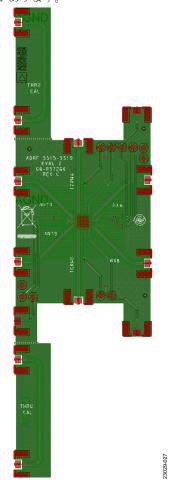

グリッチおよび過電流保護のため、デジタル制御ピンの BP-CHx と PD-CHABには  $300\Omega$  の直列抵抗を使用してください。図 27に 示した評価用ボードは、ご要望に応じてアナログ・デバイセズ から提供されます。評価用ボードの追加情報については、ADRF5515-EVALZ ユーザ・ガイドを参照してください。

図 27. ADRF5515-EVALZ 評価用ボード

Rev. 0 – 14/15 –

### 外形寸法

オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| ADRF5515BCPZN      | -40°C to +105°C   | 40-Lead Lead Frame Chip Scale Package [LFCSP] | CP-40-15       |

| ADRF5515BCPZN-R7   | −40°C to +105°C   | 40-Lead Lead Frame Chip Scale Package [LFCSP] | CP-40-15       |

| ADRF5515BCPZN-RL   | −40°C to +105°C   | 40-Lead Lead Frame Chip Scale Package [LFCSP] | CP-40-15       |

| ADRF5515-EVALZ     |                   | Evaluation Board                              |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。

Rev. 0 — 15/15 —