# 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、2021年3月24日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日: 2021年3月24日

製品名:ADRV9029

対象となるデータシートのリビジョン(Rev): Rev.0

訂正箇所:

129ページ 左の段 下から4行目

#### 【誤】

「これら2つのシナリオ・・」

#### 【正】

「これら3つのシナリオ・・」

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

# オブザベーション・パス付きの 集積化クワッド RF トランシーバー

**ADRV9029** データシート

#### 特長

差動トランスミッタ×4個 差動レシーバー×4個

2入力オブザベーション・レシーバー×2個

中心周波数:75MHz~6000MHz

パワー・アンプ直線化用の完全内蔵型 DPD アダプテーション・ エンジン

クレスト・ファクタ低減エンジン レシーバー最大帯域幅: 200MHz

トランスミッタ大信号最大帯域幅:200MHz

トランスミッタ・シンセシス最大帯域幅:450MHz オブザベーション・レシーバー最大帯域幅: 450MHz 完全内蔵型の独立したフラクショナルN無線周波数

シンセサイザ

完全内蔵型のクロック・シンセサイザ

すべての局部発振器およびベースバンド・クロック用の マルチチップ位相同期

TDD および FDD アプリケーションをサポート

24.33Gbps JESD204B/JESD204C デジタル・インターフェース

#### アプリケーション

3G/4G/5G TDD および FDD Massive MIMO、マクロ・セル およびスモール・セル基地局

#### 概要

ADRV9029 は、高度に集積化された無線周波数 (RF) アジャイ ル・トランシーバーです。個別に制御可能なトランスミッタ 4 個、各トランスミッタ・チャンネル監視専用のオブザベーショ ン・レシーバー入力、個別に制御可能なレシーバー4個、内蔵 シンセサイザ、デジタル信号処理回路を搭載し、フル機能のト ランシーバー・ソリューションを提供します。また、スモー ル・セル基地局無線、マクロ 3G/4G/5G システム、Massive MIMO (Multiple Input Multiple Output) 基地局などのセルラ・イ ンフラストラクチャ・アプリケーションに必要な性能を備えて います。

レシーバー・サブシステムには、幅広いダイナミック・レンジ を持つ独立した 4 つの広帯域幅ダイレクト・コンバージョン・ レシーバーが搭載されています。4 つの独立したトランスミッ タはダイレクト・コンバージョン変調器を使用しているため、 動作時のノイズと消費電力を低減できます。また、各トランス ミッタ出力を監視するための 2 つの入力を備えた広帯域幅の時 分割方式オブザベーション・パス・レシーバーを 2 個内蔵して います。

トランシーバー・サブシステムは全機能内蔵型で、自動および 手動の減衰制御、DC オフセット補正回路、直交誤差補正回路 (QEC)、およびデジタル・フィルタリングなどの機能を備え

ているので、デジタル・ベースバンドにこれらの機能は不要で す。また、多数のデジタル制御オプションを提供する A/D コン バータ (ADC) 、D/A コンバータ (DAC) 、汎用入出力 (GPIO) などの補助機能も搭載しています。

高レベルの RF性能を実現するため、トランシーバーには、完全 内蔵型のフェーズ・ロック・ループ (PLL) が5個搭載されてい ます。PLL のうち 2 個は、トランスミッタとレシーバー信号パ スに対し、低ノイズで低消費電力のフラクショナル N-RF シンセ シスを行います。もう 1 個は、オブザベーション・レシーバー 用の独立した局部発振器(LO)モードをサポートしています。 残り 2 個のうちの片方はコンバータとデジタル回路に必要なク ロックを生成し、もう片方はシリアル・データ・インターフェ ース用のクロックを生成します。

マルチチップ同期メカニズムは、複数の ADRV9029 チップ間で すべての局部発振器 (LO) とベースバンド・クロックの位相を 同期します。また、すべての電圧制御発振器(VCO)とルー プ・フィルタの構成要素が内蔵されており、デジタル制御イン ターフェースを通じて調節することができます。

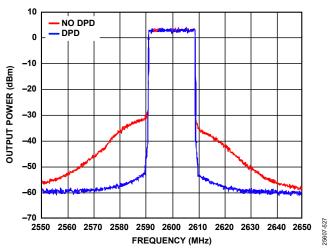

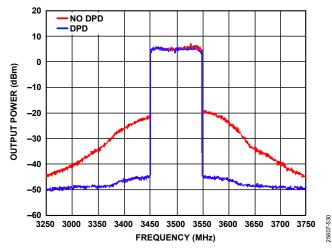

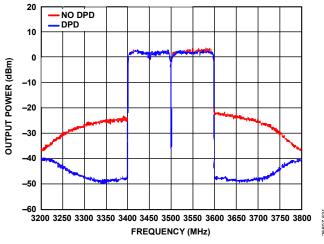

このデバイスには、パワー・アンプのリニアライゼーションに 使用する、完全内蔵型で低消費電力のデジタル・プリディスト ーション (DPD) アダプテーション・エンジンが搭載されてい ます。DPD によって、高効率のパワー・アンプを使用できるよ うになるため、基地局無線の消費電力を低減すると同時に、ベ ースバンド・プロセッサとのインターフェース接続に必要な SERDES レーンの数を削減することができます。

ADRV9029 の低消費電力クレスト・ファクタ低減(CFR)エン ジンは、入力信号のピーク値と平均値の比(PAR)を小さくし て、ベースバンド・プロセッサの処理負荷を軽減しながら、効 率の高い送信系列を実現します。

シリアル・データ・インターフェースは、4 つのシリアライ ザ・レーンと 4 つのデシリアライザ・レーンで構成されていま す。インターフェースはJESD204B規格およびJESD204C規格の 両方をサポートしており、最大24.33Gbpsのデータ・レートで動 作します。また、低帯域幅用にインターリーブ・モードをサポ ートすることで、高速データ・インターフェース・レーン数を 1 個に減らしています。データ・フォーマットは、固定小数点 と浮動小数点両方をサポートしています。浮動小数点フォーマ ットを選択すると、内部自動ゲイン制御(AGC)を復調器デバ イスから見えなくすることができます。

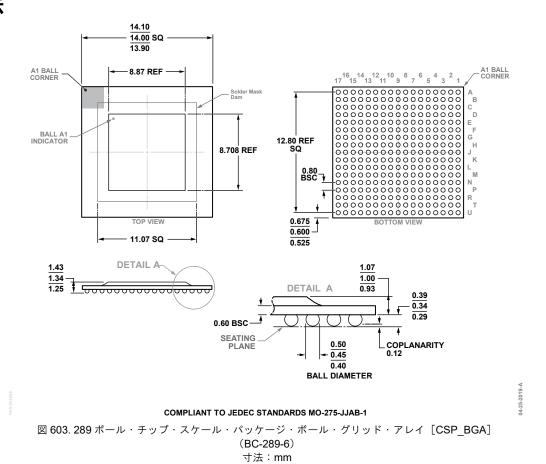

ADRV9029 は 1.0V、1.3V、1.8V のレギュレータから直接給電し、 標準シリアル・ペリフェラル・インターフェース (SPI) のシリ アル・ポートで制御します。また、通常使用の消費電力を最小 限に抑えるために、包括的パワーダウン・モードを搭載してい ます。ADRV9029は、14mm × 14mm、289ボールのチップ・ス ケール・ボール・グリッド・アレイ (CSP BGA) パッケージを 採用しています。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2020 Analog Devices, Inc. All rights reserved

Rev 0

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

### データシート

# 目次

| 特長                            | 1  |

|-------------------------------|----|

| アプリケーション                      | 1  |

| 概要                            | 1  |

| 改訂履歴                          | 2  |

| 機能ブロック図                       | 3  |

| 仕様                            | 4  |

| トランスミッタとレシーバー                 | 4  |

| シンセサイザ、補助コンバータ、およびクロック・<br>ンス |    |

| デジタル仕様                        |    |

| 電源仕様                          |    |

|                               |    |

| 消費電流                          |    |

| デジタル・インターフェースとタイミング仕様         | 17 |

| 絶対最大定格                        | 18 |

| ジャンクション温度                     | 18 |

| リフロー・プロファイル                   | 18 |

| 熱抵抗                           | 18 |

| ESD に関する注意                    | 18 |

| ピン配置およびピン機能の説明                | 19 |

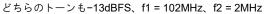

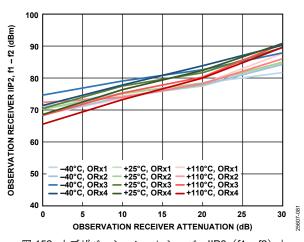

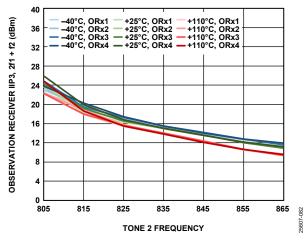

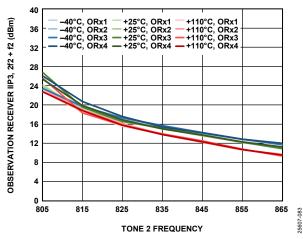

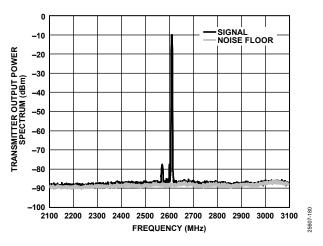

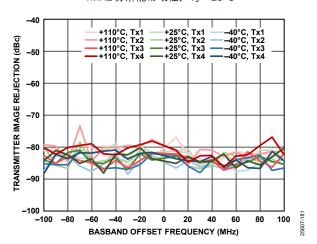

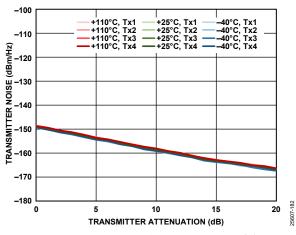

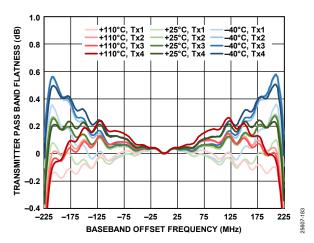

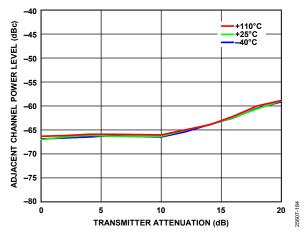

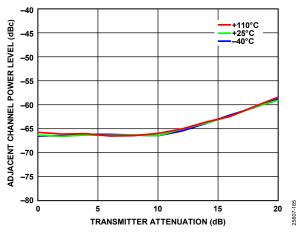

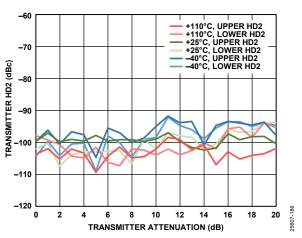

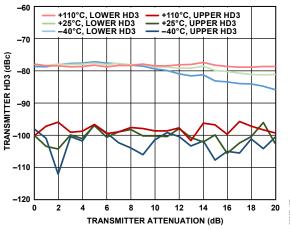

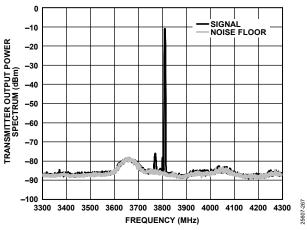

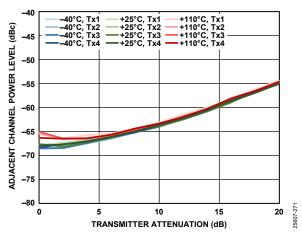

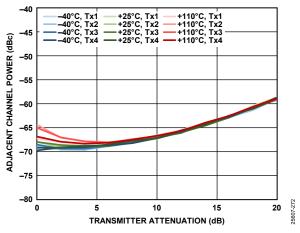

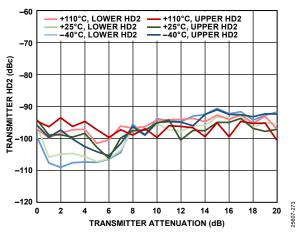

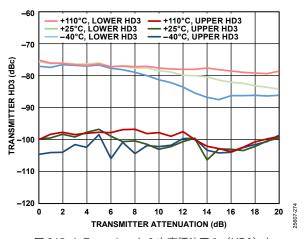

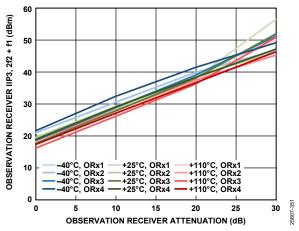

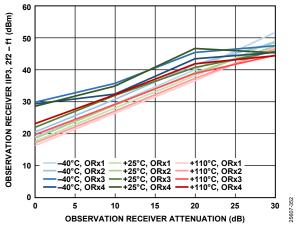

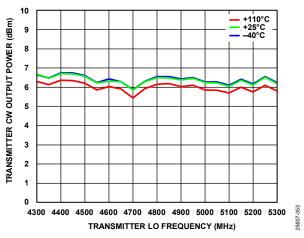

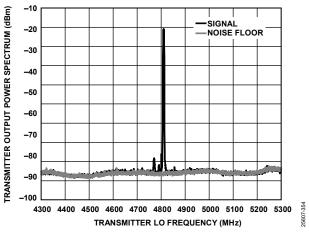

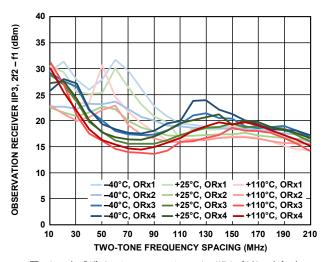

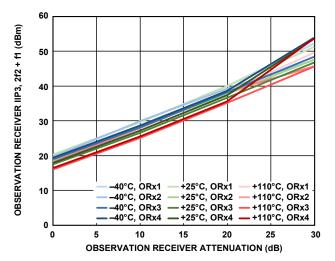

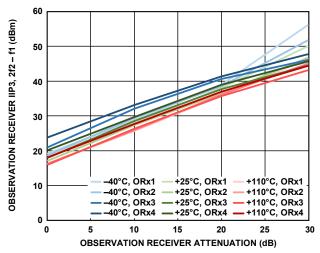

| 代表的な性能特性                      | 24 |

| 75MHz 帯域                      | 24 |

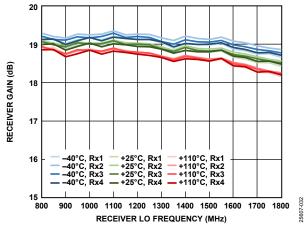

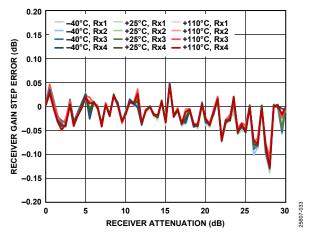

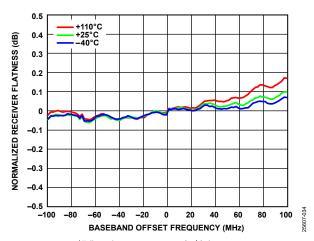

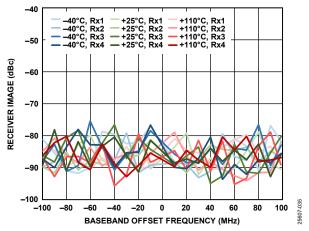

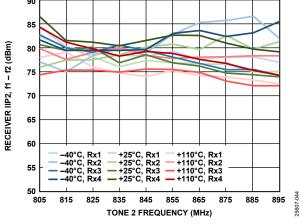

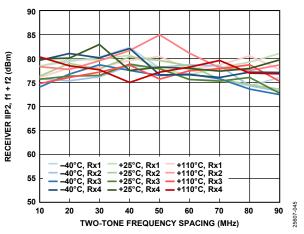

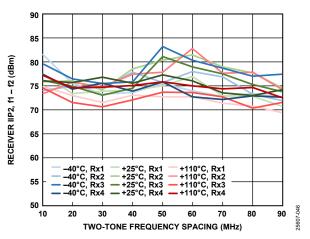

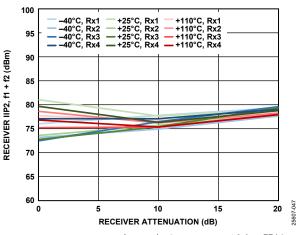

| 800MHz 帯域                     | 37 |

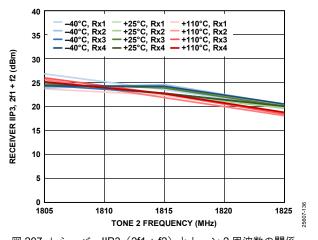

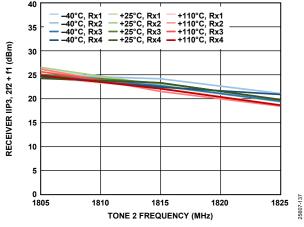

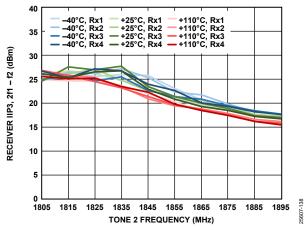

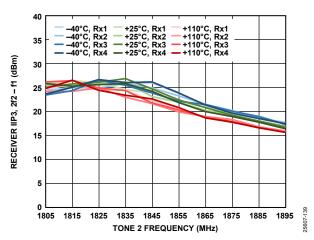

| 1800MHz 帯域                    | 52 |

| 2600MHz 帯域                    | 67 |

| 82  |

|-----|

| 97  |

| 112 |

| 127 |

| 127 |

| 127 |

| 127 |

| 127 |

| 127 |

| 128 |

| 128 |

| 128 |

| 128 |

| 128 |

| 131 |

| 131 |

| 132 |

| 132 |

| 132 |

| 133 |

| 133 |

|     |

#### 改訂履歴

12/2020—Revision 0: Initial Version

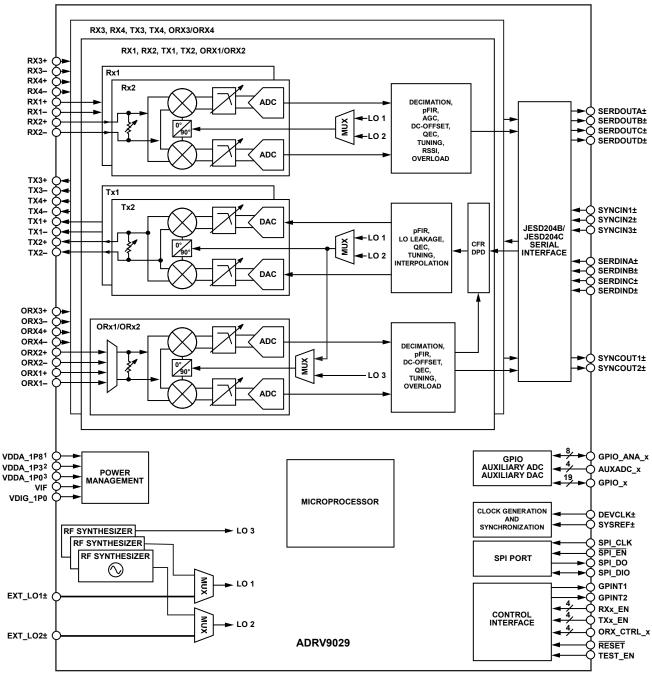

# 機能ブロック図

¹VDDA\_1P8 REPRESENTS VCONV1\_1P8, VCONV2\_1P8, VANA1\_1P8, VANA2\_1P8, VANA3\_1P8, VANA4\_1P8, AND VJVCO\_1P8.

²VDDA\_1P3 REPRESENTS VANA1\_1P3, VANA2\_1P3, VCONV1\_1P3, VCONV2\_1P3, VRFVCO1\_1P3, VRFVCO2\_1P3, VAUXVCO\_1P3, VCLKVCO\_1P3, VRFSYN1\_1P3, VRFSYN1\_1P3, VCLKSYN\_1P3, VAUXSYN\_1P3, VRXLO\_1P3, AND VTXLO\_1P3.

³VDDA\_1P0 REPRESENTS VJSYN\_1P0, VDES\_1P0, VTT\_DES, AND VSER\_1P0.

図 1.

2007

### 仕様

標準的な周囲温度範囲における電気的特性。各種電源は以下の通り。VDDA\_1P8 = 1.8V、VIF = 1.8V、VDDA\_1P3 = 1.3V、VDDA\_1P0 = 1.0V、VDIG\_1P0 = 1.0V。VDDA\_1P8 は、VCONV1\_1P8、VCONV2\_1P8、VANA1\_1P8、VANA2\_1P8、VANA3\_1P8、VANA4\_1P8、および VJVCO\_1P8 を表します。VDDA\_1P3 は、VANA1\_1P3、VANA2\_1P3、VCONV1\_1P3、VCONV2\_1P3、VRFVCO1\_1P3、VRFVCO2\_1P3、VAUXVCO\_1P3、VCLKVCO\_1P3、VRFSYN1\_1P3、VRFSYN2\_1P3、VCLKSYN\_1P3、VAUXSYN\_1P3、VRXLO\_1P3、VTXLO\_1P3 を表します。VDDA\_1P0 は、VJSYN\_1P0、VDES\_1P0、VTT\_DES、VSER\_1P0.を表します。特に指定のない限り、すべての RF 仕様は測定に基づくもので、これにはプリント回路基板(PCB)とマッチング回路の損失が含まれています。

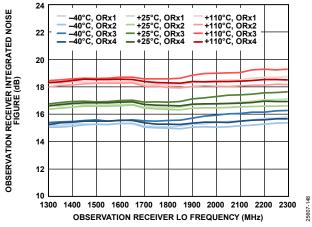

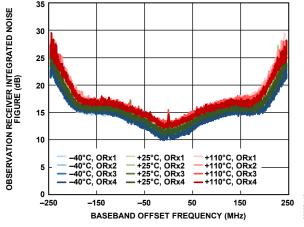

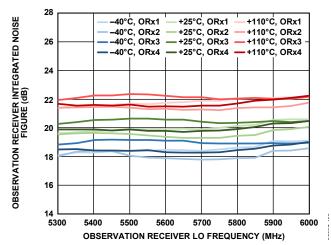

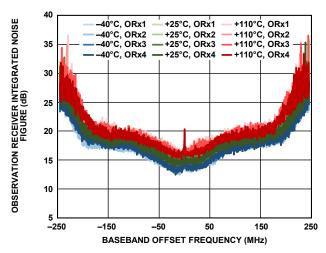

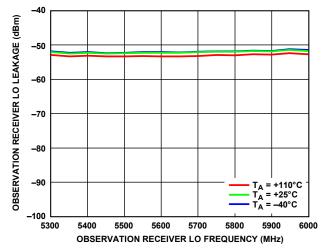

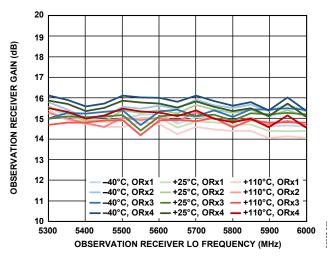

デバイス構成プロファイル:特に指定のない限り、レシーバー = 200MHz 帯域幅、I/Q レート = 245.76MHz、トランスミッタ = 200MHz 大信号帯域幅 + 450MHz シンセシス帯域幅、I/Q レート = 491.52MHz、オブザベーション・レシーバー(ORx) = 450MHz 帯域幅、I/Q レート = 491.52MHz、デバイス・クロック = 245.76MHz。75MHz での特性評価は以下のプロファイルによります:レシーバー = 62.5MHz 帯域幅、I/Q レート = 76.8MHz、トランスミッタ = 62.5MHz 大信号帯域幅 + 141MHz シンセシス帯域幅、I/Q レート = 153.6MHz、オブザベーション・レシーバー = 141MHz 帯域幅、I/Q レート = 153.6MHz、デバイス・クロック = 153.6MHz。

注:信号が基本帯域幅の外側にある場合は、直線性、イメージ除去、平坦性などの性能が低下することがあります。

#### トランスミッタとレシーバー

表 1.

| パラメータ                                                                       | 記号  | Min | Тур        | Max  | 単位      | テスト条件/コメント                                         |

|-----------------------------------------------------------------------------|-----|-----|------------|------|---------|----------------------------------------------------|

| TRANSMITTERS                                                                | Tx  |     |            |      |         |                                                    |

| Center Frequency                                                            |     | 75  |            | 6000 | MHz     |                                                    |

| Tx Synthesis Bandwidth                                                      |     |     |            | 450  | MHz     |                                                    |

| Tx Large Signal Bandwidth                                                   |     |     |            | 200  | MHz     | ゼロ中間周波数(IF)モード                                     |

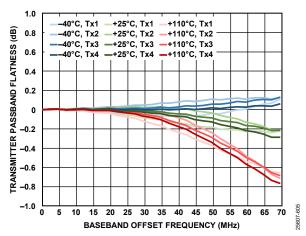

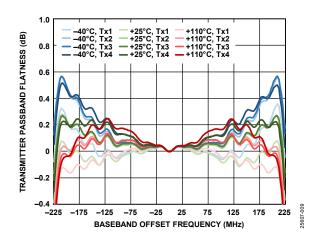

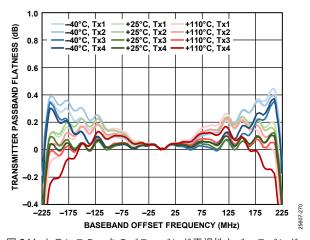

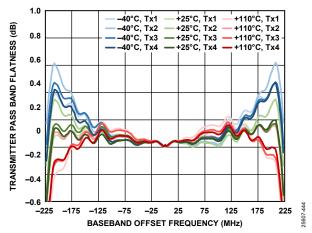

| Peak-to-Peak Gain Deviation                                                 |     |     | 1.0        |      | dB      | 帯域幅: 450MHz、プログラマブル有限インパルス<br>応答(FIR) フィルタによる補償を含む |

|                                                                             |     |     | 0.1        |      | dB      | 任意の 20MHz 帯域幅スパン、プログラマブル<br>FIR フィルタ(pFIR)による補償を含む |

| Deviation from Linear Phase                                                 |     |     | 1          |      | Degrees | 帯域幅:450MHz                                         |

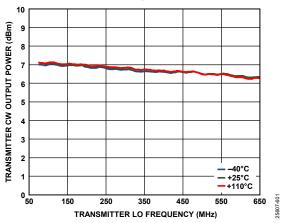

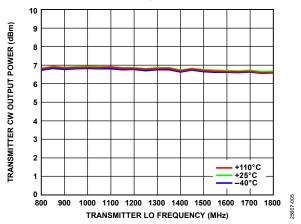

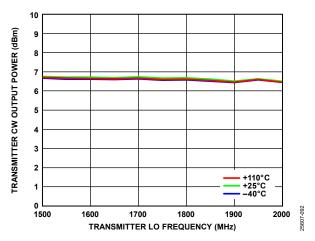

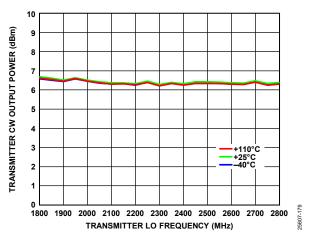

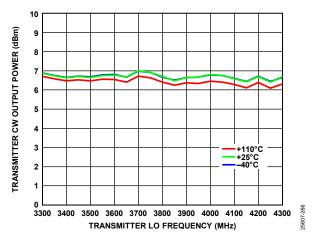

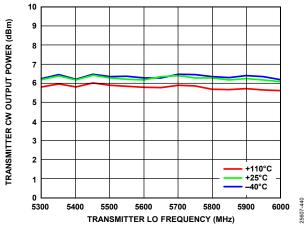

| Maximum Output Power                                                        |     |     |            |      |         | 0dBFS、1MHz 信号入力、50Ω 負荷、0dB トランスミッタ減衰               |

| 75 MHz                                                                      |     |     | 7.0        |      | dBm     |                                                    |

| 800 MHz                                                                     |     |     | 6.7        |      | dBm     |                                                    |

| 1800 MHz                                                                    |     |     | 6.6        |      | dBm     |                                                    |

| 2600 MHz                                                                    |     |     | 6.3        |      | dBm     |                                                    |

| 3800 MHz                                                                    |     |     | 6.4        |      | dBm     |                                                    |

| 4800 MHz                                                                    |     |     | 6.1        |      | dBm     |                                                    |

| 5700 MHz                                                                    |     |     | 6.4        |      | dBm     |                                                    |

| Power Control Range                                                         |     |     | 32         |      | dB      |                                                    |

| Power Control Resolution                                                    |     |     | 0.05       |      | dB      |                                                    |

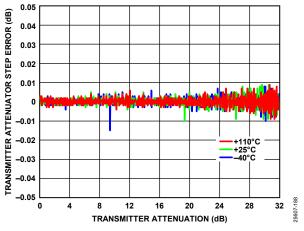

| Attenuation Accuracy                                                        |     |     |            |      |         |                                                    |

| Integral Nonlinearity (Gain)                                                | INL |     | 0.1        |      | dB      | 任意の 4dB ステップにおける全パワー・コントロール範囲で有効                   |

| Differential Nonlinearity (Gain)                                            | DNL |     | $\pm 0.04$ |      | dB      | 単調増加                                               |

| Output Power Temperature Slope                                              |     |     | -4.5       |      | mdB/°C  | 全パワー・コントロール範囲で有効                                   |

| LO Delay Temperature Slope                                                  |     |     | 1.05       |      | ps/°C   | 全パワー・コントロール範囲で有効                                   |

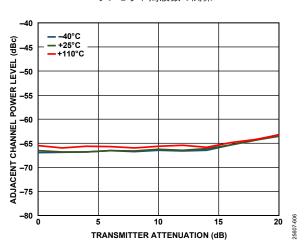

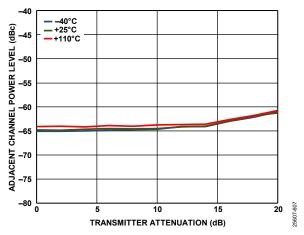

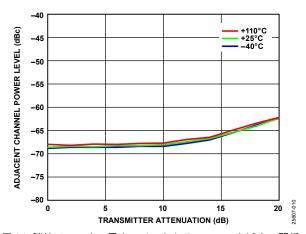

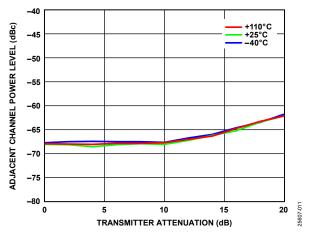

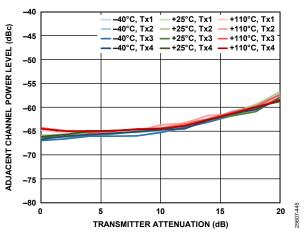

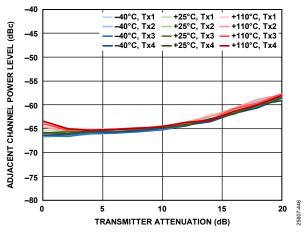

| Adjacent Channel Leakage Power<br>Ratio (ACLR) Long Term<br>Evolution (LTE) |     |     |            |      |         | −12dBFS での 20MHz LTE                               |

| 75 MHz                                                                      |     |     | -64        |      | dB      |                                                    |

| 800 MHz                                                                     |     |     | -68        |      | dB      |                                                    |

| 1800 MHz                                                                    |     |     | -67        |      | dB      |                                                    |

| 2600 MHz                                                                    |     |     | -66        |      | dB      |                                                    |

| 3800 MHz                                                                    |     |     | -65        |      | dB      |                                                    |

| 4800 MHz                                                                    |     |     | -65        |      | dB      |                                                    |

| 5700 MHz                                                                    |     |     | -65        |      | dB      |                                                    |

Rev. 0 - 4/133 -

| パラメータ                                              | 記号               | Min    | Тур    | Max  | 単位        | テスト条件/コメント                                            |

|----------------------------------------------------|------------------|--------|--------|------|-----------|-------------------------------------------------------|

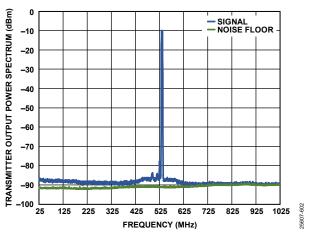

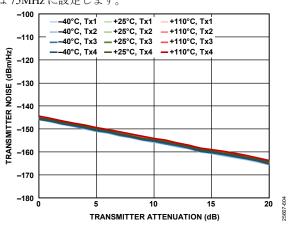

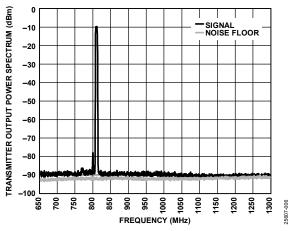

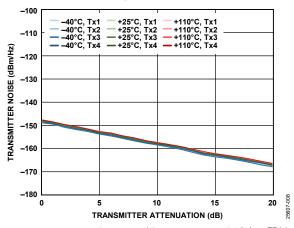

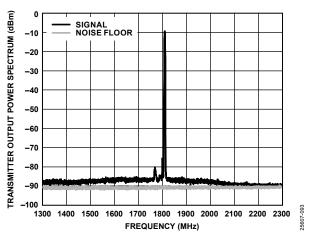

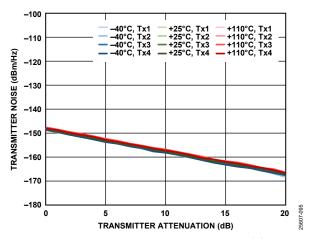

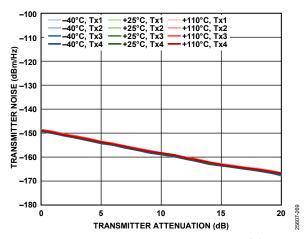

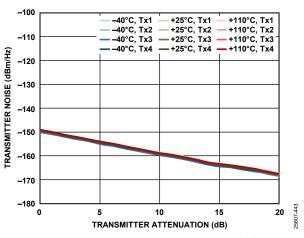

| In Band Noise Floor                                | ,,,,             | 141111 | -154.5 | WIGA | dBFS/Hz   | 0dB 減衰。0dB~20dB の減衰設定で 1dB の減衰ご                       |

| In Band Poise Floor                                |                  |        | 134.3  |      | dDI 5/112 | とに帯域内ノイズが1dB低下                                        |

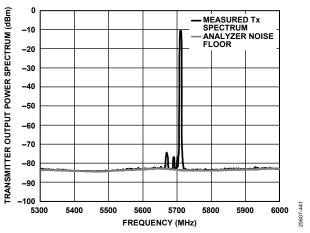

| Interpolation Images                               |                  |        | -76    |      | dBc       | CT-IIII WATER TO LEAT                                 |

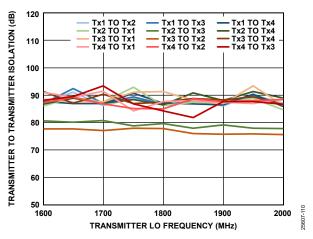

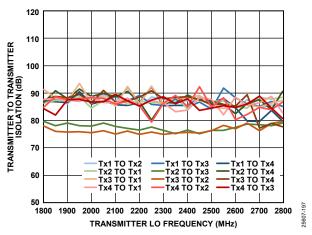

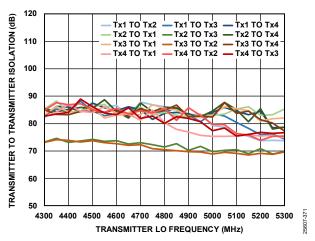

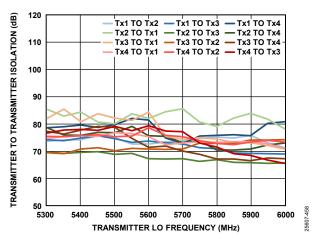

| Tx to Tx Isolation: All Tx Output                  |                  |        | 70     |      | abe       |                                                       |

| Effects on All Other Tx Outputs                    |                  |        |        |      |           |                                                       |

| 800 MHz                                            |                  |        | 78     |      | dB        |                                                       |

| 1800MHz                                            |                  |        | 77     |      | dB        |                                                       |

| 2600 MHz                                           |                  |        | 77     |      | dB        |                                                       |

| 3800 MHz                                           |                  |        | 71     |      | dB        |                                                       |

| 4800 MHz                                           |                  |        | 70     |      | dB        |                                                       |

| 5700 MHz                                           |                  |        | 65     |      | dB        |                                                       |

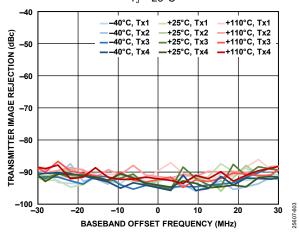

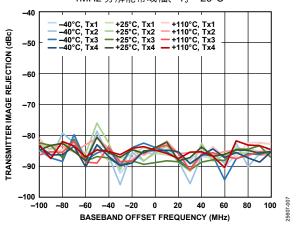

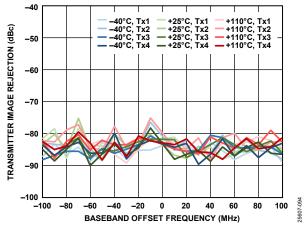

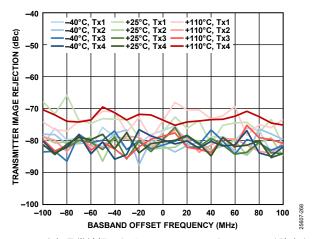

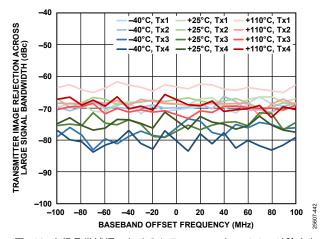

| Image Rejection                                    |                  |        |        |      |           |                                                       |

| Within 200 MHz Large Signal<br>Bandwidth           |                  |        |        |      |           | 減衰が 20dB になるまで QEC アクティブ、連続波<br>トーンで大信号帯域幅をスイープ       |

| 75 MHz                                             |                  |        | 80     |      | dB        |                                                       |

| 800 MHz                                            |                  |        | 76     |      | dB        |                                                       |

| 1800 MHz                                           |                  |        | 75     |      | dB        |                                                       |

| 2600 MHz                                           |                  |        | 73     |      | dB        |                                                       |

| 3800 MHz                                           |                  |        | 65     |      | dB        |                                                       |

| 4800 MHz                                           |                  |        | 64     |      | dB        |                                                       |

| 5700 MHz                                           |                  |        | 61     |      | dB        |                                                       |

| Beyond Large Signal Bandwidth                      |                  |        |        |      |           | 歪み電力密度が必要電力密度より 25dB 低いと仮<br>定                        |

| 800 MHz                                            |                  |        | 40     |      | dB        |                                                       |

| 1800 MHz                                           |                  |        | 38     |      | dB        |                                                       |

| 2600 MHz                                           |                  |        | 34     |      | dB        |                                                       |

| 3800 MHz                                           |                  |        | 37     |      | dB        |                                                       |

| 4800 MHz                                           |                  |        | 37     |      | dB        |                                                       |

| 5700 MHz                                           |                  |        | 37     |      | dB        |                                                       |

| Output Impedance                                   | Z <sub>OUT</sub> |        | 50     |      | Ω         | 差動 – 公称値                                              |

| Maximum Output Load Voltage<br>Standing Wave Ratio | VSWR             |        |        | 3    |           | 適切なキャリブレーションを確保するための最大<br>値                           |

| Output Return Loss                                 |                  |        | 10     |      | dB        |                                                       |

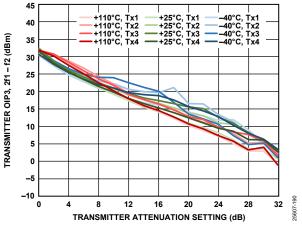

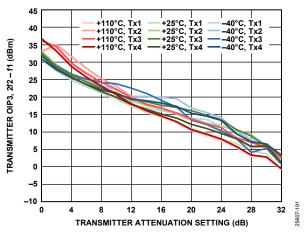

| Output Third-Order Intercept Point                 | OIP3             |        |        |      |           | 0dB トランスミッタ減衰                                         |

| 75 MHz                                             |                  |        | 30     |      | dBm       |                                                       |

| 800 MHz                                            |                  |        | 29     |      | dBm       |                                                       |

| 1800 MHz                                           |                  |        | 29     |      | dBm       |                                                       |

| 2600 MHz                                           |                  |        | 28     |      | dBm       |                                                       |

| 3800 MHz                                           |                  |        | 26.5   |      | dBm       |                                                       |

| 4800 MHz                                           |                  |        | 29     |      | dBm       |                                                       |

| 5700 MHz                                           |                  |        | 27     |      | dBm       |                                                       |

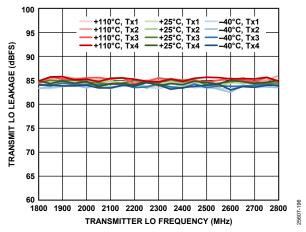

| Carrier Leakage                                    |                  |        |        |      |           | LO リーク補償アクティブ、0dB トランスミッタ<br>減衰、減衰 1 デシベルごとに 1 デシベル変化 |

| Carrier Offset from LO                             |                  |        |        |      |           |                                                       |

| 75 MHz LO                                          |                  |        | -84    |      | dBFS/MHz  |                                                       |

| 800 MHz LO                                         |                  |        | -84    |      | dBFS/MHz  |                                                       |

| 1800 MHz LO                                        |                  |        | -84    |      | dBFS/MHz  |                                                       |

| 2600 MHz LO                                        |                  |        | -83    |      | dBFS/MHz  |                                                       |

| 3800 MHz LO                                        |                  |        | -84    |      | dBFS/MHz  |                                                       |

| 4800 MHz LO                                        |                  |        | -84    |      | dBFS/MHz  |                                                       |

| 5700 MHz LO                                        |                  |        | -83    |      | dBFS/MHz  |                                                       |

Rev. 0 – 5/133 –

| パラメータ                                                   | 記号                | Min | Тур   | Max  | 単位       | テスト条件/コメント                                                 |

|---------------------------------------------------------|-------------------|-----|-------|------|----------|------------------------------------------------------------|

| Carrier on the LO                                       |                   |     | -71   |      | dBFS/MHz | LTE 20MHz 信号を使って測定                                         |

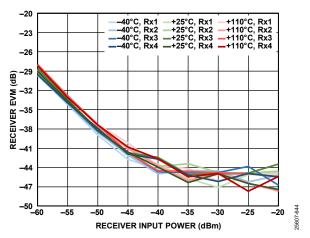

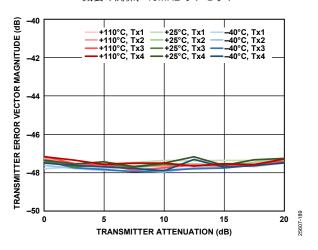

| Error Vector Magnitude                                  | EVM               |     |       |      |          | 狭帯域ノイズに最適化された PLL、LTE 20MHz                                |

|                                                         |                   |     |       |      |          | 信号を使って測定                                                   |

| 75 MHz LO                                               |                   |     | 0.25  |      | %        | PLL 帯域幅: 50kHz                                             |

| 800 MHz LO                                              |                   |     | 0.38  |      | %        | PLL 帯域幅: 50kHz                                             |

| 1800 MHz LO                                             |                   |     | 0.60  |      | %        | PLL 帯域幅:50kHz                                              |

| 2600 MHz LO                                             |                   |     | 0.44  |      | %        | PLL 帯域幅: 500kHz                                            |

| 3800 MHz LO                                             |                   |     | 0.53  |      | %        | PLL 帯域幅:200kHz                                             |

| 4800 MHz LO                                             |                   |     | 0.63  |      | %        | PLL 帯域幅:400kHz                                             |

| 5700 MHz LO                                             |                   |     | 0.84  |      | %        | PLL 帯域幅:500kHz                                             |

| Transmitter Time Division Duplex                        | TDD               |     |       |      |          |                                                            |

| Time from SPI_EN Going High to Change in Tx Attenuation | $t_{SCH}$         |     | 12    |      | ns       |                                                            |

| Time Between Consecutive<br>Microattenuation Steps      | t <sub>ACH</sub>  |     | 20    |      | ns       | 大きな減衰変化を一連の小さい減衰変化に分割可<br>能                                |

| Attenuation Overshoot During<br>Transition              |                   |     | 0.1   |      | dB       |                                                            |

| Change in Attenuation per<br>Microstep                  |                   |     | 0.1   |      | dB       |                                                            |

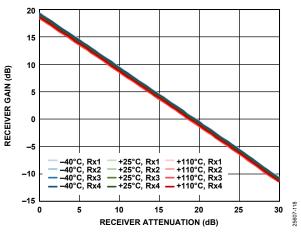

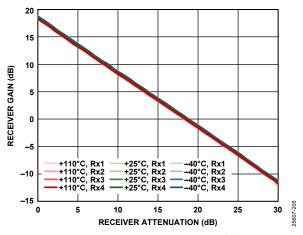

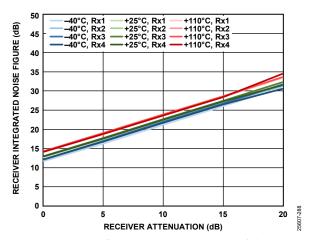

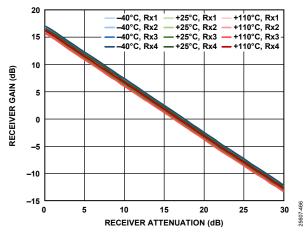

| RECEIVERS                                               | Rx                |     |       |      |          |                                                            |

| Center Frequency                                        |                   | 75  |       | 6000 | MHz      |                                                            |

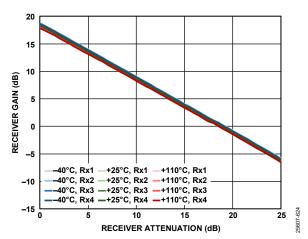

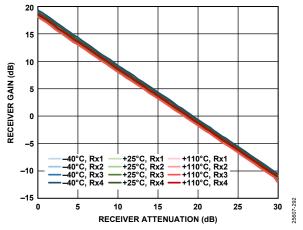

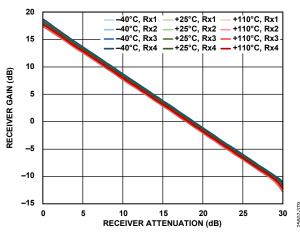

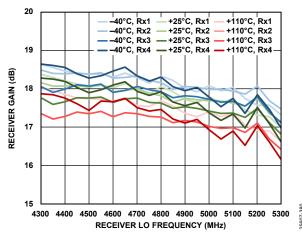

| Gain Range                                              |                   |     | 30    |      | dB       |                                                            |

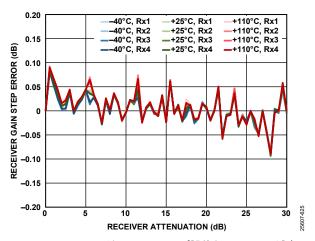

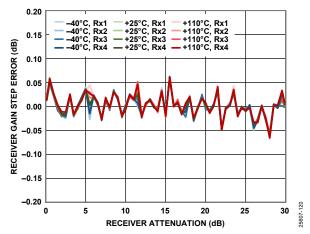

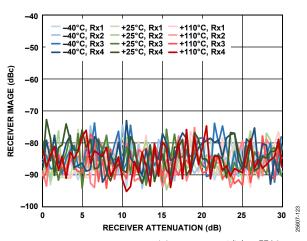

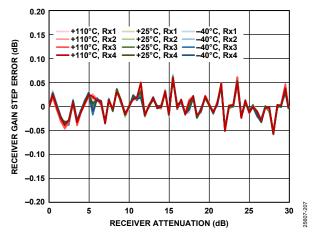

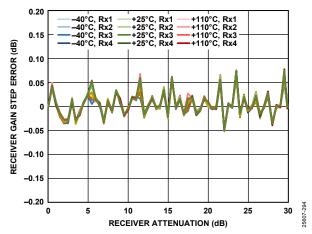

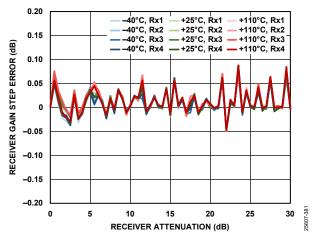

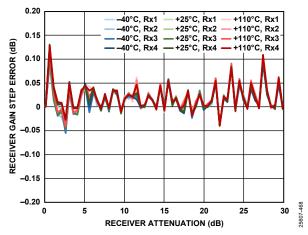

| Attenuation Accuracy                                    |                   |     |       |      |          |                                                            |

| Analog Gain Step                                        |                   |     | 0.5   |      | dB       | 0dB~6dBの減衰ステップ                                             |

|                                                         |                   |     | 1     |      | dB       | 6dB~30dBの減衰ステップ                                            |

| Residual Gain Step Error                                |                   |     | 0.1   |      | dB       |                                                            |

| Gain Temperature Slope                                  |                   |     | -6.4  |      | mdB/°C   |                                                            |

| Internal LO Delay Temperature Slope                     |                   |     | 1.0   |      | ps/°C    |                                                            |

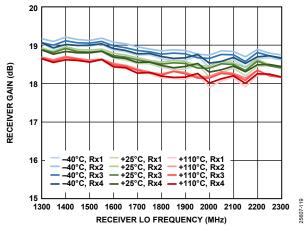

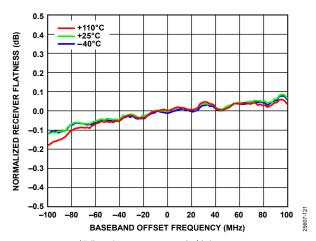

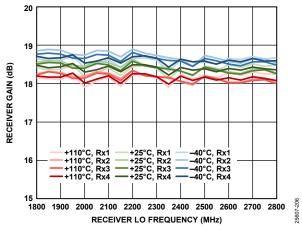

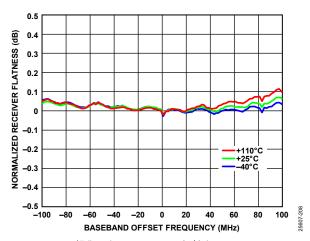

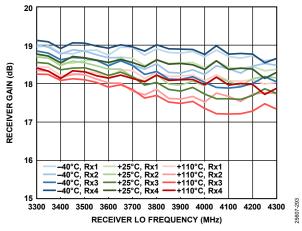

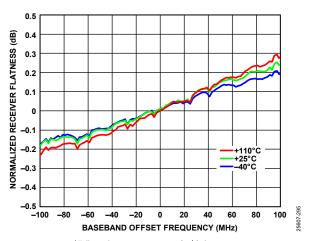

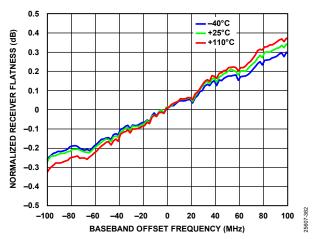

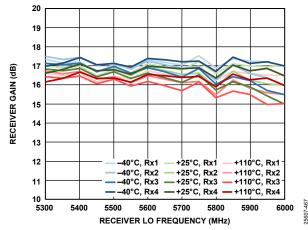

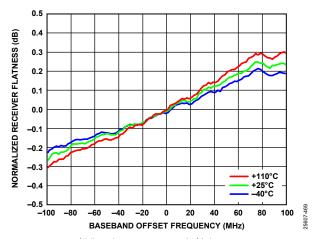

| Frequency Response                                      |                   |     |       |      | 45       | W. D                                                       |

| Peak-to-Peak Gain Deviation                             |                   |     | 1     |      | dB       | 帯域幅: 200MHz、プログラマブル FIR フィルタ<br>による補償を含む                   |

|                                                         |                   |     | 0.2   |      | dB       | 任意の 20MHz スパン、プログラマブル FIR フィルタによる補償を含む                     |

| Rx Bandwidth                                            |                   |     |       | 200  | MHz      | ゼロIFモード                                                    |

| Rx Alias Band Rejection                                 |                   | 80  |       |      | dB       | デジタル・フィルタによる                                               |

| Maximum Useable Input Level                             | P <sub>HIGH</sub> |     |       |      |          | この連続波信号レベルは、0dB チャンネル減衰で<br>デジタル出力に-2dBFS を生成する入力電力に相<br>当 |

| 75 MHz                                                  |                   |     | -11.7 |      | dBm      |                                                            |

| 800 MHz                                                 |                   |     | -12.4 |      | dBm      |                                                            |

| 1800 MHz                                                |                   |     | -12.7 |      | dBm      |                                                            |

| 2600 MHz                                                |                   |     | -11.9 |      | dBm      |                                                            |

| 3800 MHz                                                |                   |     | -11.0 |      | dBm      |                                                            |

| 4800 MHz                                                |                   |     | -12.0 |      | dBm      |                                                            |

| 5700 MHz                                                |                   |     | -11.1 |      | dBm      |                                                            |

| Maximum Source VSWR                                     |                   |     |       | 3    |          |                                                            |

| Input Impedance                                         | $Z_{\rm IN}$      |     | 100   |      | Ω        | 差動                                                         |

| Input Port/Return Loss                                  |                   |     | 10    |      | dB       | マッチングされていない差動ポートのリターン損                                     |

|                                                         |                   |     |       |      |          | 失                                                          |

Rev. 0 - 6/133 -

| パラメータ                                                                                | 記号                      | Min | Тур  | Max | 単位    | テスト条件/コメント                                                          |

|--------------------------------------------------------------------------------------|-------------------------|-----|------|-----|-------|---------------------------------------------------------------------|

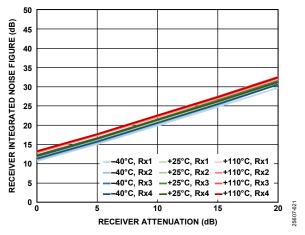

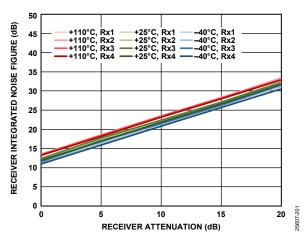

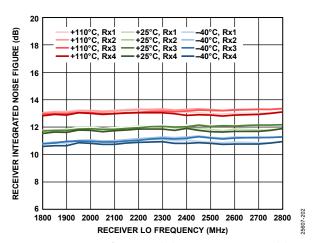

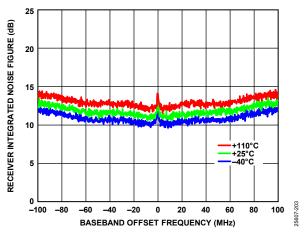

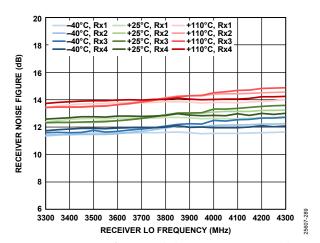

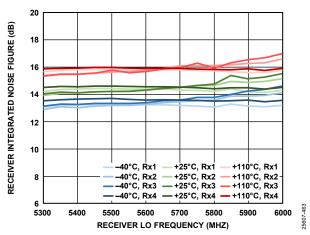

| Noise Figure                                                                         | NF                      |     |      |     |       | 0dB レシーバー減衰、シングルエンド入力で測<br>定、マッチング回路を含む                             |

| 75 MHz                                                                               |                         |     | 12   |     | dB    | 7-7-7-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1                             |

| 800 MHz                                                                              |                         |     | 11   |     | dB    |                                                                     |

| 1800 MHz                                                                             |                         |     | 11.5 |     | dB    |                                                                     |

| 2600 MHz                                                                             |                         |     | 11.9 |     | dB    |                                                                     |

| 3800 MHz                                                                             |                         |     | 12.8 |     | dB    |                                                                     |

| 4800 MHz                                                                             |                         |     | 13.3 |     | dB    |                                                                     |

| 5700 MHz                                                                             |                         |     | 14.5 |     | dB    |                                                                     |

| Noise Figure Ripple                                                                  |                         |     | 1.5  |     | dB    | バンド・エッジでの値                                                          |

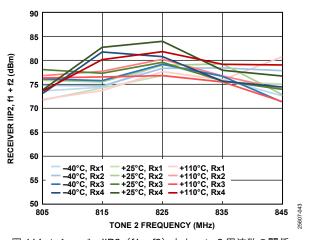

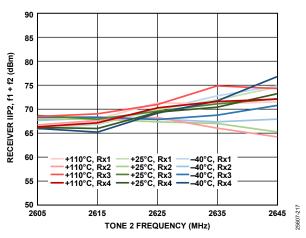

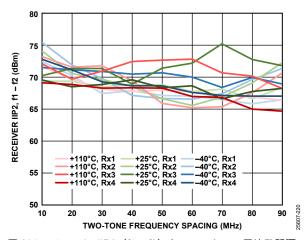

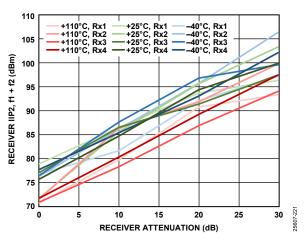

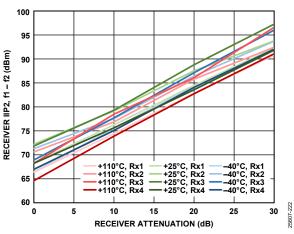

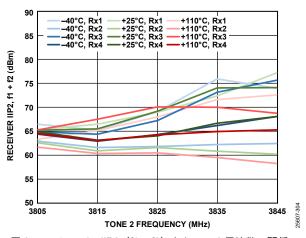

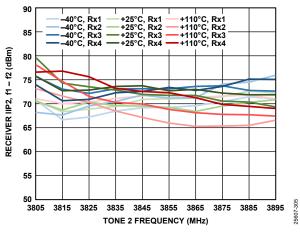

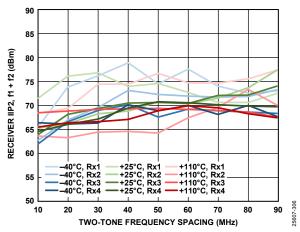

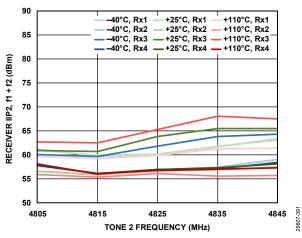

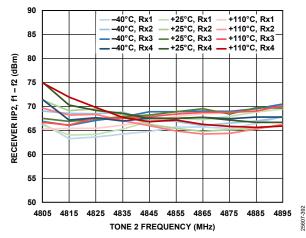

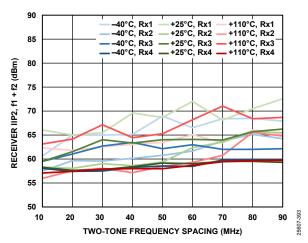

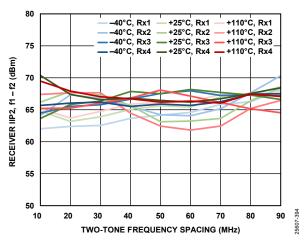

| Second-Order Input Intermodulation<br>Intercept Point                                | IIP2                    |     | 1.0  |     | uD    | 0dB 減衰、複素数                                                          |

| 75 MHz                                                                               |                         |     | 70   |     | dBm   |                                                                     |

| 800 MHz                                                                              |                         |     | 65   |     | dBm   |                                                                     |

|                                                                                      |                         |     |      |     |       |                                                                     |

| 1800 MHz                                                                             |                         |     | 65   |     | dBm   |                                                                     |

| 2600 MHz                                                                             |                         |     | 65   |     | dBm   |                                                                     |

| 3800 MHz                                                                             |                         |     | 62   |     | dBm   |                                                                     |

| 4800 MHz                                                                             |                         |     | 62   |     | dBm   |                                                                     |

| 5700 MHz                                                                             |                         |     | 58   |     | dBm   | 200                                                                 |

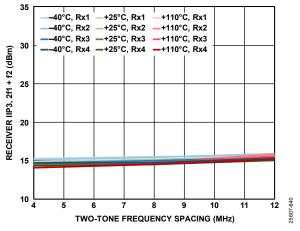

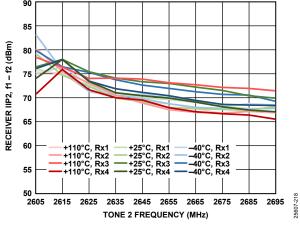

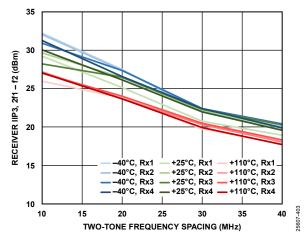

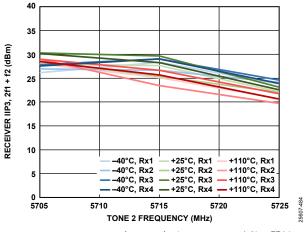

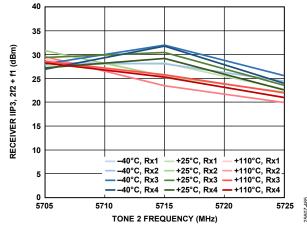

| Wideband Third-Order Input<br>Intermodulation Intercept Point,<br>Difference Product | IIP3 <sub>WB_DIFF</sub> |     |      |     |       | バンド・エッジ付近のツー・トーン、テスト条件: P <sub>HIGH</sub> – 9dB/tone                |

| 75 MHz                                                                               |                         |     | 14   |     | dBm   |                                                                     |

| 800 MHz                                                                              |                         |     | 15   |     | dBm   |                                                                     |

| 1800 MHz                                                                             |                         |     | 17   |     | dBm   |                                                                     |

| 2600 MHz                                                                             |                         |     | 17   |     | dBm   |                                                                     |

| 3800 MHz                                                                             |                         |     | 17   |     | dBm   |                                                                     |

| 4800 MHz                                                                             |                         |     | 17   |     | dBm   |                                                                     |

| 5700 MHz                                                                             |                         |     | 18   |     | dBm   |                                                                     |

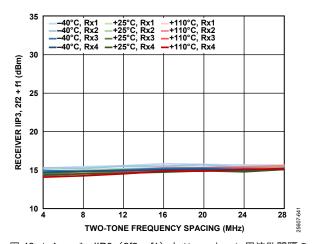

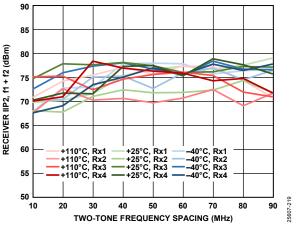

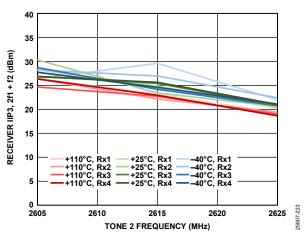

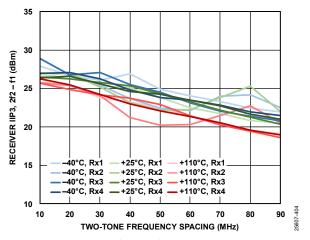

| Midband Third-Order Input<br>Intermodulation Intercept Point,<br>Difference Product  | $IIP3_{MB\_DIFF}$       |     |      |     |       | バンド中央付近のツー・トーン。テスト条件:<br>P <sub>HIGH</sub> – 9dB/tone               |

| 75 MHz                                                                               |                         |     | 20   |     | dBm   |                                                                     |

| 800 MHz                                                                              |                         |     | 18   |     | dBm   |                                                                     |

| 1800 MHz                                                                             |                         |     | 22   |     | dBm   |                                                                     |

| 2600 MHz                                                                             |                         |     | 21   |     | dBm   |                                                                     |

| 3800 MHz                                                                             |                         |     | 22   |     | dBm   |                                                                     |

| 4800 MHz                                                                             |                         |     | 22   |     | dBm   |                                                                     |

| 5700 MHz                                                                             |                         |     | 20   |     | dBm   |                                                                     |

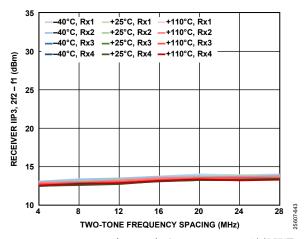

| Wideband Third-Order Input<br>Intermodulation Intercept Point, Sum<br>Product        | IIP3 <sub>WB_SUM</sub>  |     |      |     |       | LO から約「帯域幅÷6」オフセットさせた位置でのツー・トーン。テスト条件: P <sub>HIGH</sub> - 9dB/tone |

| 75 MHz                                                                               |                         |     | 15   |     | dBm   |                                                                     |

| 800 MHz                                                                              |                         |     | 17   |     | dBm   |                                                                     |

| 1800 MHz                                                                             |                         |     | 17   |     | dBm   |                                                                     |

| 2600 MHz                                                                             |                         |     | 20   |     | dBm   |                                                                     |

| 3800 MHz                                                                             |                         |     | 23   |     | dBm   |                                                                     |

| 4800 MHz                                                                             |                         |     | 23   |     | dBm   |                                                                     |

| 5700 MHz                                                                             |                         |     | 20   |     | dBm   |                                                                     |

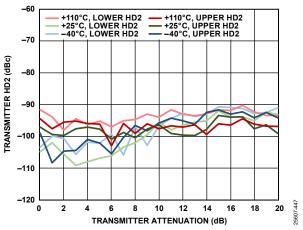

| Second-Order Harmonic Distortion                                                     |                         |     | 20   |     | uDiii |                                                                     |

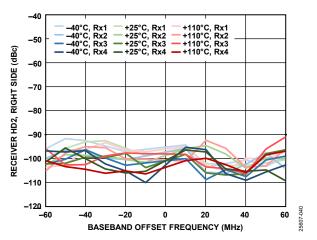

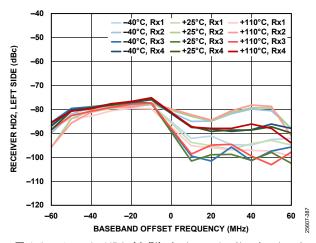

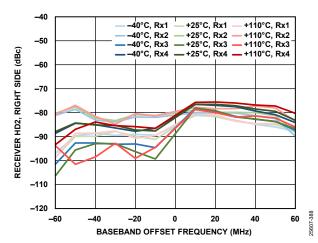

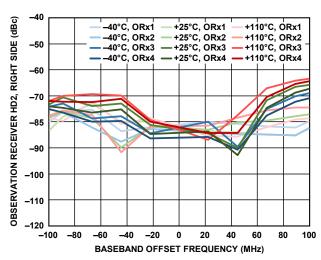

| Maximum Input                                                                        | HD2 <sub>MAX</sub>      |     | -72  |     | dBc   | P <sub>HIGH</sub> 連続波信号、高調波歪みトーンは LO の<br>100MHz 以内                 |

| Recommended Input                                                                    | HD2                     |     | -75  |     | dBc   | P <sub>HIGH</sub> - 3dB連続波信号、高調波歪みトーンは LO の 100MHz 以内               |

Rev. 0 - 7/133 -

| パラメータ                                                                | 記号                 | Min | Тур | Max  | 単位  | テスト条件/コメント                                                  |

|----------------------------------------------------------------------|--------------------|-----|-----|------|-----|-------------------------------------------------------------|

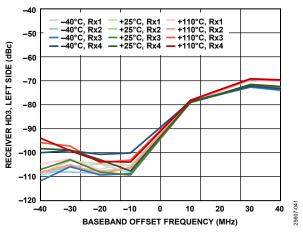

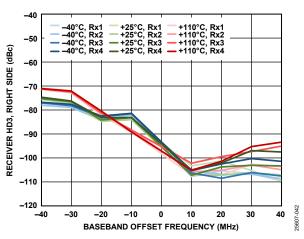

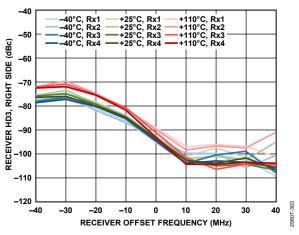

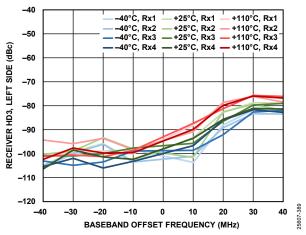

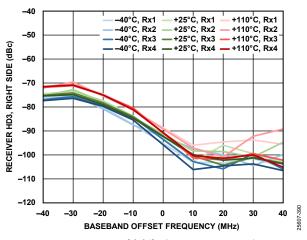

| Third-Order Harmonic Distortion                                      |                    |     |     |      |     |                                                             |

| Maximum Input                                                        | HD3 <sub>MAX</sub> |     | -66 |      | dBc | P <sub>HIGH</sub> 連続波信号、高調波歪みトーンは LO の<br>100MHz 以内         |

| Recommended Input                                                    | HD3                |     | -72 |      | dBc | P <sub>HIGH</sub> - 3dB 連続波信号、高調波歪みトーンは LO<br>の 100MHz 以内   |

| Fourth-Order Harmonic Distortion                                     |                    |     |     |      |     |                                                             |

| Maximum Input                                                        | HD4 <sub>MAX</sub> |     | -90 |      | dBc | P <sub>HIGH</sub> 連続波信号、高調波歪みトーンは LO の<br>100MHz 以内         |

| Recommended Input                                                    | HD4                |     | -90 |      | dBc | P <sub>HIGH</sub> - 3dB 連続波信号、高調波歪みトーンは LO<br>の 100MHz 以内   |

| Fifth-Order Harmonic Distortion                                      |                    |     |     |      |     |                                                             |

| Maximum Input                                                        | HD5 <sub>MAX</sub> |     | -87 |      | dBc | P <sub>HIGH</sub> 連続波信号、高調波歪みトーンは LO の 100MHz 以内            |

| Recommended Input                                                    | HD5                |     | -90 |      | dBc | P <sub>HIGH</sub> - 3dB 連続波信号、高調波歪みトーンは LO<br>の 100MHz 以内   |

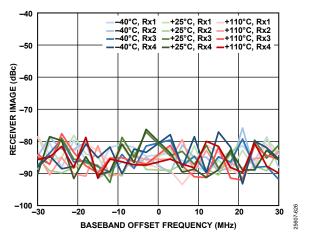

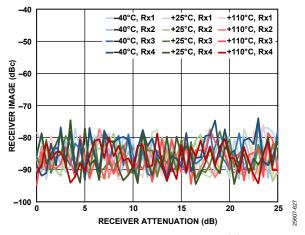

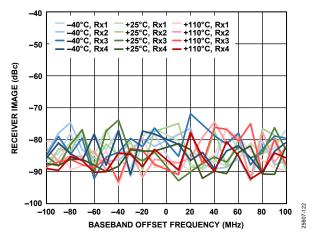

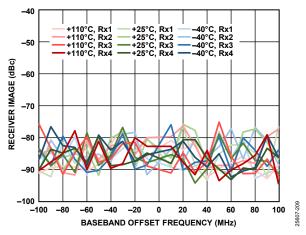

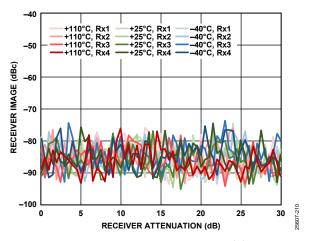

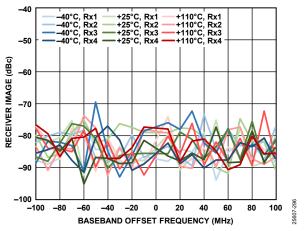

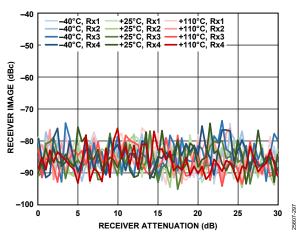

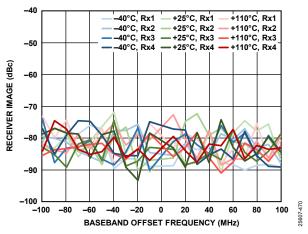

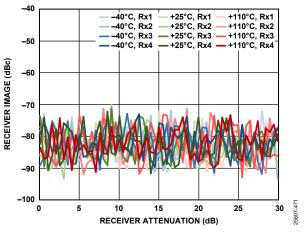

| Image Rejection                                                      |                    |     | 75  |      | dB  | QEC:アクティブ、200MHzのレシーバー帯域幅<br>内                              |

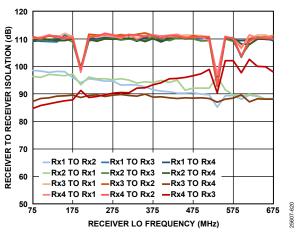

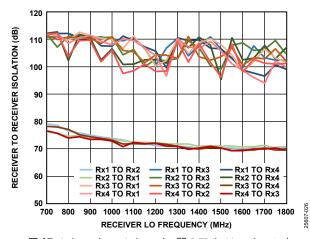

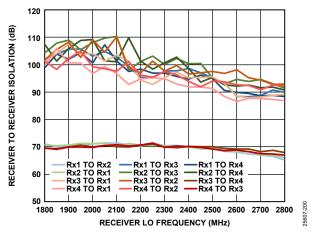

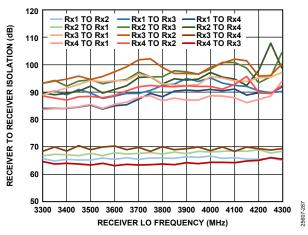

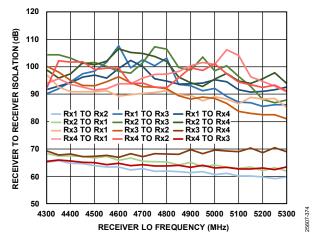

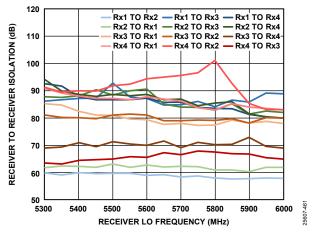

| Rx to Rx Signal Isolation                                            |                    |     |     |      |     |                                                             |

| 75 MHz                                                               |                    |     | 80  |      | dB  |                                                             |

| 800 MHz                                                              |                    |     | 75  |      | dB  |                                                             |

| 1800 MHz                                                             |                    |     | 70  |      | dB  |                                                             |

| 2600 MHz                                                             |                    |     | 70  |      | dB  |                                                             |

| 3800 MHz                                                             |                    |     | 65  |      | dB  |                                                             |

| 4800 MHz                                                             |                    |     | 62  |      | dB  |                                                             |

| 5700 MHz                                                             |                    |     | 60  |      | dB  |                                                             |

| Rx Band Spurs Referenced to RF Input at Maximum Gain                 |                    |     | -95 |      | dBm | このレベルのスプリアスはレシーバー帯域幅<br>10MHzごとに1つ以下。リファレンス・クロック<br>の高調波を除く |

| Spurious-Free Dynamic Range                                          | SFDR               |     | 81  |      | dBc | ±20MHz 帯域内の任意の位置に P <sub>HIGH</sub> 連続波信<br>号、高調波歪み積を除く     |

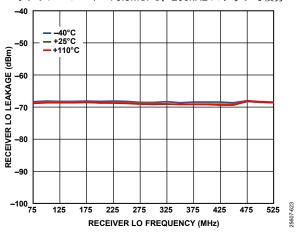

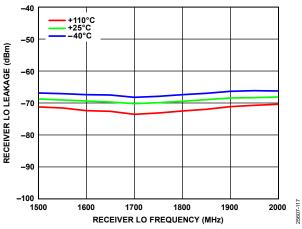

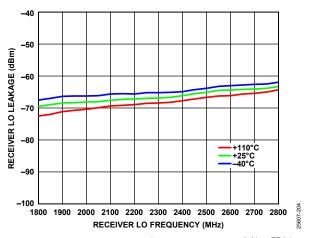

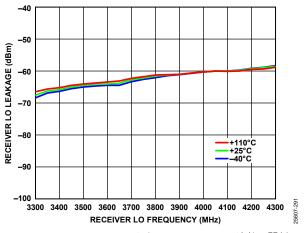

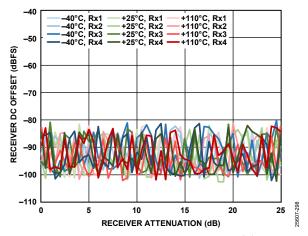

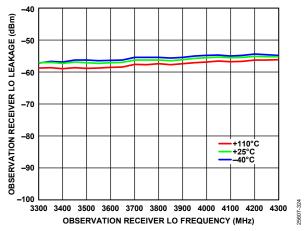

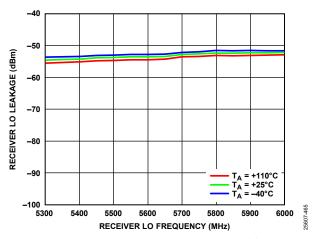

| Rx Input LO Leakage at Maximum Gain                                  |                    |     |     |      |     | 最初の12 デシベルの減衰では、1 デシベルの減衰<br>ごとにリークが1 デシベル減少                |

| 75 MHz                                                               |                    |     | -68 |      | dBm |                                                             |

| 800 MHz                                                              |                    |     | -68 |      | dBm |                                                             |

| 1800 MHz                                                             |                    |     | -68 |      | dBm |                                                             |

| 2600 MHz                                                             |                    |     | -65 |      | dBm |                                                             |

| 3800 MHz                                                             |                    |     | -65 |      | dBm |                                                             |

| 4800 MHz                                                             |                    |     | -58 |      | dBm |                                                             |

| 5700 MHz                                                             |                    |     | -54 |      | dBm |                                                             |

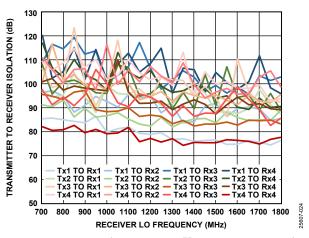

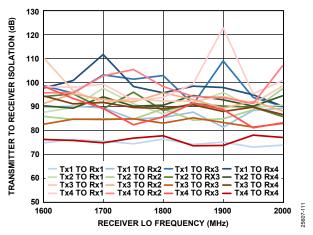

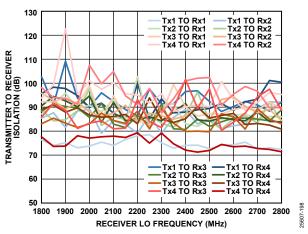

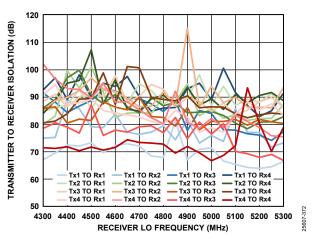

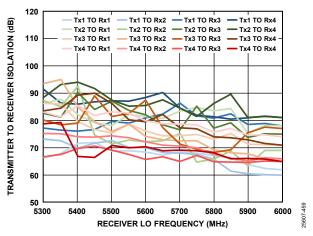

| Tx to Rx Signal Isolation: All Tx Output<br>Effects on all Rx Inputs |                    |     |     |      |     |                                                             |

| 75 MHz                                                               |                    |     | 80  |      | dB  |                                                             |

| 800 MHz                                                              |                    |     | 80  |      | dB  |                                                             |

| 1800 MHz                                                             |                    |     | 75  |      | dB  |                                                             |

| 2600 MHz                                                             |                    |     | 75  |      | dB  |                                                             |

| 3800 MHz                                                             |                    |     | 65  |      | dB  |                                                             |

| 4800 MHz                                                             |                    |     | 65  |      | dB  |                                                             |

| 5700 MHz                                                             |                    |     | 65  |      | dB  |                                                             |

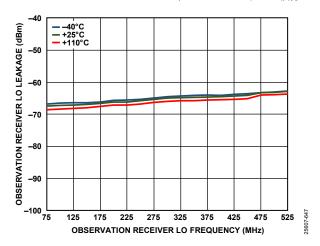

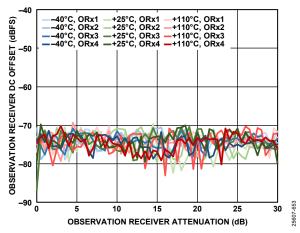

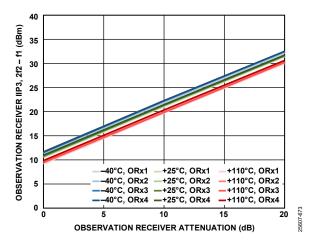

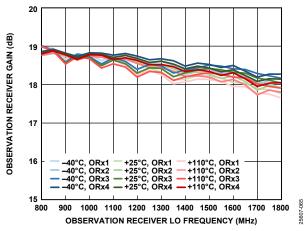

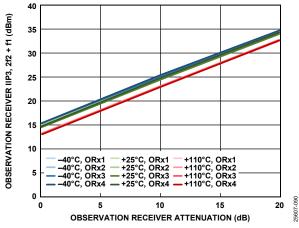

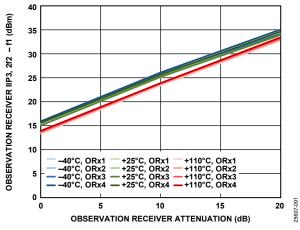

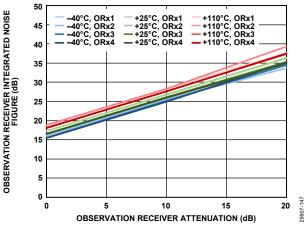

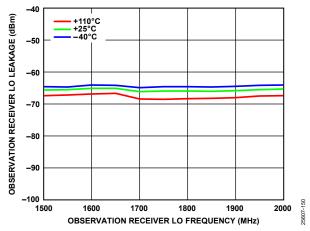

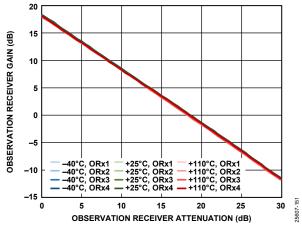

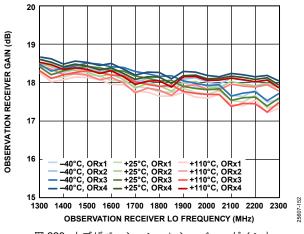

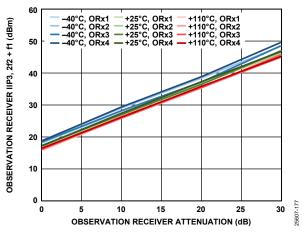

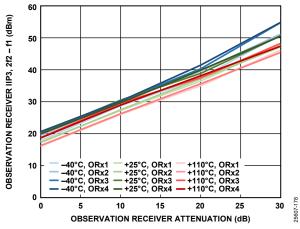

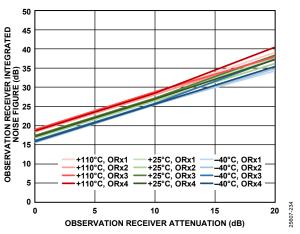

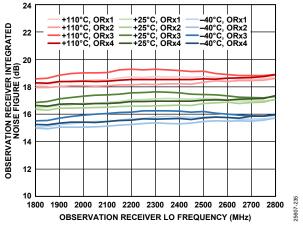

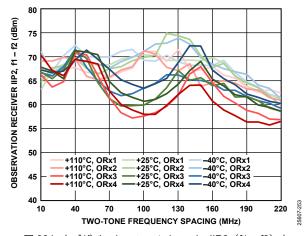

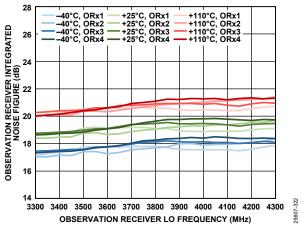

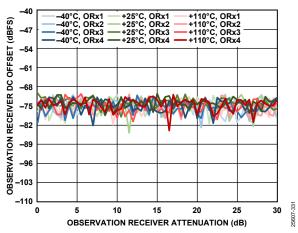

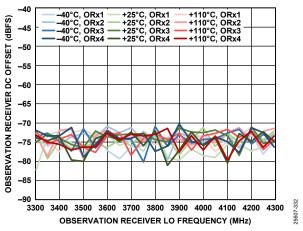

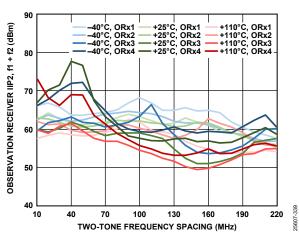

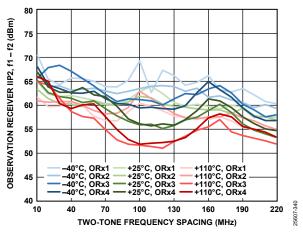

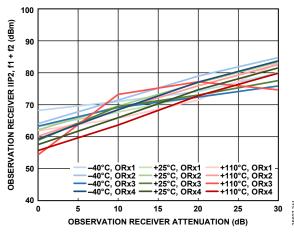

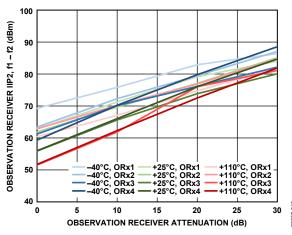

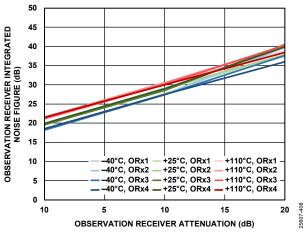

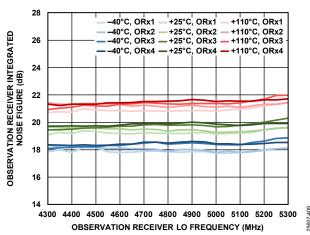

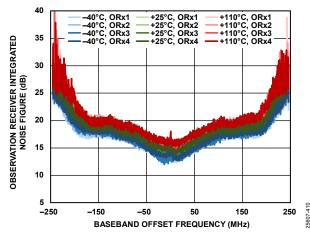

| BSERVATION RECEIVERS                                                 | ORx                |     |     | _    |     |                                                             |

| Center Frequency                                                     |                    | 75  |     | 6000 | MHz |                                                             |

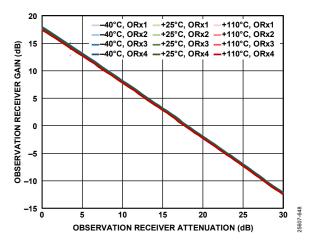

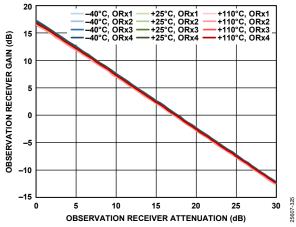

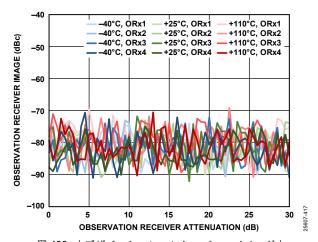

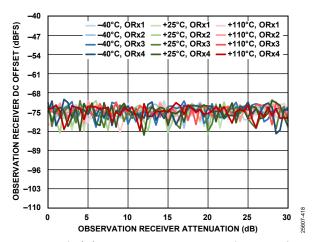

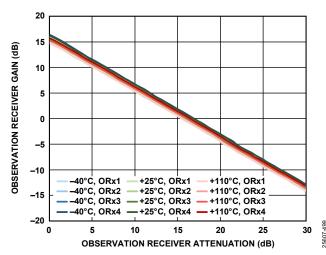

| Gain Range                                                           |                    |     | 30  |      | dB  |                                                             |

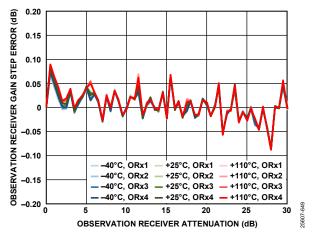

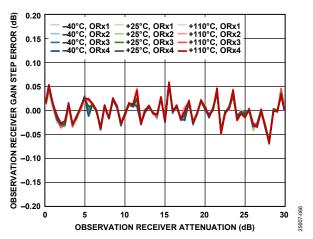

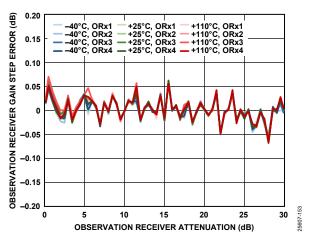

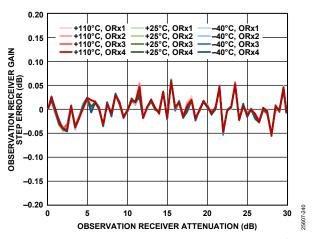

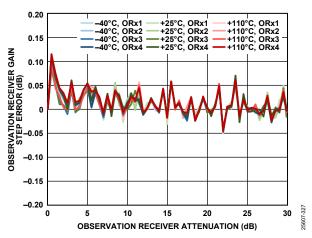

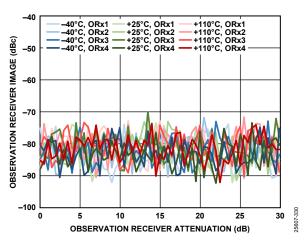

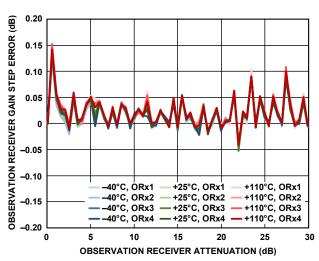

| Attenuation Accuracy                                                 |                    |     |     |      |     |                                                             |

| Analog Gain Step                                                     |                    |     | 0.5 |      | dB  | 0dB~6dBの減衰ステップ                                              |

|                                                                      |                    |     | 1   |      | dB  | 6dB~30dB の減衰ステップ                                            |

Rev. 0 - 8/133 -

| パラメータ                                                 | 記号                 | Min | Тур   | Max | 単位      | テスト条件/コメント                                                              |

|-------------------------------------------------------|--------------------|-----|-------|-----|---------|-------------------------------------------------------------------------|

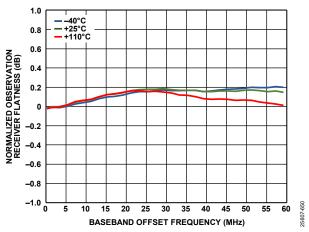

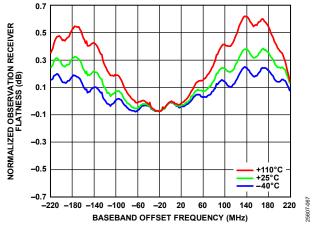

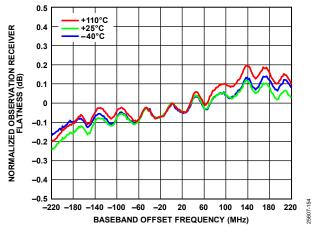

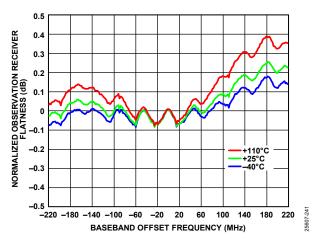

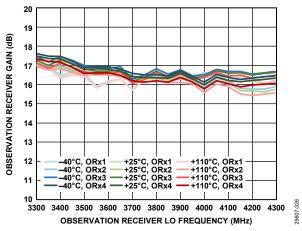

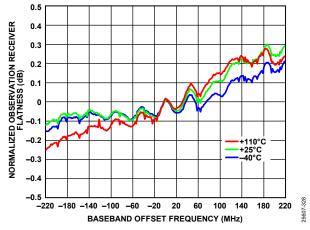

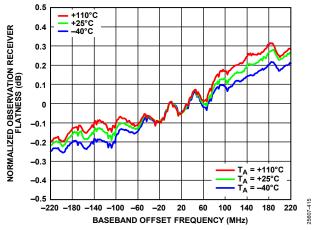

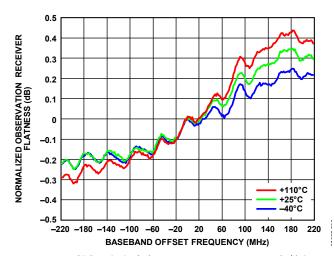

| Peak-to-Peak Gain Deviation                           |                    |     | 1     |     | dB      | RF 帯域幅: 450MHz、プログラマブル FIR フィルタによる補償                                    |

|                                                       |                    |     | 0.1   |     | dB      | 任意の 20MHz 帯域幅スパン、プログラマブル<br>FIR フィルタによる補償                               |

| Deviation from Linear Phase                           |                    |     | 1     |     | Degrees | RF 帯域幅: 450MHz                                                          |

| ORx Bandwidth                                         |                    |     |       | 450 | MHz     | Tet in section                                                          |

| ORx Alias Band Rejection                              |                    | 60  |       |     | dB      | デジタル・フィルタによる                                                            |

| Maximum Useable Input Level                           | P <sub>HIGH</sub>  |     |       |     |         | この連続波信号レベルは、0dB チャンネル減衰で<br>デジタル出力に-2dBFS を生成する入力電力に相<br>当              |

| 75 MHz                                                |                    |     | -11.4 |     | dBm     |                                                                         |

| 800 MHz                                               |                    |     | -12.7 |     | dBm     |                                                                         |

| 1800 MHz                                              |                    |     | -11.5 |     | dBm     |                                                                         |

| 2600 MHz                                              |                    |     | -10.6 |     | dBm     |                                                                         |

| 3800 MHz                                              |                    |     | -12.0 |     | dBm     |                                                                         |

| 4800 MHz                                              |                    |     | -11.3 |     | dBm     |                                                                         |

| 5700 MHz                                              |                    |     | -9.5  |     | dBm     |                                                                         |

| Input Impedance                                       | $Z_{\rm IN}$       |     | 100   |     | Ω       | 差動                                                                      |

| Input Source VSWR                                     |                    |     |       | 3   |         |                                                                         |

| Input Port Return Loss                                |                    |     | 10    |     | dB      | マッチングされていない差動ポートのリターン損<br>失                                             |

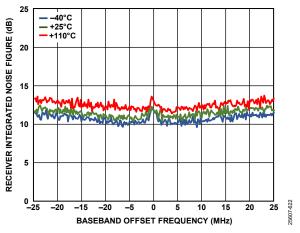

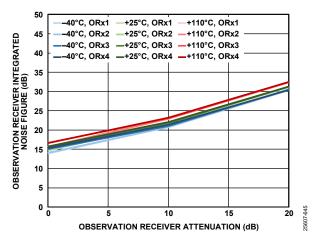

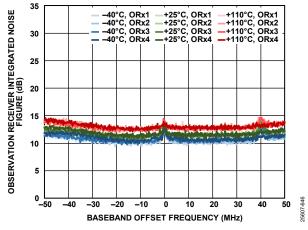

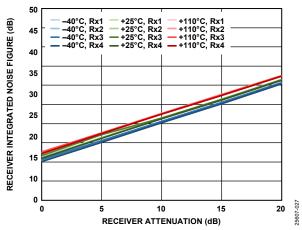

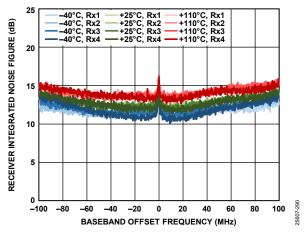

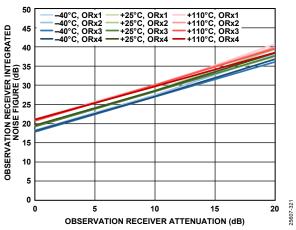

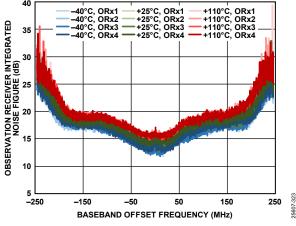

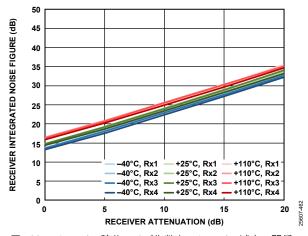

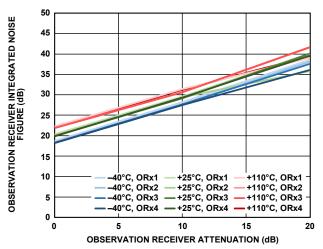

| Integrated Noise                                      |                    |     |       |     |         |                                                                         |

| 450 MHz Bandwidth                                     |                    |     | -58.5 |     | dBFS    | 500kHz~225MHz で積分した最大値でのサンプ<br>ル・レート、入力信号なし                             |

| 491.52 MHz Bandwidth (Nyquist)                        |                    |     | -57.5 |     | dBFS    | 500kHz~245.76MHz で積分した最大値でのサンフル・レート、入力信号なし                              |

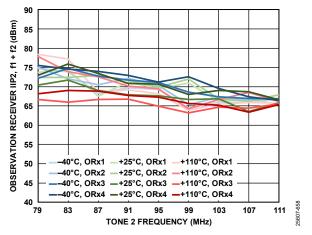

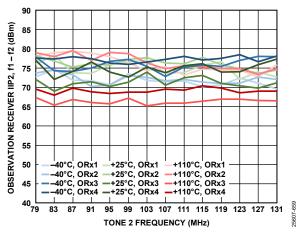

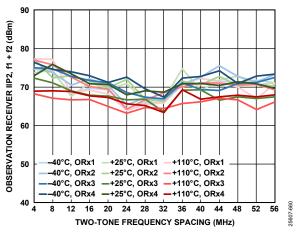

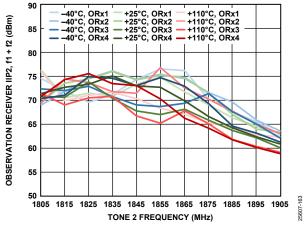

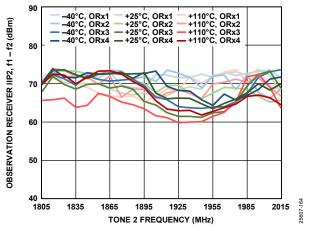

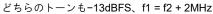

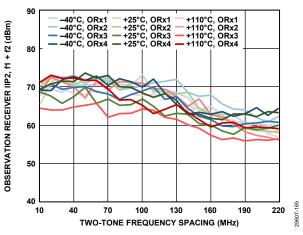

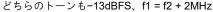

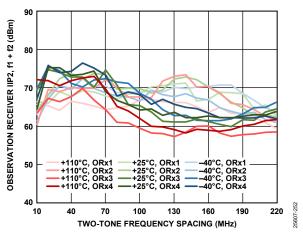

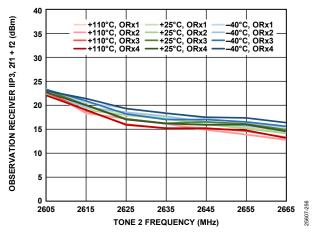

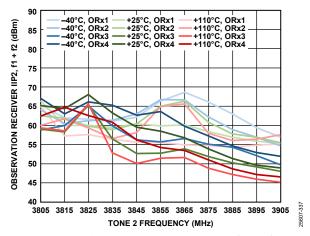

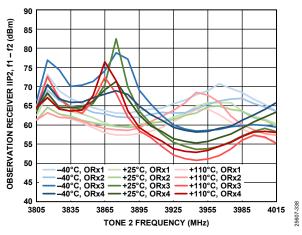

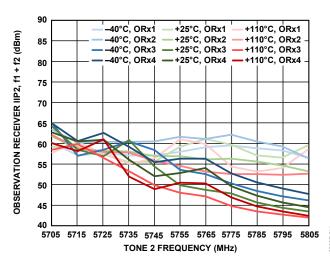

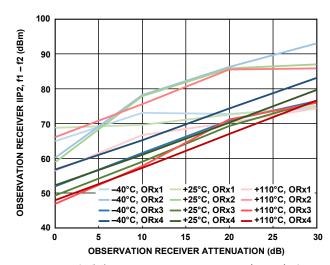

| Second-Order Input Intermodulation<br>Intercept Point | IIP2               |     |       |     |         | 最大オブザベーション・レシーバー・ゲイン。テスト条件: $P_{HIGH}$ – 11dB/tone                      |

| 75 MHz                                                |                    |     | 55    |     | dBm     |                                                                         |

| 800 MHz                                               |                    |     | 55    |     | dBm     |                                                                         |

| 1800 MHz                                              |                    |     | 53    |     | dBm     |                                                                         |

| 2600 MHz                                              |                    |     | 55    |     | dBm     |                                                                         |

| 3800 MHz                                              |                    |     | 48    |     | dBm     |                                                                         |

| 4800 MHz                                              |                    |     | 45    |     | dBm     |                                                                         |

| 5700 MHz                                              |                    |     | 55    |     | dBm     |                                                                         |

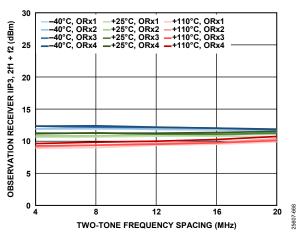

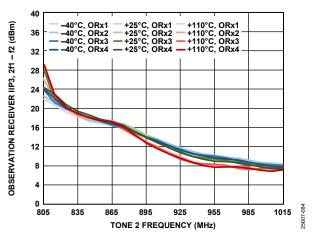

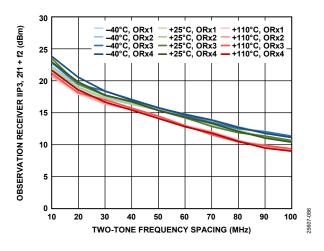

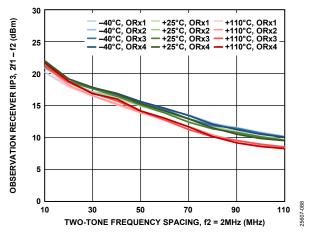

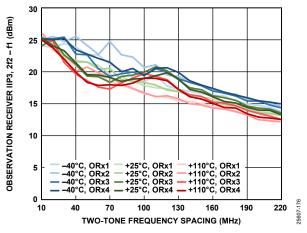

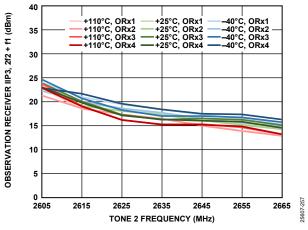

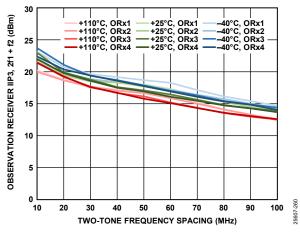

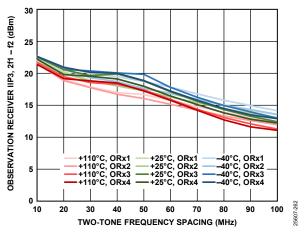

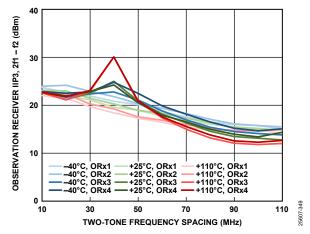

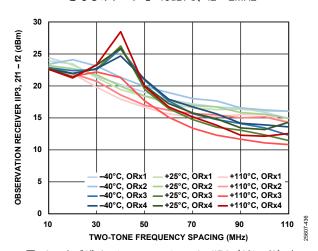

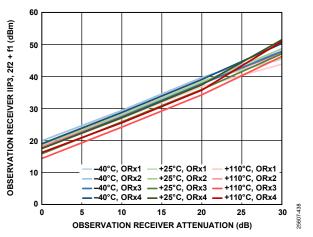

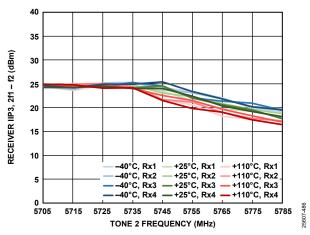

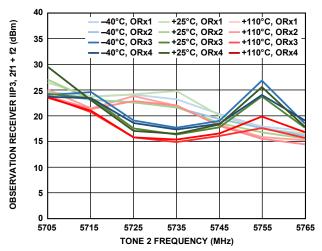

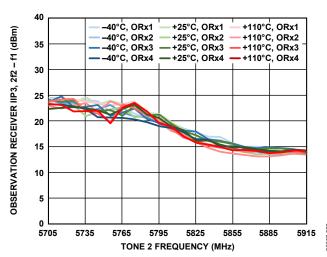

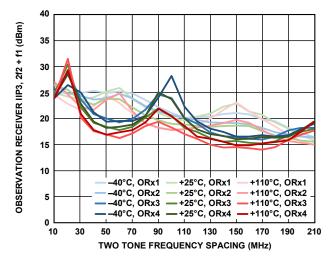

| Third-Order Input Intermodulation<br>Intercept Point  | IIP3               |     |       |     |         | 最大オブザベーション・レシーバー・ゲイン。テスト条件: $P_{HIGH}$ - $11dB/tone$                    |

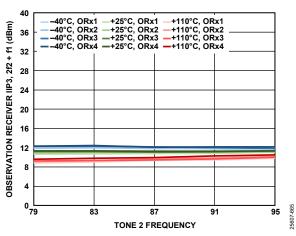

| Narrow Band                                           | IIP3 <sub>NB</sub> |     |       |     |         | ベースバンドでの IM3 積 < 130MHz。テスト条件: P <sub>HIGH</sub> - 11dB/tone、491.52MSPS |

| 75 MHz                                                |                    |     | 11    |     | dBm     |                                                                         |

| 800 MHz                                               |                    |     | 13.6  |     | dBm     |                                                                         |

| 1800 MHz                                              |                    |     | 15    |     | dBm     |                                                                         |

| 2600 MHz                                              |                    |     | 16.5  |     | dBm     |                                                                         |

| 3800 MHz                                              |                    |     | 18    |     | dBm     |                                                                         |

| 4800 MHz                                              |                    |     | 18    |     | dBm     |                                                                         |

| 5700 MHz                                              |                    |     | 18    |     | dBm     |                                                                         |

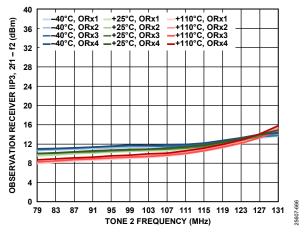

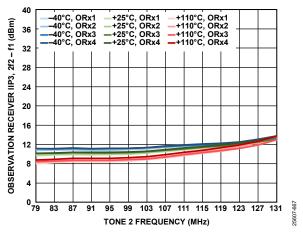

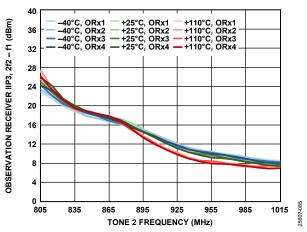

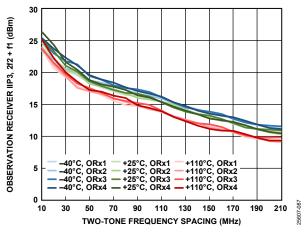

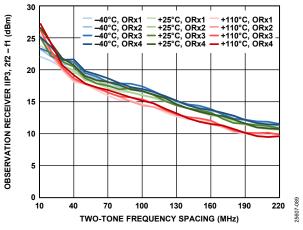

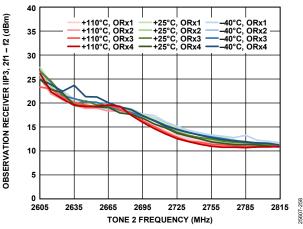

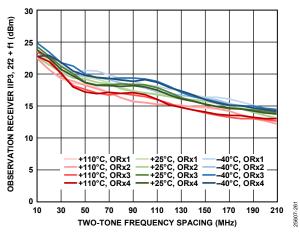

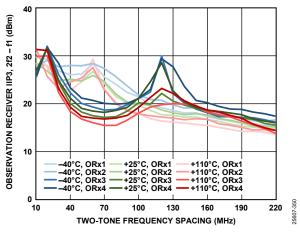

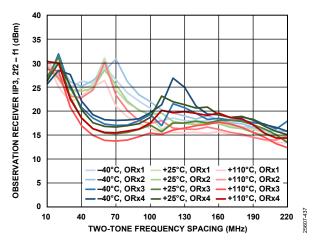

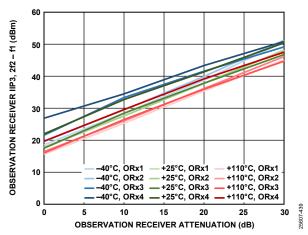

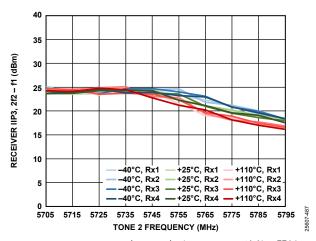

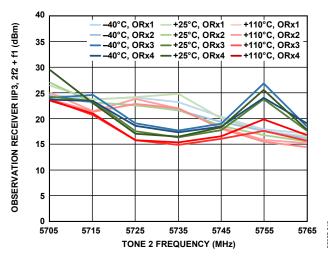

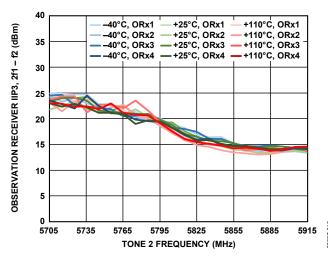

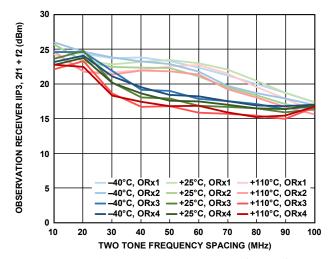

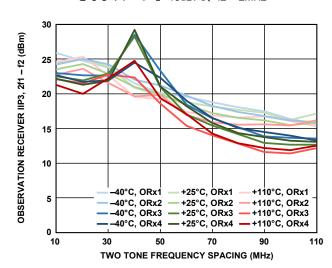

| Wide Band                                             | IIP3 <sub>WB</sub> |     |       |     |         | ベースバンドでの IM3 積 > 130MHz。テスト条件: P <sub>HIGH</sub> - 11dB/tone、491.52MSPS |

| 800 MHz                                               |                    |     | 7.8   |     | dBm     |                                                                         |

| 1800 MHz                                              |                    |     | 13    |     | dBm     |                                                                         |

| 2600 MHz                                              |                    |     | 11    |     | dBm     |                                                                         |

| 3800 MHz                                              |                    |     | 13    |     | dBm     |                                                                         |

| 4800 MHz                                              |                    |     | 13    |     | dBm     |                                                                         |

| 5700 MHz                                              |                    |     | 14    |     | dBm     |                                                                         |

Rev. 0 – 9/133 –

| パラメータ                                 | 記号                | Min Typ | Max | 単位  | テスト条件/コメント                                          |

|---------------------------------------|-------------------|---------|-----|-----|-----------------------------------------------------|

| Third-Order Intermodulation Product   | IM3               | 71      |     |     |                                                     |

| Narrow Band                           | IM3 <sub>NB</sub> |         |     |     | ベースバンドで IM3 積 < 130MHz。テスト条件:                       |

|                                       |                   |         |     |     | ツー・トーン、それぞれ P <sub>HIGH</sub> - 11dB、<br>491.52MSPS |

| 800 MHz                               |                   | -74     |     | dBc |                                                     |

| 1800 MHz                              |                   | -79     |     | dBc |                                                     |

| 2600 MHz                              |                   | -78.6   |     | dBc |                                                     |

| 3800 MHz                              |                   | -80.4   |     | dBc |                                                     |

| 4800 MHz                              |                   | -79.8   |     | dBc |                                                     |

| 5700 MHz                              |                   | -76     |     | dBc |                                                     |

| Wide Band                             | IM3 <sub>WB</sub> |         |     |     | ベースバンドで IM3 積 > 130MHz。テスト条件:                       |

|                                       |                   |         |     |     | ツー・トーン、それぞれ P <sub>HIGH</sub> - 11dB、               |

|                                       |                   |         |     |     | 491.52MSPS                                          |

| 800 MHz                               |                   | -62.4   |     | dBc |                                                     |

| 1800 MHz                              |                   | -70     |     | dBc |                                                     |

| 2600 MHz                              |                   | -67.6   |     | dBc |                                                     |

| 3800 MHz                              |                   | -70.4   |     | dBc |                                                     |

| 4800 MHz                              |                   | -69.8   |     | dBc |                                                     |

| 5700 MHz                              |                   | -66     |     | dBc |                                                     |

| Fifth-Order Intermodulation Product   | IM5               |         |     |     |                                                     |

| Narrow Band                           | IM5 <sub>NB</sub> |         |     |     | ベースバンドで IM5 積 < 130MHz。テスト条件:                       |

|                                       |                   |         |     |     | ツー・トーン、それぞれ P <sub>HIGH</sub> - 11dB、               |

|                                       |                   |         |     |     | 491.52MSPS                                          |

| 800 MHz                               |                   | -83     |     | dBc |                                                     |

| 1800 MHz                              |                   | -87     |     | dBc |                                                     |

| 2600 MHz                              |                   | -84     |     | dBc |                                                     |

| 3800 MHz                              |                   | -80     |     | dBc |                                                     |

| 4800 MHz                              |                   | -78     |     | dBc |                                                     |

| 5700 MHz                              |                   | -81     |     | dBc |                                                     |

| Wide Band                             | $IM5_{WB}$        |         |     |     | ベースバンドで IM5 積 > 130MHz。テスト条件:                       |

|                                       |                   |         |     |     | ツー・トーン、それぞれ P <sub>HIGH</sub> - 11dB、               |

|                                       |                   |         |     |     | 491.52MSPS                                          |

| 800 MHz                               |                   | -83     |     | dBc |                                                     |

| 1800 MHz                              |                   | -96     |     | dBc |                                                     |

| 2600 MHz                              |                   | -85     |     | dBc |                                                     |

| 3800 MHz                              |                   | -80     |     | dBc |                                                     |

| 4800 MHz                              |                   | -77     |     | dBc |                                                     |

| 5700 MHz                              |                   | -85     |     | dBc |                                                     |

| Seventh-Order Intermodulation Product | IM7               |         |     |     |                                                     |

| Narrow Band                           | $IM7_{NB}$        |         |     |     | ベースバンドで IM7 積 < 130MHz。テスト条件:                       |

|                                       |                   |         |     |     | ツー・トーン、それぞれ P <sub>HIGH</sub> - 11dB、               |

|                                       |                   |         |     |     | 491.52MSPS                                          |

| 800 MHz                               |                   | -74     |     | dBc |                                                     |

| 1800 MHz                              |                   | -78     |     | dBc |                                                     |

| 2600 MHz                              |                   | -75     |     | dBc |                                                     |

| 3800 MHz                              |                   | -73     |     | dBc |                                                     |

| 4800 MHz                              |                   | -78     |     | dBc |                                                     |

| 5700 MHz                              |                   | -75     |     | dBc |                                                     |

Rev. 0 - 10/133 -

| パラメータ                                                                  | 記号         | Min | Тур | Max | 単位  | テスト条件/コメント                        |

|------------------------------------------------------------------------|------------|-----|-----|-----|-----|-----------------------------------|

| Wide Band                                                              | $IM7_{WB}$ |     |     |     |     | ベースバンドで IM7 積 > 130MHz。テスト条件:     |

|                                                                        |            |     |     |     |     | ツー・トーン、それぞれ $P_{HIGH}$ $ 11dB$ 、  |

|                                                                        |            |     |     |     |     | 491.52MSPS                        |

| 800 MHz                                                                |            |     | -83 |     | dBc |                                   |

| 1800 MHz                                                               |            |     | -82 |     | dBc |                                   |

| 2600 MHz                                                               |            |     | -83 |     | dBc |                                   |

| 3800 MHz                                                               |            |     | -83 |     | dBc |                                   |

| 4800 MHz                                                               |            |     | -85 |     | dBc |                                   |

| 5700 MHz                                                               |            |     | -81 |     | dBc |                                   |

| Spurious-Free Dynamic Range                                            | SFDR       |     | 64  |     | dB  | 非相互変調関連スプリアス。高調波歪みを含まな            |

|                                                                        |            |     |     |     |     | い。入力を P <sub>HIGH</sub> - 8dB に設定 |

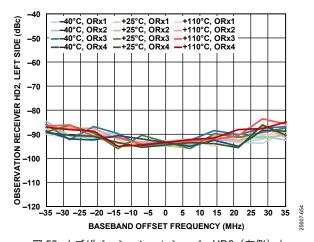

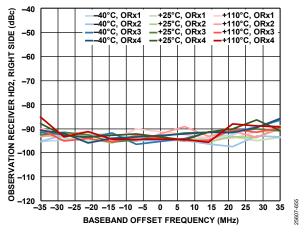

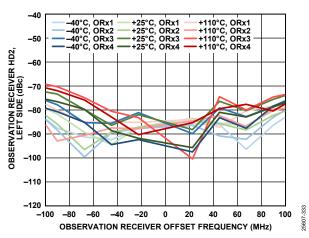

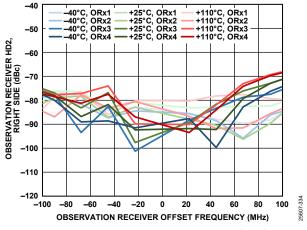

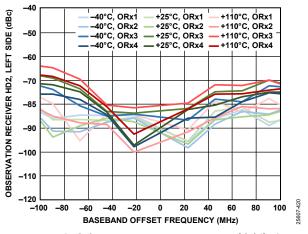

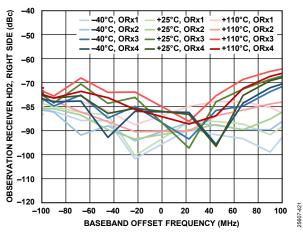

| Second-Order Harmonic Distortion                                       | HD2        |     |     |     |     | 入力を P <sub>HIGH</sub> - 8dB に設定   |

| In Band                                                                |            |     | -80 |     | dBc | 帯域内高調波歪みは±100MHz以内                |

| Out of Band                                                            |            |     | -73 |     | dBc | 帯域外高調波歪みは±225MHz以内                |

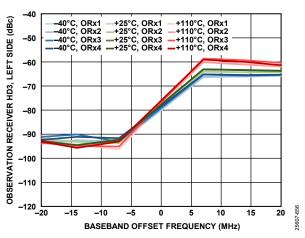

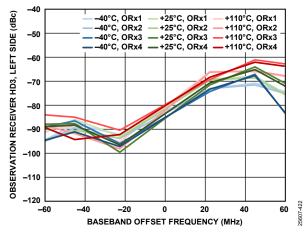

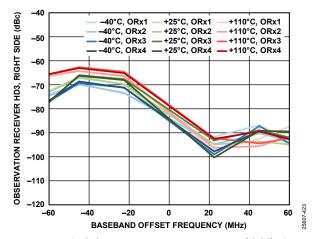

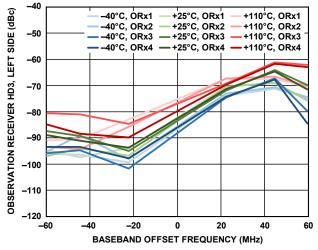

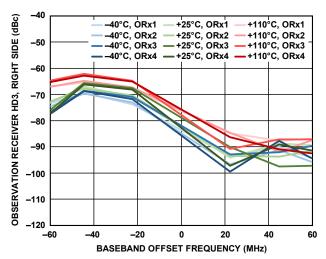

| Third-Order Harmonic Distortion                                        | HD3        |     |     |     |     | 入力を P <sub>HIGH</sub> - 8dB に設定   |

| In Band                                                                |            |     | -70 |     | dBc | 高調波歪みは±100MHz以内                   |

| Out of Band                                                            |            |     | -65 |     | dBc | 高調波歪みは±225MHz以内                   |

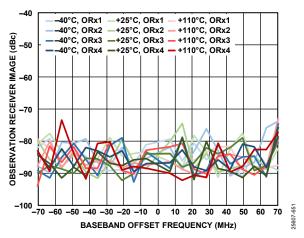

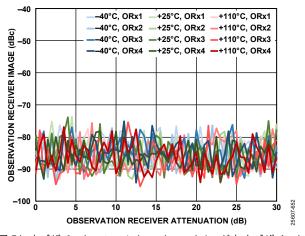

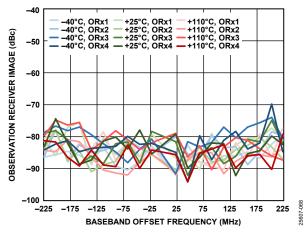

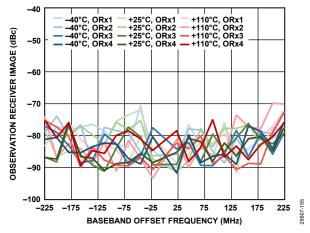

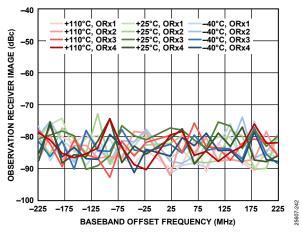

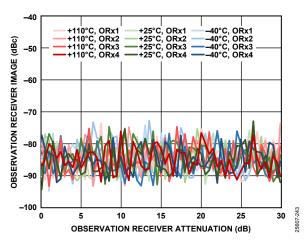

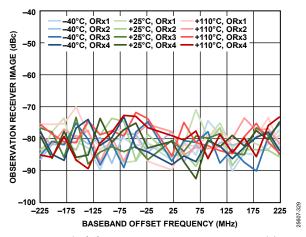

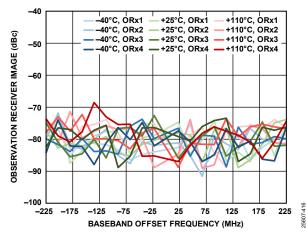

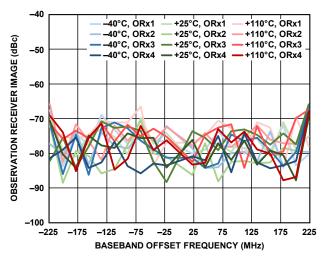

| Image Rejection                                                        |            |     | 75  |     | dB  | オンライン・トーン・キャリブレーション後、             |

|                                                                        |            |     |     |     |     | QEC: アクティブ                        |

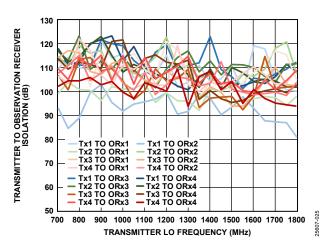

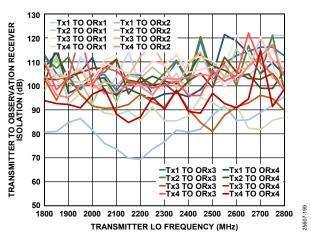

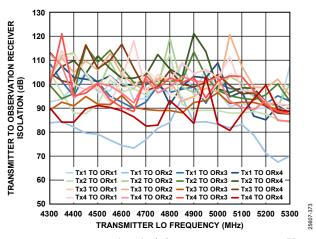

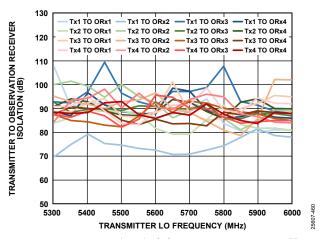

| Tx to ORx Signal Isolation: All Tx<br>Output Effects on all ORx Inputs |            |     | 75  |     | dB  |                                   |

# シンセサイザ、補助コンバータ、およびクロック・リファレンス

#### 表 2.

| パラメータ                         | 記号       | Min Typ | Max | 単位     | テスト条件/コメント                                               |

|-------------------------------|----------|---------|-----|--------|----------------------------------------------------------|

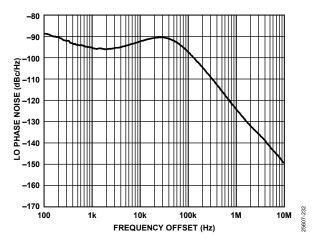

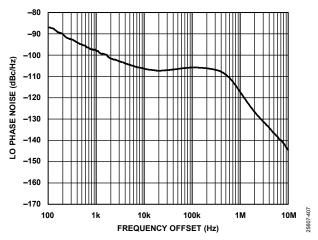

| LO1 and LO2 SYNTHESIZER       | LO1, LO2 |         |     |        |                                                          |

| Frequency Step                |          | 7.3     |     | Hz     | 1.6GHz~3.2GHz、位相周波数検出器(PFD)<br>周波数: 245.76MHz            |

| Spectral Purity               |          | -80     |     | dBc    |                                                          |

| Integrated Phase Noise        |          |         |     |        | 1kHz~100MHz で積分                                          |

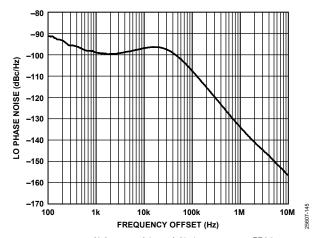

| Narrow Bandwidth Optimized    |          |         |     |        | 200kHz を超えるオフセットでの位相ノイズを<br>最小限に抑えるように最適化した PLL 帯域幅      |

| 800 MHz                       |          | 0.12    |     | °rms   |                                                          |

| 1800 MHz                      |          | 0.27    |     | °rms   |                                                          |

| 2600 MHz                      |          | 0.66    |     | °rms   |                                                          |

| 3800 MHz                      |          | 0.53    |     | °rms   |                                                          |

| 4800 MHz                      |          | 0.91    |     | °rms   |                                                          |

| 5700 MHz                      |          | 1.57    |     | °rms   |                                                          |

| Wide Bandwidth Optimized      |          |         |     |        | 積分位相ノイズと 1MHz を超えるオフセット<br>での位相ノイズに合わせて最適化した PLL 帯<br>域幅 |

| 800 MHz                       |          | 0.07    |     | °rms   |                                                          |

| 1800 MHz                      |          | 0.11    |     | °rms   |                                                          |

| 2600 MHz                      |          | 0.17    |     | °rms   |                                                          |

| 3800 MHz                      |          | 0.26    |     | °rms   |                                                          |

| 4800 MHz                      |          | 0.30    |     | °rms   |                                                          |

| 5700 MHz                      |          | 0.42    |     | °rms   |                                                          |

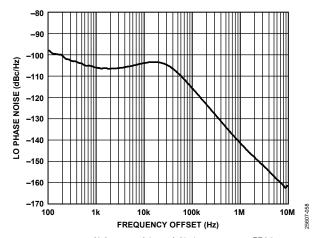

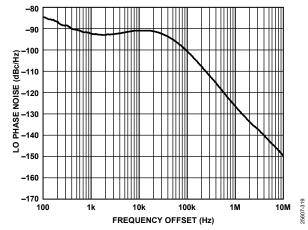

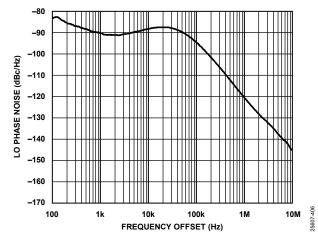

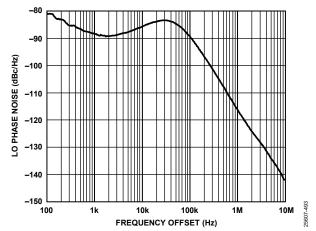

| Spot Phase Noise: Narrow Band |          |         |     |        | 200kHz を超えるオフセットでの位相ノイズを<br>最小限に抑えるように最適化した PLL 帯域幅      |

| 800 MHz LO1 and LO2           |          |         |     |        |                                                          |

| 100 kHz Offset                |          | -115    |     | dBc/Hz |                                                          |

| 1 MHz Offset                  |          | -141    |     | dBc/Hz |                                                          |

| 10 MHz Offset                 |          | -162    |     | dBc/Hz |                                                          |

Rev. 0 — 11/133 —

| パラメータ                      | 記号 | Min Typ | Max | 単位     | テスト条件/コメント                    |

|----------------------------|----|---------|-----|--------|-------------------------------|

| 1800 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -107    |     | dBc/Hz |                               |

| 200 kHz Offset             |    | -115    |     | dBc/Hz |                               |

| 400 kHz Offset             |    | -123    |     | dBc/Hz |                               |

| 600 kHz Offset             |    | -128    |     | dBc/Hz |                               |

| 800 kHz Offset             |    | -131    |     | dBc/Hz |                               |

| 1.2 MHz Offset             |    | -136    |     | dBc/Hz |                               |

| 1.8 MHz Offset             |    | -140    |     | dBc/Hz |                               |

| 6 MHz Offset               |    | -151    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -156    |     | dBc/Hz |                               |

| 2600 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -97     |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -124    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -150    |     | dBc/Hz |                               |

| 3800 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -100    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -126    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -149    |     | dBc/Hz |                               |

| 4800 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -94     |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -120    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -145    |     | dBc/Hz |                               |

| 5700 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -89     |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -115    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -141    |     | dBc/Hz |                               |

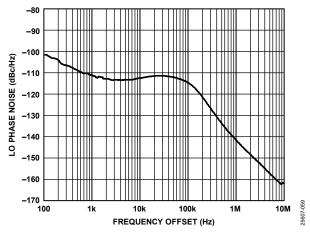

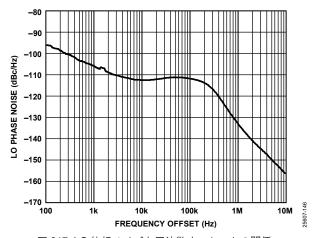

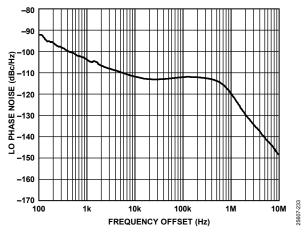

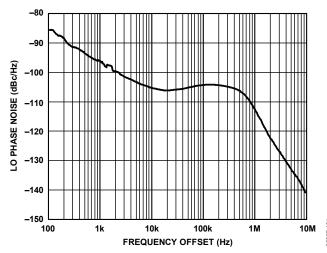

| Spot Phase Noise: Wideband |    |         |     |        | 積分位相ノイズと 1MHz を超えるオフセット       |

|                            |    |         |     |        | での位相ノイズに合わせて最適化した PLL 帯<br>域幅 |

| 800 MHz LO1 and LO2        |    |         |     |        |                               |

| 100 kHz Offset             |    | -114    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -141    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -162    |     | dBc/Hz |                               |

| 1800 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -112    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -133    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -156    |     | dBc/Hz |                               |

| 2600 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -112    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -120    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -149    |     | dBc/Hz |                               |

| 3800 MHz LO                |    |         |     |        |                               |

| 100 kHz Offset             |    | -104    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -125    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -149    |     | dBc/Hz |                               |

| 4800 MHz LO1 and LO2       |    |         |     |        |                               |

| 100 kHz Offset             |    | -106    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -117    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -144    |     | dBc/Hz |                               |

| 5700 MHz LO1 and LO2       |    | ]       |     |        |                               |

| 100 kHz Offset             |    | -104    |     | dBc/Hz |                               |

| 1 MHz Offset               |    | -112    |     | dBc/Hz |                               |

| 10 MHz Offset              |    | -140    |     | dBc/Hz |                               |

Rev. 0 – 12/133 –

| パラメータ                       | 記号  | Min Ty     | ур Мах | 単位     | テスト条件/コメント                                    |

|-----------------------------|-----|------------|--------|--------|-----------------------------------------------|

| AUXILIARY SYNTHESIZER       | LO3 |            |        |        |                                               |

| Frequency Step              |     | 1.         | 8      | Hz     | 1.625GHz~3.25GHz、61.44MHz PFD 周波数             |

| Spectral Purity             |     | -6         | 55     | dBc    | $ f_{RFLO} - f_{AUXLO}  > 15MHz$              |

| Integrated Phase Noise      |     |            |        |        | 1kHz~100MHz を積分、積分位相ノイズに合<br>わせて最適化した PLL 帯域幅 |

| 800 MHz LO3                 |     | 0.         | 18     | °rms   |                                               |

| 1800 MHz LO3                |     | 0.         | 22     | °rms   |                                               |

| 2600 MHz LO3                |     | 0.         | 46     | °rms   |                                               |

| 3800 MHz LO3                |     | 0.         | 43     | °rms   |                                               |

| 4800 MHz LO3                |     | 0.         | 70     | °rms   |                                               |

| 5700 MHz LO3                |     | 1.         | 12     | °rms   |                                               |

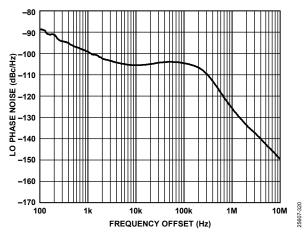

| Spot Phase Noise            |     |            |        |        |                                               |

| 800 MHz LO3                 |     |            |        |        |                                               |

| 100 kHz Offset              |     | -1         | 112    | dBc/Hz |                                               |

| 1 MHz Offset                |     | -1         | 121    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 141    | dBc/Hz |                                               |

| 1800 MHz LO3                |     |            |        |        |                                               |

| 100 kHz Offset              |     | -1         | 110    | dBc/Hz |                                               |

| 1 MHz Offset                |     | -1         | 120    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 134    | dBc/Hz |                                               |

| 2600 MHz LO3                |     |            |        |        |                                               |

| 100 kHz Offset              |     | -1         | 103    | dBc/Hz |                                               |

| 1 MHz Offset                |     | -1         | 114    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 132    | dBc/Hz |                                               |

| 3800 MHz LO3                |     |            |        |        |                                               |

| 100 kHz Offset              |     | -1         | 104    | dBc/Hz |                                               |

| 1 MHz Offset                |     | -1         | 114    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 128    | dBc/Hz |                                               |

| 4800 MHz LO3                |     |            |        |        |                                               |

| 100 kHz Offset              |     |            | 100    | dBc/Hz |                                               |

| 1 MHz Offset                |     | -1         | 110    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 127    | dBc/Hz |                                               |

| 5700 MHz LO3                |     |            |        |        |                                               |

| 100 kHz Offset              |     | - <u>ç</u> |        | dBc/Hz |                                               |

| 1 MHz Offset                |     |            | 106    | dBc/Hz |                                               |

| 10 MHz Offset               |     | -1         | 126    | dBc/Hz |                                               |

| LO PHASE<br>SYNCHRONIZATION |     |            |        |        |                                               |

| Initial Phase Sync Accuracy |     | 0.         | 9      | ps     |                                               |

| CLOCK SYNTHESIZER           |     |            |        |        |                                               |