# レベル・シフトおよび出力クランプ機能を備えた 高精度減衰計装アンプ

### 特長

- 単一のゲイン設定抵抗 G = 0.2 ~ >200

- 優れたDC 精度

- 入力オフセット電圧:最大 60 µV

- 入力オフセット電圧ドリフト:最大 0.6 µV/℃

- 低ゲイン誤差:最大0.012%(G=0.2)

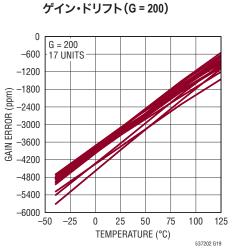

- 低ゲイン・ドリフト: 最大35ppm/°C(G > 0.2)

- 高いDC CMRR:最小80dB(G=0.2)

- 出力クランプ機能内蔵

- 出力レベル・シフト機能内蔵

- 入力バイアス電流:最大800pA

- -3dB帯域幅:4MHz(G = 0.2)

- 低ノイズ:

- 0.1Hz~10Hzでのノイズ:0.2µV<sub>P-P</sub>

- 1kHzでの電圧ノイズ:7nV/√Hz

- 入力 RFI フィルタ内蔵

- 広い電源範囲:4.75V~35V

- 温度範囲:-40℃~85℃、および-40℃~125℃

- MS16E および20ピン3mm × 4mm QFNパッケージ

### アプリケーション

- ブリッジ・アンプ

- データ・アクイジション

- 熱電対アンプ

- 歪みゲージ・アンプ

- 医療用計測機器

- 変換器インターフェース

- 差動からシングルエンドへの変換

### 概要

LT®6372-0.2は、業界最高レベルの精度を誇るプログラマブル・ゲイン式の高精度減衰計装アンプです。この高い精度はより小さい信号の検出を可能にして、特に温度に関するキャリブレーション条件を緩和します。LT6372-0.2は、LT6370に各種の機能を組み込むことにより精度を高めたデバイスで、ADCへのインターフェースを簡素化します。

LT6372-0.2 は独自の高性能バイポーラ・プロセスを使用して、業界最高レベルの精度と卓越した長期安定性を両立させています。LT6372-0.2 は、極めて低い入力オフセット電圧  $(60\mu V)$  と高い CMRR (80dB, G=0.2) を実現するために、レーザー・トリミングされています。独自のオンチップ・テスト機能により、自動化されたテストでゲイン・ドリフト  $(35ppm/\ ^{\circ}C)$  を確認することができます。

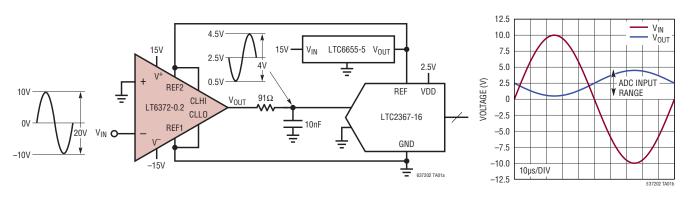

LT6372-0.2のディファレンス・アンプは分割リファレンス構成を使用しており、アンプの出力をADC入力範囲の中央に簡単にレベル・シフトすることができます。ADC入力に加えることのできる電圧を制限する、出力クランプ・ピンも備えています。更に、過酷なRF干渉が存在する環境下でも精度を維持できるように、LT6372-0.2の入力にはEMIフィルタが組み込まれています。

LT6372-0.2は、小型のMS16Eパッケージ、または20ピンの3mm×4mm QFNパッケージを採用しています。LT6372-0.2のすべての仕様は、-40℃~85℃および-40℃~125℃の温度範囲で規定されています。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

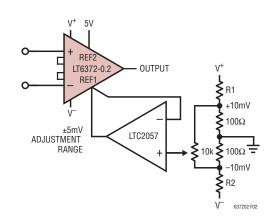

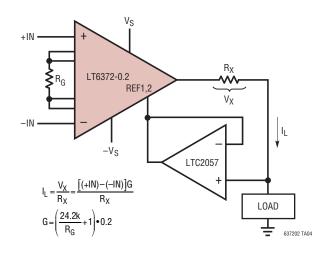

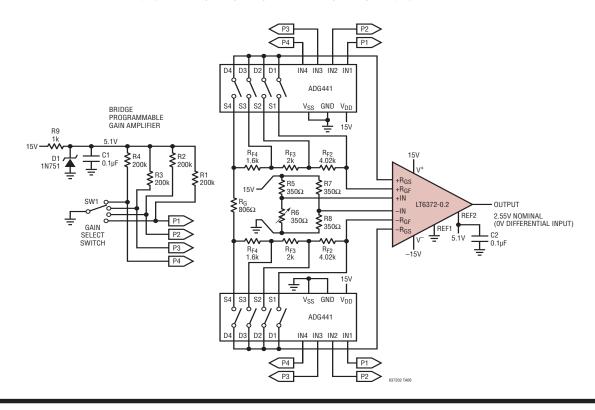

### 標準的応用例

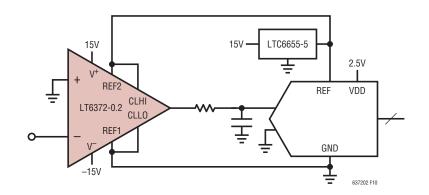

#### ±10V 入力を5VのADC 入力範囲に減衰して レベル・シフトするLT6372-0.2

Rev. 0

1

文書に関するご意見 詳細:www.analog.com

### 絶対最大定格

(Note 1)

| 総電源電圧(V <sup>+</sup> ~V <sup>-</sup> )                                                    | 36V            |

|-------------------------------------------------------------------------------------------|----------------|

| 入力電圧(+IN、-IN、+R <sub>G,S</sub> 、+R <sub>G,F</sub> 、-R <sub>G,S</sub> 、-R <sub>G,F</sub> 、 |                |

| REF1、REF2、CLHI、CLLO)( $V^-$ – 0.3 $V$ ) $\sim$                                            | $(V^+ + 0.3V)$ |

| 差動入力電圧                                                                                    |                |

| (+IN∼–IN)                                                                                 | ±36V           |

| (REF1~REF2)                                                                               | ±8V            |

| 入力電流                                                                                      |                |

| (+R <sub>GS</sub> 、+R <sub>GF</sub> 、-R <sub>GS</sub> 、-R <sub>GF</sub> )                 | ±2mA           |

| (+IN、-IN、CLLO)                                                                            | ±10mA          |

| (RFF1, RFF2, CLHI)                                                                        | 10mA           |

| 出力短絡時間           |            |

|------------------|------------|

| 出力電流             | 80mA       |

| 動作および仕様温度範囲      |            |

| Iグレード            | 40°C~85°CV |

| Hグレード            | 40°C~125°C |

| 最大ジャンクション温度      | 150°C      |

| 保存温度範囲           | 65°C~150°C |

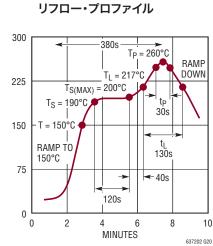

| リード温度(ハンダ処理、10秒) | 300°C      |

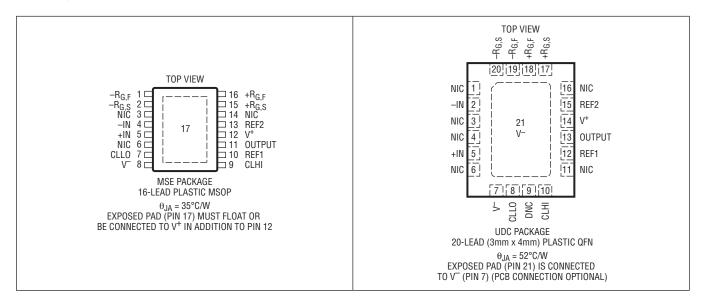

### ピン配置

### 発注情報

| チューブ                | テープ&リール              | 部品マーキング* | パッケージ                  | 温度範囲         |

|---------------------|----------------------|----------|------------------------|--------------|

| LLT6372IMSE-0.2#PBF | LT6372IMSE-0.2#TRPBF | 637202   | 16 ピンプラスチック MSOP       | -40°C∼+85°C  |

| LT6372HMSE-0.2#PBF  | LT6372HMSE-0.2#TRPBF | 637202   | 16 ピンプラスチック MSOP       | -40°C∼+125°C |

| LT6372IUDC-0.2#PBF  | LT6372IUDC-0.2#TRPBF | LHHQ     | 20ピン(3mm×4mm)プラスチックQFN | -40°C∼+85°C  |

| LT6372HUDC-0.2#PBF  | LT6372IMSE-0.2#TRPBF | LHHQ     | 20ピン(3mm×4mm)プラスチックQFN | -40°C∼+125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷容器のラベルに示されています。 テープ&リール仕様。一部のバッケージは、指定販売チャンネルを通じ500個入りのリールで購入できます。 末尾に #TRMPBF という記号が付きます。

Rev. 0

### 電気的特性

●は指定動作温度範囲での規格値を意味する。それ以外は、T<sub>A</sub> = 25°C、V<sub>S</sub> = ±15V、V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V、V<sub>CLLO</sub> = V<sup>+</sup>、V<sub>CLHI</sub> = V<sup>+</sup>、R<sub>L</sub> = 4kΩでの値。

| SYMBOL                   | PARAMETER                                                                | CONDITIONS                                                                                                                                                                                                            |   | MIN | TYP                                       | MAX                                                                            | UNITS                           |

|--------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------|--------------------------------------------------------------------------------|---------------------------------|

| G                        | Gain Range                                                               | G = 0.2 • (1 + 24.2k/R <sub>G</sub> ) (Note 2)                                                                                                                                                                        |   | 0.2 |                                           | 200                                                                            | V/V                             |

|                          | Gain Error (Notes 3, 4)                                                  | G = 0.2<br>G = 0.2<br>G = 1<br>G = 1<br>G = 10<br>G = 100<br>G = 100<br>G = 200<br>G = 200                                                                                                                            | • |     | 0.002<br>0.01<br>0.02<br>0.02<br>0.03     | 0.012<br>0.015<br>0.15<br>0.45<br>0.15<br>0.45<br>0.15<br>0.45<br>0.15<br>0.45 | %<br>%<br>%<br>%<br>%<br>%<br>% |

|                          | Gain vs Temperature (Notes 3, 4)                                         | G = 0.2 (Note 5)<br>G > 0.2 (Note 6)                                                                                                                                                                                  | • |     | 0.2<br>20                                 | 0.5<br>35                                                                      | ppm/°C<br>ppm/°C                |

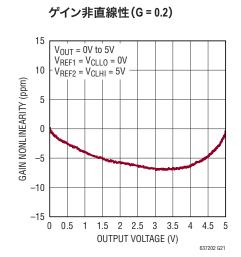

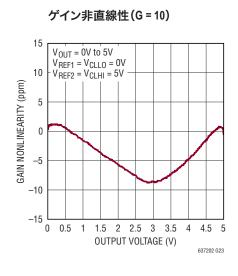

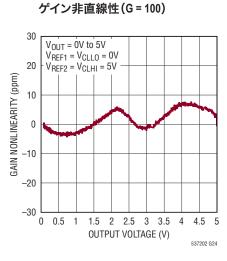

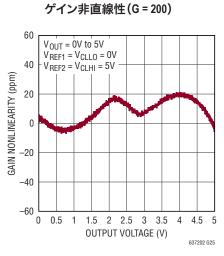

|                          | Gain Nonlinearity (Notes 3, 7)                                           | V <sub>OUT</sub> = 0V to 4.096V, G = 0.2<br>V <sub>OUT</sub> = 0V to 4.096V, G = 1<br>V <sub>OUT</sub> = 0V to 4.096V, G = 10<br>V <sub>OUT</sub> = 0V to 4.096V, G = 100<br>V <sub>OUT</sub> = 0V to 4.096V, G = 200 |   |     | 3<br>4<br>5<br>6<br>12                    | 5<br>60<br>80                                                                  | ppm<br>ppm<br>ppm<br>ppm<br>ppm |

| V <sub>OST</sub> , Total | I Input Referred Offset Voltage, V <sub>OST</sub> = V <sub>OSI</sub> + V | 'oso/G                                                                                                                                                                                                                |   |     |                                           |                                                                                |                                 |

| V <sub>OSI</sub>         | Input Offset Voltage<br>(Note 8)                                         |                                                                                                                                                                                                                       | • |     | ±15                                       | ±60<br>±175                                                                    | μV<br>μV                        |

| V <sub>OSO</sub>         | Output Offset Voltage (Note 8)                                           |                                                                                                                                                                                                                       | • |     | ±30                                       | ±175<br>±300                                                                   | μV<br>μV                        |

| V <sub>OSI</sub> /T      | Input Offset Voltage Drift<br>(Notes 5, 8)                               |                                                                                                                                                                                                                       | • |     |                                           | ±0.6                                                                           | μV/°C                           |

|                          | Input Offset Voltage<br>Hysteresis (Note 9)                              | T <sub>A</sub> = -40°C to 125°C                                                                                                                                                                                       | • |     | ±3                                        |                                                                                | μV                              |

| V <sub>OSO</sub> /T      | Output Offset Voltage Drift (Notes 5, 8)                                 |                                                                                                                                                                                                                       | • |     |                                           | ±2                                                                             | μV/°C                           |

|                          | Output Offset Voltage Hysteresis (Note 9)                                | T <sub>A</sub> = -40°C to 125°C                                                                                                                                                                                       | • |     | ±10                                       |                                                                                | μV                              |

| l <sub>B</sub>           | Input Bias Current                                                       | T <sub>A</sub> = -40°C to 85°C<br>T <sub>A</sub> = -40°C to 125°C                                                                                                                                                     | • |     | ±0.1                                      | ±0.8<br>±1.5<br>±3                                                             | nA<br>nA<br>nA                  |

| los                      | Input Offset Current                                                     |                                                                                                                                                                                                                       | • |     | ±0.2                                      | ±1.4<br>±4                                                                     | nA<br>nA                        |

|                          | Input Offset Noise Voltage (Note 10)                                     | 0.1Hz to 10Hz, G = 0.2<br>0.1Hz to 10Hz, G = 200                                                                                                                                                                      |   |     | 4<br>0.2                                  |                                                                                | µV <sub>P-P</sub>               |

| Total RTI N              | loise = $\sqrt{e_{ni}^2 + (e_{no}/G)^2}$ (Note 10)                       |                                                                                                                                                                                                                       | • |     |                                           |                                                                                |                                 |

| e <sub>ni</sub>          | Input Noise Voltage Density                                              | f = 1kHz                                                                                                                                                                                                              |   |     | 7                                         |                                                                                | nV/√Hz                          |

| e <sub>no</sub>          | Output Noise Voltage Density                                             | f = 1kHz                                                                                                                                                                                                              |   |     | 32                                        |                                                                                | nV/√Hz                          |

|                          | Input Noise Current                                                      | 0.1Hz to 10Hz                                                                                                                                                                                                         |   |     | 10                                        |                                                                                | pA <sub>P-P</sub>               |

| i <sub>n</sub>           | Input Noise Current Density                                              | f = 1kHz                                                                                                                                                                                                              |   |     | 200                                       |                                                                                | fA/√Hz                          |

| R <sub>IN</sub>          | Input Resistance                                                         | V <sub>IN</sub> = -12.6V to 13V                                                                                                                                                                                       |   |     | 225                                       |                                                                                | GΩ                              |

| C <sub>IN</sub>          | Differential<br>Common Mode                                              | f = 100kHz<br>f = 100kHz                                                                                                                                                                                              |   |     | 0.9<br>15.9                               |                                                                                | pF<br>pF                        |

| V <sub>CM</sub>          | Input Voltage Range                                                      | Guaranteed by CMRR                                                                                                                                                                                                    |   | ,   | V <sup>-</sup> + 1.8/V <sup>+</sup> – 1.4 |                                                                                | V                               |

Rev. (

### 電気的特性

●は指定動作温度範囲での規格値を意味する。それ以外は、T<sub>A</sub> = 25°C、V<sub>S</sub> = ±15V、V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V、V<sub>CLLO</sub> = V<sup>+</sup>、V<sub>CLHI</sub> = V<sup>+</sup>、R<sub>L</sub> = 4kΩでの値。

| SYMBOL           | PARAMETER                      | CONDITIONS                                                                                                                                                                           |   | MIN                                                  | TYP                             | MAX                                     | UNITS                                  |

|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------|---------------------------------|-----------------------------------------|----------------------------------------|

| CMRR             | Common Mode Rejection Ratio    | DC to 60Hz, 1k Source Imbalance, V <sub>CM</sub> = -12.6V to 13V G = 0.2 G = 0.2 G = 1 G = 1 G = 1 G = 10 G = 100 G = 100 G = 200 G = 200                                            | • | 80<br>74<br>95<br>89<br>114<br>108                   | 96<br>110<br>130<br>146<br>146  |                                         | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

|                  | AC Common Mode Rejection Ratio | f = 20kHz, QFN20 Package<br>G = 0.2<br>G = 2<br>G = 20<br>G = 200                                                                                                                    |   |                                                      | 62<br>82<br>104<br>104          |                                         | dB<br>dB<br>dB<br>dB                   |

|                  |                                | f = 20kHz, MS16E Package<br>G = 0.2<br>G = 2<br>G = 20<br>G = 200                                                                                                                    |   |                                                      | 80<br>100<br>104<br>104         |                                         | dB<br>dB<br>dB<br>dB                   |

| PSRR             | Power Supply Rejection Ratio   | V <sub>S</sub> = ±2.375V to ±17.5V<br>G = 0.2<br>G = 0.2<br>G = 1<br>G = 1<br>G = 10<br>G = 10<br>G = 100<br>G = 100<br>G = 200                                                      | • | 106<br>104<br>120<br>117<br>128<br>122<br>128<br>122 | 121<br>135<br>140<br>142<br>146 |                                         | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| Vs               | Supply Voltage                 | Guaranteed by PSRR                                                                                                                                                                   | • | 4.75                                                 |                                 | 35                                      | V                                      |

| Is               | Supply Current                 | $V_S = \pm 15V$ $T_A = -40^{\circ}\text{C}$ to 85°C $T_A = -40^{\circ}\text{C}$ to 125°C $V_S = \pm 2.375V$ $T_A = -40^{\circ}\text{C}$ to 85°C $T_A = -40^{\circ}\text{C}$ to 125°C | • |                                                      | 2.75                            | 2.85<br>3<br>3.1<br>2.7<br>2.85<br>2.95 | mA<br>mA<br>mA<br>mA<br>mA             |

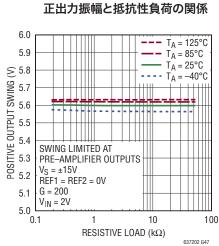

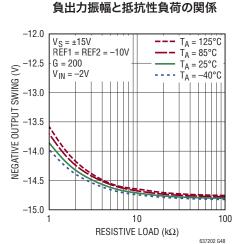

| V <sub>OUT</sub> | Output Voltage Swing           | $V_S = \pm 15V$ , RL = $10k\Omega$                                                                                                                                                   | • | -14.4<br>-14.2                                       | -14.7/14                        | 13.6<br>13.5                            | V                                      |

|                  |                                | $V_S = \pm 2.375V$ , RL = $10k\Omega$                                                                                                                                                | • | -0.7<br>-0.5                                         | -1/1.6                          | 1.4<br>1.2                              | V                                      |

| l <sub>OUT</sub> | Output Short Circuit Current   |                                                                                                                                                                                      | • | 35<br>30                                             | 55                              |                                         | mA<br>mA                               |

| BW               | -3dB Bandwidth                 | G = 0.2<br>G = 1<br>G = 10<br>G = 100<br>G = 200                                                                                                                                     |   |                                                      | 4<br>2<br>1<br>140<br>15        |                                         | MHz<br>MHz<br>MHz<br>kHz<br>kHz        |

| SR               | Slew Rate                      | G = 1, V <sub>OUT</sub> = ±2.5V                                                                                                                                                      |   |                                                      | 3.5                             |                                         | V/µs                                   |

### 電気的特性

● は指定動作温度範囲での規格値を意味する。それ以外は、T<sub>A</sub> = 25°C、V<sub>S</sub> = ±15V、V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V、V<sub>CLLO</sub> = V<sup>-</sup>、V<sub>CLHI</sub> = V<sup>+</sup>、R<sub>L</sub> = 4kΩでの値。

| SYMBOL             | PARAMETER                                                  | CONDITIONS                                                         |   | MIN                | TYP                             | MAX                  | UNITS                |

|--------------------|------------------------------------------------------------|--------------------------------------------------------------------|---|--------------------|---------------------------------|----------------------|----------------------|

| ts                 | Settling Time                                              | 4.096V Output Step to 0.0015% G = 0.2 G = 1 G = 10 G = 100 G = 200 |   |                    | 1.8<br>2.5<br>12.4<br>68<br>135 |                      | μs<br>μs<br>μs<br>μs |

| R <sub>REFIN</sub> | REF Input Resistance                                       | REF1 or REF2, Untested REF pin floating                            |   |                    | 14                              |                      | kΩ                   |

| I <sub>REFIN</sub> | REF Input Current                                          | $V_{+IN} = V_{-IN} = V_{REF1} = V_{REF2} = 0V$ , REF1 or REF2      | • | -36<br>-50         | -24                             | -12<br>0             | μA<br>μA             |

| V <sub>REF</sub>   | REF Voltage Range                                          | REF1 or REF2                                                       | • | V <sup>-</sup>     |                                 | V <sup>+</sup>       | V                    |

| AVREF              | REF Gain to Output                                         | V <sub>REF1</sub> = 0V to 5V, V <sub>REF2</sub> = 0V               |   |                    | 0.5                             |                      | V/V                  |

|                    | REF Gain Error                                             | V <sub>REF1</sub> = 0V to 5V, V <sub>REF2</sub> = 0V               | • | -250<br>-300       | ±75                             | 250<br>300           | ppm<br>ppm           |

|                    | CLLO Input Current                                         | V <sub>CLLO</sub> = 0V                                             | • |                    |                                 | 1                    | μA                   |

|                    | CLHI Input Current                                         | V <sub>CLHI</sub> = 5V                                             | • |                    |                                 | 1                    | μA                   |

|                    | CLLO Input Operating Voltage Range                         | Outside this Range CLLO is Disabled                                | • | V <sup>-</sup> + 3 |                                 | V+ - 2               | V                    |

|                    | CLHI Input Operating Voltage Range                         | Outside this Range CLHI is Disabled                                | • | V <sup>-</sup> + 2 |                                 | V <sup>+</sup> – 2.5 | V                    |

|                    | CLLO Clamp Voltage (V <sub>OUT</sub> – V <sub>CLLO</sub> ) |                                                                    | • | -0.57<br>-0.74     | -0.45                           |                      | V                    |

|                    | CLHI Clamp Voltage (V <sub>OUT</sub> – V <sub>CLHI</sub> ) |                                                                    | • |                    | 0.45                            | 0.55<br>0.755        | V                    |

Note 1: 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えることがあります。

**Note 2:** ゲインを 200 以上にすることも可能ですが、その場合は  $R_G$  の値が小さくなることで、 PCB とパッケージのリード抵抗が大きな誤差源となるおそれがあります。

Note 3: ゲインが0.2V/Nを超える場合は、-INを電源電圧の中点に設定し、+INを駆動してゲイン・テストを行います。ゲインが0.2V/Nの場合は、-INと+INを差動で駆動してテストを行います。

Note 4: ゲインが0.2 より大きい場合、ゲイン誤差とゲイン・ドリフトの仕様に外付けゲイン設定抵抗Rgの影響は含まれません。

Note 5:この仕様は設計により確認されています。

Note 6:この仕様は高速自動テストにより確認されています。

Note 7:このパラメータは高速自動テスタで測定しますが、時定数が長い熱の影響は考慮

されません。これらの熱の影響の大きさは、使用するパッケージ、PCBレイアウト、ヒート・シンクの有無、および空気流などの条件によって異なります。

Note 8: オフセットがアンプにどのように関係するかについての詳細は、アプリケーションのセクションに示す「入力および出力オフセット電圧」を参照してください。

Note 9: 出力電圧のヒステリシスは機械的応力によって生じますが、この応力は、そのにがそれまで置かれていた環境が、現在より高温だったのか低温だったのかによって異なります。 出力電圧は常に  $25^\circ$ C で測定しますが、連続測定時は、 $16^\circ$ に高温限界値または低温限界値までの温度サイクルを実行してから測定を行います。とステリシスは、温度変化の平方根にほぼ比例します。適切な温度管理(動作温度の  $20^\circ$ 30 度以内)の下に保管されている計測器の場合、通常はヒステリシスによって大きな誤差が生じることはありません。代表的なヒステリシスは、 $25^\circ$ C 低温  $-25^\circ$ C におうなとなりません。で表的なヒステリシスは、 $16^\circ$ C 低温  $-25^\circ$ C におりません。で表的なヒステリシスは、 $16^\circ$ C 低温  $-25^\circ$ C におりません。で表的なヒステリシスは、 $16^\circ$ C 低温  $-25^\circ$ C におりません。で表的なヒステリシスは、 $16^\circ$ C 低温  $-25^\circ$ C におりません。であるは、 $16^\circ$ C におりません。でありませんの熱サイクルによって行われます

Note 10:入力換算值。

特に指定のない限り、TA = 25℃、VS = ±15V、VCM = VREF1 = VREF2 = 0V、VCLLO = VT、VCLHI = VT、RL = 4k。

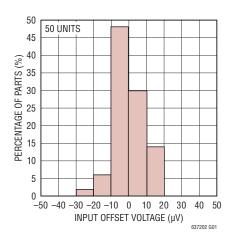

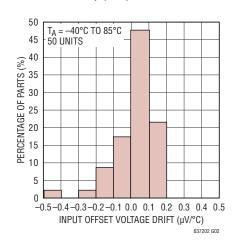

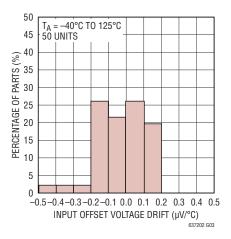

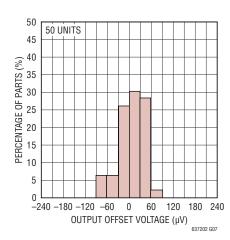

#### 入力オフセット電圧の分布、 MS16Eパッケージ

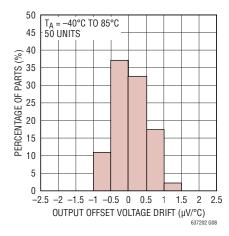

#### 入力オフセット電圧ドリフトの分布、 MS16Eパッケージ

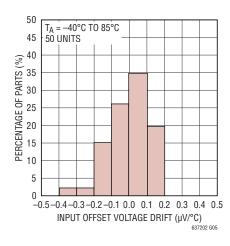

入力オフセット電圧ドリフトの分布、 MS16Eパッケージ

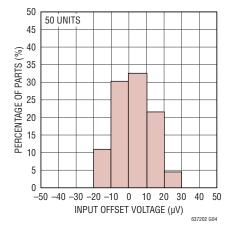

入力オフセット電圧の分布、 QFNパッケージ

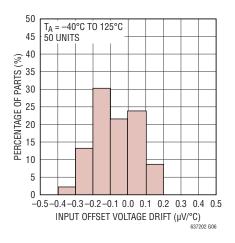

入力オフセット電圧ドリフトの分布、 QFNパッケージ

入力オフセット電圧ドリフトの分布、 QFNパッケージ

#### 出力オフセット電圧の分布、 MS16Eパッケージ

出力オフセット電圧ドリフトの分布、 MS16E パッケージ

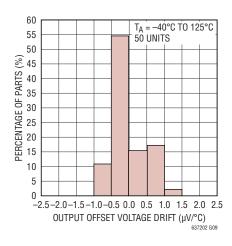

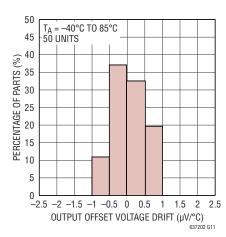

#### 出力オフセット電圧ドリフトの分布、 MS16Eパッケージ

Rev. 0

6

詳細: www.analog.com

特に指定のない限り、TA = 25°C、VS = ±15V、VCM = VREF1 = VREF2 = 0V、VCLLO = VT、VCLHI = VT、RL = 4k。

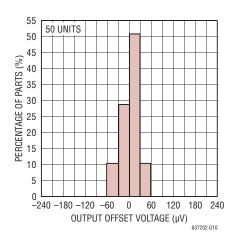

#### 出力オフセット電圧の分布、 QFNパッケージ

#### 出力オフセット電圧ドリフトの分布、 QFNパッケージ

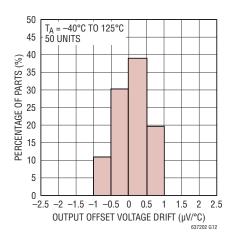

#### 出力オフセット電圧ドリフトの分布、 QFNパッケージ

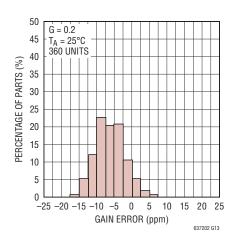

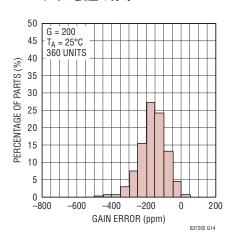

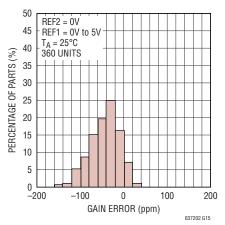

#### ゲイン誤差の分布

ゲイン誤差の分布

#### REF 分圧ゲイン誤差の分布

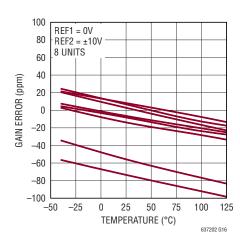

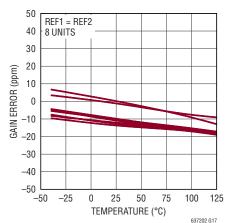

#### REF 分圧器ゲイン・ドリフト

### REF ゲイン・ドリフト

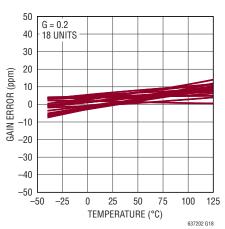

#### ゲイン・ドリフト(G=0.2)

Rev. 0

特に指定のない限り、TA = 25℃、VS = ±15V、VCM = VREF1 = VREF2 = 0V、VCLLO = VT、VCLHI = VT、RL = 4k。

IRリフローによる鉛フリー・

15  $V_{OUT} = 0V \text{ to } 5V$  $V_{REF1} = V_{CLLO} = 0V$ 10 V<sub>REF2</sub> = V<sub>CLHI</sub> = 5V GAIN NONLINEARITY (ppm) 5 0 -5 -15 0 0.5 1.5 2 2.5 3 3.5 4.5 OUTPUT VOLTAGE (V)

ゲイン非直線性(G=1)

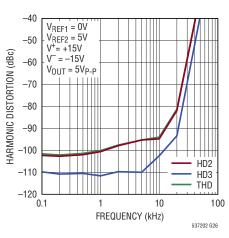

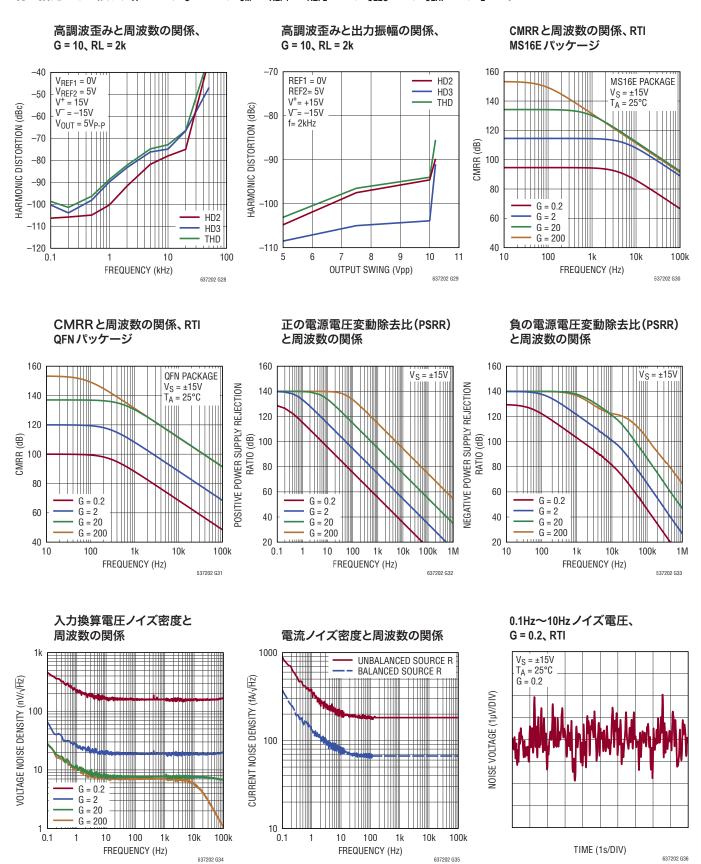

高調波歪みと周波数の関係、

G = 0.25, RL = 2k

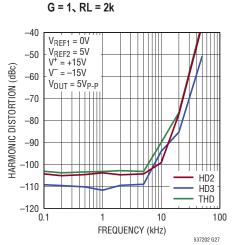

高調波歪みと周波数の関係、

Rev. 0

**3** 詳細:www.analog.com

特に指定のない限り、T<sub>A</sub> = 25℃、V<sub>S</sub> = ±15V、V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V、V<sub>CLLO</sub> = V<sup>-</sup>、V<sub>CLHI</sub> = V<sup>+</sup>、R<sub>L</sub> = 4k。

Rev. 0

特に指定のない限り、TA = 25℃、VS = ±15V、VCM = VREF1 = VREF2 = 0V、VCLLO = VT、VCLHI = VT、RL = 4k。

0.1Hz~10Hzノイズ電圧、 0.1Hz~10Hzノイズ電圧、G = 20、RTI G = 200, RTI 0.1Hz~10Hzノイズ電圧、G=2、RTI  $V_S = \pm 15V$  $V_S = \pm 15V$  $V_S = \pm 15V$ T<sub>A</sub> = 25°C G = 2 T<sub>A</sub> = 25°C G = 20  $T_A = 25^{\circ}C$  G = 200NOISE VOLTAGE (100nV/DIV) NOISE VOLTAGE (50nV/DIV) NOISE VOLTAGE (50nV/DIV) TIME (1s/DIV) TIME (1s/DIV) TIME (1s/DIV) 637202 G37 637202 G38 637202 G39 REFピン電流と 0.1Hz~10Hzノイズ電流、 0.1Hz~10Hzノイズ電流、 平衡ソースR 入力コモン・モード電圧の関係 不平衡ソースR 1600 BALANCED SOURCE R UNBALANCED SOURCE R --- T<sub>A</sub> = 125°C  $V_S = \pm 15V$  $T_A = 25^{\circ}C$  $V_S = \pm 15V$   $T_A = 25$ °C  $T_A = 85^{\circ}C$ 1200  $T_A = 25$ °C NOISE CURRENT (500fA/DIV)  $- - T_A = -40^{\circ}C$ NOISE CURRENT (1pA/DIV) 800 REF PIN CURRENT (µA) 400 0 -400 -800 -1200-1600-10-5 0 5 COMMON-MODE INPUT VOLTAGE (V)

6370 G42 TIME (1s/DIV) TIME (1s/DIV) 637202 G40 637202 G41 入力バイアス電流と 入力バイアス電流および コモン・モード電圧の関係 オフセット電流と温度の関係 電源電流と電源電圧の関係 1.0 1.0 3.0 0.8 0.8 BIAS, OFFSET CURRENTS (nA) OFFSET CURRENTS (nA) 2.5 0.6 0.6 SUPPLY CURRENT (mA) 0.4 0.4 2.0 0.2 0.2 0.0 0.0 1.5 -0.2 -0.2

Rev. 0

637202 G45

$T_A = 125$ °C

$T_A = 85^{\circ}C$

$T_A = 25^{\circ}C$

$- - - T_A = -40^{\circ}C$

30 35 40

-0.4

-0.8

-1.0\_15

-10

-5

0

INPUT COMMON-MODE VOLTAGE (V)

637202 G43

INPUT -0.6

25

TEMPERATURE (°C)

1.0

0.5

0

5 10 15 20

SUPPLY VOLTAGE (V)

+IN BIAS CURRENT

-IN BIAS CURRENT

OFFSET CURRENT

637202 G44

75 100 125

INPUT BIAS,

+IN BIAS CURRENT

-IN BIAS CURRENT

OFFSET CURRENT

-0.4

-0.6

-0.8

<del>-</del>50

-25

特に指定のない限り、TA = 25℃、VS = ±15V、VCM = VREF1 = VREF2 = 0V、VCLLO = VT、VCLHI = VT、RL = 4k。

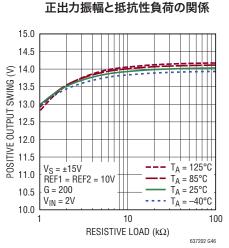

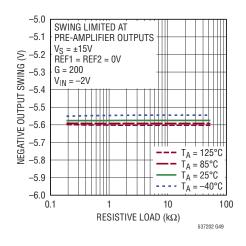

負出力振幅と抵抗性負荷の関係

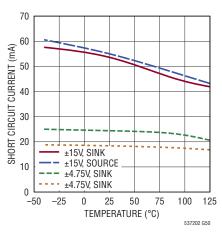

短絡電流と温度の関係

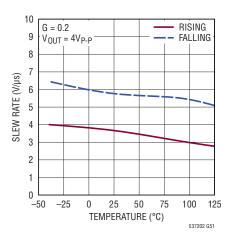

スルー・レートと温度の関係

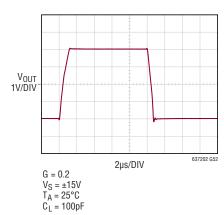

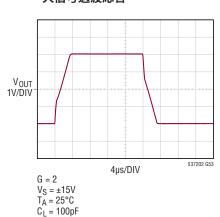

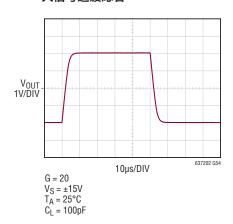

大信号過渡応答

大信号過渡応答

#### 大信号過渡応答

Rev. 0

特に指定のない限り、TA=25℃、VS=±15V、VCM=VREF1=VREF2=0V、VCLLO=VT、VCLHI=VT、RL=4k。

Rev. 0

12 詳細:www.analog.com

### ピン機能 (MS16E/QFN20)

$-R_{G,F}$ (ピン1/ピン19): 外付けのゲイン設定抵抗と共に使用します。このピンをゲイン設定抵抗へ接続する際の配線は、ゲイン誤差を最小限に抑えるために、 $-R_{G,S}$ からの配線とは別にする必要があります。

$-R_{G,S}(\mathcal{L}')$ 2/ $\mathcal{L}'$ 20): 外付けのゲイン設定抵抗と共に使用します。このピンをゲイン設定抵抗へ接続する際の配線は、ゲイン誤差を最小限に抑えるために、 $-R_{G,F}$ からの配線とは別にする必要があります。

**-IN(ピン4/ピン2)**:負の入力端子。この入力は高インピーダンスです。

**+IN (ピン5/ピン5):**正の入力端子。この入力は高インピーダンスです。

CLLO(ピン7/ピン8):ローサイド・クランプ入力。CLLOピンに加わる電圧は、出力の下限電圧を決定します。通常、出力は、CLLOピンに加わる電圧より500mV低い値にクランプされます。CLLOはフロート状態にしないでください。

**V (ピン8/ピン7)**: 負側電源。電源ピンとグラウンドの間に、バイパス・コンデンサを1個使用する必要があります。

**CLHI(ピン9/ピン10)**:ハイサイド・クランプ入力。CLHIピンに加わる電圧は、出力の上限電圧を決定します。通常、出力は、CLHIピンに加わる電圧より500mV高い値にクランプされます。CLHIはフロート状態にしないでください。

**REF1 (ピン10/ピン12)**:出力電圧のリファレンス。REF1 は、REF2に接続して出力のリファレンスとして使用できます。 REF1 は、REF2と共に使用して分圧器を構成し、出力をレベル・シフトさせることもできます。

OUTPUT(ピン11/ピン13): REFピンの出力電圧リファレンス。

**V<sup>+</sup>(ピン12/ピン14):**正側電源。電源ピンとグラウンドの間に、バイパス・コンデンサを1個使用する必要があります。

**REF2 (ピン13/ピン15)**:出力電圧のリファレンス。REF2 は、REF1 に接続して出力のリファレンスとして使用できます。 REF2 は、REF1 と共に使用して分圧器を構成し、出力をレベル・シフトさせることもできます。

$+R_{G,S}$  (ピン15/ピン17): 外付けのゲイン設定抵抗と共に使用します。このピンをゲイン設定抵抗へ接続する際の配線は、ゲイン誤差を最小限に抑えるために、 $+R_{G,F}$ からの配線とは別にする必要があります。

+RG,F(ピン16/ピン18):外付けのゲイン設定抵抗と共に使用します。このピンをゲイン設定抵抗へ接続する際の配線は、ゲイン誤差を最小限に抑えるために、+RG,Sからの配線とは別にする必要があります。

NIC(ピン3、6、14/ピン1、3、4、6、11、16):内部接続なし。

**DNC (QFN ピン9)**:接続なし。このピンはフロート状態にしてください。

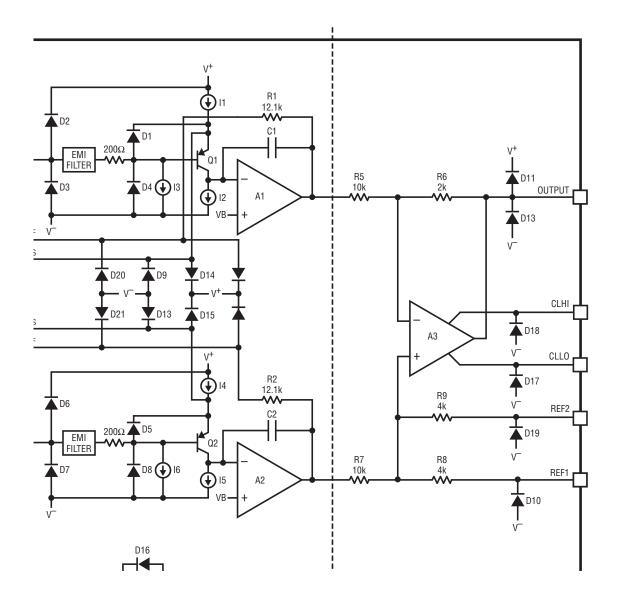

## 簡略化したブロック図

### 動作原理

LT6372-0.2は、3個のオペアンプを使った従来の計装アン プ・トポロジを改良したもので、精度を向上させ、ADCとの インターフェースを簡素化する機能が組み込まれています。 レーザー・トリミングと固有のモノリシック構造によって、指 定温度範囲全体を通じて回路パラメータの緊密なマッチン グと超低ドリフトが実現されています。簡略化したブロック 図を参照してください。この図は、以下に示す回路の説明を 理解する助けとなります。Q1とQ2のコレクタ電流、およびI1 とI4は、入力オフセット電圧ドリフトを最小限に抑えるために トリミングされているので、高レベルの性能が確保されてい ます。R1とR2は、1個の外付け抵抗RGだけを使ってゲイン を正確に設定できるように(G=100で0.15%)、12.1kの絶対 値にトリミングされています。RGの値は、プリアンプ段のトラ ンスコンダクタンスを決定します。RGを小さくして設定ゲイン を大きくすると、入力プリアンプ段のランスコンダクタンスも 増加し、入力トランジスタQ1とQ2のトランスコンダクタンスと 同じ値になります。このため、設定ゲインが増加するとオープ ンループ・ゲインが増加し、入力に関係する誤差とノイズが 減少します。高ゲイン時の入力電圧ノイズは、Q1とQ2のみに よって決まります。低ゲイン時は、ディファレンス・アンプとプ リアンプ・ゲイン設定抵抗のノイズによって、ノイズが増加す ることがあります。ゲイン帯域幅積はC1、C2、およびプリアン プのトランスコンダクタンスによって決まり、トランスコンダク タンスは設定ゲインに応じて増加します。したがって帯域幅 は自動的に調整され、ゲインに比例して減少することはあり ません。

入力トランジスタQ1とQ2は優れたマッチング性能、ドリフト性能、ノイズ性能を発揮しますが、これらの性能は、独自の高性能プロセスを使用していることと、入力デバイスの高いベータ( $\beta$ )が実現する低入力バイアス電流によって実現されています。入力バイアス電流は、I3とI6をトリミングすることによって更に減少します。I3とI6をトリミングすることによって更に減少します。I3とI6をトリミングすることによって更に減少します。I5000年間にたフィードバックによって一定に保たれます。I500年間によって、外付けのゲイン設定抵抗I50年間に表面で、その比に応じて次式に示すゲインで増幅された差動電圧が生じ、

$$G = 1 + \frac{R1 + R2}{R_G}$$

これがディファレンス・アンプ A3に加わります。ディファレンス・アンプはコモン・モード電圧を除去して、REF1とREF2の電圧の平均を基準とするシングルエンド出力電圧を供給します。この分割リファレンス抵抗構成では、外付け部品を使用することなく、出力電圧をADC入力範囲の中央まで容易にレベル・シフトすることが可能です。ディファレンス・アンプのオフセット電圧は出力オフセット電圧ドリフトが最小限となるようにトリムされるので、低ゲイン時でも高い性能を確保することができます。抵抗R5~R9は、最大限のCMRRを実現してゲイン誤差を最小限に抑えるためにトリムされます。最終的に得られるゲインの式を下に示します。

$$G = 0.2 \left( 1 + \frac{24.2k}{R_G} \right)$$

この式をゲイン設定抵抗について解くと、次のようになります。

$$R_G = \frac{24.2k}{5G-1}$$

様々なゲインに適した1%抵抗を表1に示します。

表1. LT6372-0.2のゲインとRGの対応表

| Resulting Gains for Various 1% Standard Resistor Values |                                |  |

|---------------------------------------------------------|--------------------------------|--|

| Gain                                                    | Standard 1% Resistor Value (Ω) |  |

| 0.2                                                     | -                              |  |

| 0.399                                                   | 24.3k                          |  |

| 0.499                                                   | 16.2k                          |  |

| 0.8                                                     | 8.06k                          |  |

| 1.001                                                   | 6.04k                          |  |

| 2.013                                                   | 2.67k                          |  |

| 5.04                                                    | 1k                             |  |

| 9.9                                                     | 499                            |  |

| 20.12                                                   | 243                            |  |

| 49.79                                                   | 97.6                           |  |

| 99.58                                                   | 48.7                           |  |

| 199.4                                                   | 24.3                           |  |

| 496.1                                                   | 9.76                           |  |

| 994                                                     | 4.87                           |  |

更に、LT6372-0.2は出力電圧クランプ回路を2つ内蔵しています。これらの回路は、ADCの入力に加わる電圧を制限するために使用できます。通常、CLHIはADCのリファレンスに接続し、CLLOはADCのグラウンドに接続します。

#### 有効な入出力範囲

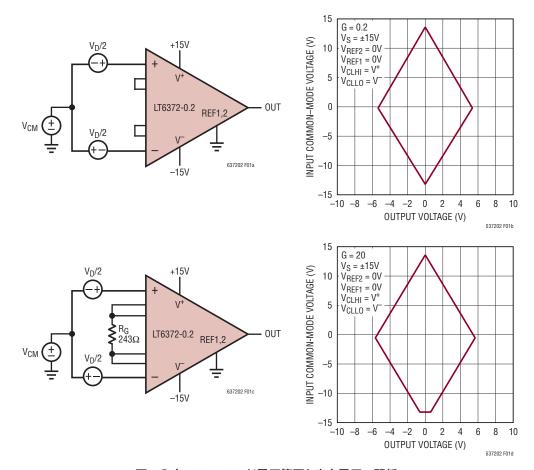

従来、計装アンプでは、有効な入力コモン・モード電圧範囲と出力振幅範囲の仕様を規定しています。しかしこのために、内部的な振幅限界に関連する制限を確認できないことがよくあります。簡略化したブロック図を見ると、プリアンプA1とA2の出力振幅、およびディファレンス・アンプA3のコ

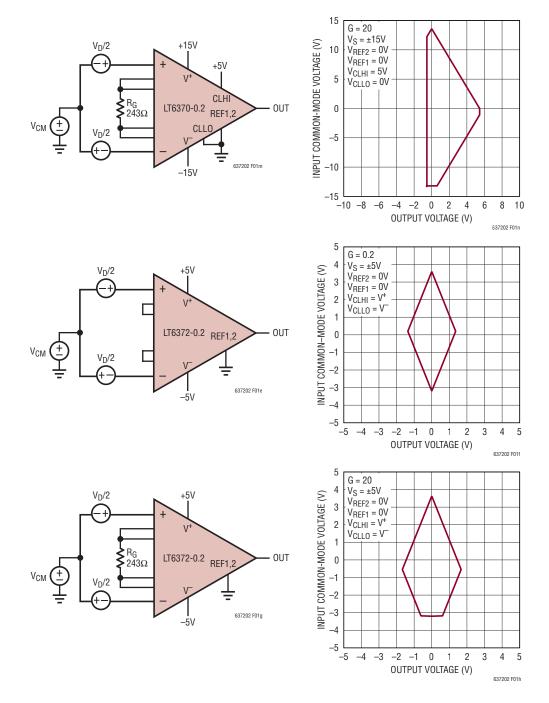

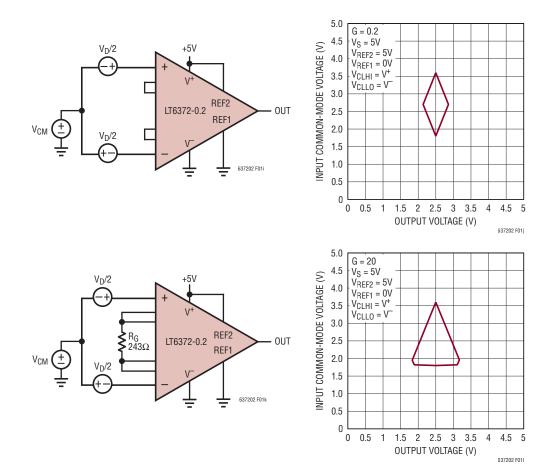

モン・モード入力範囲が、有効動作範囲を制限しています。 図1は動作範囲を示したものですが、生成される有効出力 は構成条件によって様々に異なります。ここに示す以外の有 効入出力範囲のプロットは、ダイヤモンド・プロット・ツール を使って作成できます。

図1. 入力コモン・モード電圧範囲と出力電圧の関係

図1. 入力コモン・モード電圧範囲と出力電圧の関係(続き)

図1. 入力コモン・モード電圧範囲と出力電圧の関係(続き)

Rev. 0

18

詳細:www.analog.com

#### 分割リファレンス・ピンによる出力レベル・シフト

LT6372-0.2のディファレンス・アンプは分割リファレンス・ピンREF1とREF2を備えており、これを使うことで、外付け回路を使うことなく、出力のレベルを容易に、しかも正確にシフトさせることができます。通常、REF1はADCのグラウンドに接続し、REF2はADCのリファレンスに接続します。この構成では、ADC入力範囲の中央という都合の良い位置までアンプ出力がレベル・シフトされます。

REF1とREF2を互いに短絡させると、従来の計装アンプ同様に、出力電圧のリファレンスとしてこれらのピンを機能させることができます。

CMRRとゲインの性能を維持するには、REF1とREF2に直列の寄生抵抗を最小限に抑える必要があります。また、REF1とREF2の駆動に使用するすべての回路のドリフトは、追加的な出力ドリフト要素となり得るという点に注意することも重要です。したがって、REFピンの駆動に使用する回路の温度精度を考慮することが大切です。

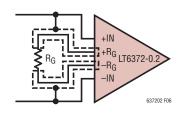

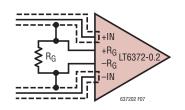

### ゲイン設定抵抗の接続

各プリアンプは一連のRG接続端子を備えており、これらの端子は、ゲイン設定抵抗まで個別に配線する必要があります。これにより、寄生パターン抵抗とリード抵抗がゲイン精度に与える影響が最小限に抑えられます。ゲイン設定抵抗への配線時は、大きいループを避ける必要があります。ループが大きいと、アンプにノイズが混入するおそれがあるからです。

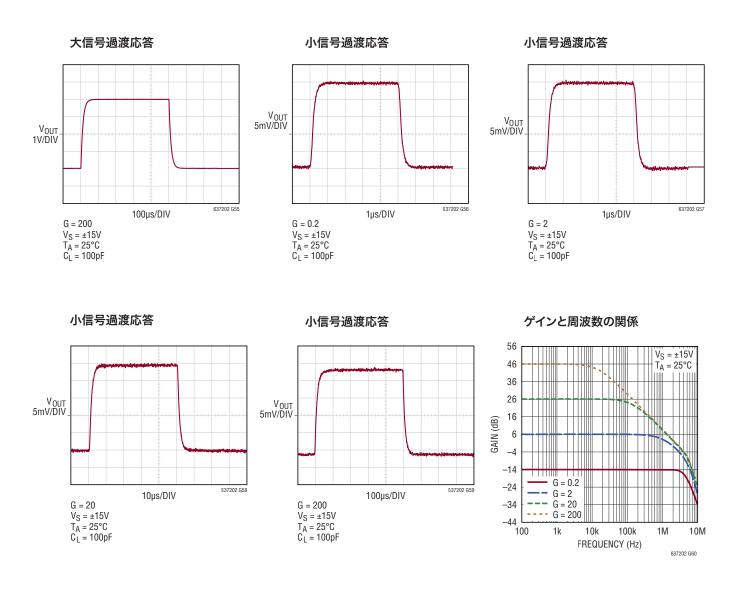

#### 出力クランプ

CLHIおよびCLLOクランプ・ピンは、LT6372-0.2の出力電 圧振幅を制限します。通常、CLHIはADCの電源/リファレンスに接続し、CLLOはADCのグラウンドに接続します。 この場合、LT6372-0.2はより高い電源電圧を生成する可能 性があるので、これによるオーバードライブを避けるために、 ADC入力は保護されます。

CLLOを0Vに接続すると、出力を0V未満に駆動しようとしても通常は-0.45Vにクランプされます。また、CLHIを5Vに接続すると、通常は、出力を5Vより高い値に駆動しようとしても5.45Vにクランプされます。

CLHIとCLLOは高インピーダンス入力で、クランプ時に大量の電流が流れることはありません。逆にCLHIとCLLOが内部アンプ・ノードを制御して、出力電圧を制限します。

クランピングの必要がないアプリケーションでは、CLLOをVに接続し、CLHIをV<sup>+</sup>に接続して、クランピングをディスエーブルします。

#### 入出力のオフセット電圧

LT6372-0.2のオフセット電圧は主に2つの成分で構成されます。入力アンプによる入力オフセット電圧と、出力アンプによる出力オフセット電圧です。入力に換算した(RTI)総オフセット電圧は、出力オフセットを設定ゲインで割り、それを入力オフセット電圧に加えることによって得られます。高ゲイン時には入力オフセット電圧が支配的ですが、低ゲイン時には出力オフセット電圧が支配的になります。総オフセット電は以下のようになります。

総入力オフセット電圧(RTI) = V<sub>OSI</sub> + V<sub>OSO</sub>/G

総出力オフセット電圧(RTO) = V<sub>OSI</sub> • G + V<sub>OSO</sub>

上の式は、同様の方法でオフセット・ドリフトを計算する場合も使用できます。

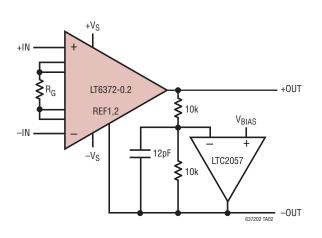

#### 出力オフセットのトリミング

LT6372-0.2は、オフセット電圧が小さくなるようにレーザー・トリミングされているので、ほとんどのアプリケーションでは外部的なオフセット・トリミングは必要ありません。オフセット電圧を調節する必要がある場合のオプションのオフセット調節回路の一例を、図2に示します。オペアンプのバッファは、最大限のCMRRと最小限のゲイン誤差を実現するために、低インピーダンスの信号をREFピンに供給します。

図2. 出力オフセット電圧のオプションのトリミング

#### 熱電対の影響

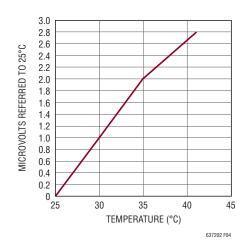

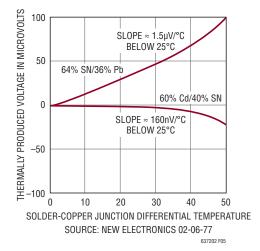

μVレベルの精度を実現するには、熱電対の影響を考慮する必要があります。異種金属を接続すると熱電接点が形成され、温度に応じてわずかな電圧が発生します。ゼーベック

効果とも呼ばれるこれらの熱起電力は、低ドリフト回路の支配的な誤差源となり得ます。

コネクタ、スイッチ、リレーの接点、ソケット、抵抗、およびハンダは、いずれも大きな熱起電力を発生させる可能性があります。異なるメーカーの銅線を接合するだけでも200nV/℃の熱起電力が発生することがありますが、これはLT6372-0.2で仕様規定された最大入力オフセット電圧ドリフトに匹敵します。このように熱起電力によって発生する電圧と、その温度に対する感度を図3と図4に示します。

熱電対による誤差を最小限に抑えるには、回路基板のレイアウトと部品の選定に注意を払う必要があります。アンプ入力とRG信号パス内の接点数を最小限に抑え、できるだけコネクタ、ソケット、スイッチ、およびリレーの使用を避けることを推奨します。これらの部品が必要な場合は、熱起電力が低い特性の部品を選定するようにしてください。更に、両入力の接合部の数、タイプ、レイアウトを、回路基板上の熱勾配の観点から揃える必要があります。これを実現するには、避けられない接合点の数を合わせるために、ダミーの接合点を設けなければならないことがあります。

空気の流れも熱勾配を生じさせて、測定システムで大きなノイズを発生させる可能性があります。影響を受けやすい複数の回路にまたがる気流をなくすことが重要です。そうすることによって熱電対ノイズが大幅に減少することも少なくありません。PCB入力パターンを互いに近付けて配線し、PCBの1つの内層上にまとめると、入力パターンの熱表面積と反応する空気流によって生じる温度差を最小限に抑える助けとなります。

図3.メーカーが異なる2本の銅線によって生じる熱起電力

図4. ハンダと銅の接合点に生じる熱起電力

#### 基板に関連するもれ電流の影響の低減

もれ電流はシステムの精度に大きく影響することがあり、これは高温および高電圧のアプリケーションで特に顕著です。高品質の絶縁材料を使用し、絶縁表面はフラックスその他の残留物を除去してクリーンな状態に保つ必要があります。湿度の高い環境では、表面にコーティングを施して防湿層を形成しなければならないことがあります。

RGピンに流れるもれ電流が内蔵の帰還抵抗に流れると、プリアンプの出力に誤差が生じます。この誤差はゲインと無関係で、ゲインが低いときに最も大きく精度を低下させます。このもれ電流は、 $R_G$ ピンの電位に非常に近い電位で動作するガード・リングで $R_G$ の接続点を囲むことにより、最小限に抑えることができます。各 $R_G$ ピンに隣接するNICピンを使用すれば、このガード・リングの実装が容易になります。これらのNICピンにバイアスはなく、内部接続もされていません。場合によっては、 $R_G$ よりダイオード1個分低い値にバイアスする入力電圧にガード・リングを接続することもできます。

図5. ガード・リングを使用してRGピンへのもれ電流を 最小限に抑えることが可能

入力ピンへのもれ電流はソース抵抗に作用して、入力に直接誤差を発生させます。このもれ電流は、入力ピンの電位に非常に近い電位で動作するガード・リングで入力接続を囲むことにより、最小限に抑えることができます。場合によっては、入力よりダイオード1個分高い値にバイアスするRGにガード・リングを接続することもできます。強制および検出RG接続を図5と図6に示します。これらの図は、単純化するために単一RG接続として示しています。

もれ電流を最小限に抑えるために、アンプを使用してガード・リングを駆動することができます。これらのバッファの入力バイアス電流はもれ電流となるので、非常に小さい値に抑える必要があります。

図 6. ガード・リングを使用して入力ピンへのもれ電流を 最小限に抑えることが可能

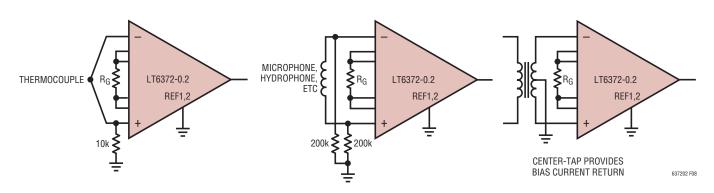

#### 入力バイアス電流のリターン・パス

LT6372-0.2は入力バイアス電流が小さく(最大800pA)入 カインピーダンスが大きいので(225GΩ)、最大限のコモン・ モード電圧範囲が必要とされる場合でも、余分なオフセット 電圧誤差を発生させることなく高インピーダンス源を使用 できます。ただし、完全差動信号を増幅する場合は、両方の 入力に入力バイアス電流用のパスを用意する必要がありま す。このパスがないと、どちらのレールに対してもフロート状 態となり、LT6372-0.2の入力コモン・モード電圧範囲を超え て、入力アンプが飽和する結果となります。入力バイアス電 流パスの3つの例を図7に示します。最初の例は完全差動信 号源を使用しており、10kΩの入力電流パスがグラウンドに 接続されています。信号源のインピーダンスが小さいので、 必要な抵抗は1個だけです。2番目の例に示すように、信号 源のインピーダンスが高い場合は2つのマッチング抵抗が 必要です。入力インピーダンスのバランスを取ると、ACおよ びDC同相ノイズ除去性能とDCオフセット性能が共に向上 します。3番目の例に示すように、センター・タップがある場合 は入力抵抗が不要になります。

図7. 入力コモン・モード電流パスの構成

Rev. (

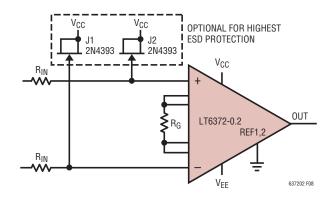

#### 入力保護

各入力と直列に外付け抵抗を追加すれば、入力保護機能を強化できます。値の小さい抵抗が必要な場合は、正電源と各入力の間にクランプ・ダイオードを配置すれば、堅牢性を向上させる助けとなります。2N4394のドレイン/ソースとゲートの間は良好な低もれ電流性能を持つダイオードで、図8に示すように使用できます。炭素複合材料やバルク金属箔などを使用した堅牢な入力抵抗を選択します。金属皮膜抵抗や炭素被膜抵抗は、性能が良くないので使用しないでください。

図8.入力保護

#### AC CMRRの維持

最適なAC CMRRを実現するには、R<sub>G</sub>ゲイン設定ピンの容量バランスをとることが重要です。更に、各入力の信号源抵抗が等しくない場合は、一方の入力に抵抗を追加して入力信号源抵抗のマッチングを改善すると、AC CMRRを改善できます。

#### RFIの低減/内蔵 RFIフィルタ

LT6372-0.2は、多くの産業用アプリケーションやデータ・アクイジション・アプリケーションで、大きなコモン・モード電圧やノイズのある環境で小信号を正確に増幅するために使われます。通常、これらの微小信号(µVまたはmV単位)の発生源はセンサーであり、シグナル・コンディショニング回路からの距離がかなり長いことがあります。これらのセンサーは、シールド付きまたはシールドなしのツイストペア・ケーブルを使用してシグナル・コンディショニング回路に接続できますが、ケーブルがアンテナとして動作して、超高周波の干渉ノイズがLT6372-0.2の入力段に直接伝達される可能性があります。

干渉ノイズの振幅と周波数は、計装アンプの入力オフセット電圧に対して不必要なDCシフトを引き起こすことにより、計装アンプの入力段に悪影響を及ぼす可能性があります。この広く知られた影響はRFI整流作用と呼ばれ、帯域外の干渉ノイズが(誘導的または容量的に、あるいは放射によって)結合すると発生し、計装アンプの入力トランジスタによって整流されます。これらのトランジスタは、高周波信号検出器として動作します。これは、初期のラジオ設計において、ダイオードがRFエンベロープ・ディテクタとして使われたのと同じです。干渉の種類や、回路への結合方法とは関係なく、帯域外の誤差信号は計装アンプの入力と直列に現れます。

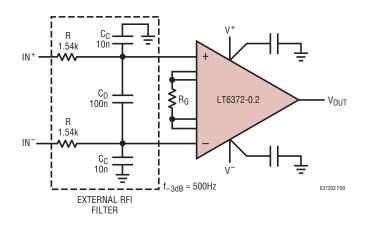

この影響を最小限に抑えるため、LT6372-0.2は50MHzのRFIフィルタを内蔵しています。このフィルタは、高周波信号を減衰して、高周波がデバイスの入力トランジスタと相互干渉せずに済むようにする助けとなります。これらの内蔵フィルタはモノリシック構造のため十分にマッチングが取られており、AC CMRRの低下を最小限に抑えるのに役立ちます。LT6372-0.2の入力オフセット電圧に対するこれらの帯域外信号の影響を低減するため、入力に外付けローパス・フィルタを追加できます。フィルタは回路の入力ピンのすぐ近くに配置してください。効果的なフィルタ構成を図9に示します。この図ではLT6372-0.2の入力に3つのコンデンサが追加されています。

このフィルタは、次式の関係に従って入力信号の帯域幅を制限します。

FilterFreq<sub>DIFF</sub> =

$$\frac{1}{2\pi R(2C_D + C_C)}$$

FilterFreq<sub>CM</sub> =  $\frac{1}{2\pi RC_C}$

ここで、 $C_D \ge 10C_C$ です。

$C_D$ は差動信号に影響し、 $C_C$ は同相信号に影響します。Rと $C_C$ の組み合わせにミスマッチがあると、LT6372-0.2の CMRR は低下します。CMRR 帯域幅性能を意図せずに低下させてしまうことがないように、 $C_C$ は、 $C_D$ より少なくとも1 桁以上小さくするようにしてください。 $C_C$ のミスマッチの影響は、 $C_D$ : $C_C$ の比を大きくすれば軽減できます。

Rev. 0

図9. シンプルな外付けRCフィルタを計装アンプの入力に追加すると高周波の帯域外信号の整流を更に減らすのに効果的

同相信号から差動信号への変換の可能性をなくすために、 各入力の同相ローパス・フィルタのマッチング精度を1%以 内にします。フィルタの適切な値を決めるのに有効な手順 を、以下に示します。 1. R と  $C_D$ を選択し、次式を使って、ローパス極の周波数が、最も周波数の高い対象信号の10倍以上高い周波数(例:50Hz信号の場合は500Hz)となるようにします。

FilterFreq<sub>DIFF</sub> =

$$\frac{1}{2\pi R(2C_D + C_C)}$$

$$= \frac{1}{2\pi R(2C_D + 0.1C_D)}$$

$$= \frac{1}{4.2\pi RC_D}$$

2.  $C_C = C_D/10$ となるように選択してください。

このように実装した場合、同相極周波数は、差動極周波数より約20倍高い位置になります。図9に示す値での差動および同相ローパス極周波数は、次のようになります。

$FilterFreq_{DIFF} = 500Hz$

$FilterFreq_{CM} = 10kHz$

#### LT6372-0.2をADCドライバとして使用する場合の利点

LT6372-0.2には、ADCとのインターフェースを従来の計装アンプより改善できる機能がいくつか組み込まれています。多くの場合は、ADCの入力範囲に合わせるために大信号を減衰する必要があります。更に、アンプの出力をADCの入力範囲の中央に合わせるために、レベル・シフトをする必要があることも少なくありません。LT6372-0.2でこれら両方の機能を実行し、高インピーダンスを維持しながらADCの入力に対して保護クランピングを行う場合の例を図10に示します。

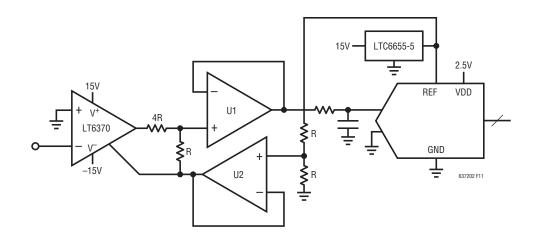

ここで、上述の回路と同機能の回路を考えます(図11)。この回路には、減衰とレベル・シフトを行うために、従来型の計装アンプといくつかの追加的な部品が使われています。出

力とADCリファレンスを減衰するために追加する抵抗分圧器には、初期許容誤差と温度係数に関する性能が優れたものを選択する必要があります。オペアンプの使用は分圧されたリファレンスをバッファするためで、アンプ出力も温度変化に対して高精度の仕様が規定されていなければなりません。この構成でADCを保護するには、U1からの電流をADCと同じにする必要があります。そのためには、U1の入力と出力がレールtoレールでなければなりません。従って選択肢が限られ、ADCの入力範囲によっては対応できない可能性もあります。これらの追加部品は、LT6372-0.2 ソリューションと比較してスペース、消費電力、ノイズ、コストの増加を招き、設計も複雑になります。

図 10. LT6372-0.2 集積化 ADC 駆動ソリューション

図11. 上図と同機能のIA-ADCインターフェース回路

Rev. 0

### 標準的応用例

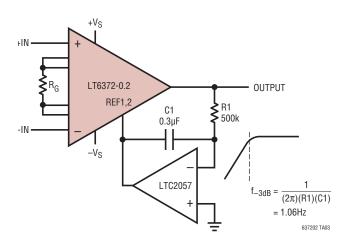

### 差動出力計装アンプ

### AC カップリングした計装アンプ

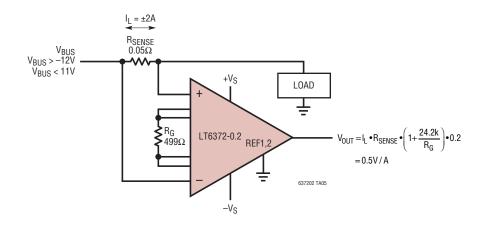

#### 高精度電圧/電流コンバータ

### ハイサイド双方向電流検出

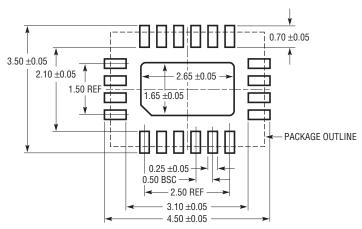

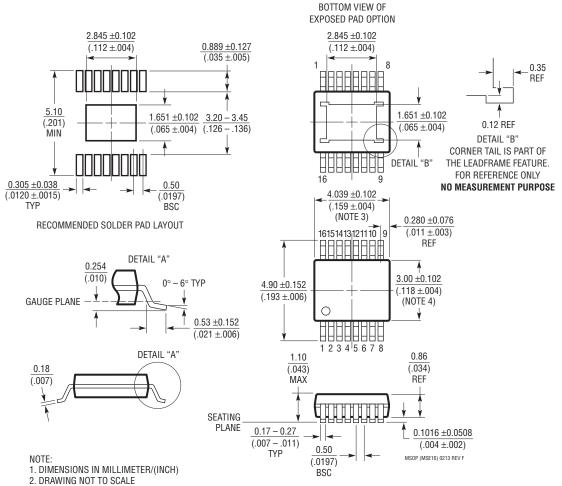

### パッケージ

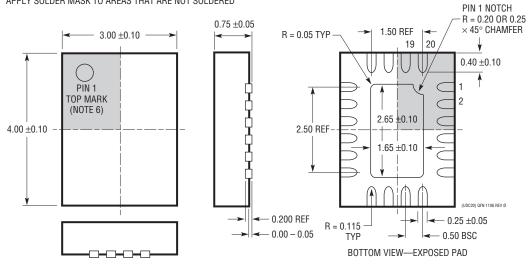

### **UDC** Package 20-Lead Plastic QFN ( $3mm \times 4mm$ )

(Reference LTC DWG # 05-08-1742 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

Rev. 0

### パッケージ

### **MSE Package** 16-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1667 Rev F)

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

### 標準的応用例

#### ゲイン 0.5V/V、1V/V、2V/V、10V/V のプログラマブル・ゲイン・アンプ

### 関連製品

| 製品番号       | 概要               | 注釈                                                                                                                                                                                     |

|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 計装アンプ      |                  |                                                                                                                                                                                        |

| AD8429     | 低ノイズ計装アンプ        | $V_S = 36V, I_S = 6.7 \text{mA}, V_{OS} = 50 \mu\text{V}, BW = 15 \text{MHz}, e_{ni} = 1 \text{nV}/\sqrt{\text{Hz}}, e_{no} = 45 \text{nV}/\sqrt{\text{Hz}}$                           |

| LT6372-1   | 低ドリフト計装アンプ       | 最小ゲインが 1V/V の LT6372-0.2                                                                                                                                                               |

| LT6370     | 低ドリフト計装アンプ       | $V_S = 30 \text{V}, I_S = 2.65 \text{mA}, V_{OS} = 25 \mu \text{V}, BW = 3.1 \text{MHz}, e_{ni} = 7 \text{nV} / \sqrt{\text{Hz}}, e_{no} = 65 \text{nV} / \sqrt{\text{Hz}}$            |

| LTC1100    | ゼロ・ドリフト計装アンプ     | $V_S = 18V$ , $I_S = 2.4$ mA, $V_{OS} = 10\mu V$ , $BW = 19$ kHz, $1.9\mu V_{P-P}$ DC $\sim$ 10Hz                                                                                      |

| AD8421     | 低ノイズ計装アンプ        | $V_S = 36 \text{V}, I_S = 2 \text{mA}, V_{OS} = 25 \mu \text{V}, BW = 10 \text{MHz}, e_{ni} = 3 \text{nV} / \sqrt{\text{Hz}}, e_{no} = 60 \text{nV} / \sqrt{\text{Hz}}$                |

| AD8221     | 低消費電力計装アンプ       | $V_S = 36 \text{V}, I_S = 900 \mu \text{A}, V_{OS} = 25 \mu \text{V}, BW = 825 \text{kHz}, e_{ni} = 8 \text{nV} / \sqrt{\text{Hz}}, e_{no} = 75 \text{nV} / \sqrt{\text{Hz}}$          |

| LT1167     | 計装アンプ            | $V_S = 36V$ , $I_S = 900\mu A$ , $V_{OS} = 40\mu V$ , $BW = 1MHz$ , $e_{ni} = 7.5 nV/\sqrt{Hz}$ , $e_{no} = 67 nV/\sqrt{Hz}$                                                           |

| AD620      | 低消費電力計装アンプ       | $V_S = 36 \text{V}, I_S = 900 \mu \text{A}, V_{OS} = 50 \mu \text{V}, \text{BW} = 1 \text{MHz}, e_{ni} = 9 \text{nV} / \sqrt{\text{Hz}}, e_{no} = 72 \text{nV} / \sqrt{\text{Hz}}$     |

| LTC6800    | RRIO計装アンプ        | $V_S = 5.5V$ , $I_S = 800\mu A$ , $V_{OS} = 100\mu V$ , $BW = 200kHz$ , $2.5\mu V_{P-P}$ DC $\sim$ 10Hz                                                                                |

| LTC2053    | ゼロ・ドリフト計装アンプ     | $V_S = 11V$ , $I_S = 750\mu A$ , $V_{OS} = 10\mu V$ , $BW = 200kHz$ , $2.5\mu V_{P-P} DC \sim 10Hz$                                                                                    |

| LT1168     | 低消費電力計装アンプ       | $V_S = 36 \text{V}, I_S = 350 \mu \text{A}, V_{OS} = 40 \mu \text{V}, \text{BW} = 400 \text{kHz}, e_{ni} = 10 \text{nV} / \sqrt{\text{Hz}}, e_{no} = 165 \text{nV} / \sqrt{\text{Hz}}$ |

| オペアンプ      |                  |                                                                                                                                                                                        |

| LTC2057    | 40Vゼロ・ドリフト・オペアンプ | $V_{OS} = 4\mu V$ , FU7 = 15nV/°C, $I_B = 200 pA$ , $I_S = 900 \mu A$                                                                                                                  |

| A/D コンバータ  |                  |                                                                                                                                                                                        |

| LTC2389-16 | 16ビットSAR ADC     | 2.5Msps、S/N比96dB、162.5mW                                                                                                                                                               |

| LTC2367-16 | 16ビットSAR ADC     | 500ksps、S/N比94.7dB、6.8mW                                                                                                                                                               |