## 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

### 概要

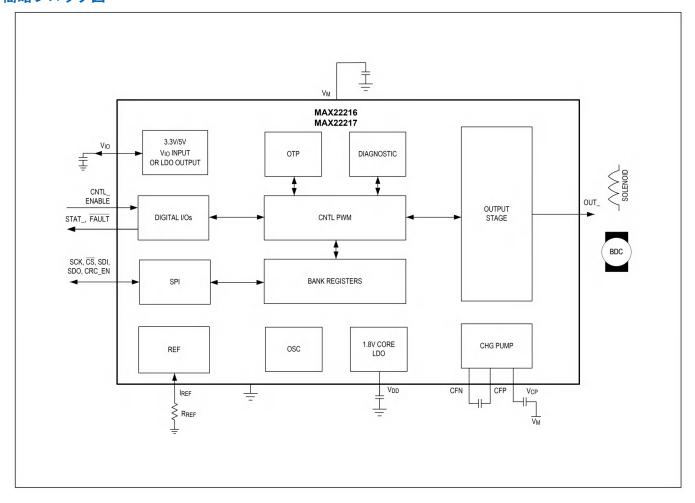

MAX22216/MAX22217 はユーザ設定可能な 36V ハーフブリッジを 4 つ内蔵しています。このデバイスは、主にオンオフ・ソレノイド・バルブ、DC モータ、比例バルブ、双安定バルブ、リレーなどの誘導負荷を駆動することを目的としており、MAX22216 はハーフブリッジあたり最大  $3.2A_{FS}$ 、MAX22217 はハーフブリッジあたり最大  $1A_{FS}$ の電流を供給できます。MAX22216/MAX22217 は $-40^{\circ}$ C~ $+125^{\circ}$ C の周囲温度で動作します。

MAX22216/MAX22217 のハーフブリッジは 2 種類の使用例に対応しています。最初の使用例ではシリアル・ペリフェラル・インタフェース (SPI) 経由で構成設定を入力でき、この設定はいつでも変更可能です。もう 1 つの使用例では、ワンタイム・プログラマブル (OTP) レジスタに設定を保存して、起動時にロードできます。これにより、スタンドアロン動作が可能になります。レジスタはユーザが設定できます。OTP 書込み手順は、温度や電圧の条件が適切に制御されている工場で実行する必要があります。

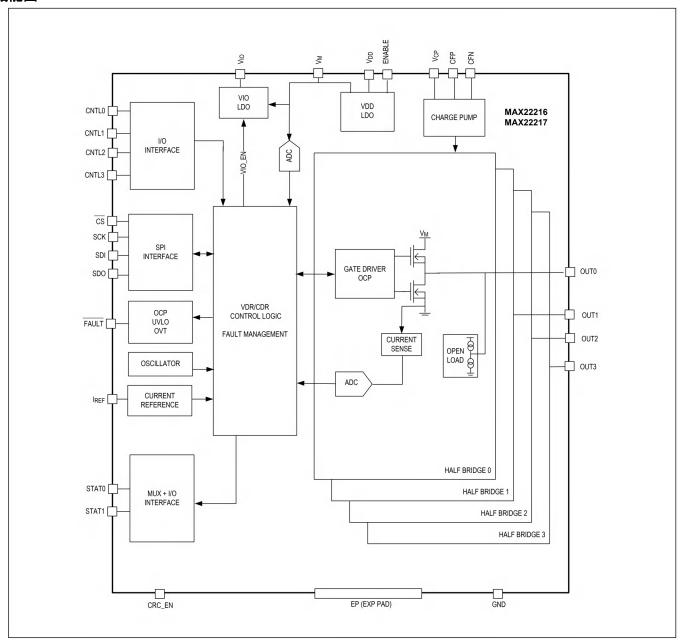

ハイサイド/ローサイドのシングルエンド駆動動作構成と、ブリッジ接続負荷(BTL)構成がサポートされています。更にチャンネルの並列化もサポートされている他、電圧制御方式と電流制御方式、および混合方式がサポートされています。

電圧駆動レギュレーション・モード (VDR モード) ではハーフブリッジ出力電圧が制御され、電源の変動は内部で補償されます。

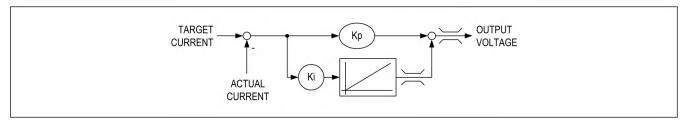

電流駆動レギュレーション・モード (CDR モード)では、ハーフブリッジ出力電流が制御されます。電流は内部で検出されて、コントローラにフィードバックされ、正確なクローズド・ループ・レギュレーションを行います。また、比例ゲインと積分ゲインを設定することで、定常状態の誤差と動的性能を最適化することができます。

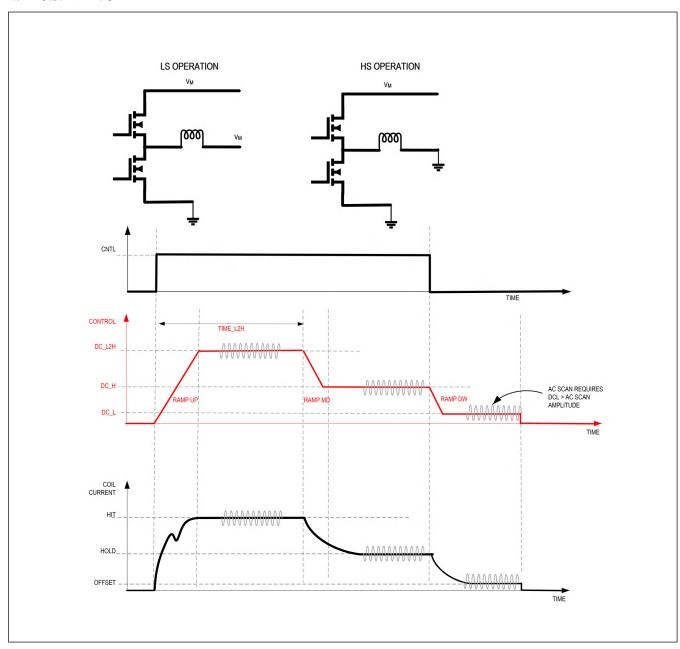

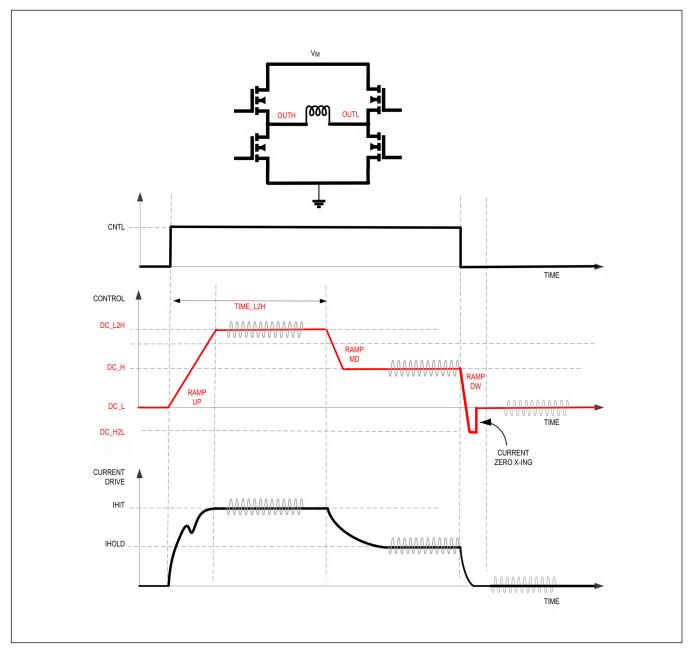

MAX22216/MAX22217 は、ソレノイドと DC モータの駆動制御を最適化するための機能を内蔵しています。これらの機能には、省電力のための 2 レベルのシーケンサ、ノイズ低減のための駆動信号ランプ制御(RAMP)、静止摩擦とヒステリシスの影響をなくすためのディザ機能(DITH)、オンオフ・サイクルを短縮するための高速消磁機能(DC\_H2L)、突入電流とストール電流を制限するための DC モータ電流リミッタなどが含まれています

高度な診断機能を備えているので、システムの信頼性を向上することや、予防保全を行うことが可能です。これらの機能には、プランジャ動作の検出(DPM)、インダクタンス測定、動作時間測定、開放負荷検出(OL)、シリアル・インタフェースを介したリアルタイム電流モニタリングなどが含まれています。

MAX22216/MAX22217 は、過電流保護 (OCP) 、過熱保護 (OVT)、低電圧ロックアウト (UVM) などを含むフルセットの保護回路を備えています。フォルトが検出されるとフォルト・インジケータ・ピンがアサートされます。

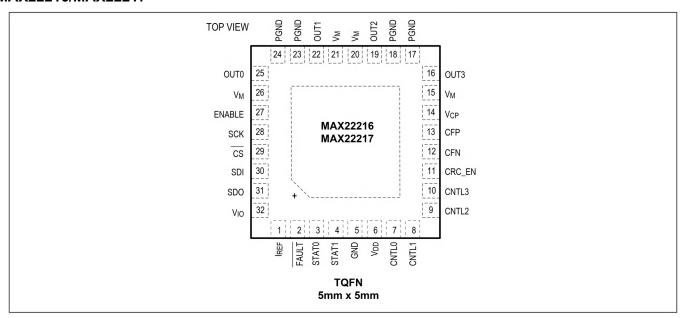

MAX22216/MAX22217 は、TQFN32 5mm × 5mm パッケージで提供されます。

#### アプリケーション

- ソレノイド・オンオフ・バルブおよびリレー

- DC モータ

- 比例バルブ

- 相安定ラッチ・ソレノイド・バルブ

- リアルタイム電流測定機能付きスイッチング・ドライバ

- デジタル出力インタフェース

#### 特長と利点

- シリアル制御の 36V ハーフブリッジを 4 つ内蔵

- 1.7A DC (T<sub>A</sub> = 25°C) および 3.2A フルスケールの 電流能力 (MAX22216)

- 0.55A DC (T<sub>A</sub> = 25°C) および 1A フルスケールの 電流能力 (MAX22217)

- 低 R<sub>ON</sub>、高効率

- 高い柔軟性:

- ・ 独立したチャンネル設定

- ハイサイド/ローサイド/ブリッジ接続負荷構成/ パラレル・モードをサポート

- 高度な制御方法

- ・ 電圧/電流駆動レギュレーション

- ・ 省電力のための 2 レベル・シーケンサ

- 電流リミッタ付き DC モータ・ドライブ

- ディザリング機能

- ランプアップ/ランプダウン制御

- 消磁電圧制御

- 電流検出機能を内蔵

- 診断機能:

- 反応時間と動作時間の測定

- プランジャ動作の検出

- ・ 開放負荷の検出

- インダクタンスの測定

- デジタル電流検出モニタ

- フルセットの保護機能

- 過電流保護

- 過熱保護

- ・ 低電圧ロックアウト

型番はデータシート末尾に記載されています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

### 簡略ブロック図

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

| 目次                                      |    |

|-----------------------------------------|----|

| 概要                                      | 1  |

| アプリケーション                                | 1  |

| 特長と利点                                   | 1  |

| 簡略ブロック図                                 | 2  |

| 絶対最大定格                                  | 8  |

| パッケージ情報                                 | 8  |

| TQFN 32 – 5mm × 5mm                     | 8  |

| 電気的特性                                   | 8  |

| ピン配置                                    | 13 |

| MAX22216/MAX22217                       | 13 |

| 端子説明                                    | 13 |

| 機能図                                     | 15 |

| 機能図                                     | 15 |

| 詳細                                      | 16 |

| 動作モードの概要                                | 17 |

| シングルエンド動作                               | 17 |

| ブリッジ接続負荷動作(フルブリッジ)                      | 19 |

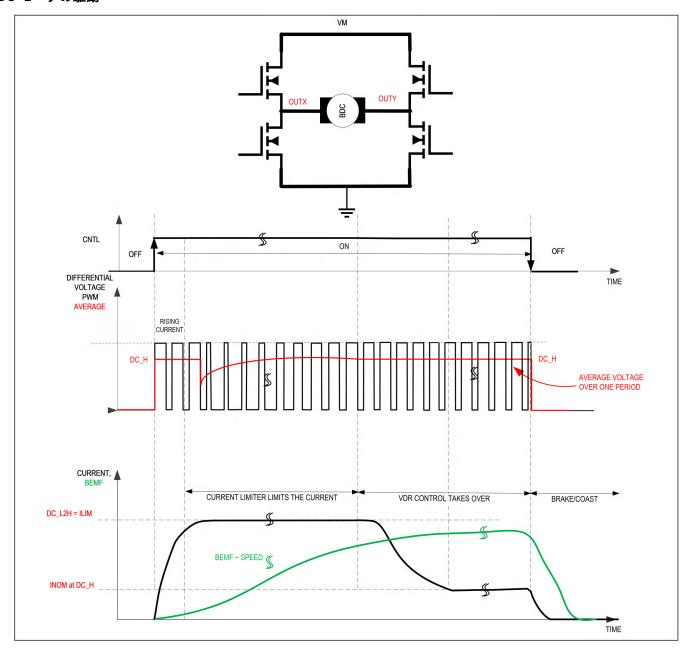

| DC モータの駆動                               | 21 |

| 機能の説明                                   | 22 |

| MAX22216/MAX22217の SPI または OTP 構成       | 22 |

| イネーブル・ロジック入力(ENABLE)                    | 22 |

| ナップ・モードとアクティブ・ビット                       | 22 |

| V <sub>IO</sub> ピンの説明(V <sub>IO</sub> ) | 23 |

| CNTL ピンと CNTL ビット                       | 23 |

| ハードウェア構成                                | 23 |

| HS または LS シングルエンド構成                     | 25 |

| チョッピング周波数と時間ベースの設定                      | 25 |

| スルー・レートとブランキング設定 (SRC)                  | 25 |

| シーケンサの設定                                | 26 |

| シーケンサ制御モードの設定                           | 26 |

| シーケンサ・レベルの設定                            | 27 |

| 電圧駆動レギュレーション (VDR)                      | 27 |

| 電流駆動レギュレーション (CDR)                      | 27 |

| 電流駆動レギュレーション(CDR)                       | 27 |

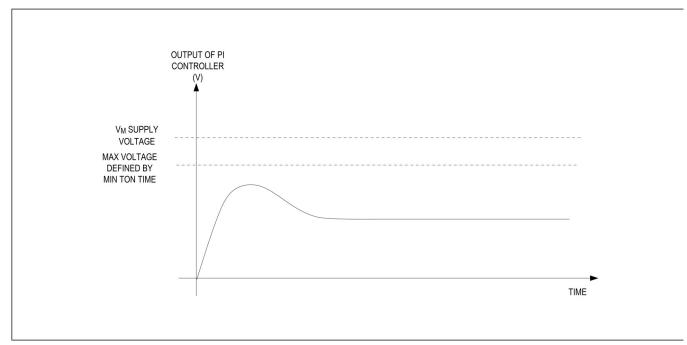

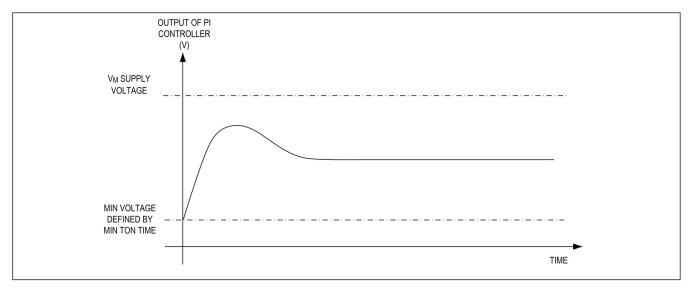

| PI コントローラ                               | 28 |

| 最小 TON に関する制約                           | 29 |

| 電流リファレンス                                | 30 |

| 励磁時間(TIME_L2H)の設定                       | 30 |

| ランプ・スロープの設定                             | 31 |

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

### 目次

| ディザリングまたはインダクタンス測定用にサイン波ジェネレータをイネーブル | 31 |

|--------------------------------------|----|

| サイン波ジェネレータの設定                        | 32 |

| ブレーキ電流リミッタ機能                         | 32 |

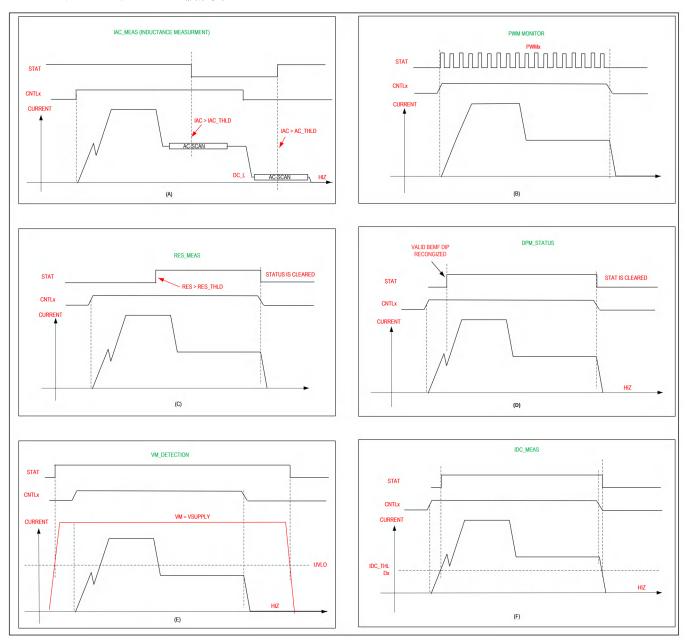

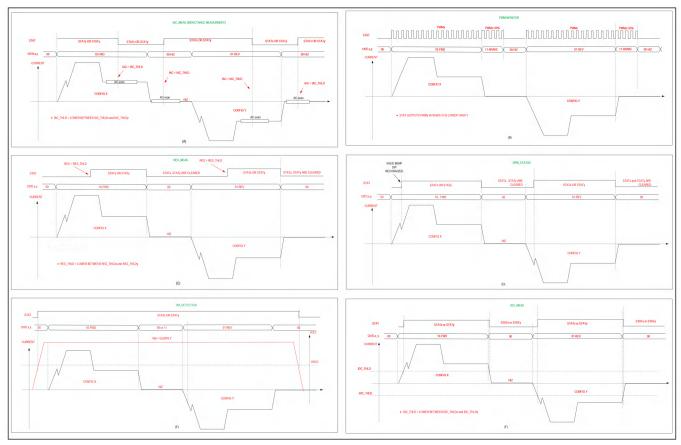

| 診断機能とステータス・モニタ                       | 33 |

| デジタル電流モニタ機能                          | 33 |

| PWM デューティ・サイクルのモニタ機能                 | 34 |

| デジタル V <sub>M</sub> 電源電圧のモニタ         | 34 |

| インダクタンス測定の概要                         | 34 |

| インダクタンス測定の設定                         | 35 |

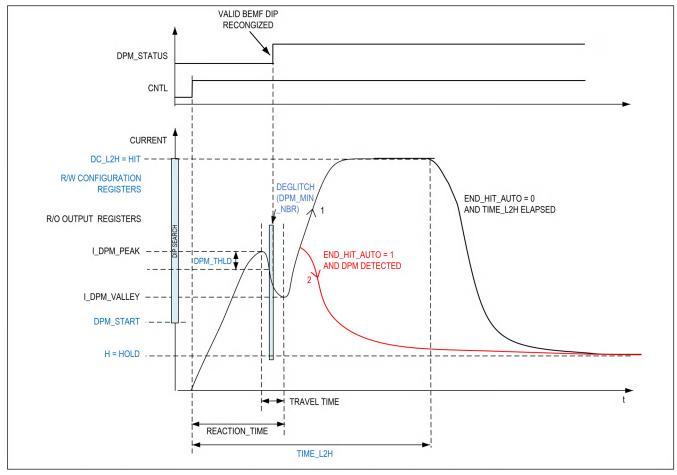

| プランジャ動作の検出(DPM) – 概要                 | 35 |

| プランジャ動作検出の設定                         | 37 |

| 抵抗測定                                 | 38 |

| ステータス・モニタの設定                         | 38 |

| STAT モニタ – シングルエンド波形図                | 41 |

| STAT モニタ – 差動波形図                     | 42 |

| 保護機能とフォルト・インジケータ                     | 42 |

| 保護機能とフォルト・インジケータ・ピン (FAULT)          | 42 |

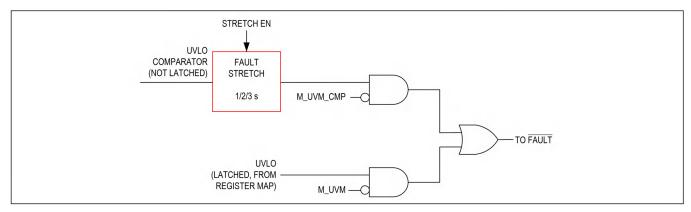

| 低電圧ロックアウト(UVM)                       | 43 |

| 過電流保護(OCP)                           | 44 |

| チャンネル・オフ時の開放負荷検出(OL)                 | 44 |

| 過熱保護(OVT)                            | 44 |

| 「ヒット電流未達」フラグ(HHF)                    | 45 |

| MAX22216/MAX22217 の設定方法              | 45 |

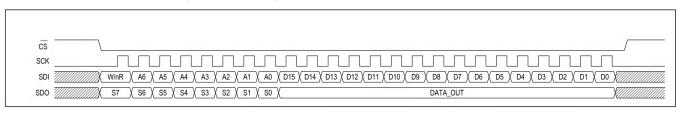

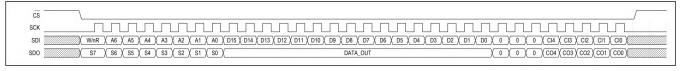

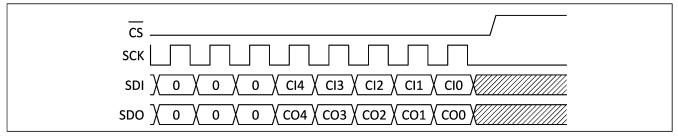

| SPI の概要                              | 45 |

| SPI データ                              | 45 |

| シリアル・インタフェースの CRC エラー検出              | 46 |

| ワンタイム・プログラマブル (OTP)                  | 47 |

| OTP プログラミング                          | 47 |

| パワーアップ時に OTP ダウンロードを行うためのウェイクアップ時間   | 48 |

| レジスタ・マップ                             | 49 |

| 機能レジスタ                               | 49 |

| レジスタの詳細                              | 54 |

| OTP_CONTROLLER                       | 72 |

| レジスタの詳細                              | 72 |

| アプリケーション情報                           | 75 |

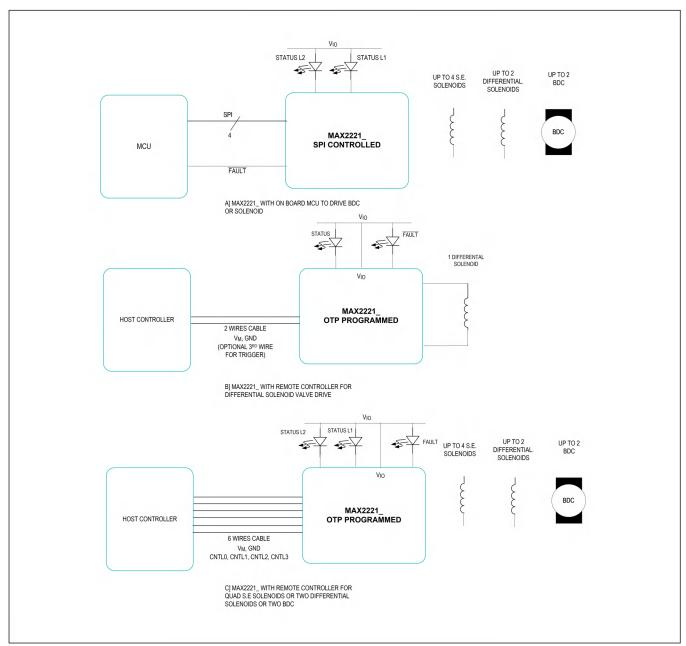

| 使用例                                  | 75 |

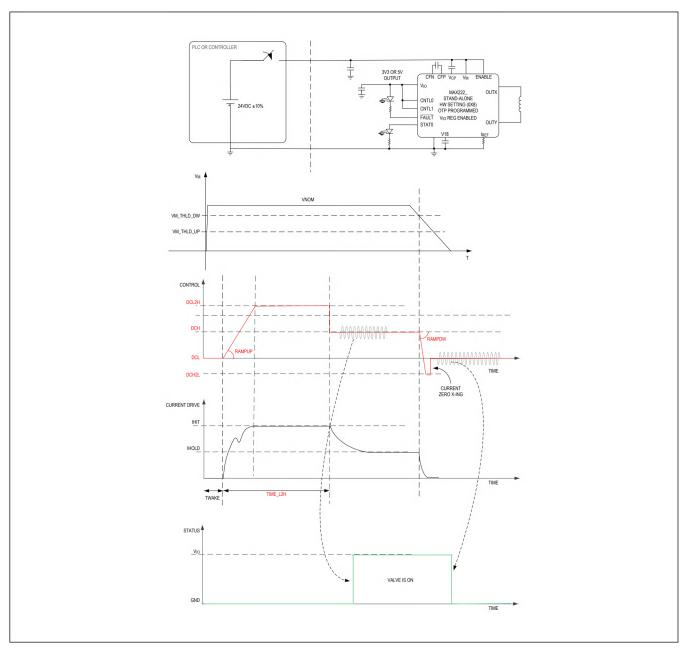

| スタンドアロン $V_{ m M}$ スイッチング            | 76 |

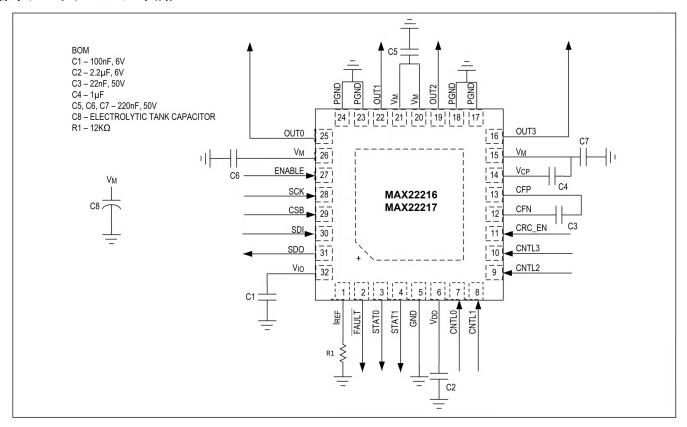

| 標準アプリケーション回路                         | 79 |

| <b>海海アプリケーション同</b> 収                 | 70 |

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

| 型番   | 79 |

|------|----|

| 改訂履壓 | 80 |

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

### 図一覧

| 図 1. シングルエンド構成                    | 17 |

|-----------------------------------|----|

| 図 2. ブリッジ接続負荷構成                   | 19 |

| 図 3. DC モータ<br>図 4. 電流制御ループのブロック図 | 21 |

| 図 4. 電流制御ループのブロック図                | 29 |

| 図 5. HS 構成における最大電圧のグラフ            | 29 |

| 図 6. LS 構成における最小電圧のグラフ            |    |

| 図 7. プランジャ動作の検出                   | 36 |

| 図 8. STATUS 出力モニタ・ピン – シングルエンド    | 41 |

| 図 9. STATUS 出力モニタ・ピン – 差動         | 42 |

|                                   |    |

| 図 11. CRC なしの SPI データグラム          | 45 |

| 図 12. CRC ありの SPI データグラム          |    |

| 図 13. CRC バイト                     | 46 |

| 図 14. 使用例                         | 76 |

| 図 15 スタンドアロン – VM スイッチング          | 78 |

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

### 表一覧

| 表 1. ハードウェア構成 23 表 2. 制御表 24 表 3. フルブリッジ制御 24 表 4. PWM マスタ周波数の設定 25 表 5. 個別 PWM 周波数 25 表 6. スルー・レート制御 25 表 7. ブランキング時間 25 表 7. ブランキング時間 26 表 7. ブランキングラ 10 また 8 また |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 表 2. 制御表24                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 表 3. フルブリッジ制御24                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 表 4. PWM マスタ周波数の設定25                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 表 5. 個別 PWM 周波数                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 表 6. スルー・レート制御                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 表 7. ブランキング時間                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>表 V</b> 到間上一 F (/) 整 元 76                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 表 9. フルスケールと検出スケール                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 表 10. ディザとインダクタンス測定                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 表 9. フルスケールと検出スケール 28<br>表 10. ディザとインダクタンス測定 32<br>表 11. I_MONITOR ADC の最大値 – 10 進 33                                                                                                                                                                                                                                                                                                                                                                                            |

| 表 12. インダクタンス測定のフォルト検出                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 表 13. インダクタンス測定に基づく STATUS のモニタ                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 表 14. STAT ロジック出力ピンの選択                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 表 15. 多機能ステータス・ピン40                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 表 16. マスク・ビット                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 表 17. 延長のイネーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# 高度な診断機能を備えたクワッド・スマート・ シリアル制御のソレノイドおよびモータ用ドライバ

#### 絶対最大定格

| $V_M \sim GND$       | 0.3V~+42V                                         |

|----------------------|---------------------------------------------------|

| $V_{CP}{\sim}GND$    | $V_M - 0.3V \sim min (+42V, V_M + 6V)$            |

| $C_{FP}{\sim}GND$    | $V_M - 0.3V \sim V_{CP} + 0.3V$                   |

| C <sub>FN</sub> ~GND | $-0.3$ V $\sim$ min (+42V, V <sub>M</sub> + 0.3V) |

| CNTL_~GND            | $-0.3V$ main $(6V, V_{IO} + 0.3V)V$               |

| OUT_~GND             | $-0.3V \sim V_M + 0.3V$                           |

| PGND~GND             | 0.3V~+0.3V                                        |

| CRC_EN~GND           | 0.3V $\sim$ min (6V, V <sub>IO</sub> + 0.3V)V     |

| STAT_~GND            | $-0.3V \sim V_{IO} + 0.3V$                        |

| ENABLE~GND           | $-0.3V \sim V_M + 0.3V$                           |

| <del>CS</del> ∼GND   | $-0.3$ V $\sim$ min (6V, V <sub>IO</sub> + 0.3V)V |

| SDI~GND              | $-0.3V \sim \min(6V, V_{IO} + 0.3V)V$             |

|                      |                                                   |

| SCK~GND               | $-0.3V\sim\min(6V, V_{IO} + 0.3V)V$               |

|-----------------------|---------------------------------------------------|

| SDO~GND               | $-0.3V \sim min (6V, V_{IO} + 0.3V)V$             |

| V <sub>DD</sub> ∼GND  | $-0.3$ V $\sim$ min (+2.2, V <sub>M</sub> + 0.3)V |

| V <sub>IO</sub> ~GND  | −0.3V~+6V                                         |

| FAULT~GND             | −0.3V~+6V                                         |

| I <sub>REF</sub> ~GND | 0.3V $\sim$ min (+2.2, V <sub>DD</sub> + 0.3)V    |

| 連続消費電力(2s2p 基板)       | (T <sub>A</sub> =+70℃、+70℃ を超える                   |

| 温度では 34.5mW/℃ でディ     | レーティング) 2758.6mW                                  |

| 動作温度範囲                | −40°C∼ +125°C                                     |

| ジャンクション温度             | +150°C                                            |

| 保存温度範囲                | 65°C~150°C                                        |

|                       | 10s)+300°C                                        |

|                       |                                                   |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する 規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### パッケージ情報

#### **TQFN 32 - 5mm × 5mm**

| Package Code                            | T3255Y+4C |

|-----------------------------------------|-----------|

| Outline Number                          | 21-100214 |

| Land Pattern Number                     | 90-100082 |

| Thermal Resistance, Single-Layer Board: |           |

| Junction to Ambient (θ <sub>JA</sub> )  | -         |

| Junction to Case (θ <sub>JC</sub> )     | -         |

| Thermal Resistance, Four-Layer Board:   |           |

| Junction to Ambient (θ <sub>JA</sub> )  | 29°C/W    |

| Junction to Case (θ <sub>JC</sub> )     | 1.7°C/W   |

最新のパッケージ外形図とランド・パターン(フットプリント)に関しては、www.maximintegrated.com/packages で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、www.maximintegrated.com/thermal-tutorial を参照してください。

### 電気的特性

$(V_M=4.5V\sim36V,\ V_{IO}=2.2V\sim5.25V,\ R_{REF}=12k\Omega,\ ENABLE=ロジック・ハイ、代表値は\ T_A=25^{\circ}C$ および  $V_M=24V$  における値。制限値は  $T_A=+25^{\circ}C$  で 100%テストされています。動作温度範囲および関連する電源電圧範囲における制限値は、設計および特性評価により裏付けられています。「GBD」と記載された仕様は、設計により確保されていますが、出荷テストの対象外です。)

| PARAMETER                      | SYMBOL             | CONDITIONS       | MIN | TYP | MAX  | UNITS |

|--------------------------------|--------------------|------------------|-----|-----|------|-------|

| POWER SUPPLY                   |                    |                  |     |     |      |       |

| Supply Voltage Range           | V <sub>M</sub>     |                  | 4.5 |     | 36   | V     |

| Logic Input Supply<br>Voltage  | V <sub>IO</sub>    |                  | 2.2 |     | 5.25 | V     |

| Sleep Mode Current consumption | I <sub>SLEEP</sub> | Enable logic low |     | 4   | 18   | μA    |

### 電気的特性(続き)

$(V_M=4.5V\sim36V,V_{IO}=2.2V\sim5.25V,R_{REF}=12k\Omega,ENABLE=$ ロジック・ハイ、代表値は  $T_A=25^{\circ}C$ および  $V_M=24V$  における値。制限値は  $T_A=+25^{\circ}C$  で 100%テストされています。動作温度範囲および関連する電源電圧範囲における制限値は、設計および特性評価により裏付けられています。「GBD」と記載された仕様は、設計により確保されていますが、出荷テストの対象外です。)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYMBOL              | СО                          | NDITIONS          | MIN                   | TYP                       | MAX                   | UNITS |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-------------------|-----------------------|---------------------------|-----------------------|-------|--|

| Nap Mode Current<br>Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>NAP</sub>    | Enable logic high           | , Active = 0      |                       | 210                       | 450                   | μΑ    |  |

| Quiescent Current<br>Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>VM</sub>     | Enable logic high           | , Active = 1      |                       | 7                         | 9                     | mA    |  |

| LOGIC LEVEL INPUTS-O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UTPUTS              |                             |                   |                       |                           |                       |       |  |

| Input Voltage Level -<br>High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>IH</sub>     |                             |                   | 0.7 x V <sub>IO</sub> |                           |                       | V     |  |

| Input Voltage Level -<br>Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>IL</sub>     |                             |                   |                       |                           | 0.3 x V <sub>IO</sub> | V     |  |

| Input Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>HYS</sub>    |                             |                   |                       | 0.15 x<br>V <sub>IO</sub> |                       | mV    |  |

| Logic Input Pin Pulldown<br>Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R <sub>PD</sub>     | To GND. Pins CN CRC_EN.     | ITL_, SCK, SDI,   | 70                    | 100                       | 130                   | kΩ    |  |

| CS Pin Pullup<br>Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R <sub>PU</sub>     | To V <sub>IO</sub>          |                   | 70                    | 100                       | 130                   | kΩ    |  |

| Logic-Low Output<br>Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>OL</sub>     | I <sub>LOAD</sub> = 5mA, ST | AT_ and FAULT pin |                       |                           | 0.4                   | V     |  |

| Logic-High Output<br>Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>OH</sub>     | I <sub>LOAD</sub> = -5mA    |                   | V <sub>IO</sub> - 0.4 |                           |                       | V     |  |

| Enable Voltage Level<br>High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>IH(EN)</sub> |                             |                   | 0.9                   |                           |                       | V     |  |

| Enable Voltage Level<br>Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{IL(EN)}$        |                             |                   |                       |                           | 0.6                   | V     |  |

| Enable Pulldown Input<br>Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R <sub>PD(EN)</sub> |                             |                   | 0.8                   | 1.5                       |                       | mΩ    |  |

| OUTPUT SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NS                  |                             |                   |                       |                           |                       |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                             | SNSF[1:0] = "00"  |                       | 0.17                      | 0.330                 |       |  |

| Output On-Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Passa as            | MAX22216                    | SNSF[1:0] = "01"  |                       | 0.23                      | 0.45                  |       |  |

| Low Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R <sub>ON(LS)</sub> |                             | SNSF[1:0] = "10"  |                       | 0.43                      | 0.83                  | Ω     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | MAX22217                    |                   |                       | 0.43                      | 0.83                  |       |  |

| Output On-Resistance<br>High Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R <sub>ON(HS)</sub> |                             |                   |                       | 0.17                      | 0.33                  | Ω     |  |

| Output Leakage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>LEAK</sub>   | Driver OFF                  |                   | -5                    |                           | 5                     | μA    |  |

| Dead Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>DEAD</sub>   |                             |                   |                       | 0.1                       |                       | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | SRC[1:0] = "00"             |                   |                       | Fast/No<br>limit          |                       |       |  |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SRC                 | SRC[1:0] = "01"             |                   |                       | 200                       |                       | V/µs  |  |

| The state of the s |                     | SRC[1:0] = "10"             |                   |                       | 100                       |                       |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | SRC[1:0] = "11"             |                   |                       | 50                        |                       |       |  |

### 電気的特性(続き)

$(V_M=4.5V\sim36V, V_{IO}=2.2V\sim5.25V, R_{REF}=12k\Omega, ENABLE=$ ロジック・ハイ、代表値は  $T_A=25^{\circ}$ C および  $V_M=24V$  における値。制限値は  $T_A=+25^{\circ}$ C で 100%テストされています。動作温度範囲および関連する電源電圧範囲における制限値は、設計および特性評価により裏付けられています。「GBD」と記載された仕様は、設計により確保されていますが、出荷テストの対象外です。)

| PARAMETER                                    | SYMBOL                  | COND                                       | ITIONS                         | MIN                  | TYP                      | MAX  | UNITS |  |

|----------------------------------------------|-------------------------|--------------------------------------------|--------------------------------|----------------------|--------------------------|------|-------|--|

| PROTECTION CIRCUITS                          |                         | •                                          |                                |                      |                          |      |       |  |

|                                              | OCP                     | SNSF[1:0] = "00"                           |                                | 4                    |                          |      |       |  |