本ハンドブックの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、その内容については英語版を正と いたします。英語版最新資料はこちらをご参照ください。

# ADE9000 テクニカル・リファレンス・ マニュアル

UG-1098

OneTechnology Way · P.O.Box9106 · Norwood, MA 02062-9106, U.S.A. · Tel: 781.329.4700 · Fax: 781.461.3113 · www.analog.com

## ADE9000 (高性能、多相電力量/電力品質モニタリング IC) の機能と特長

## 適用範囲

このリファレンス・マニュアルでは、ADE9000 の機能と特長について詳細に説明します。本書は ADE9000 のデータシー トと併用する必要があります。

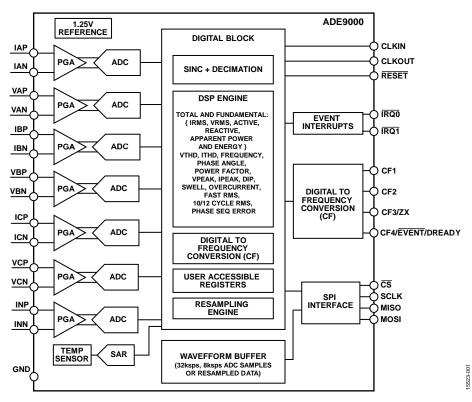

## 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2019 Analog Devices, Inc. All rights reserved.

## アナログ・デバイセズ株式会社

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

# 目次

| 適用範囲               | 1  |

|--------------------|----|

| 機能ブロック図            | 1  |

| 改訂履歴               | 2  |

| A/D コンバータ (ADC)    | 3  |

| 概要                 | 3  |

| アナログ入力構成           | 3  |

| 内部 RF イミュニティ・フィルタ  | 4  |

| 動作モード              |    |

| 出力データ・レートおよびフォーマット | 4  |

| 電圧リファレンス           | 5  |

| 水晶発振器/外部クロック       | 6  |

| パワー・マネージメント        | 7  |

| 電源モード              | 7  |

| 電源投入シーケンス          | 7  |

| 電源電圧低下の検出          | 8  |

| リセット               | 8  |

| 電源モードの変更           | 8  |

| 測定                 | 9  |

| 電流チャンネル測定の更新レート    |    |

| フルスケール時のコード        | 13 |

| 電力およびフィルタベースの      |    |

| 実効値測定アルゴリズム        |    |

| 電力量測定の概要           |    |

| 電力量の積算             |    |

| 電力の積算              |    |

| 電力品質の測定            |    |

| 温度                 |    |

| 内部データへのアクセス        |    |

| SPI プロトコルの概要       |    |

| SPI 書込み            |    |

| SPI 読出し            |    |

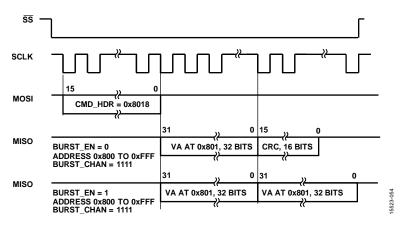

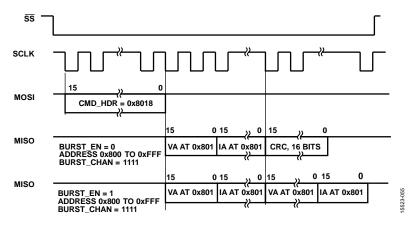

| SPI バースト読出し        | 33 |

| SPI プロトコルの CRC     | 34 |

| 追加通信検証レジスタ                                     | 35 |

|------------------------------------------------|----|

| 設定レジスタの CRC                                    | 35 |

| 波形バッファ                                         | 36 |

| 固定データ・レート波形                                    | 36 |

| 固定データ・レート波形のフィリングと                             |    |

| トリガベース・モード                                     | 37 |

| リサンプリング波形                                      | 39 |

| 波形バッファの設定                                      | 40 |

| SPI による波形バッファ・サンプルの                            |    |

| バースト読出し                                        |    |

| 割込み/ <mark>EVENT</mark>                        |    |

| 割込み( $\overline{IRQ0}$ および $\overline{IRQ1}$ ) | 43 |

| EVENT                                          | 43 |

| 追加レジスタのステータス・ビット                               | 43 |

| 様々な電力量計構成への ADE9000 の応用                        | 44 |

| ブロンデル非準拠メータ                                    | 45 |

| 4 線式 Y 結線サービスへの ADE9000 の応用                    | 46 |

| 3 線式 Δ 結線サービスへの ADE9000 の応用                    | 47 |

| ブロンデル非準拠の4線式Y結線サービスへの                          |    |

| ADE9000 の応用                                    | 48 |

| ブロンデル非準拠の4線式Δ結線サービスへの                          |    |

| ADE9000 の応用                                    |    |

| サービス・タイプのまとめ                                   |    |

| クイック・スタート                                      |    |

| キャリブレーション                                      |    |

| システム・パラメータ                                     | 51 |

| 実効値のキャリブレーション                                  | 51 |

| 位相のキャリブレーション                                   | 51 |

| 電力のキャリブレーション                                   | 52 |

| 変換定数                                           | 52 |

| レジスタの情報                                        | 53 |

| レジスタの詳細                                        | 65 |

## 改訂履歴

3/2017-Revision 0: 初版

## A/D コンバータ(ADC)

## 概要

ADE9000 は、サンプリングを同時に行う、独立した 7 つの 2次 $\Sigma$ - $\Delta$  ADC を内蔵しています。各 ADC は 24 ビットで、完全差動入力と疑似差動入力をサポートしており、グラウンドより高い電圧にも低い電圧にも対応します。ADE9000 は、低ノイズ、低ドリフトのバンドギャップ・リファレンスを内蔵しています。外部電圧リファレンス を使用する場合は、CONFIG1 レジスタのEXT\_REF ビットをセットします。各 ADC は、ゲインを 1、2、または 4 に設定できるプログラマブル・ゲイン・アンプを内蔵しています。

## アナログ入力構成

内部バッファ回路はありません。ADE9000 のインピー ダンスは、選択したプログラマブル・ゲインにより異な ります。

## 完全差動入力

IAP、IAN、IBP、IBN、ICP、ICN、VAP、VAN、VBP、VBN、VCP、および VCN ピンの入力信号が 0.6V を超えることはできません。ADC の差動フルスケール入力範囲は±1V ピーク (0.707Vrms) です。

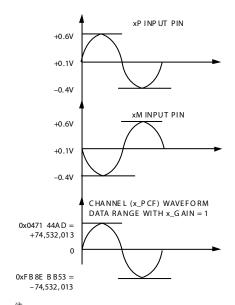

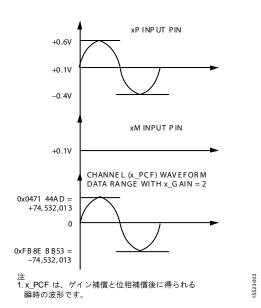

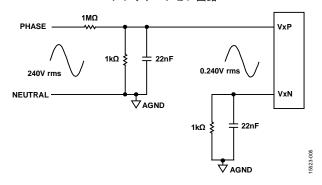

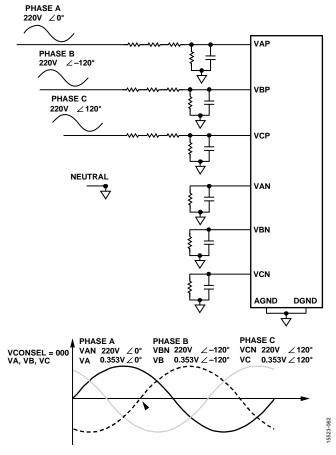

図 2 および図 3 に、電力量モニタリング・アプリケーションでの一般的な 2 種類の入力信号を示します。図 2 に、差動逆位相信号での許容最大入力を示します。カレント・トランスと、センター・タップ付きのバーデン抵抗により、差動逆位相信号が発生します。図 3 に、疑似差動信号での最大入力信号を示します。この信号は、抵抗分圧器またはロゴスキー・コイル電流センサーを使用してメインの電圧信号を検出するときに得られる信号と同様です。

ゲインが 1 の入力信号では、以下の条件を満たす必要があります。

- IAP、IAN、IBP、IBN、ICP,ICN、VAP、VAN、 VBP、VBN、VCP、およびVCN | ≤+0.6V ピーク

- $|IxP IxN| \le +1V$  ピーク、 $|VxP VxN| \le +1V$  ピーク

各 ADC は、ゲインを 1、2、または 4 に設定できるプログラマブル・ゲイン・アンプを内蔵しています。ADC は  $\pm 1V$  の入力でフルスケール出力コードを生成します。ゲインが 1 の場合、このフルスケール出力は、図 2 に示すように 0.707Vrms の差動逆位相入力に対応します。ゲインが 2 のとき、フルスケール出力コードは、図 3 に示すように 0.353Vrms の入力で生成されます。ゲインが 4 のとき、フルスケール出力コードは、0.1765Vrms の入力信号で生成されます。xP ピンと xN ピンの電圧は、データシートに仕様規定されているように、 $\pm 0.6V$  以内にする必要があります。

$PGA\_GAIN$  レジスタの  $x\_GAIN$  ビットに書き込んで、 チャンネルごとにゲインを設定します。

注 1. x\_PCF は、ゲイン補償と位相補償後に得られる 瞬時の波形です。

図 2. コモンモード電圧が 0.1V でゲインが 1 の 差動逆位相入力の場合の最大入力信号

図 3. コモンモード電圧が 0.1V でゲインが 2 の 疑似差動入力の場合の最大入力信号

Rev. 0 - 3/86 -

### 電流センサーおよび電圧センサーとのインターフェース

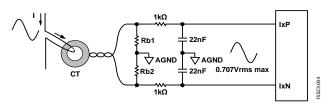

図 4 および図 6 に、カレント・トランスおよびロゴスキー・コイル電流センサーに接続する推奨回路を示します。図 5 に、メイン電圧を測定するインターフェース回路を示します。

アンチエイリアシング(折返し誤差防止)・フィルタのコーナ周波数は 7kHz 前後を選択して、変調器のクロック周波数付近の帯域外信号を十分に減衰させます。同様に、電圧チャンネルに使用する RC フィルタのコーナ周波数も同じ値にして、電流信号と電圧信号の間に位相誤差が発生しないようにします。ロゴスキー・センサーには 1/f 応答特性があるため、ロゴスキー・コイルの入力回路には、帯域外ノイズを更に低減する 2 次アンチエイリアス・フィルタがあることに注意してください。

図 4. カレント・トランス電流センサーを接続した アプリケーション回路

図 5. 抵抗分圧器を介して検出された電圧が入力される アプリケーション回路

図 6. ロゴスキー・コイル電流センサーを接続した アプリケーション回路

## 内部 RF イミュニティ・フィルタ

電力量計アプリケーションでは、メータ(電力量計)が、IEC61000-4-3 に従って、80MHz から 10GHz までの範囲で 30V/m の外部無線周波数電磁界の影響を受けないことが要求されます。これらの信号を外部でフィルタ除去するのは困難なので、ADE9000 では、アンチエイリアシング・フィルタを内蔵して、このテストでの性能を向上させています。この内部 2 次ローパス・フィルタ(LPF) のコーナ周波数は 10MHz です。7kHz より高い

周波数の信号を減衰させるには、電流センサーおよび電 圧センサーとのインターフェースのセクションに示すよ うに、外付けのアンチエイリアス・フィルタが必要です。

#### 動作モード

各 ADC には、ノーマル・モードとディスエーブル・ モードの 2 つの動作モードがあります。

ノーマル動作モードでは、ADC は常にオンしており、絶 えずサンプリングを行います。CHNL\_DIS レジスタを使 用すれば、ADC を個別にディスエーブルできます。

ADE9000 には 2 つの異なる電源モードがあります(電源モードのセクションを参照)。 PSM0 電源モードでは、全ての ADC がオンしています。 PSM3 モードでは、全ての ADC がディスエーブルされ、オンできません。

表 1. PSMx 電源モードでの ADC の動作

| PSMx Power Mode | ADC Mode of Operation |

|-----------------|-----------------------|

| PSM0            | Normal (on)           |

| PSM3            | Disabled (always off) |

#### 出力データ・レートおよびフォーマット

変換が完了すると、STATUSO レジスタの DREADY ビットは 1 にセットされます。 CONFIG1 レジ<u>スタの CF4\_CFG[3:2]</u>ビットが 11 である場合は、CF4/EVENT /DREADY ピンが DREADY に対応して、ハイのパルスを出力して、7 つの新たな A/D 変換結果の準備が整ったことを示します。

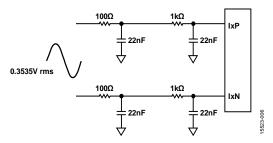

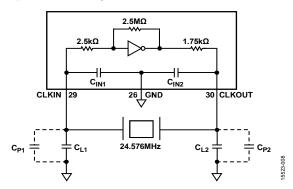

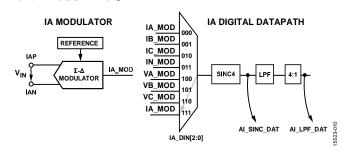

ADE9000 では、変調器のサンプリング・レート (MODCLK) は 2.048MHz (CLKIN/12 = 24.576/12) に固定されています。sinc フィルタの出力データ・レートは MODCLK/64 であるのに対して、ローパス・フィルタ/ デシメータ段の出力レートは sinc フィルタの出力レート より 4 倍低速です。2.048MHz で ADC サンプルを取り、32kHz または 8kHz のデシメーション・レートで波形情報を生成するデジタル・フィルタ処理を図 7 に示します。

図 7. ADC 段の後のデータパス

出力データ・レートのまとめを表 2 に示します。

表 2. 出力データ・レート

| Parameter                        | Output Data Rate   |

|----------------------------------|--------------------|

| CLKIN Frequency                  | 24.576 MHz         |

| ADC Modulator Clock, MODCLK      | 2.048 MHz          |

| SINC Output Data Rate, SINC_ODR  | 32 kHz             |

| Low-Pass Filter Output Data Rate | 8 kHz              |

| 3 dB Bandwidth                   | $3.2~\mathrm{kHz}$ |

Rev. 0 - 4/86 -

波形バッファの ADC データは、表 3 に示すように、4 ビットだけ左にシフトして符号拡張処理を行うことにより、32 ビットのデータとして格納されます。

表 3.32 ビットの ADC データ・フォーマット

| Bits[31:28] | Bits[27:4]     | Bits[3:0] |

|-------------|----------------|-----------|

| SE          | ADC_DATA[23:0] | 0000      |

入力が 1V ピークのとき、sinc フィルタからの波形バッファでの予想出力コードは、67,107,786(10 進数)です。入力が 1V ピークのとき、デシメータ・フィルタからの波形バッファでの予想出力コードは、74,518,668 です。詳細については、波形バッファのセクションを参照してください。

## 電圧リファレンス

ADE9000 は、1.25V の内部リファレンスをサポートしています。外部リファレンスは REFIN ピンと REFGND ピンの間に接続できます。外部電圧リファレンスを使用する場合は、CONFIG1 レジスタの EXT\_REF ビットをセットして、内部リファレンス・バッファをディスエーブルします。

Rev. 0 - 5/86 -

## 水晶発振器/外部クロック

ADE9000 は水晶発振器を内蔵しています。代わりに、ADE9000 の CLKIN ピンにデジタル・クロック信号を入力してもかまいません。

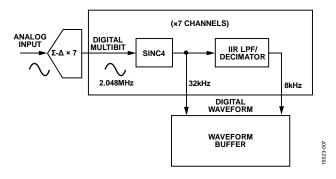

水晶発振器を ADE9000 のクロック源として使用する場合は、水晶発振器とセラミック・コンデンサ(容量は CL1 および CL2)を図 8 に示すように接続します。外付け帰還抵抗を水晶発振器と並列に接続するのは推奨しません。

デジタル・クロック信号を CLKIN ピンに入力すると、CLKOUT ピンから反転出力が得られます。この出力は内部でバッファされないので、この出力を使用して他の外部デバイスを直接駆動することはできません。CLKOUT が出力されるのは PSM0 動作モードだけなので注意してください。

図 8. 水晶発振器のアプリケーション回路

#### 水晶発振器の選択

ADE9000 の水晶発振器回路のトランスコンダクタンス (gm) は、データシートに記載されています。水晶発振器の計算上の gm critical より  $3\sim5$  倍大きい gm にすることを推奨します。

次式は、水晶発振器のデータシートに記載されている情報から水晶発振器の gmcRITICAL を算出する方法を示しています。

$gm_{CRITICAL} = 4 \times ESR_{MAX} \times 1000 \times (2 \times \pi \times f_{CLK(Hz)})^2 \times (C_0 + C_L)^2$   $= 2 \times C_{\chi}$

gmcRITICALは、水晶発振器を起動するのに必要な最小の ゲインであり、mA/Vで表されます。

$ESR_{MAX}$ は最大の ESR であり、オーム  $(\Omega)$  で表されます。  $f_{CLK}$ は 24.576MHz で、Hz で表すと 24.576× $10^6$ です。  $C_0$ は最大シャント容量で、ファラッド (F) で表されます。  $C_L$ は負荷容量で、ファラッド (F) で表されます。

低 ESR で負荷容量の小さな水晶発振器ほど gmcRITICAL が 小さくなり、駆動も容易になります。

ADE9000 の評価用ボードでは、Abracon 社製の水晶発振器 (部品番号 ABLS-24.576MHZ-8-L4Q-F-T) を使用しています。その最大 ESR は  $40\Omega$ 、負荷容量は 8pF、最大シャント容量は 7pF であり、その結果 gmcriticalは 0.86mA/V になります。

$gm_{CRTTICAL} = 4 \times ESR_{MAX} \times 1000 \times (2 \times \pi \times f_{CLK(H_2)})^2 \times (C_0 + C_L)^2$  $gm_{CRTTICAL} = 4 \times 40 \times 1000 \times (2 \times \pi \times 24.576 \times 10^6)^2 \times (7 \times 10^{-12} + 8 \times 10^{-12})^2 = 0.86$  データシートに記載されている ADE9000 内部の水晶発振器回路のゲイン (gm) は、gmcRITICALの 5 倍を超えているので、この水晶発振器を起動するのに十分な余裕があります。

## 負荷コンデンサの計算

水晶発振器のメーカーは、水晶発振器両端の合成負荷容量 (CL) の仕様を規定しています。図8の容量は、次のように説明できます。

- **CP**<sub>1</sub> および **CP**<sub>2</sub>: プリント回路基板 (**PCB**) のパターンに起因するクロック・ピン上の寄生容量。

- Cin<sub>1</sub> および Cin<sub>2</sub>: それぞれ CLKIN ピンと CLKOUT ピンの内部容量。

- CL<sub>1</sub> および CL<sub>2</sub>: 水晶発振器の正しい合成 CL を得るために選択された負荷コンデンサ。

内部のピン容量( $C_{in1}$  および  $C_{in2}$ )は、データシートに示すように、それぞれ 4pF です。 $CP_1$  と  $CP_2$  の値を求めるには、PCB のクロック・ピン(それぞれ CLKIN および CLKOUT)の各容量を AGND ピンを基準にして測定します。IC を PCB にハンダ処理した後に測定を行う場合は、クロック・ピンの 4pF の内部容量を差し引いて、水晶発振器ピンのそれぞれの寄生容量の実際の値を求めます。

セラミック・コンデンサに対して適切な容量値を選択するには、CL<sub>1</sub>および CL<sub>2</sub>を次式から計算します。

$$CL = [(CL_1 + CP_1 + C_{INI}) \times (CL_2 + CP_2 + C_{IN2})]/(CL_1 + CP_1 + C_{INI} + CL_2 + CP_2 + C_{IN2})$$

(1)

各クロック・ピンの全容量が次のようになるように CL<sub>1</sub> および CL<sub>2</sub>を選択します。

$$CL_1 + CP_1 + C_{IN1} = CL_2 + CP_2 + C_{IN2}$$

(2)

式 1 と式 2 を使用して、 $CL_1$  および  $CL_2$  の値を計算できます。

#### 負荷コンデンサの計算例

負荷容量の仕様が 8pF の水晶発振器を選択し、PCB パターンからの寄生容量測定値が CP1 = CP2 = 2pF である場合、式 1 は次のことを意味します。

$$CL = [(CL_1 + CP_1 + C_{IN1}) \times (CL_2 + CP_2 + C_{IN2})]/(CL_1 + CP_1 + C_{IN1} + CL_2 + CP_2 + C_{IN2})$$

8 pF =  $[(CL_1 + 2 pF + 4 pF) \times (CL_2 + 2 pF + 4 pF)]/(CL_1 + 2 pF + 4 pF + CL_2 + 2 pF + 4 pF)$

式 2 より、 $CL_1 = CL_2$  とすれば、以下のようになります。

8 pF =  $[(CL_l + 6 \text{ pF}) \times (CL_l + 6 \text{ pF})]/(CL_l + 6 \text{ pF} + CL_l + 6 \text{ pF})$ 8 pF =  $[(CL_l + 6 \text{ pF}) \times (CL_l + 6 \text{ pF})]/[2 \times (CL_l + 6 \text{ pF})]$

$8 \text{ pF} = (CL_I + 6 \text{ pF})/2$

したがって、 $CL_1 = CL_2 = 10 pF$ です。

この例に基づいて、 $CL_1$  および  $CL_2$  に対しては、10pF のセラミック・コンデンサを選択します。

## パワー・マネージメント

#### 電源モード

ADE9000 には、2 つの動作モード(PSM0 および PSM3)があります。どちらの電源モードに入るかは、PM1 ピンおよび PM0 ピンによって制御されます。どちらの動作モードに入るかを決めるため、これらのピンは 絶えずチェックされます。ADE9000 を低消費電力のリセット状態にする場合は、PSM3 を使用できます。

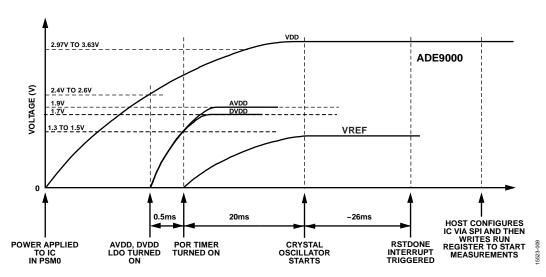

#### 電源投入シーケンス

ADE9000 IC の VDD ピンに電源が投入されると、デバイスは PM0 ピンと PM1 ピンの状態をチェックして、電源モードをチェックします(詳細については、電源モードのセクションを参照してください)。 PSM0 モード (PM1 および PM0 = 00 または 01) でRESETピンがハイの場合は、VDD が  $2.4V\sim2.6V$  に達すると、AVDD および DVDD の低ドロップアウト・レギュレータ (LDO) がオンします。 RESETピンがローの場合、AVDD LDO および DVDD LDO はオンしません。 AVDD LDO および DVDD LDO はオンしません。 AVDD LDO および DVDD LDO を充電するために使用される電流を LDO につき 17mA に制限するクランプ回路があることにがあることに注意してください。

AVDD と DVDD の電圧が両方とも  $1.3V\sim1.5V$  より高くなり、VDD の電圧が  $2.4V\sim2.6V$  より高くなると、 20ms のタイマーが作動して、電源が通常の電位(VDD

が  $2.97V \sim 3.6V$  の範囲内、AVDD が 1.9V、DVDD が 1.7V)に到達できるよう時間が長くなります。このタイマーの時間が経過すると、水晶発振器が起動します。

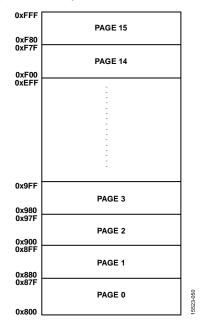

26ms 後に RSTDONE 割込みがトリガされ、 $\overline{\text{IRQ1}}$ ピン がローになって、STATUS1 レジスタの RSTDONE ビッ トがセットされます。RSTDONE ビットがセットされる ことで、ADE9000 が電源投入シーケンスを完了したこ とが示されます。これで、シリアル・ペリフェラル・イ ンターフェース (SPI) を介して IC を設定できるように なりました。デバイスを設定したら、RUN レジスタに書 き込んで DSP を起動し、デバイスが測定を開始するよう にします。アドレス 0x000 からアドレス 0x0FF までと アドレス 0x400 からアドレス 0x5FF までのレジスタは、 電源投入時にデフォルト値に戻ります。アドレス 0x200 からアドレス 0x3FF までのレジスタは、RUN レジスタ の値が 0x0000 から 0x0001 に変化してから 500µs 以内 にクリアされます。また、波形バッファ(アドレス 0x800 からアドレス 0xFFF まで) はリセット後もクリア されないことに注意してください。

PSM3 モードでは、AVDD LDO および DVDD LDO はオンしません。RSTDONE 割込みは発生せず、SPI ポートは使用できません。

図 9. PSM0 での ADE9000 の電源投入シーケンス

表 4. 電源モード (PSM0 および PSM3)

| PSMx 電源モード | 説明          | PM1ピン | PM0ピン  | 使用可能な機能       | SPI の使用可否 |

|------------|-------------|-------|--------|---------------|-----------|

| PSM0       | Normal Mode | 0     | 0 or 1 | All functions | Yes       |

| PSM3       | Idle        | 1     | 1      | None          | No        |

Rev. 0 - 7/86 -

#### 電源電圧低下の検出

パワーオン・リセット(POR)回路は、VDD、AVDD、DVDD の各電源をモニタします。AVDD または DVDD の電圧が  $1.3V\sim1.5V$  より低くなるか、VDD の電圧が  $2.4V\sim2.6V$  より低くなると、IC はリセット状態に維持され、電源投入シーケンスがもう一度始まって、AVDD および DVDD の電圧が  $1.3V\sim1.5V$  より高くなり、VDD の電圧が  $2.4V\sim2.6V$  より高くなるまで待ってから、20ms の POR タイマーが作動します。 $\overline{IRQ1}$  での RSTDONE 割込みは、ADE9000 を SPI を介して再初期 化できることを示します。

#### リセット

RESETピンが 1μs の間ローになるか、CONFIG1 レジス タの SWRST ビットをセットしてソフトウェア・リセットを開始すると、AVDD LDO と DVDD LDO はオフします。電源投入シーケンスは、AVDD LDO と DVDD LDO がオンした時点から再開します(詳細については、電源投入シーケンスのセクションを参照してください)。 ADE9000 を低消費電力のリセット状態にする必要があるアプリケーションでは、 $\overline{RESET}$ ピンをローにして  $\overline{IC}$ をリセット状態(消費電流は  $100\mu A$ )に保持するのではなく、 $\overline{PSM3}$ (消費電流は約  $2\mu A$ )を使用することを推奨します(正確な消費電流については、データシートを参照)。

## 電源モードの変更

PM1 ピンと PM0 ピンの状態は、絶えずモニタされています。電源モードが  $1\mu s$  の間 PSM0 から PSM3 (PM1 および PM0 = 11) に変わると、AVDD LDO と DVDD LDO はオフします。電源モードが PSM0 に戻ると、電源投入シーケンスは、AVDD LDO と DVDD LDO がオンした時点から再開します。

Rev. 0 - 8/86 -

## 測定

#### 電流チャンネル測定の更新レート

表 5 に、電流チャンネルの測定値を保持するレジスタと 更新時のレートを示します。

表 5. 電流チャンネル測定の更新レート

| レジスタ名           | 説明                                       | 更新レート                      |

|-----------------|------------------------------------------|----------------------------|

| AI_SINC_DAT     | IA sinc4 フィルタ出力                          | 32 ksps                    |

| BI_SINC_DAT     | IB sinc4 フィルタ出力                          | 32 ksps                    |

| $CI\_SINC\_DAT$ | IC sinc4 フィルタ出力                          | 32 ksps                    |

| $NI\_SINC\_DAT$ | IN sinc4 フィルタ出力                          | $32  \mathrm{ksps}$        |

| $AI_LPF_DAT$    | IA sinc4 + IIR LPF フィルタ出力                | $f_{DSP} = 8 \text{ ksps}$ |

| $BI_LPF_DAT$    | IB sinc4 + IIR LPF フィルタ出力                | $f_{DSP} = 8 \text{ ksps}$ |

| $CI_LPF_DAT$    | IC sinc4 + IIR LPF フィルタ出力                | $f_{DSP} = 8 \text{ ksps}$ |

| NI_LPF_DAT      | IN sinc4 + IIR LPF フィルタ出力                | $f_{DSP} = 8 \text{ ksps}$ |

| AI_PCF          | IA での瞬時電流                                | $f_{DSP} = 8 \text{ ksps}$ |

| $BI_PCF$        | IBでの瞬時電流                                 | $f_{DSP} = 8 \text{ ksps}$ |

| $CI_PCF$        | ICでの瞬時電流                                 | $f_{DSP} = 8 \text{ ksps}$ |

| NI_PCF          | INでの瞬時電流                                 | $f_{DSP} = 8 \text{ ksps}$ |

| AIRMS           | IA のフィルタベースの全実効値                         | $f_{DSP} = 8 \text{ ksps}$ |

| BIRMS           | IBのフィルタベースの全実効値                          | $f_{DSP} = 8 \text{ ksps}$ |

| CIRMS           | ICのフィルタベースの全実効値                          | $f_{DSP} = 8 \text{ ksps}$ |

| NIRMS           | IN のフィルタベースの全実効値                         | $f_{DSP} = 8 \text{ ksps}$ |

| ISUMRMS         | ベクトル和のフィルタ済み実効値                          | $f_{DSP} = 8 \text{ ksps}$ |

|                 | (AI_PCF + BI_PCF + CI_PCF ±              |                            |

|                 | NI_PCF) 。 中性電流の実効値、<br>  ベクトル電流和のセクションを参 |                            |

|                 | 照してください。                                 |                            |

| IPEAK           | ピーク電流チャンネルのサンプ                           | $f_{DSP} = 8 \text{ ksps}$ |

|                 | ル。ピーク検出のセクションを参                          | -                          |

|                 | 照してください。                                 |                            |

| ANGLx_xxx       | 電圧と電流の間の位相角または電                          | CLKIN/24 =                 |

|                 | 流間の位相角。角度測定のセク<br>  ションを参照してください。        | 1024 ksps                  |

## ADC\_REDIRECT マルチプレクサ

**ADE9000** は、任意の **ADC** 出力を任意のデジタル処理 データパスにリダイレクトできるマルチプレクサを備え ています。

デフォルトでは、各変調器はそれに対応するデータパスにマップされます。例えば、IAP ピンと IAN ピンのデータは IA 変調器に入り、その後 IA デジタル処理データパスにマップされます。ADC\_REDIRECT レジスタに書き込んで、ADC からデジタル・チャンネルへのマッピングを変更します。

ADE9000 が PCB の上面にあるか底面にあるかによって 異なりますが、IA の ADC 出力を IC のデジタル・データパスにリダイレクトし、IC の ADC 出力を IA のデジタル・データパスにリダイレクトすることにより、リダイレクトはレイアウトを簡略化するのに役立ちます。IA および IC の ADC 出力をリダイレクトするには、ADC\_REDIRECT レジスタで  $IA_DIN = 010$  および  $IC_DIN = 000$  を書き込みます。

あるいは、ADC\_REDIRECT レジスタで VB\_DIN = 101 および VC\_DIN = 101 を書き込むことにより、3 つの

データパス全てに対して VA 電圧チャンネル出力を使用することもできます。

中性電流チャンネルには、ゼロ交差出力やゼロ交差角の 測定機能はありません。中性電流  $NI_PCF$  信号の位相を 補正するには、例えば中性電流 ADC 出力の送出先を B相のデジタル電流チャンネルにして、 $IA_DIN = 111$  と 書き込むことにより、その角度が A 相とどのように対応 するかを調べます。

図 10. ADC\_REDIRECT 変調器からデジタル・データパスへの マルチプレクス処理

## 電流チャンネル・ゲイン xlGAIN

電力量計システムには、ゲイン誤差の発生源が多数あります。カレント・トランスのバーデン抵抗など、電流センサーには一定の誤差が生じる可能性があります。ADE9000 デバイス自体にデバイス間ゲイン誤差があり、また電圧リファレンスに一定のばらつきがある場合があります(デバイスの仕様についてはデータシートを参照)。ADE9000 は、各電力量計デバイスの電流チャンネルのスケーリングを同じにするため、電流ゲインのキャリブレーション・レジスタを備えています。

下の式に示すように、電流チャンネル・ゲインは xIGAIN と共に変化します。

Current Channel Gain =

$$\left(1 + \frac{xIGAIN}{2^{27}}\right)$$

この式を使用して、与えられた電流チャンネル・ゲインに対する xIGAIN の値を計算します。

$xIGAIN = ROUND((Current\ Channel\ Gain - 1) \times 2^{27}$

電流チャンネル・ゲインは正でも負でもかまいません。 例えば、電流チャンネルのゲインを 10%高くして 1.1 に する場合は、次のようになります。

$xIGAIN = \text{ROUND}((1.1 - 1) \times 2^{27} = 13421773 = 0x00CC CCCD}$

ゲインを 10%低くして 0.9 にする場合は、次のようになります。

xIGAIN = ROUND((0.9-1) ×  $2^{27}$  = -1 ×  $10^7$  = 0xFF33\_3333 また、電流チャンネル・ゲイン・レジスタを使用して電流チャンネルの符号を変更することもできます。これは、電流センサーが逆方向に取り付けられていた場合に便利です。これを補償するには、電流チャンネル・ゲイン = -1 を使用します。

$xIGAIN = ROUND((-1-1) \times 2^{27} = -268435456 = 0 \times F000\_0000$

位相とゲインのマルチポイント機能を使用する場合は、電力量計の公称電流で行う主補正に xIGAIN を使用することを推奨します (詳細については、位相/ゲインのマルチポイント・キャリブレーションのセクションを参照してください)。

与えられた相に対して、次のことに注意してください。

$|Current\ Channel\ Gain \times Voltage\ Channel\ Gain \times Power\ Gain| \leq 3.75$

#### ICONSEL を使用する IB 計算

IB = -IA - IC を計算するには、ACCMODE の ICONSEL ビットに書き込みます。この設定は、一部の 3 線  $\Delta$  構成でのカレント・トランスのコストを抑えるの に役立ちます。詳細については、3 線式  $\Delta$  結線サービス への ADE9000 の応用のセクションを参照してください。

### ハイパス・フィルタ

DC オフセットを除去して実効値と電力量を正確に計測するため、ハイパス・フィルタを装備しています。

ADE9000 の電流チャンネルと電圧チャンネルのハイパス・フィルタは、デフォルトでイネーブルされます。 ディスエーブルするには、CONFIGO レジスタの DISPHPF ビットが1になるよう書き込みます。

データシートの仕様に記載された電力量計性能を達成するため、ハイパス・フィルタはイネーブル状態を維持することを推奨します。

アプリケーションによっては、例えばロゴスキー・コイル電流センサー使用時の性能を向上するため、ハイパス・フィルタのコーナ周波数を高くすることが適しています。

ハイパス・フィルタのコーナ周波数は、CONFIG2 レジスタの  $HPF\_CRN$  ビットを使用して選択できます(表 6 を参照)。

表 6. 入力信号が 50Hz の場合の HPF コーナ周波数のゲイン

| HPF_CRN     | f <sub>-3 dB</sub> (Hz) | HPF_GAIN | Settling Time to 1% for DC Step (sec) | Settling Time to 0.1% for DC Step (sec) |

|-------------|-------------------------|----------|---------------------------------------|-----------------------------------------|

| 0           | 77.4                    | 0.537    | 0.009                                 | 0.013                                   |

| 1           | 39.3                    | 0.790    | 0.018                                 | 0.027                                   |

| 2           | 19.8                    | 0.935    | 0.037                                 | 0.055                                   |

| 3           | 9.9                     | 0.984    | 0.073                                 | 0.110                                   |

| 4           | 5.0                     | 0.997    | 0.147                                 | 0.221                                   |

| 5           | 2.5                     | 0.999    | 0.294                                 | 0.442                                   |

| 6 (default) | 1.25                    | 1.001    | 0.589                                 | 0.883                                   |

| 7           | 0.625                   | 1.001    | 1.179                                 | 1.768                                   |

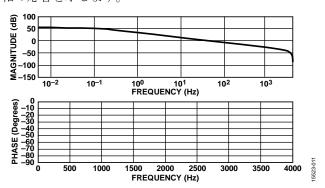

## デジタル積分器

ロゴスキー・コイルとも呼ばれる di/dt 電流センサーと 簡単にインターフェースを取れるように、デジタル積分 器が組み込まれています。di/dt センサー出力は、全周波 数範囲にわたって 20dB/decade の割合で増加します。こ の増加を補償するため、デジタル積分器は-20dB/decade のゲインと約-90°の位相シフトを適用します。

**ADC** がサンプリングしているときに対象の帯域にノイズ・エイリアシングが戻らないようにするには、2 次アンチエイリアシング・フィルタが必要です。

IA、IB、および IC チャンネルのデジタル積分器をイネーブルするには、CONFIGO レジスタの INTEN ビットをセットします。中性電流、IN チャンネルのデジタル積分器をイネーブルするには、CONFIGO レジスタの ININTEN ビットをセットします。

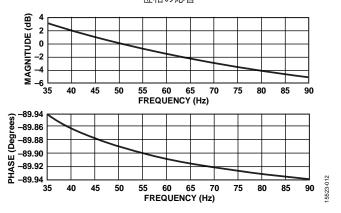

図 11 および図 12 に、デフォルト設定 DICOEFF = 0xFFFFE000 での ADE9000 デジタル積分器の振幅と位相の応答を示します。

図 11.DICOEFF = 0xFFFFE000 の場合のデジタル積分器の振幅と 位相の応答

図 12.DICOEFF = 0xFFFFE000 の場合のデジタル積分器の振幅と 位相の応答(40Hz~80Hz)

積分器がイネーブルされている場合は、DICOEFF = 0xFFFFE000を設定します。

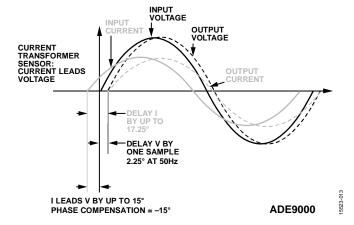

#### 位相補償

ADE9000 の位相補償では、デジタル・フィルタを使用して±0.001°の位相調整を実現しています。この高分解能により、低力率での有効電力量と無効電力量の総合的な性能が向上しています。

位相のキャリブレーション範囲は、50Hz では-15°~ +2.25°です。

このキャリブレーション範囲を実現するため、電圧チャンネルは、8ksps のサンプリング 1 回分(50Hz のとき 2.25°)だけ遅延します。

$$Voltage\ Channel\ Delay^{\circ} = \left(\frac{f_{LINE}}{f_{DSP}} \times 360^{\circ}\right)$$

Voltage Channel Delay° =

$$\left(\frac{50}{8000} \times 360^{\circ}\right) = 2.25^{\circ}$$

その後、電流チャンネルが、xPHCALx レジスタに書き込まれた値に従って、デジタル・フィルタによって遅延します。得られる位相補正は、xPHCALx レジスタの値により異なります。次式が示すのは、入力電圧と入力電流の合算遅延後の入力電流と入力電圧の間の位相補正です。この式では、PhaseCorrection。が正になると、電流の方が電圧より位相が遅れている状況を補正し、PhaseCorrection。が負になると、カレント・トランスで生じる事例のように、電流の方が電圧より位相が進んでいる状況を補正します。

Phase Correction° =

$$\arctan\left(\frac{-\sin\omega}{xPHCALx \times 2^{-27} + \cos\omega}\right)$$

$-\arctan\left(\frac{-xPHCALx \times 2^{-27} \times \sin\omega}{1 + xPHCALx \times 2^{-27} + \cos\omega}\right)$

$\text{CCC}, \ \omega = 2 \times \pi \times f_{LINE}/f_{DSP} \text{C}_{\bullet}$

xPHCALx レジスタの値は、目的の位相補正値を基に次式に従って計算できます。

$$xPHCALx = \left(\frac{\sin(\varphi - \omega) + \sin \omega}{\sin(2 \times \omega - \varphi)}\right) \times 2^{27}$$

例えば、 $f_{LINE}=50$ Hz、 $f_{DSP}=8$ kHz で、電流の方が電圧より位相が  $0.1^{\circ}$ 進んでいる場合、Phase Correction $^{\circ}=-0.1^{\circ}$ です。これを補正するには、 $xPHCALx=0xFFD3\_7760$  を書き込みます。

$$\omega = 2 \times \pi \times 50/8000 = 0.03927$$

$$xPHCALx = \left(\frac{\sin(RADIANS(-0.1) - 0.03927) + \sin 0.03927}{\sin(2 \times 0.03927 - RADIANS(-0.1))} \right) \times 2^{27}$$

$$= -2918553 = 0 \text{xFFD3}\_7767$$

図 13.カレント・トランスの位相補償例、電流の方が電圧より位相が進んでいる場合

図 14.電流の方が電圧より位相が遅れている場合の位相補償例

前の式を使用すると、60Hzでは、電圧チャンネルの遅延が 2.7°であることが分かります。

Voltage Channel Delay° =

$$\left(\frac{60}{8000} \times 360^{\circ}\right) = 2.7^{\circ}$$

このため、位相のキャリブレーション範囲は 60 Hz では  $-15^{\circ}$ ~ $+2.7^{\circ}$ になります。

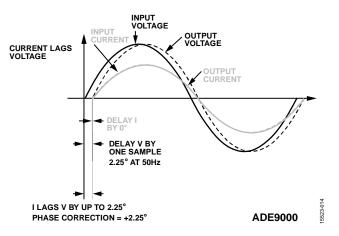

#### 位相/ゲインのマルチポイント・キャリブレーション

ADE9000 では、電流チャンネルのゲインと位相の補償を xIRMS での入力電流の実効振幅計算値の関数として変化させることができます。この機能は、カレント・トランス・センサーの非直線性を補正して、非常に高い精度 (例えばクラス 0.2 のメータ) を実現します。

## ゲインと位相のマルチポイント補償

xIRMS 入力信号レベルにかかわらず適用される電流チャンネル・ゲイン(xIGAIN)があります。このゲインは、カレント・トランスとバーデン抵抗を含めた電流チャンネルの公称ゲイン誤差を補償します。位相とゲインのマルチポイント補償をイネーブルにすると、xIRMS の値に応じて付加的な電流ゲインの値が適用され、入力信号の全振幅にわたってカレント・トランスのゲイン・シフトが補償されます。

MTEN = 1 を設定して、位相とゲインのマルチポイント 補償がイネーブルされている場合は、図 15 に示すように、xIRMS 電流実効値振幅と MTTHR\_Lx レジスタおよび MTTHR\_Hx レジスタの値に基づき、追加のゲイン係数 xIGAIN0~xIGAIN5 が適用されます。

同様に、位相補償では、位相とゲインのマルチポイント 補償をイネーブルにすると、適用される電流チャンネルの 位相補償は、xIRMS 入力信号レベルに応じて変化します。

図 15.位相とゲインのマルチポイント・キャリブレーション

MTTHR\_Lx レジスタおよび MTTHR\_Hx レジスタは、 一連の補正の適用先となる範囲を設定して、ヒステリシ スを許容します。

どの係数を適用するかは、以下の規則に従って決定されます。

If xIRMS >MTTHR\_H[current\_region]

If current\_region <=3

Current\_region++;

Else If xIRMS >MTTHR\_L[current\_region]

If current\_region >=1

current\_region--;

xIGAIN = xIGAIN[current\_region];

xPHCAL = xPHCAL[current\_region];

例えば、AIRMS が MTTHR\_H2 より大きくなると、位相とゲインの補正はそれぞれ AIGAIN3 と APHCAL3 に設定されます。その後、AIRMS が MTTHR\_L3 より小さくなると、位相とゲインの補正はそれぞれ AIGAIN2と APHCAL2 に設定されます。

正常な動作にするため、レジスタの値は

MTTHR\_L[0] < MTTHR\_L[1] < MTTHR\_H[0] < MTTHR\_L[2] < MTTHR\_H[1] < MTTHR\_L[3] < MTTHR\_H[2] < MTTHR\_L[4] < MTTHR\_H[3] < MTTHR\_H[4] にする必要があります。

位相とゲインのマルチポイント・キャリブレーションは、 デフォルトでは無効になっています。有効にするには、 CONFIGO レジスタの MTEN ビットをセットします。

## ゲインと位相のシングルポイント・キャリブレーション

位相とゲインのマルチポイント・キャリブレーションが無効の場合は、位相とゲインのシングルポイント・キャリブレーションが可能です。

この場合には、xIGAIN レジスタが適用されます。 xIRMS 振幅に応じて付加的な電流チャンネル・ゲインが 適用されることはありません。

位相とゲインのマルチポイント・キャリブレーションが 無効の場合は、xIRMS の値に関係なく、xPHCALO の位 相補償が常に適用されます。

#### 電圧チャンネルの測定

表 7 に、電圧チャンネルの測定値を保持するレジスタと 更新時のレートを示します。

表 7. 電圧チャンネル測定の更新レート

| レジスタ名           | 説明                          | 更新レート                      |

|-----------------|-----------------------------|----------------------------|

| AV_SINC_DAT     | VA sinc4 フィルタ出力             | 32 ksps                    |

| $BV\_SINC\_DAT$ | VB sinc4 フィルタ出力             | $32  \mathrm{ksps}$        |

| $CV\_SINC\_DAT$ | VC sinc4 フィルタ出力             | $32  \mathrm{ksps}$        |

| AV_LPFDAT       | VA sinc4 + IIR LPF フィルタ出力   | $f_{DSP} = 8 \text{ ksps}$ |

| BV_LPFDAT       | VB sinc4 + IIR LPF フィルタ出力   | $f_{DSP} = 8 \text{ ksps}$ |

| $CV\_LPF\_DAT$  | VC sinc4 + IIR LPF フィルタ出力   | $f_{DSP} = 8 \text{ ksps}$ |

| AV_PCF          | VAでの瞬時電流                    | $f_{DSP} = 8 \text{ ksps}$ |

| $BV\_PCF$       | VBでの瞬時電流                    | $f_{DSP} = 8 \text{ ksps}$ |

| $CV\_PCF$       | VC での瞬時電流                   | $f_{DSP} = 8 \text{ ksps}$ |

| AVRMS           | VA のフィルタベースの総合実効値           | $f_{DSP} = 8 \text{ ksps}$ |

| BVRMS           | VBのフィルタベースの総合実効値            | $f_{DSP} = 8 \text{ ksps}$ |

| CVRMS           | VC のフィルタベースの総合実効値           | $f_{DSP} = 8 \text{ ksps}$ |

| VPEAK           | ピーク電流チャンネルのサンプ              | $f_{DSP} = 8 \text{ ksps}$ |

|                 | ル。ピーク検出のセクションを参<br>照してください。 |                            |

| APERIOD         | VA でのライン周期の測定               | $f_{DSP} = 8 \text{ ksps}$ |

| BPERIOD         | VB でのライン周期の測定               | $f_{DSP} = 8 \text{ ksps}$ |

| CPERIOD         | VC でのライン周期の測定               | $f_{DSP} = 8 \text{ ksps}$ |

| $COM\_PERIOD$   | VA、VB、VC からの合成信号で           | $f_{DSP} = 8 \text{ ksps}$ |

|                 | のライン周期の測定。合成電圧の             |                            |

|                 | ゼロ交差のセクションを参照して<br>ください。    |                            |

| ANGLx_xxx       | 電圧と電流の間の位相角または電             | CLKIN/24 =                 |

|                 | 流間の位相角。角度測定のセク              | $1024  \mathrm{ksps}$      |

|                 | ションを参照してください。               |                            |

### 電圧チャンネルのゲイン

xVGAIN レジスタを使用して、各相の電圧チャンネルを 補正できます。xVGAIN レジスタのスケーリングは xIGAIN レジスタと同じです。詳細については、電流 チャンネル・ゲイン xIGAIN のセクションを参照してく ださい。

### フルスケール時のコード

PGA ゲインを 1 に設定した場合、ADC 入力がフルスケールのときの予想コードを表 8 に示します。

表 8. フルスケール時の ADC コード

| Parameter                                                       | Output Code |

|-----------------------------------------------------------------|-------------|

| Sinc4 Output at 32 ksps                                         | 67,107,786  |

| Dec Output at 8 ksps                                            | 74,518,668  |

| xPCF at 8 ksps                                                  | 74,532,013  |

| Total IRMS and VRMS                                             | 52,702,092  |

| Fundamental IRMS and VRMS                                       | 52,702,092  |

| Total WATT, VAR, and VA                                         | 20,694,066  |

| Fundamental WATT, VAR, and VA                                   | 20,694,066  |

| Fast RMS½                                                       | 52,702,092  |

| $10~\mathrm{Cycle}~\mathrm{RMS}/12~\mathrm{Cycle}~\mathrm{RMS}$ | 52,702,092  |

| Resampled Data                                                  | 18,196      |

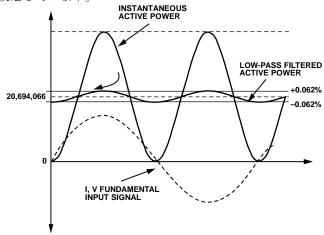

## 電力およびフィルタベースの実効値測定アルゴリズム

## フィルタベースの総合実効値(RMS 値)

ADE9000 は、電流と電圧の実効値を測定します。この値は、入力信号を 2 乗し、ローパス・フィルタ処理して、その結果の平方根を取ることによって算出されます。ローパス・フィルタ LPF2 は、実効値を抽出し、50Hzまたは 60Hz の基本波の高調波を 64dB 以上減衰させます。これにより、フルスケール時には計算上の実効値でのばらつきが非常に小さくなり、誤差は±0.064%になります。入力信号が小さくなるほど測定中のノイズが増えるため、実効読出し値のばらつきが増えることに注意してください。

入力 xP と xN を互いに短絡すると、xRMS レジスタは 0 を読み出しません。

フィルタ・ベースの実効値の帯域幅は  $3.2 \mathrm{kHz}$  です。 チャンネルごとに 1 回の実効値計算(AIRMS、BIRMS、CIRMS 、NIRMS 、AVRMS 、BVRMS 、 お よ び CVRMS)は、 $8 \mathrm{ksps}$  ごとに更新されます。ISUMRMS の計算では、同じ方法を使用して ISUMRMS を算出します。ここで、 $ISUM = IA + IB + IC \pm IN$  であり、やはり  $8 \mathrm{ksps}$  で更新されます(詳細については、中性電流の実効値、ベクトル電流和のセクションを参照してください)

フルスケール時の xRMS の値は 52,702,092 (10 進数) です。フルスケールは PGA ゲインの関数です。

$$full scale = \frac{full scale input at PGA GAIN1}{PGA GAIN}$$

小入力信号(1000:1 未満)時の性能を高めるには、xRMSOS レジスタを使用してこの測定のオフセットを補正することを推奨します。良好な性能が要求される最小の入力信号でオフセットを補正することを推奨します。入力信号がゼロのときにこの測定を補正しないでください。

次式は、xRMSOS レジスタの値が xRMS レジスタの結果をどのように変更するかを示しています。

$$xxRMS = \sqrt{xxRMS_0^2 + 2^{15} \times xxRMSOS}$$

ここで、 $xxRMS_0$  は、オフセット・キャリブレーション前の xRMS レジスタの初期値です。

例えば、1000:1 での予想 AIRMS が 52,702,092/1000 = 52,702(10 進数)で、AIRMS レジスタの読出し値が 53280(10 進数)の場合、オフセット・キャリブレーション・レジスタは次のようになります。

$$AIRMSOS = \frac{52702^2 - 53280^2}{2^{15}} = -1869d = 0xFFFF8B8$$

表 9 に、50Hz 信号でのフルスケールの 99%までの実効 セトリング時間を示します。

表 9. 実効セトリング時間

| Configuration                       | RMS Settling Time,<br>FS = 99% (sec) |

|-------------------------------------|--------------------------------------|

| Integrator On, HPF On, and LPF2 On  | 0.54                                 |

| Integrator Off, HPF On, and LPF2 On | 0.48                                 |

## 中性電流の実効値、ベクトル電流和

ADE9000 は、中性電流センサー入力から INP ピンおよび INN ピンに流れ込む中性電流の実効値を計算して、その結果を NIRMS レジスタに格納します。NIRMSOS レジスタでは、この測定のオフセット・キャリブレーションが可能です。スケーリングは他の xIRMS レジスタや xIRMSOS レジスタの場合と同じです(詳細については、フィルタベースの総合実効値(RMS 値)のセクションを参照してください)。

また、ADE9000 は、 $IA + IB + IC \pm IN$  の和の実効値を計算して、その結果を ISUMRMS レジスタに格納します。 ISUMRMSOS レジスタでは、この測定のオフセット・キャリブレーションが可能です。スケーリングは他の xIRMS レジスタや xIRMSOS レジスタの場合と同じです (詳細については、フィルタベースの総合実効値 (RMS 値) のセクションを参照してください)。

中性電流センサーを使用しない場合は、CONFIGO レジスタの ISUM\_CFG[1:0]ビットに 0 を書き込みます。これにより、ISUMRMS は IA、IB、および IC の和から中性電流を概算します。

中性電流の測定値  $NI_PCF$  が電流チャンネル波形  $AI_PCF + BI_PCF + CI_PCF$  の和からずれる場合は、システム内に障害が発生している可能性があります。

中性電流の測定値と A、B、C の電流の測定値との間の不一致がどの程度大きいかを調べるには、他の電流チャンネルの波形を基準にした中性電流の方向に基づいて、ISUM CFG[1:0]に 01 または 10 を選択します。

表 10. Isum の構成オプション

| CONFIG0.      |                                          |

|---------------|------------------------------------------|

| ISUM_CFG[1:0] | ISUM calculation                         |

| 00, 11        | ISUM = AI_PCF + BI_PCF + CI_PCF          |

| 01            | ISUM = AI_PCF + BI_PCF + CI_PCF + NI_PCF |

| 10            | ISUM = AI_PCF + BI_PCF + CI_PCF - NI_PCF |

ISUMRMS のスケーリングは xIRMS と同じです。 AI\_PCF、BI\_PCF、および CI\_PCF が全てフルスケールで、互いに位相が揃っている場合、ISUM\_CFG[1:0]を 00 または 11 にすると、ISUMRMS は  $3\times52,702,092=158,106,276$ (10 進数)になります。AI\_PCF、BI\_PCF、CI\_PCF、および NI\_PCF が全てフルスケールで、互いに位相が揃っている場合、ISUM\_CFG[1:0]を 01 にすると、ISUMRMS は  $4\times52,702,092=210,808,368$ (10 進数)になります。

ISUMRMS が閾値を超えたかどうかを表示するには、ISUMLVL を設定します。その後、STATUSO のMISMTCH ビットと関連の割込みが、ISUMRMS とISUMLVL との関係に変化があったかどうかを示します。ISUMLVL の目標値を次式に従って計算します。

$$ISUMLVL = \left(\frac{xIRMS\_FULL\_SCALE}{x}\right)$$

ここで、

$xIRMS\_Full\_Scale$  は、フルスケール入力時の xIRMS の 公称値で、52,702,092 です。

Xは、MISMTCH 誤差を示すための目的の電流レベルです。

例えば、ISUMLVL を設定して、フルスケールからの誤差が 10,000:1 より大きいベクトル電流和について警告するには、前の式で X = 10,000 にします。

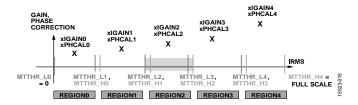

#### 総合有効電力

総合有効電力は、一般に課金の目的で使用されます。これには、基本波での電力と高調波での電力が含まれます。各相の総合有効電力を計算するには、まず  $xI_PCF$  の波形と  $xV_PCF$  の波形を掛け合わせます。次に、CONFIGO レジスタの DISAPLPF ビットが 1 でない限り、結果はローパス・フィルタで処理されます。最後に、xPGAIN を適用してゲイン補正を実行し、xWATTOS の値を適用して WATT のオフセットを補正します。

図 16 は、入力信号 I および V と、瞬時の有効電力との 関係、およびローパス・フィルタ処理後の有効電力との 関係を示します。I および V はフルスケールで基本波の みが存在し、力率が 1 であると仮定しています。

CONFIGO の DISAPLPF ビットが 1 である場合、xWATT は瞬時の有効電力を表し、0 である場合、xWATT はローパス・フィルタ処理後の有効電力を表します。図 16 では、xPGAIN = 0 および xWATTOS = 0 と仮定しています。

図 16. 力率が 1 のときの瞬時の有効電力とローパス・フィルタ処理後の有効電力

ローパス・フィルタ LPF2 は、総合有効電力を抽出し、50 Hz または 60 Hz の基本波の高調波を 64 dB 減衰させます。これにより、フルスケール時にはローパス・フィルタ 処理後の有効電力でのばらつきが非常に小さく( $\pm 0.062\%$ ) なります。

この結果として得られた xWATT 信号の更新レートは 8ksps で、帯域幅は 3.2kHz です。

xPGAIN レジスタのスケーリングは xIGAIN レジスタと同じです。xWATTOS のスケーリングは xWATT と同じです。xWATT は電力量レジスタまたは電力レジスタを使用して補正できます。電力レジスタを使用する場合、xWATTOS は次式を使用して算出されます。

$xWATTOS = xWATT_{EXPECTED} - xWATT_{MEASURED}$

フルスケール入力でゲインがない場合の xWATT の値は 20,694,066 です。xVAR と VA のスケーリングは同じなので、3 つのオフセット全てに対して同じ式を使用できます。

## ADE9000 テクニカル・リファレンス・マニュアル

変数 X は補正する最小の電力レベルです。例えば、フルスケールから 10,000 のレベルで電力量を補正するには、前の式で X=10,000 にします。

$$xWATTOS = \frac{1}{\frac{20694066}{10,000}} = 0.05\%$$

**xWATTOS** レジスタの各ビットは、10,000:1 で 0.05%の 誤差を補正できます。大半のアプリケーションでは、**xWATTOS** がゼロのときでも、小入力での総合有効電力性能は十分です。

表 11 に、50Hz 信号での総合有効電力のセトリング時間を示します。

表 11. 総合有効電力のセトリング時間

|                                         | Total Active Power Settling Time (sec) |             |

|-----------------------------------------|----------------------------------------|-------------|

| Configuration                           | FS = 99%                               | FS = 99.90% |

| Integrator On, HPF On, and LPF2 On      | 0.43                                   | 0.66        |

| Integrator Off, HPF<br>On, and LPF2 On  | 0.43                                   | 0.66        |

| Integrator Off, HPF<br>On, and LPF2 Off | 0.01                                   | 0.06        |

#### 総合無効電力

総合無効電力には、基本波での無効電力と高調波での無効電力が含まれます。電流チャンネル  $xI_PCF$  は、基本波の場合と全高調波の場合とで  $90^\circ$ ンフトします。この信号は、次に電圧波形  $xV_PCF$  と掛け合わされます。 CONFIGO レジスタの DISRPLPF ビットが 1 でない限り、結果はローパス・フィルタで処理されます。最後に、xPGAIN を適用してゲイン補正を実行し、xVAROS の値を適用して VAR のオフセットを補正します。大半のアプリケーションでは、xVAROS がゼロのときでも、小入力での総合無効電力性能は十分です。

力率が 0 のときの総合無効電力のリップルは、力率が 1 のときの総合有効電力のリップルと同様です(図 16 参照)。

この結果として得られた AVAR 信号の更新レートは 8ksps で、帯域幅は 3.2kHz です。

無効電力の計算を無効にするには、 $VAR_DIS$  レジスタの VARDIS ビットをセットします。正常動作を確保するため、このビットは RUN ビットを書き込む前にセットする必要があります。

総合無効電力のオフセットは、xVAROS レジスタを使用することにより、広いダイナミック・レンジにわたって更に高い性能が得られるよう補正できます。xVAROS のスケーリングは xVAR と同じです。このレジスタ値を計算する方法を理解するには、総合有効電力のセクションを参照してください。表 12 に、50Hz 信号での総合無効電力のセトリング時間を示します。

表 12. 総合無効電力のセトリング時間

|                                         | Total Reactive Power Settling Time (sec) |             |

|-----------------------------------------|------------------------------------------|-------------|

| Configuration                           | FS = 99%                                 | FS = 99.90% |

| Integrator On, HPF<br>On, and LPF2 On   | 0.43                                     | 0.59        |

| Integrator Off, HPF<br>On, and LPF2 On  | 0.43                                     | 0.59        |

| Integrator Off, HPF<br>On, and LPF2 Off | 0.02                                     | 0.05        |

#### 総合皮相電力

皮相電力は、電流の実効測定値 xIRMS と対応する電圧の実効値 xVRMS を掛け合わせ、その後ゲイン補正 xPGAIN を適用することで生成されます。結果は xVA レジスタに格納されます。総合皮相電力のオフセットは、xIRMSOS レジスタと xVRMSOS レジスタを使用して、xIRMS と xVRMS の測定値を補正することによって計算します。実効値計算の詳細については、フィルタベースの総合実効値(RMS 値)のセクションを参照してください。

この結果として得られた xVA 信号の更新レートは 8ksps で、帯域幅は 3.2kHz です。

アプリケーションによっては、電圧チャンネルの入力に不正な変更が検出された場合、電圧が公称レベルであることを前提に、皮相電力量を積算することを推奨します。ADE9000 はレジスタ VNOM を備えており、一例として240Vrms に対応する値に設定できます。CONFIGO レジスタの VNOMx\_EN ビットをセットすると、xVA の計算時に VNOM は xIRMS と掛け合わされます。

表 13 に、50Hz 信号での総合皮相電力のセトリング時間を示します。

表 13. 総合皮相電力のセトリング時間

| Configuration                         | Total Apparent Power Settling Time,<br>FS = 99% (sec) |

|---------------------------------------|-------------------------------------------------------|

| Integrator On, HPF On,<br>and LPF2 On | 0.54                                                  |

## 基本波の測定

ADE9000 は独自のアルゴリズムを使用して全測定信号から基本波信号を抽出し、基本波の IRMS、VRMS、WATT、VAR、VA、ITHD、VTHD などの測定を行います。このアルゴリズムでは、回路周波数の初期化と、電圧チャンネルで測定された公称電圧の初期化が必要です。ACCMODE レジスタの SELFREQ ビットは、システムが 50Hz であるか 60Hz であるかを選択します。50Hz システムの場合は、SELFREQ ビットをクリアします。60Hz システムの場合は、SELFREQ ビットを 1 に設定します。SELFREQ を先に選択してから、RUN レジスタに 1 を書き込む必要があります。

VLEVEL レジスタは、電圧チャンネルの公称値を示します。次式に従って VLEVEL を計算します。

$VLEVEL = X \times 1,114,084$

ここで X は、公称入力信号がフルスケールを基準にしている場合のダイナミック・レンジです。

公称電圧 (例えば 240Vrms) が ADE9000 のアナログ入

## ADE9000 テクニカル・リファレンス・マニュアル

力信号範囲の半分と一致するように電圧チャンネルの入力を設定することを推奨します。ADE9000 は $\pm 1V$  ピーク、0.707Vrms の入力をサポートできます。したがって、電圧チャンネルの入力を 0.353Vrms に調整することを推奨します。そうすると、公称 240V の場合は、入力信号がフルスケールの半分になり、X は 2 になります。 574,042(10 進数)を VLEVEL レジスタに書き込んで、この機能を次のように設定します。

#### $VLEVEL = 2 \times 1,114,084 = 2,288,168$

これら 2 つのパラメータ(SELFREQ および VLEVEL)を設定後、ADE9000 は、SELFREQ で選択された 50Hz または 60Hz の周波数の $\pm 5$ Hz 以内で基本波のライン周波数を追跡します。アプリケーションで $\pm 5$ Hz より広い周波数範囲が必要な場合は、ライン周期  $\mathbf{xPERIOD}$  をモニタし、それに応じて  $\mathbf{SELFREQ}$  の選択も変更します。RUN レジスタは  $\mathbf{0}$  に設定してから  $\mathbf{SELFREQ}$  の設定を変更し、その後でもう一度  $\mathbf{1}$  に設定する必要があります。

## 基本波の実効値

ADE9000 は、基本波の測定のセクションに説明されている独自の基本波推定技法を使用して、基本波の電流および電圧の実効値を測定します。xIFRMSOS レジスタおよび xVFRMSOS レジスタを使用すると、入力信号レベルが低いときに更に高い性能が得られるようオフセットを補正できます。

入力  $\mathbf{xP}$  と  $\mathbf{xN}$  を互いに短絡すると、 $\mathbf{xFRMS}$  レジスタは  $\mathbf{0}$  を読み出しません。

チャンネルごとに 1 回の基本波実効値計算(AIFRMS、BIFRMS、CIFRMS、AVFRMS、BVFRMS、および CVFRMS)は、8ksps ごとに更新されます。中性電流 チャンネルには、基本波の実効値測定機能はありません。フルスケール時の xFRMS の値は 52,702,092(10 進数)です。

小入力信号(1000:1 未満)時の性能を高めるには、xFRMSOS レジスタを使用してこの測定のオフセットを補正することを推奨します。良好な性能が要求される最小の入力信号でオフセットを補正することを推奨します。入力信号がゼロのときにこの測定を補正しないでください。

次式は、xFRMSOS レジスタの値が xFRMS レジスタの 結果をどのように変更するかを示しています。

$$xxFRMS = \sqrt{xxFRMS_0^2 + 2^{15} \times xxFRMSOS}$$

ここで、*xxFRMS*<sub>0</sub>は、オフセット・キャリブレーション 前の xFRMS レジスタの初期値です。

## 基本波の有効電力

ADE9000 は、独自の基本波推定技法を使用して、基本波の有効電力を測定します。基本波の有効電力は、その後 xPGAIN によってゲインが補正され、xFWATTOS レジスタに従ってオフセット補正が適用されます。

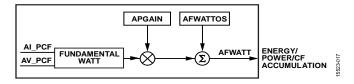

xFWATTOS レジスタを使用すると、入力信号レベルが 低いときに更に高い性能を得るオフセット・キャリブ レーションが可能です。図 17 に、AFWATT 測定のシグナル・チェーンを示します。

図 17. 基本波の WATT、AFWATT 計算

xFWATTO のスケーリングは xFWATT と同じです。こ のレジスタ値を計算する方法を理解するには、総合有効 電力のセクションを参照してください。

#### 基本波の無効電力

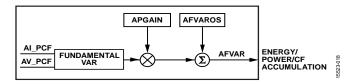

ADE9000 は、独自の基本波推定技法を使用して、基本波の無効電力を測定します。これは、その後 xPGAIN によってゲインが補正され、xFVAROS レジスタに従ってオフセット補正が適用されます。図 18 に、AFVAR 測定のシグナル・チェーンを示します。

図 18. 基本波の無効電力、AFVAR

力率が 0 のときの基本波無効電力のリップルは、力率が 1 のときの総合有効電力のリップルと同様です(図 16 参照)。

xFVAROS のスケーリングは xFVAR と同じです。この レジスタ値を計算する方法を理解するには、総合有効電 力のセクションを参照してください。

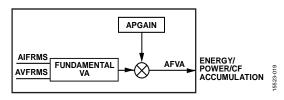

## 基本波の皮相電力

ADE9000 は、基本波の測定と基本波の実効値のセクションに説明されている独自の基本波推定技法を使用して、基本波の実効値を測定します。基本波の実効測定値(xIFRMS および xVFRMS) は、基本波の皮相電力を得るため、互いに掛け合わされます。この値は、その後xPGAIN によってゲインが補正され、xFVA レジスタに格納されます。図 19 に、AFVA 測定のシグナル・チェーンを示します。

オフセットの補正は、AIFRMS と AVFRMS の測定値を 補正することで実行できることに注意してください。

図 19. 基本波の皮相電力、AFVA

#### 電力量測定の概要

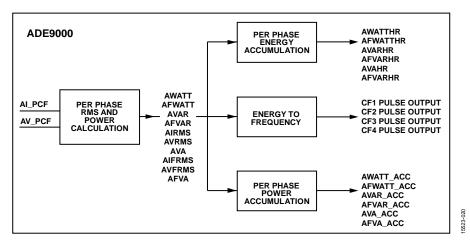

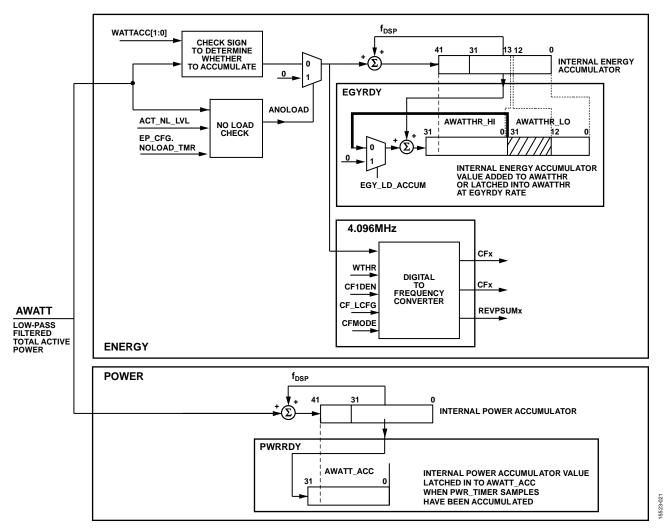

図 20. xI\_PCF と xV\_PCF の波形に基づく相ごとの電力および電力量の計算

図 20 は、AI\_PCF と AV\_PCF を使用して相ごとの実効値および電力をどのように計算するか、これらの計算値を AWATTHR レジスタおよび AWATT\_ACC レジスタにどのように積算するか、更にはどのように CFx パルス出力を設定するかを示しています。

#### 相ごとの電力量測定値の更新レート

**xWATT、xVAR、xVA、xFVAR** など、瞬時の電力測定値は、f<sub>DSP</sub> = 8ksps のレートで更新されます。

これらの測定値は  $xWATT\_ACC$  レジスタの電力測定値に 積算され、 $PWR\_TIME$  レジスタでの選択内容に応じて、 最大 1 秒のユーザ定義間隔で更新されます。

電力量の測定値は、デフォルトでは fosp = 8ksps ごとに 更新され、フルスケール時には最大 106 秒の積算値を格 納できます。あるいは、ユーザ定義のライン・サイクル数 またはサンプル数に達したらレジスタを更新する別の積算 モードにこれらのレジスタを設定することもできます。

力率、ITHD、および VTHD の測定値は、4096/8ksps = 1.024 秒ごとに更新されます。

RMS½の測定値は、½ライン・サイクル (50Hz 時は 10ms) ごとに更新されます。

10 サイクルの実効測定値/12 サイクルの実効測定値は、50Hz 回路では 10 サイクルごとに、60Hz 回路では 12 サイクルごとに更新されます。ACCMODE レジスタの SELFREQ ビットは、どの回路を使用するかを定義します。

表 14. WATT 関連レジスタの更新レート

| 表 14. WATT 関連レジスタの更新レート<br> |                                                              |                                                                  |  |

|-----------------------------|--------------------------------------------------------------|------------------------------------------------------------------|--|

| レジスタ名                       | 説明                                                           | 更新レート                                                            |  |

| AWATT                       | A相でのローパス・フィルタ処理後の総合有効電力                                      | 8ksps                                                            |  |

| BWATT                       | B相でのローパ<br>ス・フィルタ処理<br>後の総合有効電力                              | 8ksps                                                            |  |

| CWATT                       | <ul><li>C 相でのローパ</li><li>ス・フィルタ処理</li><li>後の総合有効電力</li></ul> | 8ksps                                                            |  |

| AWATT_<br>ACC               | A 相での積算総合<br>有効電力                                            | PWR_TIME の 8ksps サンプ<br>リング後、250μs~1.024 秒                       |  |

| BWATT_<br>ACC               | B相での積算総合<br>有効電力                                             | PWR_TIME の 8ksps サンプ<br>リング後、250μs~1.024 秒                       |  |

| CWATT_<br>ACC               | C 相での積算総合<br>有効電力                                            | PWR_TIME の 8ksps サンプ<br>リング後、250μs~1.024 秒                       |  |

| AWATTHR                     | A 相での積算総合<br>有効電力量                                           | EP_CFG および EP_TIME<br>での設定に従って、フルス<br>ケール時に電力量を最大 106<br>秒保持します。 |  |

| BWATTHR                     | B相での積算総合<br>有効電力量                                            | EP_CFG および EP_TIME<br>での設定に従って、フルス<br>ケール時に電力量を最大 106<br>秒保持します。 |  |

| CWATTHR                     | C 相での積算総合<br>有効電力量                                           | EP_CFG および EP_TIME<br>での設定に従って、フルス<br>ケール時に電力量を最大 106<br>秒保持します。 |  |

| APF                         | A相の力率 <sup>1</sup>                                           | 1.024 秒ごと                                                        |  |

| BPF                         | B相の力率 1                                                      | 1.024 秒ごと                                                        |  |

| CPF                         | C相の力率 <sup>1</sup>                                           | 1.024 秒ごと                                                        |  |

<sup>「</sup>力率のセクションを参照してください。

Rev. 0 — 17/86 —

#### 電力量の積算

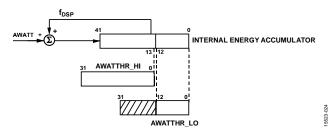

図 21.無負荷閾値および符号付き積算モードを使用した電力量および電力計算のための AWATT 積算器

図 21 に、AWATT が AWATTHR レジスタと AWATT\_ACC レジスタにどのように積算されるかを示します。無負荷 閾値が適用され、電力量がチェックされて、AWATT の サンプルを内部の電力量積算器に積算するかどうかを決定します。内部の電力量積算器は AWATTHR レジスタに 加算されるか、AWATTHR レジスタを EGYRDY のレートで上書きします。  $EP\_CFG$  レジスタの  $EGY\_PWR\_EN$  ビットをセットして、電力量積算器と電力積算器を動作させます。

#### 電力量の符号付き積算モード

#### 有効電力量の総合積算モード

実装形態によっては、正の総合有効電力量のみを課金することが望まれます。ADE9000 は、ACCMODE レジスタの WATTACC[1:0]ビットを使用することでこれを実行できます。総合および基本波の有効電力量の積算と、対応する CF パルス出力を正の電力量のみに対して設定するには、WATTACC[1:0]に 10 を書き込みます。

WATTACC[1:0]を 0 にすると、電力量の積算は符号付きになります。AWATTHR\_HI レジスタと AFWATTHR\_HI レ

ジスタの MSB は、積算電力量が負か正かを示します。 その他の積算モードには、WATTACC[1:0]が 01 のとき の(AWATT の絶対値が積算される)絶対値積算モード や、WATTACC[1:0]が 11 のときの(負の有効電力量の みが積算される)負の値限定の積算モードがあります。

#### 無効電力量の積算モード

無効電力量は誘導性負荷や容量性負荷によって正の値と 負の値の間を頻繁に変動することがあるので、実装形態 によっては、無効電力量の絶対値に対して課金すること が望まれます。ADE9000 は、ACCMODE レジスタの VARACC[1:0]ビットを使用することでこれを実行できま す。総合および基本波の無効電力量レジスタと、対応す る CF パルス出力を設定して、無効電力量の絶対値を積 算するには、VARACC[1:0]に 01 を書き込みます。

VARACC[1:0]を 0 にすると、総合と基本波の無効電力量の積算は符号付きになります。AVARHR\_HI レジスタとAFAVARHR\_HI レジスタの MSB は、電力量が負か正かを示します。

用意されているその他の積算モードには、VARACC[1:0] が 10 のときの正の値限定の積算モードや、VARACC[1:0]

Rev. 0 — 18/86 —

が11のときの(負の無効電力量のみが積算される) 負の 値限定の積算モードがあります。

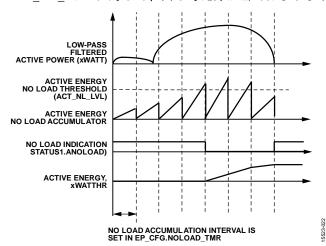

#### 無負荷検出

無負荷検出は、入力電流が電力量計の所定の起動電流よりも少ない場合、ノイズによる電力量の積算を防止します。 無負荷状態が存在するかどうかを判別するため、 ADE9000 は、積算電力量がユーザ定義の期間にわたってユーザ定義の関値より低くなっているかどうかを、相ごとおよび電力量ごとに評価します。

表 15 で説明しているように、 $EP\_CFG$  レジスタの  $NOLOAD\_TMR[2:0]$ ビットに数値を書き込むことにより、64 サンプル~4096 サンプル、64/8ksps = 8ms~512ms の範囲で無負荷状態を評価するかどうかを決定します。 無負荷検出は、デフォルトでは 64/8ksps = 8ms の最小時間にわたって有効になっています。  $EP\_CFG$  の  $NOLOAD\_TMR[2:0]$ ビットを 111 (2 進数) にすると、 無負荷検出は無効になります。

表 15. 無負荷状態の評価時間

| NOLOAD_TMR[2:0] | Samples to<br>Evaluate No Load<br>Over | Time that No-Load<br>Detection is Evaluated<br>Over |

|-----------------|----------------------------------------|-----------------------------------------------------|

| 0               | 64                                     | 8 ms                                                |

| 1               | 128                                    | 16 ms                                               |

| 2               | 256                                    | 32 ms                                               |

| 3               | 512                                    | 64 ms                                               |

| 4               | 1024                                   | 128 ms                                              |

| 5               | 2048                                   | 256 ms                                              |

| 6               | 4096                                   | 512 ms                                              |

| 7               | No-load disabled                       | No-load disabled                                    |

ユーザ定義の無負荷閾値は、ACT\_NL\_LVL、REACT\_NL\_LVL、および APP\_NL\_LVL レジスタに書き込まれます。ACT\_NL\_LVL レジスタは、総合と基本波の有効電力量に対して無負荷閾値を設定します。同様に、REACT\_NL\_LVL レジスタは総合と基本波の無効電力量に対して無負荷閾値を設定し、更に APP\_NL\_LVLレジスタは総合と基本波の皮相電力量に対して無負荷閾値を設定します。

無負荷閾値は次式に従って計算されます。

$$xNL\_LVL = \left(\frac{xWATT\_FULL\_SCALE \times 64}{X}\right)$$

ここで、

$xWATT\_Full\_Scale$  は、フルスケール入力時の xWATT の公称値で、20,694,066 です。xVAR と VA のスケーリングは同じなので、3 つの閾値全てに対して同じ値を使用できます。

X は、目的の無負荷時入力電力レベルです。例えば、無負荷閾値を設定して、フルスケールから 50,000 未満の値まで電力量を低減するには、前の式で X=50,000 にします。そうすると、50,000:1 の無負荷閾値レベルにするには、xNL LVL は 0x6804 となります。

$$xNL_LVL = \left(\frac{20,694,066 \times 64}{50000}\right) = 26,488 = 0x6778$$

ある相が無負荷のときは、 $f_{DSP}$  = 8ksps のたびに電力量 レジスタと CF 積算値に積算される電力量はゼロです。  $x\_ACC$  レジスタは無負荷検出に影響されません。無負荷 時であっても、xWATT、xVAR、xVA の各レジスタで計算された電力は、 $f_{DSP}$  = 8ksps ごとに対応する  $x\_ACC$  レジスタに積算されます。

#### 無負荷表示

PHNOLOAD レジスタは、電力量の各相が無負荷状態であるかどうかを示します。例えば、PHNOLOAD レジスタの PHATNL[2:0]ビットは、A 相の総合皮相電力量、無効電力量、および有効電力量の位相が揃っているかどうかを、それぞれビット 2~ビット 0 に示します。ビットがセットされている場合は、その相の電力量が無負荷状態であることを示します。ビットがクリアされている場合、その相が無負荷状態ではないことを示します。無負荷状態になる場合も無負荷状態から抜け出す場合も、無負荷状態になる場合も無負荷状態から抜け出す場合も、

相ごとの電力量無負荷ステータスのいずれかが変化すると生じる割込みを有効にすることができます。電力量の種類ごとに割込みイネーブル・ビットがあります。STATUS1 レジスタの VAFNOLOAD、RFNOLOAD、AFNOLOAD、VANLOAD、RNLOAD、およびANLOAD ビットをセットして、基本波 VA、基本波 VAR、基本波 WATT、総合 VA、総合 VAR、および総合 WATT 無負荷状態の 1 つまたは複数の相でステータスが

また、 $\overline{\text{EVENT}}$ ピンでの無負荷ステータスを表示するオプションもあります。詳細については、割込み/ $\overline{\text{EVENT}}$ のセクションを参照してください。

変化したら、 $\overline{IRQ1}$ での割込みを有効にします。

図 22 は、xWATT(ローパス・フィルタ処理後のWATT)の値がユーザ設定の無負荷閾値を超えてから再びその閾値より低くなると何が起こるかを示しています。電力量の全ての値(総合と基本波のVAR、総合VA)と対応する無負荷閾値REACT\_NL\_LNL およびAPP NL LVLに対して、同じ考え方が当てはまります。

図 22. 無負荷の検出と表示

Rev. 0 — 19/86 —

## 電力量積算の詳細

## 内部電力量レジスタのオーバーフロー・レート

図 21 に示すように、各電力量積算の位相ごとに 42 ビットの内部符号付き電力量積算器があります。これらの積算器は  $f_{DSP}$  = 8ksps のレートで更新されます。フルスケール入力で、全てのデジタル・ゲインとオフセット係数が 0 のときに、内部積算器がオーバーフローするまでの時間を計算する方法を次式に示します。ここで、AWATT\_AT\_FULL\_SCALE は、フルスケール入力時の公称 AWATT 値を表します。

Maximum Internal Energy Accumulator Time (sec)

$$= \left(\frac{2^{41}}{AWATT\_AT\_FULL\_SCALE \times f_{DSP}}\right)$$

例えば、CONFIGO.MTEN が 0 であり、シングルポイントのゲイン補償で、AIGAIN、AVGAIN、APGAIN、および AWATTOS を全て 0 にした場合、A 相の総合有効電力量のデジタル・ゲインは 1 です。そうすると、内部積算器に積算された A 相の総合有効電力量は、AWATT の公称フルスケール値である 20,694,066 の場合、13.3 秒以内にオーバーフローします。

Maximum Internal Energy Accumulator Time (sec)

$$= \left(\frac{2^{41}}{20,694,066 \times 8000}\right) = 13.3 \text{ sec}$$

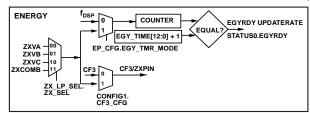

#### ユーザ電力量レジスタの更新レート、EGYRDY

図 21 に示すように、内部の電力量積算器は、EGYRDY のレートで、ユーザ・アクセス可能な電力量レジスタにラッチされるか、ユーザ・アクセス可能なレジスタに追加されます。図 23 は、EGYRDY 更新レートがどのように生成されるかを詳細に説明しています。

EGYRDY 更新 レートは、EP\_CFG レジスタの EGY\_TMR\_MODE ビットに従って、EGY\_TIME + 1 個の  $f_{DSP}$ サンプル後または EGY\_TIME + 1 回のハーフ・ライン・サイクル後に生成されます。

EGY\_TMR\_MODE が 0 の場合、内部電力量レジスタは EGY\_TIME + 1 個のサンプルを 8ksps で積算します。このモードはサンプルベースの積算と呼ばれます。

Internal Energy Accumulation Time (sec)

$$= \left(\frac{EGY\_TIME + 1}{f_{DSP}}\right)$$

EGY\_TIME[12:0] レジスタは、最大(8191 + 1) = 8192 個のサンプルを積算できます。EGY\_TMR\_MODE が 0 である場合、これは 8192/8000 = 1.024 秒に相当します。

Internal Energy Accumulation Time (sec)

$$= \left(\frac{8191+1}{8000}\right) = 1.024 \sec$$

EGY\_TMR\_MODE が 1 の場合、内部電力量レジスタは EGY\_TIME + 1 回のハーフ・ライン・サイクルを 8ksps で積算します。このモードはハーフ・ライン・サイクルベースの積算と呼ばれます。このモードでは、モニタするゼロ交差源は、図 23 に示すように、 $ZX_LP_SEL$  レジスタの  $ZX_SEL$  ビットによって設定されます。

Internal Energy Accumulation Time (sec)

$$= \left(\frac{EGY\_TIME + 1}{ZX \ Rate}\right)$$

ライン周波数が 50Hz の場合、ZX 割込みレートは 100Hz であり、EGY\_TIME が 0x1FFF、8191 (10 進数) の場合、最大積算時間は 81.92 秒です。

Internal Energy Accumulation Time (sec)

$$= \left(\frac{8191+1}{100}\right) = 81.92 \text{ sec}$$

内部電力量レジスタはフルスケール入力時に 13.3 秒以内 にオーバーフローするので、 $EGY\_TMR\_MODE$  が 1 の ときは、 $EGY\_TIME$  を 1329(10 進数)より小さい値に 設定して、オーバーフローを防止する必要があります。

図 23. 更新レート EGYRDY および PWRRDY

#### ユーザ電力量レジスタの再読込みまたは積算

EGYRDY イベントが発生すると、内部電力量の積算値は、EP\_CFG レジスタの EGY\_LD\_ACCUM ビットの状態に基づいて、xWATTHR レジスタに直接読み込まれるか、既存の積算値に加算されます。内部電力量レジスタはリセットされ、再び0からカウントを開始します。

EGY\_LD\_ACCUM が 0 である場合、内部電力量レジスタはユーザ・アクセス可能な電力量レジスタに追加されます。 EGY\_LD\_ACCUM が 1 である場合、内部電力量レジスタはユーザ・アクセス可能な電力量レジスタを上書きします。

## ユーザ電力量レジスタのオーバーフロー・レート

ADE9000 内部の電力量レジスタは、図 24 に示すように、符号付きで 45 ビット幅であり、2 つの 32 ビット・レジスタに分かれています。これらの積算器は、ユーザ電力量レジスタの更新レート、EGYRDY のセクションで説明しているように、EGYRDY に従って一定のレートで更新されます。フルスケール入力で、全てのデジタル・ゲインとオフセット係数が 0 のときに、ユーザ・アクセス可能な積算器がオーバーフローするまでの時間を計算する 方法 を次式に示します。ここで、AWATT\_AT\_FULL\_SCALEは、フルスケール入力時の公称 AWATT 値を表します。この例では、内部電力量レジスタが  $f_{DSP}$  =  $8k_{SPS}$  サンプルごとに更新されていると仮定しています。

Maximum Internal Energy Accumulator Time (sec)

$$= \left(\frac{2^{44}}{AWATT\_AT\_FULL\_SCALE \times f_{DSP}}\right)$$

Rev. 0 — 20/86 —

例えば、CONFIGO レジスタの MTEN ビットが 0 であり、シングルポイントのゲイン補償で、AIGAIN、AVGAIN、APGAIN、および AWATTOS を全て 0 にした場合、A 相の総合有効電力量のデジタル・ゲインは 1 です。そうすると、ユーザ・アクセス可能な積算器に積算された A 相の総合有効電力量は、AWATT の公称フルスケール値である 20,694,066 の場合、106.4 秒以内にオーバーフローします。

Maximum Internal Energy Accumulator Time (sec)

$$= \left(\frac{2^{44}}{20,694,066 \times 8000}\right) = 106.3 \sec$$

## ユーザ電力量レジスタのアクセス

各 45 ビットのユーザ・アクセス可能な符号付き電力量 積算器は、図 24 に示すように、2 つのレジスタ(上位 32 ビットから成るレジスタ  $xHR_HI$  と下位 13 ビットから成るレジスタ  $xHR_LO$ )に分かれています。

図 24. 内部電力量レジスタを AWATTHR\_HI と AWATTHR\_LO に分割

ユーザ電力量の予想積算値は、AWATT の平均値に基づいて、次式に従って計算できます。

$USER\_ENERGY\_ACCUMULATION$ =  $AWATT \times (EGY\_TIME + 1)$

次に、AWATTHR\_HI は上位 32 ビットから成るので、 次式を最も近い整数に丸めることにより計算できます。

#### AWATTHR\_HI

= ROUNDDOWN( $USER\_ENERGY\_ACCUMULATION \times 2^{-13}$ )

USER\_ENERGY\_ACCUMULATION の下位 13 ビットは、AWATTHR\_LO レジスタに格納されます。

#### リセットによるユーザ電力量レジスタの読出し

EP\_CFG レジスタの RD\_RST\_EN ビットをセットした 場合、その内容は、ユーザ・アクセス可能な電力量レジスタが読み出されるとリセットされます。

例えば、AWATTHR\_HI が読み出されると、 AWATTHR\_HI レジスタの値は 0 になります。 AWATTHR\_LO レジスタの内容は変更されません。

## ユーザ電力量レジスタの使用モデル

電力量の積算の主な使用モデルは、次のように 3 つあります。

- リセットによる電力量レジスタの読出し

- 規定のライン・サイクル数にわたる電力量の積算

- 規定のサンプル数にわたる電力量の積算

電力量レジスタをリセットによって読み出すには、以下 の設定を使用します。

- 設定レジスタの設定:

- EP\_CFG レジスタ、EGY\_LD\_ACCUM ビット=0

- EP CFG レジスタ、EGY TMR MODE ビット=0

- EP CFG レジスタ、RD RST EN ビット=1

- EP\_CFG レジスタ、EGY\_PWR\_EN ビット=1

- EGY\_TIME レジスタ = 1

- 出力:xHR\_HI レジスタのみを読み出します。この レジスタは、大半のアプリケーションに対して十分 な分解能を備えています。xHR\_LO レジスタは維持 されて積算されるので、読み出す必要はありません。

- フルスケール入力によるオーバーフローを防止する ため xHR HI を読み出すまでの最大時間: 106 秒。

規定のハーフ・ライン・サイクル数にわたって電力量を 積算するには、以下の設定を使用します。

- 設定レジスタの設定:

- EP\_CFG レジスタ、EGY\_LD\_ACCUM ビット=1

- EP CFG レジスタ、EGY TMR MODE ビット=1

- EP\_CFG レジスタ、RD\_RST\_EN ビット=0

- EP\_CFG レジスタ、EGY\_PWR\_EN ビット=1

- EGY\_TIME レジスタ = 目的のハーフ・ライン・サイクル数

- 出力:

- xHR\_HI レジスタは、大半のアプリケーションに 対して十分な分解能を備えています。

- CF パルス出力との完全な同期を維持するには、 xHR\_LO レジスタも同様に読み出す必要がありま す。このレジスタは EGYRDY サイクルごとにク リアされるためです。

- フルスケール入力によるオーバーフローを防止する ため xHR\_HI を読み出すまでの最大時間:13.3 秒。

規定のサンプル数にわたって電力量を積算するには、以下の設定を使用します。

- 設定レジスタの設定:

- EP\_CFG レジスタ、EGY\_LD\_ACCUM ビット=1

- EP CFG レジスタ、EGY TMR MODE ビット=0

- EP CFG レジスタ、RD RST EN ビット=0

- EP\_CFG レジスタ、EGY\_PWR\_EN ビット=1

- **EGY TIME** レジスタ = 目的のサンプル数

- 出力:

- xHR\_HI レジスタは、大半のアプリケーションに 対して十分な分解能を備えています。

- CF パルス出力との完全な同期を維持するには、 xHR\_LO レジスタも同様に読み出す必要がありま す。このレジスタは EGYRDY サイクルごとにク リアされるためです。

- フルスケール入力によるオーバーフローを防止する ため xHR HI を読み出すまでの最大時間:13.3 秒。

### デジタル/周波数変換-CF 出力

積算する電力量に比例したパルスを、所定のパルス/kWhメータ定数で出力するには、多くの電力量計が必要です。 ADE9000 には 4 つのパルス出力があり、これらは、 CF1 から CF4 までの出力ピンの電力量積算値に比例します。

#### 電力量と相の選択

CFMODE レジスタの CFxSEL[2:0]ビットは、総合または基本波の WATT、VAR、VA など、どのタイプの電力量を CFx ピンに出力するかを選択します。次に、COMPMODE レジスタの TERMSELx ビットは、どの相の電力量を CF出力に組み込むかを選択します。例えば、CFMODE レジスタの CF1SEL[2:0]ビット = 000 で COMPMODE レジスタの TERMSEL1[2:0]ビット = 111 の場合、CF1 は、A 相、B 相、および C 相の総合 WATT 出力を表します。

A 相、B 相、および C 相の総合 WATT 積算値を同時に補正するには、総合 AWATT には CF1 を、総合 BWATT には CF2 を、総合 CWATT には CF3 を使用して、CFMODE レジスタの CF1SEL、CF2SEL、および CF3SEL ビット = 000、COMPMODE レジスタの TERMSEL0[2:0]ビット = 001、COMPMODE レジスタの TERMSEL1[2:0]ビット = 010、COMPMODE レジスタの TERMSEL2[2:0]ビット = 100 を設定します。

#### CFパルス出力の最大周波数の設定

xTHR = 0x0010\_0000 を書き込むことを推奨します。 CFxDEN の範囲は 2~65535 です。CFxDEN を設定し て、CF 周波数出力を調整します。xTHR、CFxDEN、 AWATT の値の関係は、次式で与えられます。

$$CF (Hz) = \left(\frac{f_{DTOF} \times AWATT}{xTHR \times 512 \times CFxDEN}\right)$$

したがって、CF パルス出力の推奨の最大周波数は78.862kHzになります。

$MAXIMUM\_CF$  (Hz)

$$= \left(\frac{4.096 \times 10^6 \times 20,694,066}{0 \times 0010 - 0000 \times 512 \times 2}\right) = 78.9 \text{ kHz}$$

ここで、

$f_{DTOF}$ は 4.096MHz です。

*AWATT*はフルスケール時の値で、20,694,066です。 *xTHR*は 0x0010 0000です。

CFDENは2です。

xTHR のパワーオン・リセット値およびフルスケール入 力での CFxDEN を使用したデフォルトの CF パルス出 力は次のとおりです。

MAXIMUM\_CF (Hz)

$$= \left(\frac{4.096 \times 10^6 \times 20,694,066}{0 \times 0000 \text{ _FFFF} \times 512 \times 0 \times FFFF}\right) = 38.5 \text{ Hz}$$

#### CFパルス幅の設定

パルス幅は CF\_LCFG レジスタの CFx\_LT ビットと CF\_LTMR レジスタの値によって決まります。

CF<sub>x</sub>LT が 0 の場合、 $1/(2 \times 80 \text{ms}) = 6.25 \text{Hz}$  より低い周波数では、アクティブ・ローのパルス幅が 80 ms に設定されます。6.25 Hz より高い周波数では、CF<sub>x</sub>DEN が偶数の場合、デューティ・サイクルは 50%であり、CF<sub>x</sub>DEN が奇数の場合は $(1 + 1/\text{CFxDEN}) \times 50\%$ です。CF<sub>x</sub>LT を 1 に設定した場合、アクティブ・ローの CFパルス幅は CF\_LTMR×6/CLKIN です。CF\_LTMR の最大値は  $327680 = 0x0005\_0000$  です。この結果、327680/(6/CLKIN) = 80 ms のパルスが得られます。CF\_LTMR は 0 より大きくする必要があります。

表 16. CFx\_LT および CF\_LTMR に基づくアクティブ・ローの CF パルス幅およびデューティ・サイクル

| CFx_LT | 低周波数でのアクティブ・<br>ローのパルス幅(ms)                                                                | 高周波数でのアクティブ・<br>ローのパルス幅<br>(CFxDEN が偶数のとき) | 高周波数でのアクティブ・<br>ローのパルス幅<br>(CFxDEN が奇数のとき) | 無負荷になったときの動作                                   |

|--------|--------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|------------------------------------------------|

| 0      | 80                                                                                         | 50%                                        | $(1 + 1/\text{CFxDEN}) \times 50\%$        | Cfx がローの場合、電流パルスを<br>終了し、ハイに戻ります。              |

| 1      | $\begin{array}{c} \text{CF\_LTMR} \times \text{6/CLKIN} \times \\ \text{1000} \end{array}$ | 50%                                        | $(1 + 1/\text{CFxDEN}) \times 50\%$        | Cfx がローの場合、無負荷状態が<br>終了するまで CFx をローに維持し<br>ます。 |

## CFパルスの符号

アプリケーションによっては、正と負の電力量使用量を別々に記録する必要があります。これを容易にするため、PHSIGN レジスタの SUMxSIGN ビットは、最後の CFx パルスになった電力量の合計が正と負のいずれであったかを示します。 CFx パルスになった電力量の合計が正の場合、SUMxSIGN は 0 であり、電力量の合計が負の場合は 1 になります。

更に、STATUSO レジスタおよび EVENT\_STATUS レジスタの REVPSUMx ビットは、CF の極性が符号を変化させたかどうかを示します。例えば、最後の CF2 パルスが正の無効電力量を表し、次の CF2 パルスが負の無効電力量を表す場合は、STATUSO レジスタと EVENT\_STATUS レジスタの REVPSUM2 ビットがセットされます。このイベントを有効にしてTRQOでの割込みを生成できます。

#### CF 積算器のクリア

例えば、電源投入時や初期化処理時には、部分的な CF 積算値をクリアするのが望ましいことがあります。デジタル/周波数コンバータの積算値と CFDEN カウンタをクリアするには、CONFIG1 レジスタの CF\_ACC\_CLR ビットに 1 を書き込みます。CF\_ACC\_CLR ビットは自動的にクリアされます。

#### CF パルス出力と CFx 割込みの無効化

CFx パルス出力を無効にして CFx 出力をハイに維持するには、CFMODE レジスタの  $CFx_DIS$  ビットに 1 を書き込みます。CFx 出力が無効になっている場合は、新しい CF パルスの準備が整っても STATUSO の CFx ビットはセットされません。CF パルスが正と負のいずれであったかを示す REVPSUMx ビットは、 $CFx_DIS$  設定の影響を受けないことに注意してください。

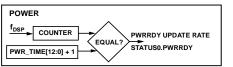

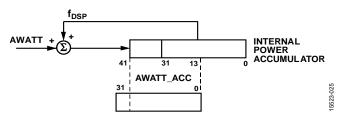

## 電力の積算

図 21 に、AWATT のローパス・フィルタ処理後の有効電力サンプルを積算して、AWATT\_ACC レジスタに正確な有効電力の値を供給する仕組みを示します。A 相の総合有効電力積算値の符号は、REVAPA ステータス・ビットでモニタされ、電力の符号が変化すると割込みが有効になります。各相の電力ごとに対応する  $\mathbf{x}$ \_ACC 積算値があり、STATUSO の REV $\mathbf{x}$  ステータス・ビットは、電力の符号が変化したかどうかを示します。

## 電力積算の詳細

図 21 は、AWATT の値が内部の電力積算器に積算され、 その後、PWRRDY のレートで  $xWATT\_ACC$  レジスタに ラッチされる仕組みを示しています。

PWRRDY は、PWR\_TIME + 1 個のサンプルが 8ksps で 積算された後にセットされます。電力の積算時間は次式 に従って計算できます。

Internal Power Accumulation Time (sec)

$$= \left(\frac{PWR\_TIME + 1}{8000}\right)$$

PWR\_TIME[12:0]レジスタは、最大(8191 + 1) = 8192 個のサンプルを積算できます。これは 8192/8000 = 1.024秒に相当します。

Internal Power Accumulation Time (sec)

$$= \left(\frac{8091 + 1}{8000}\right) = 1.024 \text{ sec}$$

内部の電力積算器は、内部の電力量積算器と同じレート でオーバーフローします(内部電力量レジスタのオー バーフロー・レートのセクションを参照してください)。

#### ユーザ電力レジスタのアクセス

各 42 ビットのユーザ・アクセス可能な符号付き電力積 算器は、図 24 に示すように、上位 32 ビットから成るレ ジスタ x ACC に分かれています。

図 25. 内部電力レジスタと AWATT\_ACC との対応

ユーザ電力の予想積算値は、AWATT の平均値に基づいて、次式に従って計算できます。

$USER\_POWER\_ACCUMULATION = AWATT \times (PWR\_TIME + 1)$

したがって、32 ビット電力積算レジスタの予想データ (xWATT\_ACC、xVAR\_ACC、xVA\_ACC) は次のように計算できます。

Power accumulation register =

ROUNDDOWN( $USER\_POWER\_ACCUMULATION \times 2^{-13}$ )

例えば、AWATT の 4000 個のサンプルを 8ksps、フルスケール入力で積算した場合、AWATT\_ACC の予想値は 0x009B 0003 になります。

$USER\_POWER\_ACCUMULATION = 20,694,066 \times (3999 + 1) = 82776264000$

$AWATT\_ACC$  = ROUNDDOWN(82776264000 × 2<sup>-13</sup>) = 10104524 = 0x009A\_2ECC

消費電力(ワット)を求めるには、xWATT\_ACC に W/LSB 定数を掛けます(xWATT\_ACC×W/LSB)。 W/LSB は PWR TIME 積算時間に応じて変化すること

に注意してください。

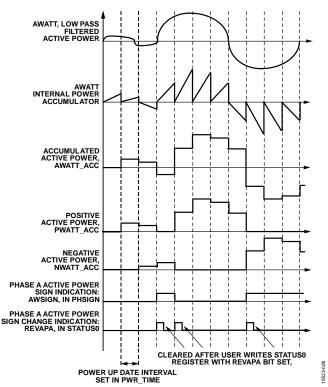

#### 電力の符号検出

STATUSO レジスタの REVRPC、REVRPB、REVRPA、REVAPC、REVAPB、および REVAPA ビットを使用すると、いずれかの相で有効電力または無効電力の符号が変化したかどうかをモニタできます。

PWR\_SIGN\_SEL[1:0]ビットを使用すると、電力の符号変化が総合または基本波の電力量に追従するかどうかを選択できます。REVAPx 電力符号ステータス・ビットで総合 WATT を追跡するには、PWR\_SIGN\_SEL[0] = 0 を設定します。基本波の VAR を REVRPx ビットで追跡す

るには、PWR\_SIGN\_SEL[1] = 1 を書き込みます。 PHSIGN レジスタの CVARSIGN、CWSIGN、BVARSIGN、BWSIGN、AVARSIGN、および AWSIGN ビットは、PWR\_SIGN\_SEL[1:0]ビットで選択した総合または基本波の VAR および WATT が正か負かを示します。

電力の符号は  $xWATT\_ACC$ 、 $xFWATT\_ACC$ 、 $xVAR\_ACC$ 、 および  $xFVAR\_ACC$  レジスタと同時に更新され、これらのレジスタの符号と一致します。電力のレジスタおよび符号は、 $f_{DSP}=8ksps$  で、 $PWR\_TIME$  レジスタで設定したサンプル数が経過した、 $250\mu s\sim 1.024$  秒後に更新されることに注意してください。REVxPx ビットでの電力符号の変化表示は、同時に更新されます。詳細については、電力積算の詳細のセクションを参照してください。

ADE9000 を使用すると、総合 WATT および総合 VAR 電力を別個の正と負のレジスタ(PWATT\_ACC とNWATT\_ACC、PVAR\_ACC とNVAR\_ACC)に積算できます。このためには、AWATT(ローパス・フィルタ処理後の有効電力)を 8ksps ごとに評価します。AWATTが正の場合は、その値が PWATT\_ACC 積算値に加算されます。AWATTが負の場合は、絶対値が NWATT\_ACC積算値に加算されます。PWR\_TIMERに設定された電力更新間隔が経過すると、新たな積算が 0 から始まります。3つ全ての相からの正と負の総合 WATT および総合 VARが正/負の WATT および VAR 積算値に加算されます。

図 26. 電力の積算と電力の符号

#### 電力品質の測定

#### ゼロ交差検出

ADE9000 は、VA、VB、VC、IA、IB、および IC 入力信号のゼロ交差検出機能を備えています。中性電流チャンネル IN には、ゼロ交差検出回路は含まれていません。ゼロ交差回路は、リサンプリング、ライン周期、角度測定、およびライン・サイクル積算モードを使用した電力量積算のタイム・ベースとして使用されます。xV\_PCFおよびxI\_PCFは、DSPによって処理される電圧および電流チャンネル波形であり、8kspsのデータ・レートで波形バッファに格納できます(詳細については、波形バッファのセクションを参照してください)。

CONFIGO レジスタの ZX SRC SEL ビットは、ゼロ交 差検出回路に送るデータを、ハイパス・フィルタ、積分 器、および位相補償部の前から取得するか後から取得す るかを設定します。デフォルトでは、位相補償後のデー タが使用されます。ハイパス・フィルタは、入力にス テップ変化がある場合に 500ms のセトリング時間を要す るので、高速応答の場合は ZX SRC SEL を設定して、 ハイパス・フィルタの前にゼロ交差を検出することを推 奨します。CONFIG0 レジスタの HPFDIS ビットを 1 に してハイパス・フィルタを無効にするか、CONFIGO レ ジスタの ZX\_SRC\_SEL ビットを 1 にすると、入力に DC オフセットがある場合は、負から正へのゼロ交差か ら正から負へのゼロ交差までの時間と、正から負へのゼ ロ交差から負から正へのゼロ交差までの時間が変化する ことがあり、ZX 検出のデューティ・サイクルが 50%で はないことを示すので注意してください。

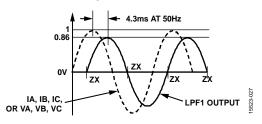

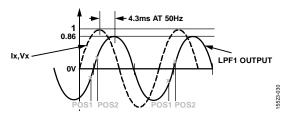

電流信号と電圧信号はローパス・フィルタに掛けられ、 高調波が除去されます。ローパス・フィルタ LPF1 の コーナ周波数は 82Hz で、式は次のとおりです。

$$H(z) = \frac{2^{-4}}{1 - (1 - 4)z^{-1}}$$

ローパス・フィルタのセトリング時間は 71 サンプル (71/8 ksps) で、8.875 ms に相当します。

図 27 に、検出されたゼロ交差信号と入力信号の間の遅延を示します。入力信号が 50Hz の場合、入力信号のゼロ交差と ZX ゼロ交差表示との間には 4.3ms の遅延があります。ゼロ交差は負から正への遷移と正から負への遷移の両方で発生します。

図 27. 電圧および電流チャンネルでのゼロ交差検出

ノイズからの保護のために、LPF1 出力電圧の絶対値が関値 ZXTHRSH より小さい場合、電圧チャンネルのゼロ交差イベント(ZXVA、ZXVB、ZXVC)は生成されません。電流チャンネルの ZX 検出出力(ZXIA、ZXIB、ZXIC)は、すべての入力信号レベルに対してアクティブです。

ゼロ交差閾値 ZXTHRSH は、次式から計算できます。

#### ZXTHRSH =

$\frac{(V\_PCF \ at \ Full \ Scale) \times (LPF1\_ATTENUATION)}{X \times 32 \times 2^{8}}$

ここで、

フルスケール時の  $V_PCF$ は $\pm 74,532,013$ (10 進数)です。

*X*はダイナミック・レンジで、この値未満ではゼロ交差をブロックする必要があります。

$LPF1\_ATTENUATION$ は 50Hz のとき 0.86、60Hz のとき 0.81 で、LPF1 フィルタのゲイン減衰量を表します。例えば、フルスケールの 100 分の 1 より小さい信号が ZX 出力を生成しないようにするには、ZXTHRSH を 78 (10 進数) に設定します。

#### ZXTHRSH =

$$\frac{(74,532,013)\times(0.86)}{100\times32\times2^8} = 78d$$

更に、誤ったゼロ交差を防止するため、ZX の生成後 1ms が経過してから次の ZX を出力できるようにする必要があります。

#### 合成電圧のゼロ交差

A 相、B 相、および C 相の電圧チャンネル信号を合成して、1 つ以上の相が欠落した場合でも安定した 1 つのゼロ交差信号 ZX COMB を生成します。

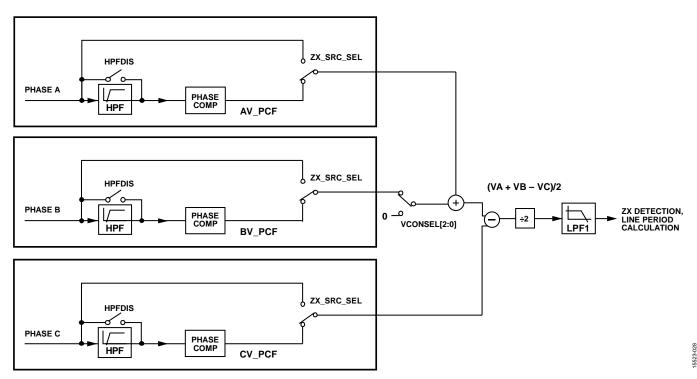

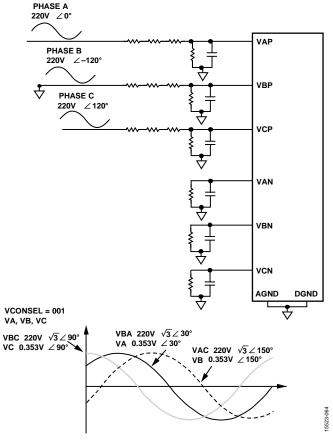

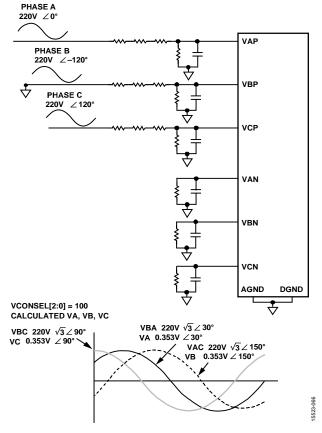

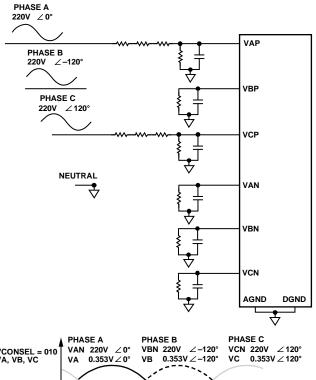

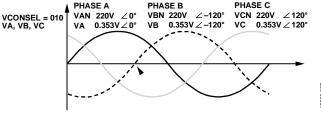

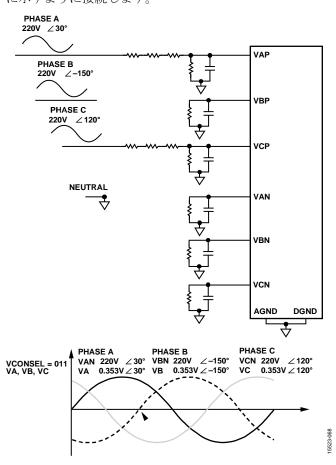

ゼロ交差検出回路への入力は(VA + VB - VC)/2で、シグナル・チェーンは図 28 に対応します。様々な電力量計構成への ADE9000 の応用のセクションで説明するように、ADE9000 を使用して様々な多相構成を測定できます。ACCMODE レジスタの VCONSEL[2:0]ビットを使用して、この選択を示します。VCONSEL[2:0]が 0 ではない場合、合成ゼロ交差回路の VB 成分を 0 に設定します。同じ予防策を講じて、ノイズによってこの出力でのゼロ交差割込みが発生しないようにします。ゼロ交差検出のセクションで説明したように、ZXTHRSH 閾値より小さい信号は ZXCOMB 出力を生成せず、次の ZXCOMB 生成までに 1ms 以上が必要です。

図 28. 合成信号のゼロ交差検出

Rev. 0

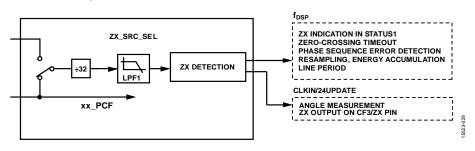

## ゼロ交差の出力レート

信号 IA、IB、IC、VA、VB、VCと、合成信号(VA+VB-VC)/2をモニタする 7 つのゼロ交差検出回路があります。ゼロ交差検出回路には、2 つの出力レート 8ksps および 1024ksps があります。8ksps のゼロ交差信号は、ライン周期を計算するために使用され、STATUS1 レジスタの ZXx ビットに送られ、ゼロ交差タイムアウト、相シーケンス・エラー検出、リサンプリング、電力量の積算の各機能によってモニタされます。1024ksps の信号は角度測定に使用され、CONFIG1 レジスタの CF3\_CFG ビットが 1 の場合は CF3/ZX ピンに出力されます。

表 17 に、どちらのゼロ交差エッジ(負から正および正から負)を使用するかを機能ごとに示し、入力信号がユーザ設定の ZXTHRSH より小さいためにゼロ交差が阻止された場合はどうなるかを示します。

CF3/ZX 出力ピンは、負から正への遷移が検出されるとローからハイになり、正から負への遷移が検出されるとハイからローになります。 ZX\_LP\_SEL レジスタの ZX\_SEL[1:0]ビットで選択するのは、ライン・サイクルでの電力量の積算と ZX 出力ピンで使用されるゼロ交差出力です。

図 29. ゼロ交差の出力レート

表 17. 他の機能でのゼロ交差の使用

| ゼロ交差を<br>使用する機能                                      | 使用される<br>ゼロ交差遷移                                | 対応する<br>STATUS1<br>レジスタのビット                         | どの相を測定に<br>使用するかの選択                                                                                     | ゼロ交差が起こらない場合の影響                                                                                                                                                                                      |

|------------------------------------------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZX Indication in<br>STATUS1 Regist<br>er             | Negative to positive, and positive to negative | ZXIA, ZXIB,<br>ZXIC, ZXVA,<br>ZXVB, ZXVC,<br>ZXCOMB | 該当せず                                                                                                    | ZXx ビットは STATUS1 でラッチされます。クリア されると、再度セットされることはありません。 ZXx 割込みは行われません。                                                                                                                                 |

| Zero-Crossing<br>Timeout                             | Negative to positive, and positive to negative | ZXTOVA,<br>ZXTOVB,<br>ZXTOVC                        | 該当せず                                                                                                    | ゼロ交差タイムアウトは STATUS1 レジスタの<br>ZXTOUT ビットによって示され、割込みを有効にし<br>て実行できます。                                                                                                                                  |

| Phase Sequence<br>Error Detection                    | Depends on VCONSEL[2: 0] setting               | SEQERR                                              | 該当せず                                                                                                    | 1つまたは2つのゼロ交差イベントがなくなると、<br>SEQERR が生成されます。全てのゼロ交差がなく<br>なった場合、SEQERR ビットはセットされません。                                                                                                                   |

| Energy<br>Accumulation                               | Negative to positive, and positive to negative | 該当せず                                                | ZX_LP_SEL.ZX_SEL[1:0]         は、ライン・サイクルで         の電力量の積算と ZX 出力         ピンで使用されるゼロ交         差出力を選択します。 | ライン・サイクルの積算は更新されません。                                                                                                                                                                                 |

| Line Period<br>Measurement                           | Negative to positive                           | 該当せず                                                | 該当せず                                                                                                    | 強制的にデフォルト値になります。<br>ACCMODE.SELFREQ = 0、50Hz 回路の場合は<br>0x00A0_0000 になり、ACCMODE.SELFREQ =<br>1、60Hz 回路の場合は 0x0085_5554 になります。                                                                         |

| Resampling,<br>RMS½,<br>10 Cycle RMS/12<br>Cycle RMS | None                                           | 該当せず                                                | ZX_LP_SEL.LP_SEL[1:0]<br>は、これらの計算の基礎と<br>して使用される相電圧のラ<br>イン周期を選択します。                                    | ゼロ交差が検出されないか、計算結果が 40Hz~70Hz の範囲外の値になることが理由で、選択したライン周期が無効になる場合、計算に使用されるライン周期は強制的にデフォルトのライン周期になります。ACCMODE.SELFREQ = 0、50Hz 回路の場合は 0x00A0_0000 になり、ACCMODE.SELFREQ = 1、60Hz 回路の場合は 0x0085_5554 になります。 |

| Angle<br>Measurements                                | Negative to positive                           | 該当せず                                                | 該当せず                                                                                                    | 更新されず、最後の値が維持されます。                                                                                                                                                                                   |

| ZX Output on<br>CF3/ZX Pin                           | Negative to positive, and positive to negative | 該当せず                                                | ZX_LP_SEL.ZX_SEL[1:0]<br>は、ライン・サイクルで<br>の電力量の積算と ZX 出力<br>ピンで使用されるゼロ交<br>差出力を選択します。                     | 現在の状態(ハイまたはロー)が維持されます。                                                                                                                                                                               |

Rev. 0 — 26/86 —

## ゼロ交差タイムアウト

ゼロ交差タイムアウト機能は、設定した時間の経過後にゼロ交差イベントが生成されないと、警報を出します。 ZXTOUT の 8ksps クロック後にゼロ交差信号を受信しなかった場合、STATUS1 レジスタの対応する ZXTOx ビットがセットされます。例えば、ZXTOUT が 8000 である場合、8000/8ksps = 1 秒以内に A 相でゼロ交差信号を受信しないと、STATUS1 レジスタの ZXTOA ビットがセットされます。 ZXTOUT レジスタに書き込むことができる最大値は、0xFFFF/8000 = 8.19 秒です。

### ライン周期計算

ADE9000 のライン周期を測定するには、ゼロ交差検出のセクションで説明したように、LPF1 でローパス・フィルタ処理された値を取った後、正から負へのゼロ交差に近い 2 つの値を使用して、線形補間によって正確なゼロ交差点を算出します。この情報を使用してライン周期を正確に計算し、xPERIOD レジスタに格納します。

図 30. ゼロ交差検出と線形補間を使用したライン周期の計算

ライン周期  $T_L$ は、xPERIOD レジスタを基に次式に従って計算できます。

$$T_L = \frac{xPERIOD + 1}{8000 \times 2^{16}} \text{ (sec)}$$

同様に、ライン周波数は、xPERIOD レジスタを基に次式を使用して計算できます。

$$f_L = \frac{8000 \times 2^{16}}{xPERIOD + 1}$$

(Hz)

50Hz 入力では、xPERIOD レジスタは 0x00A0\_0000、10485760( 10 進 数 ) で あ り 、60Hz 入力では 0x0085 5554、8738132(10 進数)です。

周期の計算値が 40Hz~70Hz の範囲外であるか、対象の相の負から正へのゼロ交差が検出されない場合、xPERIOD レジスタは、ACCMODE レジスタのSELFREQ ビットの設定に従って、50Hz または 60Hzに対応するよう強制されます。SELFREQ が 0 の場合は50Hz 回路となり、xPERIOD レジスタは強制的に0x00A0\_0000 になります。SELFREQ が 1 の場合、これは 60Hz 回路を示しており、xPERIOD レジスタは強制的に0x0085\_5554になります。

合成電圧のゼロ交差のセクションで説明したように、A相、B相、C相の電圧および合成電圧信号についてライン周期が計算され、それぞれ APERIOD、BPERIOD、CPERIOD、および COM\_PERIOD レジスタに格納されます。

ライン周期の計算値は、リサンプリング測定に使用されます。どの相電圧のライン周期をリサンプリング計算の基準として使用するかを、 $ZX_LP_SEL$  レジスタの  $LP_SEL[1:0]$ ビットを使用して選択するか、CONFIG2 レジスタの  $UPERIOD_SEL$  ビットを使用して、 $USER_PERIOD$  に書き込まれているユーザ設定の値を選択します。

周期の選択が役立つのは、別のアルゴリズムでライン周波数を決めるアプリケーションや、高速の実効測定値をリサンプリングまたは計算するときに、常に特定のライン周波数を想定するのが望ましい場合です。 USER\_PERIOD[31:0]のスケーリングは xPERIOD レジスタと同じです。x000A0\_0000 を書き込み、x00Hz の場合は x0 場合は x0 の場合は x0 の場合は x0 の場合は x0 の場合は x0 の場合は x0 の場合は x0 の 場合は

#### 角度測定

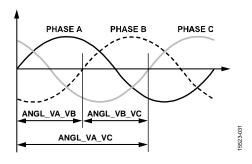

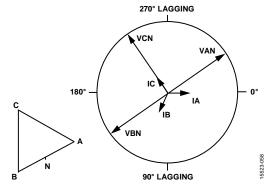

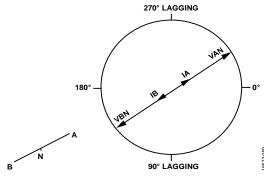

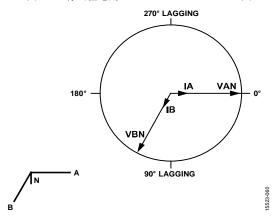

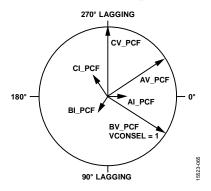

ADE9000 は、ゼロ交差間の時間を相ごとに測定します。この測定が役立つのは、システムのバランスが適切かどうかを調べる場合や、実装に誤りがあったかどうかを突き止める場合です。位相角が様々な電力量計構成へのADE9000 の応用のセクションのフェーザ図の角度と一致するかどうかを調べることができます。

正から負へのゼロ交差間の時間は、CLKIN/24 =  $24.576/24 = 1024 \mathrm{kHz}$  のクロックを使用して測定します。A 相と B 相のゼロ交差間の時間は、ANGL\_VA\_VB レジスタに格納されます。ANGLx\_x2x レジスタの分解能は、 $50 \mathrm{Hz}$  では( $1/(1024 \times 1000))/20 \mathrm{ms} \times 360^{\circ} = 0.017578125^{\circ}$ です。

図 31 に示すように、B 相と C 相のゼロ交差間の時間は  $ANGL_VB_VC$  レジスタに格納され、A 相と C 相のゼロ 交差間の時間は  $ANGL_VA_VC$  レジスタに格納されます。

図 31. 電圧間の位相角

50Hz のライン周期の場合、角度(°) は次式から計算できます。

Angle (degrees) =  $ANGL_VA_VB \times 0.017578125/LSB$

4 線式 Y 結線構成の場合、ANGL\_VA\_VB および ANGL\_VB\_VC の予想値は 120%0.017578125 = 3413 (10 進数) です。A 相の電圧から C 相の電圧までの ANGL\_VA\_VC の予想値は 240%0.017578125 = 13653 (10 進数) であり、これは C 相と A 相の間の 120%の角度 に対応します。

また、電流間のゼロ交差も測定されます。この測定は、前述した電圧間位相角と同様に行われますが、基準として電流チャンネルのゼロ交差が使用されることが異なります。A 相と B 相のゼロ交差間の時間は、ANGL\_IA\_IB レジスタに格納されます。B 相と C 相のゼロ交差間の時間は ANGL\_IB\_IC レジスタに格納され、A 相と C 相のゼロ交差間の時間は ANGL\_IA\_IC レジスタに格納されます。

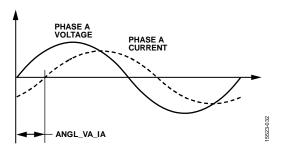

電圧と電流の間の位相角も同様に測定されます。これらの角度を使用して、基本波での力率を求めることができます。ANGL\_VA\_IA は、図 32 に示すように、A 相の電圧と電流の間の位相角を表します。ANGL\_VB\_IB は B 相の電圧と電流の間の位相角を保持し、ANGL\_VC\_IC は C 相の電圧と電流の間の位相角を保持します。

図 32. 電圧と電流の間の位相角

電圧チャンネルの振幅がユーザ設定のゼロ交差閾値より小さい場合、該当する相のゼロ交差出力は生成されません。この状況では、対応する ANGLx\_x2x 測定値は更新されません。最終値はレジスタに残ります。電流チャンネルにはこうした閾値はありません。入力信号のレベルが低いと、電流チャンネルに疑似ゼロ交差イベントが生じて、ANGLx\_I2I と ANGLx\_V2I の読出し値が意味のないものになります。

#### 相シーケンス・エラーの検出

### 4線式 Y 結線と 4線式 Δ 結線

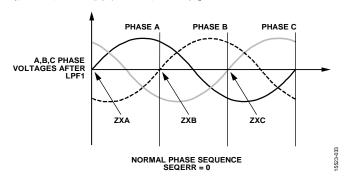

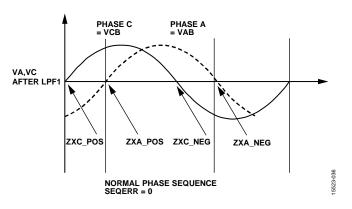

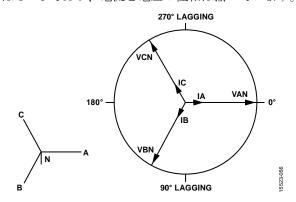

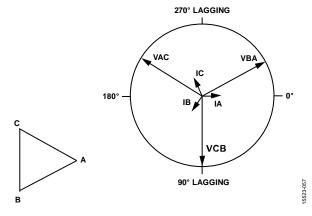

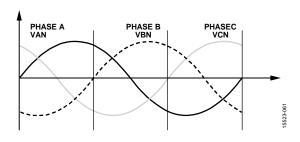

4 線式 Y 結線と 4 線式  $\Delta$  結線のメータについて、通常の相シーケンスを図 33 に示します。

図33.4線式Y結線と4線式Δ結線での通常の相シーケンス

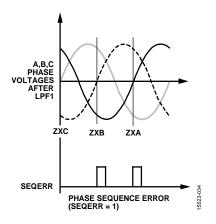

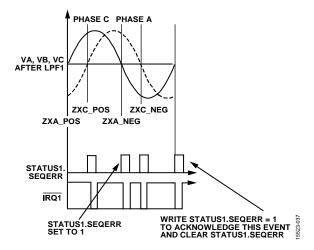

4 線式 Y 結線システムまたは 4 線式  $\Delta$  結線システムでは、様々な電力量計構成への ADE9000 の応用のセクションで説明するように、VCONSEL[2:0]は 000、010、または 011 です。これらの 4 線式システムでは、図 35 に示すように、ZXVA、ZXVB、および ZXVC での負から正への遷移がモニタされ、相シーケンス・エラーがあるかどうかが調べられます。相シーケンス・エラーを検出するには、観測するシーケンスの数を  $SEQ_CYC$  レジスタに設定します。 $SEQ_CYC$  には 1 を設定することを推奨します。図 34 に、配線または実装の誤りによる 4 線式 Y 結線または 4 線式  $\Delta$  結線での相シーケンス・エラーを示します。

図 34.4 線式 Y 結線および 4 線式 Δ 結線での 相シーケンス・エラー(配線の誤り)

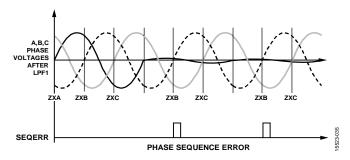

図 35 は、通常の相シーケンスを持つ実装回路で、1 つの相電圧が ZXTHRSH より低くなると相シーケンス・エラーが発生することを示しています。

図 35. SEQ\_CYC = 1 で相電圧が ZXTHRSH より低くなったことに よる 4 線式 Y 結線、4 線式  $\Delta$  結線での相シーケンス・エラー

#### 3線式∆結線

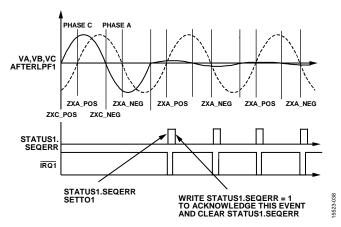

3 線式  $\Delta$  結線システムでは、様々な電力量計構成への ADE9000 の応用のセクションで説明するように、 VCONSEL[2:0]は 001 または 100 です。3 線式  $\Delta$  結線システムでは、ZXVC および ZXVA での正から負への遷移と負から正への遷移がモニタされ、相シーケンス・エラーが検出されます。図 36 は、3 線式  $\Delta$  結線で VCONSEL[2:0] = 001 の場合の通常の相シーケンスを示しています。

図 36.3 線式 △ 結線での通常の相シーケンス

SEQ\_CYC を書き込んで、連続した誤遷移の数を示してから SEQ\_ERR 割込みを生成する必要があります。 SEQ\_CYC には 1 を設定することを推奨します。図 37 に、検出された相シーケンス・エラーの原因となった 3 線式  $\Delta$  結線の実装上の誤りを示します。

図 37.3 線式 △ 結線での相シーケンス・エラー (配線の誤り)

図 38 は、通常の相シーケンスを持つ実装回路で、相電圧の1つが ZXTHRSH より低くなると相シーケンス・エラーが発生することを示しています。

図 38. SEQ\_CYC = 1 で相電圧が ZXTHRSH より低くなったことによる 4 線式 Y 結線、3 線式  $\Delta$  結線での相シーケンス・エラー

#### 高速 RMS½測定および 10/12 RMS 測定

RMS½は1ライン・サイクルについて行う実効値測定で、ハーフ・サイクルごとに更新されます。

この測定は、全ての相の電圧と電流、および中性電流に対して行われます。すべてのハーフ・サイクル実効値測定は同じ時間枠で行われ、STATUSO レジスタのRMSONERDY ビットによる指示に従って、同時に更新されます。 結果は、AIRMSONE、BIRMSONE、CIRMSONE、NIRMSONE、AVRMSONE、BVRMSONE、CVRMSONE レジスタに保存されます。

デフォルトでは、計算に使用されるサンプルの数は、測定したライン周波数に応じて変化します。 ZX\_LP\_SEL レジスタの LP\_SEL ビットは、RMS½測定に使用されるサンプルの数を設定するために、どのライン周期測定値を使用するかを選択します。

あるいは、CONFIG2 の UPERIOD\_SEL ビットをセットすれば、計算に使用するサンプルの数を設定できます。この場合には、選択したライン周期測定値ではなく、ユーザ設定の USER\_PERIOD レジスタを使用します。 USER\_PERIOD とライン周期測定の詳細については、ライン周期計算のセクションを参照してください。

RMS%の計算に使用されるサンプルは、CONFIGO レジスタの RMS\_SRC\_SEL ビットで選択したように、ハイパス・フィルタの前段または積分器の後段から供給されます。

ハイパス・フィルタに付随するセトリング時間は非常に長いので、応答時間を最も短くするには、ハイパス・フィルタの前段からのデータを使用することを推奨します。

入力信号レベルが小さい状態での性能を向上させるには、 オフセット補正レジスタ xRMSONEOS を使用すること ができます。

フルスケール入力での xRMSONE レジスタの読出し値は 52,702,092 (10 進数) です。

10 サイクルの実効値測定/12 サイクルの実効値測定は、50Hz 回路では 10 サイクルごとに、60Hz 回路では 12 サイクルごとに行われます。

入力信号レベルが小さい状態での性能を向上させるには、 オフセット補正レジスタ xRMS1012OS を使用すること ができます。

フルスケール入力での xRMS1012 レジスタの読出し値は 52,702,092 (10 進数) です。

表 18 に、50Hz 信号での%サイクル実効セトリング時間を示します。表 19 に、50Hz 信号での 10 サイクル/12 サイクル実効セトリング時間を示します。

表 18. %サイクル実効セトリング時間

| Configuration                       | ½ RMS Settling Time,<br>FS = 99% (sec) |

|-------------------------------------|----------------------------------------|

| Integrator On, HPF On, and LPF2 On  | 0.26                                   |

| Integrator Off, HPF On, and LPF2 On | 0.06                                   |

表 19. 10 サイクル/12 サイクル実効セトリング時間

| Configuration                       | 10/12 RMS Settling Time,<br>FS = 99% (sec) |

|-------------------------------------|--------------------------------------------|

| Integrator On, HPF On, and LPF2 On  |                                            |

| Integrator Off, HPF On, and LPF2 On | 0.2                                        |

| Integrator Off, HPF On, and LPF2 On | 0.2                                        |

## ディップ/スウェル表示

ディップは、設定したサイクル数での規定の閾値より電圧が低下したことを示します。逆に、スウェルは、電圧が規定のサイクル数での閾値を超えたことを示します。 RMS½の値に対応するよう DIP\_LVL レジスタをセットして、次式に従ってディップ・イベントをトリガします。

$DIP\_LVL = xVRMSONE \times 2^{-5}$

RMS½の値を観測するサイクル数を DIP\_CYC レジスタ に設定します。

A 相、B 相、および C 相での RMS½電圧は、規定の DIP\_CYC にわたって DIP\_LVL と比較されます。規定の DIP\_CYC 数での RMS½電圧が低いと、該当する相で ディップ・イベントが発生し、STATUS1 レジスタの対 応する DIPA ビット、DIPB ビット、および DIPC ビットがセットされます。ディップ・イベントを設定して、  $\overline{IRQ1}$ ピンで割込みを生成できます。

EVENT\_MASK レジスタの対応するビットがセットされている場合は、ディップ・イベントを設定して、CF4/EVENT/DREADY ピンでイベントを生成できます。これにより、CF4/EVENT/DREADY ピンと外部マイクロコントローラのタイマーを併用して、ディップまたはスウェルの持続時間を正確に測定できます。

ディップ時に測定された最小 RMS½値は、対応する DIPA、DIPB、および DIPC レジスタに保存されます。 同様に、スウェル表示には、次式に従ってスウェル閾値 を設定する SWELL\_LVL レジスタがあります。

$SWELL\_LVL = xVRMSONE \times 2^{-5}$

また、SWELL\_CYC レジスタもあります。スウェル時に 測定された RMS½電圧の最大値は、対応する SWELLA、SWELLB、および SWELLC レジスタに保存されます。 CONFIG1 レジスタの DIP\_SWELL\_IRQ\_MODE ビットを 0 に設定すると、DIP\_CYC/SWELL\_CYC サイクルごとに割込みが生成されます。 DIP\_SWELL\_IRQ\_MODE を 1 に設定した場合は、ディップ/スウェル・モードに入るとある割込みが生成され、このモードから出ると別の割込みが生成されます。モードは DIP\_CYC サイクル経過後に変更されます。 DIP\_CYC/SWELL\_CYC = 1 の場合は、ディップ/スウェル状態が終了すると追加の割込みが生成され、ディップ/スウェルの値 DIPx/SWELLxがそのときに更新されて、DIP\_LVL/SWELL\_LVL の値を超えるので注意してください。

## 過電流表示

過電流表示は、RMS½の電流測定値をモニタする機能です。RMS½の電流がユーザ設定のOILVL(過電流閾値)より大きくなると、このことがSTATUS1 レジスタのOI ビットに示されます。

$OILVL = xIRMSONE \times 2^{-5}$

CONFIG3 レジスタの OC\_EN[3:0] ビットは、どの相の 過電流イベントをモニタするかを選択します。 OISTATUS レジスタの OIPHASE[3:0]ビットは、どの電流チャンネルの RMS½測定値が閾値より大きいかを示します。

ある相を有効にして、対応する OC\_EN ビットをセットして RMS½電流を閾値より大きくすると、OI ステータスが設定され、RMS½の値は対応する OIx レジスタに格納されます。ある相を無効にした場合や、その相で過電流イベントが発生しなかった場合、OIx レジスタは最後の値を維持します。

#### ピーク検出

ADE9000 は、 $xI_PCF$  および  $xV_PCF$  波形の電流及び電圧チャンネルで測定されたピーク値を記録します。 CONFIG3 レジスタの PEAKSEL[2:0]ビットを使用すると、モニタする相を選択できます。C 相をモニタするには PEAKSEL[2]を設定し、B 相をモニタするには PEAKSEL[0]を設定します。3 つの相全てをモニタするには、PEAKSEL[2:0] = 111(2 進数)を設定します。

IPEAK レジスタはピーク電流値を IPEAKVAL[23:0]に 格納して、どの相電流が IPPHASE[2:0]ビットの値に達 したかを示します。IPEAKVAL = xI\_PCF/2<sup>5</sup>です。

IPPHASE[2] は C 相に、IPPHASE[1] は B 相に、IPPHASE[0]は A 相に、それぞれピーク値があることを示します。

同様に、VPEAK はピーク電圧値を VPEAKVAL[23:0]に 格納します。VPEAKVAL = xV\_PCF/2<sup>5</sup>です。

VPPHASE[2] は C 相に、VPPHASE[1] は B 相に、 VPPHASE[0] は A 相に、それぞれピーク電圧値があるか どうかを示します。

IPEAK レジスタを読み出すと、その値はリセットされます。VPEAK の読出しについても同じことが当てはまります。

### 力率

総合有効電力量と総合皮相電力は、1.024 秒間積算されます。その後、次式に従って各相の力率が計算されます。

$APF = \frac{AWATT\ accumulated\ over\ 1.024\ sec}{AVA\ accumulated\ over\ 1.024\ sec}$

範囲内にとどまることに注意してください。

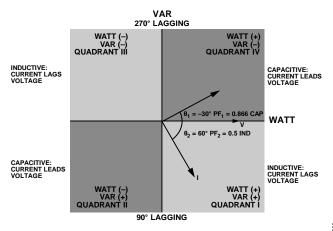

APF 計算の符号は AWATT の符号に従います。 電力量がどの象限に入っているかを割り出すには、データシートに示すように、その相での総合無効電力量および基本波無効電力量の符号に加えて、 $\mathbf{x}$ PF または $\mathbf{x}$ WATT の値の符号を確認します。第 1 象限と第 3 象限の力率は容量性負荷の力率であり、第 2 象限と第 4 象限の力率は誘導性負荷の力率です。ほとんどのアプリケーションでは、WATT を電力網から受け取って(取り込んで)いるため、WATT と VAR は第 1 象限と第 4 象限の

WATT(+) INDICATES POWER RECEIVED (IMPORTED FROM GRID) WATT(-) INDICATES POWER DELIVERED (EXPORTED TO GRID)

図 39. 容量性負荷と誘導性負荷における WATT と VAR の符号

力率の結果は、5.27 フォーマットで保存されます。力率の最大値は  $0x07FF\_FFFF$  で、これは力率 1 に相当します。力率-1 は  $0xF800\_0000$  として保存されます。xPF レジスタの値から力率を求めるには、次式を使用します。

Power Factor =  $APF \times 2^{-27}$

#### 全高調波歪み

全高調波歪み (THD) は、次式に示すように、総合と基本波の実効値を使用して、1秒に1回計算されます。

$$AITHD = \sqrt{\frac{AIRMS^2 - AIFRMS^2}{AIFRMS^2}}$$

THD の計算結果は、符号付き 5.27 フォーマットで保存されます。THD の最大値は  $0x2000\_0000$  で、これは 400%の THD に相当します。THD の値をパーセンテージで求めるには、次式を使用します。

%THD on Current Channel A = AITHD  $\times$  2<sup>-27</sup>  $\times$  100%

THD の計算は、AITHD、BITHD、CITHD、AVTHD、BVTHD、CVTHD レジスタを使い、それぞれ IA、IB、IC、VA、VB、VC チャンネルで行うことができます。IN チャンネルでは THD 測定ができないことに注意してください。

#### 温度

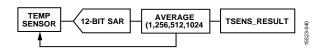

ADE9000 は、温度センサーと 12 ビット逐次比較レジスタ (SAR) ADC を併用する温度測定ユニットを内蔵しています。

図 40. 温度測定のブロック図

TEMP\_CFG レジスタの TEMP\_EN ビットをセットして、温度センサーをイネーブルします。TEMP\_TIME[1:0]では、1、256、512、または 1024 個の温度指示値を平均化して、 $1.25ms\sim1.3$  秒後に結果を出力できます。温度のアクイジション・サイクルは、TEMP\_CFG レジスタの TEMP\_START ビットをセットすれば開始されます。結果は TEMP\_RSLT レジスタで利用できます。TEMP\_START ビットはセルフ・クリア・ビットです。新しい指示値を得るには、TEMP\_START ビットをセットします。新しい温度測定が可能な時に割込みを受けるには、MASKO レジスタの TEMP\_RDY ビットをセットします。

温度指示値のオフセットとゲインは出荷テスト時に測定され、 $TEMP\_TRIM$  レジスタに格納されます。 $TEMP\_RSLT$  の温度指示値を温度( $^{\circ}C$ ) に変換するには、次式を使用します。

$Temperature \ (^{\circ}C) = TEMP\_RSLT \times (-TEMP\_GAIN/65536) + (TEMP\_OFFSET/32)$

## 内部データへのアクセス

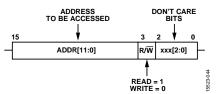

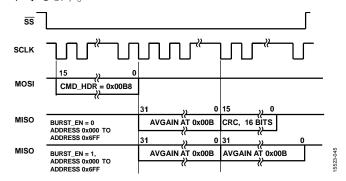

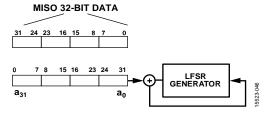

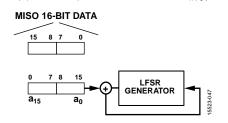

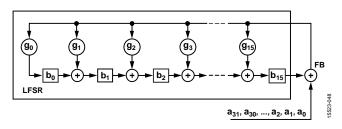

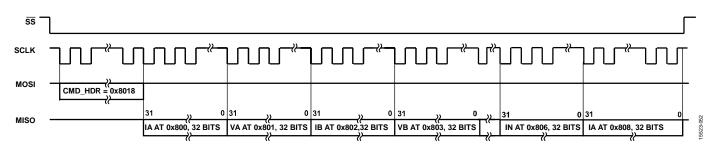

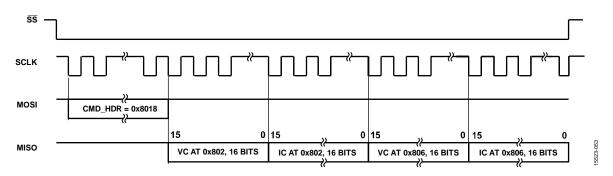

## SPI プロトコルの概要