# MT-074 ミニ・チュートリアル

## 高精度 A/D コンバータ用の差動ドライバ

### 差動入力型 ADC の特徴

現在では、高性能 A/D コンバータ (ADC) の多くは差動入力型で設計されています。ADC を完全差動系で設計することには、コ モンモード除去性能が得られる、2次高調波歪み積を低減できる、DCトリムのアルゴリズムを簡素化できる、といったメリットが あります。差動入力型の ADC は、シングルエンド入力で使うことも可能ですが、通常は差動ドライバ(アナログ信号入力用の完 全差動型アンプ回路)を使用することで全体的な性能を最適化することができます。

差動入力型 ADC 用の入力回路として一般的なものの 1 つに、トランスを使用する方法があります。しかし、実際にはトランスを 使用できないケースも数多く存在します。DC 信号も扱わなければならない場合、トランスでは対応できないからです。そのよう な場合には、トランスではなく、差動ドライバを使う必要があります。

このチュートリアルでは、サンプリング・レートが最大 10MSPS (メガサンプル/秒) で、16~18 ビットもの高い分解能を備える ADC 用の差動ドライバについて解説します。このような条件では、入力信号の帯域幅は、一般的に数 MHz に制限されます。なお、 別のチュートリアルである MT-075 では、高速 ADC を駆動するのに適した差動ドライバについて説明しています。

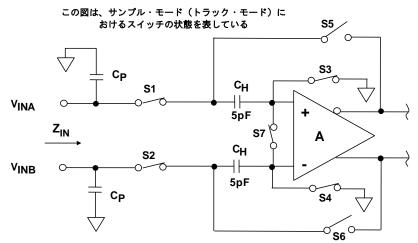

多くの ADC は、高性能の CMOS スイッチド・キャパシタをパイプライン型に接続する構成をとっています。そのほとんどは、図 1に示すような差動入力を備えています。

入力インピーダンス ZINは、以下の要素に依存して変化する

- ◆ サンプル・モード(トラック・モード)かホールド・モードか

- ◆ 入力信号周波数

図 1. ADC の入力部の一般的な構成。CMOS のスイッチド・キャパシタで サンプル&ホールド回路を構成しています。その前段にはバッファは存在しません。

通常、ADCの多くは差動構成で設計されています。これによって、マッチングの要件が緩和されるとともに、2次高調波歪み積が 低減されるからです。また、差動構成は、コモンモード・ノイズの除去にも寄与します。

> アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に ファロファ アハド こへ社は、近次する『特報が上述』に自殺しこのものもことを対しているすが、くの情報が分析に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 予告なく変更される場合があります。 本紙記載の商標および登録商標は、それぞれの所有者の財産です。 ※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2012 Analog Devices, Inc. All rights reserved.

Rev. 0, 10/08, WK

# ミニ・チュートリアル

図1の回路において、サンプル&ホールド・アンプ(以下、SHA)のスイッチが、各入力に直接接続されていることに注目してください。このように、アイソレーション(分離)用のバッファ(入力用のアンプ回路)が存在しない場合には、スイッチング時に発生する過渡現象によって大きな影響が現れる可能性があります。この問題はバッファを使用することで回避可能なのですが、その際にも注意すべきことがあります。それは、使用するバッファのセトリング時間が、過渡現象に対して十分に短くなければならないということです。具体的には、サンプリング時間の半分未満の時間で、バッファの出力が所望の精度内に収まるレベルに収束する必要があります(外部に直列抵抗が存在する場合、その分の影響も含めたセトリング時間が十分に短くなければなりません)。

図1のような構造を持つADCの場合、差動入力部の入力インピーダンスは動的に変化します。具体的には、SHAのスイッチの状態がサンプル・モード(トラック・モード)とホールド・モードの間で切り替わるときに変化が生じます。サンプル・モードでは、入力信号によってホールド用のキャパシタ $C_H$ に対する充電/放電が行われます。ホールド・モードではスイッチの位置が切り替わり、ホールド用のキャパシタ $C_H$ にかかっていた電圧が出力側に転送されます。このような動きから、入力インピーダンスに変化が生じるのです。また、この入力インピーダンスはアナログ入力信号の周波数にも依存して変化します。

このようなタイプの入力回路を備える ADC を使用する場合には、スイッチング時に生じる過渡現象に対してコモンモード除去を有効に働かせるために、バッファとして、差動ドライバを使用することを強くお勧めします。また、このタイプの ADC をシングルエンドで利用 (片側の入力を適切なコモンモード電圧に接続) することも可能なのですが、その場合、偶数次の歪み積を除去する効果が得られないため、SFDR が低下してしまいます。

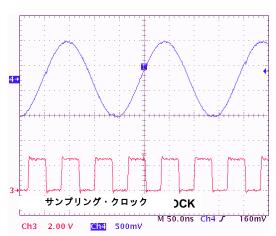

図 2 (A) は、バッファを備えていない一般的な CMOS ADC の差動入力の各信号とサンプリング・クロックの関係を観測したものです。信号は  $50\Omega$  のソース抵抗を介して入力しています。上述したスイッチング動作により、サンプリング・クロックの各エッジで過渡現象が生じている様子が見てとれます。

一方、図 2 (B) に示したのは、図 2 (A) と同じ条件で入力を差動信号として観測したものです。過渡的に生じるグリッチの大部分は、コモンモード信号であるため除去されていることがわかります。また、この除去が最適に行われるようにするためには、2つの入力を平衡(balanced)ソース・インピーダンスによって駆動する必要があることにも注意してください(有効/無効インピーダンスが整合している必要があります)。

(A) シングルエンドで観測

サンプリング・クロック )CK Ch1 200mV eh2 200mV M 50.0ns Ch2 ア 1.69 V Ch3 2.00 V

(B) 差動で観測

- ◆ 差動入力の過渡的充放電は、同相で、同じ形になる。線形的な要素が大部分を占める

- ◆ コモンモードの過渡現象が打ち消されるようにするには、ソース・インピーダンスを等しくする必要もある

注:ソース抵抗が 50Ω の場合の結果

図 2. CMOS スイッチド・キャパシタ入力を備える ADC に現れる一般的な入力過渡現象。 シングルエンドで観測した場合(A)と差動で観測した場合(B)を示しています。

#### 16/18 ビットの高精度 ADC 向けの差動ドライバ回路

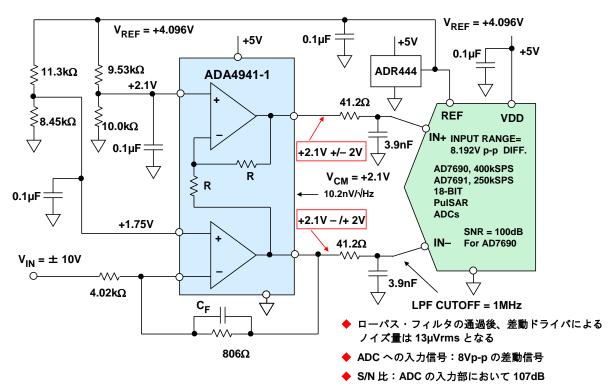

図 3 に示したのは、入力アナログ信号がシングルエンドの正負(双極)信号で、ADC が差動入力型のものである場合に一般的に使われる回路です。具体例として、ADC にはスイッチド・キャパシタ入力を備える PulSAR®ファミリーの 18 ビット ADC 「AD7690」 または「AD7691」を、差動ドライバには「ADA4941-1」を使用しています。分解能の高い ADC を使って高精度の結果を得るためには、 ${}_{\sim}$  には、 ${}_{\sim}$  このような条件に対し、ADA4941-1 の特性は以下のようになっています。

●低消費電力:電源電圧が3Vの場合の消費電流が2.2mA

●低ノイズ: 100kHz の周波数において 10.2nV/√Hz

●低歪み:100kHz の周波数において 110dBc

これであれば、分解能が最大 18 ビットの ADC にも対応可能です。

ADA4941-1 の小信号帯域幅は 31MHz です。また、この差動ドライバは、入力インピーダンスが高く、レール to レール出力に対応していることも特徴とします。利得 (ゲイン) についてはユーザーによる設定が可能です。

ADA4941-1 は、2 つのオペアンプ回路で構成されています。図の下側に示されているオペアンプは、外付けのフィードバック抵抗を使用して反転アンプを構成し、後段の反転アンプ(図の上側のアンプ)を駆動しています。この IC は、後段のアンプで反転アンプを構成するためのフィードフォワード抵抗とフィードバック抵抗も内蔵しています。2 つのアンプ回路によって遅延/位相のずれが生じますが、対象とする周波数が最大 1MHz~2MHz 程度であれば、それによって大きな誤差が生じることはありません。

図 3. PulSAR ファミリーの 18 ビット ADC (AD7690/AD7691) 用の差動入力回路。 差動ドライバとして ADA4941-1 を使用しています。5V 単一電源で動作します。

この回路では、2つの抵抗分圧回路によって ADA4941-1 の出力コモンモード電圧を 2.1V に設定しています。これにより、出力信号は  $100 \text{mV} \sim 4.1V$  の範囲で推移することになります。そのため、アンプのレール to レール出力段にとっては十分な動作余裕度を確保することができるとともに、回路全体としても、5V 単一電源で動作可能となります。

AD7690/AD7691 の差動入力範囲は  $2\times V_{REF}V_{P-P}$  です  $(V_{REF}$  は、各 ADC に入力する基準電圧)。基準電圧の生成に使用しているのは、出力電圧が 4.096V の電圧リファレンス IC「ADR444」です。図 3 の回路では  $41.2\Omega$  の抵抗と 3.9nF のキャパシタを使って、カット

オフ周波数が 1MHz のローパス・フィルタを構成しています。 AD7690 は入力帯域幅が 9MHz なので、このような設計にしています。

ADA4941-1 の出力ノイズ密度は  $10.2nV/\sqrt{Hz}$  です。ローパス・フィルタの帯域幅までの積分を行うと、ノイズ量は  $13\mu Vrms$  になります。これを基に差動ドライバにおける S/N 比を計算すると、その値は 107dB となり、ADC の S/N 比である 100dB よりも 7dB 優れていることになります。

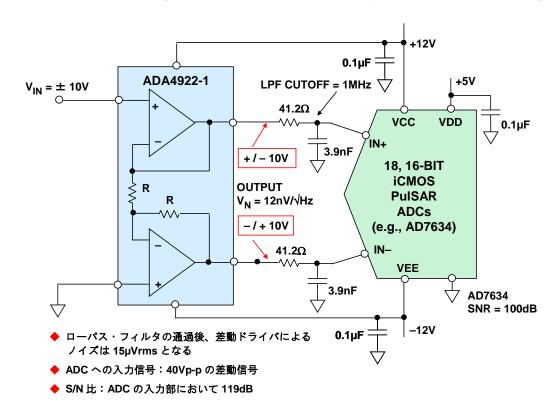

続いて、図 4 をご覧ください。これは、PulSAR ファミリーの ADC のなかでも、iCMOS<sup>TM</sup> 高電圧プロセスで製造される「AD7634」などに適した入力回路の例です。工業アプリケーションでは、 $\pm 10$ V といった高電圧の信号がよく用いられます。iCMOS プロセスで製造される ADC は、このような用途を対象として開発されたものです。iCMOS プロセスを採用した PulSAR ファミリーの ADC は、ほとんどが差動入力を備えています。図 4 の例は、差動ドライバ「ADA4922-1」を使用して、iCMOS/PulSAR の 16 ビット/18 ビット ADC 用の入力回路を構成しています。シングルエンドから差動への変換は、ADA4922-1 によって行います。

図 4. iCMOS/PulSAR ファミリーの 18 ビット ADC (AD7634) 用の差動入力回路。差動ドライバとして ADA4922-1 を使用しています。±12V の電源を用いる工業アプリケーションの例です。

ADA4922-1 は、 $16\sim18$  ビットの ADC 用の差動ドライバであり、ADC の差動入力範囲として最大 40Vp-p に対応可能です。アナログ・デバイセズ独自の第 2 世代 XFCB プロセスによって製造されており、電源電圧が高くても、優れたノイズ/歪み性能を実現することができます。なお、小信号帯域幅は 38MHz です。

図 3 の例の場合と同様に計算を行うと、まず 1MHz のローパス・フィルタを用いた場合、差動ドライバのノイズ量は  $15\mu Vrms$  になります。この回路では、ADC の入力信号範囲(差動ドライバの出力信号範囲)は 40Vp-p であり、これは 14.14Vrms に相当します。このことから、差動ドライバの S/N 比は 119dB となります。

AD7634 の S/N 比を 100dB として計算すると、ADC の性能に影響を与える入力ノイズの RMS 値は 141 $\mu$ Vrms となります。S/N 比から換算すると、差動ドライバと ADC のトータルでの入力換算ノイズは 142 $\mu$ Vrms なので、オペアンプによる影響はほぼ無視できることがわかります。

## 参考資料

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 3.

- 3. Walt Kester, *Analog-Digital Conversion*, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 6. Also available as *The Data Conversion Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 6.

- 4. Walt Kester, *High Speed System Applications*, Analog Devices, 2006, ISBN-10: 1-56619-909-3, ISBN-13: 978-1-56619-909-4, Chapter 2.