# MT-075 ミニ・チュートリアル

### 高速 ADC 向け差動ドライバの基礎と応用

#### 差動ドライバの基礎理論

現在では、高性能 A/D コンバータ (ADC) の多くは差動入力型で設計されています。ADC を完全差動系で設計することには、コ モンモード除去性能が得られる、2次高調波歪み積を低減できる、DCトリムのアルゴリズムを簡素化できる、といったメリットが あります。差動入力型の ADC は、シングルエンド入力で使うことも可能ですが、通常は差動ドライバ(アナログ信号入力用の完 全差動型アンプ回路)を使用することで全体的な性能を最適化することができます。

上記のとおり、差動設計には、2次高調波歪み積を低減できるというメリットがあります。このことは以下のように説明できます。

まず歪み積は、回路の伝達関数をべき級数で表すことによってモデル化することができます。アンプの整合がとれていると仮定し、 出力を一般的な式に展開すると、正相、逆相の各差動信号は、それぞれ次の式 1、式 2で表せます。

$$V_{OUT+} = k_1(V_{IN}) + k_2(V_{IN})^2 + k_3(V_{IN})^3 + \dots$$

(式 1)

$$V_{OUT-} = k_1(-V_{IN}) + k_2(-V_{IN})^2 + k_3(-V_{IN})^3 + \dots$$

(\$\frac{1}{2}\$)

ここで、k1、k2、k3…は定数であり、2 次の項は 2 次高調波歪み、3 次の項は 3 次高調波歪み…となります。完全差動型のアンプ回 路では、奇数次の項については入力信号の極性がそのまま出力に現れますが、偶数次の項については負 (-) の極性が正 (+) に 変化します。そのため両者の差をとった差動出力は、次の式3で示されるように奇数次の項は2倍になり、偶数次の項は打ち消さ れるという結果になります。

$$V_{OUT+} - V_{OUT-} = 2k_1(V_{IN}) + 2k_3(V_{IN})^3 + \dots$$

(式 3)

差動入力型 ADC 用の入力回路として一般的なものの 1 つに、トランスを使用する方法があります。しかし、実際にはトランスを 使用できないケースも数多く存在します。DC 信号も扱わなければならない場合、トランスでは対応できないからです。そのよう な場合には、トランスではなく、差動ドライバを使う必要があります。また、ADC の前段で大きな信号ゲイン(利得)が必要な場 合にも、差動アンプが優れたソリューションとなります。トランスを使用してゲインを得る方法にはノイズが少ないというメリッ トがありますが、巻数比が 2 以上になると、特に IF レベルの周波数において帯域幅と歪みの問題が発生します。

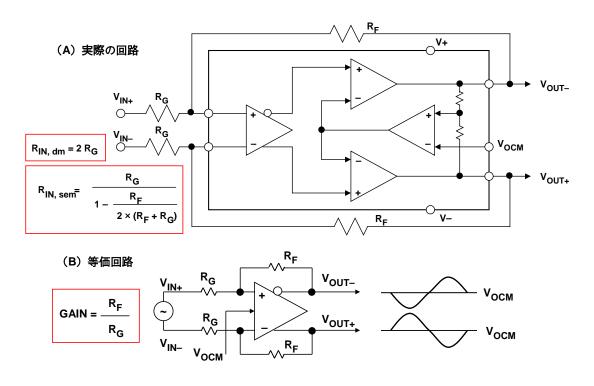

図1に、ADC の駆動用に最適化された差動ドライバの製品ファミリー「AD813x」と「ADA493x」のブロック図を示します。図1 (A) はチップ内部の実際の回路、図 1 (B) はその等価回路を表しています。ゲインは外付け抵抗  $R_F$ と  $R_G$ によって設定し、コモ ンモード電圧は V<sub>OCM</sub> ピンから入力します。出力の V<sub>OUT+</sub>と V<sub>OUT</sub>-は、内部のコモンモード帰還回路によって平衡に保たれます。 この関係は、次式のように表すことができます。

> アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。 ※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2012 Analog Devices, Inc. All rights reserved.

Rev. 0, 10/08, WK

アナログ・デバイセズ株式会社

$$V_{OCM} = (V_{OUT+} + V_{OUT-}) / 2.$$

(式 4)

このとき、2本の出力信号の振幅は常に等しく、位相には180度の差があるということになります。

図 1. AD813x と AD493x のブロック図

AD813x/ADA493x では、2 つの帰還ループを使って差動電圧とコモンモード電圧を別々に制御します。外付け抵抗で設定される差動帰還ループは差動出力電圧のみを制御し、コモンモード帰還ループはコモンモード出力電圧のみを制御します。このようなアーキテクチャであることから、レベル変換を伴うアプリケーションにおけるコモンモード出力レベルの設定が任意かつ容易に行えます。出力のコモンモード・レベルは、内部のコモンモード帰還回路によって、差動出力電圧に影響を与えることなく、 $V_{OCM}$  に印加された電圧と等しくなるように調整されます。その結果、ほぼ完全に平衡で、振幅が等しく、広い周波数範囲で位相が正確に 180度異なる差動出力が得られます。これらの差動ドライバは差動入力とシングルエンド入力のどちらでも使用可能です。電圧ゲインは  $R_F$  と  $R_G$  の比で決まります。

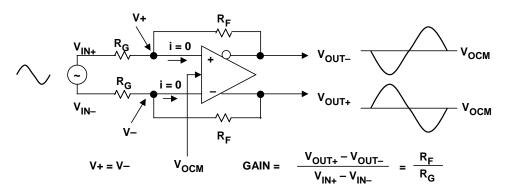

図 1 に示した回路は、図 2 に示す仮定と手順を使用することで解析することができます。まず、オペアンプ回路の DC 解析の場合と同様に、アンプの反転入力ノードと非反転入力ノードに流れる電流はゼロである(すなわち、入力インピーダンスが帰還抵抗の値と比較して非常に高い)と仮定します。次に、帰還回路によってアンプの非反転入力ノードと反転入力ノードの電圧は等しくなると仮定します。さらに、2 つの出力電圧は位相が 180 度異なり、 $V_{OCM}$ に対して対称であると仮定します。

- ◆ アンプの反転入力ノードと非反転入力ノードにおける入力電流はゼロ

- ◆ アンプの反転入力ノードと非反転入力ノードにおける入力電圧は等しい

- ◆ 出力電圧は 180 度位相が異なり、VocMに対して対称

- ◆ ゲインは G=R<sub>F</sub>/R<sub>G</sub>で決まる

図 2. 差動ドライバの電圧レベルの解析手法

ここで、 $R_F/R_G$  として決まる外付け帰還抵抗による整合がとれていないケースを考えます。その場合でも、内部のコモンモード帰還回路は出力の平衡を維持するよう働きます。そのため、2 本の出力信号は振幅が等しく、位相が 180 度異なったままになります。入力から出力への差動モード・ゲインは、帰還回路の不整合の程度に比例して所望の値からずれますが、出力は平衡のままで影響を受けることはありません。また、外付け抵抗の誤差による不整合は、回路の入力コモンモード信号除去性能(CMRR)を低下させます。これについては、多くの場合、4 個の抵抗とオペアンプで構成された従来型の差動アンプと同程度になります。

また、入力と出力のコモンモード電圧の DC レベルが異なる場合、抵抗の誤差による不整合によって、差動モード出力には微小なオフセット電圧が生じます。例として、以下のようなケースを考えてみます。

- ゲインは1 (G=1)

- 入力信号はグラウンドを基準とする

- 出力信号のコモンモード・レベルは 2.5V に設定されている

この条件で、許容誤差が 1%の抵抗を使用した場合、25mV の出力オフセット電圧(コモンモード・レベルの 1%に相当)が生じる可能性があります。抵抗の許容誤差が 1%の場合、入力 CMRR の最悪値は約 40dB、差動モード出力のオフセット電圧の最悪値は、2.5V のレベル変換を行う場合で 25mV となり、出力の整合が大きく劣化することはありません。

図 2 のような回路の場合、 $V_{IN+}$ と  $V_{IN-}$ から見た実効入力インピーダンスは、アンプを駆動する信号源がシングルエンドか差動であるかによって異なります。平衡差動入力信号の場合、 $V_{IN+}$ と  $V_{IN-}$ 間の入力インピーダンス  $R_{IN,dm}$  は次のような簡単な式で表すことができます。

$$R_{\text{IN.dm}} = 2 \times R_{\text{G}} \tag{\textsterling 5}$$

一方、シングルエンド入力信号の場合(たとえば、 $V_{IN-}$ がグラウンドに接続され、 $V_{IN+}$ に入力信号が印加される場合)、入力インピーダンス  $R_{IN.sem}$  は次式のようになります。

$$R_{\text{IN,sem}} = \left(\frac{R_{\text{G}}}{1 - \frac{R_{\text{F}}}{2 \times (R_{\text{G}} + R_{\text{F}})}}\right) \tag{$\not \equiv $6}$$

この回路をシングルエンド入力で用いる場合、入力インピーダンスはインバータ(反転回路)として接続される従来型のオペアンプより実質的に高くなります。これは、差動出力電圧の一部がコモンモード信号として入力に現れ、入力抵抗  $R_G$  を介して電圧をブートストラッピングする(押し上げる)ためです。

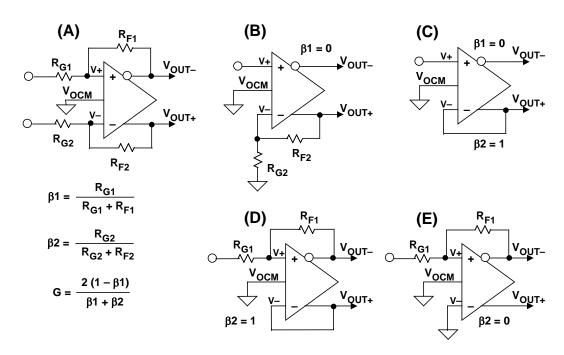

図 3 は、差動ドライバとして AD813x を使う場合に考えられる回路構成の例を示したものです。図 3 (A) は最も代表的な構成例であり、帰還率がそれぞれ  $\beta$ 1 と  $\beta$ 2 の 2 つの帰還回路を使用しています。ここで、帰還率は 0~1 の値になることに注意してください。

図 3. 差動ドライバ (AD813x) を使用した回路の構成例

図 3 (B) は  $V_{OUT}$  から  $V_+$  への帰還がない、 $\beta 1=0$  の構成です。この場合、 $V_-$  に帰還する  $V_{OUT}$  の量は  $\beta 2$  によって決まります。また、この回路は、相補出力(差動の片側出力)が追加されていること以外は、オペアンプを使用したごく一般的な非反転増幅回路の構成とほぼ同じです。全体のゲインは一般的な非反転増幅回路の 2 倍、すなわち  $G=2\times(1+R_{F2}/R_{G2})$ 、言い換えれば  $G=2\times(1/\beta 2)$  になります。

図 3 (C) は  $\beta$ 1=0、 $\beta$ 2=1 の回路です。この回路では外付け抵抗を使っておらず、G=2 になります。

図 3 (D) は  $\beta 2=1$  の回路です。 $\beta 1$  は  $R_{F1}$  と  $R_{G1}$  によって決まります。この回路のゲイン G は常に 2 より小さくなります。

最後の図3(E)の回路は、 $\beta 2=0$ の構成です。相補出力が追加されたこと以外は、オペアンプを使用した従来型の反転増幅回路と非常によく似ています。

#### 差動ドライバ/レシーバのアプリケーション

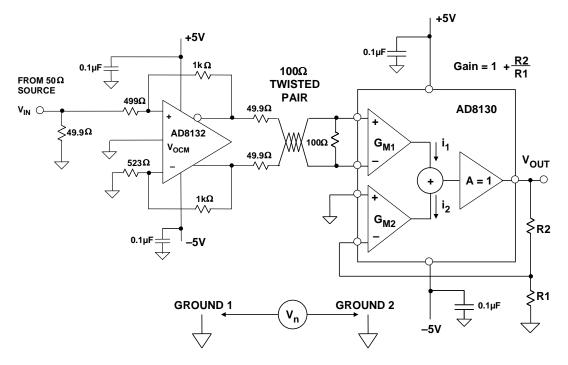

AD813x/ADA493x は、図 4 に示すような平衡差動ラインの駆動にも最適な製品ファミリーです。この例は「AD8132」によって特性インピーダンスが  $100\Omega$  のツイストペア・ケーブルを駆動するというものです。信号源とケーブルを終端する負荷によって生じる 2 倍の損失 (1/2) に減衰)を相殺するために、AD8132 を使って G=2 のドライバを構成しています。このような使い方では、AD8132 の帯域幅は約 160MHz となります。

図 4. 高速差動ドライバ/ライン・レシーバの応用回路例

ライン・レシーバには、「アクティブ・フィードバック」という独自のアーキテクチャを備えた差動レシーバ「AD8130」を使用しています。このアーキテクチャにより、10MHz において約70dB の CMRR が実現されます。AD8130 を使って G=1 の回路を構成した場合、-3dB 帯域幅は約270MHz となります。

AD8130 では、同一の  $g_m$ (入力相互コンダクタンス)ステージを 2 つ利用しています。各ステージからの出力電流がハイ・インピーダンスのノードで加算され、それがバッファリングされたうえで最終的な電圧出力となります。この系が成り立つには、2 つの  $g_m$ ステージの出力電流の値が等しく、符号が逆でなければなりません。言い換えれば、それぞれの入力電圧も値が等しく、符号が逆である必要があります。差動入力信号は一方のステージ( $G_{M1}$ )に入力され、もう一方( $G_{M2}$ )には従来型のオペアンプ回路と同様に負帰還をかけます。ゲインは G=1+R2/R1 で求められる値となります。このような仕組みにより、 $G_{M1}$  ステージの入力は終端されたツイストペア・ケーブルと正確に平衡し、最大の CMRR 性能を得ることができます。

このほかにも、CAT5(カテゴリ 5)のケーブルによる RGB(赤 - 緑 - 青)信号の伝送に使用可能なトリプルドライバとして「AD8133」、「AD8146」、「AD8147」、「AD8148」など、多数の製品が用意されています。

また、それに対応するトリプルレシーバとして「AD8143」、「AD8145」などが提供されています。なかでも、トリプルレシーバの「AD8123」とシングルレシーバの「AD8128」は、調節機能を備えるラインイコライザも内蔵しています。

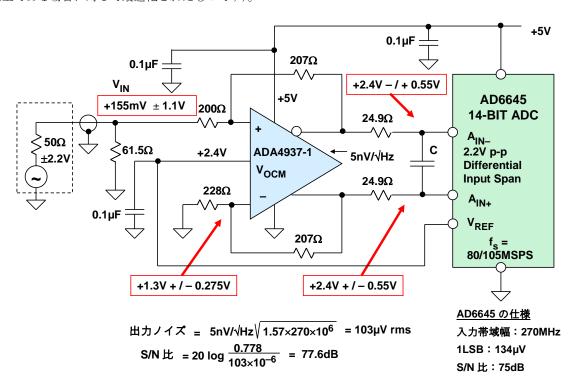

#### 14 ビット、80/105MSPS の ADC 用差動ドライバ回路

ここでは、分解能が 14 ビットで、サンプリング・レートが 80/105MSPS(メガサンプル/秒)の ADC「AD6645」用の入力回路として、差動ドライバ「ADA4937-1」を使用した具体例を紹介します。

差動ドライバの製品ファミリーである AD813x/ADA493x は、電圧ゲインが  $1\sim4$  ( $0dB\sim12dB$ )、周波数が 100MHz 程度までの DC 結合/AC 結合アプリケーションに適しています。特に、差動入力型 ADC のためにシングルエンド入力を差動出力に変換する低歪み/DC 結合のコンバータとして非常に重宝します。ADC のコモンモード入力電圧に合わせて正負(双極)信号のレベルを変換する処理には、各差動ドライバの  $V_{OCM}$  を利用することができます。DC ドライバの回路解析の方法や抵抗値の選択方法については、MT-076(英文資料)で詳細に説明しています。また、そのような設計を支援するツール「ADIsimDiffAmp」も提供されています。

ADA4937-1 は ADA493x ファミリーの最新製品であり、5V 単一電源での動作に最適化されています。図 5 において、ADA4937-1 は AD6645 の入力部に用いるレベル変換器として使用されています(同様の製品に「ADA4939-1」がありますが、こちらは電圧ゲインが 2 以上である場合に対して最適化されたものです)。

図 5. ADA4937-1 を使用して構成した AD6645 用の入力回路。 5V 単一電源の DC 結合アプリケーションとして実現しています。

## ミニ・チュートリアル

実際の設計では、すべての電圧が各デバイスの仕様の範囲内にあることを確認しなければなりません。ここでは、図 5 の回路について、信号の振幅とコモンモード電圧レベルの観点から詳細に解析してみます。

AD6645 の仕様は、コモンモード電圧が 2.4V(リファレンス電圧として  $V_{REF}$  ピンから出力されます)で、差動入力電圧範囲が  $2.2V_{P-P}$  となっています。すなわち、ADA4937-1 の各出力は、5V 単一電源で利用できるようにするために  $1.85V \sim 2.95V$  の範囲内になければなりません。

そのためには、入力信号を、5V 単一電源で動作する ADA4937-1 が許容できる  $1.025V \sim 1.575V$  の範囲内に収める必要があります。

この回路への入力はソース抵抗が  $50\Omega$  の信号源で駆動されます。シングルエンド構成であることから、ブートストラップされた入力インピーダンスは約  $267\Omega$  になります(図 5 では帰還抵抗が  $207\Omega$  となっていますが、まずは  $200\Omega$  であるとして考えます)。ゲイン設定に用いるこの  $267\Omega$  の抵抗と並列に接続された  $61.5\Omega$  の入力終端抵抗によって、全体のインピーダンスは約  $50\Omega$  になります。ここで、 $228\Omega$  の抵抗が反転入力と直列に挿入されていることに注意してください。これは、非反転入力における純インピーダンス( $200\Omega+61.5\Omega$ | $50\Omega=200\Omega+28\Omega=228\Omega$ )と整合させるためです。ゲイン設定用の  $200\Omega$  の抵抗に  $28\Omega$  の整合用の抵抗を直列に追加しなければ、インピーダンスは不平衡になり、望ましくない差動オフセット電圧が出力に現れます。

ゲイン調整用の抵抗を  $200\Omega$  から  $228\Omega$  に増やしたので、ゲインを 1 に維持するためには帰還抵抗を  $207\Omega$  に増やす必要があります。 実際の設計では、許容誤差が 1%の一般的な抵抗のうち最も計算値に近いものを使用します。 設計ツールの ADIsimDiffAmp を使えば、こうした設計を容易に行うことができます。 また、必要なゲインや信号源のインピーダンスを得るための抵抗値を算出することも可能です。 さらに、コモンモード入力 出力範囲が、 使用する差動ドライバ製品の仕様に反していないことを確認することもできます。

ADA4937-1 の出力ノイズ密度はわずか 5nV√Hz です。これは G=1 の場合の値で、帰還抵抗やゲイン設定抵抗による影響の分も含まれています。AD6645 のアナログ入力帯域幅(270MHz)までの積分を行うと、出力ノイズは 103μVrms となります。これは差動ドライバの S/N 比が 77.6dB であるということに相当します。なお、この回路にはノイズの低減のための外付けフィルタは設けていないので、ノイズの計算にあたっては、ADC の入力帯域幅全域にわたって積分しなければならないことに注意してください。

AD6645 の S/N 比は75dB であり、これを入力ノイズに換算すると  $138\mu Vrms$  となります。差動ドライバ ( $103\mu Vrms$ ) と ADC ( $138\mu Vrms$ ) のノイズを合わせると  $172\mu Vrms$  となるので、系全体の S/N 比は 73dB となります。

なお、AD6645 の全帯域幅を必要としない場合には、適切な値のキャパシタを追加して単極のノイズ除去フィルタを構成してもかまいません。

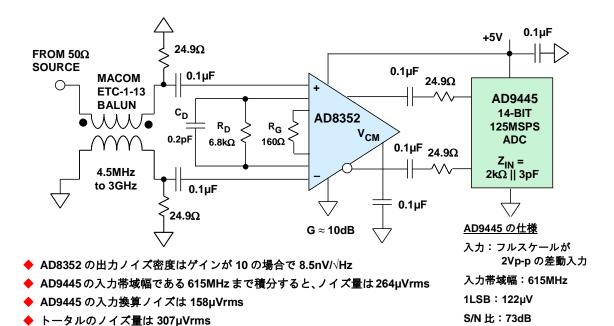

#### IF 用途向けの広帯域 AC 結合ドライバ

続いて、分解能が 14 ビットでサンプリング・レートが 125MSPS の ADC「AD9445」を用い、広帯域信号のデジタル化(IF 用途)を行う場合を例にとります。

入力バッファ有り

♦ S/N 比は 2Vp-p 入力の場合で 67dB

図 6. AD8352 を使用して構成した AD9445 用の入力回路。AD9445 の分解能は

AD9445 の入力帯域幅は 615MHz、SFDR は 100MHz の入力に対して 90dBc です。この ADC の入力部に用いる差動ドライバとしては、帯域幅が 2GHz で、3dB~25dB の範囲で抵抗によるゲインの設定が可能な「AD8352」を選択しました。この差動ドライバは、低ノイズ(ゲインを 10dB に設定したときの入力換算ノイズ密度が 2.7nV/ $\sqrt{\text{Hz}}$ )、低歪み(100MHz において 3 次高調波が 82dBc)で、入力周波数の下限は約 10MHz です。

14 ビットでサンプリング・レートは 125MSPS、AD8352 の帯域幅は 2GHz です。

図 6 に示したのは、AD9445 と AD8352 を用いて広帯域アプリケーションを構成する場合に最適な回路例です。このアプリケーションでは、ADC の入力帯域幅をできるだけ広く維持したいので、各ステージ間にはノイズ除去フィルタを設けていません。また、差動ドライバである AD8352 に合わせるために、バランによってシングルエンドの信号を差動信号に変換しています。AD8352 はシングルエンド入力で使用することも可能ですが(AD8352 のデータシートを参照)、図 6 のように差動入力で使用したほうが優れた歪み特性が得られます。AD8352 の 3 次相互変調特性を最適化するために、 $C_D/R_D$ で構成される回路を使用しています。 $C_D/R_D$  それぞれの値は、ゲインに対する要求に基づいて選択することになります(AD8352 のデータシートを参照)。

この回路では、SFDR は、105MSPS でサンプリングされた 98.9MHz の入力信号に対して 83dBc となります。G=10 の場合、AD8352 の出力ノイズ密度は  $8.5nV/\sqrt{Hz}$  です。出力ノイズは、AD9445 の入力部にノイズ除去フィルタが存在しないため、同 ADC の入力帯域幅である 615MHz まで積分して求める必要があります。差動ドライバと ADC を合わせた系全体の S/N 比は 67dB になります。

#### 参考資料

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 3.

- 3. Walt Kester, *Analog-Digital Conversion*, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 6. Also available as *The Data Conversion Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 6.

- Walt Kester, High Speed System Applications, Analog Devices, 2006, ISBN-10: 1-56619-909-3, ISBN-13: 978-1-56619-909-4, Chapter 2.

- 5. ADIsimDiffAmp: アナログ・デバイセズが提供する差動アンプ向けのインタラクティブなオンライン設計ツール