LTC3309A

ADI 中国在线商城焕新登场

支持非整包购买、人民币支付、报关无忧、在线客服专业高效!

LTC3309A

推荐新设计使用采用 2mm x 2mm LQFN 封装的 5V、6A 同步降压型 Silent Switcher

- 产品模型

- 22

Viewing:

产品详情

- 与LTC3307(3A)和LTC3308(4A)引脚兼容

- 高效率:8mΩ NMOS,31mΩ PMOS

- 可编程频率:1MHz - 3MHz

- 小型电感和电容

- 峰值电流模式控制

- 22ns最短导通时间

- 宽带宽、快速瞬态响应

- Silent Switcher® 架构

- 超低EMI辐射

- 低纹波突发工作模式(Burst Mode®),IQ为40µA

- 可在过载情况下安全地承受电感饱和

- VIN 范围:2.25V至5.5V

- VOUT 范围:0.5V至VIN

- VOUT 精度:±1%(全温度范围)

- 精准400mV使能阈值,关断时1µA

- 电源良好指示、内部补偿和软启动

- 散热增强型2mm x 2mm LQFN封装

- 通过AEC-Q100汽车应用认证

LTC3309A是一款非常小巧、高效率、低噪声、单片同步6A降压型DC/DC转换器,采用2.25V至5.5V输入电源。该稳压器在1MHz至3MHz的开关频率下使用恒定频率峰值电流模式控制,最小导通时间低至22 ns,可通过小型外部元件实现快速瞬态响应。Silent Switcher架构可较大程度地降低EMI辐射。

LTC3309A 可在强制连续或跳脉冲模式实现低噪声运行,或在轻负载下以低纹波突发模式工作以实现高效率,非常适合电池供电系统。该IC可将输出电压调节到最低500mV。其他特性包括输出过压保护、短路保护、热关断、时钟同步以及高达100%占空比运行以实现低压差。该套件采用12引脚2 mm × 2 mm × 0.74 mm纤薄LQFN封装,并带有裸露焊盘以降低热阻。

对于需要更快上电的应用,LTC3309A-7支持更快上电和软启动。

应用

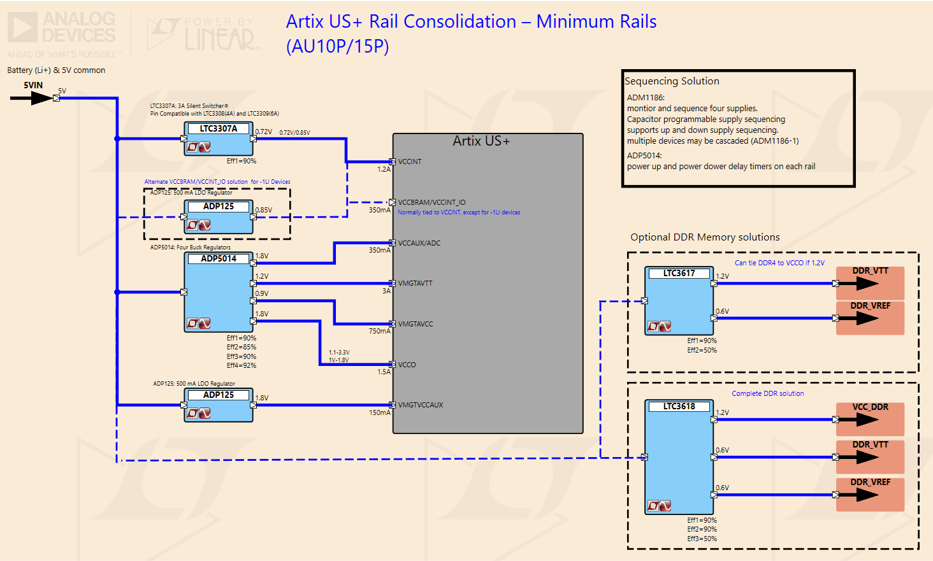

- 光网络、服务器、电信

- 汽车、工业、通信

- 分布式直流电源系统(POL)

- FPGA、ASIC、微处理器内核电源

- 电池供电系统

工具及仿真模型

LTspice 1

LTpowerCAD 1

LTpowerCAD中提供以下器件的设计工具:

- LTC3309A

- LTC3309B

LTspice®是一款强大高效的免费仿真软件、原理图采集和波形观测器,为改善模拟电路的仿真提供增强功能和模型。

LTpowerCAD®是一种电源设计程序,它选择功率级元件,提供详细效率信息,显示快速环路波特图稳定性和负载瞬态分析,并可导出至LTspice进行仿真。

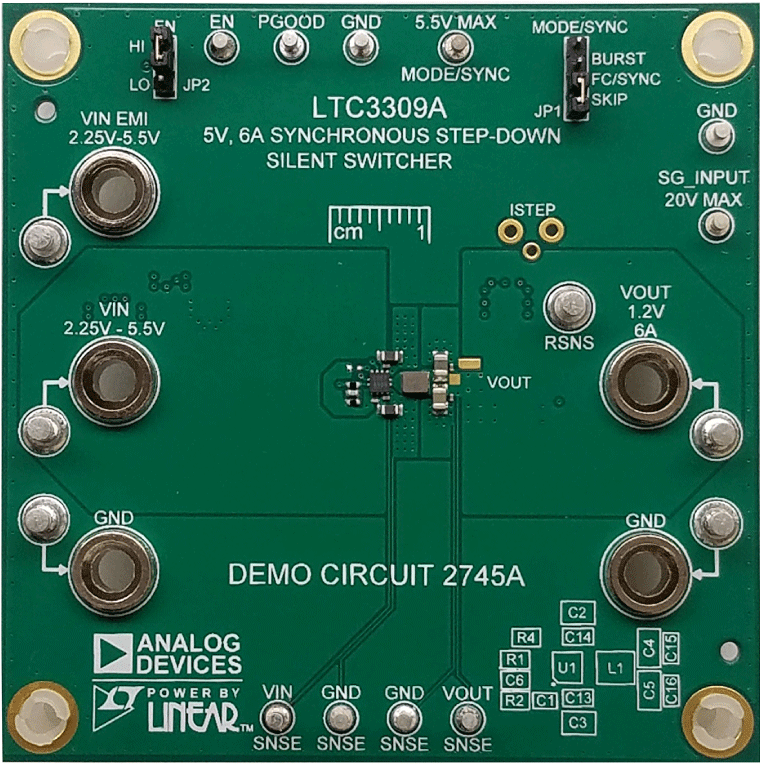

评估套件

参考电路

最新评论

需要发起讨论吗? 没有关于 LTC3309A的相关讨论?是否需要发起讨论?

在EngineerZone®上发起讨论