概要

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- EVAL-ADF4350EB1Z ($224.70) ADF4350 evaluation board used to evaluate this circuit. Please see "Circuit Evaluation & Test" section for set up information.

デバイス・ドライバ

コンポーネントのデジタル・インターフェースとを介して通信するために使用されるCコードやFPGAコードなどのソフトウェアです。

ADF4350 GitHub Linux Driver Source Code

ADF4350 GitHub no-OS Driver Source Code

ADF4350 IIO Wideband Synthesizer GitHub Linux Driver Source Code

参考資料

-

CN-01472010/11/16PDF260 kB

-

Get the Best from Your Low-Dropout Regulator1999/02/18

回路機能とその特長

この回路では、ワイドバンドのPLLとワイドバンド電圧制御発振器(VCO)が集積化されたデバイスに電源を供給するために、低ノイズ・低ドロップアウト(LDO)のリニア・レギュレータが使われています。ワイドバンドVCOは、電源電圧のノイズに対する感度が高い傾向にあります、したがって最良の性能を得るためには、超低ノイズのレギュレータを使用することを推奨します。

図1に示した回路は、137.5MHz~4400MHzの周波数を生成できる、フラクショナルN PLLとVCOを完全集積化したADF4350を使っています。 ADF4350, における適切な位相ノイズ性能を得るため、超低ノイズの3.3V LDOレギュレータ ADP150を電源としています。

ADP150の積分rmsノイズ(10Hz~100kHz)はわずか9μVrmsと小さく、VCO位相ノイズの最適化を手助けしてくれ、さらにVCOでのプッシングの影響を低減できます(VCOの電源電圧変動除去と等価)。

図2は、ADF4350の電源としてLDO レギュレータADP150を用いた、評価用ボードの写真を示しています。ADP150は、ローコストで非常に小型なパッケージに収められており、業界最小の低ノイズを実現しています。この製品は、0.8mm×0.8mm、0.4mmピッチの4ボールWLCSPまたは使いやすい5ピンTSOPパッケージを採用しています。したがってADP150を設計に採用することで、システム全体のコストとボード面積への影響を最小限することができ、位相ノイズについても大幅な改善を期待できます。

回路説明

ADF4350はワイドバンドのPLLとVCOで構成されており、VCOは3つのマルチバンドVCOから構成されています。各VCOは約700MHzの周波数範囲をカバーしています(各VCO間はいくらかのオーバーラップがあります)。さらに低い周波数は、出力デバイダによって生成できます。

VCOのプッシング特性は、ADF4350のVTUNEピンに定常のチューニング電圧を与え、電源電圧を変化させることで、周波数が変化することによって計測します。プッシング指数(P)は、表1に示されているように、周波数変動量を電圧変動量で割った値になります。

| VCO Frequency (MHz) | VTune (V) | VCO Pushing (MHz/V) |

| 2200 |

2.5 |

0.73 |

| 3300 |

2.5 |

1.79 |

| 4400 |

2.5 |

5.99 |

PLLシステムにおいて、より高いVCOプッシング指数であると、電源電圧のノイズがVCOの位相ノイズを劣化させてしまうことになります。もしVCOプッシング指数が低い場合、電源電圧のノイズはそれほど大きく位相ノイズを劣化させません。しかしVCOプッシング指数が高い場合には、電源のノイズの多い電圧が、位相ノイズへ測定可能なほどの影響を与えることになります。

プッシングが最大となるVCO出力周波数4.4GHzにおいて、異なるレギュレータを使った場合の比較実験を行ってみました。

ADF4350のRevA評価用ボードではレギュレータADP3334が使われています。このレギュレータの積分rmsノイズは27μVです(10Hz~100kHzの積分)。これとEVAL-ADF4350EB1Z RevBに、積分rmsノイズが9μVの ADP150を搭載した場合と比較します。電源電圧ノイズからの影響を測定するために、VCOの位相ノイズをより強調できる実験として、狭帯域のPLLループ・フィルタ(10kHz)を使用しました。このセットアップを図3に示します。更に詳細な周波数ごとの出力ノイズ密度はADP3334とADP150のそれぞれのデータシートから比較できます。

図4では、ADP3334レギュレータを用いた場合のノイズ・スペクトラム密度が100kHzのオフセットで100nV/√Hzであることが示されています。ADP150での同じオフセット(図5)では25nV/√Hzを示しています。

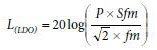

電源電圧ノイズによる位相ノイズの劣化を計算する式は以下のようになります。:

この式で、L(LDO)はオフセットfm; でのレギュレータからVCOの位相ノイズ(dBc/Hz)へ影響する量、PはVCOプッシング指数(単位:Hz/V)、Sfm; は対応するオフセット周波数(V/Hz)でのノイズ・スペクトラム密度、fmは1Hzあたりのノイズ・スペクトラム密度を測定したオフセット周波数です。

電源からのノイズの影響度は、VCO自体のノイズ量(これ自体は非常にノイズの小さな電源を用いて測定されます)とrss(自乗和平方根)合計され、使用するレギュレータでのVCO出力での全体のノイズが得られます。

つまり総合VCO位相ノイズを求めるために、それぞれのノイズの影響度がrss(自乗和平方根)されるわけです。:

この例では、100kHzオフセットでのノイズ・スペクトラム密度、6MHz/Vのプッシング指数が使われ、理想的な電源でのVCO単体ノイズとして-110dBc/Hzが得られています。

専用の信号源アナライザ(例:Rohde & Schwarz社のFSUP)を使って、VCOの位相ノイズを比較してみました。100kHzオフセットで、ADP3334では-102.6dBc/Hz(図6)が得られ、同じ構成でADP150では-108.5dBc/Hz(図7)が得れらています。

| ADP3334 | ADP150 | |

| Noise contribution from regulator (nV/√Hz) |

150 |

25 |

| Noise contribution from regulator (dBc/Hz) |

-104 |

-119.5 |

| Total calculated noise at VCO output (dBc/Hz) |

-103 |

-109.5 |

| Measured VCO nose at 100 kHz offset (dBc/Hz) |

-102.6 |

-108.5 |

また、積分位相rmsノイズも1.95°から1.4°に改善されています。測定結果は計算結果と非常に相関性が高く、ADF4350の代わりにADP150を使うことの有利さが明確になっています。

この回路ノートに関する完全な設計サポート・パッケージはhttp://www.analog.com/CN0147-DesignSupportで入手できます。

バリエーション回路

必要に応じて、より大きな電源間のアイソレーションを得るために、さらにレギュレータを追加することもできます。またLDOレギュレータADF150をADF4350全体の電源として使うことも出来ます。しかしこのような場合、単一のADP150の規格上の最大電流を越えることのないように注意が必要です。これはADF4350の設定を最小パワー出力に選択することで、実現も可能です。

回路の評価とテスト

この回路ノートCN-0147に記載されている回路評価には、EVAL-ADF4350EB1Zが使用されており、これによって即座にセットアップおよび評価が可能です。EVAL-ADF4350EB1Zボードは、標準のADF4350プログラミング・ソフトウエアを使っており、これは評価用ボードに添付されているCDに入っています。

必要な装置

この回路ノートCN0147には、回路の説明、回路図およびセットアップのブロック図が含まれています。ユーザ・ガイドUG-109には、EVAL-ADF4350評価用ソフトウエアのインストール方法および使用法が説明されています。またUG-109には、ボードのセットアップ方法、ボードの回路図、レイアウト図および部品表も含まれています。

評価開始にあたって

この回路ノートCN0147には、回路の説明、回路図およびセットアップのブロック図が含まれています。ユーザ・ガイドUG-109には、EVAL-ADF4350評価用ソフトウエアのインストール方法および使用法が説明されています。またUG-109には、ボードのセットアップ方法、ボードの回路図、レイアウト図および部品表も含まれています。

機能ブロック図

回路ノートCN-0147には、図3にテスト・セットアップの機能ブロック図も含まれています。

セットアップとテスト

各装置のセットアップ後、出力信号のスペクトラム純度を測定するためには、標準的なRFテスト方法を使ってください。