概要

完全差動アンプ(FDA)は差動入力と差動出力を備えたデバイスで、直流(DC)入力電圧により出力コモン・モードを独立して制御します。FDAは、データ・アクイジション・システムにおけるA/D変換のフロント・エンドに使われ、信号を次段(通常はA/Dコンバータ(ADC))に合わせて適切なレベルに調整します。FDAは一般にシングル・チップで提供され、電源電圧が小さいので出力ダイナミック・レンジも制限されます。本稿では、コモン・モード出力を調整可能な、高電圧低ノイズの複合型FDAの設計方法を示します。また、FDAのノイズと、そのノイズが高性能データ・アクイジション・システムのシグナル・チェーン全体のS/N比(SNR)に与える影響についても、詳しく分析します。

はじめに

広い出力ダイナミック・レンジと、高性能FDAと同等の交流(AC)性能とが求められるアプリケーションには、高電圧のFDAを使用する必要があります。例えば、入力範囲の広い高精度データ・アクイジション・シグナル・チェーンのテストと評価には、高電圧のFDAが必要となる場合があります。一般に、今日使われているほとんどのFDAは電源電圧が小さいので、出力電圧範囲も狭くなっています。これらのFDAは、一般に単電源を使用する高性能ADCの入力を駆動するのに適しており、最良のS/N比と全高調波歪み(THD)に迫る優れたAC性能を備えています。しかし、比較的高電圧で使われる多くの高精度オペアンプのような、レールまでの十分な振幅、オフセット、バイアス電流、およびドリフトは備えていません。ただ、ADCを駆動するのに必要な条件は満たしているので、これらの点が問題になることはまったくありません。アナログ・デバイセズは、様々なアプリケーションに使用されるADCドライバを数多く提供しています。

FDAは、シングルエンド入力または差動入力のどちらにも対応可能で、ゲインがあり、また、一般に出力コモン・モード入力ピン(VOCM)を介してコモン・モードを調整可能な差動出力を備えています(図1を参照)。FDAには出力ダイナミック・レンジが広いという利点がありますが、これは、実現可能な最大出力が、出力レールの2倍の大きさを持ち、ノイズの影響を受けにくく、そして偶数次高調波歪みが小さい、という理由によります。例えば、±5VのFDAは、±10V(20V p-p)に近い最大ピークtoピーク出力を生成することができます。

図1. FDA

したがって、±18Vの回路は60V p-p以上の出力を生成できることになります。ADA4625-1/ADA4625-2は非常に良好なノイズ性能と歪み性能を備えた低ノイズのJFETアンプで、最大±18Vの広い電源範囲を使用できます。DCおよびAC性能に関するアプリケーションの要求をすべて満たすことがFDAに求められる場合には、ディスクリート・オペアンプを使ってFDAを設計しようとしても難しい作業になりがちです。

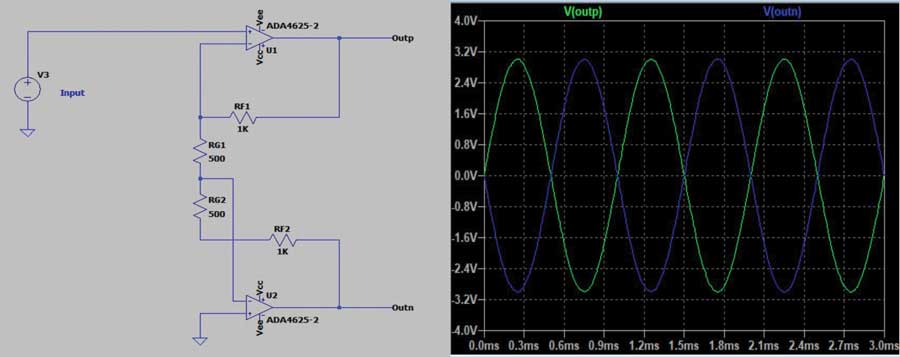

差動アンプを作成するための1つの明らかな方法は、非反転アンプと反転アンプを使用して、出力に差動信号を生成することです(図2)。この方法の欠点は、これら2つのアンプU1とU2が完全には対称な動作をしないことで、これは性能が最適化されないことを意味します。

図2. シングルエンド入力/差動出力回路

これを改善する方法は、基本的な差動アンプと同様に2つのオペアンプを差動方式で構成して帰還抵抗とゲイン抵抗をU1とU2の間で共有し、ゲインをAv = (RG + 2RF)/RGとすることです(図3を参照)。

図3. 差動アンプ回路

この構成は簡単なゲイン回路でバランスの取れた出力を提供し、ゲイン設定抵抗RGを通じて容易にゲインを変更することができます。しかし、入力がシングルエンドの場合は、差動出力の振幅が対称になりません(図4を参照)。非対称出力の場合は、一方の出力がレールに達する前に他方の出力がレールに達してしてしまうので、出力範囲が大幅に制限されます。これは、抵抗ゲイン回路を変更して出力を対称にすることで解決できます(図5)。図では、ゲイン抵抗を2つ(RG1とRG2)に分け、更にRG1とRG2の中央からU2のフィードバックを取ることで、出力を対称にしています。ゲインは次式で与えられます:Av = (RG1 + RG2 + RF1 + RF2)/RG1。

図4. 非対称出力

図5. 対称出力

調整可能な出力コモン・モードの追加

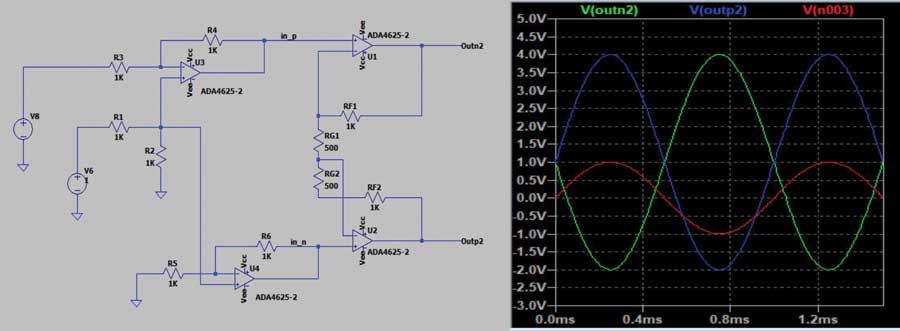

調整可能なコモン・モードを追加する方法は2つあります。1つめは2個のADA4625デバイスを使ってそれぞれの入力にVOCMアンプを追加する方法で(図6と図7)、2つめはADA4625-1をVOCMアンプとして1個だけ使用する方法です(図8と図9)。以下に述べるように、これらの方法にはそれぞれ長所と短所があります。

アンプU3とU4を追加することにより、そこに印加される任意のDC入力電圧(V6)が正入力と負入力に加えられるようになります。それぞれの入力には同じ電圧が加わるので、それらの電圧はDCコモン・モードとして出力に現れます。しかしU3とU4にはノイズが追加され、これがU1とU2の差動段によって更に増幅される他、U3とU4は回路に新たな消費電力を発生させます。ただしこれは非常に直接的な作用であり、全体的なシグナル・ゲインには影響しません。図6に示す回路のシグナル・ゲインはAv = (RG1 + RG2 +RF1 + RF2)/RG1で与えられ、図7の回路のゲインはAv = (RG + RF1 +RF2)/RGで与えられます。

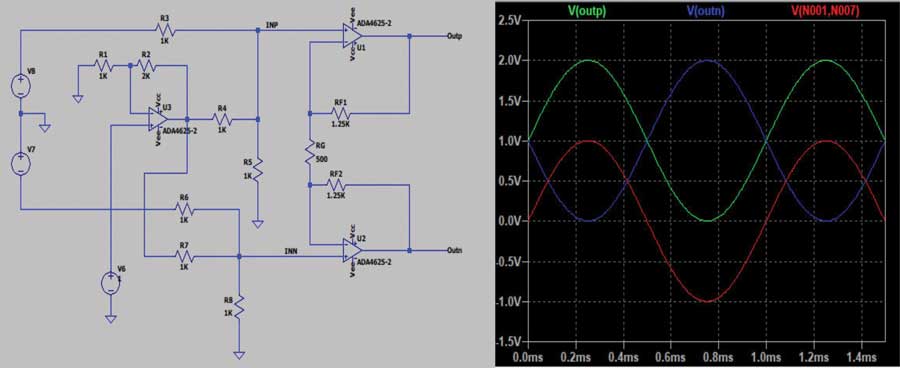

図6. 2個のアンプでコモン・モードを調整可能なシングルエンド入力/差動出力回路。右側のプロットは、LTspice®による入力(赤)と出力(青と緑)のシミュレーションです。

図7. 2個のアンプでコモン・モードを調整可能な差動入力/差動出力回路。右側のプロットはLTspiceによる入力(赤)と出力(青と緑)のシミュレーションです。

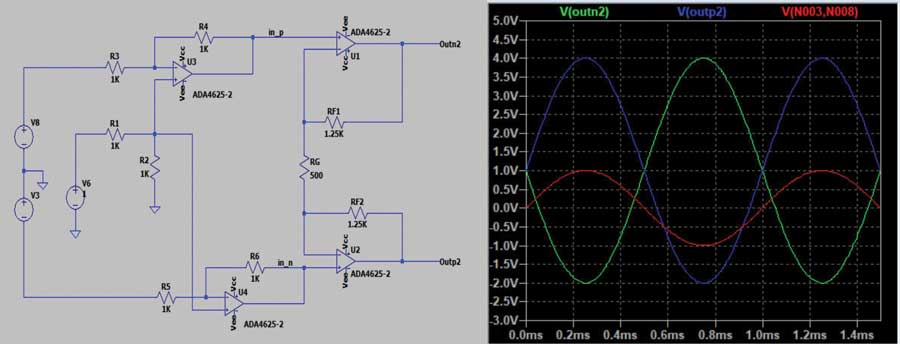

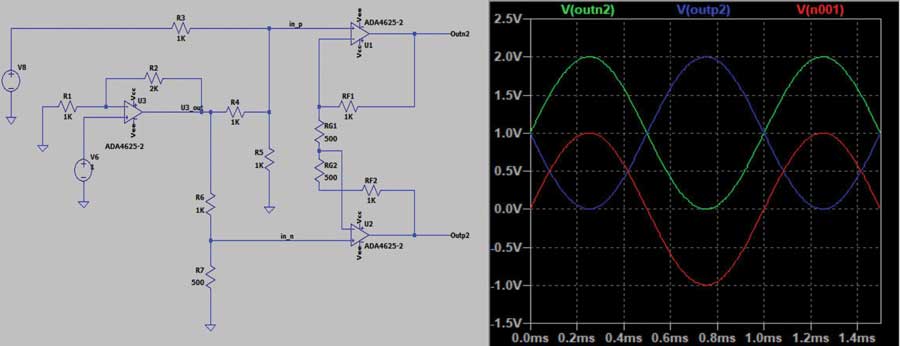

調整可能なVOCMを追加するもう1つの方法は、アンプを1個追加して、その出力をそれぞれの入力に接続することです。この方法の利点は、使用部品数が少ないこと、アンプが1個だけであること、抵抗の数が少ないこと、そして追加部品から生じるノイズが少ないことなどです。実際、抵抗分圧器R4~R7で生じるノイズを除き、U3の出力換算ノイズはコモン・モードとしてU1とU2の入力に現れるので、U3によってノイズが増えることはありません。抵抗R3~R7は、入力信号にVOCMを加算する抵抗加算回路を形成します。R3~R5は正の入力信号にコモン・モードを追加し、R6~R8(シングルエンド入力ではR6とR7)は負の入力にコモン・モードを追加します。同じ抵抗回路が入力信号を減衰させる点に留意してください。これは、回路の全体的なシグナル・ゲインを低下させます。図8の回路の全体的なシグナル・ゲインはAv = [(RG1 + RG2 + RF1 + RF2)/RG1][(R4//R5)/(R4//R5 + R3)]で与えられ、図9の回路のゲインはAv = [(RG + RF1 + RF2)/RG][(R4//R5)/(R4//R5 + R3)]で与えられます。ノイズ分析のセクションでは、何がノイズの主要発生源になるのかを説明し、また、必要とされる全体的ゲインと設計者にとって重要なその他の要素に応じ、2つめの方法を使ってVOCMを追加する方が最初の方法より有利なのかどうかについての検討を示します。

図8. 1個のアンプでコモン・モードを調整可能なシングルエンド入力/差動出力回路。右側のプロットはLTspiceによる入力(赤)と出力(青と緑)のシミュレーションです。

図9. 1個のアンプでコモン・モードを調整可能な差動入力/差動出力回路。右側のプロットはLTspiceによる入力(赤)と出力(青と緑)のシミュレーションです。

ノイズ分析

ノイズは、最終的にシステムのダイナミック・レンジとS/N比に制約を加えるので、高性能高精度のデータ・アクイジション・シグナル・チェーンに大きく影響する重要な検討事項です。16ビットADCの理論的S/N比は–98dBで(6.02N + 1.76dB、N =ビット数)、これは、4.096Vp(または8.192V p-p)出力時の等価ノイズが約36μV rmsであることを意味します。このノイズは量子化ノイズと呼ばれ、ADCの量子化誤差により発生します。–98dBのS/N比は16ビット・システムの理論的限界値で、これより悪化する場合、それはすべてADCの入力や周辺回路に加わるイズによるものです。以下は、シングル・アンプおよびデュアル・アンプ両方のVOCM完全差動回路について、回路内の各部品によって生じるノイズを分析したものです。図10は、2アンプVOCMを使用するFDA回路のノイズ・モデルです。

図10. 2アンプVOCMノイズ・モデル

差動段 - U1とU2によるノイズ

ADA4625-1/ADA4625-2の電流ノイズ密度は1kHzで4.5fA/√Hzという極めて低い値です。その一方、入力換算(RTI)電圧ノイズは1kHzで約3nV/√Hzであり、ここでは広帯域ノイズと見なせます。出力に差動的に現れるU1とU2の電流および電圧ノイズの合計を実効値で表すと、次のようになります。

ここで、eNv,U1U2はU1とU2のRTI電圧ノイズによる出力電圧ノイズで、eNI,U1U2は入力電流ノイズによる出力電圧ノイズです。RTI電圧ノイズは入力における二乗和平方根(RSS)を取ることによって結合され、ゲインおよび帰還回路RFおよびRGによって増幅されます。同様に、電流ノイズもRSSが取られてRGによって電圧ノイズに変換され、その後増幅されて出力されます。入力電流ノイズは非常に小さいので全体に占める率は小さく、出力においてはアンプの抵抗および電圧ノイズが主要なノイズ発生源となります。

U1とU2のゲインおよび帰還回路(RF1、RF2、およびRG)による出力ノイズは、次のようになります。

ここで、室温における1kΩの熱ノイズは4.06nV⁄√Hzです。

式(1)と式(3)を使い、U1とU2の電圧ノイズおよびその帰還抵抗回路ノイズを出力で組み合わせて電流ノイズを無視すると、次式が得られます。

前述の内容から、ゲインが大きい場合は、アンプの電圧ノイズが容易に支配的な存在になり得ることが分かります。RGの値を小さくすれば(例えば500Ω)、抵抗によるノイズを大幅に減らすことができます。

VOCM回路 – U3とU4のノイズ

次に、図10のVOCM回路からノイズを分析していきます。抵抗ノイズを含むVOCM回路(U3とU4)からの合計ノイズは、各アンプからの入力電流ノイズを無視すると次のようになります。

ここで、R1//R2はR1とR2の並列の組合せです。この場合も、前述の内容から、U3とU4からの合計ノイズはアンプの電圧ノイズと抵抗ノイズが支配的であることが明らかです。抵抗の値を小さく抑えて全体のノイズに対する影響を最小限にし、アンプを主要なノイズ発生源とするのは優れた方法です。VOCM回路の出力からのノイズは差動段の入力に現れ、結果として差動段により増幅されて出力されます。

VOCM回路 – シングル・アンプU3のノイズ

既に述べたように、U3の出力におけるノイズはコモン・モードとしてU1とU2の入力に現れるので(図11にはinpおよびinnとして示されています)、差動段のノイズは増えません。ノイズの増加は抵抗R3~R8で生じますが、詳しく見ると、これらの抵抗は差動段への各入力で3つが並列になっていて、R3~R5が正入力、R6~R8が負入力にありますが(図11c)、これも抵抗によるノイズを最小限に抑えています。

図11. 1アンプVOCMノイズ・モデル

これら2つの回路(デュアル・アンプとシングル・アンプのVOCM回路)のうちでは、ノイズの発生は後者の方がはるかに少なくなります。その欠点は全体的なシグナル・ゲインが小さくなることですが、消費電力は小さくなり、アンプの数も少なくなります。式(7)と式(8)は、それぞれ図11に示すVOCM回路の出力におけるノイズと、U1とU2への差動段変化の出力における、それに対応したノイズ寄与分を示しています。

すべての要素を結合 – ADCシグナル・チェーンの全体的なS/N比

ADC信号の合計S/N比は、アナログ・フロント・エンド(AFE)とADCによって生じるノイズの合計によって決まりますが、これには他の発生源からのノイズが含まれる場合もあります。ADCシグナル・チェーンの合計S/N比は次式で得られます。

ここで、VREFは、バイポーラ出力ADCの正のフルスケールとします。

一般に、シグナル・チェーンの合計S/N比は図12のようにまとめることができます。

図12. データ・アクイジション・フロント・エンドのシグナル・チェーン

ADCのノイズは、AFEから入力されるノイズと組み合わされることによって、合計S/N比をADCの理論値または理想値より低下させます。AFEのノイズをADCのノイズと組み合わせるには、次式に従ってADCのS/N比を等価実効値積分ノイズに変換する必要があります。

例えば、ADAQ7767-1のS/N比の代表値は–106dBで、その等価実効値ノイズは14.5μVです。

ADAQ7767-1は24ビットのデータ・アクイジション・ソリューションで、ADCドライバとアンチエイリアシング(折返しノイズ防止)フィルタを内蔵しています。そのゲインは、1、0.364、0.143V/Vです。このデバイスは250kSPSで110kHzのノイズ帯域幅(BW)を備えており、その急峻なカットオフはデジタル・ブリックウォール・フィルタに支配されます。ADA4625-1/ADA4625-2の広帯域電圧ノイズの代表値が3.3nV⁄√Hzだとすると、ノイズ・ゲインが6の図13の差動段(U1とU2)により生じるノイズは、次のようになります。

eN,V_U1U2 = [√2(3.3nV)2] (500Ω + 1.5kΩ + 1kΩ)/500Ω =28nV⁄√Hz。U1とU2のRTIノイズによる。式(1)を使用。

eN,RES_U1U2 = √[2.87nV(6)]2 + (4nV)2 + (4.97nV)2 =18.4nV⁄√Hz。抵抗ゲイン回路による。式(3)を使用。

eN,U1U2 = √(28nV)2 + (18.4nV)2 = 33.5nV⁄√Hz。差動段で生じる合計出力ノイズ。

図13. 高電圧入力のADAQ7767-1高精度シグナル・チェーン

式(8)で、3つの並列抵抗(1kΩ)の等価値を差動段の入力に対して333.3Ω、ノイズを2.3nV⁄√Hzとすると、次のようになります。

eNO,VOCM_U3 = 6√2(2.3nV)2 = 19.5nV⁄√Hz。抵抗R3~R8による出力ノイズ発生回路。

したがって、ADAQ7767-1の入力に現れる合計出力ノイズは次のようになります。

ADAQ7767-1の入力ゲイン段は0.143V/Vに設定されており、入力範囲は±28V(56V p-p)です。入力回路のノイズをデバイスのノイズと組み合わせ、S/N比の代表値–106dBは14.5μVrmsのノイズにあたると仮定すると、次のような結果が得られます。

入力回路が合計システム・ノイズに影響する割合は非常に小さく、これはADAQ7767-1の入力ゲインが小さいことも理由の1つになっています。なお、帯域幅の乗算時にはフィルタの帯域幅調整係数を使いませんが、これは110kHzがブリックウォール特性を備えたデジタル・フィルタだからです。S/N比の代表値が–106dBなので、結果として得られるシグナル・チェーンのS/N比は次のようになります。

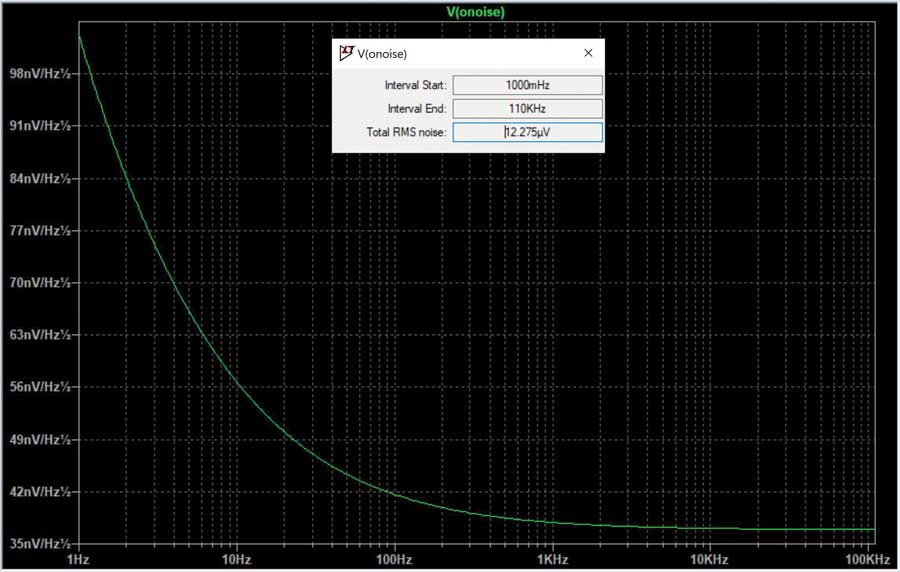

LTspiceを使って図13の入力回路のノイズをシミュレーションすると( 図1 4 )、合計実効値ノイズは帯域幅1 1 0 k H zで12.3μV rmsとなります。これに0.143V/Vのゲインを乗じると、ADAQ7767-1の入力におけるノイズは1.8μV rmsとなりますが、これは合計入力ノイズの計算値と同じです。

図14. 図13に示すADAQ7767-1入力回路のLTspiceノイズ

ADAQ7767-1でその他のゲインを使用した場合のシグナル・チェーン全体のS/N比を表1に示します。

| 合計 AFE(FDA)ノイズ(Vrms) | 帯域幅、Hz(ブリックウォール) | ADAQ7767-1のゲイン | 合計 ADC入力ノイズ(V rms) | 合計 システム・ノイズ(V rms) | 全体的なS/N比(dB) |

| 3.88E-08 | 1.10E+05 | 0.143 | 1.84E-06 | 1.46E-05 | –105.94 |

| 3.88E-08 | 1.10E+05 | 0.364 | 4.68E-06 | 1.52E-05 | –105.58 |

| 3.88E-08 | 1.10E+05 | 1 | 1.29E-05 | 1.94E-05 | –103.49 |

ここでは、図13に示すシングル・アンプのVOCM回路だけを使用しました。この回路は、ノイズ性能に大きな影響を与えることなく、フロント・エンド・シグナル・チェーン・システムに高い入力電圧を供給するために使用できます。デュアル・アンプのVOCM回路も、同じ全体的信号ゲインで同様のノイズ性能を実現できます。ノイズ分析のセクションに示したノイズの式(VOCM回路のU3およびU4ノイズ)は、デュアル・アンプVOCM回路の出力における合計ノイズの計算に使用できます。また、シグナル・チェーンの合計S/N比の計算にも同じ方法と概念を適用できます。

まとめ

本稿に示した回路にADA4625-1/ADA4625-2を使用して創出される複合型FDAは、入力範囲の広い高性能データ・アクイジション・シグナル・チェーンに使用できる、コモン・モードを調整可能な低ノイズ高電圧出力のソリューションを実現します。差動段の帰還回路を適切に設定することによって、シングルエンド入力にも差動入力にも対応可能です。シングル・アンプVOCM回路は、消費電力が小さくアンプの数も少ないので、デュアル・アンプVOCM回路を上回る利点を備えています。ここで述べた例は、ゲインが小さければ、ADAQ7767-1シグナル・チェーンの全体的なS/N比はFDA回路による大きな影響は受けない、ということを示しています。その入力範囲は±4.096V、±11.264V、および±28Vで、それぞれに対応するゲインは1V/V、0.364V/V、および0.143V/Vです。つまり、最小ゲインの場合が最も入力範囲が広く、ソリューションを最大限に利用することができます。